54AC11241中文资料

SN54LS123中文资料

RETRIGGERABLE MONOSTABLE MULTIVIBRATORSThese dc triggered multivibrators feature pulse width control by three meth-ods. The basic pulse width is programmed by selection of external resistance and capacitance values. The LS122 has an internal timing resistor that allows the circuits to be used with only an external capacitor. Once triggered, the ba-sic pulse width may be extended by retriggering the gated low-level-active (A)or high-level-active (B) inputs, or be reduced by use of the overriding clear.•Overriding Clear Terminates Output Pulse•Compensated for V CC and T emperature Variations•DC Triggered from Active-High or Active-Low Gated Logic Inputs •Retriggerable for Very Long Output Pulses, up to 100% Duty Cycle •Internal Timing Resistors on LS122SN54/74LS122 (TOP VIEW)(SEE NOTES 1 THRU 4)SN54/74LS123 (TOP VIEW)(SEE NOTES 1 THRU 4)NOTES:1.An external timing capacitor may be connected between C ext and R ext /C ext (positive).2.To use the internal timing resistor of the LS122, connect R int to V CC .3.For improved pulse width accuracy connect an external resistor between R ext /C ext and V CC with R int open-circuited.4.To obtain variable pulse widths, connect an external variable resistance between R int /C ext and V CC .R ext/CR ext/C ext 11ĂRext/2CLRC extNC Ċ NO INTERNAL CONNECTION.。

ADS1240E;ADS1241E;ADS1240E1K;ADS1240E1KG4;ADS1241E1KG4;中文规格书,Datasheet资料

DESCRIPTION

The ADS1240 and ADS1241 are precision, wide dynamic range, delta-sigma, Analog-to-Digital (A/D) converters with 24-bit resolution operating from 2.7V to 5.25V power supplies. The delta-sigma A/D converter provides up to 24 bits of no missing code performance and effective resolution of 21 bits. The input channels are multiplexed. Internal buffering can be selected to provide very high input impedance for direct connection to transducers or low-level voltage signals. Burnout current sources are provided that allow for detection of an open or shorted sensor. An 8-bit Digital-to-Analog (D/A) converter provides an offset correction with a range of 50% of the Full-Scale Range (FSR). The Programmable Gain Amplifier (PGA) provides selectable gains of 1 to 128, with an effective resolution of 19 bits at a gain of 128. The A/D conversion is accomplished with a 2nd-order delta-sigma modulator and programmable Finite-Impulse Response (FIR) filter that provides a simultaneous 50Hz and 60Hz notch. The reference input is differential and can be used for ratiometric conversion. The serial interface is SPI compatible. Up to eight bits of data I/O are also provided that can be used for input or output. The ADS1240 and ADS1241 are designed for high-resolution measurement applications in smart transmitters, industrial process control, weigh scales, chromatography, and portable instrumentation.

宽讯ACAP2410-54'H 快速安装指南 v1.1.01

AboveCable ACAP2410-54/H快速安装手册....................................................版本:1.1.01 1 ACAP2410-54/ H 简介新一代企业级无线接入点——ACAP2410-54/H 54Mbps公共网络无线AP,可应用于WISP(无线网络运营商)的公共无线局域网络,支持基于SNMP的集中网管、认证和计费。

该产品主要是为了实现无线在公共网络的应用,提供高达108Mbps数据传输速率(开启了Super G功能后)的无线覆盖。

该产品的设计完全符合802.11b/g国际标准,可提供强大的功能,如基于SNMP的集中网管,支持802.1x认证,WPA/WPA2认证,802.1Q VLAN等等。

主要应用于机场、酒店、会展中心、咖啡吧、新闻中心等公共区域。

2 硬件安装本章描述了该设备的初始化安装。

2.1 产品包装安装之前,请确认产品包括以下各项内容:z一台Hotspot APz一根偶极天线z一张产品光盘z一个电源适配器z一份快速安装手册z一份质量保修卡如果上述项目中的任一项缺少或损坏,请与本地销售取得联系。

2.2 硬件安装按照下面的步骤安装你的AP。

a.将偶极天线安装在AP后侧的插座中。

b.安装之前,选好AP的安放地点。

合适的位置可以为AP提供良好的射频信号质量。

一般来讲,比较好的位置是无线覆盖区域的中心。

由于障碍物会妨碍无线信号的传递,请将移动的无线节点放在AP视线所及的地点。

c.Hotspot AP支持10/100M以太网连接。

使用非屏蔽双绞线连接AP和HUB或者工作站。

d.将电源适配器插入AP后侧的电源插孔(DC 12V),另一端插在电源插座上;或者将带有POE的5类线插入AP后侧的RJ45口。

AP正面面板上的三个指示灯会瞬间打开,用以检测指示灯功能是否正常。

请注意,只能使用AP原配的电源适配器,或者使用AboveCable的POE模块,否则可能会损坏AP。

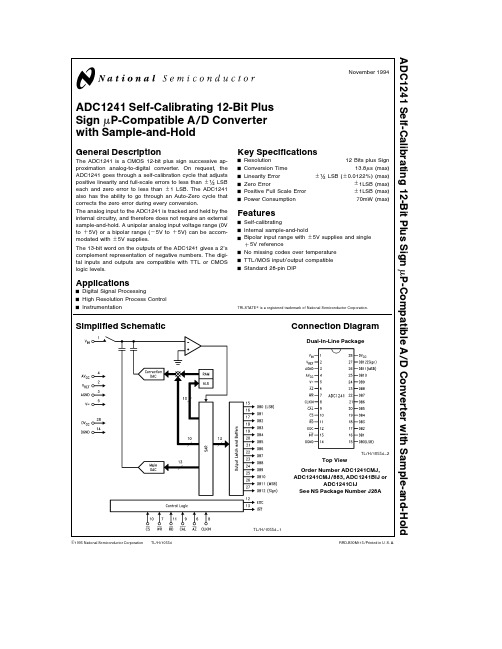

ADC1241 芯片资料

TL H 10554ADC1241Self-Calibrating 12-Bit Plus Sign m P-Compatible A D Converter with Sample-and-HoldNovember 1994ADC1241Self-Calibrating 12-Bit Plus Sign m P-Compatible A D Converter with Sample-and-HoldGeneral DescriptionThe ADC1241is a CMOS 12-bit plus sign successive ap-proximation analog-to-digital converter On request the ADC1241goes through a self-calibration cycle that adjusts positive linearity and full-scale errors to less than g LSB each and zero error to less than g 1LSB The ADC1241also has the ability to go through an Auto-Zero cycle that corrects the zero error during every conversionThe analog input to the ADC1241is tracked and held by the internal circuitry and therefore does not require an external sample-and-hold A unipolar analog input voltage range (0V to a 5V)or a bipolar range (b 5V to a 5V)can be accom-modated with g 5V suppliesThe 13-bit word on the outputs of the ADC1241gives a 2’s complement representation of negative numbers The digi-tal inputs and outputs are compatible with TTL or CMOS logic levelsApplicationsY Digital Signal ProcessingY High Resolution Process Control YInstrumentationKey SpecificationsY Resolution12Bits plus SignY Conversion Time 13 8m s (max)Y Linearity Error g LSB (g 0 0122%)(max)Y Zero Errorg 1LSB (max)Y Positive Full Scale Error g 1LSB (max)YPower Consumption 70mW (max)FeaturesY Self-calibratingY Internal sample-and-holdYBipolar input range with g 5V supplies and single a 5V referenceY No missing codes over temperature Y TTL MOS input output compatible YStandard 28-pin DIPTRI-STATE is a registered trademark of National Semiconductor CorporationSimplified Schematic TL H 10554–1Connection DiagramDual-In-Line PackageTL H 10554–2Top ViewOrder Number ADC1241CMJ ADC1241CMJ 883 ADC1241BIJ orADC1241CIJSee NS Package Number J28AC 1995National Semiconductor CorporationRRD-B30M115 Printed in U S AAbsolute Maximum Ratings(Notes1 2) If Military Aerospace specified devices are required please contact the National Semiconductor Sales Office Distributors for availability and specifications Supply Voltage(V CC e DV CC e AV CC)6 5V Negative Supply Voltage(V b)b6 5V Voltage at Logic Control Inputs b0 3V to(V CC a0 3V) Voltage at Analog Input(V IN)(V b b0 3V)to(V CC a0 3V) AV CC-DV CC(Note7)0 3V Input Current at any Pin(Note3)g5mA Package Input Current(Note3)g20mA Power Dissipation at25 C(Note4)875mW Storage Temperature Range b65 C to a150 C ESD Susceptability(Note5)2000V Soldering InformationJ Package(10sec)300 C Operating Ratings(Notes1 2) Temperature Range T MIN s T A s T MAX ADC1241BIJ ADC1241CIJ b40 C s T A s a85 C ADC1241CMJ ADC1241CMJ 883b55 C s T A s a125 CDV CC and AV CC Voltage(Notes6 7)4 5V to5 5V Negative Supply Voltage(V b)b4 5V to b5 5V Reference Voltage(V REF Notes6 7)3 5V to AV CC a50mVConverter Electrical CharacteristicsThe following specifications apply for V CC e DV CC e AV CC e a5 0V V b e b5 0V V REF e a5 0V and f CLK e2 0MHz unless otherwise specified Boldface limits apply for T A e T J e T MIN to T MAX all other limits T A e T J e25 C (Notes6 7 and8)Symbol Parameter Conditions Typical Limit Units (Note9)(Notes10 18)(Limit)STATIC CHARACTERISTICSPositive Integral ADC1241BIJ After Auto-Cal g LSB(max)Linearity ErrorADC1241CMJ CIJ (Notes11 12)g1LSB maxNegative Integral ADC1241BIJ After Auto-Cal g1LSB(max)Linearity ErrorADC1241CMJ CIJ (Notes11 12)g1LSB(max)Differential Linearity After Auto-Cal(Notes11 12)12Bits(min)Zero Error After Auto-Zero or Auto-Calg1LSB(max)(Notes12 13)Positive Full-Scale Error After Auto-Cal(Note12)g g1LSB(max) Negative Full-Scale Error After Auto-Cal(Note12)g1 g2LSB(max) C REF V REF Input Capacitance80pFC IN Analog Input Capacitance65pFV IN Analog Input Voltage V b b0 05V(min)V CC a0 05V(max) Power Supply Zero Error(Note14)AV CC e DV CC e5V g5% g LSBSensitivityFull-Scale Error V REF e4 75V V b e b5V g5%g LSBLinearity Error g LSB DYNAMIC CHARACTERISTICSS (N a D)Unipolar Signal-to-Noise a Distortion f IN e1kHz V IN e4 85V p-p72dBRatio(Note17)f IN e10kHz V IN e4 85V p-p72dB S (N a D)Bipolar Signal-to-Noise a Distortion f IN e1kHz V IN e g4 85V p-p76dBRatio(Note17)f IN e10kHz V IN e g4 85V p-p76dBUnipolar Full Power Bandwidth(Note17)V IN e0V to4 85V32kHz Bipolar Full Power Bandwidth(Note17)V IN e g4 85V p-p25kHz t Ap Aperture Time100ns Aperture Jitter100ps rms2Digital and DC Electrical CharacteristicsThe following specifications apply for V CC e DV CC e AV CC e a5 0V V b e b5 0V V REF e a5 0V and f CLK e2 0MHz unless otherwise specified Boldface limits apply for T A e T J e T MIN to T MAX all other limits T A e T J e25 C(Notes6and7)Symbol Parameter Condition Typical Limit Units (Note9)(Notes10 18)(Limits)V IN(1)Logical‘‘1’’Input Voltage for V CC e5 25V2 0V(min)All Inputs except CLK INV IN(0)Logical‘‘0’’Input Voltage for V CC e4 75V0 8V(max)All Inputs except CLK INI IN(1)Logical‘‘1’’Input Current V IN e5V0 0051m A(max) I IN(0)Logical‘‘0’’Input Current V IN e0V b0 005b1m A(max)V T a CLK IN Positive-Going2 82 7V(min)Threshold VoltageV T b CLK IN Negative-Going2 12 3V(max)Threshold VoltageV H CLK IN Hysteresis0 70 4V(min)V T a(min)b V T b(max)V OUT(1)Logical‘‘1’’Output Voltage V CC e4 75VI OUT e b360m A2 4V(min)I OUT e b10m A4 5V(min)V OUT(0)Logical‘‘0’’Output Voltage V CC e4 75V0 4V(max)I OUT e1 6mAI OUT TRI-STATE Output Leakage V OUT e0V b0 01b3m A(max)Current VOUT e5V0 013m A(max) I SOURCE Output Source Current V OUT e0V b20b6 0mA(min) I SINK Output Sink Current V OUT e5V208 0mA(min) DI CC DV CC Supply Current f CLK e2MHz CS e‘‘1’’12mA(max) AI CC AV CC Supply Current f CLK e2MHz CS e‘‘1’’2 86mA(max) I b V b Supply Current f CLK e2MHz CS e‘‘1’’2 86mA(max)3AC Electrical CharacteristicsThe following specifications apply for DV CC e AV CC e a5 0V V b e b5 0V t r e t f e20ns unless otherwise specified Boldface limits apply for T A e T J e T MIN to T MAX all other limits T A e T J e25 C (Notes6and7)Symbol Parameter Conditions Typical Limit Units (Note9)(Notes10 18)(Limits)f CLK Clock Frequency2 0MHz0 5MHz(min)4 0MHZ(max)Clock Duty Cycle50%40%(min)60%(max)t C Conversion Time27(1 f CLK)27(1 f CLK)a300ns(max)f CLK e2 0MHz13 5m st A Acquisition Time R SOURCE e50X7(1 f CLK)7(1 f CLK)a300ns(max) (Note15)f CLK e2 0MHz3 5m st Z Auto Zero Time26261 f CLK(max)f CLK e2 0MHz13m st CAL Calibration Time13961 f CLKf CLK e2 0MHz698706m s(max)t W(CAL)L Calibration Pulse Width(Note16)60200ns(min)t W(WR)L Minimum WR Pulse Width60200ns(min)t ACC Maximum Access Time C L e100pF(Delay from Falling Edge of5085ns(max)RD to Output Data Valid)t0H t1H TRI-STATE Control(Delay R L e1k Xfrom Rising Edge of RD C L e100pF3090ns(max)to Hi-Z State)t PD(INT)Maximum Delay from Falling Edge of100175ns(max) RD or WR to Reset of INTNote1 Absolute Maximum Ratings indicate limits beyond which damage to the device may occur Operating Ratings indicate conditions for which the device is functional but do not guarantee specific performance limits For guaranteed specifications and test conditions see the Electrical Characteristics The guaranteed specifications apply only for the test conditions listed Some performance characteristics may degrade when the device is not operated under the listed test conditionsNote2 All voltages are measured with respect to AGND and DGND unless otherwise specifiedNote3 When the input voltage(V IN)at any pin exceeds the power supply rails(V IN k V b or V IN l(AV CC or DV CC) the current at that pin should be limited to 5mA The20mA maximum package input current rating allows the voltage at any four pins with an input current limit of5mA to simultaneously exceed the power supply voltagesNote4 The maximum power dissipation must be derated at elevated temperatures and is dictated by T JMAX(maximum junction temperature) i JA(package junction to ambient thermal resistance) and T A(ambient temperature) The maximum allowable power dissipation at any temperature is P Dmax e(T Jmax b T A) i JA or the number given in the Absolute Maximum Ratings whichever is lower For this device T Jmax e125 C and the typical thermal resistance(i JA)of the ADC1241with CMJ BIJ and CIJ suffixes when board mounted is47 C WNote5 Human body model 100pF discharged through a1 5k X resistorNote6 Two on-chip diodes are tied to the analog input as shown below Errors in the A D conversion can occur if these diodes are forward biased more than 50mVTL H 10554–3This means that if AV CC and DV CC are minimum(4 75V DC)and V b is maximum(b4 75V DC) full-scale must be s4 8V DC4AC Electrical Characteristics(Continued)Note7 A diode exists between AV CC and DV CC as shown belowTL H 10554–4To guarantee accuracy it is required that the AV CC and DV CC be connected together to a power supply with separate bypass filters at each V CC pinNote8 Accuracy is guaranteed at f CLK e2 0MHz At higher and lower clock frequencies accuracy may degrade See curves in the Typical Performance Characteristics SectionNote9 Typicals are at T J e25 C and represent most likely parametric normNote10 Limits are guaranteed to National’s AOQL(Average Outgoing Quality Level)Note11 Positive linearity error is defined as the deviation of the analog value expressed in LSBs from the straight line that passes through positive full scale and zero For negative linearity error the straight line passes through negative full scale and zero (See Figures1b and1c)Note12 The ADC1241’s self-calibration technique ensures linearity full scale and offset errors as specified but noise inherent in the self-calibration process will result in a repeatability uncertainty of g0 20LSBNote13 If T A changes then an Auto-Zero or Auto-Cal cycle will have to be re-started see the typical performance characteristic curvesNote14 After an Auto-Zero or Auto-Cal cycle at the specified power supply extremesNote15 If the clock is asynchronous to the falling edge of WR an uncertainty of one clock period will exist in the interval of t A therefore making the minimum t A e 6clock periods and the maximum t A e7clock periods If the falling edge of the clock is synchronous to the rising edge of WR then t A will be exactly6 5clock periodsNote16 The CAL line must be high before any other conversion is startedNote17 The specifications for these parameters are valid after an Auto-Cal cycle has been completedNote18 A military RETS electrical test specification is available on request At time of printing the ADC1241CMJ 883RETS specification complies fully with the boldface limits in this columnTL H 10554–5FIGURE1a Transfer Characteristic5AC Electrical Characteristics(Continued)TL H 10554–6 FIGURE1b Simplified Error Curve vs Output Code Without Auto-Cal or Auto-Zero CyclesTL H 10554–7 FIGURE1c Simplified Error Curve vs Output Code After Auto-Cal CycleTypical Performance CharacteristicsZero Error Change vsZero Error vs V REF Ambient TemperatureTL H 10554–86Typical Performance Characteristics(Continued)Linearity Error vs V REFFrequencyLinearity Error vs Clock Ambient TemperatureFull Scale Error Change vs Input Frequency Noise a Distortion Ratio vs Bipolar Signal-to-Input Frequency Noise a Distortion Ratio vs Unipolar Signal-to-Input Source ImpedanceNoise a Distortion Ratio vs Bipolar Signal-to-Input Signal Level Noise a Distortion Ratio vs Bipolar Signal-to-Input Signal LevelNoise a Distortion Ratio vs Unipolar Signal-to-with 10kHz Sine Wave InputBipolar Spectral Response with 1kHz Sine Wave Input Bipolar Spectral Response with 1kHz Sine Wave Input Unipolar Spectral Response with 10kHz Sine Wave InputUnipolar Spectral Response TL H 10554–217Test CircuitsTL H 10554–9TL H 10554–11TL H 10554–10TL H 10554–12FIGURE2 TRI-STATE Test Circuits and WaveformsTiming DiagramsAuto-Cal Cycle(CS e1 WR e X RD e X AZ e X X e Don’t Care)TL H 10554–138Timing Diagrams(Continued)Normal Conversion with Auto-Zero(CAL e1 AZ e0)TL H 10554–14Normal Conversion without Auto-Zero(CAL e1 AZ e1)TL H 10554–1591 0Pin DescriptionsDV CC(28) The digital and analog positive power supply AV CC(4)pins The digital and analog power supply voltage range of the ADC1241is a4 5V toa5 5V To guarantee accuracy it is requiredthat the AV CC and DV CC be connected to-gether to the same power supply with sepa-rate bypass filters(10m F tantalum in parallelwith a0 1m F ceramic)at each V CC pinV b(5)The analog negative supply voltage pin V b has a range of b4 5V to b5 5V and needs abypass filter of10m F tantalum in parallel witha0 1m F ceramicDGND(14) The digital and analog ground pins AGND AGND(3)and DGND must be connected together ex-ternally to guarantee accuracyV REF(2)The reference input voltage pin To maintain accuracy the voltage at this pin should notexceed the AV CC or DV CC by more than50mV or go below3 5VDCV IN(1)The analog input voltage pin To guarantee accuracy the voltage at this pin should notexceed V CC by more than50mV or go belowV b by more than50mVCS(10)The Chip Select control input This input is active low and enables the WR and RD func-tionsRD(11)The Read control input With both CS and RD low the TRI-STATE output buffers are en-abled and the INT output is reset highWR(7)The Write control input The converison is started on the rising edge of the WR pulsewhen CS is lowCLK(8)The external clock input pin The clock fre-quency range is500kHz to4MHzCAL(9)The Auto-Calibration control input When CAL is low the ADC1241is reset and a cali-bration cycle is initiated During the calibra-tion cycle the values of the comparator offsetvoltage and the mismatch errors in the ca-pacitor reference ladder are determined andstored in RAM These values are used to cor-rect the errors during a normal cycle of A DconversionAZ(6)The Auto-Zero control input With the AZ pin held low during a conversion the ADC1241goes into an auto-zero cycle before the actu-al A D conversion is started This Auto-Zerocycle corrects for the comparator offset volt-age The total conversion time(t C)is in-creased by26clock periods when Auto-Zerois usedEOC(12)The End-of-Conversion control output This output is low during a conversion or a calibra-tion cycleINT(13)The Interrupt control output This output goes low when a conversion has been completedand indicates that the conversion result isavailable in the output latches Reading theresult or starting a conversion or calibrationcycle will reset this output highDB0–DB12The TRI-STATE output pins The output is in (15–27)two’s complement format with DB12the signbit DB11the MSB and DB0the LSB2 0Functional DescriptionThe ADC1241is a12-bit plus sign A D converter with the capability of doing Auto-Zero or Auto-Cal routines to mini-mize zero full-scale and linearity errors It is a successive-approximation A D converter consisting of a DAC compar-ator and a successive-approximation register(SAR) Auto-Zero is an internal calibration sequence that corrects for theA D’s zero error caused by the comparator’s offset voltageAuto-Cal is a calibration cycle that not only corrects zero error but also corrects for full-scale and linearity errors caused by DAC inaccuracies Auto-Cal minimizes the errors of the ADC1241without the need of trimming during its fab-rication An Auto-Cal cycle can restore the accuracy of the ADC1241at any time which ensures its long term stability2 1DIGITAL INTERFACEOn power up a calibration sequence should be initiated by pulsing CAL low with CS RD and WR high To acknowl-edge the CAL signal EOC goes low after the falling edge of CAL and remains low during the calibration cycle of1396 clock periods During the calibration sequence first the comparator’s offset is determined then the capacitive DAC’s mismatch error is found Correction factors for these errors are then stored in internal RAMA conversion is initiated by taking CS and WR low The AZ(Auto Zero)signal line should be tied high or low during the conversion process If AZ is low an auto zero cycle which takes approximately26clock periods occurs before the ac-tual conversion is started The auto zero cycle determines the correction factors for the comparator’s offset voltage If AZ is high the auto zero cycle is skipped Next the analog input is sampled for7clock periods and held in the capaci-tive DAC’s ladder structure The EOC then goes low signal-ing that the analog input is no longer being sampled and that the A D successive approximation conversion has startedDuring a conversion the sampled input voltage is succes-sively compared to the output of the DAC First the ac-quired input voltage is compared to analog ground to deter-mine its polarity The sign bit is set low for positive input voltages and high for negative Next the MSB of the DAC is set high with the rest of the bits low If the input voltage is greater than the output of the DAC then the MSB is left high otherwise it is set low The next bit is set high making the output of the DAC three quarters or one quarter of full scale A comparison is done and if the input is greater than the new DAC value this bit remains high if the input is less than the new DAC value the bit is set low This process continues until each bit has been tested The result is then stored in the output latch of the ADC1241 Next EOC goes high and INT goes low to signal the end of the conversion The result can now be read by taking CS and RD low to enable the DB0–DB12output buffers102 0Functional Description(Continued)Digital Control InputsA D FunctionCS WR RD CAL AZ111Start Conversion without Auto-Zero1 11Read Conversion Result without Auto-Zero110Start Conversion with Auto-Zero1 10Read Conversion Result with Auto-Zero1X X X Start Calibration Cycle0X10X Test Mode(DB2 DB3 DB5and DB6become active)FIGURE1 Function of the A D Control InputsThe table in Figure1summarizes the effect of the digital control inputs on the function of the ADC1241 The Test Mode where RD is high and CS and CAL are low is used by the factory to thoroughly check out the operation of the ADC1241 Care should be taken not to inadvertently be in this mode since DB2 DB3 DB5 and DB6become active outputs which may cause data bus contention2 2RESETTING THE A DAll internal logic can be reset which will abort any conver-sion in process The A D is reset whenever a new conver-sion is started by taking CS and WR low If this is done when the analog input is being sampled or when EOC is low the Auto-Cal correction factors may be corrupted therefore making it necessary to do an Auto-Cal cycle before the next conversion This is true with or without Auto-Zero The Cali-bration Cycle cannot be reset once started On power-up the ADC1241automatically goes through a Calibration Cy-cle that takes typically1396clock cycles 3 0Analog Considerations3 1REFERENCE VOLTAGEThe voltage applied to the reference input of the converter defines the voltage span of the analog input(the difference between V IN and AGND) over which4095positive output codes and4096negative output codes exist The A-to-D can be used in either ratiometric or absolute reference ap-plications The voltage source driving V REF must have a very low output impedance and very low noise The circuit in Figure2is an example of a very stable reference that is appropriate for use with the ADC1241In a ratiometric system the analog input voltage is propor-tional to the voltage used for the A D reference When this voltage is the system power supply the V REF pin can be tied to V CC This technique relaxes the stability requirement of the system reference as the analog input and A D refer-ence move together maintaining the same output code for given input conditionTL H 10554–17TantalumFIGURE2 Low Drift Extremely Stable Reference Circuit113 0Analog Considerations(Continued)TL H 10554–18FIGURE3 Analog Input Equivalent CircuitFor absolute accuracy where the analog input varies be-tween very specific voltage limits the reference pin can be biased with a time and temperature stable voltage source In general the magnitude of the reference voltage will re-quire an initial adjustment to null out full-scale errors3 2INPUT CURRENTA charging current will flow into or out of(depending on the input voltage polarity)of the analog input pin(V IN)on the start of the analog input sampling period(t A) The peak val-ue of this current will depend on the actual input voltage applied3 3INPUT BYPASS CAPACITORSAn external capacitor can be used to filter out any noise due to inductive pickup by a long input lead and will not degrade the accuracy of the conversion result3 4INPUT SOURCE RESISTANCEThe analog input can be modeled as shown in Figure3 External R S will lengthen the time period necessary for the voltage on C REF to settle to within LSB of the analog input voltage With f CLK e2MHz t A e7clock periods e 3 5m s R S s1k X will allow a5V analog input voltage to settle properly3 5NOISEThe leads to the analog input pin should be kept as short as possible to minimize input noise coupling Both noise and undesired digital clock coupling to this input can cause er-rors Input filtering can be used to reduce the effects of these noise sources3 6POWER SUPPLIESNoise spikes on the V CC and V b supply lines can cause conversion errors as the comparator will respond to this noise The A D is especially sensitive during the auto-zero or auto-cal procedures to any power supply spikes Low inductance tantalum capacitors of10m F or greater paralleled with0 1m F ceramic capacitors are recommended for supply bypassing Separate bypass capacitors whould be placed close to the DV CC AV CC and V b pins If an unregulated voltage source is available in the system a separate LM340LAZ-5 0voltage regulator for the A-to-D’s V CC(and other analog circuitry)will greatly reduce digital noise on the supply line3 7THE CALIBRATION CYCLEOn power up the ADC1241goes through an Auto-Cal cycle which cannot be interrupted Since the power supply refer-ence and clock will not be stable at power up this first calibration cycle will not result in an accurate calibration of the A D A new calibration cycle needs to be started after the power supplies reference and clock have been given enough time to stabilize During the calibration cycle cor-rection values are determined for the offset voltage of the sampled data comparator and any linearity and gain errors These values are stored in internal RAM and used during an analog-to-digital conversion to bring the overall gain offset and linearity errors down to the specified limits It should be necessary to go through the calibration cycle only once af-ter power up3 8THE AUTO-ZERO CYCLETo correct for any change in the zero(offset)error of theA D the auto-zero cycle can be used It may be necessaryto do an auto-zero cycle whenever the ambient temperature changes significantly (See the curved titled‘‘Zero Error Change vs Ambient Temperature’’in the Typical Perform-ance Characteristics )A change in the ambient temperature will cause the V OS of the sampled data comparator to change which may cause the zero error of the A D to be greater than g1LSB An auto-zero cycle will maintain the zero error to g1LSB or less124 0Dynamic PerformanceMany applications require the A D converter to digitize ac signals but the standard dc integral and differential nonlin-earity specifications will not accurately predict the A D con-verter’s performance with ac input signals The important specifications for ac applications reflect the converter’s abil-ity to digitize ac signals without significant spectral errors and without adding noise to the digitized signal Dynamic characteristics such as signal-to-noise a distortion ratio (S (N a D)) effective bits full power bandwidth aperture time and aperture jitter are quantitative measures of the A D converter’s capabilityAn A D converter’s ac performance can be measured using Fast Fourier Transform(FFT)methods A sinusoidal wave-form is applied to the A D converter’s input and the trans-form is then performed on the digitized waveform S (N a D) is calculated from the resulting FFT data and a spectral plot may also be obtained Typical values for S (N a D)are shown in the table of Electrical Characteristics and spectral plots are included in the typical performance curvesThe A D converter’s noise and distortion levels will change with the frequency of the input signal with more distortion and noise occurring at higher signal frequencies This can be seen in the S (N a D)versus frequency curves These curves will also give an indication of the full power band-width(the frequency at which the S (N a D)drops3dB) Two sample hold specifications aperture time and aperture jitter are included in the Dynamic Characteristics table since the ADC1241has the ability to track and hold the analog input voltage Aperture time is the delay for the A D to respond to the hold command In the case of the ADC1241 the hold command is internally generated When the Auto-Zero function is not being used the hold command occurs at the end of the acquisition window or seven clock periods after the rising edge of the WR The delay between the internally generated hold command and the time that the ADC1241actually holds the input signal is the aperture time For the ADC1241 this time is typically100ns Aper-ture jitter is the change in the aperture time from sample to sample Aperture jitter is useful in determining the maximum slew rate of the input signal for a given accuracy For exam-ple an ADC1241with100ps of aperture jitter operating with a5V reference can have an effective gain variation of about 1LSB with an input signal whose slew rate is12V m sPower Supply BypassingTL H 10554–19 TantalumProtecting the Analog InputsTL H 10554–20 13A D C 1241S e l f -C a l i b r a t i n g 12-B i t P l u s S i g n m P -C o m p a t i b l e AD C o n v e r t e r w i t h S a m p l e -a n d -H o l dPhysical Dimensions inches (millimeters)Order Number ADC1241CMJ ADC1241CMJ 883 ADC1241BIJ or ADC1241CIJNS Package Number J28ALIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION As used herein 1 Life support devices or systems are devices or 2 A critical component is any component of a life systems which (a)are intended for surgical implant support device or system whose failure to perform can into the body or (b)support or sustain life and whose be reasonably expected to cause the failure of the life failure to perform when properly used in accordance support device or system or to affect its safety or with instructions for use provided in the labeling can effectivenessbe reasonably expected to result in a significant injury to the userNational Semiconductor National Semiconductor National Semiconductor National Semiconductor CorporationEuropeHong Kong LtdJapan Ltd1111West Bardin RoadFax (a 49)0-180-530858613th Floor Straight Block Tel 81-043-299-2309。

REF 541 543 545 馈线保护终端

数实现CT和PT二次值与保护单元额定值的数 有效性(无效性)等特性都可以通过继电器参

值调整。当整定值为 1.00 时,保护单元的额定 数配置得到,并可以应用于不同的需求。

值就等于测量设备二次额定值。

RT41 和 REF 543 馈线保护终端可以配置

当使用传感器时,REF 54_ 馈线保护终端使用 RTD/模拟量输入模块,该模块具有8个通用的

组保护和控制

● 可用于电能质量的监测、保护、电容器组的 ● RTD/ 模拟量测量模块可用于温度、电流 / 电

保护和控制以及电动机的保护

压测量和 mA 量的信号输出

● 可以用电流电压传感器或者传统的CT和PT 来进行电流电压测量

● 装置人机界面采用 17x19 行大液晶图形显 示屏,且该液晶屏可以和装置分离,便于在 开关柜上安装

输入的类型。

关量是否发生了接点抖动或振荡。如果检测到

接点抖动或振荡,将作为事件记录。

继电器模拟量通道的配置由 CAP 505 继电器

配置工具软件完成。

馈线终端开关量输入特性的设置

对每个开关量输入点,输入量的状态(逻辑

每个模拟量通道可以设置不同的比例系数,系 值)、状态变化的时标(时间)、开关量输入的

控制。在 MIMIC 画面上开关设备不同状态的显

示方式,例如分闸 / 合闸 / 不确定都是可以任意 辅助电源低压告警

设计的。

REF 54_馈线保护终端具有辅助电源低压告警功

能。当检测到装置电源电压下降(或交流电源丢

故障定位

失)时,装置电源模块就发出内部告警信号。如

故障定位功能适用于辐射状配电系统。在各种 果电源电压比电源模块的最小额定直流输入电

如电压凹陷,暂态升高和瞬时中断。测量依照 Profibus-DPV1,SPA,LON,DNP 3.0 和

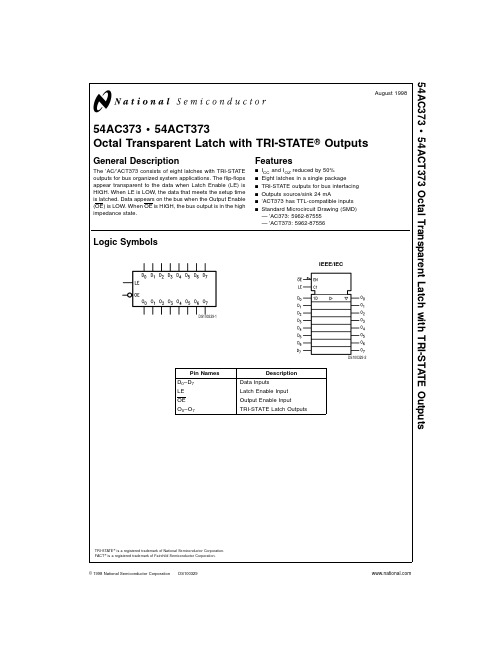

54AC373中文资料

Features

n ICC and IOZ reduced by 50% n Eight latches in a single package n TRI-STATE outputs for bus interfacing n Outputs source/sink 24 mA n ’ACT373 has TTL-compatible inputs n Standard Microcircuit Drawing (SMD)

Supply Voltage (VCC) DC Input Diode Current (IIK)

VI = −0.5V VI = VCC + 0.5V DC Input Voltage (VI) DC Output Diode Current (IOK) VO = −0.5V VO = VCC + 0.5V DC Output Voltage (VO) DC Output Source

— ’AC373: 5962-87555 — ’ACT373: 5962-87556

Logic Symbols

IEEE/IEC

DS100329-1

Pin Names D0– D7 LE OE O0– O7

Description Data Inputs Latch Enable Input Output Enable Input TRI-STATE Latch Outputs

DS100329-3

Functional Description

The ’AC/’ACT373 contains eight D-type latches with TRI-STATE standard outputs. When the Latch Enable (LE) input is HIGH, data on the Dn inputs enters the latches. In this condition the latches are transparent, i.e., a latch output will change state each time its D input changes. When LE is LOW, the latches store the information that was present on the D inputs a setup time preceding the HIGH-to-LOW transition of LE. The TRI-STATE standard outputs are controlled by the Output Enable (OE) input. When OE is LOW, the standard outputs are in the 2-state mode. When OE is HIGH, the standard outputs are in the high impedance mode but this does not interfere with entering new data into the latches.

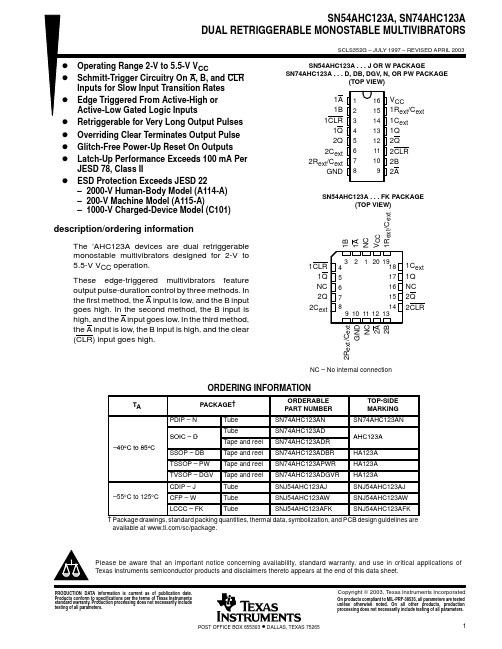

SN54AHC123A中文资料

PACKAGING INFORMATIONOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)5962-9860801Q2A ACTIVE LCCC FK201TBD Call TI Level-NC-NC-NC 5962-9860801QEA ACTIVE CDIP J161TBD Call TI Level-NC-NC-NC 5962-9860801QFA ACTIVE CFP W161TBD Call TI Level-NC-NC-NC SN74AHC123AD ACTIVE SOIC D1640Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AHC123ADBR ACTIVE SSOP DB162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AHC123ADBRE4ACTIVE SSOP DB162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AHC123ADE4ACTIVE SOIC D1640Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AHC123ADG4ACTIVE SOIC D1640Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AHC123ADGVR ACTIVE TVSOP DGV162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AHC123ADGVRE4ACTIVE TVSOP DGV162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AHC123ADR ACTIVE SOIC D162500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AHC123ADRE4ACTIVE SOIC D162500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AHC123ADRG4ACTIVE SOIC D162500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AHC123AN ACTIVE PDIP N1625Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NCSN74AHC123ANE4ACTIVE PDIP N1625Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NCSN74AHC123APWR ACTIVE TSSOP PW162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AHC123APWRE4ACTIVE TSSOP PW162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SNJ54AHC123AFK ACTIVE LCCC FK201TBD Call TI Level-NC-NC-NC SNJ54AHC123AJ ACTIVE CDIP J161TBD Call TI Level-NC-NC-NC SNJ54AHC123AW ACTIVE CFP W161TBD Call TI Level-NC-NC-NC (1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan-The planned eco-friendly classification:Pb-Free(RoHS)or Green(RoHS&no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free(RoHS):TI's terms"Lead-Free"or"Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all6substances,including the requirement that lead not exceed0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Green(RoHS&no Sb/Br):TI defines"Green"to mean Pb-Free(RoHS compatible),and free of Bromine(Br)and Antimony(Sb)based flame retardants(Br or Sb do not exceed0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.元器件交易网元器件交易网元器件交易网IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications,enhancements, improvements, and other changes to its products and services at any time and to discontinueany product or service without notice. Customers should obtain the latest relevant information before placingorders and should verify that such information is current and complete. All products are sold subject to TI’s termsand conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale inaccordance with TI’s standard warranty. T esting and other quality control techniques are used to the extent TIdeems necessary to support this warranty. Except where mandated by government requirements, testing of allparameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible fortheir products and applications using TI components. T o minimize the risks associated with customer productsand applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right,copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or processin which TI products or services are used. Information published by TI regarding third-party products or servicesdoes not constitute a license from TI to use such products or services or a warranty or endorsement thereof.Use of such information may require a license from a third party under the patents or other intellectual propertyof the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is withoutalteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproductionof this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable forsuch altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for thatproduct or service voids all express and any implied warranties for the associated TI product or service andis an unfair and deceptive business practice. TI is not responsible or liable for any such statements.Following are URLs where you can obtain information on other Texas Instruments products and applicationsolutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetworkMicrocontrollers Security /securityTelephony /telephonyVideo & Imaging /videoWireless /wirelessMailing Address:Texas InstrumentsPost Office Box 655303 Dallas, Texas 75265Copyright 2005, Texas Instruments Incorporated。

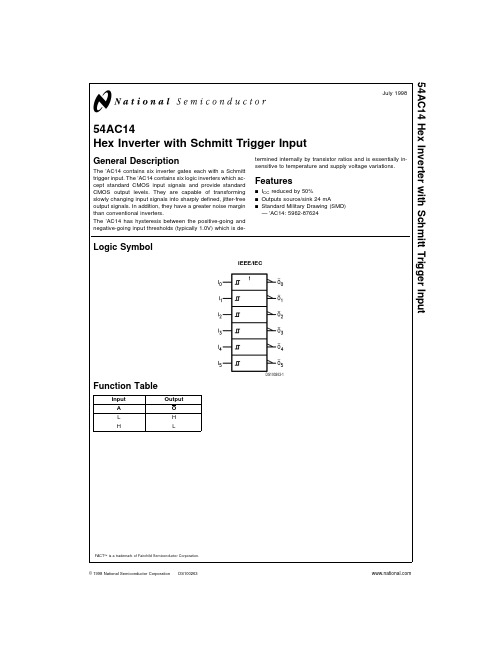

54AC14中文资料

54AC14Hex Inverter with Schmitt Trigger InputGeneral DescriptionThe ’AC14contains six inverter gates each with a Schmitt trigger input.The ’AC14contains six logic inverters which ac-cept standard CMOS input signals and provide standard CMOS output levels.They are capable of transforming slowly changing input signals into sharply defined,jitter-free output signals.In addition,they have a greater noise margin than conventional inverters.The ’AC14has hysteresis between the positive-going and negative-going input thresholds (typically 1.0V)which is de-termined internally by transistor ratios and is essentially in-sensitive to temperature and supply voltage variations.Featuresn I CC reduced by 50%n Outputs source/sink 24mAn Standard Military Drawing (SMD)—’AC14:5962-87624Logic SymbolFunction TableInput Output A O L H HLFACT ™is a trademark of Fairchild Semiconductor Corporation.IEEE/IECDS100263-1July 199854AC14Hex Inverter with Schmitt Trigger Input©1998National Semiconductor Corporation Connection DiagramsPin Names Description I n Inputs O nOutputsPin Assignment for DIP and FlatpackDS100263-2Pin Assignment for LCCDS100263-3 2Absolute Maximum Ratings(Note1)If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.Supply Voltage(V CC)−0.5V to+7.0V DC Input Diode Current(I IK)V I=−0.5V−20mA V I=V CC+0.5V+20mA DC Input Voltage(V I)−0.5V to V CC+0.5V DC Output Diode Current(I OK)V O=−0.5V−20mA V O=V CC+0.5V+20mA DC Output Voltage(V O)−0.5V to V CC+0.5V DC Output Sourceor Sink Current(I O)±50mA DC V CC or Ground Currentper Output Pin(I CC or I GND)±50mA Storage Temperature(T STG)−65˚C to+150˚C Junction Temperature(T J)CDIP175˚C Recommended Operating ConditionsSupply Voltage(V CC)’AC 2.0V to6.0V Input Voltage(V I)0V to V CC Output Voltage(V O)0V to V CC Operating Temperature(T A)54AC−55˚C to+125˚C Note1:Absolute maximum ratings are those values beyond which damage to the device may occur.The databook specifications should be met,without exception,to ensure that the system design is reliable over its power supply, temperature,and output/input loading variables.National does not recom-mend operation of FACT™circuits outside databook specifications.DC Characteristics for’AC Family Devices54ACSymbol Parameter V CC T A=−55˚C to+125˚C Units Conditions(V)Guaranteed LimitsV OH Minimum High Level OutputVoltage 3.0 2.9I OUT=−50µA4.5 4.4V5.5 5.4(Note2)V IN=V IL or V IH3.0 2.4−12mA4.5 3.7V I OH−24mA5.5 4.7−24mAV OL Maximum Low Level OutputVoltage 3.00.1I OUT=50µA4.50.1V5.50.1(Note2)V IN=V IL or V IH3.00.512mA4.50.5V I OL24mA5.50.524mAI IN Maximum Input 5.5±1.0µA V I=V CC,GNDLeakage CurrentV t+Maximum Positive 3.0 2.2T A=Worst Case Threshold 4.5 3.2V5.5 3.9V t−Minimum Negative 3.00.5T A=Worst Case Threshold 4.50.9V5.5 1.1V h(max)Maximum Hysteresis 3.0 1.2T A=Worst Case4.5 1.4V5.5 1.6V h(min)Minimum Hysteresis 3.00.3T A=Worst Case4.50.4V5.50.5DC Characteristics for’AC Family Devices(Continued)54ACSymbol Parameter V CC T A=−55˚C to+125˚C Units Conditions(V)Guaranteed LimitsI OLD(Note3)Minimum DynamicOutput Current 5.550mA V OLD=1.65V MaxI OHD 5.5−50mA V OHD=3.85V MinI CC Maximum Quiescent 5.540.0µA V IN=V CCSupply Current or GND Note2:All outputs loaded;thresholds on input associated with output under test.Note3:Maximum test duration2.0ms,one output loaded at a time.Note4:I IN and I CC@3.0V are guaranteed to be less than or equal to the respective limit@5.5V V CC.I CC for54AC@25˚C is identical to74AC@25˚C.AC Electrical Characteristics54ACV CC T A=−55˚C Fig.Symbol Parameter(V)to+125˚C Units No.(Note5)C L=50pFMin Maxt PLH Propagation Delay 3.3 1.016.0ns5.0 1.012.0t PHL Propagation Delay 3.3 1.014.0ns5.0 1.510.0Note5:Voltage Range3.3is3.3V±0.3VVoltage Range5.0is5.0V±0.5VCapacitanceSymbol Parameter Typ Units ConditionsC IN Input Capacitance 4.5pF V CC=OPENC PD Power Dissipation25.0pF V CC=5.0VCapacitance45Physical Dimensions inches(millimeters)unless otherwise noted20Terminal Ceramic Leadless Chip Carrier(L)NS Package Number E20A6Physical Dimensions inches(millimeters)unless otherwise noted(Continued)14-Lead Ceramic Dual-In-Line Package(D)NS Package Number J14A14-Lead Ceramic Flatpak(F)NS Package Number W14BLIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DE-VICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMI-CONDUCTOR CORPORATION.As used herein:1.Life support devices or systems are devices or sys-tems which,(a)are intended for surgical implant intothe body,or (b)support or sustain life,and whose fail-ure to perform when properly used in accordancewith instructions for use provided in the labeling,can be reasonably expected to result in a significant injury to the user.2.A critical component in any component of a life support device or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system,or to affect its safety or effectiveness.National Semiconductor Corporation AmericasTel:1-800-272-9959Fax:1-800-737-7018Email:support@National Semiconductor EuropeFax:+49(0)180-5308586Email:europe.support@Deutsch Tel:+49(0)180-5308585English Tel:+49(0)180-5327832Français Tel:+49(0)180-5329358Italiano Tel:+49(0)180-5341680National Semiconductor Asia Pacific Customer Response Group Tel:65-2544466Fax:65-2504466Email:sea.support@National Semiconductor Japan Ltd.Tel:81-3-5620-6175Fax:81-3-5620-617954A C 14H e x I n v e r t e r w i t h S c h m i t t T r i g g e r I n p u tNational does not assume any responsibility for use of any circuitry described,no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.。

减压控制阀设计说明书

毕业设计(论文)说明书题目:减压控制阀的设计系名机械工程系专业机械设计制造及其自动化学号6012201230学生姓名周翔指导教师朱家玲2016年5月20日摘要随着工业技术的发展,液压系统在当今机械领域用途越来越广泛,各种大、中、小型液压设备中,液压减压阀是系统中的一个关键性的压力控制元件,它们的性能和寿命在很大程度上决定着整个液压系统的平稳性和工作能力。

设计中对减压阀结构进行了探讨,并且比较了两种方案的优劣特点,选择了管式螺纹连接定值输出减压阀。

在现有的减压阀基础上通过改变主阀芯的材料,从而提高减压阀的灵敏度,使产品在满足设计条件要求的情况下,更加经济合理化。

在这次毕业设计中主要参考了DR50型先导式减压阀的相关产品的结构和技术参数,并以其为基础,重新设计了先导式定值输出液压减压阀阀芯的结构参数,通过计算和不断优化使减压阀的部分或整体性能有所提高完善。

关键词:先导式减压阀;管式连接;阀芯结构参数AbstractAlong with the development of the technology industry, Hydraulic system in tod- ay's machinery field use more and more widely, In all the big or small hydraulic equi- pment, Hydraulic pressure reducing valve is system of a key pressure control compo- nents.This design mainly in the market today of the pressure reducing valve for the fo- undation, Pilot type setting value output pressure reducing valve design. In the gradu- ation design process adopted some of the pressure reducing valve about new technolo- gy and new ideas, And used topilot type setting value output pressure reducing valve design, In the design of pressure reducing valve structure were discussed.In the graduation design main reference the forerunner of the pressure reducing valve DR50 type of related products structure and technical parameters, And as the f- oundation, To guide the design of hydraulic pressure reducing valve setting value ou- tput valve core structure parameters, Through calculation and continuous optimization of the pressure reducing valve to part or whole performance improved perfect.Key words:Pilot Operated Reducing Valves;Tube Type Conjunction;The Valve Core Structure Parameters目录第一章引言 (1)第二章减压阀 (3)2.1 减压阀的简介 (3)2.2 定值减压阀 (3)2.3 定比减压阀 (5)2.4 定差减压阀 (6)2.5 我国引进的德国力士乐公司压力阀系列 (7)第三章设计方案的分析与选定 (9)3.1 设计的目的及范围 (9)3.2 设计的任务要求 (9)3.3 设计的总体思路 (9)3.4 设计方案的对比与确定 (10)第四章减压阀的结构设计及计算 (12)4.1 减压阀的设计内容 (12)4.2 减压阀的设计步骤 (12)4.2.1 主要结构尺寸的初步确定 (12)4.2.2 主阀弹簧的设计 (14)4.2.3 先导阀弹簧的设计计算 (17)第五章减压阀结构材料的选择及回油路的设计205.1 减压阀主要构件的材料选择 (20)5.1.1 阀体(壳体)的材料选择 (20)5.1.2 阀芯与阀套的材料选择 (20)5.1.3 先导式减压阀的远程控制口K的用途 (20)5.1.4 液压阀主要构件加工工艺 (20)5.2 减压阀回油路的设计 (21)5.2.1 减压回路的工作原理 (21)5.2.2 减压阀设计应该注意事项 (22)5.2.3 减压阀常见的故障及诊断排除 (22)第六章减压阀的性能指标及造型 (25)6.1 减压阀的主要静态性能指标 (25)6.2 减压阀的动态性能 (26)6.3 减压阀的设计造型图 (27)第七章结论 (29)参考文献 (30)外文资料中文译文致谢第一章引言液压技术在功率密度、结构组成、响应速度、调速保护、过载保护、电液整台等方面都具有一定的优势,使其成为现代传动的重要技术手段和不可替代的关键基础技术之一,这些应用已经遍及了国民经济各个领域。

SN54132中文资料

Copyright © 1988, Texas Instruments Incorporated PRODUCTION DATA information is current as of publication date.Products conform to specifications per the terms of Texas Instrumentsstandard warranty. Production processing does not necessarily includetesting of all parameters.POST OFFICE BOX 655303 • DALLAS, TEXAS 75265元器件交易网IMPORTANT NOTICETexas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinueany product or service without notice, and advise customers to obtain the latest version of relevant informationto verify, before placing orders, that information being relied on is current and complete. All products are soldsubject to the terms and conditions of sale supplied at the time of order acknowledgement, including thosepertaining to warranty, patent infringement, and limitation of liability.TI warrants performance of its semiconductor products to the specifications applicable at the time of sale inaccordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extentTI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarilyperformed, except those mandated by government requirements.CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OFDEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICALAPPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, ORWARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHERCRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TOBE FULLY AT THE CUSTOMER’S RISK.In order to minimize risks associated with the customer’s applications, adequate design and operatingsafeguards must be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance or customer product design. TI does not warrant or representthat any license, either express or implied, is granted under any patent right, copyright, mask work right, or otherintellectual property right of TI covering or relating to any combination, machine, or process in which suchsemiconductor products or services might be or are used. TI’s publication of information regarding any thirdparty’s products or services does not constitute TI’s approval, warranty or endorsement thereof.Copyright © 1999, Texas Instruments Incorporated。

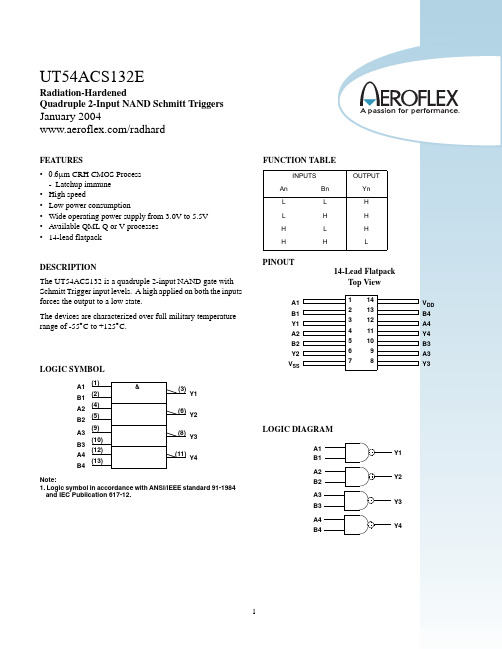

UT54ACS132EUCC中文资料

1UT54ACS132ERadiation-HardenedQuadruple 2-Input NAND Schmitt TriggersJanuary 2004/radhardFEATURES•0.6µm CRH CMOS Process - Latchup immune •High speed•Low power consumption•Wide operating power supply from 3.0V to 5.5V •Available QML Q or V processes •14-lead flatpackDESCRIPTIONThe UT54ACS132 is a quadruple 2-input NAND gate with Schmitt Trigger input levels. A high applied on both the inputs forces the output to a low state.The devices are characterized over full military temperature range of -55°C to +125°C.LOGIC SYMBOLY1(3)(6)Y2Y3(8)(11)Y4(1)A1(2)B1(4)A2(5)B2(9)A3(10)B3(12)A4(13)B4Note:1. Logic symbol in accordance with ANSI/IEEE standard 91-1984 and IEC Publication 617-12.&RADIATION HARDNESS SPECIFICATIONS 1PARAMETER LIMIT UNITSTotal Dose 1.0E6rads(Si)SEU Threshold 280MeV-cm2/mgSEL Threshold 120MeV-cm2/mgNeutron Fluence 1.0E14n/cm2Notes:1. Logic will not latchup during radiation exposure within the limits defined in the table.2. Device storage elements are immune to SEU affects.ABSOLUTE MAXIMUM RATINGSSYMBOL PARAMETER LIMIT UNITS V DD Supply voltage-0.3 to 7.0VV I/O V oltage any pin-.3 to V DD + .3VT STG Storage Temperature range-65 to +150°CT J Maximum junction temperature+175°CT LS Lead temperature (soldering 5 seconds)+300°CΘJC Thermal resistance junction to case20°C/WI I DC input current±10mAP D Maximum power dissipation1WNote:1. Stresses outside the listed absolute maximum ratings may cause permanent damage to the device. This is a stress rating only, functional operation of the device at these or any other conditions beyond limits indicated in the operational sections is not recommended. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.RECOMMENDED OPERATING CONDITIONSSYMBOL PARAMETER LIMIT UNITS V DD Supply voltage 3.0 to 5.5VV IN Input voltage any pin0 to V DD VT C Temperature range-55 to +125°C23DC ELECTRICAL CHARACTERISTICS FOR THE UT54ACS132E 7 ( V DD = 3.0V to 5.5V; V SS = 0V 6; -55°C < T C < +125°C)Notes:1. Functional tests are conducted in accordance with MIL-STD-883 with the following input test conditions: V IH = V IH (min) + 20%, - 0%; V IL = V IL (max) + 0%, - 50%, as specified herein, for TTL, CMOS, or Schmitt compatible inputs. Devices may be tested using any input voltage within the above specified range, but are guaranteed to V IH (min) and V IL (max).2. Supplied as a design limit but not guaranteed or tested.3. Per MIL-PRF-38535, for current density ≤5.0E5 amps/cm 2, the maximum product of load capacitance (per output buffer) times frequency should not exceed 3,765pF/MHz.4. Not more than one output may be shorted at a time for maximum duration of one second.5. Capacitance measured for initial qualification and when design changes may affect the value. Capacitance is measured between the designated terminal and V SS at frequency of 1MHz and a signal amplitude of 50mV rms maximum.6. Maximum allowable relative shift equals 50mV .7. All specifications valid for radiation dose ≤ 1E6 rads(Si) per MIL-STD-883 Method 1019 Condition B.8. Power dissipation specified per switching output.9. This value is guaranteed based on characterization data, but not tested.SYMBOL DescriptionCONDITIONVDD MINMAX UNIT V T+Schmitt trigger positive-going threshold 13.0V 2.1V5.5V 3.85V T-Schmitt trigger negative-going threshold 1 3.0V 0.9V 5.5V 1.65V HHysteresis 2(V T+ - V T-)3.0V 0.3 1.2V4.5V .6 1.5I IN Input leakage current V IN = V DD or V SS5.5V -11µA V OL Low-level output voltage 3I OL = 100µA 3.0V 0.25V 4.5V 0.25V OH High-level output voltage 3I OH = -100µA 3.0V 2.75V 4.5V 4.25I OSShort-circuit output current 2 ,4V O = V DD and V SS3.0V -100100mA5.5V-200200I OLLow level output current 9V IN = V DD or V SS V OL = 0.4V3.0V 6mA 5.5V 8I OHHigh level output current 9V IN = V DD or V SS V OH = V DD -0.4V3.0V -6mA5.5V -8P total Power dissipation 2, 8C L = 50pF 5.5V 3.0V 1.90.76mW/MHz I DDQ Quiescent Supply Current V IN = V DD or V SS 5.5V 10µA C IN Input capacitance 5ƒ = 1MHz 0V 15pF C OUTOutput capacitance 5ƒ = 1MHz0V15pFAC ELECTRICAL CHARACTERISTICS FOR THE UT54ACS132E2(V DD = 3.0V to 5.5V; V SS = 0V 1, -55°C < T C < +125°C)SYMBOL PARAMETER V DD MINIMUM MAXIMUM UNIT t PHL Input to Yn C L = 30pF 3.0V & 3.6V212ns4.5V &5.5V28C L = 50pF 3.0V & 3.6V216ns4.5V &5.5V212t PLH Input to Yn C L = 30pF 3.0V & 3.6V215ns4.5V &5.5V211C L = 50pF 3.0V & 3.6V219ns4.5V &5.5V215Notes:1. Maximum allowable relative shift equals 50mV.2. All specifications valid for radiation dose ≤ 1E6 rads(Si) per MIL-STD-883 Method 1019 Condition B.4PackagingOrdering Information UT54ACS132EUT54*******-***Lead Finish: (Notes 1 & 2)A = SolderC = GoldX = OptionalScreening: (Note 3)C = Military Temperature Range (-55o C to +125o C)Package Type:U = 14-lead ceramic bottom-brazed dual-in-line FlatpackPart Number:132E = Quadruple 2-Input NAND GateI/O Type:ACS = CMOS compatible I/O levelNotes:1. Lead finish (A, C, or X) must be specified.2. If an "X" is specified when ordering, then the part marking will match the lead finish and will be either "A" (solder) or "C" (gold).3. Military Temperature Range flow per Aeroflex Manufacturing Flows Document. Devices have 48 hours of burn-in and are test at -55o C, room temperature, and 125o C. Radiation characterisitics are neither tested nor guaranteed and may not be specified.67UT54ACS132E: SMDDrawing Number:96542 = UT54ACS132E Device Type:02 = TID per MIL-STD-883 TM1019 Condition B Package Type:X = 14-lead ceramic bottom-brazed dual-in-line Flatpack Lead Finish: (Notes 1 & 2)A = Solder C = Gold X = Optional5962 *********Notes:1. Lead finish (A, C, or X) must be specified.2. If an "X" is specified when ordering, then the part marking will match the lead finish and will be either "A" (solder) or "C" (gold).3. Total dose radiation must be specified when ordering. QML V is not available without radiation testing.**Total Dose: (Note 3 & 4)R = 1E5 rads(Si)F = 3E5 rads(Si)G = 5E5 rads(Si)H = 1E6 rads(Si)03 = TID per MIL-STD-883 TM1019 Condition A Class Designator:Q = QML Class Q V = QML Class V4. Device type 02 is only offered with a TID tolerance guarantee of 3E5 rads(Si) or 1E6 rads(Si) and is tested in accordance with MIL-STD-883 Test Method 1019 Condition B. Device type 03 is only offered with a TID tolerance guarantee of 1E5 rads(Si), 3E5 rads(Si), and 5E5 rads(Si), and is tested in accordance with MIL-STD-883 Test Method 1019 Condition A.8。

54AC2525DMQB中文资料

MICROCIRCUIT DATA SHEET

Features

Ideal for signal generation and clock distribution Guaranteed pin to pin and part to part skew Guaranteed 2000V minimum ESD protection 24 mA output drive capability CONTROLLING DOCUMENT: 54AC2525WFQMLV 5962F9217401VDA 54AC2525WRQMLV 5962R9217401VDA

125mV/ns

3

元器件交易网

MV54AC2525-X-RH REV 1A0

MICROCIRCUIT DATA SHEET

Electrical Characteristics

DC PARAMETERS

(The following conditions apply to all the following parameters, unless otherwise specified.) DC: VCC 3.0V to 5.5V, Temp. Range: -55 C to 125 C. NOTE: -55C TEMPERATURE, SUBGROUP 3 IS GUARANTEED BUT NOT TESTED. SYMBOL IIH PARAMETER High level input Current Low level input Current Low level Output Voltage CONDITIONS VCC=5.5V, VM=5.5V NOTES PINNAME MIN MAX 0.1 1.0 -0.1 -1.0 .10 .10 .10 .32 .40 .36 .50 .36 .50 1.65 UNIT uA uA uA uA V V V V V V V V V V V V V V V V V V V V 90 80 nA uA SUBGROUPS 1 2, 3 1 2, 3 1, 2, 3 1, 2, 3 1, 2, 3 1 2, 3 1 2, 3 1 2, 3 1, 2, 3 1, 2, 3 1, 2, 3 1, 2, 3 1 2, 3 1 2, 3 1 2, 3 1, 2, 3 1 2, 3

SNJ54AC11FK中文资料

PACKAGING INFORMATIONOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)5962-87611012A ACTIVE LCCC FK201TBD Call TI Level-NC-NC-NC 5962-8761101CA ACTIVE CDIP J141TBD Call TI Level-NC-NC-NC 5962-8761101DA ACTIVE CFP W141TBD Call TI Level-NC-NC-NCSN74AC11D ACTIVE SOIC D1450Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AC11DBLE OBSOLETE SSOP DB14TBD Call TI Call TISN74AC11DBR ACTIVE SSOP DB142000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AC11DBRE4ACTIVE SSOP DB142000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AC11DE4ACTIVE SOIC D1450Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AC11DR ACTIVE SOIC D142500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AC11DRE4ACTIVE SOIC D142500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AC11N ACTIVE PDIP N1425Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NCSN74AC11NE4ACTIVE PDIP N1425Pb-Free(RoHS)CU NIPDAU Level-NC-NC-NCSN74AC11NSR ACTIVE SO NS142000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AC11NSRE4ACTIVE SO NS142000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AC11PW ACTIVE TSSOP PW1490Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AC11PWE4ACTIVE TSSOP PW1490Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74AC11PWLE OBSOLETE TSSOP PW14TBD Call TI Call TISN74AC11PWR ACTIVE TSSOP PW142000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74AC11PWRE4ACTIVE TSSOP PW142000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SNJ54AC11FK ACTIVE LCCC FK201TBD Call TI Level-NC-NC-NC SNJ54AC11J ACTIVE CDIP J141TBD Call TI Level-NC-NC-NC SNJ54AC11W ACTIVE CFP W141TBD Call TI Level-NC-NC-NC (1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan-The planned eco-friendly classification:Pb-Free(RoHS)or Green(RoHS&no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free(RoHS):TI's terms"Lead-Free"or"Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all6substances,including the requirement that lead not exceed0.1%by weight in homogeneous materials.Where designed to be solderedat high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Green(RoHS&no Sb/Br):TI defines"Green"to mean Pb-Free(RoHS compatible),and free of Bromine(Br)and Antimony(Sb)based flame retardants(Br or Sb do not exceed0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.元器件交易网元器件交易网IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications,enhancements, improvements, and other changes to its products and services at any time and to discontinueany product or service without notice. Customers should obtain the latest relevant information before placingorders and should verify that such information is current and complete. All products are sold subject to TI’s termsand conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale inaccordance with TI’s standard warranty. T esting and other quality control techniques are used to the extent TIdeems necessary to support this warranty. Except where mandated by government requirements, testing of allparameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible fortheir products and applications using TI components. T o minimize the risks associated with customer productsand applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right,copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or processin which TI products or services are used. Information published by TI regarding third-party products or servicesdoes not constitute a license from TI to use such products or services or a warranty or endorsement thereof.Use of such information may require a license from a third party under the patents or other intellectual propertyof the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is withoutalteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproductionof this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable forsuch altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for thatproduct or service voids all express and any implied warranties for the associated TI product or service andis an unfair and deceptive business practice. TI is not responsible or liable for any such statements.Following are URLs where you can obtain information on other Texas Instruments products and applicationsolutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetworkMicrocontrollers Security /securityTelephony /telephonyVideo & Imaging /videoWireless /wirelessMailing Address:Texas InstrumentsPost Office Box 655303 Dallas, Texas 75265Copyright 2005, Texas Instruments Incorporated。

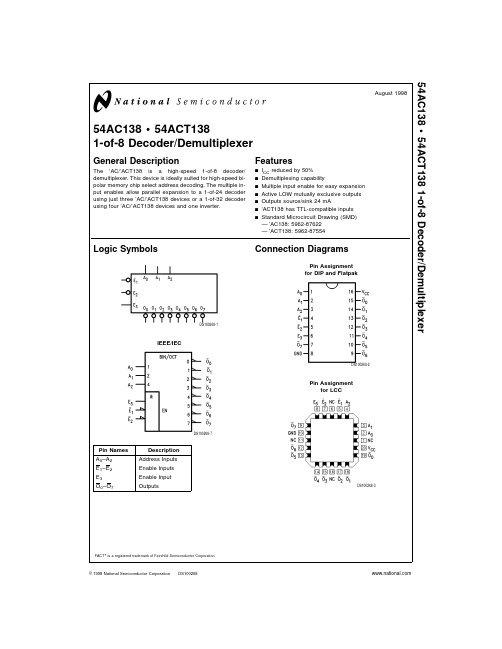

54AC138中文资料

−0.5V to +7.0V

−20 mA +20 mA −0.5V to VCC + 0.5V

−20 mA +20 mA −0.5V to VCC + 0.5V

±50 mA

±50 mA −65˚C to +150˚C

175˚C

Conditions

Supply Voltage (VCC) ’AC

2.0V to 6.0V

125 mV/ns

Note 1: Absolute maximum ratings are those values beyond which damage

to the device may occur. The databook specifications should be met, without

exception, to ensure that the system design is reliable over its power supply,

temperature, and output/input loading variables. National does not recom-

— ’AC138: 5962-87622 — ’ACT138: 5962-87554

Logic Symbols

Connection Diagrams

Pin Assignment for DIP and Flatpak

IEEE/IEC

DS100268-1

Pin Names A0– A2 E1– E2 E3 O0– O7

L

H = HIGH Voltage Level L = LOW Voltage Level X = Immaterial

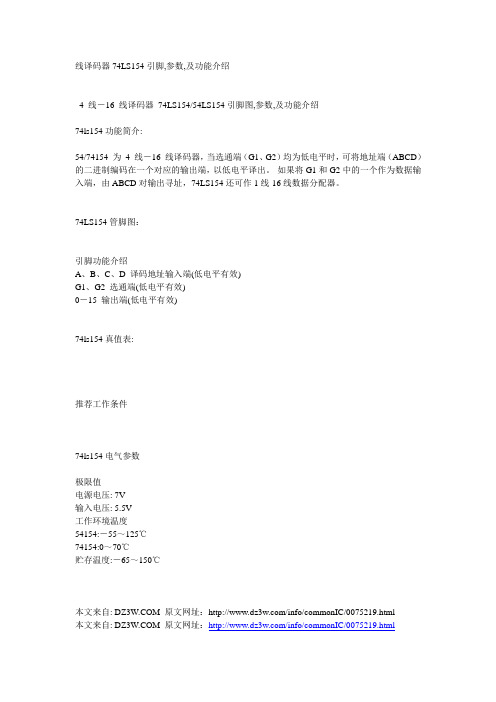

74154中文资料

线译码器74LS154引脚,参数,及功能介绍--------------------------------------------------------------------------------4 线-16 线译码器74LS154/54LS154引脚图,参数,及功能介绍74ls154功能简介:54/74154 为4 线-16 线译码器,当选通端(G1、G2)均为低电平时,可将地址端(ABCD)的二进制编码在一个对应的输出端,以低电平译出。

如果将G1和G2中的一个作为数据输入端,由ABCD对输出寻址,74LS154还可作1线-16线数据分配器。

74LS154管脚图:引脚功能介绍A、B、C、D 译码地址输入端(低电平有效)G1、G2 选通端(低电平有效)0-15 输出端(低电平有效)74ls154真值表:推荐工作条件74ls154电气参数极限值电源电压: 7V输入电压: 5.5V工作环境温度54154:-55~125℃74154:0~70℃贮存温度:-65~150℃本文来自: 原文网址:/info/commonIC/0075219.html本文来自: 原文网址:/info/commonIC/0075219.html74ls154芯片资料2007-08-20 20:4874ls138译码器74ls139 跟74ls138类似,区别在于139内部是2个独立的2-4译码器。

74ls154跟74LS138很类似,差别就在于,138是3-8译码器,154是4-16译码器。

类别:集成块资料| 添加到搜藏| 分享到i贴吧| 浏览(1104) | 评论(1)上一篇:DDS芯片AD9850的工作原理及其与...下一篇:芯片的型号及功能最近读者:登录后,您就出现在这里。

有梦无花wangjunxiahah艺新。

说明书 通用电磁阀门系列53和54

General Purpose Solenoid ValvesSeries 53 and 54•2 Way•Diaphragm Pilot Operated •Normally Closed •Normally Open •3/8", 1/2" and 3/4" NPT/G •Air, Gas, Waterand Light OilSales BulletinBrazil Automation DivisionParker Hannifin Ind. e Com. Ltda.Av. Lucas Nogueira Garcez 218112325-900 Jacarei, SP - BrasilOptions (Add the suffixes after the voltage)Seals•Viton (FKM), use suffix "V".•Ethylene propylene (EPDM), use suffix "P".•Neoprene (CR), use suffix "N".Enclosure•Open enclosure, use suffix "O".•General purpose with plug-in connector (Nema 3R),use suffix "C".•General purpose with plug-in connector + LED + surge supressor, use suffix "U".•Explosion proof, water and dust (Nema 4, 7 and 9),use suffix "E".•Air pilot operated valve, modify the eighth and nineth digit from "XX" to "L" (Only for normally closed valves).Shading Coil•Aluminium (only for AC valve with acetylene),use suffix "5".Others•"G" thread, use suffix "B".•Manual override, use suffix "M" (only for NC valves).•Coil class "H", use suffix "H".•"G" thread + Manual override, use suffix "Q".•Coil class "H" + Manual override, use suffix "R".•"G" thread + Manual override + Coil class "H", use suffix "D".Installation•Valves can be mounted in any position without jeopardising their operation.Vacuum•Valves in which minimum differential pressure is zero can be used until 10-2 mm Hg (Please consult our office).Oxygen•Use suffix "I " and seals in neoprene (CR).Standard MaterialsValve Body:BrassSeals:Buna-N (NBR)Plunger and Stop:430F S.S.Springs:302 S.S.Shading Coil:Copper Coil:Class "F"Valves with Plug-in ConnectorsTwo Way - Normally Closed - ACBody and Seals: Forged Brass and NBRNote: If LED and surge supressor are necessary, modify the seventh digit from "Z" to "J".∆Two Way - Normally Closed - DCBody and Seals: Forged Brass and NBRNote: If LED and surge supressor are necessary, modify the seventh digit from "Z" to "J".∆Note: Enclosure "9" is only compatible with normally closed valves and coil powers 8 W and 10 W.Repair kit for series 54 is only compatible with "G" and "E" enclosures.∆How to Order Repair KitsRepair Kit for Series 53 and 543/8"Q 1/2"3/4"NC F NOA SealsC 11 W 311,5 W 78 W710 WACDCCoil Power EnclosureFunction Port Size (NPT/G)K 53K 54For coil which power is 8 N or 10 N (IP 65)GOpen enclosureGeneral purpose (NEMA 1)General purpose with plug-in connector (NEMA 3R)Explosion, water and dust proof(NEMA 4, 7 and 9)E 9L Air pilot operatedvalvesB NBR V FKM P EPDM N CRParker Hannifin Ind. e Com. Ltda.Av. Lucas Nogueira Garcez 2181Esperança Caixa Postal 148。

集成设备技术公司ICS854S54AKI-01双2 1,1 2差分到LVDS多路复用器说明书