New group of chalcopyrite-type semiconductor for solar cells

超米特电子有限公司产品说明书

1US Headquarters TEL +(1) 781-935-4850FAX +(1) 781-933-4318 • Europe TEL +(44) 1628 404000FAX +(44) 1628 404090Asia Pacific TEL +(852) 2 428 8008FAX +(852) 2 423 8253South America TEL +(55) 11 3917 1099FAX +(55) 11 3917 0817Superior elongation and tensilestrength help to prevent tearing in use due to mishandling. Typical properties for CHO-SEAL 1310 and 1273 materi-al are shown on pages 33 and 32respectively.High Shielding PerformanceCHO-SEAL 1310 material provides more than 80 dB of shielding effectiv-ness from 100 MHz to 10 GHz, while CHO-SEAL 1273 material provides more than 100 dB.Low Volume ResistivityBoth materials have exceptionally low volume resistivity, which makes them well suited for grounding appli-cations in which a flexible electrical contact is needed.Low Compression GasketSpacer gaskets are typicallydesigned to function under low deflec-tion forces. Chomerics uses design tools such as Finite Element Analysis (FEA) to accurately predict compres-sion-deflection behavior of various cross section options. Refer to page16.LCP Plastic SpacerLiquid crystal polymer (LCP)spacers, including those made with Vectra A130 material, provide aCHO-SEAL ®1310 or 1273Conductive ElastomersWith EMI spacer gaskets, shielding and grounding are provided by Chomerics’CHO-SEAL 1310 and 1273 conductive elastomers, specifi-cally formulated for custom shape molded parts. They provide excellent shielding and isolation against electro-magnetic interference (EMI), or act as a low impedance ground path between PCB traces and shielding media. Physically tough, these elas-tomers minimize the risk of gasket damage, in contrast to thin-walled extrusions or unsupported molded gaskets.Silicone-based CHO-SEAL 1310and 1273 materials offer excellent resistance to compression set over a wide temperature range, resulting in years of continuous service. CHO-SEAL 1310 material is filled with silver-plated-glass particles, while 1273 utilizes silver-plated-copper filler to provide higher levels of EMI shielding effectiveness.EMI Spacer GasketsThe unique design of Chomerics’EMI spacer gaskets features a thin plastic retainer frame onto which a conductive elastomer is molded. The elastomer can be located inside or outside the retainer frame, as well as on its top and bottom surface. EMI spacer gaskets provide a newapproach to designing EMI gaskets into handheld electronics such as dig-ital cellular phones. Board-to-board spacing is custom designed to fit broad application needs. Customized cross sections and spacer shapes allow for very low closure forcerequirements and a perfect fit in any design or device.Robotic InstallationSpacer gaskets can be installed quickly by robotic application. Integral locater pins in the plastic spacer help ensure accuratepositioning in both manual and pick-and-place assembly. Benefits include faster assembly and lower labor costs.The integrated conductive elastomer/plastic spacer gasket is a low cost,easily installed system for providing EMI shielding and grounding in small electronic enclosures.Figure 1Single Piece EMI Gasket/Locator PinsCHO-SEAL 1310 or 1273 Conductive Elastomer (Inside)Plastic Spacer Around Outsideor InsideApplications for EMI Spacer GasketsThe spacer gasket concept is especially suited to digital and dual board telephone handsets or other handheld electronic devices. It provides a low impedance path between peripheral ground traces on printed circuit boards and components such as:•the conductive coating on a plastic housing•another printed circuit board •the keypad assemblyTypical applications for EMI spacer gaskets include:•Digital cellular, handyphone and personal communications services (PCS) handsets •PCMCIA cards•Global Positioning Systems (GPS)•Radio receivers•Other handheld electronics, e.g.,personal digital assistants (PDAs)•Replacements for metal EMI shield-ing “fences” on printedcircuit boards in wireless tele-communications devicesstable platform for direct, highprecision molding of conductive elas-tomers. The Vectra A130 material described in Table 1 has excellent heat deflection temperature character-istics (489°F, 254°C). For weight con-siderations, the LCP has aspecific gravity of only 1.61. This plas-tic is also 100% recyclable.Typical EMI Spacer Gasket Design ParametersThe EMI spacer gasket concept can be considered using the design parameters shown in Table 2. Some typical spacer gasket profiles are shown below.Figure 2Typical Spacer Gasket Profiles3US Headquarters TEL +(1) 781-935-4850FAX +(1) 781-933-4318 • Europe TEL +(44) 1628 404000FAX +(44) 1628 404090Asia Pacific TEL +(852) 2 428 8008FAX +(852) 2 423 8253South America TEL +(55) 11 3917 1099FAX +(55) 11 3917 0817Finite Element AnalysisChomerics, a division of the Parker Hannifin Corporation’s Seal Group, is the headquarters of Parker Seal’s Elastomer Simulation Group. This unit specializes in elastomer finite element analysis (FEA) using MARC K6 series software as a foundation for FEA capability.Benefits of FEA include:•Quickly optimizing elastomer gasket designs•Allowing accurate predictions of alternate elastomer design concepts •Eliminating extensive trial and error prototype evaluationTypical use of FEA in EMI spacer gasket designs is to evaluate the force vs. deflection requirements of alternate designs.For example, onespacer design features a continuous bead of con-ductive elastomer molded onto a plastic spacer. An alternative designemploys an “interrupted bead,” where the interrup-tions (gaps left on the plastic frame) are sized to maintain the requiredlevel of EMI shielding. Figure 4illustrates these alternative designs.Gasket DeflectionFigure 5 compares the effect of continuous and interrupted elastomer gasket designs in terms of the force required to deflect the conductive elastomer. This actual cellular handset application required a spacer gasket with interrupted bead to meet desired deflection forces.Chomerics Designand Application ServicesChomerics will custom design a spacer for your application. Advice,analysis and design assistance will be provided by Chomerics Applications and Design engineers at no additional fee. Contact Chomerics directlyat the locations listed at the bottom of the page.Figure 3FEA Example of an EMISpacer Gasket Cross SectionFigure 4Continuous (top) and InterruptedElastomer GasketsFigure 5Typical Spacer Gasket Deflection。

Richtek RT4823 单元说明书

RT4823Wide Input and Ultra-Low Quiescent Current Boost Converter with High EfficiencyGeneral DescriptionThe RT4823 integrates built-in power transistors, synchronous rectification, and low supply current to provide a compact solution for systems using advanced Li-Ion battery chemistries. The RT4823 is capable of supplying significant energy when the battery voltage is lower than the required voltage for system power ICs. The RT4823 is a boost regulator designed to provide a minimum output voltage from a single-cell Li-Ion battery, even when the battery voltage is below system minimum. In boost mode, output voltage regulation is guaranteed to a maximum load current of 1500mA. Quiescent current in shutdown mode is less than 1μA, which maximizes the battery life. The regulator transitions smoothly between bypass and normal boost mode. The device can be forced into bypass mode to reduce quiescent current.The RT4823 is available in the WL-CSP-9B 1.3x1.2 (BSC) package.Applications⚫NFC Device Power Supply⚫USB Charging Ports⚫PC Accessory Application (Keyboard, Mouse...etc.)⚫TWS (True Wireless Stereo) Hall Sensor⚫Gaming Device Sensor Features⚫Ultra-Low Operating Quiescent Current⚫Quickly Start-Up Time (< 400μsec)⚫3 Few External Components : 1μH Inductor, 0402 Case Size Input and 0603 Case Size Output Case Size Capacitors⚫Input Voltage Range : 1.8V to 5.5V⚫Support V IN > V OUT Operation⚫Default Boost Output Voltage Setting :V OUT = 5V⚫Maximum Continuous Load Current : 1.3A atV IN > 3.6V Boosting V OUT to 5V⚫Up to 93% Efficiency⚫EN(H) : Boost Mode⚫EN(L), BP(H) : Bypass Mode⚫EN(L), BP(L) : Shutdown Mode⚫Internal Synchronous Rectifier⚫Over-Current Protection⚫Cycle-by-Cycle Current Limit⚫Over-Voltage Protection⚫Short-Circuit Protection⚫Over-Temperature Protection⚫Small WL-CSP-9B 1.3x1.2 (BSC) PackageSimplified Application CircuitV INV OUTRT4823Ordering InformationRT4823WSC : WL-CSP-9B 1.3x1.2 (BSC)Note :Richtek products are :④ RoHScompliant and compatible with the currentrequirements of IPC/JEDEC J -STD -020.④ Suitable for use in SnPb or Pb -free soldering processes.Marking Information8B : Product CodeW : Date CodePin Configuration(TOP VIEW)VOUT GNDVIN EN BPSW V O U TSWG N DC1C2C3B3B1B2A1A2A3WL -CSP -9B 1.3x1.2 (BSC)Functional Pin DescriptionRT4823Functional Block DiagramVINVOUTENBPGNDOperationThe RT4823 combines built-in power transistors, synchronous rectification, and low supply current, and it provides a compact solution for system using advanced Li-Ion battery chemistries.In boost mode, output voltage regulation is guaranteed to maximum load current of 1.5A. Quiescent current in Shutdown mode is less than 1 A, which maximizes the battery life.Power-On ResetIf input voltage is lower than POR, the internal digital and analog circuit are disabled. If input voltage is higher than POR, the Boost converter behavior is shown as follows :1. IC Digital circuit will be activated.2. Internal register will be loaded in default value.3. Boost converter will enter free-running mode (detailed information is shown in free-running mode section).4. If V OUT > 2.2V (or V IN > 2.2V), Boost converter will enter closed loop control and load in E-fuse value to the internal register.RT4823Free-Running ModeIf both voltages of V IN and V OUT are lower than 2.2V, the Boost converter will into free-running mode. In this mode, switching frequency operation is 1.5MHz and duty cycle of Boost converter is 25%. It is translation of power-on stage, and there is implemented current limit function for converter soft-start. The current limit level should be lower than 900mA.EN and BPAs Table 1 shows, there are three device states in the RT4823. When EN and BP pull low, it is shutdown mode, and the quiescent current is less than 1μA. If EN pulls high (BP do not care), the RT4823 is in boost mode and it is with low quiescent operation. If BP pulls high and EN pulls low, the RT4823 is in bypass mode. There should be a delay time (< 250μs) from EN pull-high to power ready, to guarantee normal operation.EnableThe boost can be enabled or disabled by the EN pin. When the EN pin is higher than the threshold of logic-high, the device starts operating as shown in Figure 1 operation diagram. In shutdown mode, the converter stops switching, and the internal control circuit is turned off. The output voltage is discharged by component consumption (such as Cap ESR) since there is no discharge function in this state. Soft-Start StateDuring soft-start state, if VOUT reaches 99% V OUT_Target , the RT4823 will enter boost operation. When system powers on with heavy loading (higher than pre-charge current), the RT4823 is in pre-charge state until loading release. Boost/Auto Bypass ModeThere are two normal operation modes, the boost mode, and the auto bypass mode. In the boost mode (V IN – 0.3V < V OUT_Target ), the converter boosts output voltage to V OUT_Target , and delivers power to loading by internal synchronous switches after the soft-start state. In the auto bypass mode (V IN – 0.3V ≥ V OUT_Target ), input voltage will deliver to the output terminal loadingdirectly. That can provide maximum current capacity with the RT4823. Detailed information is shown in the Boost Mode section.Boost Mode (Auto PFM/PWM Control Method) In order to save power and improve efficiency at low loads, the Boost converter operates in PFM (Pulse Frequency Modulation) as the inductor drops into DCM (DiscontinuousCurrentMode).Theswitchingfrequency is proportional to loading to reach output voltage regulation. When loading increases and inductor current is in continuous current mode, the Boost automatically enters PWM mode.RT4823Table 2. The RT4823 Start -Up DescriptionV OUTV V IN V 0.99 x VFigure 1. V OUT Mode Transition Diagram with EN L to H and V IN Variation (I OUT = 0A)ProtectionThe RT4823 features protections listed in the table below. It describes the protection behaviors.RT4823Absolute Maximum Ratings (Note 1)⚫VIN, VOUT, SW, EN, BP -------------------------------------------------------------------------------------------- –0.3V to 6.5V ⚫Power Dissipation, P D@ T A = 25°C⚫WL-CSP-9B 1.3x1.2 (BSC) ----------------------------------------------------------------------------------------- 1.54W⚫Package Thermal Resistance (Note 2)⚫WL-CSP-9B 1.3x1.2 (BSC) ----------------------------------------------------------------------------------------- 64.9︒C/W⚫Lead Temperature (Soldering, 10 sec.) -------------------------------------------------------------------------- 260︒C⚫Junction Temperature ------------------------------------------------------------------------------------------------ 150︒C⚫Storage Temperature Range --------------------------------------------------------------------------------------- −65︒C to 150︒C ⚫ESD Susceptibility (Note 3)HBM (Human Body Model) ----------------------------------------------------------------------------------------- 2kV Recommended Operating Conditions (Note 4)⚫Input Voltage Range (Boost Mode) ------------------------------------------------------------------------------- 1.8V to 5.5V⚫Input Voltage Range (Bypass Mode) ----------------------------------------------------------------------------- 2.2V to 5.5V⚫Output Voltage Range ----------------------------------------------------------------------------------------------- 5V⚫Input Capacitor, CIN -------------------------------------------------------------------------------------------------- 4.7μF⚫Output Capacitor, COUT -------------------------------------------------------------------------------------------- 3.5μF to 50μF ⚫Inductance, L ----------------------------------------------------------------------------------------------------------- 0.7μH to 2.2μH ⚫Input Current (Average current into SW) ----------------------------------------------------------------------- 1.8A⚫Input Current (Peak current into SW) ----------------------------------------------------------------------------- 4A⚫Ambient Temperature Range -------------------------------------------------------------------------------------- −40︒C to 85︒C ⚫Junction Temperature Range -------------------------------------------------------------------------------------- −40︒C to 125︒C Electrical Characteristics(V IN = 3.6V, C IN = 4.7μF, C OUT = 10μF, L1 = 1μH. All typical (TYP) limits apply for T A = 25︒C, unless otherwise specified. All minimum (MIN) and maximum (MAX) apply over the full operating ambient temperature range (−40︒C ≤ T A≤85︒C).RT4823RT4823Note 1. Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.Note 2. θJA is measured under natural convection (still air) at T A= 25°C with the component mounted on a high effective-thermal-conductivity four-layer test board on a JEDEC 51-7 thermal measurement standard. θJC is measured at the exposed pad of the package.Note 3. Devices are ESD sensitive. Handling precautions are recommended.Note 4. The device is not guaranteed to function outside its operating conditions.RT4823Typical Application CircuitV OUTV INTable 3. Recommended Components InformationRT4823Typical Operating CharacteristicsEfficiency vs. Output Current204060801000.0010.010.11101001000Output Current (mA)E f f i c i e n c y (%)Boost Load Regulation4.904.955.005.055.105.155.200.0010.0100.1001.00010.000Output Current (A)O u t p u t V o l t a g e (V )Boost Line Regulation4.905.005.105.205.305.405.502.43.03.64.24.85.46.0Input Voltage (V)O u t p u t V o l t a g e(V )Maximum Output Current vs. Input Voltage0.00.51.01.52.02.51.82.22.63.03.43.84.24.65.0Input Voltage (V)M a x i m u m O u t p u t C ur r e n t (A )204060801001200.0010.010.11Output Current (A)O u t p u t R i p p l e (m V )Output Ripple vs. Output Current204060801001200.0010.010.11Output Current (A)O u t p u t R i p p l e (m V )Quiescent Current vs. Input Voltage1.82.12.42.73.03.33.63.94.24.54.8Input Voltage (V)2.2 2.5 2.83.1 3.4 3.74.0 4.3 4.6 4.95.2 5.5Input Voltage (V)Pre-Charge Current vs. Input Voltage0501001502002503003504004505001.82.12.42.73.03.33.63.94.24.5Input Voltage (V)P r e -C h a r g e C u r r e n t (m A)Pre-Charge Current vs. Temperature50100150200250300350400-50-250255075100125Temperature (°C)P r e -C h a r g e C u r r en t (m A )VOUT (1V/Div)ILX (1V/Div)Boost Short CircuitTime (0.01ms/Div)SW (4V/Div)VOUT (1V/Div)ILX (0.2V/Div)Power-OnTime (0.1ms/Div)E N (2V/Div)VOUT (0.1V/Div)Load TransientTime (0.1ms/Div)IOUT (0.2V/Div)VOUT (0.1V/Div)IOUT (0.2V/Div)Time (0.1ms/Div)Load TransientVOUT (0.1V/Div)IOUT (0.5V/Div)Load Transient Time (0.1ms/Div)IOUT (0.5V/Div)Sine Waveform StabilityTime (5ms/Div)VOUT (0.1V/Div)SW (4A/Div)VOUT (0.1V/Div)Time (20ms/Div)PFM Output RippleILX (0.4A/Div)Time (20ms/Div)PFM Output RippleVOUT (0.02V/Div)ILX (0.4V/Div)PWM Output RippleTime (0.0002ms/Div)SW (4V/Div)VOUT (0.02V/Div)ILX (0.4V/Div)PWM Output RippleTime (0.0002ms/Div)SW (4V/Div)SW (2V/Div)E N (1V/Div)Bypass Mode into Boost ModeTime (1ms/Div)VOUT (1V/Div)VOUT (1V/Div)SW (2V/Div)Time (1ms/Div)Boost Mode into Bypass ModeE N (1V/Div)Application InformationEnableThe device can be enabled or disabled by the EN pin. When the EN pin is higher than the threshold of logic-high, the device starts operating with soft-start. Once the EN pin is set at low, the device will be shut down. In shutdown mode, the converter stops switching, internal control circuitry is turned off, and the load is disconnected from the input. This also means that the output voltage can drop below the input voltage during shutdown. Power Frequency Modulation (PFM)PFM is used to improve efficiency at light load. When the output voltage is lower than a set threshold voltage, the converter will operate in PFM. It raises the output voltage with several pulses until the loop exits PFM.Thermal ShutdownThe device has a built-in temperature sensor which monitors the internal junction temperature. If the temperature exceeds the threshold, the device stops operating. As soon as the IC temperature decreases below the threshold with a hysteresis, it starts operating again. The built-in hysteresis is designed to avoid unstable operation at IC temperatures near the over temperature threshold. Inductor SelectionThe primary concern of inductor selection is the maximum loading of the application. The example is given by the application condition and equations below.Application condition:V IN = 3.6V, V OUT = 5V, I OUT = 1.3A, converter efficiency = 90.2%, Frequency = 3.5MHz, L = 1μH. Step 1 : To calculate input current (I IN ).OUT OUT IN IN V II 2.001A V Eff⨯==⨯Step 2 : To calculate duty cycle of boost converter.INOUTV D 10.28V =−= Step 3 : To calculate peak current of inductor.IN L(Peak)IN V DI I 0.5 2.145A L Freq.⨯=+⨯=⨯The recommended nominal inductance value is 1μH. It is recommended to use inductor with dc saturation current ≥ 2200mA. Input Capacitor SelectionAt least an input capacitor of 4.7μF and the rate voltage of 6.3V for DC bias is recommended to improve transient behavior of the regulator and EMI behavior of the total power supply circuit for SW. And input capacitor placed as close as possible to the VIN and GND pins of the IC is recommended. Output Capacitor SelectionAt least a 10μF capacitors is recommended to improve V OUT ripple.Output voltage ripple is inversely proportional toC OUT .Output capacitor is selected according to output ripple which is calculated as :LOADRIPPLE(P P)ON OUT IN ON SW SW OUT INLOAD OUT SW OUT RIPPLE(P P)SW SWIV t C andV t t D t 1V therefore :VI C t 1V V and1t f −−=⨯⎛⎫=⨯=⨯− ⎪⎝⎭⎛⎫=⨯−⨯⎪⎝⎭=The maximum V RIPPLE occurs at minimum input voltage and maximum output load.Boost Converter Sleeping Mode OperationThe PFM mode and PWM mode are implemented in the RT4823. PFM mode is designed for power saving operation when the system operates at light load. There is a mode transition between PFM and PWM mode. When system loading is increasing, the operating mode transitions from PFM mode to PWM mode. Please note that, within this small loading current range, the mode changed causes output ripple to increase.Current LimitThe RT4823 employs a valley-current limit detection scheme to sense inductor current during the off-time. When the loading current is increased such that the loading is above the valley current limit threshold, the off-time is increased until the current is decreased to valley-current threshold. Next on-time begins after current is decreased to valley-current threshold. On-time is decided by (V OUT− V IN) / V OUT ratio. The output voltage decreases when further loading current increases. The current limit function is implemented by the scheme, refer to Figure 2.OCP (I LIM(5A)) Shutdown ProtectionThe RT4823 implements OCP shutdown protection. When the converter operates in boost mode, peak current limit and valley current limit function cannot protect the IC from short circuit or the huge loading. The RT4823 implements truth disconnection function. When peak current is > 5A (Typ.), the boost converter will turn off high-side MOSFET (UG) and low-side MOSFET (LG).I IN (DC) Inductor CurrentV DINI =L L fD⨯Figure 2. Inductor Currents in Current Limit OperationThermal ConsiderationsThe junction temperature should never exceed the absolute maximum junction temperature T J(MAX), listed under Absolute Maximum Ratings, to avoid permanent damage to the device. The maximum allowable power dissipation depends on the thermal resistance of the IC package, the PCB layout, the rate of surrounding airflow, and the difference between the junction and ambient temperatures. The maximum power dissipation can be calculated using the following formula :P D(MAX) = (T J(MAX) - T A) / θJAwhere TJ(MAX) is the maximum junction temperature, TA is the ambient temperature, and θJA is the junction-to-ambient thermal resistance.For continuous operation, the maximum operating junction temperature indicated under Recommended Operating Conditions is 125°C. The junction-to- ambient thermal resistance, θJA, is highly package dependent. For a WL-CSP-9B 1.3x1.2 (BSC) package, the thermal resistance, θJA, is 64.9°C/W on a standard JEDEC 51-7 high effective-thermal-conductivity four-layer test board. The maximum power dissipation at T A = 25°C can be calculated as below :P D(MAX) = (125°C - 25°C) / (64.9°C/W) = 1.54W for a WL-CSP-9B 1.3x1.2 (BSC) package.The maximum power dissipation depends on the operating ambient temperature for the fixed TJ(MAX) and the thermal resistance, θJA. The derating curves in Figure 3 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.Figure 3. Derating Curve of Maximum PowerDissipationLayout ConsiderationsThe PCB layout is an important step to maintain the high performance of the RT4823.Both the high current and the fast switching nodes demand full attention in the PCB layout to save the robustness of the RT4823. Improper layout might show the symptoms of poor line or load regulation, ground and output voltage shifts, stability issues, unsatisfying EMI behavior or worsened efficiency. For the best performance of the RT4823, the following PCB layout guidelines must be strictly followed.④Place the input and output capacitors as close aspossible to the input and output pins respectively for good filtering.④For thermal consideration, it is needed to maximizethe pure area for power stage area besides the SW.0.00.40.81.21.62.00255075100125Ambient Temperature (°C)MaximumPowerDissipation(W)input voltage ringing because of long wires.Layer 1Layer 4Figure 4. PCB Layout GuideOutline Dimension9B WL-CSP 1.3x1.2 Package (BSC)Footprint InformationRichtek Technology Corporation14F, No. 8, Tai Yuen 1st Street, Chupei CityHsinchu, Taiwan, R.O.C.Tel: (8863)5526789Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.。

74LVC1G157-Q100 单路2输入复用器商品说明书

74LVC1G157-Q100Single 2-input multiplexerRev. 2 — 8 December 2016Product data sheet1.General descriptionThe 74LVC1G157-Q100 is a single 2-input multiplexer which select data from two datainputs (I0 and I1) under control of a common data select input (S). The state of thecommon data select input determines the particular register from which the data comes.The output (Y) presents the selected data in the true (non-inverted) form.Inputs can be driven from either 3.3V or5V devices. This feature allows the use of thesedevices as translators in mixed 3.3V and5V applications.This device is fully specified for partial power-down applications using I OFF.The I OFF circuitry disables the output, preventing the damaging backflow current throughthe device when it is powered down.Schmitt-trigger action at all inputs makes the circuit highly tolerant to slower input rise andfall times.This product has been qualified to the Automotive Electronics Council (AEC) standardQ100 (Grade 1) and is suitable for use in automotive applications.2.Features and benefits⏹Automotive product qualification in accordance with AEC-Q100 (Grade 1)◆Specified from -40︒C to +85︒C and from -40︒C to +125︒C⏹Wide supply voltage range from 1.65 V to5.5V⏹High noise immunity⏹Complies with JEDEC standard:◆JESD8-7 (1.65 V to1.95V)◆JESD8-5 (2.3 V to2.7V)◆JESD8B/JESD36 (2.7 V to3.6V)⏹±24mA output drive (V CC=3.0V)⏹CMOS low power consumption⏹Latch-up performance exceeds 250mA⏹Direct interface with TTL levels⏹Inputs accept voltages up to 5V⏹ESD protection:◆MIL-STD-883, method 3015 exceeds 2000 V◆HBM JESD22-A114F exceeds 2000V◆MM JESD22-A115-A exceeds 200V (C = 200 pF, R = 0 Ω)⏹Multiple package options3. Ordering informationTable 1.Ordering informationType number PackageTemperature range Name Description Version 74LVC1G157GW-Q100-40︒C to+125︒C SC-88plastic surface-mounted package; 6 leads SOT363 74LVC1G157GV-Q100-40 ︒C to +125 ︒C SC-74plastic surface-mounted package (TSOP6); 6 leads SOT4574. MarkingTable 2.MarkingType number Marking code[1]74LVC1G157GW-Q100YP74LVC1G157GV-Q100YP[1]The pin 1 indicator is located on the lower left corner of the device, below the marking code.5. Functional diagram6. Pinning information6.1Pinning6.2Pin descriptionTable 3.Pin descriptionSymbol Pin DescriptionI11data input from source 1 GND2ground (0V)I03data input from source 0 Y4multiplexer outputV CC5supply voltageS6common data select input7. Functional descriptionTable 4.Function table[1]Inputs OutputS I1I0YL X L LL X H HH L X LH H X H[1]H=HIGH voltage level;L=LOW voltage level;X=don’t care.8. Limiting valuesTable 5.Limiting valuesIn accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V). Symbol Parameter Conditions Min Max UnitV CC supply voltage-0.5+6.5VI IK input clamping current V I < 0 V-50-mAV I input voltage[1]-0.5+6.5VI OK output clamping current V O > V CC or V O < 0 V-±50mAV O output voltage Active mode[1][2]-0.5V CC + 0.5VPower-down mode[1][2]-0.5+6.5VI O output current V O = 0 V to V CC-±50mAI CC supply current-100mAI GND ground current-100-mAP tot total power dissipation T amb=-40︒C to+125︒C[3]-250mWT stg storage temperature-65+150︒C[1]The input and output voltage ratings may be exceeded if the input and output current ratings are observed.[2]When V CC=0V (Power-down mode), the output voltage can be 5.5V in normal operation.[3]For SC-88 and SC-74 packages: above 87.5︒C the value of P tot derates linearly with 4.0mW/K.9. Recommended operating conditions10. Static characteristicsTable 6.Recommended operating conditions Symbol Parameter ConditionsMin Typ Max Unit V CC supply voltage 1.65- 5.5V V I input voltage 0- 5.5V V O output voltage Active mode--V CC V V CC = 0 V; Power-down mode -- 5.5V T amb ambient temperature-40-+125︒C ∆t/∆Vinput transition rise and fall rate V CC = 1.65 V to 2.7 V--20ns/V V CC = 2.7 V to 5.5 V --10ns/VTable 7.Static characteristicsAt recommended operating conditions. Voltages are referenced to GND (ground =0V).Symbol Parameter Conditions-40 ︒C to +85 ︒C -40 ︒C to +125 ︒C UnitMin Typ [1]Max Min Max V IHHIGH-level input voltageV CC = 1.65 V to 1.95 V 0.65V CC--0.65V CC-V V CC = 2.3 V to 2.7 V 1.7-- 1.7-V V CC = 2.7 V to 3.6 V 2.0-- 2.0-V V CC = 4.5 V to 5.5 V0.7V CC--0.7V CC-V V ILLOW-level input voltageV CC = 1.65 V to 1.95 V --0.35V CC-0.35V CC VV CC = 2.3 V to 2.7 V --0.7-0.7V V CC = 2.7 V to 3.6 V --0.8-0.8V V CC = 4.5 V to 5.5 V--0.3V CC-0.3V CCV V OHHIGH-level output voltage V I =V IH or V IL I O =-100 μA;V CC =1.65V to 5.5VV CC -0.1--V CC -0.1-V I O =-4mA; V CC = 1.65V 1.2 1.54-0.95-V I O =-8mA; V CC = 2.3V 1.9 2.15- 1.7-V I O =-12mA; V CC = 2.7 V 2.2 2.50- 1.9-V I O =-24mA; V CC = 3.0 V 2.3 2.62- 2.0-V I O =-32mA; V CC = 4.5 V3.84.11- 3.4-V V OLLOW-level output voltage V I =V IH or V IL I O =100μA;V CC =1.65V to 5.5 V--0.10-0.10V I O =4mA;V CC = 1.65V -0.070.45-0.70V I O =8mA;V CC = 2.3V -0.120.30-0.45V I O =12mA;V CC = 2.7 V -0.170.40-0.60V I O =24mA;V CC = 3.0 V -0.330.55-0.80V I O =32mA;V CC = 4.5 V-0.390.55-0.80V[1]All typical values are measured at T amb =25︒C.11. Dynamic characteristics[1]Typical values are measured at T amb =25︒C and V CC = 1.8 V, 2.5 V, 2.7 V, 3.3 V and 5.0 V respectively.[2]t pd is the same as t PLH and t PHL .[3]C PD is used to determine the dynamic power dissipation (P D in μW).P D =C PD ⨯V CC 2⨯f i ⨯N +∑(C L ⨯V CC 2⨯f o )where:f i =input frequency in MHz;f o =output frequency in MHz;C L =output load capacitance in pF;V CC =supply voltage in Volts;N =number of inputs switching;∑(C L ⨯V CC 2⨯f o )=sum of the outputs.I I input leakage currentV I = 5.5 V or GND; V CC =0V to 5.5V-±0.1±1-±1μA I OFF power-off leakage current V CC = 0 V; V I or V O =5.5V -±0.1±2-±2μA I CC supply current V I = 5.5 V or GND; I O = 0 A; V CC =1.65V to 5.5 V -0.14-4μA ∆I CC additional supply currentper pin; V CC = 2.3 V to 5.5 V; V I =V CC -0.6V; I O =0 A -5500-500μA C Iinput capacitanceV CC =3.3V;V I = GND to V CC-2.5---pFTable 7.Static characteristics …continuedAt recommended operating conditions. Voltages are referenced to GND (ground =0V).Symbol Parameter Conditions -40 ︒C to +85 ︒C -40 ︒C to +125 ︒C Unit MinTyp [1]Max Min Max Table 8.Dynamic characteristicsVoltages are referenced to GND (ground =0V); for load circuit see Figure 7.Symbol Parameter Conditions-40 ︒C to +85 ︒C -40 ︒C to +125 ︒C UnitMinTyp [1]Max Min Max t pdpropagation delay I0, I1 to Y; see Figure 6[2]V CC = 1.65 V to 1.95 V 1.5 4.311.0 1.513.0ns V CC = 2.3 V to 2.7 V 1.0 2.9 6.1 1.07.6ns V CC = 2.7 V 1.0 3.1 5.6 1.07.0ns V CC = 3.0 V to 3.6 V 1.0 2.7 5.0 1.0 6.3ns V CC = 4.5 V to 5.5 V 0.52.2 4.00.5 5.0ns S to Y; see Figure 6[2]V CC = 1.65 V to 1.95 V 1.5 4.311.0 1.513.0ns V CC = 2.3 V to 2.7 V 1.0 2.9 6.9 1.08.6ns V CC = 2.7 V 1.0 3.3 5.9 1.07.4ns V CC = 3.0 V to 3.6 V 1.0 2.9 5.0 1.0 6.3ns V CC = 4.5 V to 5.5 V0.52.3 4.00.5 5.0ns C PDpower dissipation capacitanceV I = GND to V CC ; V CC =3.3 V [3]-18---pF12. WaveformsTable 9.Measurement pointsSupply voltage Input Output V CC V M V M1.65V to 1.95V0.5V CC0.5V CC2.3V to 2.7V0.5V CC0.5V CC2.7V 1.5V 1.5V3.0V to 3.6V 1.5V 1.5V4.5V to5.5V0.5V CC0.5V CCTable 10.Test dataSupply voltage Input Load V EXTV CC V I t r=t f C L R L t PLH, t PHL1.65V to 1.95V V CC≤2.0ns30pF1kΩopen2.3V to 2.7V V CC≤2.0ns30pF500Ωopen2.7V 2.7V≤2.5ns50pF500Ωopen3.0V to 3.6V 2.7V≤2.5ns50pF500Ωopen4.5V to5.5V V CC≤2.5ns50pF500Ωopen13. Package outline3ODVWLF VXUIDFH PRXQWHG SDFNDJH OHDGV627Fig 8.Package outline SOT363 (SC-88)3ODVWLF VXUIDFH PRXQWHG SDFNDJH 7623 OHDGV627Fig 9.Package outline SOT457 (SC-74)14. AbbreviationsTable 11.AbbreviationsAcronym DescriptionCMOS Complementary Metal Oxide SemiconductorDUT Device Under TestESD ElectroStatic DischargeHBM Human Body ModelMM Machine ModelMIL MilitaryTTL Transistor-Transistor Logic15. Revision historyTable 12.Revision historyDocument ID Release date Data sheet status Change notice Supersedes74LVC1G157_Q100 v.220161208Product data sheet-74LVC1G157_Q100 v.1 Modifications:•Table7: The maximum limits for leakage current and supply current have changed.74LVC1G157_Q100 v.120130121Product data sheet--16. Legal information16.1 Data sheet status[1]Please consult the most recently issued document before initiating or completing a design.[2]The term ‘short data sheet’ is explained in section “Definitions”.[3]The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product statusinformation is available on the Internet at URL .16.2 DefinitionsDraft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. Nexperia does not give anyrepresentations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local Nexperia salesoffice. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.Product specification — The information and data provided in a Product data sheet shall define the specification of the product as agreed between Nexperia and its customer, unless Nexperia andcustomer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the Nexperia product isdeemed to offer functions and qualities beyond those described in the Product data sheet.16.3 DisclaimersLimited warranty and liability — Information in this document is believed to be accurate and reliable. However, Nexperia does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. Nexperia takes noresponsibility for the content in this document if provided by an information source outside of Nexperia.In no event shall Nexperia be liable for any indirect, incidental,punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.Notwithstanding any damages that customer might incur for any reason whatsoever, Nexperia’s aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of Nexperia.Right to make changes — Nexperia reserves the right to makechanges to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.Suitability for use in automotive applications — This Nexperiaproduct has been qualified for use in automotiveapplications. Unless otherwise agreed in writing, the product is not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of a Nexperia product can reasonably be expectedto result in personal injury, death or severe property or environmental damage. Nexperia and its suppliers accept no liability forinclusion and/or use of Nexperia products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.Applications — Applications that are described herein for any of these products are for illustrative purposes only. Nexperia makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.Customers are responsible for the design and operation of their applications and products using Nexperia products, and Nexperiaaccepts no liability for any assistance with applications or customer product design. It is customer’s sole responsibility to determine whether the Nexperia product is suitable and fit for the customer’s applications andproducts planned, as well as for the planned application and use of customer’s third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.Nexperia does not accept any liability related to any default,damage, costs or problem which is based on any weakness or default in the customer’s applications or products, or the application or use by customer’s third party customer(s). Customer is responsible for doing all necessary testing for the customer’s applications and products using Nexperia products in order to avoid a default of the applications andthe products or of the application or use by customer’s third partycustomer(s). Nexperia does not accept any liability in this respect.Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.Terms and conditions of commercial sale — Nexperiaproducts are sold subject to the general terms and conditions of commercial sale, as published at /profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. Nexperia hereby expressly objects toapplying the customer’s general terms and conditions with regard to the purchase of Nexperia products by customer.Document status[1][2]Product status[3]DefinitionObjective [short] data sheet Development This document contains data from the objective specification for product development. Preliminary [short] data sheet Qualification This document contains data from the preliminary specification.Product [short] data sheet Production This document contains the product specification.No offer to sell or license — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.Export control — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.Translations — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.16.4 TrademarksNotice: All referenced brands, product names, service names and trademarks are the property of their respective owners.17. Contact informationFor more information, please visit: For sales office addresses, please send an email to: ***************************18. Contents1 General description. . . . . . . . . . . . . . . . . . . . . . 12 Features and benefits . . . . . . . . . . . . . . . . . . . . 13 Ordering information. . . . . . . . . . . . . . . . . . . . . 24 Marking. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 Functional diagram . . . . . . . . . . . . . . . . . . . . . . 26 Pinning information. . . . . . . . . . . . . . . . . . . . . . 36.1 Pinning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36.2 Pin description . . . . . . . . . . . . . . . . . . . . . . . . . 37 Functional description . . . . . . . . . . . . . . . . . . . 48 Limiting values. . . . . . . . . . . . . . . . . . . . . . . . . . 49 Recommended operating conditions. . . . . . . . 510 Static characteristics. . . . . . . . . . . . . . . . . . . . . 511 Dynamic characteristics . . . . . . . . . . . . . . . . . . 612 Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 713 Package outline . . . . . . . . . . . . . . . . . . . . . . . . . 914 Abbreviations. . . . . . . . . . . . . . . . . . . . . . . . . . 1115 Revision history. . . . . . . . . . . . . . . . . . . . . . . . 1116 Legal information. . . . . . . . . . . . . . . . . . . . . . . 1216.1 Data sheet status . . . . . . . . . . . . . . . . . . . . . . 1216.2 Definitions. . . . . . . . . . . . . . . . . . . . . . . . . . . . 1216.3 Disclaimers. . . . . . . . . . . . . . . . . . . . . . . . . . . 1216.4 Trademarks. . . . . . . . . . . . . . . . . . . . . . . . . . . 1317 Contact information. . . . . . . . . . . . . . . . . . . . . 1318 Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14© Nexperia B.V. 2017. All rights reserved For more information, please visit: Forsalesofficeaddresses,pleasesendanemailto:*************************** Date of release:Mouser ElectronicsAuthorized DistributorClick to View Pricing, Inventory, Delivery & Lifecycle Information:N experia:74LVC1G157GV-Q100H74LVC1G157GW-Q100H。

芯片测试与产量分析解决方案:Synopsys Yield Explorer说明书

DATASHEET Overview Nanometer node yield issues are dominated by design-process-test interactions, mandating cross-domain analyses to mitigate these issues rapidly. Yield Explorer brings yield relevant data from diverse sources such as the physical design flow, wafer manufacturing, and wafer and chip level testing into a single data bank. With the widest possible range of data at their disposal, users achieve unsurpassed clarity in root cause analysis when faced with systematic yield limiters. Yield Explorer achieves this with an order of magnitude advantage in analysis speed in the most complex of use cases—for example, 10X faster volume diagnostics analysis of ATPG output.This significant analysis capability and speed advantage sets Yield Explorer in a class apart from previous yield management systems and enables, for the first time, true connectivity to EDA tools.Yield Explorer Fully Addresses the Needs of Product and Test Engineering Teams • Rapidly diagnose yield and performance issues with available fab, test and design data • Accept any new types of data for ease in characterization and debug efforts • Maximize learning from first silicon debug and minimize design re-spins • Enable wide standardization of analysis methods through scripting and automation • Manage the product across multiple wafer sources and test housesDesign-Centric Yield ManagementYield ExplorerDesign At the Core of All ActivitiesA built-in layout viewer makes it easy to correlate any yield relevant information to physical design, e.g. failing cells to DRC flags or lithographic marginalities (Figure 1).Figure 1: The versatile Yield Explorer client simultaneously manages a variety of yield data Customization and end-User ControlAnalysis routines are easily automated, and the application can be rapidly extended using built-in industry-standard scripting. Rapid and Secure Data AccessMobile and geographically distributed workforces can easily and actively participate in data-driven decision making.Yield Explorer Benefits• Improved turnaround time to find design, test and production problems (from weeks to hours)• Quality of results (high accuracy of failure analysis candidate identification)• Easy customization of recipes for each customers’ unique requirements (editable in Tcl scripting environment)• Open architecture and flexible interface (enables connectivity to existing customer databases)Key Technical Features• A full complement of statistical and data analysis tools along with wafer and test visualization capabilities• Complex correlations across site-parametric, design, physical verification, simulation, product test and custom data sources • Synchronized Component Architecture integrates all incoming data into a single, coherent analysis application• Interactive use-case flow between the chart and spreadsheet windows to wafer maps to failing net overlays onto design • Dynamically extendable data model to accept any number of custom data fields into the Yield Explorer database• Platform neutral Analysis Client (Windows, Linux, UNIX) to allow all users to use the same application regardless of desktop computing environmentTypical Yield Explorer Use CaseOne of the key decisions in solving yield issues on early silicon lots is to separate the random yield loss from systematic yield loss. Most often, random yield loss is controlled by fab defectivity and is handed over to the fab to rectify.Systematic issues, however, need careful analysis by product and test engineers to understand the root cause of the failures leading to yield loss. Modern structural testing techniques like DFT diagnostics identify possible candidate cell occurrences in a given design that may have contributed to a given die failure.Once the XY locations of failing cells and nets are overlaid on top of the physical layout an entire new set of possibilities is opened for analysis. For example, the identified cells are logical entities which are manifested in several layers of GDS file as physical entities. FEOL DRC flags within the XY coordinates of failing cell boundary provide one explanation for the observed failure, whereas BEOL DRC flags provide connections to failing nets.Design fixProgram fixFaster FAProcess fixFigure 2: Yield Explorer collects data from fab, test and EDA domains to enable faster discovery of yield root-cause sourcesLow yieldlot Cell failby testFailing cellmapSpatialtrendsFailing nets Physical FA50% accurateFigure 3A: Traditional diagnostics methods typically require 2-3 weeks to reach root cause—and with only about 50% accuracy©2018 Synopsys, Inc. All rights reserved. Synopsys is a trademark of Synopsys, Inc. in the United States and other countries. A list of Synopsys trademarks isavailable at /copyright .html . All other names mentioned herein are trademarks or registered trademarks of their respective owners.Low yield lot Physical FA 90% accurateFigure 3B: With Yield Explorer, actual time to results, with 90% accuracy, was reduced to 2-3 daysAdditional information about hotspots, as simulated and flagged through LRC or stress models, provides alternate explanations for cell failure.By allowing the customer to do this in a single seamless system (Figure 2), Yield Explorer offers a tremendous time savings (Figure 3) over the manual movement of volumes of data between logical, electrical and physical domains.Efficient and Effective Analysis• Yield Explorer Assistants help users create more efficient analysis flows:• Chart/Data Analysis Assistant• Spreadsheet Assistant• Data Selection Assistant• DRC Assistant• Rapid data extraction over Wide• Area Networks• Client Scripting using Tcl/Tk• User actions recorded as analysis flows in Tcl script formatAdditional Capabilities• Application Developer’s Kit (option)• Provides access to Yield Explorer data to drive external applications• Job Scheduler (option)• Users can schedule specific jobs to run on a periodic basis in an automated mannerFor more information about Synopsys products, support services or training, visit us on the web at: , contact your local sales representative or call 650.584.5000.。

synopsys iC Compiler II 数据手册说明书

DATASHEETOverview IC Compiler™ II is the industry leading place and route solution that delivers best-in-class quality-of-results (QoR) for next-generation designs across all market verticals and process technologies while enabling unprecedented productivity. IC Compiler II includes innovative for flat and hierarchical design planning, early design exploration, congestion aware placement and optimization, clock tree synthesis, advanced node routing convergence, manufacturing compliance, and signoff closure.IC Compiler II is specifically architected to address aggressive performance, power, area (PPA), and time-to-market pressures of leading-edge designs. Key technologies include a pervasively parallel optimization framework, multi-objective global placement, routing driven placement optimization, full flow Arc based concurrent clock and data optimization, total power optimization, multi-pattern and FinFET aware flow and machine learning (ML) driven optimization for fast and predictive design closure. Advanced Fusion technologies offer signoff IR drop driven optimization, PrimeTime ® delay calculation within IC Compiler II, exhaustive path-based analysis (PBA) and signoff ECO within place and route for unmatched QoR and design convergence. F U S I O N D E S I G N P L A T F O R M PrimeTime, StarRC, PrimePower,IC Validator, RedHawk Analysis Fusion Fusion Compiler IC Compiler II Design Compiler NXT TestMAX F o r m a l i t y ECO Fusion S i g n o f f F u s i o n S i g n o f f F u s i o n Test Fusion Figure 1: IC Compiler II Anchor in Synopsys Design PlatformAccelerating DesignClosure on AdvancedDesignsIC Compiler II Industry Leading Place and Route SystemKey BenefitsProductivity• The highest capacity solution that supports 500M+ instances with a scalable and compact data model• A full suite of design planning features including transparent hierarchical optimization• Out-of-the-box simple reference methodology for easy setup• Multi-threaded and distributed computing for all major flow steps• Golden signoff accuracy with direct access to PrimeTime delay calculationPPA• Unified TNS driven optimization framework• Congestion, timing, and power-driven logic re-synthesis• IEEE 1801 UPF/multi-voltage support• Arc-based concurrent clock and data optimization• Global minima driven total power optimizationAdvanced Nodes• Multi-pattern and FinFET aware design flow• Next generation advanced 2D placement and legalization• Routing layer driven optimization, auto NDR, and via pillar optimization• Machine learning driven congestion prediction and DRC closure• Highest level of foundry support and certification for advanced process nodes• IC Validator in the loop signoff driven DRC validation and fixingAdvanced Fusion Technology• Physically aware logic re-synthesis• IR drop driven optimization during all major flow steps• PrimeTime delay calculation based routing optimization for golden accuracy• Integrated PrimeTime ECO flow during routing optimization for fastest turnaround timeEmpowering Design Across Diversified ApplicationsThe dizzying pace of innovation and highly diversified applications across the design spectrum is forcing a complete rethink of the place and route systems to design and implement differentiated designs in a highly competitive semiconductor market on schedule. Designers on emerging process nodes must meet aggressive PPA and productivity goals. It essentially means efficient and intelligent handling of 100s of millions of place-able instances, multiple levels of hierarchy, 1000s of hard macros, 100s of clocks, wide busses, and 10s of modes and corners power domains and complex design constraints and process technology mandates. Emphasis on Designer ProductivityIC Compiler II is architected from the ground up for speed and scalability. Its hierarchical data model consumes 2-3X less memory than conventional tools, boosting the limits of capacity to 500M placeable instances and beyond. Adaptive abstraction and on-the-fly data management minimize memory requirements and enable fast responsive data manipulation. Near-linear multi-core threading of key infrastructural components and core algorithms such as database access and timing analysis speed up optimization at all phases of design. Patented, lossless compact modeling and independent R and C extraction allow handling more modes and corners (MCMM scenarios) with minimal runtime impact.IC Compiler II has built-in Reference Methodology(RM) that ensures fast flow bring up. This RM Flow is Foundry Process/Design Type specific to ensure a robust starting point and seamless bring up. IC Compiler II has direct access to the Golden PrimeTime delay calculation engine to minimize ECO iterations.IC Compiler II’s new data model enables designers to perform fast exploration and floorplanning with complex layout requirements. IC Compiler II can create bus structures, handle designs with n-levels of physical hierarchy, and support Multiply Instantiated Blocks (MIBs) in addition to global route driven pin assignment/feedthrough flow, timing driven macro placement, MV area design planning.A design data mismatch inferencing engine analyzes the quality of inputs and drives construct creation on the fly, delivering design insights even with “incomplete” data early in the design cycle. Concurrent traversal of logical and physical data models enables hierarchical Data-Flow Analysis (DFA) and fast interactive analysis through multi-level design hierarchies and MIBs. Data flow and feedthrough paths highlighted in Figure 2 allow analysis and manipulation through n-levels of hierarchy to complete early design exploration and prototyping.Figure 2: Fast interactive analysis through multiple-levels of physical hierarchy and MIBPipeline-register-planning shown in Figure 3, provides guidance for optimal placement to meet the stringent timing requirementsof high-performance designs. Interactive route editor integrated which is advanced node aware shown in Figure 4, allows intricate editing and routing functions, including the creation of special signal routes, buses, etc.Figure 3: Pipeline register placement enables superior QoR for designs with complex busesAchieving Best Performance, Power, Area, and TATIC Compiler II features a new optimization framework built on global analytics. This Unified TNS Driven Optimization framework is shared with Design Compiler NXT synthesis to enable physically-aware synthesis, layer assignment, and route-based optimization for improved PPA and TAT. Multi-Corner Multi-Mode (MCMM) and Multi-Voltage (MV) aware, level-based analytical algorithms continuously optimize using parallel heuristic algorithms. Multi-factor costing functions deliver faster results on both broad and targeted design goals. Concurrent PPA driven logic remapping, rewiring, and legalization interleaved with placement minimizes congested logic, resulting in simple localized logic cones that maximize routability and QoR.IC Compiler II minimizes leakage with fast and efficient cell-by-cell power selection across HVT, SVT and LVT cells and varying channel lengths. Activity-driven power optimization uses VCD/ SAIF, net toggle rates, or probability functions to drive placement decisions and minimize pin capacitances. Multi-bit register banking optimizes clock tree structures, reduces area, and net length, while automatically managing clock, data, and scan chain connections.Advanced modeling of congestion across all layers highlighted in Figure 4 provides accurate feedback throughput the flow from design planning to post- route optimization.Figure 4: Intelligent and accurate analysis for congestion and powerIC Compiler II introduces a new Concurrent Clock and Data (CCD) analysis and optimization engine that is built-in to every flow step resulting in meeting both aggressive performance and minimizing total power footprint. ARC-based CCD optimization performs clock tree traversal across all modes/corners in path-based fashion to ensure optimal delay budgeting.Robust support for clock distribution enables virtually any clock style, including mesh, multi-source, or H-tree topologies. Advanced analysis and debugging features perform accurate clock QoR analysis and debugging as highlighted in Figure 5.Figure 5: Accurate clock QoR analysis and debugging (a & b) Abstracted clock graph and schematic.(c) Latency clock graph. (d) Colored clock tree in layout.IC Compiler II features many innovative technologies that make it the ideal choice for high-performance, energy-efficient Arm®processor core implementation, resulting in industry-best milliwatts/megahertz (mW/MHz) for mobile and other applications across the board. Synopsys and Arm work closely together to offer optimized implementation of popular Arm cores for IC Compiler II,with reference flows available for Arm Cortex®-A high-performance processors and Mali GPUs. In addition, Arm offers off-the-shelf Artisan® standard cell and memory models that have been optimally tuned and tested for fast deployment in an IC Compiler II environment. Continuous technology innovation and close collaboration makes IC Compiler II the leading choice for Arm-based high- performance design.Highest Level of Advanced Node Certification and SupportIC Compiler II provides advanced node design enablement across major foundries and technology nodes—including 16/14nm,12/10nm, 7/5nm, and sub-5nm geometries. Zroute digital router technology ensures early and full compliance with the latest design rules required for these advanced node technologies. Synopsys collaborates closely with all the leading foundries to ensure that IC Compiler II is the first to deliver support for early prototype design rules and support for the final production design rules. IC Compiler II design technologies maximize the benefits of new process technologies and offer optimal return on investment for cutting-edge silicon applications.IC Compiler II advanced node design support includes multi-pattern/FinFET aware placement and routing, Next-generation advanced 2D placement and legalization, routing layer driven optimization, auto NDR, and via pillar optimization. IC Validator in the loop provides signoff DRC feedback during Implementation.Foundry fill Track based fillFigure 6: IC Validator In-Design metal fill color aware metal fill, optimized for density and foundry requirementsMachine learning driven congestion prediction and DRC closure allow for fastest routing convergence with best PPA. Multiple sets of training data are used to extract key predictive elements that guide the pre-route flow.Advanced Fusion TechnologyThe Fusion Design Platform™ delivers unprecedented full-flow QoR and time-to-results (TTR) to accelerate the next wave of semiconductor industry innovation. The industry’s first AI-enhanced, cloud-ready Design Platform with Fusion Technology™ isbuilt from Synopsys’ market-leading, massively-parallel digital design tools, and augmented with innovative capabilities to tacklethe escalating challenges in cloud computing, automotive, mobile, and IoT market segments and accelerate the next wave of industry innovation.Fusion Technology redefines conventional EDA tool boundaries across synthesis, place-and-route, and signoff, sharing integrated engines across the industry’s premier digital design products. It enables designers to accelerate the delivery of their next-generation designs with the industry-best QoR and the TTR.©2019 Synopsys, Inc. All rights reserved. Synopsys is a trademark of Synopsys, Inc. in the United States and other countries. A list of Synopsys trademarks isavailable at /copyright.html . All other names mentioned herein are trademarks or registered trademarks of their respective owners.。

智能融合cSoC:多通道FFT共享处理器使用FPGA纤维说明书

Application Note AC381February 20121© 2012 Microsemi Corporation SmartFusion cSoC: Multi-Channel FFT Co-Processor Using FPGA FabricTable of ContentsIntroductionThe SmartFusion ® customizable system-on-chip (cSoC) device integrates FPGA technology with a hardened ARM ® Cortex™-M3 processor based microcontroller subsystem (MSS) and programmable high-performance analog blocks built on a low power flash semiconductor process. The MSS consists of hardened blocks such as a 100 MHz ARM Cortex-M3 processor, peripheral direct memory access (PDMA), embedded nonvolatile memory (eNVM), embedded SRAM (eSRAM), embedded FlashROM (eFROM), external memory controller (EMC), Watchdog Timer, the Philips Inter-Integrated Circuit (I 2C),serial peripheral interface (SPI), 10/100 Ethernet controller, real-time counter (RTC), GPIO block, fabric interface controller (FIC), in-application programming (IAP), and analog compute engine (ACE).The SmartFusion cSoC device is a good fit for applications that require interface with many analog sensors and analog channels. SmartFusion cSoC devices have a versatile analog front-end (AFE) that complements the ARM Cortex-M3 processor based MSS and general-purpose FPGA fabric. The SmartFusion AFE includes three 12-bit successive approximation register (SAR) ADCs, one first order sigma-delta DAC (SDD) per ADC, high performance signal conditioning blocks, and comparators. The SmartFusion cSoCs have a sophisticated controller for the AFE called the ACE. The ACE configures and sequences all the analog functions using the sample sequencing engine (SSE) and post-processes the results using the post processing engine (PPE) and handles without intervention of Cortex-M3 processor.Refer to the SmartFusion Programmable Analog User’s Guide for more details.This application note describes the capability of SmartFusion cSoC devices to compute the Fast Fourier Transform (FFT) in real time. The Multi Channel FFT example design can be used in medical applications, sensor network applications, multi channel audio Spectrum analyzers, Smart Metering, and sensing applications (such as vibration analysis).This example design uses the Cortex-M3 processor in the SmartFusion MSS as a master and the FFT processor in the FPGA fabric as a slave. All three of the SmartFusion cSoC A2F500’s ADCs are used for data acquisition. The example design uses Microsemi’s CoreFFT IP and the advanced peripheral bus interface (CoreAPB3). A custom-made APB3 interface has been developed to connect CoreFFT with the MSS via CoreAPB3. The Cortex-M3 processor uses the PDMA controller in the MSS for the data transfer and thus helps to free up the Cortex-M3 processor instruction bandwidth.A basic understanding of the SmartFusion design flow is assumed. Refer to Using UART with SmartFusion - Microsemi Libero ® SoC and SoftConsole Flow Tutorial to understand the SmartFusion design flow.Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1Design Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2Design Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2Implementing Multi Channel FFT on EVAL KIT BOARD . . . . . . . . . . . . . . . . . . . . . . . . . 7Running the Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8Conclusion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9Appendix A – Design Files . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10SmartFusion cSoC: Multi-Channel FFT Co-Processor Using FPGA Fabric2Design OverviewThis design example demonstrates the capability of the SmartFusion cSoC device to compute the FFT for multiple data channels. The FFT computation is a complex task that utilizes extensive logic resources and computation time. In general, for N number of channels, N number of FFT IP’s are needed to be instantiated, which in turn utilize more logic resources on the FPGA. A way to avoid this limitation is to use the same FFT logic for multiple input channels.This design illustrates the implementation of a Multichannel FFT to process multiple data channels through a single FFT and store FFT points in a buffer. The FFT computes the input data read from each channel and stores the N-point result in the respective channel’s allocated buffer. The channel multiplexing is done once each channel buffer has been loaded with the FFT length.Computing frequency components for a real time data of six channels is described in this application note. For sampling the input signals the AFE is used and the complex FFT computation is implemented in the fabric of the SmartFusion cSoC device. The Cortex-M3 processor in the MSS of the SmartFusion cSoC handles the buffer management and channel muxing.Figure 1 depicts the block diagram of six channel FFT co-processor in FPGA fabric.Design DescriptionThe design uses CoreFFT for computing the FFT results. You can download the core generator for CoreFFT at /soc/portal/default.aspx?r=4&p=m=624,ev=60.The design example uses a 512-point and 16-bit FFT. A custom-made APB3 interface has been developed to connect CoreFFT IP with the MSS’s FIC. The CoreFFT output data is stored in a 512x32FIFO within the fabric. The FIFO status signals are given in Table 1 on page 3. The status signals indicate that FFT is ready to receive data and data is available in the output of FIFO. These status signals are mapped to the GPIOs in the MSS. The Cortex-M3 processor can read the GPIOs to handle flow control in the data transfer process from the MSS to CoreFFT.Figure 1 • Multi Channel FFT Block DiagramDesign Description3Figure 2 shows the block diagram of logic in the fabric with custom-made APB3 bus.The data valid signal (ifiD_valid) is generated in custom logic whenever the master needs to write data into the input buffer of the FFT to process through the APB3 interface. The FFT_IP_RDY signal indicates the status of the input buffer of the FFT. If the input buffer is full, the FFT_IP_RDY goes low. The master can read the FFT_IP_RDY signal to get the FFT input buffer status. The FFT generates the processed data with a data valid signal (ifoY_valid). The processed data is stored in the FIFO. When FIFO is not ready to receive output data, it can stop the data fetching from the FFT by pulling down the ifiRead_y signal. The status signal FFT_OP_RDY is used to indicate to the master that processed data is available in the FIFO. FFT_OP_RDY goes High whenever processed data is available in the FFT output buffer.The master can use AEMPTY_OUT or EMPTY_OUT to determine whether the FIFO is empty and all the processed data has been read. Refer to the CoreFFT Handbook for more details on architecture and interface signal descriptions.Three ADCs are configured to have two channels, each channel with 100 ksps sampling rate. The external memory is used for input and output buffers. For each channel, one input buffer having length double to the length of FFT i.e. 1024 words and one output buffer having length equal to the length of FFT i.e. 512 words are used. After each channel's input buffer has 512 points required for the full length of the FFT, each channel, one after the other, streams its points from the FIFO through the FFT. During the FFT computational period, the sampled data values of each channel are stored in the second half of the input buffer. Once the FFT computations for the First half of input buffer completes then the points in the second half of the input buffer will be streamed to FFT. This operation utilizes a ping-pong method. The Cortex-M3 processor is used for data management, that is, buffering the sampled points and data routing or muxing of these values to the FFT computation block. Sampling of the real time data is done by the ACE. The PDMA handles the data transfer between the external SRAM (eSRAM) buffers and CoreFFT logic in FPGA fabric.Figure 2 • CoreFFT with APB Slave InterfaceTable 1 • FIFO Status Signals with DescriptionsSignalDescription FFT_IP_RDYFFT is ready to receive the Input from the master processor FFT_OP_RDYProcessed data is ready in output buffer of FFT AEMPTY_OUTOutput FIFO is almost empty EMPTY_OUT Output FIFO is emptySmartFusion cSoC: Multi-Channel FFT Co-Processor Using FPGA Fabric4Figure 3 shows the implementation of multi channel FFT on the SmartFusion cSoC device.Hardware ImplementationThe MSS is configured with an FIC, clock conditioning circuit (CCC), GPIOs, EMC and a UART. The CCC generates 80 MHz clock, which acts as the clock source. The FIC is configured to use a master interface with an AMBA APB3 interface. Four GPIOs in the MSS are configured as inputs that are used to handle flow control in data transfer from MSS to FFT coprocessor. The EMC is configured for Region 0as Asynchronous RAM and port size as half word. The UART_0 is configured for printing the FFT values to the PC though a serial terminal emulation program.ADC0, ADC1, and ADC2 are configured with 12-bit resolution, two channels and the sampling rate is set to approximately 100 KHz. Figure 4 on page 5 shows the ACE configuration window.Figure 3 • Implementation of Multi Channel FFT on the SmartFusion cSoCDesign Description5The APB wrapper logic is implemented on the top of CoreFFT and connected to CoreAPB3. A FIFO of size 512*32 is used to connect to CoreFFT output.CoreAPB3 acts as a bridge between the MSS and the FFT coprocessor block. It provides an advanced microcontroller bus architecture (AMBA3) advanced peripheral bus (APB3) fabric supporting up to 16APB slaves. This design example uses one slave slot (Slot 0) to interface with the FFT coprocessor block and is configured with direct addressing mode. Refer to the CoreAPB3 Handbook for more details on CoreAPB3 IP .For more details on how to connect FPGA logic MSS, refer to the Connecting User Logic to the SmartFusion Microcontroller Subsystem application note.The logic in the FPGA fabric consumes 18 RAM blocks out of 24. We cannot use eSRAM blocks for implementing CoreFFT as the transactions between these SRAM blocks and FFT logic are very high and are time critical.Figure 5 on page 6 illustrates the multi channel FFT example design in the SmartDesign.Figure 4 • Configure ACESmartFusion cSoC: Multi-Channel FFT Co-Processor Using FPGA Fabric6Table 2 summarizes the logic resource utilization of the design on the A2F500M3F device.Software ImplementationThe Cortex-M3 processor continuously reads the values from ACE and stores the values into the input buffers. If the first 512 points are filled then the processor initiates the FFT process. In the FFT process,the input buffers are streamed one after other to the CoreFFT with the help of PDMA. Using another channel of PDMA the output of FFT is moved to the corresponding channel output buffers.During the FFT process the Cortex-M3 processor stores the sampled values into the second half of the input buffers. Once the FFT process completes the first half of input buffer, then the second half of the input buffer are streamed to CoreFFT.Figure 5 • SmartDesign Implementation of Multi Channel FFTTable 2 • Logic Utilization of the Design on A2F500M3FCoreFFTOther Logic in Fabric Total Ram Blocks14418 (75%)Tiles 78424718313 (72.1%)Implementing Multi Channel FFT on EVAL KIT BOARD7The CALL_FFT(int *) application programmable interface (API) initiates the PDMA to transfer input buffer data to the FFT in the fabric. Before initiating PDMA it checks for FFT whether or not it is ready to read the data. The CALL_FFT(int *) API also checks if the output FIFO is empty so that all the FFT out values have been already read. When the input buffer has points equal to the full length of FFT, then it will be called.The Read_FFT() API initiates the PDMA for reading the FFT output values from FIFO in fabric to the corresponding output buffer. After reading all the values it calls the CALL_FFT() API with the next channel buffer to compute the FFT for next channel. This is done for all channels. After completion of FFT computation for all channels, if the continuous variable is not defined, it will print the FFT output values on the serial terminal. When FFT_OP_READY interrupt occurs then this API will be called.The GPIO1_IRQHandler() interrupt service routine occurs on the positive edge of FFT_OP_READY signal. It calls Read_FFT() API. This interrupt mechanism is used to read the sample values continuously while computing the FFT.If continuous variable is defined, then the FFT is computed without any loss of data samples. If #define continuous line is commented then after every completion of FFT computation of all channels the FFT output is printed on serial terminal. The printed values are in the form of complex numbers.The ping-pong mechanism is used for input data buffer to store the samples continuously. For each channel the input buffer length is double of the full FFT length. While computing the FFT for the first half of the buffer, the new sample values are stored in the second half of the input buffer and while computing the FFT for second half of buffer, the new sample values are stored in first half of the input buffer.Customizing the Number of ChannelsYou can change the design depending on your requirement. Configure the ADC (Figure 4 on page 5)with the required number of channels and required sampling rate. In SoftConsole project change the parameter value NUM_CHANNELS according to the ADC configuration. Edit the main code for reading ADCs data into buffers according to ACE configuration.Throughput CalculationsThe actual time to get 512 samples with 100 ksps is 5.12 ms. Each channel is configured to 100 ksps, so for every 5.12 ms we will have 512 samples in the input buffers.The actual time taken to compute the FFT for each channel is the sum of time taken to transfer 512points to CoreFFT, FFT computation time, and time to read FFT output to the output buffer.•Total time for computing FFT = (time taken to receive 512 data + computational latency for 512points + time taken to store 512 data) = 512*5 + 23292 + 512*5 =28412 clks •Time to compute FFT for 6 channels = 28412*6 = 170472 clksTime to compute FFT for six channels is 2.1309 ms (If CLK is 80 MHz). It is less than half the sample rate of 5.12 ms.If only one channel is configured with maximum sampling rate (600 ksps) then time to get 512 samples with 600 ksps is 0.853 ms. Time to compute FFT for these 512 samples is 0.355 ms. If you configure three ADCs with maximum sampling rate (1800 ksps) then time to compute the FFT for these three channels will be 1.065 ms which is higher than the sampling time. In this there is a loss of some samples.The design works fine up to 1440 ksps.Implementing Multi Channel FFT on EVAL KIT BOARDTo implement the design on the SmartFusion Evaluation Kit Board the FFT must be 256 point and 8 bit because the A2F200 device has less RAM blocks and logic cells. The ADC channels must be selected for only ADC0 and ADC1. Figure 6 on page 8 shows the implementation of multi channel FFT on the SmartFusion cSoC (A2F200M3F) device.SmartFusion cSoC: Multi-Channel FFT Co-Processor Using FPGA Fabric8Table 3 summarizes the logic resource utilization of the design with 256 points 8-bit FFT on A2F200M3F device.Running the DesignProgram the SmartFusion Evaluation Kit Board or the SmartFusion Development Kit Board with the generated or provided *.stp file (refer to "Appendix A – Design Files" on page 10) using FlashPro and then power cycle the board.For computing continuous FFT values for the all six signals sampled through the ADCs, uncomment the line #define continuous in the main program. The FFT output values are stored in the rdata buffer. This buffer is updated for every computation of FFT.For printing the FFT values on serial terminal (HyperTerminal or PuTTy), comment the line #define continuous in the main program.Figure 6 • Implementation of Multi Channel FFT on the SmartFusion Evaluation Kit BoardTable 3 • Logic Utilization of the Design on A2F200M3F DeviceCoreFFTOther Logic in Fabric Total Ram Blocks718 (100%)Tiles 3201853286 (66%)Conclusion9Connect the analog inputs to the SmartFusion Kit Board with the information provided in Table 4.Invoke the SoftConsole IDE, by clicking on Write Application code under Develop Firmware in Libero ®System-on-Chip (SoC) project (refer to "Appendix A – Design Files") and launch the debugger. Start HyperTerminal or PuTTY with a baud rate of 57600, 8 data bits, 1 stop bit, no parity, and no flow control.If your PC does not have the HyperTerminal program, use any free serial terminal emulation program such as PuTTY or Tera Term. Refer to the Configuring Serial Terminal Emulation Programs Tutorial for configuring the HyperTerminal, Tera Term, or PuTTY .ConclusionThis application note describes the capability of the SmartFusion cSoC devices to compute the multi channel FFT. The Cortex-M3 processor, AFE, and FPGA fabric together gives a single chip solution for real time multi channel FFT system. This design example also shows the 6-channel data acquisition system.Table 4 • SettingsChannelEvaluation Kit Development Kit Channel 173 of J21 (signal header)ADC0 of JP4Channel 274 of J21 (signal header)ADC1 of JP4Channel 377 of J21 (signal header)77 of J21 (signal header)Channel 478 of J21 (signal header)78 of J21 (signal header)Channel 585 of J21 (signal header)Channel 686 of J21 (signal header)Figure 7 • FFT Output Data for 1 kHz Sinusoidal Signal on PUTTYSmartFusion cSoC: Multi-Channel FFT Co-Processor Using FPGA Fabric10Appendix A – Design FilesThe Design files are available for download on the Microsemi SoC Product Groups website:/soc/download/rsc/?f=A2F_AC381_DF.The design zip file consists of Libero SoC projects and programming file (*.stp) for A2F200 and A2F500.Refer to the Readme.txt file included in the design file for directory structure and description.51900249-0/02.12© 2012 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor solutions for: aerospace, defense and security; enterprise and communications; and industrial and alternative energy markets. Products include high-performance, high-reliability analog and RF devices, mixed signal and RF integrated circuits, customizable SoCs, FPGAs, and complete subsystems. Microsemi is headquartered in Aliso Viejo, Calif. Learn more at .Microsemi Corporate HeadquartersOne Enterprise, Aliso Viejo CA 92656 USAWithin the USA: +1 (949) 380-6100Sales: +1 (949) 380-6136Fax: +1 (949) 215-4996。

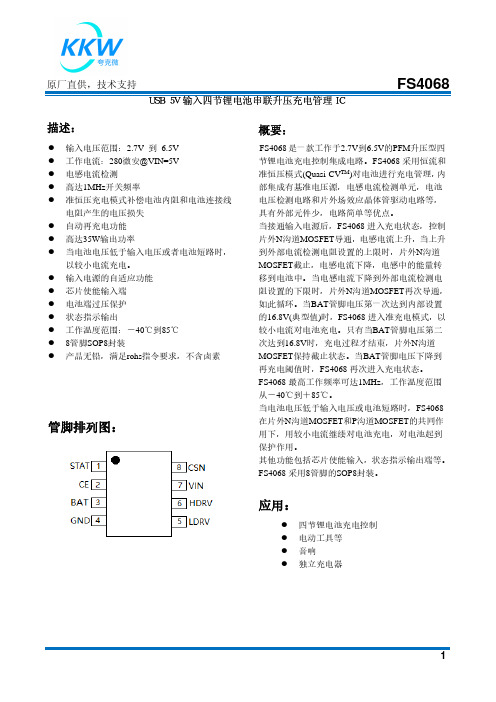

FS4068夸克微芯片规格书

FS4068是一款工作于2.7V到6.5V的PFM升压型四节锂电池充电控制集成电路。