MC1GU256NBCB-0QC00中文资料

金士顿e MMC 5.1嵌入式多媒体卡(e

Embedded Multi-Media Card(e•MMC™ 5.1)EMMC16G-IB29-PE90EMMC32G-IB29-PE90EMMC64G-IB29-PE90v1.0Product Features•Packaged managed NAND flash memory with e•MMC™ 5.1 interface•Backward compatible with all prior e•MMC™ specification revisions•153-ball JEDEC FBGA RoHS Compliant package•Operating voltage range:o VCCQ = 1.8 V/3.3 Vo VCC = 3.3 V•Operating Temperature (T case) - 40C to +85C•Storage Temperature -55C to +85C•Compliant with e•MMC™ 5.1 JEDEC Standard Number JESD84-B51•Factory configured with pseudo Single Level Cell (pSLC) mode for enhanced reliability and performance•Factory configured with reliable writee•MMC™ Specific Feature Support•High-speed e•MMC™ protocol•Variable clock frequencies of 0-200MHz•Ten-wire bus interface (clock, 1 bit command, 8 bit data bus) with an optional hardware reset •Supports three different data bus widths: 1 bit(default), 4 bits, 8 bits•Bus Modes:o Single data transfer rate: up to 52MB/s (using 8 parallel data lines at 52MHz)o Dual data rate mode (DDR-104) : up to 104MB/s @ 52MHzo High speed, single data rate mode (HS-200) : up to 200MB/s @ 200MHzo High speed, dual data rate mode (HS-400) : up to 400MB/s @ 200MHz•Supports alternate boot operation mode to provide a simple boot sequence methodo Supports SLEEP/AWAKE (CMD5)o Host initiated explicit sleep mode for power saving•Enhanced write protection with permanent and partial protection options•Multiple user data partition with enhanced attribute for increased reliability•Error free memory accesso Cyclic Redundancy Code (CRC) for reliable command and data communicationo Internal error correction code (ECC) for improved data storage integrityo Internal enhanced data management algorithmo Data protection for sudden power failure during program operations•Securityo Secure bad block erase commandso Enhanced write protection with permanent and partial protection options•Power off notification for sleep•Field firmware update (FFU)•Production state awareness•Device health report•Command queuing•Enhanced strobe•Cache flushing report•Cache barrier•Background operation control & High Priority Interrupt (HPI)•RPMB throughput improvement•Secure write protection•Pre EOL information•Optimal sizeProduct DescriptionKingston’s e•MMC™ products conform to the JEDEC e•MMC™ 5.1standard. These devices are an ideal universal storage solution for many commercial and industrial applications. In a single integrated packaged device, e•MMC™ combines triple-level cell (TLC) NAND flash memory with an onboard e•MMC™ controller, providing an industry standard interface to the host system. The integrated e•MMC™ controller directly manages NAND flash media which relieves the host processor of these tasks, including flash media error control, wear-leveling, NAND flash management and performance optimization. Future revision to the JEDEC e•MMC™ standard will always maintain backward compatibility. The industry standard interface to the host processor ensures compatibility across future NAND flash generations as well, easing product sustainment throughout the product life cycle. ConfigurationsKingston’s e•MMC™ products support a variety of configurations that allow the e•MMC™ device to be tailored to your specific application needs. The most popular configurations described below are each offered under standard part numbers.Standard TLC – By default the e•MMC™ device is configured with the NAND flash in a standard TLC mode. This configuration provides reasonable performance and reliability for many applications. Pseudo Single Level Cell (pSLC) – The TLC NAND flash in the Kingston e•MMC™ device can be configured to further improve device endurance, data retention, reliability and performance over the standard TLC configuration. This is done by converting the NAND TLC cells to a pseudo single level cell (SLC) configuration. In this configuration, along with the performance and reliability gains, the device capacity is reduced by 2/3 of the capacity. This one-time configuration is achieved by setting the e•MMC™ enhanced attribute for the hardware partition.Kingston e•MMC™ can be ordered preconfigured with the option of reliable write or pSLC at no additional cost. Standard TLC devices can also be one-time configured in-field by following the procedures outlined in the JEDEC e•MMC™ specification. The JEDEC e•MMC™ specification allows for many additional configurations such as up to 4 additional general purpose (GPn) hardware partitions each with the option to support pSLC and reliable write. Additionally, Kingston provides a content loading service that can streamline your product assembly while reducing production costs. For more information, contact your Kingston representative.Kingston e•MMC™ devices are fully compliant with the JEDEC Standard Specification No. JESD84-B51. This datasheet provides technical specifications for Kingston’s family of e•MMC™ devices. Refer to the JEDEC e•MMC™ standard for specific information related to e•MMC™ device function and operation. See: /sites/default/files/docs/JESD84-B51.pdfe•MMC™ Mode and ControllerTLC mode using PS8229 - Leading edge 3D NAND flash technology in TLC mode rated to 3,000 endurance cycles.- Strong data protection with LDPC Error control- Improved data integrity with end-to-end data protection.pSLC mode using PS8229 - Leading edge 3D NAND flash technology in pSLC mode.- Strong data protection with LDPC Error control- Improved data integrity with end-to-end data protection.Part NumberingFigure 1 – Part Number FormatEMMC 16G - xxxx - PE90A B C DPart Number FieldsA: Product Family : EMMCB: Device Capacity : Available capacities of 16GB – 64GBC: Hardware Revision and ConfigurationD: Device Firmware Revision and ConfigurationTable 1 - Device SummaryDevice PerformanceTable 2 below provides sequential read and write speeds for all capacities. Performance numbers can vary under different operating conditions. Values are given at HS400 bus mode. Contact your Kingston Representative for performance numbers using other bus modes.Power ConsumptionDevice current consumption for various device configurations is defined in the power class fields of the EXT_CSD register. Power consumption values are summarized in Table 3 below.Device and Partition CapacityThe device NAND flash capacity is divided across two boot partitions (2048 KB each), a Replay Protected Memory Block (RPMB) partition (512 KB), and the main user storage area. Four additional general purpose storage partitions can be created from the user partition. These partitions can be factory preconfigured or configured in-field by following the procedure outlined in section 6.2 of the JEDEC e•MMC™ specification JESD84-B51. A small portion of the NAND storage capacity is used for the storage of the onboard controller firmware and mapping tables. Additionally, several NAND blocks are held in reserve to boost performance and extend the life of the e•MMC™ device. Table 4 identifies the specific capacity of each partition. This information is reported in the device EXT_CSD register. The contents of this register are also listed in the Appendix.e•MMC™ Bus ModesKingston e•MMC™ devices support all bus modes defined in the JEDEC e•MMC™ 5.1 specification. These modes are summarized in Table 6 below.Signal DescriptionTable 7 - e•MMC™ Signals Name Type DescriptionCLK I Clock: Each cycle of this signal directs a one bit transfer on the command and either a one bit (1x) or a two bits transfer (2x) on all the data lines. The frequency may vary between zero and the maximum clock frequency.DAT[7:0] I/O/PP Data: These are bidirectional data channels. The DAT signals operate in push-pull mode. These bidirectional signals are driven by either the e•MMC™ device or the host controller. By default, after power up or reset, only DAT0 is used for data transfer. A wider data bus can be configured for data transfer, using either DAT0-DAT3 or DAT0-DAT7, by the e•MMC™ host controller. The e•MMC™ device includes internal pull-ups for data lines DAT1-DAT7. Immediately after entering the 4-bit mode, the device disconnects the internal pull ups of lines DAT1, DAT2, and DAT3. Correspondingly, immediately after entering to the 8-bit mode, the device disconnects the internal pull-ups of lines DAT1–DAT7.CMD I/O/PP/OD Command: This signal is a bidirectional command channel used for device initialization and transfer of commands. The CMD signal has two operation modes: open-drain for initialization mode, and push-pull for fast command transfer. Commands are sent from the e•MMC™ host controller to the e•MMC™ device and responses are sent from the device to the host.DS O This signal is generated by the device and used for output in HS400 mode. The frequency of this signal follows the frequency of CLK. For data output each cycle of this signal directs two bits transfer(2x) on the data - one bit for positive edge and the other bit for negative edge. For CRC status response output and CMD response output (enabled only HS400 enhanced strobe mode), the CRC status and CMD Response are latched on the positive edge only, and don't care on the negative edge.RST_n I Hardware Reset: By default, hardware reset is disabled and must be enabled in the EXT_CSD register if used. Otherwise, it can be left un-connected.RFU - Reserved for future use: These pins are not internally connected. Leave floatingNC - Not Connected: These pins are not internally connected. Signals can be routed through these balls to ease printed circuit board design. See Kingston’s Design Guidelines for further details.VSF - Vendor Specific Function: These pins are not internally connectedVddi - Internal Voltage Node: Note that this is not a power supply input. This pin provides access to the output of an internal voltage regulator to allow for the connection of an external Creg capacitor. See Kingston’s Design Guidelines for further details.Vcc S Supply voltage for core Vccq S Supply voltage for I/ODesign GuidelinesDesign guidelines are outlined in a separate document. Contact your Kingston Representative for more information.Package DimensionsFigure 2 – Package DimensionsFigure 3 – Ball Pattern DimensionsBall Assignment (153 ball)Table 8 – Ball Assignment, Top View (HS400)1 2 3 4 5 6 7 8 9 10 11 12 13 14A NC NC DAT0 DAT1 DAT2 Vss RFU NC NC NC NC NC NC NC AB NC DAT3 DAT4 DAT5 DAT6 DAT7 NC NC NC NC NC NC NC NC BC NC Vddi NC Vssq NC Vccq NC NC NC NC NC NC NC NC CD NC NC NC NC NC NC NC DE NC NC NC RFU Vcc Vss VSF VSF VSF NC NC NC EF NC NC NC Vcc VSF NC NC NC FG NC NC RFU Vss VSF NC NC NC GH NC NC NC DS Vss NC NC NC H J NC NC NC Vss Vcc NC NC NC J K NC NC NC RST_n RFU RFU Vss Vcc VSF NC NC NC K L NC NC NC NC NC NC L M NC NC NC Vccq CMD CLK NC NC NC NC NC NC NC NC M N NC Vssq NC Vccq Vssq NC NC NC NC NC NC NC NC NC N P NC NC Vccq Vssq Vccq Vssq RFU NC NC RFU NC NC NC NC P1 2 3 4 5 6 7 8 9 10 11 12 13 14 Note: VSF, RFU and NC balls are not electrically connected. RFU balls may be defined with functionality by the Joint Electron Device Engineering Council (JEDEC) in future revisions of the e•MMC™ standard. Please refer to Kingston’s design guidelines for more info.Device MarkingFigure 4 - EMMC Package Marking240xxxx-xxx.xxxxYYWW PPPPPPPPxxxxxxx-xxxx2xxxxxxTAIWANKingston Logo240xxxx-xxx.xxxx:Internal control numberYYWW:Date code (YY– Last 2 digits ofyear, WW- Work week)PPPPPPPP: Internal control numberxxxxxxx-xxxx Sales P/N2xxxxxx : Internal control numberCountry:TAIWANCard Identification Register (CID)The Card Identification (CID) register is a 128-bit register that contains device identification information used during the e•MMC™ protocol device identification phase. Refer to JEDEC Standard Specification No.JESD84-B51 for details.Field Byte ValueMID [127:120] 0x70reserved [119:114] 0x00CBX [113:112] 0x01OID [111:104] 0x00PNM [103:56 ] IB2916(16G) IB2932(32G) IB2964(64G)PRV [ 55:48 ] 0x90PSN [ 47:16 ] RandomMDT [ 15:8 ] month, yearCRC [ 7:1 ] Follows JEDEC Standard reserved [ 0:0 ] 0x01Card Specific Data Register [CSD]The Card-Specific Data (CSD) register provides information on how to access the contents stored in e•MMC™. The CSD registers are used to define the error correction type, maximum data access time, data transfer speed, data format…etc. For details, refer to section 7.3 of the JEDEC Standard Specification No.JESD84-B51.Field Byte ValueCSD_Structure [127:126] 0x03 (V2.0)SPEC_VER [125:122] 0x04 (V4.0~4.2)reserved [121:120] 0x00TAAC [119:112] 0x4F (40ms)NSAC [111:104] 0x01TRAN_SPEED [103:96 ] 0x32 (26Mbit/s)CCC [ 95:84 ] 0x0F5READ_BL_LEN [ 83:80 ] 0x09 (512 Bytes)READ_BL_PARTIAL [ 79:79 ] 0x00WRITE_BLK_MISALIGN [ 78:78 ] 0x00READ_BLK_MISALIGN [ 77:77 ] 0x00DSR_IMP [ 76:76 ] 0x00reserved [ 75:74 ] 0x00C_SIZE [ 73:62 ] 0xFFFVDD_R_CURR_MIN [ 61:59 ] 0x07 (100mA)VDD_R_CURR_MAX [ 58:56 ] 0x07 (200mA)VDD_W_CURR_MIN [ 55:53 ] 0x07 (100mA)VDD_W_CURR_MAX [ 52:50 ] 0x07 (200mA)C_SIZE_MULT [ 49:47 ] 0x07 (512 Bytes)ERASE_GRP_SIZE [ 46:42 ] 0x1FERASE_GRP_MULT [ 41:37 ] 0x1FWP_GRP_SIZE [ 36:32 ] 0x0FWP_GRP_ENABLE [ 31:31 ] 0x01DEFAULT_ECC [ 30:29 ] 0x00R2W_FACTOR [ 28:26 ] 0x02WRITE_BL_LEN [ 25:22 ] 0x09 (512 Bytes)WRITE_BL_PARTIAL [ 21:21 ] 0x00reserved [ 20:17 ] 0x00CONTENT_PROT_APP [ 16:16 ] 0x00FILE_FORMAT_GRP [ 15:15 ] 0x00COPY [ 14:14 ] 0x00PERM_WRITE_PROTECT [ 13:13 ] 0x00TMP_WRITE_PROTECT [ 12:12 ] 0x00FILE_FORMAT [ 11:10 ] 0x00Field Byte ValueECC [ 9:8 ] 0x00CRC [ 7:1 ] Follow JEDEC Standard reserved [ 0:0 ] 0x01Extended Card Specific Data Register [EXT_CSD]The Extended CSD register defines the Device properties and selected modes. It is 512 bytes long. The most significant 320 bytes are the Properties segment, which defines the Device capabilities and cannot be modified by the host. The lower 192 bytes are the Modes segment, which defines the configuration the Device is working in. These modes can be changed by the host by means of the SWITCH command. For details, refer to section 7.4 of the JEDEC Standard Specification No.JESD84-B51.Field Byte ValueReserved [511:506] 0EXT_SECURITY_ERR [505:505] 0x00S_CMD_SET [504:504] 0x01HPI_FEATURES [503:503] 0x01BKOPS_SUPPORT [502:502] 0x01MAX_PACKED_READS [501:501] 0x3CMAX_PACKED_WRITES [500:500] 0x20DATA_TAG_SUPPORT [499:499] 0x01TAG_UNIT_SIZE [498:498] 0x03TAG_RES_SIZE [497:497] 0x00CONTEXT_CAPABILITIES [496:496] 0x05LARGE_UNIT_SIZE_M1 [495:495] 0x17(16G) 0x2F(32G) 0x5F(64G)EXT_SUPPORT [494:494] 0x03 SUPPORTED_MODES [493:493] 0x01FFU_FEATURES [492:492] 0x00 OPERATION_CODE_TIMEOUT [491:491] 0x00FFU_ARG [490:487] 65535 BARRIER_SUPPORT [486:486] 0x01Reserved [485:309] 0CMDQ_SUPPORT [308:308] 0x01CMDQ_DEPTH [307:307] 0x0FReserved [306:306] 0x00 NUMBER_OF_FW_SECTORS_CORRECTLY_PROGRAMMED [305:302] 0 VENDOR_PROPRIETARY_HEALTH_REPORT [301:270] 0 DEVICE_LIFE_TIME_EST_TYP_B [269:269] 0x01DEVICE_LIFE_TIME_EST_TYP_A [268:268] 0x01PRE_EOL_INFO [267:267] 0x01 OPTIMAL_READ_SIZE [266:266] 0x01OPTIMAL_WRITE_SIZE [265:265] 0x08Field Byte Value OPTIMAL_TRIM_UNIT_SIZE [264:264] 0x01 DEVICE_VERSION [263:262] 0FIRMWARE_VERSION [261:254] 0x90 PWR_CL_DDR_200_360 [253:253] 0x00 CACHE_SIZE [252:249] 1024 GENERIC_CMD6_TIME [248:248] 0x32 POWER_OFF_LONG_TIME [247:247] 0xFF BKOPS_STATUS [246:246] 0x00 CORRECTLY_PRG_SECTORS_NUM [245:242] 0 INI_TIMEOUT_AP [241:241] 0x64 CACHE_FLUSH_POLICY [240:240] 0x01 PWR_CL_DDR_52_360 [239:239] 0x00 PWR_CL_DDR_52_195 [238:238] 0x00PWR_CL_200_195 [237:237] 0x00PWR_CL_200_130 [236:236] 0x00 MIN_PERF_DDR_W_8_52 [235:235] 0x00 MIN_PERF_DDR_R_8_52 [234:234] 0x00 Reserved [233:233] 0x00TRIM_MULT [232:232] 0x11(16G) 0x11(32G) 0x22(64G)SEC_FEATURE_SUPPORT [231:231] 0x55 SEC_ERASE_MULT [230:230] 0xF7 SEC_TRIM_MULT [229:229] 0xF7 BOOT_INFO [228:228] 0x07Reserved [227:227] 0x00 BOOT_SIZE_MULT [226:226] 0x20ACC_SIZE [225:225] 0x07(16G) 0x08(32G) 0x09(64G)HC_ERASE_GRP_SIZE [224:224] 0x01ERASE_TIMEOUT_MULT [223:223] 0x11(16G) 0x11(32G) 0x22(64G)REL_WR_SEC_C [222:222] 0x01HC_WP_GRP_SIZE [221:221] 0x10 S_C_VCC [220:220] 0x08S_C_VCCQ [219:219] 0x08 PRODUCTION_STATE_AWARENESS_TIMEOUT [218:218] 0x14 S_A_TIMEOUT [217:217] 0x15 SLEEP_NOTIFICATION_TIME [216:216] 0x0FField Byte ValueSEC_COUNT [215:212] 10207232 (16G) 20414464 (32G) 40828928 (64G)SECURE_WP_INFO [211:211] 0x01 MIN_PERF_W_8_52 [210:210] 0x08 MIN_PERF_R_8_52 [209:209] 0x08 MIN_PERF_W_8_26_4_52 [208:208] 0x08 MIN_PERF_R_8_26_4_52 [207:207] 0x08 MIN_PERF_W_4_26 [206:206] 0x08 MIN_PERF_R_4_26 [205:205] 0x08 Reserved [204:204] 0x00 PWR_CL_26_360 [203:203] 0x00 PWR_CL_52_360 [202:202] 0x00 PWR_CL_26_195 [201:201] 0x00 PWR_CL_52_195 [200:200] 0x00 PARTITION_SWITCH_TIME [199:199] 0xFF OUT_OF_INTERRUPT_TIME [198:198] 0xFF DRIVER_STRENGTH [197:197] 0x1F DEVICE_TYPE [196:196] 0x57 Reserved [195:195] 0x00 CSD_STRUCTURE [194:194] 0x02 Reserved [193:193] 0x00 EXT_CSD_REV [192:192] 0x08 CMD_SET [191:191] 0x00Reserved [190:190] 0x00 CMD_SET_REV [189:189] 0x00 Reserved [188:188] 0x00 POWER_CLASS [187:187] 0x00 Reserved [186:186] 0x00HS_TIMING [185:185] 0x01 STROBE_SUPPORT [184:184] 0x01 BUS_WIDTH [183:183] 0x02Reserved [182:182] 0x00 ERASED_MEM_CONT [181:181] 0x00 Reserved [180:180] 0x00 PARTITION_CONFIG [179:179] 0x00 BOOT_CONFIG_PROT [178:178] 0x00 BOOT_BUS_CONDITIONS [177:177] 0x00 Reserved [176:176] 0x00 ERASE_GROUP_DEF [175:175] 0x00 BOOT_WP_STATUS [174:174] 0x00C - 4Field Byte Value BOOT_WP [173:173] 0x00 Reserved [172:172] 0x00 USER_WP [171:171] 0x00 Reserved [170:170] 0x00 FW_CONFIG [169:169] 0x00 RPMB_SIZE_MULT [168:168] 0x20 WR_REL_SET [167:167] 0x00 WR_REL_PARAM [166:166] 0x15 SANITIZE_START [165:165] 0x00 BKOPS_START [164:164] 0x00 BKOPS_EN [163:163] 0x00 RST_n_FUNCTION[162:162] 0x00 HPI_MGMT[161:161] 0x00 PARTITIONING_SUPPORT [160:160] 0x07 MAX_ENH_SIZE_MULT [159:157] 623(16G) 1246(32G) 2492(64G) PARTITIONS_ATTRIBUTE[156:156] 0x01 PARTITION_SETTING_COMPLETED[155:155] 0x01 GP_SIZE_MULT_4 [154:152] 0 GP_SIZE_MULT_3 [151:149] 0 GP_SIZE_MULT_2 [148:146] 0 GP_SIZE_MULT_1[145:143] 0 ENH_SIZE_MULT[142:140] 623(16G) 1246(32G) 2492(64G)ENH_START_ADDR[139:136] 0 Reserved[135:135] 0x00 SEC_BAD_BLK_MGMNT[134:134] 0x00 PRODUCTION_STATE_AWARENESS[133:133] 0x00 TCASE_SUPPORT [132:132] 0x00 PERIODIC_WAKEUP[131:131] 0x00 PROGRAM _CID_CSD_DDR_SUPPORT[130:130] 0x01 Reserved[129:128] 0 VENDOR_SPECIFIC_FIELD[127:67 ] 538968064ERROR_CODE [ 66:65 ] 0 ERROR_TYPE[ 64:64 ] 0x00 NATIVE_SECTOR_SIZE [ 63:63 ] 0x00 USE_NATIVE_SECTOR [ 62:62 ] 0x00 DATA_SECTOR_SIZE [ 61:61 ] 0x00 INI_TIMEOUT_EMU[ 60:60 ] 0x00C - 5FieldByte Value CLASS_6_CTRL [ 59:59 ] 0x00 DYNCAP_NEEDED[ 58:58 ] 0x00 EXCEPTION_EVENTS_CTRL [ 57:56 ] 0 EXCEPTION_EVENTS_STATUS [ 55:54 ] 0 EXT_PARTITIONS_ATTRIBUTE[ 53:52 ] 0 CONTEXT_CONF[ 51:37 ] 0 PACKED_COMMAND_STATUS [ 36:36 ] 0x00 PACKED_FAILURE_INDEX [ 35:35 ] 0x00 POWER_OFF_NOTIFICATION[ 34:34 ] 0x00 CACHE_CTRL [ 33:33 ] 0x00 FLUSH_CACHE [ 32:32 ] 0x00 BARRIER_CTRL [ 31:31 ] 0x00 MODE_CONFIG[ 30:30 ] 0x00 MODE_OPERATION_CODES[ 29:29 ] 0x00 Reserved [ 28:27 ] 0 FFU_STATUS[ 26:26 ] 0x00 PRE_LOADING_DATA_SIZE [ 25:22 ] 0MAX_PRE_LOADING_DATA_SIZE[ 21:18 ] 3304106(16G) 6608213(32G) 13216426(64G)PRODUCT_STATE_AWARENESS_ENABLEMENT[ 17:17 ] 0x01 SECURE_REMOVAL_TYPE[ 16:16 ] 0x01 CMDQ_MODE_EN[ 15:15 ] 0x00 Reserved[ 14:0 ]。

PA2561L1-1(NEC)光耦规格书

DATA SHEETThe information in this document is subject to change without notice.©1992Document No. P12989EJ4V0DS00 (4th edition)(Previous No. LC-2225)Date Published August 1997 NS Printed in JapanPHOTOCOUPLERPS2561-1,-2, PS2561L-1,-2HIGH ISOLATION VOLTAGE SINGLE TRANSISTOR TYPE MULTI PHOTOCOUPLER SERIESThe mark shows major revised points.DESCRIPTIONThe PS2561-1, -2 and PS2561L-1, -2 are optically coupled isolators containing a GaAs light emitting diode and an NPN silicon phototransistor.PS2561-1, -2 are in a plastic DIP (Dual In-line Package) and PS2561L-1, -2 are lead bending type (Gull-wing) for surface mount.FEATURES•High isolation voltageBV = 5 000 Vr.m.s.: standard productsBV = 3 750 Vr.m.s.: VDE0884 approved products (Option)•High collector to emitter voltage (V CEO = 80 V)•High current transfer ratio (CTR = 200 % TYP.)•High-speed switching (t r = 3 µs TYP., t f = 5 µs TYP.)•UL approved (File No. E72422 (S) )•CSA approved (No. CA 101391)•BSI approved (BS415, BS7002) No. 7112•SEMKO approved (SS4410165) No. 9317144•NEMKO approved (NEK-HD 195S6) No. A21409•DEMKO approved (Section 101, 137) No. 300535•FIMKO approved (E69-89) No. 167265-08•VDE0884 approved (Option)APPLICATIONS•Power supply •Telephone/FAX.•FA/OA equipment•Programmable logic controller2PACKAGE DIMENSIONS (in millimeters)DIP Type5.1 MAX.6.53.8M A X .4.55M A X .2.8M I N .0.652.547.620.50 ± 0.100.25M4312PS2561-1 (New Package)10.2 MAX.1.25±0.156.53.8M A X .4.55M A X .2.8M I N .0.652.547.620.50 ± 0.100.25M871265340 to 15˚PS2561-20 to 15˚PS2561-14.6 ± 0.351.25±0.156.53.8M A X .4.55M A X .2.8M I N .0.650.50 ± 0.100.25M0 to 15˚7.622.5443121.25±0.15PS2561L1-15.1 MAX.6.53.8M A X .4.25M A X .2.8M I N .0.352.547.620.50 ± 0.100.25M0 to 15˚43121.25±0.1510.161. Anode 2. Cathode 3. Emitter 4. Collector 1, 3. Anode 2, 4. Cathode 5, 7. Emitter 6, 8. Collector1. Anode2. Cathode3. Emitter4. Collector 1. Anode 2. Cathode 3. Emitter 4. Collector Caution New package 1ch only3Lead Bending Type5.1 MAX.6.53.8M A X .2.547.620.25M4312PS2561L-1 (New Package)10.2 MAX.1.25±0.156.53.8M A X .2.547.6287126534PS2561L-2PS2561L-14.6 ± 0.351.25±0.156.53.8M A X .0.25M7.622.5443121.25±0.150.05 t o 0.29.60 ± 0.40.90 ± 0.250.05 t o 0.29.60 ± 0.40.90 ± 0.250.25M0.05 t o 0.29.60 ± 0.40.90 ± 0.255.1 MAX.6.53.8M A X .2.547.620.25MPS2561L2-143121.25±0.150.05 t o 0.210.160.9 ± 0.2512.0 MAX.1. Anode2. Cathode3. Emitter4. Collector1, 3. Anode 2, 4. Cathode 5, 7. Emitter 6, 8. Collector 1. Anode 2. Cathode 3. Emitter 4. Collector 1. Anode 2. Cathode 3. Emitter 4. Collector Caution New package 1ch only4ORDERING INFORMATIONPart NumberPackageSafety Standard ApprovalApplication partnumber *1PS2561-1PS2561L-1PS2561L1-1PS2561L2-14-pin DIP4-pin DIP (lead bending surface mount)4-pin DIP (for long distance)4-pin DIP (for long distance surfacemount)Standard products PS2561-1PS2561-2PS2561L-28-pin DIP8-pin DIP (lead bending surface mount)PS2561-2PS2561-1-V PS2561L-1-V PS2561L1-1-V PS2561L2-1-V 4-pin DIP4-pin DIP (lead bending surface mount)4-pin DIP (for long distance)4-pin DIP (for long distance surfacemount)VDE0884 approved products (Option)PS2561-1PS2561-2-V PS2561L-2-V8-pin DIP8-pin DIP (lead bending surface mount)PS2561-2*1 As applying to Safety Standard, following part number should be used.ABSOLUTE MAXIMUM RATINGS (T A = 25 °C, unless otherwise specified)ParameterSymbolRatingsUnitPS2561-1,PS2561L-1PS2561-2,PS2561L-2DiodeReverse Voltage V R 6V Forward Current (DC)I F80mAPower Dissipation Derating ∆P D /°C 1.5 1.2mW/°C Power Dissipation P D 150120mW/ch Peak Forward Current*1I FP 1A TransistorCollector to Emitter Voltage V CEO 80V Emitter to Collector Voltage V ECO 7V Collector CurrentI C50mA/chPower Dissipation Derating ∆P C /°C 1.5 1.2mW/°C Power DissipationP C 150120mW/ch Isolation Voltage*2BV5 0003 750*3Vr.m.s.Operating Ambient Temperature T A –55 to +100°C Storage TemperatureT stg–55 to +150°C*1PW = 100 µs, Duty Cycle = 1 %*2AC voltage for 1 minute at T A = 25 °C, RH = 60 % between input and output *3VDE0884 approved products (Option)•UL approved •CSA approved •BSI approved•NEMKO approved •DEMKO approved •SEMKO approved•FIMKO approved5ELECTRICAL CHARACTERISTICS (T A = 25 °C)ParameterSymbol Conditions MIN.TYP.MAX.Unit DiodeForward Voltage V F I F = 10 mA 1.171.4VReverse Current I R V R = 5 V5µA Terminal CapacitanceC t V = 0 V, f = 1.0 MHz 50pFTransistorCollector to Emitter Dark CurrentI CEOV CE = 80 V, I F = 0 mA100nACoupled Current Transfer Ratio *1CTR I F = 5 mA, V CE = 5 V 80200400%Collector Saturation VoltageV CE (sat)I F = 10 mA, I C = 2 mA0.3V Isolation Resistance R I-O V I-O = 1.0 kV 1011ΩIsolation Capacitance C I-O V = 0 V, f = 1.0 MHz0.5pFRise Time *2t r V CC = 10 V, I C = 2 mA, R L = 100 Ω3µsFall Time*2t f5*1CTR rank (only PS2561-1, PS2561L-1)*2Test circuit for switching timeL: 200 to 400 (%)M : 80 to 240 (%)D : 100 to 300 (%)H : 80 to 160 (%)W : 130 to 260 (%)V CCV OUTR L = 100 Ω50 ΩI F µPulse InputPW = 100 sDuty Cycle = 1/106TYPICAL CHARACTERISTICS (T A = 25 °C, unless otherwise specified)150100500255075100125150 1.5 mW/˚C1.2 mW/˚C15010050255075100125150010 0001001 000100101755025–25–50V CE = 80 V10 1.00.80.60.40.20510.50.110 m A401.5 mW/˚C1.2 mW/˚C20 m A 50 m A 2 m AI F = 1 mA5 m A 70260504030201004681020 m A I F = 5 mA10m A 50 m A 40 V 24 V 10 V 5 VPS2561-1PS2561L-1PS2561-2PS2561L-2PS2561-1PS2561L-1PS2561-2PS2561L-2100 1.51.41.31.21.11.00.90.80.75010510.50.10 ˚C –25 ˚C –55 ˚C+60 ˚C +25 ˚CT A = +100 ˚CD i o d e P o w e r D i s s i p a t i o n P D (m W )T r a n s i s t o r P o w e r D i s s i p a t i o n P C (m W )Ambient Temperature T A (˚C)F o r w a r d C u r r e n t I F (m A )Forward Voltage V F (V)C o l l e c t o r C u r r e n t I C (m A )Collector to Emitter Voltage V CE (V)C o l l e c t o r t o E m i t t e rD a r k C u r r e n t I CE O (n A )Collector Saturation Voltage V CE(sat) (V)Ambient Temperature T A (˚C)Ambient Temperature T A (˚C)DIODE POWER DISSIPATION vs.AMBIENT TEMPERATURETRANSISTOR POWER DISSIPATION vs. AMBIENT TEMPERATUREFORWARD CURRENT vs.FORWARD VOLTAGECOLLECTOR CURRENT vs.COLLECTOR TO EMITTER VOLTAGECOLLECTOR TO EMITTER DARKCURRENT vs. AMBIENT TEMPERATURECOLLECTOR CURRENT vs.COLLECTOR SATURATION VOLTAGEC o l l e c t o r C u r r e n t I C (m A )7PS2561-1,-2,PS2561L-1,-21.2–501.00.80.60.40.20–252550751004504003503002502001501005000.050.10.5151050501010.110 k5 k 1 k50010050101 000100101100 k50 k 10 k5 k 1 k5001000–5–10–15–200.5125102050100200500I C = 2 mA,V CC = 10 V,CTR = 290 %t f t rt dt sI F = 5 mA,V CC = 5 V,CTR = 290 %t st dt rt fI F = 5 mA,V CE = 5 V100 Ω300 ΩR L = 1 k ΩI F = 5 mA T A = 25 ˚CI F = 5 mA T A = 60 ˚C 1.21.00.80.60.40.2102103104105Normalized to 1.0at T A = 25 ˚C,I F = 5 mA, V CE = 5 VForward Current I F (mA)Ambient Temperature T A (˚C)Load Resistance R L (Ω)Frequency f (kHz)N o r m a l i z e d C u r r e n t T r a n s f e r R a t i o C T RC u r r e n t T r a n s f e r R a t i o C T R (%)N o r m a l i z e d G a i n G VLoad Resistance R L (Ω)S w i t c h i n g T i m e t ( s )µNORMALIZED CURRENT TRANSFER RATIO vs. AMBIENT TEMPERATURECURRENT TRANSFER RATIO vs.FORWARD CURRENTSWITCHING TIME vs.LOAD RESISTANCESWITCHING TIME vs.LOAD RESISTANCEFREQUENCY RESPONSELONG TIME CTR DEGRADATIONS w i t c h i n g T i m e t ( s )µTYP.Time (Hr)C T R (R e l a t i v e V a l u e )8TAPING SPECIFICATIONS (in millimeters)Taping DirectionPS2561L-1-E3PS2561L-1-F3PS2561L-1-E4PS2561L-1-F4Outline and Dimensions (Tape)1.55±0.12.0±0.14.0±0.11.55±0.11.75±0.14.3±0.210.3±0.10.37.5±0.116.0±0.35.6±0.18.0±0.1Outline and Dimensions (Reel)Packing: PS2561L-1-E3, E4 1 000 pcs/reel2.0±0.5R 1.013.0±0.5φ21.0±0.8φ16.4+2.0–0.0P S 2561L -1-E 3, E 4: 250P S 2561L -1-F 3, F 4: 330φ80.0±5.0φφPS2561L-1-F3, F4 2 000 pcs/reel9Taping DirectionPS2561L-2-E3PS2561L-2-E4Outline and Dimensions (Tape)1.55±0.12.0±0.14.0±0.11.55±0.11.75±0.14.3±0.210.3±0.10.37.5±0.116.0±0.310.4±0.112.0±0.1Outline and Dimensions (Reel)Packing: 1 000 pcs/reel16.4+2.0–0.080.0±5.0φ330φ2.0±0.5R 1.013.0±0.5φ21.0±0.8φ10RECOMMENDED SOLDERING CONDITIONS(1) Infrared reflow soldering • Peak reflow temperature235 °C (package surface temperature)• Time of temperature higher than 210 °C 30 seconds or less • Number of reflows Three• FluxRosin flux containing small amount of chlorine (The flux with a maximum chlorine content of 0.2 Wt % is recommended.)60 to 90 s (preheating)210 ˚C120 to 160 ˚CP a c k a g e S u r f a c e T e m p e r a t u r e T (˚C )Time (s)(heating)to 10 sto 30 s235 ˚C (peak temperature)Recommended Temperature Profile of Infrared ReflowPeak temperature 235 ˚C or belowCaution Please avoid to removed the residual flux by water after the first reflow processes.(2) Dip soldering • Temperature 260 °C or below (molten solder temperature)• Time10 seconds or less • Number of times One• FluxRosin flux containing small amount of chlorine (The flux with a maximum chlorine content of 0.2 Wt % is recommended.)11SPECIFICATION OF VDE MARKS LICENSE DOCUMENT (VDE0884)ParameterSymbolSpeckUnitApplication classification (DIN VDE 0109)for rated line voltages ≤ 300 Vr.m.s.for rated line voltages ≤ 600 Vr.m.s.IV III Climatic test class (DIN IEC 68 Teil 1/09.80)55/100/21Dielectric strength maximum operating isolation voltageTest voltage (partial discharge test procedure a for type test and random test)U pr = 1.2 × U IORM , P d < 5 pCU IORM U pr 8901 068V peak V peakTest voltage (partial discharge test procedure b for random test)U pr = 1.6 × U IORM , P d < 5 pC U pr 1 424V peakHighest permissible overvoltage U TR 6 000V peakDegree of pollution (DIN VDE 0109)2Clearance distance > 7.0mm Creepage distance> 7.0mmComparative tracking index (DIN IEC 112/VDE 0303 part 1)CTI 175Material group (DIN VDE 0109)III a Storage temperature range T stg –55 to +150°C Operating temperature rangeT A –55 to +100°C Isolation resistance, minimum value V IO = 500 V dc at T A = 25 °CV IO = 500 V dc at T A MAX. at least 100 °CRis MIN.Ris MIN.10121011ΩΩSafety maximum ratings (maximum permissible in case of fault, see thermal derating curve)Package temperatureCurrent (input current I F , Psi = 0)Power (output or total power dissipation)Isolation resistanceV IO = 500 V dc at T A = 175 °C (Tsi)Tsi Isi Psi Ris MIN.175********9°C mA mW ΩCAUTIONWithin this device there exists GaAs (Gallium Arsenide) material which is aharmful substance if ingested. Please do not under any circumstances break thehermetic seal.No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.NEC devices are classified into the following three quality grades:"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronicequipment and industrial robotsSpecial: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designedfor life support)Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.Anti-radioactive design is not implemented in this product.M4 96. 5。

Eaton Moeller NZM型号熔断器产品说明说明书

Eaton 281306Eaton Moeller series NZM - Molded Case Circuit Breaker. Circuit-breaker, 3p, 100A, H2-M100Allgemeine spezifikationEaton Moeller series NZM molded case circuit breaker thermo-magnetic281306149 mm184 mm 105 mm 2.323 kg RoHS conform IEC/EN 60947 IEC4015082813062NZMH2-M100Product NameCatalog NumberProduct Length/Depth Product Height Product Width Product Weight Compliances Certifications EANModel Code100 AIs the panel builder's responsibility. The specifications for the switchgear must be observed.5 kA130 kAMeets the product standard's requirements.Is the panel builder's responsibility. The specifications for the switchgear must be observed.Built-in device fixed built-in techniqueFixed100 ADoes not apply, since the entire switchgear needs to be evaluated.Max. 10 segments of 24 mm x 0.8 mm at rear-side connection (punched)Min. 2 segements of 16 mm x 0.8 mm at rear-side connection (punched)Max. 10 segments of 16 mm x 0.8 mm at box terminalMax. 8 segments of 24 mm x 1 mm (2x) at box terminal Min. 2 segments of 9 mm x 0.8 mm at box terminalRocker leverMeets the product standard's requirements.40 °C eaton-circuit-breaker-let-through-current-nzm-mccb-characteristic-curve-005.epseaton-circuit-breaker-characteristic-power-defense-mccb-characteristic-curve-037.epsMH2-M100il01206006z2015_11.pdfDas neue digitale NZM-Sortiment - In Kurze verfugbar DE Vorstellung des neuen digitalen Leistungsschalter NZMDA-CD-nzm2_3pDA-CS-nzm2_3peaton-manual-motor-starters-starter-nzm-mccb-wiring-diagram.eps eaton-manual-motor-starters-starter-msc-r-reversing-starter-wiring-diagram.epseaton-nzm-technical-information-sheeteaton-circuit-breaker-nzm-mccb-dimensions-019.epsRated operational current for specified heat dissipation (In) 10.11 Short-circuit ratingRated short-circuit breaking capacity Ics (IEC/EN 60947) at 690 V, 50/60 HzRated short-circuit breaking capacity Icu (IEC/EN 60947) at 400/415 V, 50/60 Hz10.4 Clearances and creepage distances10.12 Electromagnetic compatibilityMounting MethodAmperage Rating10.2.5 LiftingTerminal capacity (copper strip)Handle type10.2.3.1 Verification of thermal stability of enclosuresAmbient storage temperature - min Characteristic curveeCAD model Installationsanleitung Installationsvideos mCAD modelSchaltpläneTechnische Datenblätter ZeichnungenFitted with:Thermal protectionProtection against direct contactFinger and back-of-hand proof to VDE 0106 part 100Terminal capacity (copper busbar)M8 at rear-side screw connectionMax. 24 mm x 8 mm direct at switch rear-side connectionMin. 16 mm x 5 mm direct at switch rear-side connection10.8 Connections for external conductorsIs the panel builder's responsibility.Special featuresMaximum back-up fuse, if the expected short-circuit currents at the installation location exceed the switching capacity of the circuit breaker (Rated short-circuit breaking capacity Icn) Rated current = rated uninterrupted current: 100 A Tripping class 10 A IEC/EN 60947-4-1, IEC/EN 60947-2 The circuit-breaker fulfills all requirements for AC-3 switching category.Ambient operating temperature - max70 °CClimatic proofingDamp heat, constant, to IEC 60068-2-78Damp heat, cyclic, to IEC 60068-2-30Terminal capacity (aluminum stranded conductor/cable)25 mm² - 185 mm² (1x) at tunnel terminal25 mm² - 50 mm² (1x) direct at switch rear-side connection25 mm² - 50 mm² (2x) direct at switch rear-side connectionTerminal capacity (copper stranded conductor/cable)25 mm² - 185 mm² (1x) at 1-hole tunnel terminal25 mm² - 185 mm² (1x) at box terminal25 mm² - 185 mm² (1x) direct at switch rear-side connection25 mm² - 70 mm² (2x) at box terminal25 mm² - 70 mm² (2x) direct at switch rear-side connectionLifespan, electrical5000 operations at 690 V AC-36500 operations at 415 V AC-37500 operations at 690 V AC-110000 operations at 400 V AC-16500 operations at 400 V AC-310000 operations at 415 V AC-1Electrical connection type of main circuitScrew connectionShort-circuit total breaktime< 10 msRated impulse withstand voltage (Uimp) at main contacts8000 VRated short-circuit breaking capacity Ics (IEC/EN 60947) at 400/415 V, 50/60 Hz130 kA10.9.3 Impulse withstand voltageIs the panel builder's responsibility.Utilization categoryA (IEC/EN 60947-2)Number of polesThree-poleAmbient operating temperature - min-25 °C10.6 Incorporation of switching devices and componentsDoes not apply, since the entire switchgear needs to be evaluated.10.5 Protection against electric shockDoes not apply, since the entire switchgear needs to be evaluated.Terminal capacity (control cable)0.75 mm² - 1.5 mm² (2x)0.75 mm² - 2.5 mm² (1x)Equipment heat dissipation, current-dependent25.65 WInstantaneous current setting (Ii) - min800 A10.13 Mechanical functionThe device meets the requirements, provided the information in the instruction leaflet (IL) is observed.10.2.6 Mechanical impactDoes not apply, since the entire switchgear needs to be evaluated.10.9.4 Testing of enclosures made of insulating materialIs the panel builder's responsibility.Rated operational current99 A (400 V AC-3)Rated short-circuit breaking capacity Ics (IEC/EN 60947) at 230 V, 50/60 Hz150 kAApplicationUse in unearthed supply systems at 690 V10.3 Degree of protection of assembliesDoes not apply, since the entire switchgear needs to be evaluated.Rated short-circuit making capacity Icm at 240 V, 50/60 Hz330 kARated short-circuit breaking capacity Ics (IEC/EN 60947) at 440 V, 50/60 Hz130 kADegree of protection (IP), front sideIP40 (with insulating surround)IP66 (with door coupling rotary handle)Rated short-circuit making capacity Icm at 525 V, 50/60 Hz105 kARated short-circuit making capacity Icm at 690 V, 50/60 Hz40 kAInstantaneous current setting (Ii) - max1250 AOverload current setting (Ir) - min80 A10.2.3.2 Verification of resistance of insulating materials to normal heatMeets the product standard's requirements.10.2.3.3 Resist. of insul. mat. to abnormal heat/fire by internal elect. effectsMeets the product standard's requirements.Lifespan, mechanical20000 operationsOverload current setting (Ir) - max100 AVoltage rating690 V - 690 VTerminal capacity (copper solid conductor/cable)6 mm² - 16 mm² (2x) at box terminal10 mm² - 16 mm² (1x) direct at switch rear-side connection6 mm² - 16 mm² (2x) direct at switch rear-side connection16 mm² (1x) at tunnel terminal10 mm² - 16 mm² (1x) at box terminalDegree of protection (terminations)IP00 (terminations, phase isolator and strip terminal)IP10 (tunnel terminal)10.9.2 Power-frequency electric strengthIs the panel builder's responsibility.Short-circuit release non-delayed setting - min800 ADegree of protectionIP20 (basic degree of protection, in the operating controls area) IP20Overvoltage categoryIIIRated short-time withstand current (t = 1 s)1.9 kARated impulse withstand voltage (Uimp) at auxiliary contacts 6000 VTerminal capacity (aluminum solid conductor/cable)10 mm² - 16 mm² (1x) direct at switch rear-side connection10 mm² - 16 mm² (2x) direct at switch rear-side connection16 mm² (1x) at tunnel terminalSwitch off techniqueThermomagneticRated short-time withstand current (t = 0.3 s)1.9 kAAmbient storage temperature - max70 °CRated short-circuit breaking capacity Ics (IEC/EN 60947) at 525 V, 50/60 Hz37.5 kAOptional terminalsBox terminal. Connection on rear. Tunnel terminalRelease systemThermomagnetic releasePollution degree310.7 Internal electrical circuits and connectionsIs the panel builder's responsibility.Rated operating power at AC-3, 230 V30 kW10.10 Temperature riseThe panel builder is responsible for the temperature rise calculation. Eaton will provide heat dissipation data for the devices.FunctionsMotor protectionShort-circuit release non-delayed setting - max1400 AStandard terminalsScrew terminalRated short-circuit making capacity Icm at 400/415 V, 50/60 Hz 330 kARated operating power at AC-3, 400 V55 kWTypeCircuit breaker10.2.2 Corrosion resistanceMeets the product standard's requirements.10.2.4 Resistance to ultra-violet (UV) radiationMeets the product standard's requirements.10.2.7 InscriptionsMeets the product standard's requirements.Rated short-circuit making capacity Icm at 440 V, 50/60 Hz 286 kAIsolation500 V AC (between auxiliary contacts and main contacts)300 V AC (between the auxiliary contacts)Number of operations per hour - max120Circuit breaker frame typeNZM2Direction of incoming supplyAs requiredShock resistance20 g (half-sinusoidal shock 20 ms)Eaton Konzern plc Eaton-Haus30 Pembroke-Straße Dublin 4, Irland © 2023 Eaton. Alle Rechte vorbehalten. Eaton ist eine eingetrageneMarke.Alle anderen Warenzeichen sindEigentum ihrer jeweiligenBesitzer./socialmedia1000 VRated insulation voltage (Ui)。

毛斯(Moxa)UC-8200系列双核ARM Cortex-A7 1GHz IIoT网关产品说明书

UC-8200SeriesArm Cortex-A7dual-core1GHz IIoT gateways with built-in LTE Cat.4,1mini PCIe expansion slot for a Wi-Fi module,1CAN port,4DIs,4DOsFeatures and Benefits•Armv7Cortex-A7dual-core1GHz•ISASecure IEC62443-4-2Security Level2certified with Moxa IndustrialLinux3Secure•Moxa Industrial Linux with10-year superior long-term support•LTE-ready computer with Verizon/AT&T certification and industrial-grade CE/FCC/UL certifications•Dual-SIM slots•2auto-sensing10/100/1000Mbps Ethernet ports•Integrated LTE Cat.4module with US/EU/APAC band support•1CAN port supports CAN2.0A/B•microSD socket for storage expansion•-40to85°C wide temperature range and-40to70°C with LTE enabledCertificationsIntroductionThe UC-8200computing platform is designed for embedded data acquisition applications.The computer comes with dual RS-232/422/485serial ports,dual10/100/1000Mbps Ethernet ports,and one CAN port as well as dual Mini PCIe socket to support Wi-Fi/cellular modules.These versatile capabilities let users efficiently adapt the UC-8200to a variety of complex communications solutions.The UC-8200is built around a Cortex-A7dual core processor that has been optimized for use in energy monitoring systems,but is widely applicable to a variety of industrial solutions.With flexible interfacing options,this tiny embedded computer is a reliable and secure gateway for data acquisition and processing at field sites as well as a useful communications platform for many other large-scale deployments.Wide temperature LTE-enabled models are available for extended temperature applications.All units are thoroughly tested in a testing chamber, guaranteeing that the LTE-enabled computing platforms are suitable for wide-temperature applications.AppearanceUC-8210UC-8220SpecificationsComputerCPU Armv7Cortex-A7dual-core1GHzDRAM2GB DDR3LSupported OS Moxa Industrial Linux1(Debian9,kernel4.4),2027EOLMoxa Industrial Linux31(Debian11,kernel5.10),2031EOLSee /MILStorage Pre-installed8GB eMMCExpansion Slots MicroSD(SD3.0)socket x13OS is selectable via Moxa Computer Configuration System(CCS)for CTO models.For the model names,see the Ordering Information section of thedatasheet PDF file.Computer InterfaceEthernet Ports Auto-sensing10/100/1000Mbps ports(RJ45connector)x2 Serial Ports RS-232/422/485ports x2,software selectable(DB9male) CAN Ports CAN2.0A/B x1(DB9male)Digital Input DIs x4Digital Output DOs x4USB2.0USB2.0hosts x1,type-A connectorsWi-Fi Antenna Connector UC-8220Models:RP-SMA x2Cellular Antenna Connector UC-8220Models:SMA x2GPS Antenna Connector UC-8220Models:SMA x1Expansion Slots UC-8220-T-LX:mPCIe slot x2UC-8220-T-LX US/EU/AP Models:mPCIe slot x1SIM Format UC-8220Models:NanoNumber of SIMs UC-8220Models:2Buttons Programmable buttonTPM TPM v2.0Ethernet InterfaceMagnetic Isolation Protection 1.5kV(built-in)Security FunctionsHardware-based Security TPM2.0Hardware Root of Trust Secure BootIntrusion Detection Host-based Intrusion DetectionSecurity Tools Security Diagnostic ToolSecurity Event AuditingSecure UpdateDisk Protection LUKS Disk EncryptionRecovery One-step recovery to the last known secure stateDual-system design with automatic failbackReliability Network Keep AliveNetwork Failover and FailbackSerial InterfaceBaudrate300bps to921.6kbpsData Bits7,8Stop Bits1,2Parity None,Even,Odd,Space,MarkFlow Control RTS/CTS,XON/XOFFADDC(automatic data direction control)for RS-485RTS Toggle(RS-232only)Console Port1x4-pin header to DB9console portRS-232TxD,RxD,RTS,CTS,DTR,DSR,DCD,GNDRS-422Tx+,Tx-,Rx+,Rx-,GNDRS-485-2w Data+,Data-,GNDCAN InterfaceNo.of Ports1Connector DB9maleBaudrate10to1000kbpsIndustrial Protocols CAN2.0ACAN2.0BIsolation2kV(built-in)Signals CAN_H,CAN_L,CAN_GND,CAN_SHLD,CAN_V+,GNDDigital InputsConnector Screw-fastened Euroblock terminalDry Contact Off:openOn:short to GNDIsolation3K VDCSensor Type Wet contact(NPN)Dry contactWet Contact(DI to COM)On:10to30VDCOff:0to3VDCDigital OutputsConnector Screw-fastened Euroblock terminalCurrent Rating200mA per channelI/O Type SinkVoltage24VDC nominal,open collector to30VDCCellular InterfaceCellular Standards LTE Cat.4Band Options US Models:LTE Band2(1900MHz)/LTE Band4(1700MHz)/LTE Band5(850MHz)/LTE Band13(700MHz)/LTE Band17(700MHz)UMTS/HSPA850MHz/1900MHzCarrier Approval:Verizon,AT&TEU Models:LTE Band1(2100MHz)/LTE Band3(1800MHz)/LTE Band5(850MHz)/LTE Band7(2600MHz)/LTE Band8(900MHz)/LTE Band20(800MHz)UMTS/HSPA850MHz/900MHz/1900MHz/2100MHzAP Models:LTE Band1(2100MHz)/LTE Band3(1800MHz)/LTE Band5(850MHz)/LTE Band7(2600MHz)/LTE Band8(900MHz)/LTE Band28(700MHz)UMTS/HSPA850MHz/900MHz/1900MHz/2100MHzReceiver Types GPS/GLONASS/GalileoState-of-the-art GNSS solutionAccuracy Position:2.0m@CEP50Acquisition Hot starts:1.1secCold starts:29.94secSensitivity Cold starts:-145dBmTracking:-160dBmTime Pulse0.25Hz to10MHzLED IndicatorsSystem Power x2Programmable x1SIM card indicator x1Wireless Signal Strength Cellular/Wi-Fi x6Power ParametersNo.of Power Inputs Redundant dual inputsInput Voltage12to48VDCPower Consumption10WInput Current0.8A@12VDCReliabilityAlert Tools External RTC(real-time clock)Automatic Reboot Trigger External WDT(watchdog timer)Physical CharacteristicsDimensions UC-8220Models:141.5x120x39mm(5.7x4.72x1.54in)UC-8210Models:141.5x120x27mm(5.7x4.72x1.06in)141.5x120x27mm(5.7x4.72x1.06in)Weight UC-8210Models:560g(1.23lb)UC-8220Models:750g(1.65lb)Housing SECCMetalIP Rating IP30Installation DIN-rail mountingWall mounting(with optional kit)Environmental LimitsOperating Temperature-40to70°C(-40to158°F)Storage Temperature(package included)-40to85°C(-40to185°F)Ambient Relative Humidity5to95%(non-condensing)Shock IEC60068-2-27Vibration2Grms@IEC60068-2-64,random wave,5-500Hz,1hr per axis(without USB devicesattached)Standards and CertificationsEMC EN55032/35EN61000-6-2/-6-4EMI CISPR32,FCC Part15B Class AEMS IEC61000-4-2ESD:Contact:4kV;Air:8kVIEC61000-4-3RS:80MHz to1GHz:10V/mIEC61000-4-4EFT:Power:2kV;Signal:1kVIEC61000-4-6CS:10VIEC61000-4-8PFMFIEC61000-4-5Surge:Power:0.5kV;Signal:1kV Industrial Cybersecurity IEC62443-4-1IEC62443-4-2Hazardous Locations Class I Division2ATEXIECExCarrier Approvals VerizonAT&TSafety UL62368-1EN62368-1Green Product RoHS,CRoHS,WEEEMTBFTime UC-8210-T-LX-S:708,581hrsUC-8220-T-LX:650,836hrsUC-8220-T-LX-US-S/EU-S/AP-S:528,574hrs Standards Telcordia(Bellcore)Standard TR/SRWarrantyWarranty Period5yearsDetails See /warrantyPackage ContentsDevice1x UC-8200Series computerDocumentation1x quick installation guide1x warranty cardInstallation Kit1x DIN-rail kit(preinstalled)1x power jack6x M2.5mounting screws for the cellular module Cable1x console cableDimensions UC-8210UC-8220Ordering Information12UC-8210-T-LX-SDefault:MIL1(-Debian9),2027EOLOrder WithModel UC-8210-T-LX-S(CTO):MIL3(Debian11)Secure/Standard,2031EOLWith MIL3Secure1GHzDual CoreBuilt in––-40to85°CUC-8220-T-LXDefault:MIL1(-Debian9),2027EOLOrder WithModel UC-8220-T-LX(CTO):MIL3(Debian11)Secure/Standard,2031EOLWith MIL3Secure1GHzDual CoreBuilt in Reserved Reserved-40to70°CUC-8220-T-LX-US-SDefault:MIL1(-Debian9),2027EOLOrder WithModel UC-8220-T-LX-US-S(CTO):MIL3(Debian11)Secure/Standard,2031EOLWith MIL3Secure1GHzDual CoreBuilt inUS region LTEmodulepreinstalledReserved-40to70°CUC-8220-T-LX-EU-SDefault:MIL1(-Debian9),2027EOLOrder WithModel UC-8220-T-LX-EU-S(CTO):MIL3(Debian11)Secure/Standard,2031EOLWith MIL3Secure1GHzDual CoreBuilt inEurope regionLTE modulepreinstalledReserved-40to70°CUC-8220-T-LX-AP-SDefault:MIL1(-Debian9),2027EOLOrder WithModel UC-8220-T-LX-AP-S(CTO):MIL3(Debian11)Secure/Standard,2031EOLWith MIL3Secure1GHzDual CoreBuilt inAPAC regionLTE modulepreinstalledReserved-40to70°CUC-8210-T-LX-S(CTO)MIL3(Debian11)Secure orStandard,2031EOLWith MIL3Secure1GHzDual CoreBuilt in––-40to85°CUC-8220-T-LX(CTO)MIL3(Debian11)Secure orStandard,2031EOLWith MIL3Secure1GHzDual Core–Reserved Reserved-40to70°CUC-8220-T-LX-US-S (CTO)MIL3(Debian11)Secure orStandard,2031EOLWith MIL3Secure1GHzDual CoreBuilt inUS region LTEmodulepreinstalledReserved-40to70°C12UC-8220-T-LX-EU-S (CTO)MIL3(Debian11)Secure orStandard,2031EOLWith MIL3Secure1GHzDual CoreBuilt inEurope regionLTE modulepreinstalledReserved-40to70°CUC-8220-T-LX-AP-S (CTO)MIL3(Debian11)Secure orStandard,2031EOLWith MIL3Secure1GHzDual CoreBuilt inAPAC regionLTE modulepreinstalledReserved-40to70°CAccessories(sold separately)Power AdaptersPWR-12150-EU-SA-T Locking barrel plug,12VDC,1.5A,100to240VAC,EU plug,-40to75°C operating temperature PWR-12150-UK-SA-T Locking barrel plug,12VDC,1.5A,100to240VAC,UK plug,-40to75°C operating temperature PWR-12150-USJP-SA-T Locking barrel plug,12VDC1.5A,100to240VAC,US/JP plug,-40to75°C operating temperature PWR-12150-AU-SA-T Locking barrel plug,12VDC,1.5A,100to240VAC,AU plug,-40to75°C operating temperature PWR-12150-CN-SA-T Locking barrel plug,12VDC,1.5A,100to240VAC,CN plug,-40to75°C operating temperature Power WiringCBL-PJTB-10Non-locking barrel plug to bare-wire cableCablesCBL-F9DPF1x4-BK-100Console cable with4-pin connector,1mWi-Fi Wireless ModulesUC-8200-WLAN22-AC Wireless package for UC-8200V2.0or later with Wi-Fi module,2screws,2spacers,1heat sink,1pad AntennasANT-LTEUS-ASM-01GSM/GPRS/EDGE/UMTS/HSPA/LTE,1dBi,omnidirectional rubber-duck antennaANT-LTE-ASM-04BK704to960/1710to2620MHz,LTE omnidirectional stick antenna,4.5dBiANT-LTE-OSM-03-3m BK700-2700MHz,multiband antenna,specifically designed for2G,3G,and4G applications,3m cable ANT-LTE-ASM-05BK704-960/1710-2620MHz,LTE stick antenna,5dBiANT-LTE-OSM-06-3m BK MIMO Multiband antenna with screw-fastened mounting option for700-2700/2400-2500/5150-5850MHzfrequenciesANT-WDB-ARM-02022dBi at2.4GHz or2dBi at5GHz,RP-SMA(male),dual-band,omnidirectional antennaDIN-Rail Mounting KitsUC-8210DIN-rail Mounting Kit DIN-rail mounting kit for UC-8210with4M3screwsUC-8220DIN-rail Mounting Kit DIN-rail mounting kit for UC-8220with4M3screwsWall-Mounting KitsUC-8200Wall-mounting Kit Wall-mounting kit for UC-8200with4M3screws©Moxa Inc.All rights reserved.Updated Jul18,2023.This document and any portion thereof may not be reproduced or used in any manner whatsoever without the express written permission of Moxa Inc.Product specifications subject to change without notice.Visit our website for the most up-to-date product information.。

宏碁笔记本的技术参数

品牌宏碁 Acer型号AO531H-0CR颜色靓丽红平台Intel软件操作系统Linpus Linux BE 操作系统处理器CPU类型Atom凌动速度N270(1.60GHz)系统总线533MHz二级缓存512KB芯片组芯片组Intel 945GSE内存内存容量1GB内存类型DDR2 667插槽数量 1 x SO-DIMM最大支持容量2GB硬盘硬盘容量250GB转速5400转/分钟接口类型SATA 串行显卡类型集成显卡显示芯片Intel GMA950显存容量共享系统内存(集成)显示器屏幕尺寸10.1英寸显示比例宽屏物理分辨率1024 x 600屏幕类型LED背光特征丽镜宽屏,支持 Acer CrystalBrite技术光驱光驱类型无光驱通信调制解调器modem 无内置蓝牙无局域网10/100Mbps无线局域网802.11b/g无线模块内置3G 无端口PC卡插槽无USB 3 个IEEE 1394 无音频端口 1 x 麦克风接口; 1 x 音频接口显示端口VGA x 1音效系统扬声器双立体声音箱内置麦克风有输入设备键盘ASOne专用键盘,89%标准尺寸触摸板多触点触控板其它设备网络摄像头有摄像头像素30万指纹识别无读卡器 5 in 1读卡器电源电池3芯锂离子电池续航时间2-3小时, 具体时间视使用环境而定电源适配器100-240V自适应交流电源适配器机器规格尺寸255 (W) x 183 (D) x 19/26.9 (H) mm重量 1 kg(含3芯电池)特性特性描述支持Acer Recovery 还原管理软件电池x1 电源适配器x1 说明书x1本产品全国联保,享受三包服务,质保期为:三年有限质保,全球联保一年;笔记本电脑:整机三包有效期1年。

保修36个月的硬件包括:CPU、内存。

保修24个月的硬件包括:主板、显卡、LCD屏、硬盘、电源适配器、键盘、鼠标模块。

保修12个月的硬件包括:LCD之附件、光驱、DVD、CDR/W、软驱、Modem卡、网卡、摄像头等其余功能模块和部件。

莫加 UC 系列产品说明书

Entry-level Arm-based 64-bit ComputersDual-core, 2-GB RAMCompact Dual-core, 2-GB RAM Built-in LTEValue-added Arm-based 64-bit ComputersQuad-core, 4-GB RAMQuad-core, 4-GB RAM5G/CAN/serial IsolationBuilt-in LTEMoxa Industrial LinuxMoxa's Debian-based industrial-grade stable Linux distribution for long-term projectsFeatures and Benefits5Debian-based distribution that can use all standard Debian packages5Developed as per IEC 62443-4-1 and compliant with IEC 62443-4-2 industrialcybersecurity standards (Moxa Industrial Linux 3 Secure)5Long-term support until 2027 for Moxa Industrial Linux 1 and 2031 for MoxaIndustrial Linux 35Wireless connection management utility with automatic network keep alive andfailover5Ready-to-use APIs and library to ease access to hardware and I/O interfaces5Crash-free robust file system5Over-the air (OTA) software updatesWireless-ready Arm-based 32-bit Computers Built-in cellular or Wi-Fi module, RF type approvals, and carrier approvalsBuilt-in LTE Cat.1Built-in LTECat.1 and Wi-FiBuilt-in LTECat.1 and Wi-FiBuilt-in LTECat.4 with Wi-Fi expansion1. Wireless module is built-in. Refer to the Wireless Connection and Expansion Modules section for details.2. Wireless module must be purchased separately. Refer to the Wireless Connection and Expansion Modules section for details.1 mPCIe for cellular/Wi-Fi1 mPCIe forcellular/Wi-Fi1 mPCIe forcellular/Wi-Fi1 mPCIe forcellular/Wi-Fi1 mPCIe for cellular 1mPCIe for Wi-Fi1 mPCIe forcellular/Wi-FiArm-based 32-bit Computers With Wireless Options Flexibility to add cellular or Wi-Fi capability when needed1. Wireless module must be purchased separately. Refer to the Wireless Connection and Expansion Modules section for details.1 LAN,1 serial2 LAN 2 LAN,2 serial2 LAN,2 serial2 LAN,4 serial2 LAN,4 serial2 LAN,1 serial2 LAN,2 serial3 LAN,8 serialStandard Arm-based 32-bit Computers Low power consumption and small form factorWireless Connectivity and Expansion Modules* Details of cellular and Wi-Fi support with a list of wireless accessory models* Antennas must be purchased separatelyLast updated: Aug. 15, 2023. All specifications are subject to change without notice.。

芝加哥热点6系列60x60厨具,黑色HRG579BB6B说明书

Series 6, Built-in oven with addedsteam function, 60 x 60 cm, BlackHRG579BB6BIncluded accessories2 x combination grid, 1 x universal panOptional accessoriesHEZ317000 Pizza pan, enamelled, HEZ327000 Pizza stone,HEZ333001 Lid for professional pan, HEZ530000 Half tray,HEZ531000 Baking tray, enamelled, HEZ531010 Baking tray,non-stick ceramic coated, HEZ915003 Glass roasting dish, 5,4 L, HEZ532000 Multipurpose pan, enamelled, HEZ532010 Universal pan, non-stick ceramic coated, HEZ533000 Professional pan, enamelled, HEZ538000 1fold telescopic rail, level independent, HEZ629070 Air Fry & Grill tray, HEZ633001 Lid for professional pan, enamelled, HEZ633070 Professional pan, enamelled, HEZ634000 Baking and roasting grid (standard), HEZ636000 Glass pan, HEZ638000 Full ext rails, level independent, HEZ660050 Cover Strip, HEZ664000 Baking and roasting grid (steam)The built-in oven with added steam: achieve delicious baking results thanks to hotair steam heating mode.• AutoPilot 40: every dish is a perfect success thanks to 40 pre-set automatic programmes.• TFT display control: easy-to-use thanks to display with full text and symbols.• Pop-out controls: Make the front of the oven easy to clean and give it a sleek look.• Pyrolytic self-cleaning: Automatically cleans the oven, just wipe out the ash.• Cleaning Assistance: less cleaning effort thanks to the new cleaning option, which can be especially used for cleaning of light soiling.Technical DataInstallation type: ......................................................................Built-in Integrated Cleaning system: ................................Pyrolytic+Hydrolytic Min. required niche size for installation (HxWxD): 585-595 x 560-568 x 550 mmDimensions: ........................................................595 x 594 x 548 mm Dimensions of the packed product (HxWxD): .....675 x 690 x 660 mm Control Panel Material: ..............................................................Glass Door Material: ............................................................................Glass Net weight: ..............................................................................38.6 kg Usable volume of cavity: ...............................................................71 l Cooking method: .......Defrost, Full width grill, Hotair gentle, Hot Air, Intensive heat, Half width grill, Conventional heat, Pizza setting, low temperature cooking, Bottom heat, Hot air grilling, pre-heating, warmingFirst cavity material: ..................................................................Other Oven control: ......................................................................electronic Number of interior lights: .. (1)Length of electrical supply cord: ..........................................120.0 cm EAN code: (4242005332151)Number of cavities (2010/30/EC): (1)Energy efficiency rating: ....................................................................A Energy consumption per cycle conventional (2010/30/EC): ........0.99 kWh/cycleEnergy consumption per cycle forced air convection (2010/30/EC):0.81 kWh/cycleEnergy efficiency index (2010/30/EC): .....................................95.3 % Connection rating: ..................................................................2990 W Fuse protection: ...........................................................................13 A Voltage: ...............................................................................220-240 V Frequency: ...........................................................................50; 60 Hz Plug type: .....................no plug (electrical connection by electrician) Included accessories: .............2 x combination grid, 1 x universal panSeries 6, Built-in oven with addedsteam function, 60 x 60 cm, BlackHRG579BB6BThe built-in oven with added steam: achieve delicious baking results thanks to hotair steam heating mode.Features- Oven with 14 heating methods: 3D Hotair, conventional top and bottom heat, Hotair grilling, full width variable grill, half width grill, pizza function, bottom heat, intensive heat, low temperature cooking, defrost, plate warming, keep warm, Hotair gentle, hot air and steam combined- Temperature range 30 °C - 275 °C- Cavity volume: 71 litre capacityLevel independent telescopic rails- 5 shelf positions- Available as an additional accessoryDesign- Rotary dial, Retractable control dials, round- Extra large capacity oven with grey enamelCleaning- Pyrolytic self-cleaning function- Cleaning Assistance: hydrolyse manual- Full glass inner doorProgrammes/functions- BE54- Electronic clock timer- Digital temperature display with proposal- Actual temperature display Heating-up indicator AutoPilot Automatic start- AutoPilot, 40- Drop down door, SoftClose, SoftOpen- Straight bar handle- Automatic programmes- Fast pre-heating function- Interior halogen light, Light on/off when oven door opened/closed - Water bowl with a volume of 250 ml- Integral cooling fan- Info buttonAccessories- 2 x combination grid, 1 x universal panFeatures- Maximum window temperature 30° C- Low door temperature during pyrolitic cleaning- Electronic door lock- Control panel lock Automatic safety switch off Residual heat indicator Door contact switchTechnical information- 120 cm Cable length- Nominal voltage: 220 - 240 V- Total connected load electric: 2.99 KW - Energy efficiency rating (acc. EU Nr. 65/2014): A- Energy consumption per cycle in conventional mode:0.99 kWh- Energy consumption per cycle in fan-forced convection mode:0.81 kWh- Number of cavities: Main cavity Heat source: electrical Cavity volume:71 litre capacityPerformance/technical information- Appliance dimension (hxwxd): 595 mm x 594 mm x 548 mm- Niche dimension (hxwxd): 585 mm - 595 mm x 560 mm - 568 mm x 550 mm- Please refer to the dimensions provided in the installation manual - We recommend you to choose complementary products within SER6, in order to assure an optimal design combination of your Built-In appliances.。

AT25640B中文资料

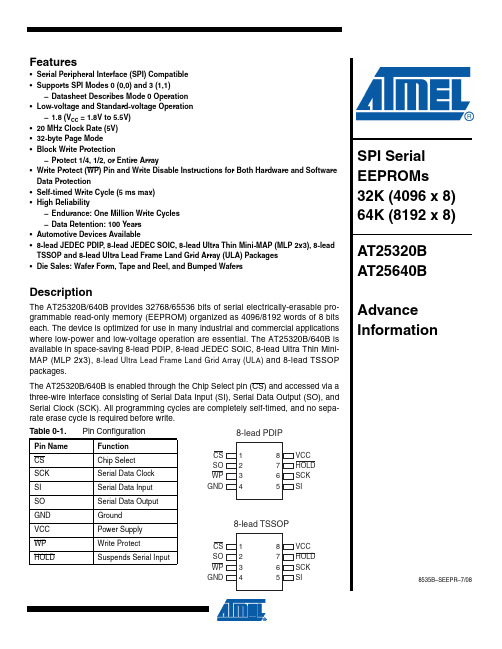

Features

• Serial Peripheral Interface (SPI) Compatible • Supports SPI Modes 0 (0,0) and 3 (1,1)

– Datasheet Describes Mode 0 Operation • Low-voltage and Standard-voltage Operation

Output Leakage Input Low-voltage Input High-voltage

VIN = 0V to VCC, TAC = 0°C to 70°C

–3.0 –0.6 VCC x 0.7

3.0

µA

VCC x 0.3

V

VCC + 0.5

V

VOL1 VOH1

Output Low-voltage 4.5V ≤ VCC ≤ 5.5V

2 AT25320B/640B

8535B–SEEPR–7/08

元器件交易网

Figure 0-1. Block Diagram

AT25320B/640B

Table 0-2. Pin Capacitance(1)

Applicable over recommended operating range from TA = 25°C, f = 1.0 MHz, VCC = +5.0V (unless otherwise noted)

Data Protection • Self-timed Write Cycle (5 ms max) • High Reliability

– Endurance: One Million Write Cycles – Data Retention: 100 Years • Automotive Devices Available • 8-lead JEDEC PDIP, 8-lead JEDEC SOIC, 8-lead Ultra Thin Mini-MAP (MLP 2x3), 8-lead TSSOP and 8-lead Ultra Lead Frame Land Grid Array (ULA) Packages • Die Sales: Wafer Form, Tape and Reel, and Bumped Wafers

ATMEGA2561V资料