KLS216中文资料

KU80L186EC16中文资料

CONTENTS

Recommended Connections DC SPECIFICATIONS ICC versus Frequency and Voltage PDTMR Pin Delay Calculation AC SPECIFICATIONS AC Characteristics 80C186EC25 AC Characteristics 80C186EC20 13 AC Characteristics 80L186EC13 AC Characteristics 80L186EC16 Relative Timings Serial Port Mode 0 Timings AC TEST CONDITIONS AC TIMING WAVEFORMS DERATING CURVES RESET BUS CYCLE WAVEFORMS EXECUTION TIMINGS INSTRUCTION SET SUMMARY ERRATA REVISION HISTORY

Y

Available in Extended Temperature Range ( b 40 C to a 85 C) Supports 80C187 Numerics Processor Extension (80C186EC only) Package Types 100-Pin EIAJ Quad Flat Pack (QFP) 100-Pin Plastic Quad Flat Pack (PQFP) 100-Pin Shrink Quad Flat Pack (SQFP) Speed Versions Available (5V) 25 MHz (80C186EC25 80C188EC25) 20 MHz (80C186EC20 80C188EC20) 13 MHz (80C186EC13 80C188EC13) Speed Version Available (3V) 16 MHz (80L186EC16 80L188EC16) 13 MHz (80L186EC13 80L188EC13)

RK16中文资料

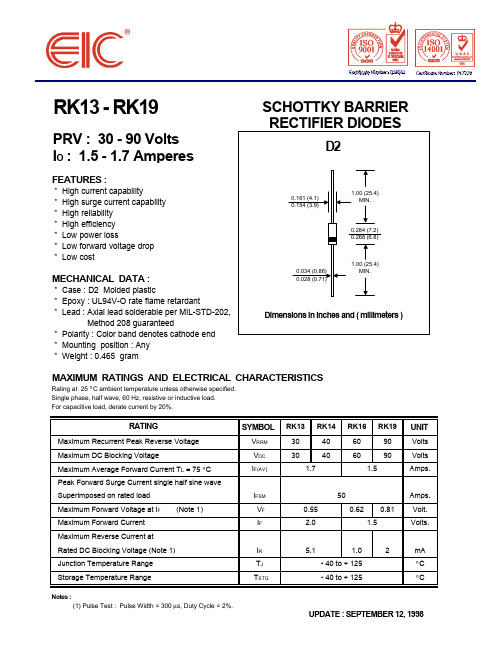

0.034 (0.86) 0.028 (0.71)

1.00 (25.4) MIN.

Dimensions in inches and ( millimeters )

MAXIMUM RATINGS AND ELECTRICAL CHARACTERISTICS

Rating at 25 ° C ambient temperature unless otherwise specified. Single phase, half wave, 60 Hz, resistive or inductive load. For capacitive load, derate current by 20%.

RK13 RK14

RK19

1.0

RK16 1.0

0.1

TJ = 25 °C

TJ = 25 °C PULSE WIDTH = 300µs DUTY CYCLE = 1% 0.1 0.1

0.01 0 20 40 60 80 100 120 140

0.3

0.5

0.7

0.9

1.1

1.3

1.5

1.7

1.9

2.1

RATING

Maximum Recurrent Peak Reverse Voltage Maximum DC Blocking Voltage Maximum Average Forward Current TL = 75 °C Peak Forward Surge Current single half sine wave Superimposed on rated load Maximum Forward Voltage at IF Maximum Forward Current Maximum Reverse Current at Rated DC Blocking Voltage (Note 1) Junction Temperature Range Storage Temperature Range

PSK1216-7-9中文资料

•RoHS lead solder exemption compliant •Efficiency up to 97%•L ow input-output differential voltage •No derating over temperatureSelection chartOutput Input voltageRated powerEfficiencyTypeOptionsV o nom I o nom V i P o tot h typ [VDC][A][VDC][W][%]3.3258 - 4082.582PSK 3E25-7-9, E, P, B, B15.1128 - 8061.279PSS 5A12-7-9, E, P , C, B, B15.1148 - 4071.483PSS 5A14-2B, B15.1168 - 8081.679PSK 5A16-7-9, E, P , C, B, B15.1188 - 4091.882PSK 5A18-2B, B15.1208 - 8010279PSK 5A20-7-9, E, P , C, B, B15.1258 - 40127.582PSK 5A25-7-9, E, P , C, B, B112 (15)1918 - 144108 (135)91PSS 129-7-9, E, P , C, B, B112 (15)11215 - 80144 (180)91PSS 1212-7-9, E, P , C, B, B112 (15)11218 - 144144 (180)91PSK 1212-7-9, E, P , C, B, B112 (15)11416 - 40168 (210)90PSS 1214-2B, B112 (15)11615 - 80192 (240)90PSK 1216-7-9, E, P , C, B, B112 (15)11816 - 40216 (270)90PSK 1218-2B, B112 (15)12015 - 80240 (300)90PSK 1220-7-9, E, P , C, B, B124931 - 14421694PSS 249-7-9, E, P, C, B, B1241229 - 8028894PSS 2412-7-9, E, P, C, B, B1241231 - 14428894PSK 2412-7-9, E, P, C, B, B1241429 - 6033694PSS 2414-2B, B1241629 - 8038494PSK 2416-7-9, E, P, C, B, B1241829 - 6043294PSK 2418-2B, B1242029 - 8048094PSK 2420-7-9, E, P, C, B, B136944 - 14432496PSS 369-7-9, E, P, C, B, B1361242 - 8043296PSS 3612-7-9, E, P, C, B, B1361244 - 14443296PSK 3612-7-9, E, P, C, B, B1361642 - 8057695PSK 3616-7-9, E, P, C, B, B1362042 - 8072095PSK 3620-7-9, E, P, C, B, B148958 - 14443297PSS 489-7-9, E, P, C, B, B1481258 - 14457697PSK 4812-7-9, E, P, C, B, B11 These converters (V o nom = 12 V) can be adjusted to 15 V using the R-control input.InputInput voltage refer to selection chart No load input current≤ 50 mAOutputEfficiency V i nom, I o nom up to 97%i nom o nom o nom Output voltage switching noise IEC/EN 61204, total typ. 0.2% L ine regulation V i min - V i max, I o nom typ. ±0.2% L oad regulation V i nom, 0 - I o nom typ. 0.15% Minimum load not required0 A Current limitation rectangular U/I characteristic typ. 110% I o nom Hold-up time V i nom, I o nom, with ext. diode in input line, PSS up to 7 ms ProtectionInput reverse polarity built-in fusei min Input transient protection suppressor diodeOutput overvoltage suppressor diode in each output typ. 150% V o nomCControlInhibit TTL input, output enabled if left openR control min. adjustable output voltage0 Vo nom Output voltage indication LED (except -2)Test sockets test sockets for check of output voltageOperation in parallel current sharing feature (CS)SafetyApprovals EN 60950, UL 1950, CSA C22.2 No. 950Electric strength test voltage I/case and O/case500/750/1500 VDCEMCElectrostatic discharge IEC/EN 61000-4-2Electromagnetic field IEC/EN 61000-4-3Electr. fast transients/bursts IEC/EN 61000-4-4Surge IEC/EN 61000-4-5Electromagnetic emissions CISPR 22/EN 55022EnvironmentalOperating ambient temperature-2, V i nom, I o nom, convection cooled–10 to 50°C Operating case temperature T C-2, V i nom, I o nom–10 to 80°C Operating ambient temperature-7, V i nom, I o nom, convection cooled–25 to 71°CC i nom o nomStorage temperature-7, non operational–40 to 100°C Vibration, sinusoidal IEC/EN 60068-2-6Bump IEC/EN 60068-2-29MTBF MIL-HDBK-217OptionsLarge and small cooling plate instead of standard heatsink B/B1 Extended temperature range–40 to 71°C, ambient, operating-9 Output voltage adjustment±8% V o nom, excludes feature R and vice versa P Thyristor crowbar on output CAccessoriesFront panels 19" (Schroff/Intermas), 12 und 16 TEMating H15 or H15 S4 connectors with screw, solder, fast-on or press-fit terminalsAdapter kit for DIN-railPin allocationElectrical Determination Type H15Type H15 S4Pin No.Ident.Pin No.Ident. Output voltage (positive)4Vo+4/6Vo+ Output voltage (positive)6Vo+Output voltage (negative)8Go–8/10Go–Output voltage (negative)10Go–Crowbar trigger input (option C)12C12CInhibit input14i14iR-input (output voltage programming) 116R16RSense line (negative)18S–18S–Sense line (positive)20S+20S+ Current sharing control input22CS22CS Protective ground (leading pin)2424Input voltage (negative)26Gi–26/28Gi–Input voltage (negative)28Gi–Input voltage (positive)30Vi+30/32Vi+Input voltage (positive)32Vi+32 28 24 20 16 12 8 4Connector type H15S1001030 26 22 18 14 106H15 S4 connectors for 20 and 25 A typesMechanical dataTolerances ±0.3 mm (0.012") unless otherwise indicated.European ProjectionPSKPin allocationPSSNUCLEAR AND MEDICAL APPLICATIONS - Power-One products are not authorized for use as critical components in life support systems, equipment used in hazardous environments, or nuclear control systems without the express written consent of the respective divisional president of Power-One, Inc.TECHNICAL REVISIONS - The appearance of products, including safety agency certifications pictured on labels, may change depending on the date manufactured. Specifications are subject to change without notice.。

S216S02中文资料

600

Critical rate of rise of ON-state current dIT/dt

50

A/µs

Operating frequency

f

45 to 65 Hz

*1Isolation voltage

Viso(rms) 4.0

kV

Operating temperature Storage temperature *2Soldering temperature

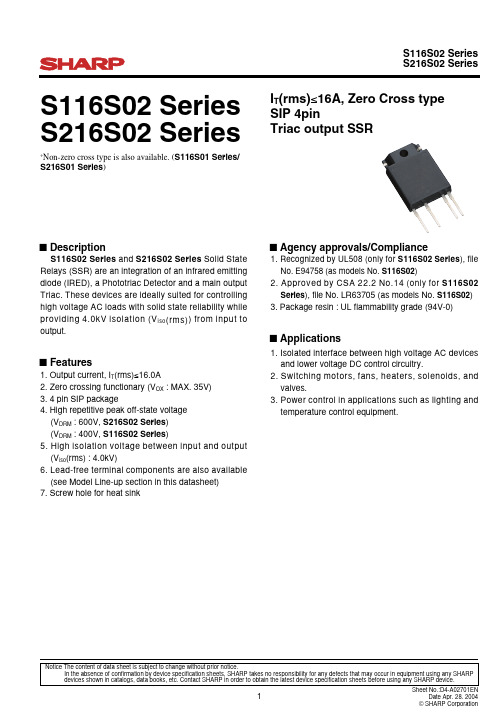

■ Features

1. Output current, IT(rms)≤16.0A 2. Zero crossing functionary (VOX : MAX. 35V) 3. 4 pin SIP package 4. High repetitive peak off-state voltage

3. Package resin : UL flammability grade (94V-0)

■ Applications

1. Isolated interface between high voltage AC devices and lower voltage DC control circuitry.

Thermal resistance

Rth(j-c) Rth(j-a)

Between junction and case Between junction and ambient

MIN. − − − − − 30 5 −

1010 −

−

−

−

−

− −

TYP. 1.2 − − − − − − − − −

■ Absolute Maximum Ratings

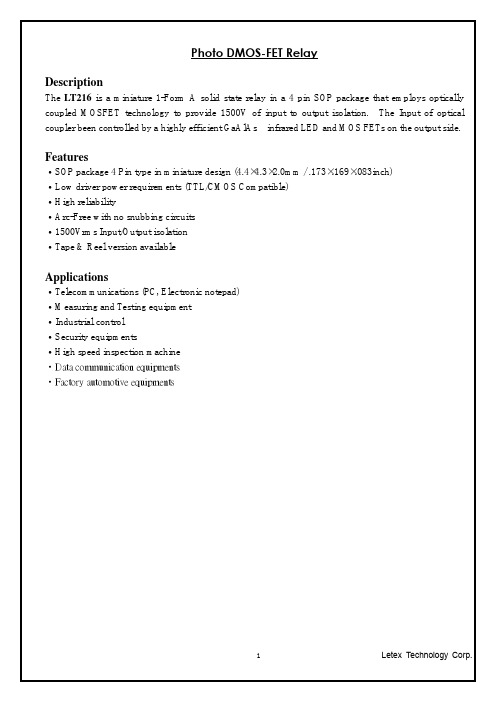

LT216中文资料

1

Letex Technology Corp.

元器件交易网

Photo DMOS-FET Relay Specifications

Part Name: LT216 (Load voltage:20V / Load current: AC:1.7A) Absolute Maximum Ratings (Ambient Temperature: 25℃) Item Symbol Value Continuous LED Current Input Peak LED Current IF IFP VR PIn VL IL IPeak Pout PT VI/O TOpr TStg TSol 50 1000 5 75 20 1.7 35 1.8 2 1500 -40 to +85 -40 to +100 260

Applied voltage (V)

4

Letex Technology Corp.

பைடு நூலகம்

元器件交易网

Taping Specifications for Surface Mount Devices

Label sticking position

Direction of feed

Unit : mm

Recommended Mounting Pad

(Top view)

Marking

(Each photo MOS Relay shall be marked with the following information)

Brand Name

Letex

LT216

162

Date Code Part Name

1.5

20

1.0

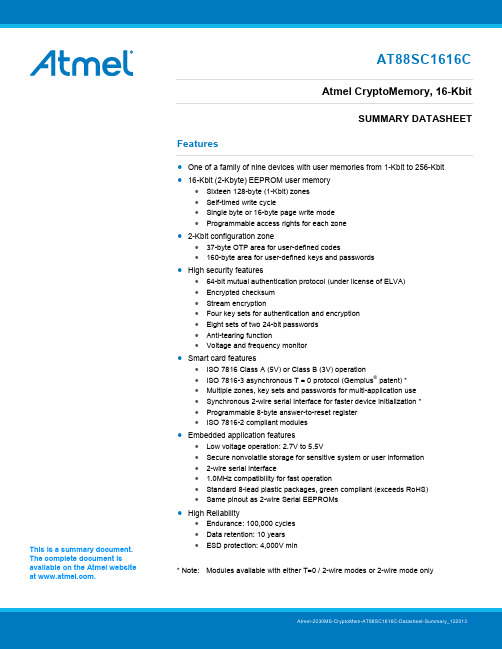

AT88SC1616C Atmel CryptoMemory 16K 位安全电器记忆晶体管数据手册说

AT88SC1616CAtmel CryptoMemory, 16-KbitSUMMARY DATASHEETFeatures • One of a family of nine devices with user memories from 1-Kbit to 256-Kbit •16-Kbit (2-Kbyte) EEPROM user memory• Sixteen 128-byte (1-Kbit) zones • Self-timed write cycle• Single byte or 16-byte page write mode • Programmable access rights for each zone• 2-Kbit configuration zone• 37-byte OTP area for user-defined codes• 160-byte area for user-defined keys and passwords •High security features• 64-bit mutual authentication protocol (under license of ELVA) • Encrypted checksum • Stream encryption• Four key sets for authentication and encryption • Eight sets of two 24-bit passwords • Anti-tearing function• Voltage and frequency monitor•Smart card features• ISO 7816 Class A (5V) or Class B (3V) operation• ISO 7816-3 asynchronous T = 0 protocol (Gemplus ®patent) * • Multiple zones, key sets and passwords for multi-application use • Synchronous 2-wire serial interface for faster device initialization * • Programmable 8-byte answer-to-reset register •ISO 7816-2 compliant modules•Embedded application features• Low voltage operation: 2.7V to 5.5V• Secure nonvolatile storage for sensitive system or user information • 2-wire serial interface• 1.0MHz compatibility for fast operation• Standard 8-lead plastic packages, green compliant (exceeds RoHS) •Same pinout as 2-wire Serial EEPROMs•High Reliability• Endurance: 100,000 cycles• Data retention: 10 years • ESD protection: 4,000V min* Note: Modules available with either T=0 / 2-wire modes or 2-wire mode onlyT his is a summary document. The complete document is available on the Atmel website at .AT88SC1616C [SUMMARY DATASHEET]Atmel-2030MS-CryptoMem-AT88SC1616C-Datasheet-Summary_1220132Table 1. Pin AssignmentFigure 1.Pin Configuration1. DescriptionThe Atmel ®AT88SC1616C member of the Atmel CryptoMemory ®family is a high-performance secure memory providing 16-Kbits of user memory with advanced security and cryptographic features built in. The user memory is divided into 16 128-byte zones, each of which may be individually set with different security access rights or effectively combined together to provide space for 1 to 16 data files.1.1 Smart Card ApplicationsThe AT88SC1616C provides high security, low cost, and ease of implementation without the need for a microprocessor operating system. The embedded cryptographic engine provides for dynamic and symmetric mutual authentication between the device and host, as well as performing stream encryption for all data and passwords exchanged between the device and host. Up to four unique key sets may be used for these operations. The AT88SC1616C offers the ability to communicate with virtually any smart card reader using the asynchronous T = 0 protocol (Gemplus patent) defined in ISO 7816-3.1.2 Embedded ApplicationsThrough dynamic and symmetric mutual authentication, data encryption, and the use of encrypted checksums, theAT88SC1616C provides a secure place for storage of sensitive information within a system. With its tamper detection circuits, this information remains safe even under attack. A 2-wire serial interface running at 1.0MHz is used for fast and efficientcommunications with up to 15 devices that may be individually addressed. The AT88SC1616C is available in industry standard 8-lead packages with the same familiar pinout as 2-wire serial EEPROMs.V CC =C1RST=C2SCL/CLK=C3NC=C4ISO Smart Card ModuleC5=GND C6=NC C7=SDA/IO C8=NCNC NC NCGND123487658-lead SOIC, PDIP V CC NC SCL SDAV CC =C1NC=C2SCL/CLK=C3NC=C4TWI Smart Card Module C5=GND C6=NC C7=SDA/IO C8=NCAT88SC1616C [SUMMARY DATASHEET]Atmel-2030MS-CryptoMem-AT88SC1616C-Datasheet-Summary_1220133Figure 1-1. Block Diagram2.Pin Descriptions2.1Supply Voltage (V CC )The V CC input is a 2.7V to 5.5V positive voltage supplied by the host.2.2 Clock (SCL/CLK)In the asynchronous T = 0 protocol, the SCL/CLK input is used to provide the device with a carrier frequency f . The nominal length of one bit emitted on I/O is defined as an “elementary time unit” (ETU) and is equal to 372/f . When the synchronous protocol is used, the SCL/CLK input is used to positive edge clock data into the device and negative edge clock data out of the device.2.3 Reset (RST)The AT88SC1616C provides an ISO 7816-3 compliant asynchronous answer to reset sequence. When the reset sequence is activated, the device will output the data programmed into the 64-bit answer-to-reset register. An internal pull-up on the RST input pad allows the device to be used in synchronous mode without bonding RST. The AT88SC1616C does not support the synchronous answer-to-reset sequence.2.4 Serial Data (SDA/IO)The SDA pin is bidirectional for serial data transfer. This pin is open-drain driven and may be wired with any number of other open drain or open collector devices. An external pull-up resistor should be connected between SDA and V CC . The value of this resistor and the system capacitance loading the SDA bus will determine the rise time of SDA. This rise time will determine the maximum frequency during read operations. Low value pull-up resistors will allow higher frequency operations while drawing higher average power. SDA/IO information applies to both asynchronous and synchronous protocols.When the synchronous protocol is used, the SCL/CLK input is used to positive edge clock data into the device and negative edge clock data out of the device.V CCAT88SC1616C [SUMMARY DATASHEET]Atmel-2030MS-CryptoMem-AT88SC1616C-Datasheet-Summary_12201343.*Notice:Stresses beyond those listed under “AbsoluteMaximum Ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other condition beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect device reliability.Table 3-1.DC CharacteristicsNotes: 1. V IL min and V IH max are reference only and are not tested2. To prevent latch up conditions from occurring during power up of the AT88SCxxxxC, V CC must be turned onbefore applying V IH . For powering down, V IH must be removed before turning V CC offAT88SC1616C [SUMMARY DATASHEET]Atmel-2030MS-CryptoMem-AT88SC1616C-Datasheet-Summary_1220135Table 3-2.AC CharacteristicsApplicable over recommended operating range from V CC = +2.7 to 5.5V, T AC = -40°C to +85°C, CL = 30pF4. Device Operation for Synchronous ProtocolsClock and Data Transitions:The SDA pin is normally pulled high with an external device. Data on the SDA pin may change only during SCL low time periods (see Figure 4-3 on page 7). Data changes during SCL high periods will indicate a start or stop condition as defined below.Start Condition:A high-to-low transition of SDA with SCL high is a start condition which must precede any other command (see Figure 4-4 on page 7).Stop Condition:A low-to-high transition of SDA with SCL high is a stop condition. After a read sequence, the stop command will place the EEPROM in a standby power mode (see Figure 4-4 on page 7).Acknowledge:All addresses and data words are serially transmitted to and from the EEPROM in 8-bit words. The EEPROM sends a zero to acknowledge that it has received each word. This happens during the ninth clock cycle (see Figure 4-5 on page 7). Memory Reset:After an interruption in protocol, power loss or system reset, any 2-wire part can be reset by following these steps: 1. Clock up to nine cycles2. Look for SDA high in each cycle while SCL is high3. Create a start conditionAT88SC1616C [SUMMARY DATASHEET] Atmel-2030MS-CryptoMem-AT88SC1616C-Datasheet-Summary_1220136 Figure 4-1. Bus Timing for 2-wire CommunicationsSCL: Serial Clock, SDA – Serial Data I/OFigure 4-2. Write Cycle Timing: SCLSerial Clock, SDA – Serial Data I/ONote: The write cycle time t WR is the time from a valid stop condition of a write sequence to the end of the internalclear/write cycleSCLSDA INSDA OUTSTOPCONDITIONSTARTCONDITIONSCLSDAAT88SC1616C [SUMMARY DATASHEET]Atmel-2030MS-CryptoMem-AT88SC1616C-Datasheet-Summary_1220137Figure 4-3. Data ValidityFigure 4-4. Start and Stop DefinitionsFigure 4-5. Output AcknowledgeDATA CHANGE ALLOWEDDATA STABLEDATA STABLESDASCLSDASCLSTART STOPSCLDAT A INDAT A OUTEG D E L W O N K C A T R A T S 981AT88SC1616C [SUMMARY DATASHEET]Atmel-2030MS-CryptoMem-AT88SC1616C-Datasheet-Summary_12201385.Device Architecture5.1User ZonesThe EEPROM user memory is divided into 16 zones of 1024 bits each. Multiple zones allow for different types of data or files to be stored in different zones. Access to the user zones is allowed only after security requirements have been met. These security requirements are defined by the user during the personalization of the device in the configuration memory. If the same security requirements are selected for multiple zones, then these zones may effectively be accessed as one larger zone.6. Control LogicAccess to the user zones occurs only through the control logic built into the device. This logic is configurable through access registers, key registers and keys programmed into the configuration memory during device personalization. Also implemented in the control logic is a cryptographic engine for performing the various higher-level security functions of the device.AT88SC1616C [SUMMARY DATASHEET]Atmel-2030MS-CryptoMem-AT88SC1616C-Datasheet-Summary_12201397. Configuration MemoryThe configuration memory consists of 2048 bits of EEPROM memory used for storing passwords, keys and codes and for defining security levels to be used for each user zone. Access rights to the configuration memory are defined in the control logic and may not be altered by the user.AT88SC1616C [SUMMARY DATASHEET]Atmel-2030MS-CryptoMem-AT88SC1616C-Datasheet-Summary_122013108. Security FusesThere are three fuses on the device that must be blown during the device personalization process. Each fuse locks certain portions of the configuration memory as OTP memory. Fuses are designed for the module manufacturer, card manufacturer and card issuer and should be blown in sequence, although all programming of the device and blowing of the fuses may be performed at one final step.9. Protocol SelectionThe AT88SC1616C supports two different communication protocols.• Smart Card Applications:The asynchronous T = 0 protocol defined by ISO 7816-3 is used for compatibility with the industry’s standard smart card readers• Embedded Applications:A 2-wire serial interface is used for fast and efficient communication with logic or controllersThe power-up sequence determines which of the two communication protocols will be used.9.1 Asynchronous T = 0 ProtocolThis power-up sequence complies with ISO 7816-3 for a cold reset in smart card applications.• V CC goes high; RST, I/O-SDA and CLK-SCL are low • Set I/O-SDA in receive mode • Provide a clock signal to CLK-SCL •RST goes high after 400 clock cyclesThe device will respond with a 64-bit ATR code, including historical bytes to indicate the memory density within theCryptoMemory family. Once the asynchronous mode has been selected, it is not possible to switch to the synchronous mode without powering off the device.Figure 9-1. Asynchronous T = 0 Protocol (Gemplus Patent)V cc I/O-SDARSTCLK-SCL9.2 Synchronous 2-wire Serial InterfaceThe synchronous mode is the default after powering up V CC due to an internal pull-up on RST. For embedded applications using CryptoMemory in standard plastic packages, this is the only communication protocol.• Power-up V CC , RST goes high also• After stable V CC , CLK-SCL and I/O-SDA may be drivenFigure 9-2. Synchronous 2-wire ProtocolNote:Five clock pulses must be sent before the first command is issued10. Communication Security ModesCommunications between the device and host operate in three basic modes. Standard mode is the default mode for the device after power-up. Authentication mode is activated by a successful authentication sequence. Encryption mode is activated by a successful encryption activation following a successful authentication. Table 10-1. Communication Security Modes (1)Notes: 1. Configuration data include viewable areas of the configuration zone except the passwords:• MDC: Modification Detection Code •MAC: Message Authentication CodeV cc I/O-SDARST CLK-SCL1234511. Security Options11.1 Anti-tearingIn the event of a power loss during a write cycle, the integrity of the device’s stored data may be recovered. This function is optional – the host may choose to activate the anti-tearing function, depending on application requirements. When anti-tearing is active, write commands take longer to execute, since more write cycles are required to complete them, and data are limited to eight bytes.Data are written first to a buffer zone in EEPROM instead of the intended destination address, but with the same accessconditions. The data are then written in the required location. If this second write cycle is interrupted due to a power loss, the device will automatically recover the data from the system buffer zone at the next power-up.In 2-wire mode, the host is required to perform ACK polling for up to 8mS after write commands when anti-tearing is active. At power-up, the host is required to perform ACK polling, in some cases for up to 2mS, in the event that the device needs to carry out the data recovery process.11.2 Write LockIf a user zone is configured in the write lock mode, the lowest address byte of an 8-byte page constitutes a write access byte for the bytes of that page.Example: The write lock byte at $080 controls the bytes from $080 to $087Table 11-1. Write Lock ExampleThe write lock byte may also be locked by writing its least significant (rightmost) bit to “0”. Moreover, when write lock mode is activated, the write lock byte can only be programmed – that is, bits written to “0” cannot return to “1”. In the write lockconfiguration, only one byte can be written at a time. Even if several bytes are received, only the first byte will be taken into account by the device.12. Password VerificationPasswords may be used to protect read and/or write access of any user zone. When a valid password is presented, it ismemorized and active until power is turned off, unless a new password is presented or RST becomes active. There are eight password sets that may be used to protect any user zone. Only one password is active at a time, but write passwords give read access also.12.1 Authentication ProtocolThe access to a user zone may be protected by an authentication protocol. Any one of four keys may be selected to use with a user zone.The authentication success is memorized and active as long as the chip is powered, unless a new authentication is initialized or RST becomes active. If the new authentication request is not validated, the card loses its previous authentication and itshould be presented again. Only the last request is memorized.Note: Password and authentication may be presented at any time and in any order. If the trials limit has been reached (after four consecutive incorrect attempts), the password verification or authentication process will not be takeninto accountFigure 12-1. Password and Authentication Operations12.2 ChecksumThe AT88SC1616C implements a data validity check function in the form of a checksum, which may function in standard,authentication or encryption modes.In the standard mode, the checksum is implemented as a Modification Detection Code (MDC), in which the host may read an MDC from the device in order to verify that the data sent was received correctly.In the authentication and encryption modes, the checksum becomes more powerful since it provides a bidirectional dataintegrity check and data origin authentication capability in the form of a Message Authentication Code (MAC). Only thehost/device that carried out a valid authentication is capable of computing a valid MAC. While operating in the authentication or encryption modes, the use of a MAC is required. For an ingoing command, if the device calculates a MAC different from the MAC transmitted by the host, not only is the command abandoned but the mode is also reset. A new authentication and/or encryption activation will be required to reactivate the MAC.12.3 EncryptionThe data exchanged between the device and the host during read, write and verify password commands may be encrypted to ensure data confidentiality.The issuer may choose to require encryption for a user zone by settings made in the configuration memory. Any one of four keys may be selected for use with a user zone. In this case, activation of the encryption mode is required in order to read/write data in the zone and only encrypted data will be transmitted. Even if not required, the host may elect to activate encryption provided the proper keys are known.12.4 Supervisor ModeEnabling this feature allows the holder of one specific password to gain full access to all eight password sets, including the ability to change passwords.12.5 Modify ForbiddenNo write access is allowed in a user zone protected with this feature at any time. The user zone must be written during device personalization prior to blowing the security fuses.12.6 Program OnlyFor a user zone protected by this feature, data within the zone may be changed from a “1” to a “0”, but never from a “0” to a “1”.13. Initial Device ProgrammingTo enable the security features of CryptoMemory, the device must first be personalized to set up several registers and load in the appropriate passwords and keys. This is accomplished through programming the configuration memory of CryptoMemory using simple write and read commands. To gain access to the configuration memory, the secure code must first besuccessfully presented. For the AT88SC1616C device, the secure code is $20 0C E0. After writing and verifying data in the configuration memory, the security fuses must be blown to lock this information in the device. For additional information on personalizing CryptoMemory, please see the application notes Programming CryptoMemory for Embedded Applications and Initializing CryptoMemory for Smart Card Applications (at ).Notes: 1. Formal drawings may be obtained from an Atmel sales office2. Both the J and P module packages are used for either ISO (T=0 / 2-wire mode) or TWI (2-wire mode only)Ordering Code: MJ or MJTG Ordering Code: MP or MPTGModule Size: M2Dimension*: 12.6 x 11.4 [mm] Glob Top: Round - ∅ 8.5 [mm] Thickness: 0.58 [mm]Pitch: 14.25mm Module Size: M2Dimension*: 12.6 x 11.4 [mm]Glob Top: Square - 8.8 x 8.8 [mm] Thickness: 0.58 [mm]Pitch: 14.25mmNote: *The module dimensions listed refer to the dimensions of the exposed metal contact area. The actual dimensions of the module after excise or punching from the carrier tape are generally 0.4mm greater in both directions(i.e., a punched M2 module will yield 13.0 x 11.8mm)15.1 Atmel AT88SC1616C Package Marking Information8S1 – 8-lead JEDEC SOIC8P3 – 8-lead PDIP16. Revision History。

KSC1623中文资料

KSC1623NPN Epitaxial Silicon TransistorAbsolute Maximum Ratings T a =25°C unless otherwise notedElectrical Characteristics T a =25°C unless otherwise notedh FE ClassificationSymbol ParameterRatings Units V CBO Collector-Base Voltage 60V V CEO Collector-Emitter Voltage 50V V EBO Emitter-Base Voltage 5V I C Collector Current100mA P C Collector Power Dissipation 200mW T J Junction Temperature 150°C T STGStorage Temperature-55 ~ 150°CSymbol ParameterTest Condition Min.Typ.Max.Units I CBO Collector Cut-off Current V CB =60V, I E =00.1µA I EBO Emitter Cut-off Current V EB =5V, I C =00.1µAh FE DC Current GainV CE =6V, I C =1mA 90200600V CE (sat)Collector-Emitter Saturation Voltage I C =100mA, I B =10mA0.150.3V V BE (sat)Base-Emitter Saturation Voltage I C =100mA, I B =10mA 0.861.0V V BE (on)Base-Emitter On Voltage V CE =6V, I C =1mA 0.550.620.65V f T Current Gain Bandwidth Product V CE =6V, I C =10mA 250MHz C obOutput CapacitanceV CB =6V, I E =0, f=1MHz3pF Classification OY G L h FE90 ~ 180135 ~ 270200 ~ 400300 ~ 6001. Base2. Emitter3. CollectorKSC1623Low Frequency Amplifier & High Frequency OSC.•Complement to KSA812C1OMarkingh FE gradeSOT-23123KSC1623KSC1623TRADEMARKSThe following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.DISCLAIMERFAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN;NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.As used herein:1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body,or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.PRODUCT STATUS DEFINITIONS Definition of TermsDatasheet Identification Product Status DefinitionAdvance InformationFormative or In Design This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.PreliminaryFirst ProductionThis datasheet contains preliminary data, andsupplementary data will be published at a later date.Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design.No Identification Needed Full ProductionThis datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design.Obsolete Not In ProductionThis datasheet contains specifications on a product that has been discontinued by Fairchild semiconductor.The datasheet is printed for reference information only.FACT™FACT Quiet series™FAST ®FASTr™FRFET™GlobalOptoisolator™GTO™HiSeC™I 2C™ImpliedDisconnect™ISOPLANAR™LittleFET™MicroFET™MicroPak™MICROWIRE™MSX™MSXPro™OCX™OCXPro™OPTOLOGIC ®OPTOPLANAR™PACMAN™POP™Power247™PowerTrench ®QFET™QS™QT Optoelectronics™Quiet Series™RapidConfigure™RapidConnect™SILENT SWITCHER ®SMART START™SPM™Stealth™SuperSOT™-3SuperSOT™-6SuperSOT™-8SyncFET™TinyLogic™TruTranslation™UHC™UltraFET ®VCX™ACEx™ActiveArray™Bottomless™CoolFET™CROSSVOLT ™DOME™EcoSPARK™E 2CMOS™EnSigna™Across the board. Around the world.™The Power Franchise™Programmable Active Droop™。

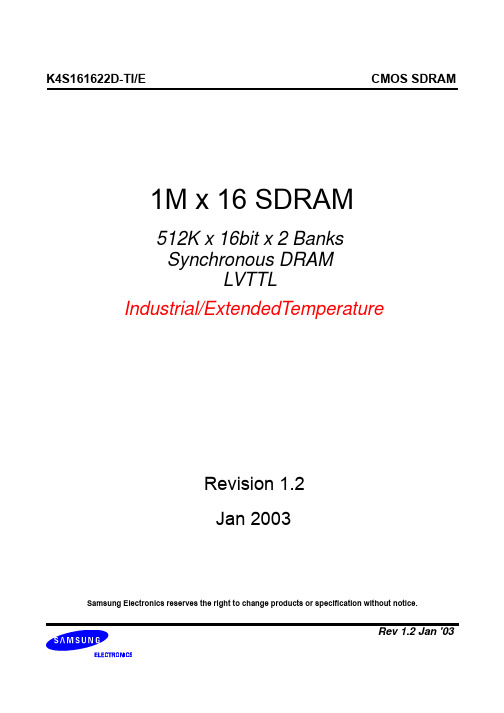

K4S161622D-LE10中文资料

K4S161622D-TI/E CMOS SDRAM1M x 16 SDRAM512K x 16bit x 2 BanksSynchronous DRAMLVTTLIndustrial/ExtendedTemperatureRevision 1.2Jan 2003Samsung Electronics reserves the right to change products or specification without notice.Rev 1.2 Jan '03K4S161622D-TI/E CMOS SDRAM Revision HistoryRevision 1.0 (June 1999)• Define Industrial Temperature spec of K4S161622DRevision 1.1 (June 2001)• Add Industrial Temperature Specification.Revision 1.2 (Jan 2003)• Changed VDD condition of High speed (over 166MHz) from 3.135V~ 3.6V to 3.0V ~ 3.0V.Rev 1.2 Jan '03K4S161622D-TI/E CMOS SDRAMRev 1.2 Jan '03K4S161622D-TI/ECMOS SDRAMRev 1.2 Jan '03V DD DQ0DQ1V SSQ DQ2DQ3V DDQ DQ4DQ5V SSQ DQ6DQ7V DDQ LDQM WE CAS RAS CS BA A10/APA0A1A2A3V DD1234567891011121314151617181920212223242550494847464544434241403938373635343332313029282726PIN CONFIGURATION (TOP VIEW)V SS DQ15DQ14V SSQ DQ13DQ12V DDQ DQ11DQ10V SSQ DQ9DQ8V DDQN.C/RFU UDQM CLK CKE N.C A9A8A7A6A5A4V SS50PIN TSOP (II)(400mil x 825mil)(0.8 mm PIN PITCH)PIN FUNCTION DESCRIPTIONPin NameInput FunctionCLK System Clock Active on the positive going edge to sample all inputs.CSChip SelectDisables or enables device operation by masking or enabling all inputs except CLK, CKE and L(U)DQMCKE Clock EnableMasks system clock to freeze operation from the next clock cycle.CKE should be enabled at least one cycle prior to new command.Disable input buffers for power down in standby.A 0 ~ A 10/AP AddressRow / column addresses are multiplexed on the same pins.Row address : RA 0 ~ RA 10, column address : CA 0 ~ CA 7BA Bank Select Address Selects bank to be activated during row address latch time.Selects bank for read/write during column address latch time.RAS Row Address Strobe Latches row addresses on the positive going edge of the CLK with RAS low.Enables row access & precharge.CAS Column Address Strobe Latches column addresses on the positive going edge of the CLK with CAS low.Enables column access.WE Write EnableEnables write operation and row tches data in starting from CAS, WE active.L(U)DQM Data Input/Output Mask Makes data output Hi-Z, t SHZ after the clock and masks the output.Blocks data input when L(U)DQM active.DQ 0 ~ 15Data Input/Output Data inputs/outputs are multiplexed on the same pins.V DD /V SS Power Supply/Ground Power and ground for the input buffers and the core logic.V DDQ /V SSQ Data Output Power/Ground Isolated power supply and ground for the output buffers to provide improved noise immunity.N.C/RFUNo Connection/Reserved for Future UseThis pin is recommended to be left No Connection on the device.K4S161622D-TI/ECMOS SDRAMRev 1.2 Jan '03ABSOLUTE MAXIMUM RATINGSParameter Symbol Value Unit Voltage on any pin relative to Vss V IN , V OUT -1.0 ~ 4.6V Voltage on V DD supply relative to Vss V DD , V DDQ-1.0 ~ 4.6V Storage temperature T STG -55 ~ +150°C Power dissipation P D 1W Short circuit currentI OS50mAPermanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded.Functional operation should be restricted to recommended operating condition.Exposure to higher than recommended voltage for extended periods of time could affect device reliability.Note :DC OPERATING CONDITIONSRecommended operating conditions (Voltage referenced to V SS = 0V, Extended T A = -25 to +85°C , Industrial T A = -40 to +85°C) Parameter Symbol Min Typ Max Unit NoteSupply voltage V DD , V DDQ3.0 3.3 3.6V Input logic high votlage V IH 2.0 3.0V DDQ +0.3V 1Input logic low voltage V IL -0.300.8V 2Output logic high voltage V OH 2.4--V I OH = -2mA Output logic low voltage V OL --0.4V I OL = 2mAInput leakage currentI LI-10-10uA3Note :CAPACITANCE (V DD = 3.3V, T A = 23°C, f = 1MHz, V REF =1.4V ± 200 mV)Pin Symbol Min Max Unit ClockC CLK 24pF RAS, CAS, WE, CS, CKE, L(U)DQMC IN 24pF Address C ADD 24pF DQ 0 ~ DQ 15C OUT35pF1. V IH (max) = 5.6V AC. The overshoot voltage duration is ≤ 3ns.2. V IL (min) = -2.0V AC. The undershoot voltage duration is ≤ 3ns.3. Any input 0V ≤ V IN ≤ V DDQ .Input leakage currents include HI-Z output leakage for all bi-directional buffers with Tri-State outputs.:DECOUPLING CAPACITANCE GUIDE LINERecommended decoupling capacitance added to power line at board. ParameterSymbol Value Unit Decoupling Capacitance between V DD and V SS C DC10.1 + 0.01uF Decoupling Capacitance between V DDQ and V SSQC DC20.1 + 0.01uF1. V DD and V DDQ pins are separated each other.All V DD pins are connected in chip. All V DDQ pins are connected in chip.2. V SS and V SSQ pins are separated each otherAll V SS pins are connected in chip. All V SSQ pins are connected in chip.Note :K4S161622D-TI/ECMOS SDRAMRev 1.2 Jan '031. Unless otherwise notes, Input level is CMOS(V IH /V IL =V DDQ /V SSQ ) in LVTTL.2. Measured with outputs open. Addresses are changed only one time during tcc(min).3. Refresh period is 32ms. Addresses are changed only one time during tcc(min).Note :DC CHARACTERISTICS(Recommended operating condition unless otherwise noted, Extended T A = -25 to +85°C , Industrial T A = -40 to +85°C)ParameterSymbolTest ConditionCASLatency Version Unit Note-50-55-60-70-80-10Operating Current (One Bank Active)I CC1Burst Length =1t RC ≥t RC (min)I o = 0 mA31251201151059585mA22---959580Precharge Standby Current in power-down mode I CC2P CKE ≤V IL (max), t CC = 15ns 2mAI CC2PSCKE & CLK ≤V IL (max), t CC = ∞2Precharge Standby Current in non power-down modeI CC2NCKE ≥V IH (min), CS ≥V IH (min), t CC = 15ns Input signals are changed one time during 30ns15mAI CC2NSCKE ≥V IH (min), CLK ≤V IL (max), t CC = ∞Input signals are stable 5Active Standby Current in power-down modeI CC3P CKE ≤V IL (max), t CC = 15ns 3mAI CC3PS CKE & CLK ≤V IL (max), t CC = ∞3Active Standby Current in non power-down mode (One Bank Active)I CC3NCKE ≥V IH (min), CS ≥V IH (min), t CC = 15ns Input signals are changed one time during 30ns25mAI CC3NS CKE ≥V IH (min), CLK ≤V IL (max), t CC = ∞Input signals are stable 15mAOperating Current (Burst Mode)I CC4I o = 0 mAPage Burst 2Banks Activated t CCD = 2CLKs3160155150140130115mA22---115115100Refresh Current I CC5t RC ≥t RC (min)3110105100909080mA 32---909080Self Refresh CurrentI CC6CKE ≤0.2V1mAK4S161622D-TI/ECMOS SDRAMRev 1.2 Jan '03AC OPERATING TEST CONDITIONS (V DD = 3.3V ±0.3V *2, Extended T A = -25 to +85°C , Industrial T A = -40 to +85°C)Parameter Value Unit Input levels (Vih/Vil)2.4 / 0.4V Input timing measurement reference level 1.4V Input rise and fall timetr / tf = 1 / 1ns Output timing measurement reference level 1.4VOutput load condition See Fig. 23.3V1200Ω870ΩOutputV OH (DC) = 2.4V, I OH = -2mAV OL (DC) = 0.4V, I OL = 2mAVtt=1.4V50ΩOutputZ0=50Ω(Fig. 2) AC Output Load Circuit(Fig. 1) DC Output Load Circuit1. The DC/AC Test Output Load of K4S161622D-50/55/60/70 is 30pF.Note :50pF *250pF *11. The minimum number of clock cycles is determined by dividing the minimum time required with clock cycle time and thenrounding off to the next higher integer. Refer to the following clock unit based AC conversion tableNotes :OPERATING AC PARAMETER(AC operating conditions unless otherwise noted)ParameterSymbol VersionUnit Note-50-55-60-70-80-10CASLatency CL 323232323232CLK CLK cycle timet CC(min)5105.5106107108101012ns Row active to row active delay t RRD(min)2CLK 1RAS to CAS delay t RCD(min)333332323222CLK 1Row precharge time t RP(min)333332323222CLK 1Row active time t RAS(min)877775756554CLK 1t RAS(max)100us Row cycle timet RC (min )111010101071079776CLK 1Last data in to row precharge t RDL(min)1CLK 2, 5Last data in to new col.address delay t CDL(min)1CLK 2Last data in to burst stopt BDL(min)1CLK 2Col. address to col. address delay t CCD(min)1CLK Mode Register Set cycle time t MRS(min)2CLK Number of valid output dataCAS Latency=32ea4CAS Latency=21K4S161622D-TI/ECMOS SDRAMRev 1.2 Jan '031. Parameters depend on programmed CAS latency.2. If clock rising time is longer than 1ns, (tr/2-0.5)ns should be added to the parameter.3. Assumed input rise and fall time (tr & tf)=1ns.If tr & tf is longer than 1ns, transient time compensation should be considered, i.e., [(tr + tf)/2-1]ns should be added to the parameter.Note :AC CHARACTERISTICS (AC operating conditions unless otherwise noted)ParameterSymbol-50-55-60-70-80-10Unit NoteMin Max Min Max Min Max Min Max Min Max Min Max CLK cycle time CAS Latency=3t CC 51000 5.51000610007100081000101000ns 1CAS Latency=210--101012CLK to validoutput delay CAS Latency=3t SAC - 4.5-5- 5.5- 5.5-6-6ns 1, 2CASLatency=2-6-6-6-6-6-8Output datat OH 2-2- 2.5- 2.5- 2.5 - 2.5- ns 2CLK high pulse width CAS Latency=3t CH2-2- 2.5-3-3- 3.5-ns3CAS Latency=2333CLK low pulse widthCAS Latency=3t CL 2-2- 2.5-3-3- 3.5-ns 3CAS Latency=2333Input setup time CAS Latency=3t SS 1.5- 1.5- 1.5- 1.75-2- 2.5-ns 3CAS Latency=22222Input hold time t SH 1-1-1-1-1-1-ns 3CLK to output in Low-Z t SLZ 1-1-1-1-1-1-ns 2CLK to output in Hi-ZCAS Latency=3t SHZ- 4.5-5- 5.5- 5.5 -6-6nsCAS Latency=2-6-6-6-6-6-82. Minimum delay is required to complete write.3. All parts allow every cycle column address change.4. In case of row precharge interrupt, auto precharge and read burst stop.5. Also, supported tRDL=2CLK for - 60 part which is distinguished by bucket code "J".From the next generation, tRDL will be only 2CLK for every clock frequency.ParameterSymbolVersionUnit -50-55-60-70-80-10CLK cycle timet CC(min)5 5.567810ns Row active to row active delay t RRD(min)101112141620ns RAS to CAS delay t RCD(min)1516.518202020ns Row precharge time t RP(min)1516.518202020ns Row active time t RAS(min)4038.542494848ns t RAS(max)100us Row cycle timet RC (min )555560697070nsK4S161622D-TI/ECMOS SDRAMRev 1.2 Jan '03SIMPLIFIED TRUTH TABLE(V=Valid, X=Don ′t Care, H=Logic High, L=Logic Low)COMMANDCKEn-1CKEnCSRASCASWEDQMBAA 10/APA 9~ A 0NoteRegisterMode Register Set H X L L L L X OP CODE1, 2RefreshAuto RefreshHH L L L H XX3Self RefreshEntryL 3ExitL H L H H H X X3H X X X 3Bank Active & Row Addr.H X L L H H X V Row Address Read &Column Address Auto Precharge Disable HXLHLHXVL Column Address (A 0~A 7)4Auto Precharge Enable H 4, 5Write &Column Address Auto Precharge Disable H X L H L L X VL Column Address (A 0~A 7)4Auto Precharge EnableH 4, 5Burst Stop H X L H H L X X6PrechargeBank Selection HXL L H L XV L XBoth BanksXHClock Suspend or Active Power DownEntry H L H X X X X XL V V V Exit L H X X X X X Precharge Power Down ModeEntryHLH X X X XXL H H H ExitL HH X X X X LV VVDQMH VX 7No Operation CommandHXH X X X XXLHHH1. OP Code : Operand CodeA 0 ~ A 10/AP , BA : Program keys. (@MRS)2. MRS can be issued only at both banks precharge state. A new command can be issued after 2 clock cycle of MRS.3. Auto refresh functions are as same as CBR refresh of DRAM.The automatical precharge without row precharge command is meant by "Auto". Auto/self refresh can be issued only at both banks precharge state.4. BA : Bank select address.If "Low" at read, write, row active and precharge, bank A is selected. If "High" at read, write, row active and precharge, bank B is selected.If A 10/AP is "High" at row precharge, BA is ignored and both banks are selected.5. During burst read or write with auto precharge, new read/write command can not be issued. Another bank read/write command can be issued after the end of burst.New row active of the assoiated bank can be issued at t RP after the end of burst.6. Burst stop command is valid at every burst length.7. DQM sampled at positive going edge of a CLK masks the data-in at the very CLK (Write DQM latency is 0), but makes Hi-Z state the data-out of 2 CLK cycles after. (Read DQM latency is 2)Note :XK4S161622D-TI/ECMOS SDRAMRev 1.2 Jan '03MODE REGISTER FIELD TABLE TO PROGRAM MODESRegister Programmed with MRS Address FunctionA 10/AP RFUA 9W.B.LA 8A 7TMA 6A 5A 4A 3A 2A 1A 0CAS LatencyBTBurst LengthA 8A 7A 6A 5A 4A 3A 2A 1A 0BT = 0Test ModeTypeMode Register SetReserved Reserved Reserved 00110101Write Burst Length A 901Length Burst Single BitLatency Reserved-23Reserved Reserved Reserved ReservedCAS Latency 000011110011001101010101Burst Type 01BT = 1Burst Length Type Sequential Interleave0000111100110011010101011248Reserved Reserved Reserved Full Page 1248Reserved Reserved Reserved ReservedPOWER UP SEQUENCESDRAMs must be powered up and initialized in a predefined manner to prevent undefined operations. 1. Apply power and start clock. Must maintain CKE= "H", DQM= "H" and the other pins are NOP condition at the inputs.2. Maintain stable power, stable clock and NOP input condition for a minimum of 200us.3. Issue precharge commands for all banks of the devices.4. Issue 2 or more auto-refresh commands.5. Issue a mode register set command to initialize the mode register.cf.) Sequence of 4 & 5 is regardless of the order.The device is now ready for normal operation.Note : 1. If A 9 is high during MRS cycle, "Burst Read Single Bit Write" function will be enabled. 2. RFU (Reserved for future use) should stay "0" during MRS cycle.Full Page Length : x4 (1024), x8 (512), x16 (256)BA RFUK4S161622D-TI/ECMOS SDRAMRev 1.2 Jan '03BURST SEQUENCE (BURST LENGTH = 4)Initial Address SequentialInterleaveA 1A 00011010101231230230130120123103223013210BURST SEQUENCE (BURST LENGTH = 8)Initial Address Sequential Interleave 000011110101010101234567234567014567012367012345A 1A 0A 200110011123456703456701256701234701234560123456723016745456701236745230110325476321076545476103276543210K4S161622D-TI/ECMOS SDRAMRev 1.2 Jan '03DEVICE OPERATIONSADDRESS INPUTS (A0 ~ A10/AP): In case x 4The 21 address bits are required to decode the 2,097,152 word locations are multiplexed into 11 address input pins (A 0 ~ A 10/AP). The 11 bit row addresses are latched along with RAS and BA during bank activate command. The 10 bit column addresses are latched along with CAS, WE and BA during read or write command.: In case x 8The 20 address bits are required to decode the 1,048,576 word locations are multiplexed into 11 address input pins (A 0 ~ A 10/AP). The 11 bit row addresses are latched along with RAS and BA during bank activate command. The 9 bit column addresses are latched along with CAS, WE and BA during read or write command.: In case x 16The 19 address bits are required to decode the 524,288 word locations are multiplexed into 11 address input pins (A 0 ~ A 10/AP). The 11 bit row addresses are latched along with RAS and BA during bank activate command. The 8 bit column addresses are latched along with CAS, WE and BA during read or write command.NOP and DEVICE DESELECTWhen RAS, CAS and WE are high, the SDRAM performs no operation (NOP). NOP does not initiate any new operation, but is needed to complete operations which require more than sin-gle clock cycle like bank activate, burst read, auto refresh, etc.The device deselect is also a NOP and is entered by asserting CS high. CS high disables the command decoder so that RAS,CAS, WE and all the address inputs are ignored.POWER-UPSDRAMs must be powered up and initialized in a pre-defined manner to prevent undefined operations.1. Apply power and start clock. Must maintain CKE= "H", DQM= "H" and the other pins are NOP condition at the inputs.2. Maintain stable power, stable clock and NOP input condition for a minimum of 200us.3. Issue precharge commands for both banks of the devices.4. Issue 2 or more auto-refresh commands.5. Issue a mode register set command to initialize the mode reg- ister.cf.) Sequence of 4 & 5 is regardless of the order.The device is now ready for normal operation.CLOCK (CLK)The clock input is used as the reference for all SDRAM opera-tions. All operations are synchronized to the positive going edge of the clock. The clock transitions must be monotonic between V IL and V IH . During operation with CKE high all inputs are assumed to be in a valid state (low or high) for the duration of set-up and hold time around positive edge of the clock in order to function well Q perform and I CC specifications.CLOCK ENABLE (CKE)The clock enable(CKE) gates the clock onto SDRAM. If CKE goes low synchronously with clock (set-up and hold time are the same as other inputs), the internal clock is suspended from the next clock cycle and the state of output and burst address is fro-zen as long as the CKE remains low. All other inputs are ignored from the next clock cycle after CKE goes low. When all banks are in the idle state and CKE goes low synchronously with clock,the SDRAM enters the power down mode from the next clock cycle. The SDRAM remains in the power down mode ignoring the other inputs as long as CKE remains low. The power down exit is synchronous as the internal clock is suspended. When CKE goes high at least "1CLK + t SS " before the high going edge of the clock, then the SDRAM becomes active from the same clock edge accepting all the input commands.BANK ADDRESS (BA): In case x 4This SDRAM is organized as two independent banks of 2,097,152 words x 4 bits memory arrays. The BA input is latched at the time of assertion of RAS and CAS to select the bank to be used for the operation. The bank select BA is latched at bank active, read, write, mode register set and precharge operations.: In case x 8This SDRAM is organized as two independent banks of 1,048,576 words x 8 bits memory arrays. The BA input is latched at the time of assertion of RAS and CAS to select the bank to be used for the operation. The bank select BA is latched at bank active, read, write, mode register set and precharge operations.: In case x 16This SDRAM is organized as two independent banks of 524,288words x 16 bits memory arrays. The BA input is latched at the time of assertion of RAS and CAS to select the bank to be used for the operation. The bank select BA is latched at bank active,read, write, mode register set and precharge operations.K4S161622D-TI/ECMOS SDRAMRev 1.2 Jan '03MODE REGISTER SET (MRS)The mode register stores the data for controlling the various operating modes of SDRAM. It programs the CAS latency, burst type, burst length, test mode and various vendor specific options to make SDRAM useful for variety of different applications. The default value of the mode register is not defined, therefore the mode register must be written after power up to operate the SDRAM. The mode register is written by asserting low on CS,RAS, CAS and WE (The SDRAM should be in active mode with CKE already high prior to writing the mode register). The state of address pins A 0 ~ A 10/AP and BA in the same cycle as CS,RAS, CAS and WE going low is the data written in the mode register. Two clock cycles is required to complete the write in the mode register. The mode register contents can be changed using the same command and clock cycle requirements during operation as long as all banks are in the idle state. The mode register is divided into various fields depending on the fields of functions. The burst length field uses A 0 ~ A 2, burst type uses A 3, CAS latency (read latency from column address) uses A 4 ~A 6, vendor specific options or test mode use A 7 ~ A 8, A 10/AP and BA. The write burst length is programmed using A 9. A 7 ~ A 8,A 10/AP , BA must be set to low for normal SDRAM operation.Refer to the table for specific codes for various burst length,burst type and CAS latencies.BANK ACTIVATEThe bank activate command is used to select a random row in an idle bank. By asserting low on RAS and CS with desired row and bank address, a row access is initiated. The read or write operation can occur after a time delay of t RCD (min) from the time of bank activation. t RCD is an internal timing parameter of SDRAM, therefore it is dependent on operating clock frequency.The minimum number of clock cycles required between bank activate and read or write command should be calculated by dividing t RCD (min) with cycle time of the clock and then rounding off the result to the next higher integer. The SDRAM has two internal banks in the same chip and shares part of the internal circuitry to reduce chip area, therefore it restricts the activation of two banks simultaneously. Also the noise generated during sensing of each bank of SDRAM is high, requiring some time for power supplies to recover before the other bank can be sensed reliably. t RRD (min) specifies the minimum time required between activating different bank. The number of clock cycles required between different bank activation must be calculated similar to t RCD specification. The minimum time required for the bank to beactive to initiate sensing and restoring the complete row of dynamic cells is determined by t RAS (min). Every SDRAM bank activate command must satisfy t RAS (min) specification before a precharge command to that active bank can be asserted. The maximum time any bank can be in the active state is determined by t RAS (max). The number of cycles for both t RAS (min) and t RAS (max) can be calculated similar to t RCD specification.BURST READThe burst read command is used to access burst of data on con-secutive clock cycles from an active row in an active bank. The burst read command is issued by asserting low on CS and CAS with WE being high on the positive edge of the clock. The bank must be active for at least t RCD (min) before the burst read com-mand is issued. The first output appears in CAS latency number of clock cycles after the issue of burst read command. The burst length, burst sequence and latency from the burst read com-mand is determined by the mode register which is already pro-grammed. The burst read can be initiated on any column address of the active row. The address wraps around if the initial address does not start from a boundary such that number of out-puts from each I/O are equal to the burst length programmed in the mode register. The output goes into high-impedance at the end of the burst, unless a new burst read was initiated to keep the data output gapless. The burst read can be terminated by issuing another burst read or burst write in the same bank or the other active bank or a precharge command to the same bank.The burst stop command is valid at every page burst length.BURST WRITEThe burst write command is similar to burst read command and is used to write data into the SDRAM on consecutive clock cycles in adjacent addresses depending on burst length and burst sequence. By asserting low on CS, CAS and WE with valid column address, a write burst is initiated. The data inputs are provided for the initial address in the same clock cycle as the burst write command. The input buffer is deselected at the end of the burst length, even though the internal writing can be com-pleted yet. The writing can be completed by issuing a burst read and DQM for blocking data inputs or burst write in the same or another active bank. The burst stop command is valid at every burst length. The write burst can also be terminated by using DQM for blocking data and procreating the bank t RDL after the last data input to be written into the active row. See DQM OPERATION also.DEVICE OPERATIONS (Continued)K4S161622D-TI/ECMOS SDRAMRev 1.2 Jan '03DQM OPERATIONThe DQM is used to mask input and output operations. It works similar to OE during read operation and inhibits writing during write operation. The read latency is two cycles from DQM and zero cycle for write, which means DQM masking occurs two cycles later in read cycle and occurs in the same cycle during write cycle. DQM operation is synchronous with the clock. The DQM signal is important during burst interruptions of write with read or precharge in the SDRAM. Due to asynchronous nature of the internal write, the DQM operation is critical to avoid unwanted or incomplete writes when the complete burst write is not required. Please refer to DQM timing diagram also.PRECHARGEThe precharge operation is performed on an active bank by asserting low on CS, RAS, WE and A 10/AP with valid BA of the bank to be precharged. The precharge command can be asserted anytime after t RAS (min) is satisfied from the bank active command in the desired bank. t RP is defined as the minimum number of clock cycles required to complete row precharge is calculated by dividing t RP with clock cycle time and rounding up to the next higher integer. Care should be taken to make sure that burst write is completed or DQM is used to inhibit writing before precharge command is asserted. The maximum time any bank can be active is specified by t RAS (max). Therefore, each bank activate command. At the end of precharge, the bank enters the idle state and is ready to be activated again. Entry to Power down, Auto refresh, Self refresh and Mode register set etc. is possible only when both banks are in idle state.AUTO PRECHARGEThe precharge operation can also be performed by using auto precharge. The SDRAM internally generates the timing to satisfy t RAS (min) and "t RP " for the programmed burst length and CAS latency. The auto precharge command is issued at the same time as burst read or burst write by asserting high on A 10/AP . If burst read or burst write by asserting high on A 10/AP , the bank is left active until a new command is asserted. Once auto precahrge command is given, no new commands are possible to that particular bank until the bank achieves idle state.BOTH BANKS PRECHARGEBoth banks can be precharged at the same time by using pre-charge all command. Asserting low on CS, RAS, and WE with high on A 10/AP after both banks have satisfied t RAS (min)requirement, performs precharge on both banks. At the end of t RP after performing precharge to all the banks, both banks are in idle state.DEVICE OPERATIONS (Continued)AUTO REFRESHThe storage cells of SDRAM need to be refreshed every 32ms to maintain data. An auto refresh cycle accomplishes refresh of a single row of storage cells. The internal counter increments automatically on every auto refresh cycle to refresh all the rows.An auto refresh command is issued by asserting low on CS,RAS and CAS with high on CKE and WE. The auto refresh com-mand can only be asserted with both banks being in idle state and the device is not in power down mode (CKE is high in the previous cycle). The time required to complete the auto refresh operation is specified by t RFC (min). The minimum number of clock cycles required can be calculated by driving t RFC with clock cycle time and them rounding up to the next higher integer.The auto refresh command must be followed by NOP's until the auto refresh operation is completed. Both banks will be in the idle state at the end of auto refresh operation. The auto refresh is the preferred refresh mode when the SDRAM is being used for normal data transactions. The auto refresh cycle can be per-formed once in 15.6us or a burst of 2048 auto refresh cycles once in 32ms.SELF REFRESHThe self refresh is another refresh mode available in the SDRAM. The self refresh is the preferred refresh mode for data retention and low power operation of SDRAM. In self refresh mode, the SDRAM disables the internal clock and all the input buffers except CKE. The refresh addressing and timing are internally generated to reduce power consumption.The self refresh mode is entered from both banks idle state by asserting low on CS, RAS, CAS and CKE with high on WE.Once the self refresh mode is entered, only CKE state being low matters, all the other inputs including the clock are ignored in order to remain in the self refresh mode.The self refresh is exited by restarting the external clock and then asserting high on CKE. This must be followed by NOP's for a minimum time of t RFC before the SDRAM reaches idle state to begin normal operation. If the system uses burst auto refresh during normal operation, it is recommended to use burst 2048auto refresh cycles immediately after exiting in self refresh mode.。

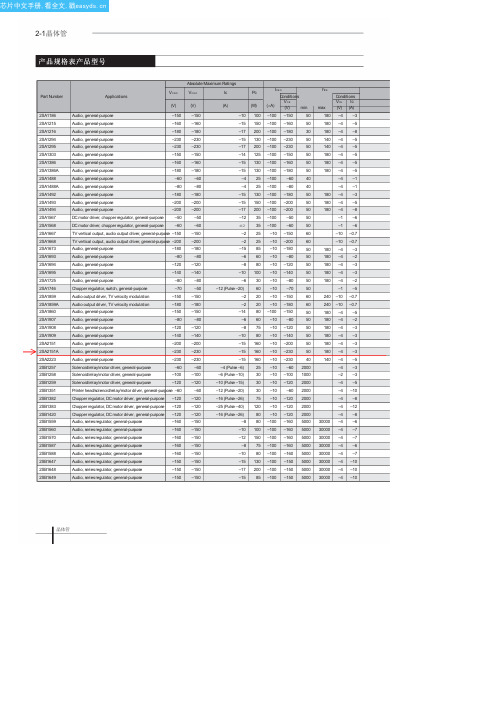

2SA1215中文资料(sanken)中文数据手册「EasyDatasheet - 矽搜」

Chopper regulator, DC motor driver, general-purpose –120

Chopper regulator, DC motor driver, general-purpose –120

Audio, seriesregulator, general-purpose

–100 –160 5000

–100 –160 5000

–100 –160 5000

–100 –160 5000

–100 –160 5000

–100 –150 5000

–100 –150 5000

–100 –150 5000

hFE max

Conditions VCE Ic (V) (A)

180 –4 –3

–150

Audio output driver, TV velocity modulation

–180

Audio, general-purpose

–150

Audio, general-purpose

–80

Audio, general-purpose

–120

Audio, general-purpose

–80

Audio, general-purpose

–120

Audio, general-purpose

–140

Audio, general-purpose

–80

Chopper regulator, switch, general-purpose

–70

Audio output driver, TV velocity modulation

VCBO Applications

(V)

斯威格洛克管道工具和配件产品说明书

Tubing Tools and Accessories 1 Tubing Tools and AccessoriesProducts■ Electric, bench top, and hand tube benders■ Tube preparation tools2 Tubing, Tubing Tools, and Welding SystemT U B I N G T O O L STube BendersSwagelok ® benders provide high-quality bends on fractional and metric tubingmade from materials that can be used with Swagelok tube fittings. These easy-to-use tube benders reduce installation time and effort as well as the potential for wrinkling or other damage to the tubing during bending.ContentsTube BendersElectric (2)Bench Top ............... 3 Hand . (5)Tube Preparation ToolsTube Cutter (6)Tube Sawing Guide ........ 6 Tube Deburring Tools ...... 6 Tube Gripper Pad (6)Features■ Electronic control ■ 1 to 110° bending range■ 1 to 2 in. outside diameter (0.049to 0.220 in. wall thickness) and 25 to 50 mm outside diameter (1.2 to 5.0 mm wall thickness) tubing range■ One bend shoe for 1, 1 1/4, 1 1/2, and2 in. sizes■ One bend shoe for 25, 32, 38, and50 mm sizesTechnical Data■ Dimensions—vertical position: 44 in. (112 cm) high, 29 in. (74 cm)wide, 30 in. (76 cm) deep■ Weight—420 lb (191 kg)■ Power requirementsM S-TBE-1—115 V (ac), 50/60 Hz; maximum current—13 A M S-TBE-2—230 V (ac), 50/60 Hz; maximum current—7 A See Ordering Information, page 4.See the Swagelok Electric Tube Bender User’s Manual, MS-13-138, for complete setup and operating instructions.Electric Tube BendersTubing DataMinimum tube length, bend radius, and wall thickness limits required to make a 90° bend in annealed tubing are listed below. Some applications require specific bend radii; consult applicable codes for bend radius requirements. Refer to Tubing Data catalog , MS-01-107, for suggested tubing wall thickness for use with Swagelok tube fittings.Fractional TubingMetric TubingTubing Tools and Accessories 3TUBING TOOLS Bench Top Tube BendersFeatures■ Rugged, lightweight aluminum construction■ 1 to 180° bending range■ 1/4 to 1 1/4 in. outside diameter (0.028 to 0.120 in. wallthickness) and 6 to 30 mm outside diameter (0.8 to 3.0 mmwall thickness) tubing range■ Steel bend shoes required for:■1 in. outside diameter tubing with greater than 0.095 in.wall thickness■25 mm tubing with greater than 2.4 mm wall thickness■a ll sizes of Alloy 2507 tubing■a ll sizes of heavy-wall annealed stainless steel tubing■a ll sizes of cold-drawn 1/8-hard stainless steel seamlesstubing.■a ll sizes of IPT medium and high pressure tubing.■ Includes grease gun and metal carrying case for storage■ Manual model can be operated with a 1/2 in. drill motorusing optional torque clutch and support arm.■ CE compliantTubing DataThe bend radius and wall thickness limits for making a bend in annealed tubing are listed below. Some applications requirespecific bend radii; consult applicable codes for bend radius requirements. Refer to Swagelok Tubing Data catalog, MS-01-107for suggested tubing wall thickness for use with Swagelok tube fittings.Fractional Tubing Metric TubingManual ModelElectric ModelTube Benders➀9/16 in. bend shoe is steel and for use with IPT tubing only.See the Swagelok Bench Top Tube Bender User’s Manual, MS-13-145, for completesetup and operating instructions.Technical Data■ Dimensions—tube bender in case:14 1/2 in. (37 cm) high, 21 in. (53 cm) wide, 11 in. (28 cm)deep■ Weight—tube bender in case, excluding tools:Manual model—75 lb (34 kg)Electric model—79 lb (36 kg)■ Power requirements (electric model)M S-BTB-1—110 V (ac), 50/60 Hz; maximum current—10 AM S-BTB-2—230 V (ac), 50/60 Hz; maximum current—5 ASee Ordering Information, page 4, and Options andAccessories, page 4.4 Tubing, Tubing Tools, and Welding SystemTUBINGTOOLSOrdering Information, Electric and Bench Top Tube Benders1. Select a basic ordering number.Example: MS-BTB-1-2. Add a power cord designator (electric models).Example: MS-BTB-1-13. Add a user’s manual language designator.Example: MS-BTB-1-1-E4. Add a tool kit designator.Example: MS-BTB-1-1-E-FKITBench Top Tube Bender KitsTo substitute a steel bend shoe for a 1 in. or 25 mm aluminumbend shoe, add -S16 to the fractional kit ordering number or-S25M to the metric kit ordering number. These are the onlysizes permitted to be changed to steel in these kits.Example: MS-BTB-1-1-E-FKIT-S16-FKIT and -MKIT kits contain tooling for the tubing sizes listedin the table above only. Tooling for 1 1/4 in, 28 mm, and 30mm must be ordered separately and is only offered in steel.Individual tool kits with aluminum or steel bend shoes for1/4 in., 3/8 in., 6 mm, and 10 mm tubing must be orderedseparately; see Options and Accessories, Bench Top TubeBenders, page 5.Tube Benders➀N ot available in European Union or China.N ot available in European Union or China.Tubing Tools and Accessories 5TUBING TOOLSTo order a complete aluminum fractional kit (1/2 in., 5/8 in., 3/4in., 7/8 in., and 1 in.) use ordering number MS-BTT-K-F-CASE.For a metric kit (12 mm, 16 mm, 18 mm, 20 mm, 22 mm, and25 mm) use ordering number MS-BTT-K-M-CASE. These kitsare only available in aluminum and contains the bend shoes,all rollers, and a carrying case. We do not offer kits in steel.■ The tripod provides portable support for the tube bender.Ordering number: MS-BTB-A-TP■ The torque clutch and support arm kit allows the manualmodel to be operated with a 1/2 in. drill motor.Ordering number: MS-BTB-A-TCSA■ The foot pedal can be used in place of the toggle switch tooperate the electric model.Ordering number: MS-BTB-A-FSRefer to Bench Top Tube Bender User’s Manual, MS-13-145,for additional accessories.Heavy-Duty Shipping CaseThe upgraded, rugged plastic customshipping case provides maximumprotection of the manual or electricbench top tube bender during transportand enhances portability with anextendable handle and wheels. The casecan also accommodate a an aluminumfractional or metric tool kit.Case dimensions, with handles foldedand retracted:30.5 H by 20.5 W by 15.5 D in. approx(77.5 by 52.1 by 39.4 cm approx).Ordering number: MS-BTB-CASE-SHIPTube BendersHand Tube BendersSwagelok hand tubebenders provideconsistent, high-qualitybends in tubing madefrom materials that canbe used with Swageloktube fittings.Features■ The hand tube bender is available in 1/8, 1/4, 5/16, 3/8, and1/2 in., as well as 3, 6, 8, 10, and 12 mm tubing sizes.■ Clevis handle design provides enhanced leverage for bendsgreater than 90°.■ Roll dies reduce bending force and tube ovality, ascompared to conventional slide block design.■ 1 to 180° bending range.The hand tube bender cannot be used for Alloy 2507tubing over 1/4 in. or for medium-pressure tubing.Refer to Hand Tube Bender Manual, MS-13-43, for additionalinformation.Tubing DataSee Ordering Information, below, for bend radius data.Some applications require specific bend radii; consultapplicable codes for bend radius requirements. Refer toTubing Data catalog, MS-01-107, for suggested tubing wallthickness for use with Swagelok tube fittings.Ordering InformationOptions and Accessories, Bench Top Tube Benders■ Individual tool kits withaluminum or steel bendshoes are available for alltubing sizes listed in thetables below and must beordered to obtain toolingfor 1/4 in., 3/8 in., 6 mm,and 10 mm tubing. Steel bend shoes are required for selecttubing, as listed on page 3.Kits contain 1 bend shoe, 1 guide roller, and 1 deformationroller.To order, replace XX with a size designator from the tablesbelow.Example: MS-BTT-K-4➀N ot available in 1 1/4 in., 28 mm, and30 mm sizes.➀9/16 in. bend shoe is steel and foruse with IPT tubing only.➁A vailable only in steel.➀A vailable only in steel.6 Tubing, Tubing Tools, and Welding SystemT U B I N G T O O L STube CutterThe Swagelok tube cutter cuts stainless steel, soft copper, and aluminum tubing from 3/16 to 1 in. and 6 to 25 mm outside diameter.Features■ Flare-out and work hardening of tube end is reduced.■ Knobs on handle are spaced in 1/8-turn increments toprovide easy reference when advancing cutter wheel.Ordering Number: MS-TC-308Replacement Cutting Wheel Ordering Number:MS-TCW-308Tube Gripper PadThe Swagelok tube gripper pad allows users to hold tubing with a firm, secure grip while using the tube cutter or tube deburring tool. Contact your authorized Swagelok sales and service representative for more information.Tube Sawing GuideThe tube sawing guide holds tubing to enable fast, accurate cutting with a hacksaw. The guide helps reduce tubing preparation time, thereby speeding system assembly.Features■ Specially designed clamp holds tubing accurately, withoutdistorting or scratching the tube surface.■ Precision guides easily position blade for all cuts.■ Recess under guide plates provides blade clearance at endof stroke.■ Retractable spring-loaded clamp allows tubing to beinserted easily.■ Guide accepts tubing sizes from 3/16 to 1 in. and 4 to25 mm outside diameter.■ Design permits easy mounting in vise.Ordering Number: MS-TSG-16For deburring the inside diameter of 1/4, 3/8, and 9/16 in. stainless steel tubing.Ordering Number: MS-44CT-27Tube Preparation ToolsTube Deburring ToolsAfter use of the tube cutter or tube sawing guide, Swagelok deburring tools deburr stainless steel, steel, and hard alloy tube ends.Features■ For deburring the inside and outside diameters of 3/16 to1 1/2 in. and 4 to 38 mm tubing■ Steel blades for long life■ Rugged, heavy-duty die-cast housingOrdering Number: MS-TDT -24MS-01-179, RevL, November 2020Safe Product SelectionWhen selecting a product, the total system design must be considered to ensure safe, trouble-free performance. Function, material compatibility, adequate ratings, proper installation, operation, and maintenance are the responsibilities of the system designer and user.。

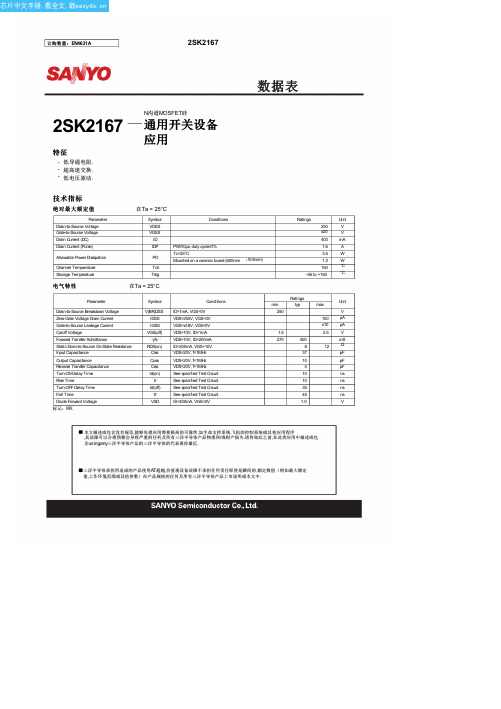

2SK2167中文资料(sanyo)中文数据手册「EasyDatasheet - 矽搜」

订购数量: EN4631A

2SK2167

数据表

N沟道MOSFET硅

2SK2167

特征

• • •

通用开关设备 应用

低导通电阻. 超高速交换. 低电压驱动.

技术指标

绝对最大额定值

Parameter Drain-to-Source Voltage Gate-to-Source Voltage Drain Current (DC) Drain Current (Pulse) Allowable Power Dissipation Channel Temperature Storage Temperature

2.4V

40

2.1V

0 0 2 4 6 8

2.3V 2.2V

10 ITR02529

100

0 0 1 2

C °C ° 5 --25 7 Tc= C ° 25

3 4 ITR02530 5

漏 - 源电压VDS - V

24

栅源电压VGS - V

18 16

RDS(ON) - VGS

Ω

RDS(ON) - 锝

Ω

20

60

80

100

120

140

栅源电压VGS - V

外壳温度,锝 -

°C

ITR02532

No.4631-2/4

芯片中文手册,看全文,戳

2SK2167

2

yfs - ID

VDS=10V

3 2

SW 时间 - ID

VDD=100V VGS=10V

1.0 fs -S

y

7 5

25°C Tc= -25°C 75°C

漏极电流ID 2

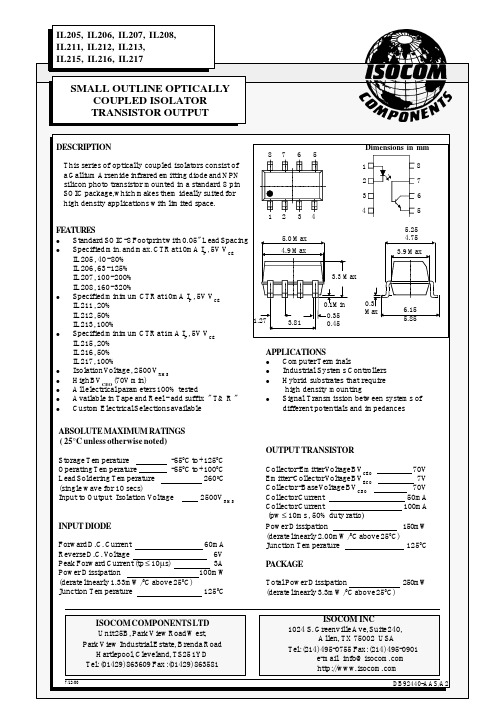

IL216中文资料

t on tf

toff tr

OUTPUT 10% 10%

FIG 1

90%

90%

7/12/00

DB92440-AAS/A2

元器件交易网

Collector Power Dissipation vs. Ambient Temperature 200 Collector power dissipation PC (mW) Current transfer ratio CTR (%) 320 280 240 200 160 120 80 40 0 -30 0 25 50 75 100 125 Ambient temperature TA ( °C ) Forward Current vs. Ambient Temperature 80 Current transfer ratio CTR (%) 70 Forward current IF (mA) 60 50 40 30 20 10 0 -30 0 25 50 75 100 125 Ambient temperature TA ( °C ) Relative Current Transfer Ratio vs. Ambient Temperature 320 Relative current transfer ratio IF = 10mA VCE = 5V Current transfer ratio CTR (%) 1.5 280 240 200 160 120 80 40 0 -30 0 25 50 75 100 320 280 240 200 160 120 80 40 0 0

Current Transfer Ratio vs. Forward Current

VCE = 5V TA = 25°C IL208 IL207

Nicerizer 16 mk2 用户手册说明书