What goes in FPGA of USRP1

USRPN210使用说明

19

体系结构

Transmitter

User-defined Code

ETH

FPGA

DAC

PC

USRP-N210 (mother board)

RF Front end

Daughter board

Receiver

User-defined Code

ETH FPGA

ADC

RF Front end

PC

USRP-N210 (mother board)

Daughter board

20

体系结构-硬件

User-defined Code

ETH FPGA

ADC DAC

RF Front end

RX2400 2.3-2.9 GHz Transceiver 50mW output (17dBm) 0-70dB Gain Direct conversion architecture Transceiver switch

2

软件无线电技术和USRP

软件无线电

From FCC : “We view software radios as the result of an evolutionary process from purely hardware-based equipment to fully software-based equipment. In this regard, the process can be roughly described in three stages

See: /uhd_docs/manual/html/build.html

基于FPGA的并行数据转SPI接口设计

0 0 l

l

数据 , 但可从串行端 口 输人数据 , 使该系统不仅具有与并行输 出设备j 亍亘 j 信的能力, 同时具有与串行设备通信的能力。

串行接收的数据通过并行输 出端 口 dt u 从数据缓 a bf a

1

O

10 o 1 1 o 0 l

10 lO O o O 1

1 0 1 OoU 0 0 O 1 o 0 1l 0 0 l o ) 0 ll ( 0 0l 10 ( 1 0) o l nO o) l ( o

图 2 系 统 工 作 流 程

系统有两种数据输入方式 : 1 )当复位信号 rs 为 1 , ee t 时 将并行数据锁存输人主 设备 , 此后在 rst 0时进行数据 的串行输出 ] ee 为 。 2 )当复位信号 rs 为0时, et e 不能从并行输入端 口输人

1

O

O

O

0

O

O

0

O

O

置移 出 全部 并 入 数据 标 志f l f 输出接收数据dt u a bf a

1 n 0 l O O o

l

l

l 0 0

0 l 0

l l O 0 O

1 1 o l 0 1O o Ol 0 0 1 1 o1 1 0 】 l o Ol l

系统与并行设备和串行设备之 间进 行双 向数据传 输 的接

d tb f7 ) aa u ( :0

bf

平使从设备获得一个选通 信号 , 进入工作状 态 , 向从设 并

备发送系统工作 时钟 sk使 主 、 c, 从设备能 同步传输 数据。

此外还使发送 完毕标志信号 b 置 0 f 。

r e es t

IntelFPGA并行闪存加载器IP内核用户指南

Intel® FPGA并行闪存加载器IP内核用户指南针对Intel® Quartus® Prime设计套件的更新:17.1订阅反馈UG-01082 | 2017.11.06官网最新文档:PDF | HTML内容内容1 Intel® FPGA并行闪存加载器IP内核用户指南 (3)1.1 功能 (3)1.2 器件支持 (3)1.2.1 支持的闪存器件 (3)1.2.2 支持的方案和功能 (7)1.3 功能说明 (8)1.3.1 编程闪存 (8)1.3.2 控制基于闪存器件的 Intel FPGA被动加载 (11)1.3.3 PFL和闪存地址的映射关系 (12)1.3.4 pof文件在Flash中页存储 (13)1.3.5 使用增强型位流压缩和解压缩 (16)1.3.6 使用远程系统更新 (17)1.4 PFL IP的使用 (20)1.4.1 将.sof文件转换成.pof (21)1.4.2 PFL的约束时序 (23)1.4.3 PFL的仿真设计 (25)1.4.4 编程 Intel CPLD和闪存器件 (29)1.4.5 定义新的CFI闪存器件(Define New CFI Flash Device) (30)1.4.6 编程多个闪存器件 (31)1.4.7 为 Intel CPLD和Flash Memory Device Programming创建Jam文件(Jam File) (31)1.5 嵌入式系统中的PFL IP内核 (31)1.6 第三方编程器支持 (34)1.7 参数 (35)1.8 信号 (37)1.9 规范 (39)1.9.1 配置时间计算实例 (41)1.10 并行闪存加载器IP内核用户指南的文件存档 (46)1.11 Intel FPGA并行闪存加载器IP内核用户指南的文档修订历史 (46)Intel® FPGA并行闪存加载器IP内核用户指南21 Intel® FPGA并行闪存加载器IP内核用户指南本文档介绍了如何在设计中例化并行闪存加载器(PFL) IP内核,编程闪存,以及从闪存中配置FPGA。

PolarFire SoC FPGA 启动和配置指南说明书

UG0881User Guide PolarFire SoC FPGA Booting And ConfigurationMicrosemi HeadquartersOne Enterprise, Aliso Viejo,CA 92656 USAWithin the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136Fax: +1 (949) 215-4996Email: *************************** ©2020 Microsemi, a wholly owned subsidiary of Microchip Technology Inc. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners. Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer’s responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided “as is, where is” and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.About MicrosemiMicrosemi, a wholly owned subsidiary of Microchip T echnology Inc. (Nasdaq: MCHP), offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs andmidspans; as well as custom design capabilities and services. Learn more at .Contents1Booting And Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11.1Boot-up Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11.1.1MSS Pre-Boot . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21.1.2MSS User Boot . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81.2Different Sources of Booting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91.3Boot Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 2Acronyms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10 3Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .113.1Revision 2.0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113.2Revision 1.0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11FiguresFigure 1Boot-up Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Figure 2MSS Pre-boot Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 Figure 3Idle Boot Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 Figure 4Non-secure Boot Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 Figure 5User Secure Boot Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 Figure 6Factory Secure Boot Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Figure 7SoftConsole Project . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 Figure 8Typical Linux Boot Process Flow . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8TablesTable 1MSS Core Complex Boot Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 Table 2U_MSS_BOOTCFG Usage in Non-Secure Boot Mode 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 Table 3U_MSS_BOOTCFG Usage in User Secure Boot . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 Table 4Secure Boot Image Certificate (SBIC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 Table 5U_MSS_BOOTCFG Usage in Factory Boot Loader Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 Table 6List of Acronyms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101Booting And ConfigurationPolarFire SoC FPGAs use advanced power-up circuitry to ensure reliable power on at power-up andreset. At power-up and reset, PolarFire SoC FPGA boot-up sequence follows Power-on reset (POR),Device boot, Design initialization, Microcontroller Subsystem (MSS) pre-boot, and MSS user boot. Thisdocument describes MSS pre-boot and MSS User Boot. For information about POR, Device Boot andDesign initialization, see UG0890: PolarFire SoC FPGA Power-Up and Resets User Guide.For more information about MSS features, see UG0880: PolarFire SoC MSS User Guide.1.1Boot-up SequenceThe boot-up sequence starts when the PolarFire SoC FPGA is powered-up or reset. It ends when theprocessor is ready to execute an application program. This booting sequence runs through severalstages before it begins the execution of programs.A set of operations are performed during the Boot-up process that includes power-on reset of thehardware, peripheral initialization, memory initialization, and loading the user-defined application fromnon-volatile memory to the volatile memory for execution.The following figure shows different phases of the Boot-up sequence.Figure 1 • Boot-up Sequence1.1.1MSS Pre-BootUpon successful completion of Design Initialization, MSS Pre-boot starts its execution. The MSS isreleased from a reset after completion of all normal startup procedures. The system controller manages the programming, initialization, and configuration of the devices. MSS Pre-boot does not occur if the programmed device is configured for system controller suspend mode.The MSS pre-boot phase of initialization is coordinated by system controller firmware, although it may make use of the E51 in the MSS Core Complex to perform certain parts of the pre-boot sequence.The following events occur during the MSS pre-boot stage:•Power-up of the MSS embedded Non-Volatile Memory (eNVM)•Initialization of the redundancy repair associated with the MSS Core Complex L2 cache •Authentication of User boot code (if User Secure boot option is enabled) •Handover operational MSS to User Boot codeThe MSS Core Complex can be booted in one of four modes. The following table lists the MSS pre-boot options, which can be configured and programmed into the sNVM. The boot mode is defined by the user parameter U_MSS_BOOTMODE[1:0]. Additional boot configuration data is mode-dependent and is defined by the user parameter U_MSS_BOOTCFG (see Table 3, page 4 and Table 5, page 6).The boot option is selected as part of the Libero design flow. Changing the mode can only be achieved through the generation of a new FPGA programming file.Figure 2 • MSS Pre-boot FlowTable 1 • MSS Core Complex Boot ModesU_MSS_BOOTMODE[1:0]ModeDescription 0Idle bootMSS Core Complex boots from boot ROM if MSS is not configured 1Non-secure bootMSS Core Complex boots directly from address defined by the U_MSS_BOOTADDR 2User secure bootMSS Core Complex boots from sNVM 3Factory secure boot MSS Core Complex boots using the factory secure boot protocol1.1.1.1Idle BootIf the MSS is not configured (for example, blank device), then the MSS Core Complex executes a bootROM program which holds all the processors in an infinite loop until a debugger connects to the target.The boot vector registers maintains their value until the device is reset or a new boot mode configurationis programmed. For configured devices, this mode can be implemented using theU_MSS_BOOTMODE=0 boot option in the Libero configurator.Note:In this mode, U_MSS_BOOTCFG is not used.The following figure shows the Idle boot flow.Figure 3 • Idle Boot FlowIn this mode, the MSS Core Complex executes from a specified eNVM address without authentication. Itprovides the fastest boot option, but there is no authentication of the code image. The address can bespecified by setting U_MSS_BOOTADDR in the Libero Configurator. This mode can also be used to bootfrom any FPGA Fabric memory resource through FIC. This mode is implemented using theU_MSS_BOOTMODE=1 boot option.The MSS Core Complex is released from reset with boot vectors defined by U_MSS_BOOTCFG (aslisted in the following table).Table 2 • U_MSS_BOOTCFG Usage in Non-Secure Boot Mode 1Offset(bytes)Size (bytes)Name Description04BOOTVEC0Boot vector for E5144BOOTVEC1Boot vector for U54084BOOTVEC2Boot vector for U541164BOOTVEC3Boot vector for U542204BOOTVEC4Boot vector for U543Figure 4 • Non-secure Boot Flow1.1.1.3User Secure BootThis mode allows user to implement their own custom secure boot and the user secure boot code isplaced in the sNVM. The sNVM is a 56 KB non-volatile memory that can be protected by the built-inPhysically Unclonable Function (PUF). This boot method is considered secured because sNVM pagesmarked as ROM are immutable. On power up, the system controller copies the user secure boot codefrom sNVM to Data Tightly Integrated Memory (DTIM) of the E51 Monitor core. E51 starts executing theuser secure boot code.If the size of the user secure boot code is more than the size of the DTIM then user needs to split theboot code into two stages. The sNVM may contain the next stage of the user boot sequence, which mayperform authentication of the next boot stage using the user authentication/decryption algorithm.If authenticated or encrypted pages are used then the same USK key (that is,U_MSS_BOOT_SNVM_USK) must be used for all authenticated/encrypted pages.If authentication fails, the MSS Core Complex can be placed in reset and the BOOT_FAIL tamper flagcan be raised. This mode is implemented using the U_MSS_BOOTMODE=2 boot option.Table 3 • U_MSS_BOOTCFG Usage in User Secure BootOffset (bytes)Size (bytes)Name Description01U_MSS_BOOT_SNVM_PAGE Start page in SNVM13RESERVED For alignment412U_MSS_BOOT_SNVM_USK For authenticated/encrypted pagesFigure 5 • User Secure Boot Flow1.1.1.4Factory Secure BootIn this mode, the system controller reads the Secure Boot Image Certificate (SBIC) from eNVM andvalidates the SBIC. On successful validation, System Controller copies the factory secure boot code fromits private, secure memory area and loads it into the DTIM of the E51 Monitor core. The default secureboot performs a signature check on the eNVM image using SBIC which is stored in eNVM. If no errorsare reported, reset is released to the MSS Core Complex. If errors are reported, the MSS Core Complexis placed in reset and the BOOT_FAIL tamper flag is raised. Then, the system controller activates atamper flag which asserts a signal to the FPGA fabric for user action. This mode is implemented usingthe U_MSS_BOOTMODE=3 boot option.The SBIC contains the address, size, hash, and Elliptic Curve Digital Signature Algorithm (ECDSA) signature of the protected binary blob. ECDSA offers a variant of the Digital Signature Algorithm which uses elliptic curve cryptography. It also contains the reset vector for each Hardware thread/core/processor core (Hart) in the system. DSNIf the DSN field is non-zero, it is compared against the device's own serial number. If the comparison fails, then the boot_fail tamper flag is set and authentication is aborted.VERSIONIf SBIC revocation is enabled by U_MSS_REVOCATION_ENABLE, the SBIC is rejected unless the value of VERSION is greater than or equal to the revocation threshold. SBIC REVOCATION OPTIONIf SBIC revocation is enabled by U_MSS_REVOCATION_ENABLE and OPTIONS[0] is ‘1’, all the SBIC versions less than VERSION are revoked upon complete authentication of the SBIC. The revocation threshold remains at the new value until it increments again by a future SBIC with OPTIONS[0] = ‘1’ and a higher VERSION field. The revocation threshold may only be incremented using this mechanism and can only be reset by a bit-stream.When the revocation threshold is updated dynamically, the threshold is stored using the redundant storage scheme used for passcodes such that a power failure during device boot does not cause a subsequent device boot to fail. If the update of revocation threshold fails, it is guaranteed that the threshold value is either the new value or the previous one.Table 4 • Secure Boot Image Certificate (SBIC)Offset Size (bytes)Value Description04IMAGEADDR Address of UBL in MSS memory map44IMAGELEN Size of UBL in bytes 84BOOTVEC 0Boot vector in UBL for E51124BOOTVEC 1Boot vector in UBL for U540164BOOTVEC 2Boot vector in UBL for U541204BOOTVEC 3Boot vector in UBL for U542244BOOTVEC 4Boot vector in UBL for U543281OPTIONS[7:0]SBIC options283RESERVED 328VERSION SBIC/Image version 4016DSN Optional DSN binding 5648HUBL image SHA-384 hash 104104CODESIG DER-encoded ECDSA signature Total 208BytesTable 5 • U_MSS_BOOTCFG Usage in Factory Boot Loader Mode Offset (bytes)Size (bytes)NameDescription04U_MSS_SBIC_ADDRAddress of SBIC in MSS address space44U_MSS_REVOCATION_ENABLE Enable SBIC revocation if non-zeroThe following figure shows the factory secure boot flow. Figure 6 • Factory Secure Boot Flow1.1.2MSS User BootMSS user boot takes place when the control is given from System Controller to MSS Core Complex.Upon successful MSS pre-boot, system controller releases the reset to the MSS Core Complex. MSScan be booted up in one of the following ways:•Bare Metal Application•Linux Application•AMP Application1.1.2.1Bare Metal ApplicationThe bare metal applications for the PolarFire SoC can be developed using SoftConsole tool. This toolprovides the output files in the form of .hex which can be used in the Libero flow to include into theprogramming bitstream file. The same tool can be used to debug the Bare Metal applications using JTAGinterface.Th following figure shows the SoftConsole Bare Metal application which has five harts (Cores) includingE51 Monitor core.Figure 7 • SoftConsole ProjectThis section describes the boot sequence for Linux running on all U54 cores.A typical boot process consists of three stages. The first stage boot loader (FSBL) gets executed fromthe on-chip Boot flash (eNVM). The FSBL loads the second stage boot loader (SSBL) from a boot deviceto external RAM or Cache. The boot device can be eNVM or embedded memory microcontroller (eMMC)or external SPI Flash. The SSBL loads the Linux operating system from boot device to external RAM. Inthe third stage, Linux is executed from the external RAM.The following figure shows the Linux Boot Process flow.Figure 8 • Typical Linux Boot Process FlowDetails of FSBL, Device tree, Linux, and YOCTO build, how to build and configure Linux will be providedin the future release of this document.1.1.2.3AMP ApplicationDetailed description of Libero MSS Configurator and how to debug multi-processor applications usingSoftConsole will be provided in the future release of this document.1.2Different Sources of BootingTo be updated in future versions of this document.1.3Boot ConfigurationTo be updated in future versions of this document.Acronyms2AcronymsThe following acronyms are used in this document.Table 1 • List of AcronymsAcronym ExpandedAMP Asymmetric Multi-processingDTIM Data Tightly Integrated Memory (also called as SRAM)ECDSA Elliptic Curve Digital Signature AlgorithmeNVM embedded Non-Volatile MemoryFSBL First Stage Boot LoaderHart Hardware thread/core/processor coreMSS Microprocessor SubsystemPOR Power on ResetPUF Physically Unclonable FunctionROM Read-only MemorySCB System Controller BridgesNVM Secure Non-volatile MemoryRevision History3Revision HistoryThe revision history describes the changes that were implemented in the document. The changes arelisted by revision, starting with the current publication.3.1Revision 2.0The following is a summary of the changes made in this revision.•Information about Factory Secure Boot was updated.•Information about Bare Metal Application was updated.3.2Revision 1.0The first publication of this document.。

基于USRP的802.11a OFDM收发信机的设计与实现

ISSN1006-7167CN31-1707/TRESEARCHANDEXPLORATIONINLABORATORY 第40卷第5期 Vol.40No.52021年5月May2021 DOI:10.19927/j.cnki.syyt.2021.05.029基于USRP的802.11aOFDM收发信机的设计与实现李昊洋, 刘海涛, 李冬霞(中国民航大学电子信息与自动化学院,天津300300)摘 要:OFDM是一种多载波传输技术,被应用于无线局域网标准IEEE802.11a的物理层。

基于USRP和LabVIEW的软件无线电平台实现了802.11aOFDM系统原型。

给出了802.11aOFDM系统的工作原理及实现方法,利用USRP和LabVIEW实现了OFDM收发信机的原型构建,在实验室无线信道环境下通过对文本的传输进行了测试验证。

测试结果表明,系统原型工作稳定,该平台可以实现通信系统原型的快速开发及算法验证。

该设计实例为USRP平台在通信学科的实验教学及科研工作的应用提供了很好的范例。

关键词:正交频分复用;802.11a标准;通用软件无线电外设中图分类号:TN914 文献标志码:A 文章编号:1006-7167(2021)05-0134-05DesignandImplementationof802.11aOFDMTransceiverBasedonUSRPLIHaoyang, LIUHaitao, LIDongxia(CollegeofElectronicInformationandAutomation,CivilAviationUniversityofChina,Tianjin300300,China)Abstract:OFDMisamulti carriertransmissiontechnology,andisappliedtothephysicallayerofIEEE802.11awhichisthestandardofwirelesslocalareanetwork.Aprototypeofthe802.11aOFDMsystemisimplementedbasedonthesoftwareradioplatformofUSRPandLabVIEW.Theworkingprincipleandimplementationmethodof802.11aOFDMsystemaregivenfirstly.ThentheprototypeofOFDMtransceiverisconstructedbasedonUSRPandLabVIEW.Finally,theprototypeistestedandverifiedthroughtexttransmissionintherealwirelesschannelenvironmentofthelaboratory.Thetestresultsshowthatthedesignedsystemprototypeoperatesstablyandtheplatformcanrealizetherapiddevelopmentofthesystemprototypeandalgorithmverification.ThepaperprovidesagoodexampleforthefurtherpromotionoftheUSRPplatformintheexperimentalteachingandscientificresearchofthecommunicationsubject.Keywords:orthogonalfrequencydivisionmultiplexing(OFDM);802.11astandard;universalsoftwareradioperipheral(USRP)收稿日期:2020 08 03基金项目:天津市本科教学质量与教学改革研究计划项目(B201005907);天津市一流课程建设项目(10412004);中央高校基本科研业务费项目中国民航大学专项(3122019056)作者简介:李昊洋(1995-),男,河南安阳人,硕士生,主要研究方向为无线通信。

NX-series EtherCAT Coupler Unit用户手册说明书

Combine flexibility in Remote I/O configurationwith the speed and determinism of EtherCAT.•The EtherCAT Coupler Unit is the link between the EtherCAT MachineControl network and the NX-series I/O Units. With I/O Units ranging frombasic I/O's to high-speed synchronous models, the NX-series is the perfectmatch for the Sysmac Machine Automation Controllers.Features•Up to 63 NX-IO Units can be connected to one EtherCAT Coupler Unit. Standard and high-performance units can be mixed.*1•High-speed remote I/O control is possible at the fastest communication cycle of 125 μs.*2•Each Coupler plus its I/O form just a single EtherCAT node on the network.•I/O control and safety control can be integrated by connecting Units for safety.•The Coupler supports the EtherCAT Distributed Clock (DC) and propagates this to synchronous I/O units.•The node address can be fixed by rotary switches, or set by software. Choose the method that best suits your way of engineering.•Slave configuration by Sysmac Studio can be done centrally via the controller, or on-the-spot using the Coupler's built-in USB port.*1Input per Coupler Unit: Maximum 1024 bytes, Output per Coupler Unit: Maximum 1024 bytes*2NX7-@@@@ and NX-ECC203 combinedSysmac is a trademark or registered trademark of OMRON Corporation in Japan and other countries for OMRON factory automation products. EtherCAT is a registered trademark of Beckhoff Automation GmbH for their patented technology. EtherNet/IP TM is the trademarks of ODVA. Other company names and product names in this document are the trademarks or registered trademarks of their respective companies.System ConfigurationSystem Configuration of Slave TerminalsThe following figure shows an example of the system configuration when an EtherCAT Coupler Unit is used as a Communications Coupler Unit.*1.The connection method for the Sysmac Studio depends on the model of the CPU Unit or Industrial PC.*2.An EtherCAT Slave Terminal cannot be connected to any of the OMRON CJ1W-NC @81/@82 Position Control Units even though they canoperate as EtherCAT masters.*3.For whether NX Units can be connected to the CPU Unit or Communications Coupler Unit to be used, refer to the user's manual for the CPUUnit or Communications Coupler Unit to be used.EtherCAT master *2Sysmac Studio Support SoftwareOrdering InformationApplicable standardsRefer to the OMRON website () or ask your OMRON representative for the most recent applicable standards for each model.*1.This depends on the specifications of the EtherCAT master. For example, the values are as follows when the EtherCAT Coupler Unit isconnected to the built-in EtherCAT port on an NJ5-series CPU Unit: 500 μs, 1,000 μs, 2,000 μs, and 4,000 μs. Refer to the NJ/NX-series CPU Unit Built-in EtherCAT Port User’s Manual (Cat. No. W505) for the specifications of the built-in EtherCAT ports on NJ/NX-series CPU Units.*2.This depends on the Unit configuration.Recommended EtherCAT Communications CableUse a straight STP (shielded twisted-pair) cable of category 5 or higher with double shielding (braiding and aluminum foil tape) for EtherCAT.Cable with Connectors*1.Standard type cables length 0.2, 0.3, 0.5, 1, 1.5, 2, 3, 5, 7.5, 10, 15 and 20 m are available.Rugged type cables length 0.3, 0.5, 1, 2, 3, 5, 10 and 15 m are available.For details, refer to Cat.No.G019.*2.The lineup features Low Smoke Zero Halogen cables for in-cabinet use and PUR cables for out-of-cabinet use. Although the LSZH cable issingle shielded, its communications and noise characteristics meet the standards.*3.Cables colors are available in blue, yellow, or Green.*4.For details, contact your OMRON representative.Product nameCommunications cycle inDC Mode *1 *2Current consumptionMaximum I/O power supply current Model EtherCAT Coupler Unit250 to 4,000 μs 1.45 W or lower4 ANX-ECC20110 ANX-ECC202125 to 10,000 μs 1.25 W or lower NX-ECC203ItemAppearanceRecommended manufacturerCable length [m] *1ModelCable with Connectors on Both Ends (RJ45/RJ45)Standard RJ45 plugs type *1Wire gauge and number of pairs: AWG26, 4-pair cable Cable sheath material: LSZH *2Cable color: Yellow *3OMRON0.3XS6W-6LSZH8SS30CM-Y 0.5XS6W-6LSZH8SS50CM-Y 1XS6W-6LSZH8SS100CM-Y 2XS6W-6LSZH8SS200CM-Y 3XS6W-6LSZH8SS300CM-Y 5XS6W-6LSZH8SS500CM-Y Cable with Connectors on Both Ends (RJ45/RJ45)Rugged RJ45 plugs type *1Wire gauge and number of pairs: AWG22, 2-pair cable Cable color: Light blueOMRON0.3XS5W-T421-AMD-K 0.5XS5W-T421-BMD-K 1XS5W-T421-CMD-K 2XS5W-T421-DMD-K 5XS5W-T421-GMD-K 10XS5W-T421-JMD-K Cable with Connectors on Both Ends (M12 Straight/M12 Straight)Shield Strengthening Connector cable *4M12/Smartclick ConnectorsWire Gauge and Number of Pairs: AWG22, 2-pair Cable Cable color: BlackOMRON0.5XS5W-T421-BM2-SS 1XS5W-T421-CM2-SS 2XS5W-T421-DM2-SS 3XS5W-T421-EM2-SS 5XS5W-T421-GM2-SS 10XS5W-T421-JM2-SS Cable with Connectors on Both Ends (M12 Straight/RJ45)Shield Strengthening Connector cable *4M12/Smartclick Connectors Rugged RJ45 plugs typeWire Gauge and Number of Pairs: AWG22, 2-pair Cable Cable color: BlackOMRON0.5XS5W-T421-BMC-SS 1XS5W-T421-CMC-SS 2XS5W-T421-DMC-SS 3XS5W-T421-EMC-SS 5XS5W-T421-GMC-SS 10XS5W-T421-JMC-SSCables / ConnectorsWire Gauge and Number of Pairs: AWG24, 4-pair Cable*We recommend you to use above cable and connector together.Wire Gauge and Number of Pairs: AWG22, 2-pair Cable*We recommend you to use above cable and connector together.Note:Connect both ends of cable shielded wires to the connector hoods.Optional ProductsAccessoriesEnd Cover (NX-END01)An End Cover is connected to the end of the EtherCAT Slave Terminal.One End Cover is provided together with the EtherCAT Coupler Unit.ItemAppearanceRecommended manufacturerModelCables-Hitachi Metals, STAR-C5E SAB 0.5 × 4P CP *-Kuramo Electric Co.KETH-SB *-SWCC Showa Cable Systems Co.FAE-5004 *RJ45 Connectors-Panduit CorporationMPS588-C *ItemAppearanceRecommended manufacturer ModelCables-Kuramo Electric Co.KETH-PSB-OMR *-JMACS Japan Co., Ltd.PNET/B *RJ45 Assembly ConnectorOMRONXS6G-T421-1 *Product nameSpecificationModelUnit/Terminal Block Coding PinsPins for 10 Units(30 terminal block pins and 30 Unit pins)NX-AUX02Product NameSpecificationModelNo. of terminals Ground terminal mark Terminal current capacity Terminal Block8Present10 ANX-TBC082General Specification*Refer to the OMRON website (/) or consult your OMRON representative for the most recent applicable standards for each model.SpecificationsEtherCAT Coupler Unit NX-ECC201/NX-ECC202/NX-ECC203*1.Refer to the NX-series Safety Control Units User’s Manual (Cat. No. Z930) for the number of Safety Control Units that can be connected.*2.This function was added or improved for a version upgrade. Refer to the NX-series EtherCAT Coupler Unit User’s Manual (Cat. No. W519) forinformation on version upgrades.*3.The range of node addresses that can be set depends on the model of the built-in EtherCAT port. For the node address ranges that can beset for a built-in EtherCAT port, refer to the user's manual for the built-in EtherCAT port on the connected CPU Unit or Industrial PC.*4.This depends on the specifications of the EtherCAT master. For example, the values are as follows when the EtherCAT Coupler Unit isconnected to the built-in EtherCAT port on an NJ5-series CPU Unit: 500 μs, 1,000 μs, 2,000 μs, and 4,000 μs. For the specifications of the built-in EtherCAT port, refer to the user's manual for the built-in EtherCAT port on the connected CPU Unit or the Industrial PC.*5.This depends on the Unit configuration.*6.There are restrictions in the communications cycles that you can set for some of the NX Units. If you use any of those NX Units, set acommunications cycle that will satisfy the specifications for the refresh cycles that can be executed by the NX Unit. Refer to the appendix of the NX-series Data Reference Manual (Cat. No. W525-E1-07 or later) to see if there are restrictions on any specific NX Units. For information on the communications cycles that you can set, refer to the user’s manuals for the NX Units.*7.Refer to the NX-series EtherCAT Coupler Unit User’s Manual (Cat. No. W519) for procedures for designing the Unit power supply system andI/O power supply system.*e a voltage that is appropriate for the I/O circuits of the NX Units and the connected external devices.ItemSpecificationEnclosureMounted in a panel Grounding methodGround to 100 Ω or less Operating environmentAmbient operating temperature 0 to 55°CAmbient operating humidity 10% to 95% (with no condensation or icing)AtmosphereMust be free from corrosive gases.Ambient storage temperature −25 to 70°C (with no condensation or icing)Altitude2,000 m max.Pollution degree Pollution degree 2 or less: Meets IEC 61010-2-201.Noise immunity Conforms to IEC61000-4-4. 2 kV (power supply line)Overvoltage category Category II: Meets IEC 61010-2-201.EMC immunity level Zone BVibration resistance Conforms to IEC 60068-2-6.5 to 8.4 Hz with 3.5-mm amplitude, 8.4 to 150 Hz, acceleration of 9.8 m/s 2, 100 min each in X, Y, and Z directions (10 sweeps of 10 min each = 100 min total)Shock resistanceConforms to IEC 60068-2-27. 147 m/s 2, 3 times each in X, Y, and Z directions Applicable standards *cULus: Listed (UL 508 or UL61010-2-201), ANSI/ISA 12.12.01,EU: EN 61131-2, C-Tick or RCM, KC Registration, NK, and LRItemSpecificationNX-ECC201NX-ECC202NX-ECC203Number of connectable NX Units 63 Units max.*1Send/receive PDO data sizes Input: 1,024 bytes max. (including input data, status, and unused areas)Output: 1,024 bytes max. (including output data and unused areas)Mailbox data size Input: 256 bytes Output: 256 bytesMailboxEmergency messages and SDO requestsRefreshing methods *2•Free-Run refreshing •Synchronous I/O refreshing •Time stamp refreshing•Free-Run refreshing•Synchronous I/O refreshing •Time stamp refreshing •Task period prioritized refreshingNode address setting rangeWhen the settable node address range for the built-in EtherCAT port is 1 to 512*3•Set on switches: 1 to 199•Set with the Sysmac Studio: 1 to 512When the settable node address range for the built-in EtherCAT port is 1 to 192*3•Set on switches: 1 to 192•Set with the Sysmac Studio: 1 to 192I/O jitter performanceInputs: 1 μs max.Outputs: 1 μs munications cycle in DC Mode250 to 4,000 μs *4 *5125 to 10,000 μs *3 *4 *6Unit power supply *7Power supply voltage24 VDC (20.4 to 28.8 VDC)NX Unit power supply capacity10 W max.Refer to Installation orientation and restrictions for details.NX Unit power supply efficiency 70%Isolation methodNo isolation between NX Unit power supply and Unit power supply terminals Current capacity of power supply terminals4 A max.I/O powersupply *7Power supply voltage5 to 24 VDC (4.5 to 28.8 VDC) *8Maximum I/O power supply current4 A 10 A Current capacity of power supply terminals4 A max.10 A max.NX Unit power consumption1.45 W max. 1.25 W max.Current consumption from I/O power supply 10 mA max. (for 24 VDC)Dielectric strength 510 VAC for 1 min, leakage current: 5 mA max. (between isolated circuits)Insulation resistance100 VDC, 20 M Ω min. (between isolated circuits)EtherCAT Communications Specifications*The EtherCAT Coupler Unit conforms to EtherCAT standards. Check the specifications of the EtherCAT master being connected for the configurable topology. However, note that only NX-ECC203 EtherCAT Coupler Units (Ver. 1.5 or later) is compatible with a ring topology.Version InformationNote:Some Units do not have all of the versions given in the above table. If a Unit does not have the specified version, support is provided by theoldest available version after the specified version. Refer to the user's manuals for the specific Units for the relation between models and versions.*1For the NX-ECC202, there is no unit version of 1.1 or earlier.*2For the NX-ECC203, there is no unit version of 1.2 or earlier.ItemSpecificationCommunications standard IEC 61158 Type 12Physical layer 100BASE-TX (IEEE 802.3)Modulation Baseband Baud rate 100 MbpsTopologyDepends on the specifications of the EtherCAT master. *Transmission mediaCategory 5 or higher twisted-pair cable (Recommended cable: double-shielded cable with aluminum tape and braiding)Transmission distance Distance between nodes: 100 m or lessModel number of EtherCAT Coupler UnitUnit version Corresponding versionsUsing an NX-series CPU Unit Using an NJ-series CPU Unit Using an NY-series Industrial PC Unit version of CPU UnitSysmac StudioversionUnit version of CPU Unit Sysmac Studioversion Unit version of Industrial PCSysmac StudioversionNX-ECC201Ver. 1.2Ver. 1.10Ver. 1.13Ver. 1.07Ver. 1.08Ver. 1.12Ver. 1.17Ver. 1.1Ver. 1.06Ver. 1.07Ver. 1.0Ver. 1.05Ver. 1.06NX-ECC202Ver. 1.2*1Ver. 1.07Ver. 1.08NX-ECC203Ver. 1.7Ver. 1.41Ver. 1.41Ver. 1.41Ver. 1.6Ver. 1.25Ver. 1.25Ver. 1.25Ver. 1.5Ver. 1.19Ver. 1.19Ver. 1.19Ver. 1.4Ver. 1.16Ver. 1.16Ver. 1.17Ver. 1.3*2Ver. 1.13Ver. 1.13External InterfaceEtherCAT Coupler Unit NX-ECC20@Terminal BlockApplicable Terminal Blocks for Each Unit ModelSymbol NameFunction(A)NX bus connectorThis connector is used to connect each Unit.(B)IndicatorsThe indicators show the current operating status of the Unit.(C)Communications connectors These connectors are connected to the communications cables of the EtherCAT network.There are two connectors, one for the input port and one for the output port.(D)Peripheral USB port This port is used to connect to the Sysmac Studio Support Software.(E)Terminal block The terminal block is used to connect external devices.The number of terminals depends on the type of Unit.(F)Rotary switches These rotary switches are used to set the 1s digit and 10s digit of the node address of the EtherCAT Coupler Unit as an EtherCAT slave. The address is set in decimal.(G)DIP switchThe DIP switch is used to set the 100s digit of the node address of the EtherCAT Coupler Unit as an EtherCAT slave.Symbol NameFunction(A)Terminal number indications The terminal numbers (A1 to A8 and B1 to B8) are displayed.The terminal number indicators are the same regardless of the number of terminals on the terminal block, as shown above.(B)Release holes Insert a flat-blade screwdriver into these holes to connect and remove the wires.(C)Terminal holes The wires are inserted into these holes.(D)Ground terminal markThis mark indicates the ground terminals. Only the NX-TBC082 has this mark.Unit modelCurrent capacity ofUnit's power supply terminals Terminal BlocksUnit power supplyI/O power supplyModelNo. of terminalsGround terminalmark Terminal currentcapacity NX-ECC201 4 A NX-TBC0828Present 10 A NX-ECC202 or NX-ECC2034 A10 ANX-TBC0828Present10 A(B)(D)(E)Eight-terminal Block(A)NX-TBC082Applicable WiresUsing FerrulesIf you use ferrules, attach the twisted wires to them.Observe the application instructions for your ferrules for the wire stripping length when attaching ferrules.Always use plated one-pin ferrules. Do not use unplated ferrules or two-pin ferrules.The applicable ferrules, wires, and crimping tool are given in the following table.*1.Some AWG 14 wires exceed 2.0 mm 2 and cannot be used in the screwless clamping terminal block.When you use any ferrules other than those in the above table, crimp them to the twisted wires so that the following processed dimensions are achieved.Using Twisted Wires/Solid WiresIf you use the twisted wires or the solid wires, use the following table to determine the correct wire specifications.*1Secure wires to the screwless clamping terminal block. Refer to the Securing Wires in the USER'S MANUAL for how to secure wires.*2With the NX-TB @@@1 Terminal Block, use twisted wires to connect the ground terminal. Do not use a solid wire.<Additional Information> If more than 2 A will flow on the wires, use plated wires or use ferrules.Terminal typesManufacturerFerrule model Applicable wire (mm 2 (AWG))Crimping toolTerminals other than ground terminalsPhoenix Contact AI0,34-80.34 (#22)Phoenix Contact (The figure in parentheses is the applicable wire size.)CRIMPFOX 6 (0.25 to 6 mm 2, AWG 24 to 10)AI0,5-80.5 (#20)AI0,5-10AI0,75-80.75 (#18)AI0,75-10AI1,0-8 1.0 (#18)AI1,0-10AI1,5-8 1.5 (#16)AI1,5-10Ground terminalsAI2,5-102.0 *1Terminals other than ground terminalsWeidmuller H0.14/120.14 (#26)Weidmueller (The figure in parentheses is the applicable wire size.)PZ6 Roto (0.14 to 6 mm 2, AWG 26 to 10)H0.25/120.25 (#24)H0.34/120.34 (#22)H0.5/140.5 (#20)H0.5/16H0.75/140.75 (#18)H0.75/16H1.0/14 1.0 (#18)H1.0/16H1.5/14 1.5 (#16)H1.5/16TerminalsWire typeWire sizeConductor length(stripping length)Twisted wires Solid wire Classification Current capacity Plated Unplated Plated UnplatedAll terminals except ground terminals2 A max.Possible Possible Possible Possible0.08 to 1.5 mm 2AWG28 to 168 to 10 mmGreater than2 A and 4 A or less Not Possible Possible*1NotPossible Greater than 4 A Possible *1NotPossibleGround terminals ---Possible PossiblePossible *2Possible*22.0 mm 29 to 10 mm1.6 mm max.2.0 mm max.(Ground terminals)(Ground terminals)Conductor length (stripping length)Dimensions(Unit: mm)EtherCAT Coupler Unit● EtherCAT Coupler Unit Only*The dimension is 1.35 mm for Units with lot numbers through December 2014.● With Cables Connected*1.*2.•• 1.5NX-ECC 11End Cover*This is the shape for Units with lot numbers through December 2014.Related Manuals Man. No Model Manual ApplicationDescription W519NX-ECC20@NX-series EtherCAT Coupler Unit User’s ManualLeaning how to use anNX-series EtherCATCoupler Unit andEther-CAT Slave Terminals The following items are described: the overall system and configuration methods of an EtherCAT Slave Terminal (which consists of an NX-series EtherCAT Coupler Unit and NX Units), and information on hardware, setup, and functions to setup, control, and monitor NX Units through EtherCAT.2020.6In the interest of product improvement, specifications are subject to change without notice. OMRON CorporationIndustrial Automation Company/(c)Copyright OMRON Corporation 2020 All Right Reserved.。

FPGA可编程逻辑器件芯片EP4CE40F29C8中文规格书

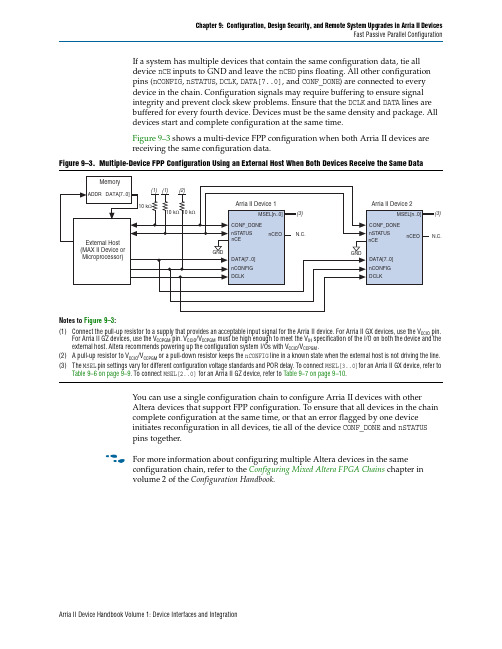

Chapter 9:Configuration, Design Security, and Remote System Upgrades in Arria II DevicesFast Passive Parallel Configuration Arria II Device Handbook Volume 1: Device Interfaces and IntegrationIf a system has multiple devices that contain the same configuration data, tie alldevice nCE inputs to GND and leave the nCEO pins floating. All other configurationpins (nCONFIG , nSTATUS , DCLK , DATA[7..0], and CONF_DONE ) are connected to everydevice in the chain. Configuration signals may require buffering to ensure signalintegrity and prevent clock skew problems. Ensure that the DCLK and DATA lines arebuffered for every fourth device. Devices must be the same density and package. Alldevices start and complete configuration at the same time.Figure 9–3 shows a multi-device FPP configuration when both Arria II devices arereceiving the same configuration data.You can use a single configuration chain to configure Arria II devices with otherAltera devices that support FPP configuration. To ensure that all devices in the chaincomplete configuration at the same time, or that an error flagged by one deviceinitiates reconfiguration in all devices, tie all of the device CONF_DONE and nSTATUSpins together.f For more information about configuring multiple Altera devices in the sameconfiguration chain, refer to the Configuring Mixed Altera FPGA Chains chapter involume 2 of the Configuration Handbook.Figure 9–3.Multiple-Device FPP Configuration Using an External Host When Both Devices Receive the Same DataNotes to Figure 9–3:(1)Connect the pull-up resistor to a supply that provides an acceptable input signal for the Arria II device. For Arria II GX devices, use the V CCIO pin.For Arria II GZ devices, use the V CCPGM pin. V CCIO /V CCPGM must be high enough to meet the V IH specification of the I/O on both the device and the external host. Altera recommends powering up the configuration system I/Os with V CCIO /V CCPGM .(2) A pull-up resistor to V CCIO /V CCPGM or a pull-down resistor keeps the nCONFIG line in a known state when the external host is not driving the line.(3)The MSEL pin settings vary for different configuration voltage standards and POR delay. To connect MSEL[3..0]for an Arria II GX device, refer toTable 9–6 on page 9–9. To connect MSEL[2..0] for an Arria II GZ device, refer to Table 9–7 on page 9–10..C.Chapter 9:Configuration, Design Security, and Remote System Upgrades in Arria II DevicesPower-On Reset Circuit and Configuration Pins Power Supply Arria II Device Handbook Volume 1: Device Interfaces and IntegrationV CCPD PinsArria II devices have a dedicated programming power supply, the V CCPD pins.Table 9–5 lists the power supply for Arria II devices.For more information about configuration pins power supply, refer to “DeviceConfiguration Pins” on page 9–39.Table 9–5.Power Supply for Arria II Devices Devices Programming Power SupplyArria II GX V CCPD must be connected to 3.3, 3.0, or 2.5V to power the I/O pre-drivers,HSTL/SSTL input buffers, and MSEL[3..0] pins.V CCPD and V CCIO for I/O banks 3C and 8C must ramp up from 0V to the desiredvoltage level within 100ms when PORSEL is low or 4ms when PORSEL is high. Ifthese supplies are not ramped up in this specified time, your Arria II GX devicewill not configure successfully. If the system cannot ramp up the power supplieswithin 100ms or 4ms, you must hold nCONFIG low until all the power suppliesare stable.You must connect V CCPD according to the I/O standard used in the same bank:■For 3.3-V I/O standards, connect V CCPD to 3.3V.■For 3.0-V I/O standards, connect V CCPD to 3.0V.■For 2.5-V and below I/O standards, connect V CCPD to 2.5V.Arria II GZ V CCPD must be connected to 3.0 or 2.5V to power the I/O pre-drivers and JTAGI/O pins (TCK , TMS , TDI , TDO , and TRST ).V CCPD and V CCPGM must ramp up from 0V to the desired voltage level within100ms when PORSEL is low or 4ms when PORSEL is high. If these supplies arenot ramped up in this specified time, your Arria II GZ device will not configuresuccessfully. If the system cannot ramp up the power supplies within 100ms or4ms, you must hold nCONFIG low until all the power supplies are stable.V CCPD must be greater than or equal to V CCIO of the same bank:■If the V CCIO of the bank is powered to 3.0V, V CCPD must be powered up to3.0V.■If the V CCIO of the bank is powered to 2.5V or lower, V CCPD must be poweredup to 2.5V.Chapter 9:Configuration, Design Security, and Remote System Upgrades in Arria II DevicesConfiguration Schemes Arria II Device Handbook Volume 1: Device Interfaces and Integration Table 9–7 lists the configuration schemes for Arria II GZ devices.AS with or without remote system upgrade 0011Fast 3.31101Fast 3.0, 2.51110Standard 3.31111Standard 3.0, 2.5JTAG-based configuration (3)(4)(4)(4)(4)——Notes to Table 9–6:(1)Configuration voltage standard applied to the V CCIO power supply in which the configuration pins reside.(2)These modes are only supported when using a MAX II device or a microprocessor with flash memory for configuration. In these modes, thehost system must output a DCLK that is x4 the data rate.(3)JTAG-based configuration takes precedence over other configuration schemes, which means the MSEL pin settings are ignored. JTAG-basedconfiguration does not support the design security or decompression features.(4)Do not leave the MSEL pins floating. Connect them to V CCPD or GND. These pins support the non-JTAG configuration scheme used in production.If you only use the JTAG configuration, Altera recommends connecting the MSEL pins to GND.Table 9–6.Configuration Schemes for Arria II GX Devices (Part 2 of 2)Configuration Scheme MSEL3MSEL2MSEL1MSEL0POR Delay Configuration Voltage Standard (V) (1) Table 9–7.Configuration Schemes for Arria II GZ Devices Configuration SchemeMSEL2MSEL1MSEL0POR Delay Configuration Voltage Standard (V)FPP000Fast/Standard 3.0, 2.5, 1.8PS010Fast/Standard 3.0, 2.5, 1.8Fast AS (40MHz) (1)011Fast/Standard 3.0, 2.5, 1.8Remote system upgrade fast AS (40MHz) (1)011Fast/Standard 3.0, 2.5, 1.8FPP with design security feature and/ordecompression enabled (2)001Fast/Standard 3.0, 2.5, 1.8JTAG-based configuration (3)(4)(4)(4)——Notes to Table 9–7:(1)Arria II GZ devices only support fast AS configuration. You must use either EPCS64 or EPCS128 devices to configure an Arria II GZ device infast AS mode.(2)These modes are only supported when using a MAX II device or microprocessor with flash memory for configuration. In these modes, the hostsystem must output a DCLK that is x4 the data rate.(3)The JTAG-based configuration takes precedence over other configuration schemes, which means the MSEL pin settings are ignored. TheJTAG-based configuration does not support the design security or decompression features.(4)Do not leave the MSEL pins floating, connect them to V CCPGM or GND. These pins support non-JTAG configuration scheme used in production.If you only use the JTAG configuration, Altera recommends connecting the MSEL pins to GND.。

FPGA可编程逻辑器件芯片EP4S100G5F45I1中文规格书

Document Revision Historythe Device & Pin Options dialog box in the Quartus II software uses a32-bit CRC circuit to ensure data reliability and is one of the best optionsfor mitigating SEU.You can implement the error detection CRC feature with existing circuitryin Stratix II devices, eliminating the need for external logic. For Stratix IIdevices, CRC is computed by the device during configuration andchecked against an automatically computed CRC during normaloperation. The CRC_ERROR pin reports a soft error when configurationSRAM data is corrupted, triggering device reconfiguration.Custom-Built CircuitryDedicated circuitry is built in the Stratix II devices to perform errordetection automatically. This error detection circuitry in Stratix II devicesconstantly checks for errors in the configuration SRAM cells while thedevice is in user mode. You can monitor one external pin for the error anduse it to trigger a re-configuration cycle. You can select the desired timebetween checks by adjusting a built-in clock divider.Software InterfaceIn the Quartus II software version 4.1 and later, you can turn on theautomated error detection CRC feature in the Device & Pin Optionsdialog box. This dialog box allows you to enable the feature and set theinternal frequency of the CRC between 400kHz to 50MHz. This controlsthe rate that the CRC circuitry verifies the internal configuration SRAMbits in the FPGA device.For more information on CRC, refer to AN 357: Error Detection Using CRCin Altera FPGA Devices.DocumentTable3–7 shows the revision history for this chapter.Revision HistoryTable3–7.Document Revision History (Part 1 of2)Date andDocumentChanges Made Summary of Changes Version—May 2007, v4.2Moved Document Revision History section to the endof the chapter.—Updated the “Temperature Sensing Diode (TSD)”section.Operating ConditionsTable5–10.2.5-V LVDS I/O SpecificationsSymbol Parameter Conditions Minimum Typical Maximum Unit2.375 2.500 2.625V V CCIO I/O supply voltage for left andright I/O banks (1, 2, 5, and6)V ID Input differential voltage100350900mV swing (single-ended)V ICM Input common mode voltage2001,2501,800mVR L = 100 Ω250450mV V OD Output differential voltage(single-ended)R L = 100 Ω 1.125 1.375V V OCM Output common modevoltageR L Receiver differential input90100110Ωdiscrete resistor (external toStratix II devices)Table5–11.3.3-V LVDS I/O SpecificationsSymbol Parameter Conditions Minimum Typical Maximum Unit V CCIO (1)I/O supply voltage for top3.135 3.300 3.465Vand bottom PLL banks (9,10, 11, and 12)100350900mV V ID Input differential voltageswing (single-ended)V ICM Input common mode voltage2001,2501,800mV V OD Output differential voltageR L = 100 Ω250710mV (single-ended)R L = 100 Ω8401,570mV V OCM Output common modevoltage90100110ΩR L Receiver differential inputdiscrete resistor (external toStratix II devices)Note to Table5–11:(1)The top and bottom clock input differential buffers in I/O banks 3, 4, 7, and 8 are powered by V CCINT, not V CCIO.The PLL clock output/feedback differential buffers are powered by VCC_PLL_OUT. For differential clockoutput/feedback operation, VCC_PLL_OUT should be connected to 3.3 V.Timing ModelTable5–34.Output Timing Measurement Methodology for Output Pins Notes(1), (2), (3)I/O StandardLoading and TerminationMeasurementPointR S (Ω)R D (Ω)R T (Ω)V CCIO (V)V TT (V)C L (pF)V MEAS (V)LVTTL (4) 3.1350 1.5675 LVCMOS (4) 3.1350 1.5675 2.5 V (4) 2.3750 1.1875 1.8 V (4) 1.71000.855 1.5 V (4) 1.42500.7125 PCI (5) 2.97010 1.485 PCI-X (5) 2.97010 1.485 SSTL-2 Class I2550 2.325 1.1230 1.1625 SSTL-2 Class II2525 2.325 1.1230 1.1625 SSTL-18 Class I2550 1.6600.79000.83 SSTL-18 Class II2525 1.6600.79000.83 1.8-V HSTL Class I5050 1.6600.79000.83 1.8-V HSTL Class II2525 1.6600.79000.83 1.5-V HSTL Class I5050 1.3750.64800.6875 1.5-V HSTL Class II25 1.3750.64800.6875 1.2-V HSTL with OCT50 1.14000.570 Differential SSTL-2 Class I5050 2.325 1.1230 1.1625 Differential SSTL-2 Class II2525 2.325 1.1230 1.1625 Differential SSTL-18 Class I5050 1.6600.79000.83 Differential SSTL-18 Class II2525 1.6600.79000.83 1.5-V Differential HSTL Class I5050 1.3750.64800.6875 1.5-V Differential HSTL Class II25 1.3750.64800.6875 1.8-V Differential HSTL Class I5050 1.6600.79000.83 1.8-V Differential HSTL Class II2525 1.6600.79000.83 LVDS100 2.3250 1.1625 HyperTransport100 2.3250 1.1625 LVPECL100 3.1350 1.5675 Notes to Table5–34:(1)Input measurement point at internal node is 0.5 × V CCINT.(2)Output measuring point for V MEAS at buffer output is 0.5 × V CCIO.(3)Input stimulus edge rate is 0 to V CC in 0.2 ns (internal signal) from the driver preceding the I/O buffer.(4)Less than 50-mV ripple on V CCIO and V CCPD, V CCINT = 1.15 V with less than 30-mV ripple(5)V CCPD = 2.97 V, less than 50-mV ripple on V CCIO and V CCPD, V CCINT = 1.15 V。

USRP1_中文产品说明

通用软件无线电外设 USRP 旨在使普通计算机能像高带宽的软件无线电设 备一样工作。从本质上讲,它充当了一个无线电通讯系统的数字基带和中频部 分。 USRP 背后的基本设计理念是在主机 CPU 上完成所有波形相关方面的处理, 比如调制和解调 。所有诸如数字上下变频、抽样和内插等高速通用操作都在 FPGA 上完成。 USRP 的真正价值是它能使工程师和设计师以低预算和最少的精力进行创 造。为数不少的开发者和用户贡献了大量的代码库,并为软件和硬件提供了许 多实际应用。灵活的硬件、开源软件和拥有经验丰富用户社区群的强强联合, 使它成为您软件无线电开发的理想平台。

1.2 数模转换器部分

在传输路径上也有 4 个高速 14 位数模转换器。 DAC 时钟频率为 128 MS / s,所以奈奎斯特频率为 64MHz 。然而,我们可能会希望低于该频率以使滤波 容易。一个有用的输出频率范围是从 DC 到 44MHz 。DACs 可为 50 欧姆或 10mW ( 10dBm )差分负载提供峰值 1V 的电压。DAC 之后也使用了 PGA 用于提供高 达 20dB 增益。PGA 是软件可编程的。DAC 信号( IOUTP_A / IOUTN_A 和 IOUTP_B / IOUTN_B )是电流输出的,每个介于 0 和 20 毫安之间。它们可以通 过一个电阻转换成差分电压。

1.4 辅助数字 I/O 端口

USRP 母板有一个高速 64 位数字 I / O 端口。这些被分为二组(32 位用于 IO_RX,32 位用于 IO_TX ) 。这些数字 I / O 引脚连接到子板接口连接器 ( RxA ,TxA, RxB 和 TxB ) 。所有这些连接器有 16 位数字 I / O 位。这些 信号可以由软件通过读/写特殊的 FPGA 寄存器来控制,而且每个都可以被独立 配置为数字输入或数字输出。 其中一些引脚来用于控制所安装子板上的特定操作,如控制选择接收射频 输入的端口,在自动发送/接收模式控制不同的 Tx 和 Rx 部件的供电电源,合成 器锁定检测等。它也可被用于实现 AGC 处理。当连接到逻辑分析仪时,它非常 有助于 FPGA 实现的调试。

剑桥雅思8阅读解析Test1Passage1

智课网IELTS备考资料剑桥雅思8阅读解析Test1Passage1摘要:雅思阅读成绩不好的烤鸭,要好好从自身上找原因,知道缺点以及不足在哪里,才能去弥补,并且取得进步。

小马小编带来剑桥雅思8阅读解析Test1Passage1,希望能帮到你。

剑桥雅思 8阅读解析Test1Passage1名师点题剑桥雅思8阅读:体裁主要内容:由古及今介绍计时的历史。

说明文A 段 :介绍古巴比伦人的计时方法。

B 段 :月亮对于历法计时的社会重要性。

C 段 :介绍古埃及人的计时方法。

结构D 段 :形形色色的计时器陆续出现,尽管并不完美。

E 段 :机械计时器引发各国最终统一校准开始时间。

F 段 :介绍最早的重力驱动机械钟。

G 段 :机械钟的进一步改良,并成为最早的座钟。

H 段 :今天的计时器。

名师点题剑桥雅思8阅读:Questions 1-4● 题型归类 :Matching 本题解题时可先划出题目中的关键词,然后迅速回到文章寻找其同义替换后的对应词。

其间可大致通过题目中的关键词猜测其在文章的位置与段落特点。

题目编号题目定位词答案位置题解1early timekeep- ing, cold tem- peraturesD 段最后一句答案 D 题目中出现 early timekeeping 字样,按照文章写作顺序,应在文章前部或中部寻找答案。

D 段最后一句中的 freezing weather 与题目中的 cold temperatures 相对应。

2geography, calendar, farmingB 段倒数第 2 句答案 B B 段倒数第二句中的 northern climes 与题目中的geography 相对应, farming 与 agriculture 相对应。

3origins, pendulum clockF 段最后一句答案F 由文中F段最后一句中的a pendulum clock had been devised 可直接得出答案。

时钟芯片的信号流程

时钟芯片的信号流程英文回答:Signal Flow in a Clock Chip.A clock chip is an electronic component that generates a regular, precise electrical signal. This signal is used to synchronize the operation of other electronic devices, such as microprocessors and memory chips.The signal flow in a clock chip can be divided into three main stages:1. Oscillation: The oscillation stage generates the basic timing signal. This is typically done using a quartz crystal, which vibrates at a specific frequency.2. Amplification: The amplification stage amplifies the oscillation signal to a level that can be used by other devices.3. Distribution: The distribution stage distributes the amplified signal to the other devices in the system.The specific signal flow in a clock chip will vary depending on the design of the chip. However, the general principles are the same.中文回答:时钟芯片的信号流程。

DSP系统中WatchDog与UART的FPGA实现

D SP 系统中W atchDog 与U A R T 的FPGA 实现Ξ曾 理1,陈 亮2(1.解放军理工大学通信工程学院研究生4队,江苏南京210007;2.解放军理工大学通信工程学院电子信息工程系)摘 要:卫星话音通信设备广泛采用了“D SP +FPGA ”的系统结构。

为了保证话音通信的工作模式随业务变化作自适应切换,需要和UA R T 监控信道随时交换信息;同时,为保障系统安全可靠工作,还需采用故障监控W atchDog 电路。

文中研究了W atchDog 和UA R T 的FPGA 设计实现过程,区别于传统方案中使用专用芯片M A X 6701、TL 16C 550分别实现W atchDog 、UA R T 功能,直接利用声码板上现成的FPGA 芯片L attice 4256V 210T 100I 实现上述两功能,并在话音处理系统中进行了硬件测试。

结果表明:与传统方案相比,文中方案具有资源利用率高、体积轻便、功耗低、系统配置方便等优点。

关键词:;通用异步收发器;现场可编程门阵列中图分类号:TN 91212文献标识码:B 文章编号:CN 3221289(2010)0120056204FPGA I m p lem e nta tion of W a tchD og a nd UART in DS P S ys temZ EN G L i 1,CH EN L iang 2(1.Po stgraduate T eam 4I CE ,PLAU ST ,N anjing 210007,Ch ina ;2.D epartm ent of E lectronic Info r m ati on Engineering I CE ,PLAU ST )A bs tra c t :Structu re “D SP +FPGA ”is w idely u sed in satellite comm un icati on equ i pm en ts.To en su re its w o rk m ode s w itches adap tab le w ith the changing operati on ,it is needed to exchange info r m ati on w ith the su rveillance channel in real ti m e ;m eanw h ile m alfuncti on supervising W atchDog circu it is also needed to p rovide system stab ility .D esign and FPGA i m p lem en tati on of W atchDog and UA R T w ere discu ssed .D ifferen t from the traditi onal w ay w h ich u ses app rop riate ch i p s M A X 6701and TL 16C 550to carry ou t W atchDog and UA R T functi on resp ectively ,a new m ethod w as p ropo sed to i m p lem en t these functi on s above th rough ready FPGA ch i p L attice 4256V 210T 100I on the vo icoder directly ,and tested in speech p rocessing hardw are system .T est resu lt suggests th is m ethod can satisfy D SP system requ irem en ts .Com pared w ith the traditi onal m ethod ,th is p ro ject m akes h igher u se of hardw are resou rce w ith low er energy u sage ,and is m uch s m aller and easier to configu re .Ke y w o rds :W atchDog ;UA R T ;FPGA 卫星通信具有综合业务、抗干扰业务,不同的业务下又有不同的话音编码传输速率,因此必须采用多模式多速率自适应的话音处理系统。

FPGA详细教程_IP复用

IP核

还包含有:

Communication & Networking(通讯和网络) IP Digital Signal Processing(数字信号处理) IP Math Functions(数学功能) IP Memories & Storage Elements(存储器) IP

Prototype & Development Hardware Product(原形和开发硬

学习动物精神

12、善解人意的海豚:常常问自己:我是主管该 怎么办才能有助于更好的处理事情的方法。在工 作上善解人意, 会减轻主管、共 事者的负担,也 让你更具人缘。

学习动物精神

11、机智应变的猴子:工作的流程有时往往是一成不变的, 新人的优势在于不了解既有的做法,而能创造出新的创意与 点子。一味 地接受工作的交付, 只能学到工作方法 的皮毛,能思考应 变的人,才会学到 方法的精髓。

5.建立一个IP文件

IP 初始化窗口

IP核生成器操作界面

IP核

在Xilinx Core Generator(IP核生成器)操作界面 左边的窗口中包含了很多文件夹,文件夹下又有子 文件夹,子文件夹中装的就是各种功能的 IP。Core Generator 中的 IP 相当丰富,而且已经分门别类装在 不同的文件夹中。如: Basic Elements( 基本元素 ) 中 包含有一些最基本的功能 IP,比较器,计数器,编 码器/译码器,格式转换,逻辑门/缓冲器,各种存储 器,复选器,寄存器,移位寄存器等。

Q : OUT std_logic_VECTOR(3 downto 0); end Behavioral;

到此已经使用IP完成了整个设计。

国家licht技术USRP N300 N310March2019说明书

Manufacturer: National InstrumentsBoard Assembly Part Numbers (Refer to Procedure 1 for identification procedure): Part Number and Revision Description141064A-01L or later USRP N310141064A-03L or later USRP N310 without TPM (Trusted Platform Module) 141064A-02L or later USRP N300 without TPM (Trusted Platform Module) Volatile MemoryTarget Data Type Size Backup1Accessible Accessible ProcedurePowerDevice operation FPGA / Processor XilinxXC7Z100(-01/-03)XC7Z035(-02) No Yes Yes CyclePowerDevice operation storage DRAM 1 GB No Yes Yes CyclePowerNon-Volatile Memory (incl. Media Storage)Target Data Type Size Backup Accessible Accessible Procedure Module configuration EEPROM 256 B No Yes Yes Procedure 2 JTAG interface configuration EEPROM 256 B No No Yes None RF configuration, slot 0 EEPROM 32 KB No Yes Yes Procedure 3 RF configuration, slot 1(not populated on -02)EEPROM 32 KB No Yes Yes Procedure 3RF control PLD, slot 0 CPLD Altera5M570ZNo Yes Yes Procedure 4RF control PLD, slot 1 (not populated on -02) CPLD Altera5M570ZNo Yes Yes Procedure 41 Refer to Terms and Definitions section for clarification of User and System AccessibleProceduresProcedure 1 – Board Assembly Part Number identification:To determine the Board Assembly Part Number and Revision, refer to the label applied to the surface of your product. The Assembly Part Number should be formatted as “P/N: 141064a-01L” for the USRP N310, “P/N: 141064a-03L” for the USRP N310 without TPM, or “P/N: 141064a-02L” for the USRP N300 without TPM, where “a” is a capital letter indicating the revision (e.g. A, B, C…).Procedure 2 – Clear the Module Configuration EEPROM:This EEPROM stores device-specific serial numbers and MAC addresses. The user is provided with commands to directly modify these critical values. To prevent rendering the device inoperable, the original EEPROM contents should be saved and referenced for future use, prior to clearing the device. However, it is also possible to completely erase the device with user-defined values. Both options are shown below.As a precursor to all the following instructions, log into the device using a remote console.Option A: Save and Restore Original DataSave:User-accessible portions of the module EEPROM may be read from the device using the following command entered in the console. Save the information in any format of your choosing.eeprom-dumpRestore:User-accessible portions of the module EEPROM may be written using the following command entered in the console. Use the --help flag to view the latest command syntax. Enter the previously saved data into the command in the appropriate fields.eeprom-initOption B: Erase DataCaution: The erase procedure renders the module inoperable. The device will still be able to have communications established with it and can be reprogrammed with the contents from “Option A: Save and Restore Original Data”; however, the driver will report a fatal error if any configuration is attempted without restoring the data. If you want to use a module again after erasing the EEPROM without having stored a copy of the original EEPROM contents, contact National Instruments for information about costs and procedures to return the module to the factory for repair.To erase the EEPROM contents, use the following command. Use the --help flag to view the latest command syntax. Enter zeroes or data of your choosing into the fields.eeprom-initProcedure 3 – Clear the RF Configuration EEPROM:This EEPROM stores device-specific serial numbers and board revisions. The user is provided with commands to directly modify these critical values. To prevent rendering the device inoperable, the original EEPROM contents should be saved and referenced for future use, prior to clearing the device. However, it is also possible to completely erase the device with user-defined values. Both options are shown below.As a precursor to all the following instructions, log into the device using a remote console.Option A: Save and Restore Original DataSave:User-accessible portions of the module EEPROM may be read from the device using the following command entered in the console. Save the information in any format of your choosing. The command is entered once for daughterboard slot 0 and once for daughterboard slot 1, as shown below. For the (-02) variant, there is no daughterboard in slot 1 and the following command should only be run for slot 0.db-dump 0db-dump 1Restore:User-accessible portions of the module EEPROM may be written using the following command entered in the console. Use the --help flag to view the latest command syntax. Enter the previously saved data into the command in the appropriate fields. The command must be repeated for every daughterboard slot that should be restored.d b-initOption B: Erase DataCaution: The erase procedure renders the module inoperable. The device will still be able to have communications established with it and can be reprogrammed with the contents from “Option A: Save and Restore Original Data”; however, the driver will report a fatal error if any configuration is attempted without restoring the data. If you want to use a module again after erasing the EEPROM without having stored a copy of the original EEPROM contents, contact National Instruments for information about costs and procedures to return the module to the factory for repair.To erase the EEPROM contents, use the following command. Use the --help flag to view the latest command syntax. Enter zeroes or data of your choosing into the fields. The command must be repeated for every daughterboard slot that should be erased.d b-initProcedure 4 – Clear the RF Control PLD:All sections of the CPLD on each of the daughterboards may be overwritten from the FPGA using built-in API commands. The most recent CPLD image is located in the Ettus Research files server.To clear the current CPLD image and load factory defaults, follow these steps:1)Log into the device using a remote console.2)Download the usrp_n310_mg_cpld.svf file to your device.The file will be saved to the /usr/share/uhd/images/ directory.uhd_images_downloader -t n310_cpld3)Run the following commands to update the CPLD on both daughterboards. For the (-02) variant, there is nodaughterboard in slot 1 and the following command should only be run for slot 0.python3 /usr/lib/python3.5/site-packages/usrp_mpm/dboard_manager/magnesium_update_cpld.py --file=/usr/share/uhd/images/usrp_n310_mg_cpld.svf --dboards=0python3 /usr/lib/python3.5/site-packages/usrp_mpm/dboard_manager/magnesium_update_cpld.py --file=/usr/share/uhd/images/usrp_n310_mg_cpld.svf --dboards=14)The API call will report success at the end of the procedure on each daughterboard. If failures are reportedcontact National Instruments for assistance.Terms and DefinitionsCycle Power:The process of completely removing power from the device and its components and allowing for adequate discharge. This process includes a complete shutdown of the PC and/or chassis containing the device; a reboot is not sufficient for the completion of this process.Volatile Memory:Requires power to maintain the stored information. When power is removed from this memory, its contents are lost. This type of memory typically contains application specific data such as capture waveforms.Non-Volatile Memory:Power is not required to maintain the stored information. Device retains its contents when power is removed.This type of memory typically contains information necessary to boot, configure, or calibrate the product or may include device power up states.User Accessible:The component is read and/or write addressable such that a user can store arbitrary information to the component from the host using a publicly distributed NI tool, such as a Driver API, the System Configuration API, or MAX. System Accessible:The component is read and/or write addressable from the host without the need to physically alter the product. Clearing:Per NIST Special Publication 800-88 Revision 1, “clearing” is a logical technique to sanitize data in all User Accessible storage locations for protection against simple non-invasive data recovery techniques using the same interface available to the user; typically applied through the standard read and write commands to the storage device.Sanitization:Per NIST Special Publication 800-88 Revision 1, “sanitization” is a process to render access to “Target Data” on the media infeasible for a given level of effort. In this document, clearing is the degree of sanitization described.。

计算机B卷参考答案

一、选择搭配题:(每题2分×15=30分)G O A D L I B N C M E H F J K二、翻译题:(每题6分×5=30分)1、指令译码器需要将每个操作码转换成一组信号,以驱动微处理器中的不同组件。

2、听起来好像很多,因为大多数家用计算机目前只用256MB到522MB的RAM。

3、主板就是所有其他内部组件都连接其上的主电路板。

4、硬盘是大容量永久存储器,用于保护程序和文档之类的信息。

5、大多数视频卡本身有个微型BIOS,用于初始化图形处理器。

三、阅读题(每题4分×5=20分)1、The instruction decoder needs to turn each of the operation codes intoa set of signals that drive the different components inside the microprocessor.2、What it needs to do:during the first clock cycle, we need to actually load the instruction. During the second clock cycle, the ADD instruction is decoded. During the third clock cycle, the program counter is incremented (in theory this could be overlapped into the second clock cycle).3、Therefore the instruction decoder needs to: activate the tri-state buffer for the program counter; activate the RD line; activate the data-in tri-state buffer, and latch the instruction into the instruction register.4、It needs to do very little: set the operation of the ALU to addition, and latch the output of the ALU into the C register.5、Every instruction can be broken down as a set of sequenced operations like these that manipulate the components of the microprocessor in the proper order. Some instructions, like this ADD instruction, might take two or three clock cycles. others might take five or six clock cycles.四、作文题题(1题 20分)略。

fpga中done的作用

fpga中done的作用英文回答:DONE is a signal in the FPGA (Field Programmable Gate Array) that indicates the completion of a specific task or operation. It is used for synchronization and control purposes, ensuring that subsequent operations do not commence until the preceding operation is completed.The DONE signal can be generated by various hardware modules within the FPGA, such as arithmetic logic units (ALUs), multipliers, and memory controllers. It istypically asserted high when the operation is complete and de-asserted low when the operation is in progress.The DONE signal is an important part of the FPGA design, as it allows for efficient and reliable operation. It enables the FPGA to execute complex tasks in a predictable and controlled manner, ensuring that data is processed correctly and that errors are minimized.中文回答:DONE信号是FPGA(现场可编程门阵列)中用于指示特定任务或操作完成的信号。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。