PAD500中文资料

13745资料

TOP VIEW GND NC VIN VIN BOOST FB/SENSE NC GND 1 2 3 4 5 6 7 8

LT1374CFE LT1374IFE

FE16 PACKAGE 16-LEAD PLASTIC TSSOP

θJA = 40°C/ W EXPOSED PAD SOLDERED TO GROUND PLANE

VOUT = 5V VIN = 10V L = 10µH

1374 TA02

U

1374fb

1

元器件交易网

LT1374

ABSOLUTE

AXI U

RATI GS

Input Voltage LT1374 ............................................................... 25V LT1374HV .......................................................... 32V BOOST Pin Voltage ................................................. 38V BOOST Pin Above Input Voltage ............................. 15V SHDN Pin Voltage ..................................................... 7V BIAS Pin Voltage ...................................................... 7V FB Pin Voltage (Adjustable Part) ............................ 3.5V

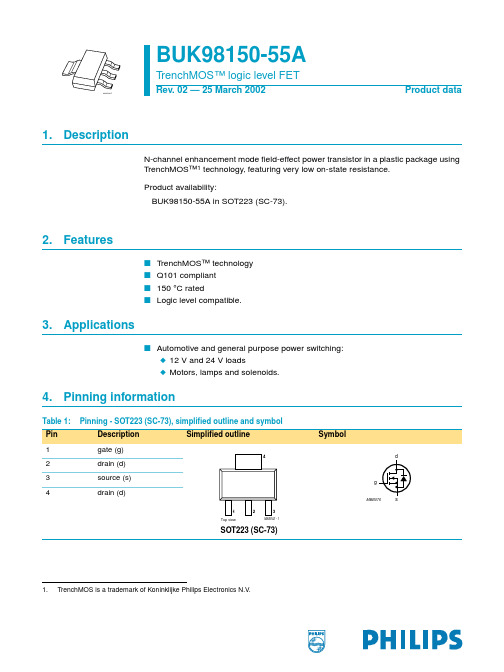

BUK98150-55A中文资料

© Koninklijke Philips Electronics N.V. 2002. All rights reserved.

2 of 12

Philips Semiconductors

BUK98150-55A

TrenchMOS™ logic level FET

120 Pder

(%)

80

03aa17

starting Tj = 25 °C

Max Unit

55

V

5

A

8

W

150

°C

150

mΩ

161

mΩ

137

mΩ

Max Unit

55

V

55

V

±15

V

5

A

3

A

22

A

8

W

+150 °C

+150 °C

5

A

22

A

31

mJ

9397 750 09435

Product data

Rev. 02 — 25 March 2002

Tsp = 25 °C; Figure 1

-

Tstg

storage temperature

−55

Tj

operating junction temperature

−55

Source-drain diode

IDR

reverse drain current (DC)

Tsp = 25 °C

-

IDRM

peak reverse drain current

128

VGS = 4.5 V; ID = 5 A

tPad中文使用手册

11目录第1章.tPad 简介 (3)1.1 关于tPad 套件............................................................................................................................................7 1.2 获取帮助 (8)第2章. tPad 概述 (9)2.1 布局和组件...............................................................................................................................................9 2.2 tPad 系统框图. (10)第3章. 使用 tPad (11)3.1 配置 Cyclone IV E FPGA 芯片...............................................................................................................11 3.2 总线控制器.............................................................................................................................................14 3.3 使用 8英寸LCD 触摸屏模块..................................................................................................................15 3.4 使用 500万像素数字影像传感器模块.. (16)第4章. tPad 设计范例 (18)4.1 系统要求.................................................................................................................................................18 4.2 出厂配置.................................................................................................................................................18 4.3 tPad Starter 设计范例..............................................................................................................................19 4.4 tPad 图片查看器.....................................................................................................................................23 4.5 视频与图像处理.....................................................................................................................................26 4.6 tPad 摄像头应用.....................................................................................................................................29 4.7 使用摄像头的视频与图像处理. (32)第5章. 应用选择器 (36)5.1 即刻可用的SD 卡演示范例....................................................................................................................36 5.2 运行应用选择器.....................................................................................................................................37 5.3 应用选择器详解.....................................................................................................................................37 5.4 恢复出厂默认程序 (40)2第6章. 附录 (43)6.1 修改历史.................................................................................................................................................43 6.2 版权声明. (43)第1章.tPad 简介tPad 高阶多媒体嵌入式系统开发套件为嵌入式开发人员创建多媒体系统提供了一个非常全面的设计环境。

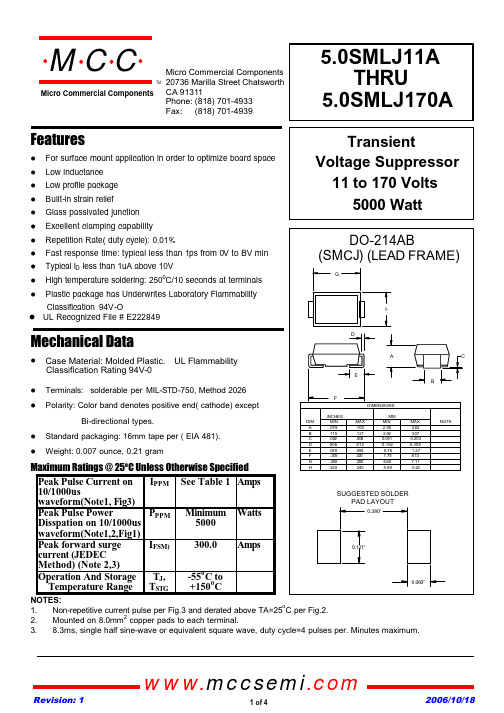

5.0SMLJ22CA中文资料

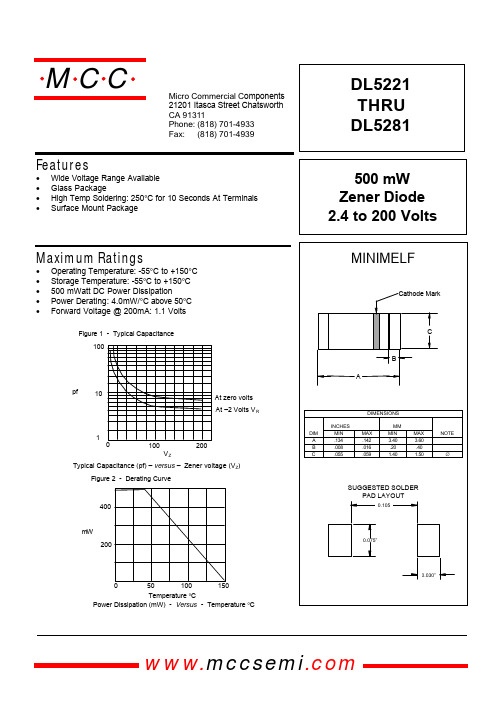

FeaturesMechanical DataTerminals: solderable per MIL-STD-750, Method 2026 Polarity: Color band denotes positive end( cathode) exceptBi-directional types.Standard packaging: 16mm tape per ( EIA 481). Weight: 0.007 ounce, 0.21 gramMaximum Ratings @ 25o C Unless Otherwise SpecifiedPeak Pulse Current on 10/1000uswaveform(Note1, Fig3)I PPM See Table 1Amps Peak Pulse Power Disspation on 10/1000us waveform(Note1,2,Fig1)P PPMMinimum 5000Watts Peak forward surge current (JEDEC Method) (Note 2,3)I FSM)300.0Amps Operation And Storage Temperature Range T J ,T STG -55o C to +150o CNOTES:1.Non-repetitive current pulse per Fig.3 and derated above TA=25oC per Fig.2.2.Mounted on 8.0mm 2copper pads to each terminal.3.8.3ms, single half sine-wave or equivalent square wave, duty cycle=4 pulses per. Minutes maximum.For surface mount application in order to optimize board space Low inductance Low profile package Built-in strain relief Glass passivated junction Excellent clamping capability Repetition Rate( duty cycle): 0.01%Fast response time: typical less than 1ps from 0V to BV min Typical I D less than 1uA above 10VHigh temperature soldering: 250oC/10 seconds at terminals Plastic package has Underwrites Laboratory FlammabilityClassification 94V-Oomp onents 20736 Marilla Street Chatsworth! "# $ % ! "#Revision: 1 2006/10/18 UL Recognized File # E222849TMMicro Commercial ComponentsCase Material: Molded Plastic. UL Flammability Classification Rating 94V-0www.mccsemi .com1 of 4MAXIMUM CLAMPING VOLTAGE REVERSE LEAKAGE @Ipp @V RWM Vc(V)I D (µA)5.0SMLJ 11A 1112.213.51018.22758005PEN 5.0SMLJ 12A 1213.314.71019.92528005PEP 5.0SMLJ 13A 1314.415.91021.52335005PEQ 5.0SMLJ 14A 1415.617.21023.22162005PER 5.0SMLJ 15A 1516.718.5124.42051005PES 5.0SMLJ 16A 1617.819.7126193505PET 5.0SMLJ 17A 1718.920.9127.6181205PEU 5.0SMLJ 18A 182022.1129.2172105PEV 5.0SMLJ 20A 2022.224.5132.415555PEW 5.0SMLJ 22A 2224.426.9135.514155PEX 5.0SMLJ 24A 2426.729.5138.912955PEZ 5.0SMLJ 26A 2628.931.9142.111955PFE 5.0SMLJ 28A 2831.134.4145.411055PFG 5.0SMLJ 30A 3033.336.8148.410355PFK 5.0SMLJ 33A 3336.740.6153.393.955PFM 5.0SMLJ 36A 364044.2158.186.155PFP 5.0SMLJ 40A 4044.449.1164.577.655PFR 5.0SMLJ 43A 4347.852.8169.472.155PFT 5.0SMLJ 45A 455055.3172.768.855PFV 5.0SMLJ 48A 4853.358.9177.464.755PFX 5.0SMLJ 51A 5156.762.7182.460.755PFZ 5.0SMLJ 54A 546066.3187.157.555RGE 5.0SMLJ 58A 5864.471.2193.653.555PGG 5.0SMLJ 60A 6066.773.7196.851.755PGK 5.0SMLJ 64A 6471.178.6110348.655PGM 5.0SMLJ 70A 7077.886111344.355PGP 5.0SMLJ 75A 7583.392.1112141.455PGR 5.0SMLJ 78A 7886.795.8112639.755PGT 5.0SMLJ 85A 8594.4104113736.555PGV 5.0SMLJ 90A 90100111114634.355PGX 5.0SMLJ 100A 100111123116230.955PGZ 5.0SMLJ 110A 110122135117728.355PHE 5.0SMLJ 120A 12013314711932655PHG 5.0SMLJ 130A 13014415912092455PHK 5.0SMLJ 150A 150167185124320.655PHM 5.0SMLJ 160A 160178197125919.355PHP 5.0SMLJ 170A170189209127518.255PHRDEVICE MARKING CODE PART NUMBERPEAK PULSE CURRENT Ipp (A)TEST CURRENT I T (mA)BREAKDOWNVOLTAGE V BR (V)MAX.@ITBREAKDOWN VOLTAGEV BR (V)MIN.@IT REVERSE STAND- OFF VOLTAGE V RWM (V)TMMicro Commercial Components5.0SMLJ11A~5.0SMLJ170Awww.mccsemi .com2 of 4Revision: 1 2006/10/18MAXIMUM CLAMPING VOLTAGE REVERSE LEAKAGE @Ipp @V RWM Vc(V)I D (µA)5.0SMLJ 11CA 1112.213.51018.22758005BEN 5.0SMLJ 12CA 1213.314.71019.92528005BEP 5.0SMLJ 13CA 1314.415.91021.52335005BEQ 5.0SMLJ 14CA 1415.617.21023.22162005BER 5.0SMLJ 15CA 1516.718.5124.42051005BES 5.0SMLJ 16CA 1617.819.7126193505BET 5.0SMLJ 17CA 1718.920.9127.6181205BEU 5.0SMLJ 18CA 182022.1129.2172105BEV 5.0SMLJ 20CA 2022.224.5132.415555BEW 5.0SMLJ 22CA 2224.426.9135.514155BEX 5.0SMLJ 24CA 2426.729.5138.912955BEZ 5.0SMLJ 26CA 2628.931.9142.111955BFE 5.0SMLJ 28CA 2831.134.4145.411055BFG 5.0SMLJ 30CA 3033.336.8148.410355BFK 5.0SMLJ 33CA 3336.740.6153.393.955BFM 5.0SMLJ 36CA 364044.2158.186.155BFP 5.0SMLJ 40CA 4044.449.1164.577.655BFR 5.0SMLJ 43CA 4347.852.8169.472.155BFT 5.0SMLJ 45CA455055.3172.768.855BFVPART NUMBERREVERSE STAND- OFF VOLTAGE V RWM (V)BREAKDOWN VOLTAGEV BR (V)MIN.@IT BREAKDOWNVOLTAGE V BR (V)MAX.@ITTEST CURRENT I T (mA)PEAK PULSE CURRENT Ipp (A)DEVICE MARKING CODE TMMicro Commercial Components5.0SMLJ11C A~5.0SMLJ 45C AFor Bidirectional type having Vrwm of 20 volts and less,the Ir limit is double.www.mccsemi .com3 of 4Revision: 1 2006/10/18Revision: 12006/10/18Micro Commercial Componentswww.mccsemi .com4 of 4products are represented on our website, harmless against all damages.***APPLICATIONS DISCLAIMER******IMPORTANT NOTICE***Aerospace or Military Applications.Products offer by Micro Commercial Components Corp .are not intended for use in Medical,Micro Commercial Components Corp .reserve s the right to make changes without further notice to any product herein to make corrections, modifications , enhancements , improvements , or other changes .Micro Commercial Components Corp .does not assume any liability arising out of the application or use of any product described herein; neither does it convey any license under its patent rights ,nor the rights of others . The user of products in such applications shall assume all risks of such use and will agree to hold Micro Commercial Components Corp .and all the companies whose。

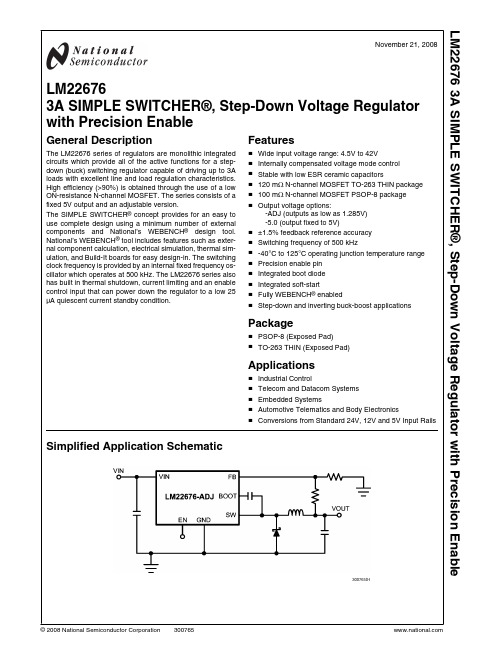

LM22676中文资料

November 21, 2008 LM226763A SIMPLE SWITCHER®, Step-Down Voltage Regulator with Precision EnableGeneral DescriptionThe LM22676 series of regulators are monolithic integrated circuits which provide all of the active functions for a step-down (buck) switching regulator capable of driving up to 3A loads with excellent line and load regulation characteristics. High efficiency (>90%) is obtained through the use of a low ON-resistance N-channel MOSFET. The series consists of a fixed 5V output and an adjustable version.The SIMPLE SWITCHER® concept provides for an easy to use complete design using a minimum number of external components and National’s WEBENCH® design tool. National’s WEBENCH® tool includes features such as exter-nal component calculation, electrical simulation, thermal sim-ulation, and Build-It boards for easy design-in. The switching clock frequency is provided by an internal fixed frequency os-cillator which operates at 500 kHz. The LM22676 series also has built in thermal shutdown, current limiting and an enable control input that can power down the regulator to a low 25µA quiescent current standby condition.Features■Wide input voltage range: 4.5V to 42V■Internally compensated voltage mode control■Stable with low ESR ceramic capacitors■120 mΩ N-channel MOSFET TO-263 THIN package■100 mΩ N-channel MOSFET PSOP-8 package■Output voltage options:-ADJ (outputs as low as 1.285V)-5.0 (output fixed to 5V)■±1.5% feedback reference accuracy■Switching frequency of 500 kHz■-40°C to 125°C operating junction temperature range■Precision enable pin■Integrated boot diode■Integrated soft-start■Fully WEBENCH® enabled■Step-down and inverting buck-boost applications Package■PSOP-8 (Exposed Pad)■TO-263 THIN (Exposed Pad)Applications■Industrial Control■Telecom and Datacom Systems■Embedded Systems■Automotive Telematics and Body Electronics■Conversions from Standard 24V, 12V and 5V Input RailsSimplified Application Schematic30076501© 2008 National Semiconductor LM22676 3A SIMPLE SWITCHER®, Step-Down Voltage Regulator with Precision EnableConnection Diagrams300765408-Lead Plastic PSOP-8 Package NS Package Number MRA08B300765027-Lead Plastic TO-263 THIN PackageNS Package Number TJ7AOrdering InformationOutput VoltageOrder Number Package Type NSC Package DrawingSupplied As ADJ LM22676MR-ADJ PSOP-8 Exposed PadMRA08B95 Units in Rails ADJ LM22676MRE-ADJ 250 Units in Tape and Reel ADJ LM22676MRX-ADJ 2500 Units in Tape and Reel ADJ LM22676TJE-ADJ TO-263 THIN Exposed PadTJ7A250 Units in Tape and Reel ADJ LM22676TJ-ADJ 1000 Units in Tape and Reel5.0LM22676MR-5.0PSOP-8 Exposed PadMRA08B95 Units in Rails 5.0LM22676MRE-5.0250 Units in Tape and Reel 5.0LM22676MRX-5.02500 Units in Tape and Reel 5.0LM22676TJE-5.0TO-263 THIN Exposed PadTJ7A250 Units in Tape and Reel 5.0LM22676TJ-5.01000 Units in Tape and Reel 2L M 22676Pin DescriptionsPin Numbers PSOP-8Package Pin NumbersTO-263 THINPackageName Description Application Information13BOOT Bootstrap input Provides the gate voltage for the high side NFET.2, 35NC Not Connected Pins are not electrically connected inside the chip. Pins dofunction as thermal conductor.46FB Feedback pin Inverting input to the internal voltage error amplifier.57EN Precision enable pin When pulled low regulator turns off.64GND System ground Provide good capacitive decoupling between VIN and thispin72VIN Source input voltage Input to the regulator. Operates from 4.5V to 42V.81SW Switch pin Attaches to the switch nodeLM22676Absolute Maximum Ratings (Note 1)If Military/Aerospace specified devices are required,please contact the National Semiconductor Sales Office/Distributors for availability and specifications.VIN to GND 43VEN Pin Voltage-0.5V to 6V SW to GND (Note 2)-5V to V IN BOOT Pin Voltage V SW + 7V FB Pin Voltage -0.5V to 7V Power DissipationInternally LimitedJunction Temperature 150°CSoldering Information Infrared (5 sec.)260°CESD Rating (Note 3) Human Body Model±2 kVStorage Temperature Range -65°C to +150°COperating Ratings(Note 1)Supply Voltage (V IN )4.5V to 42V Junction Temperature Range-40°C to +125°CElectrical CharacteristicsLimits in standard type are for T J = 25°C only; limits in boldface type apply over thejunction temperature (T J ) range of -40°C to +125°C. Minimum and Maximum limits are guaranteed through test, design, or statistical correlation. Typical values represent the most likely parametric norm at T A = T J = 25°C, and are provided for reference purposes only. Unless otherwise specified: V IN = 12V.Symbol ParameterConditionsMin (Note 5)Typ (Note 4)Max (Note 5)UnitsLM22676-5.0V FBFeedback VoltageV IN = 8V to 42V4.925/4.95.05.075/5.1VLM22676-ADJV FB Feedback Voltage V IN = 4.7V to 42V 1.266/1.2591.285 1.304/1.311V All Output Voltage VersionsI Q Quiescent Current V FB = 5V 3.46mA I STDBY Standby Quiescent Current EN Pin = 0V 2540µA I CL Current Limit3.4/3.354.25.3/5.5A I L Output Leakage Current V IN = 42V, EN Pin = 0V, V SW = 0V 0.22µA V SW = -1V0.13µA R DS(ON)Switch On-Resistance TO-263 THIN Package 0.120.16/0.22ΩPSOP-8 Package 0.100.16/0.20f O Oscillator Frequency 400500600kHz T OFFMIN Minimum Off-time 300 ns T ONMIN Minimum On-time100 ns I BIAS Feedback Bias Current V FB = 1.3V (ADJ Version Only) 230 nA V EN Enable Threshold Voltage1.3 1.6 1.9V I EN Enable Input Current EN Input = 0V 6 µA T SD Thermal Shutdown Threshold150 °C θJA Thermal Resistance TJ Junction to ambient temperature resistance (Note 6)22 °C/W θJAThermal ResistanceMR Package, Junction to ambient temperature resistance (Note 7)60°C/W 4L M 22676Note 1:Absolute Maximum Ratings indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the recommended Operating Ratings is not implied. The recommended Operating Ratings indicate conditions at which the device is functional and should not be operated beyond such conditions.Note 2:The absolute maximum specification of the ‘SW to GND’ applies to DC voltage. An extended negative voltage limit of -10V applies to a pulse of up to 50ns.Note 3:ESD was applied using the human body model, a 100 pF capacitor discharged through a 1.5 k Ω resistor into each pin.Note 4:Typical values represent most likely parametric norms at the conditions specified and are not guaranteed.Note 5:Min and Max limits are 100% production tested at 25°C. Limits over the operating temperature range are guaranteed through correlation using Statistical Quality Control (SQC) methods. Limits are used to calculate National’s Average Outgoing Quality Level (AOQL).Note 6:The value of θJA for the TO-263 THIN (TJ) package of 22°C/W is valid if package is mounted to 1 square inch of copper. The θJA value can range from 20 to 30°C/W depending on the amount of PCB copper dedicated to heat transfer. See application note AN-1797 for more information.Note 7:The value of θJA for the PSOP-8 exposed pad (MR) package of 60°C/W is valid if package is mounted to 1 square inch of copper. The θJA value can range from 42 to 115°C/W depending on the amount of PCB copper dedicated to heat transfer.Typical Performance CharacteristicsUnless otherwise specified the following conditions apply: Vin =12V, T J = 25°C.Efficiency vs I OUT and V INV OUT = 3.3V30076527Normalized Switching Frequency vs Temperature30076504Current Limit vs Temperature30076503Normalized R DS(ON) vs Temperature30076508LM22676Feedback Bias Current vs Temperature30076505Normalized Enable Threshold Voltage vs Temperature30076510Standby Quiescent Current vs Input Voltage 30076506Normalized Feedback Voltage vs Temperature30076507Normalized Feedback Voltage vs Input Voltage30076509 6L M 22676Typical Application Circuit and Block Diagram30076514FIGURE 1. 3.3V VOUT, 3A LM22676Detailed Operating DescriptionThe LM22676 switching regulator features all of the functions necessary to implement an efficient high voltage buck regu-lator using a minimum of external components. This easy to use regulator integrates a 42V N-Channel switch with an out-put current capability of 3A. The regulator control method is based on voltage mode control with input voltage feed for-ward. The loop compensation is integrated into the LM22676so that no external compensation components need to be se-lected or utilized. Voltage mode control offers short minimum on-times allowing short duty-cycles necessary in high input voltage applications. The operating frequency is fixed at 500kHz to allow for small external components while avoiding excessive switching losses. The output voltage can be set as low as 1.285V with the -ADJ device. Fault protection features include current limiting, thermal shutdown and remote shut-down capability. The device is available in the TO-263 THIN and PSOP-8 packages featuring an exposed pad to aid ther-mal dissipation.The functional block diagram with typical application of the LM22676 are shown in Figure 1.The internal compensation of the -ADJ option of the LM22676is optimized for output voltages up to 5V. If an output voltage of 5V or higher is needed, the -5.0 fixed output voltage option with an additional external resistive feedback voltage divider may also be used.Precision EnableThe precision enable pin (EN) can be used to shut down the power supply. Connecting this pin to ground or to a voltage less than typical 1.6V will completely turn off the regulator.The current drain from the input supply when off is typically 25 µA with 12V input voltage. The power consumed during this off state is mostly defined by an internal 2 M Ω resistor to VIN. The enable pin has an internal pull-up current source of approximately 6 µA. When driving the enable pin, the high voltage level for the on condition should not exceed the 6V absolute maximum limit. When enable control is not required,the EN pin should be left floating. The precision feature en-ables simple sequencing of multiple power supplies with a resistor divider from another power supply.Maximum Duty-Cycle / Dropout VoltageThe typical maximum duty-cycle is 85% at 500 kHz switching frequency. This corresponds to a typical minimum off-time of 300 ns. When operating at switching frequencies higher than 500 kHz, the 300 ns minimum off-time results in a lower max-imum duty-cycle limit than 85%. This forced off-time is impor-tant to provide enough time for the Cboot capacitor to charge during each cycle.The lowest input voltage required to maintain operation is:Where V D is the forward voltage drop across the re-circulating Schottky diode and V Q is the voltage drop across the internal power N-FET of the LM22676. The R DS(ON) of the FET is specified in the electrical characteristics section of this datasheet to calculate V Q according to the FET current. F is the switching frequency.Minimum Duty-CycleBesides a minimum off-time, there is also a minimum on-time which will take effect when the output voltage is adjusted very low and the input voltage is very high. Should the operation require a shorter minimum on-time than the typical 100 ns,individual switching pulses will be skipped.where D is the duty-cycle.Current LimitWhen the power switch turns on, the slight capacitance load-ing of the Schottky diode, D1, causes a leading-edge current spike with an extended ringing period. This spike can cause the current limit comparator to trip prematurely. A leading edge blanking time (T BLK ) of 110 ns (typical) is used to avoid sampling the spike.When the switch current reaches the current limit threshold,the switch is immediately turned off and the internal switching frequency is reduced. This extends the off time of the switch to prevent a steady state high current condition. As the switch current falls below the current limit threshold, the switch cur-rent will attempt to turn on. If a load fault continues, the switch will again exceed the threshold and turn off. This will result in a low duty-cycle pulsing of the power switch to minimize the overall fault condition power dissipation.The switching frequency will reduce (fold back) if the overload condition causes the output voltage to be 72.4% (typical) of the adjusted output voltage.The current limit will only protect the inductor from a runaway condition if the LM22676 is operating in its safe operating area. A runaway condition of the inductor is potentially catas-trophic to the application. For every design, the safe operating area needs to be calculated. Factors in determining the safe operating area are the switching frequency, input voltage,output voltage, minimum on-time and feedback voltage dur-ing an over current condition.As a first pass check, if the following equation holds true, a given design is considered in a safe operating area and the current limit will protect the circuit:V IN x T BLK x F < V OUT x 0.724If the equation above does not hold true, the following sec-ondary equation will need to hold true to be in safe operating area:If both equations do not hold true, a particular design will not have an effective current limit function which might damage the circuit during startup, over current conditions, or steady state over current and short circuit condition. Oftentimes a reduction of the maximum input voltage will bring a design into the safe operating area.Soft-StartThe soft-start feature allows the regulator to gradually reach the initial steady state operating point, thus reducing start-up stresses and surges. The soft-start is fixed to 500 µs (typical)start-up time and cannot be modified.8L M 22676Boot PinThe LM22676 integrates an N-Channel FET switch and as-sociated floating high voltage level shift / gate driver. This gate driver circuit works in conjunction with an internal diode and an external bootstrap capacitor. A 0.01 µF ceramic capacitor connected with short traces between the BOOT pin and the SW pin is recommended to effectively drive the internal FET switch. During the off-time of the switch, the SW voltage is approximately -0.5V and the external bootstrap capacitor is charged from the internal supply through the internal boot-strap diode. When operating with a high PWM duty-cycle, the buck switch will be forced off each cycle to ensure that the bootstrap capacitor is recharged. See the maximum duty-cy-cle section for more details.Thermal ProtectionInternal Thermal Shutdown circuitry protects the LM22676 in the event the maximum junction temperature is exceeded.When activated, typically at 150°C, the regulator is forced into a low power reset state. There is a typical hysteresis of 15degrees.Internal CompensationThe LM22676 has internal compensation designed for a sta-ble loop with a wide range of external power stage compo-nents.Insuring stability of a design with a specific power stage (in-ductor and output capacitor) can be tricky. The LM22676stability can be verified over varying loads and input and out-put voltages using WEBENCH® Designer online circuit sim-ulation tool at . A quick start spreadsheet can also be downloaded from the online product folder.The internal compensation of the -ADJ option of the LM22676is optimized for output voltages below 5V. If an output voltage of 5V or higher is needed, the -5.0 option with an additional external resistor divider may also be used.The typical location of the internal compensation poles and zeros as well as the DC gain is given in Table 1. The LM22676has internal type III compensation allowing for the use of most output capacitors including ceramics.This information can be used to calculate the transfer function from the FB pin to the internal compensation node (input to the PWM comparator in the block diagram).TABLE 1.Corners Frequency Pole 1150 kHz Pole 2250 kHz Pole 3100 Hz Zero 1 1.5 kHz Zero 215 kHz DC gain37.5 dBFor the power stage transfer function the standard voltage mode formulas for the double pole and the ESR zero apply:The peak ramp level of the oscillator signal feeding into the PWM comparator is V IN /10 which equals a gain of 20dB of this modulator stage of the IC. The -5.0 fixed output voltage option has twice the gain of the compensation transfer func-tion compared to the -ADJ option which is 43.5dB instead of 37.5dB.Generally, calculation as well as simulation can only aid in selecting good power stage components. A good design prac-tice is to test for stability with load transient tests or loop measurement tests. Application note AN-1889 shows how to easily perform a loop transfer function measurement with only an oscilloscope and a function generator.Application InformationEXTERNAL COMPONENTSThe following design procedures can be used to design a non-synchronous buck converter with the LM22676.InductorThe inductor value is determined based on the load current,ripple current, and the minimum and maximum input voltage.To keep the application in continuous current conduction mode (CCM), the maximum ripple current, I RIPPLE , should be less than twice the minimum load current.The general rule of keeping the inductor current peak-to-peak ripple around 30% of the nominal output current is a good compromise between excessive output voltage ripple and ex-cessive component size and cost. When selecting the induc-tor ripple current ensure that the peak current is below the minimum current limit as given in the Electrical Characteris-tics section. Using this value of ripple current, the value of inductor, L, is calculated using the following formula:where F is the switching frequency which is 500 kHz (typical).This procedure provides a guide to select the value of the inductor L. The nearest standard value will then be used in the circuit.Increasing the inductance will generally slow down the tran-sient response but reduce the output voltage ripple amplitude.Reducing the inductance will generally improve the transient response but increase the output voltage ripple.The inductor must be rated for the peak current, I PK+, to pre-vent saturation. During normal loading conditions, the peak current occurs at maximum load current plus maximum ripple.Under an overload condition as well as during load transients,the peak current is limited to 4.2A typical (5.5A maximum).This requires that the inductor be selected such that it can run at the maximum current limit and not only the steady state current.Depending on inductor manufacturer, the saturation rating is defined as the current necessary for the inductance to reduce by 30% at 20°C. In typical designs the inductor will run at higher temperatures. If the inductor is not rated for enough current, it might saturate and due to the propagation delay of the current limit circuitry, the power supply may get damaged.Input CapacitorGood quality input capacitors are necessary to limit the ripple voltage at the VIN pin while supplying most of the switch cur-rent during on-time. When the switch turns on, the current into the VIN pin steps to the peak value, then drops to zero at turn-9LM22676off. The average current into VIN during switch on-time is theload current. The input capacitance should be selected forRMS current, IRMS, and minimum ripple voltage. A good ap-proximation for the required ripple current rating necessary isIRMS> IOUT/ 2.Quality ceramic capacitors with a low ESR should be selectedfor the input filter. To allow for capacitor tolerances and volt-age effects, multiple capacitors may be used in parallel. If stepinput voltage transients are expected near the maximum rat-ing of the LM22676, a careful evaluation of ringing and pos-sible voltage spikes at the VIN pin should be completed. Anadditional damping network or input voltage clamp may berequired in these cases.Usually putting a higher ESR electrolytic input capacitor inparallel to the low ESR bypass capacitor will help to reduceexcessive voltages during a line transient and will also movethe resonance frequency of the input filter away from the reg-ulator bandwidth.Output CapacitorThe output capacitor can limit the output ripple voltage andprovide a source of charge for transient loading conditions.Multiple capacitors can be placed in parallel. Very low ESRcapacitors such as ceramic capacitors reduce the output rip-ple voltage and noise spikes, while larger higher ESR capac-itors in parallel provide large bulk capacitance for transientloading conditions. An approximation for the output voltageripple is:where ΔILis the inductor ripple current.Cboot CapacitorThe bootstrap capacitor between the BOOT pin and the SWpin supplies the gate current to turn on the N-channel MOS-FET. The recommended value of this capacitor is 10 nF andshould be a good quality, low ESR ceramic capacitor.It is possible to put a small resistor in series with the Cbootcapacitor to slow down the turn-on transition time of the in-ternal N-channel MOSFET. Resistors in the range of 10Ω to50Ω can slow down the transition time. This can reduce EMIof a switched mode power supply circuit. Using such a seriesresistor is not recommended for every design since it will in-crease the switching losses of the application and makesthermal considerations more challenging.Resistor DividerFor the -5.0 option no resistor divider is required for 5V outputvoltage. The output voltage should be directly connected tothe FB pin. Output voltages above 5V can use the -5.0 optionwith a resistor divider as an alternative to the -ADJ option.This may offer improved loop bandwidth in some applications.See the Internal Compensation section for more details.For the -ADJ option no resistor divider is required for 1.285Voutput voltage. The output voltage should be directly con-nected to the FB pin. Other output voltages can use the -ADJoption with a resistor divider.The resistor values can be determined by the following equa-tions:-ADJ option:-5.0 option:Where VFB= 1.285V typical for the -ADJ option and 5V for the-5.0 option30076523FIGURE 2. Resistive Feedback DividerA maximum value of 10 kΩ is recommended for the sum ofR1 and R2 to keep high output voltage accuracy for the –ADJoption. A maximum of 2 kΩ is recommended for the -5.0 out-put voltage option. For the 5V fixed output voltage option, thetotal internal divider resistance is typically 9.93 kΩ.At loads less than 5 mA, the boot capacitor will not holdenough charge to power the internal high side driver. Theoutput voltage may droop until the boot capacitor isrecharged. Selecting a total feedback resistance to be below3 kΩ will provide some minimal load and can keep the outputvoltage from collapsing in such low load conditions.Catch DiodeA Schottky type re-circulating diode is required for allLM22676 applications. Ultra-fast diodes which are not Schot-tky diodes are not recommended and may result in damageto the IC due to reverse recovery current transients. The nearideal reverse recovery characteristics and low forward volt-age drop of Schottky diodes are particularly important diodecharacteristics for high input voltage and low output voltageapplications common to the LM22676. The reverse recoverycharacteristic determines how long the current surge lastseach cycle when the N-channel MOSFET is turned on. Thereverse recovery characteristics of Schottky diodes mini-mizes the peak instantaneous power in the switch occurringduring turn-on for each cycle. The resulting switching lossesare significantly reduced when using a Schottky diode. Thereverse breakdown rating should be selected for the maxi-mum VIN, plus some safety margin. A rule of thumb is to selecta diode with the reverse voltage rating of 1.3 times the max-imum input voltage.The forward voltage drop has a significant impact on the con-version efficiency, especially for applications with a low outputvoltage. ‘Rated’ current for diodes varies widely from variousmanufacturers. The worst case is to assume a short circuitload condition. In this case the diode will carry the output cur-rent almost continuously. For the LM22676 this current canbe as high as 4.2A (typical). Assuming a worst case 1V drop 10LM22676across the diode, the maximum diode power dissipation can be as high as 4.2W.Circuit Board LayoutBoard layout is critical for switching power supplies. First, the ground plane area must be sufficient for thermal dissipation purposes. Second, appropriate guidelines must be followed to reduce the effects of switching noise. Switch mode con-verters are very fast switching devices. In such devices, the rapid increase of input current combined with the parasitic trace inductance generates unwanted L di/dt noise spikes. The magnitude of this noise tends to increase as the output current increases. This parasitic spike noise may turn into electromagnetic interference (EMI) and can also cause prob-lems in device performance. Therefore, care must be taken in layout to minimize the effect of this switching noise.The most important layout rule is to keep the AC current loops as small as possible. Figure 3 shows the current flow of a buck converter. The top schematic shows a dotted line which rep-resents the current flow during the FET switch on-state. The middle schematic shows the current flow during the FET switch off-state.The bottom schematic shows the currents referred to as AC currents. These AC currents are the most critical since current is changing in very short time periods. The dotted lines of the bottom schematic are the traces to keep as short as possible. This will also yield a small loop area reducing the loop induc-tance. To avoid functional problems due to layout, review the PCB layout example. Providing 3A of output current in a very low thermal resistance package such as the TO-263 THIN is challenging considering the trace inductances involved. Best results are achieved if the placement of the LM22676, the by-pass capacitor, the Schottky diode and the inductor are placed as shown in the example. It is also recommended to use 2oz copper boards or thicker to help thermal dissipation and to reduce the parasitic inductances of board traces.It is very important to ensure that the exposed DAP on the TO-263 THIN package is soldered to the ground area of the PCB to reduce the AC trace length between the bypass ca-pacitor ground and the ground connection to the LM22676. Not soldering the DAP to the board may result in erroneous operation due to excessive noise on the board.30076524FIGURE 3. Current Flow in a Buck ApplicationThermal ConsiderationsThe two highest power dissipating components are the re-circulating diode and the LM22676 regulator IC. The easiestmethod to determine the power dissipation within theLM22676 is to measure the total conversion losses (Pin –Pout) then subtract the power losses in the Schottky diodeand output inductor. An approximation for the Schottky diodeloss is:P = (1 - D) x IOUTx VDAn approximation for the output inductor power is:P = IOUT2 x R x 1.1,where R is the DC resistance of the inductor and the 1.1 factoris an approximation for the AC losses. The regulator has anexposed thermal pad to aid power dissipation. Adding severalvias under the device to the ground plane will greatly reducethe regulator junction temperature. Selecting a diode with anexposed pad will aid the power dissipation of the diode. Themost significant variables that affect the power dissipated bythe LM22676 are the output current, input voltage and oper-ating frequency. The power dissipated while operating nearthe maximum output current and maximum input voltage canbe appreciable. The junction-to-ambient thermal resistance ofthe LM22676 will vary with the application. The most signifi-cant variables are the area of copper in the PC board, thenumber of vias under the IC exposed pad and the amount offorced air cooling provided. The integrity of the solder con-nection from the IC exposed pad to the PC board is critical.Excessive voids will greatly diminish the thermal dissipationcapacity. The junction-to-ambient thermal resistance of theLM22676 TO-263 THIN and PSOP-8 packages are specifiedin the electrical characteristics table under the applicable con-ditions. For more information regarding the TO-263 THINpackage, refer to Application Note AN-1797 at.LM22676。

PSD03_03中文资料

PSD03thruPSD24CST ANDARD CAP ACIT ANCE TVS ARRA YOnly One Name Means ProTek’Tion™APPLICA TIONS✔ Laptop Computers✔ Cellular Phones ✔ Digital Cameras✔ Personnal Digital Assistant (PDA)IEC COMP A TIBILITY (EN61000-4)✔ 61000-4-2 (ESD): Air - 15kV , Contact - 8kV ✔ 61000-4-4 (EFT): 40A - 5/50ns✔ 61000-4-5 (Surge): 24A, 8/20µs - Level 2(Line-Ground) & Level 3(Line-Line)FEA TURES✔ Unidirectional: 500 Watts Peak Pulse Power per Line (tp = 8/20µs)✔ BidirectionalL 400 Watts Peak Pulse Power per Line (tp = 8/20µs)✔ Unidirectional & Bidirectional Configurations ✔ Replacement for MLV (0805)✔ Protects One Power or I/O Port ✔ ESD Protection > 40 kilovolts ✔ Low Clamping Voltage✔ Available in Multiple Voltage Types Ranging from 3V to 24V MECHANICAL CHARACTERISTICS✔ Molded JEDEC SOD-323✔ Weight 10 milligrams (Approximate)✔ Flammability Rating UL 94V-0✔ 8mm Tape and Reel Per EIA Standard 481✔ Device Marking: Marking Code & Polarity Band (Unidirectional Only)05118PIN CONFIGURA TIONSSOD-323UNIDIRECTIONALBIDIRECTIONALPSD24CDEVICE CHARACTERISTICSMAXIMUM RATINGS @ 25°C Unless Otherwise SpecifiedUndirectional: Peak Pulse Power (t p = 8/20µs) - See Fig. 1Operating T emperature SYMBOL VALUE -55°C to 150°C°C°C -55°C to 150°C Watts UNITS 500T J P PP T STGPARAMETERStorage T emperatureBidirectional: Peak Pulse Power (t p = 8/20µs) - See Fig. 1Watts 400P PP Note 1: Part numbers with an additional “C” suffix are bidirectional devices, i.e., PSD05C.Note 2: For Bidirectional Devices Only: Electrical characteristics apply in both directions.ELECTRICAL CHARACTERISTICS PER LINE @ 25°C Unless Otherwise SpecifiedPART NUMBER (See Notes 1-2)DEVICE MARKINGMINIMUM BREAKDOWN VOLTAGE@ 1mA V (BR)VOLTS MAXIMUM CLAMPING VOLTAGE (See Fig. 2)@ I P = 1AV C VOLTS MAXIMUM CLAMPING VOLTAGE (See Fig. 2)@8/20µs V C @ I PP TYPICAL CAPACITANCE@0V , 1 MHzC J pFPSD03PSD03C PSD05PSD05C PSD08PSD08C PSD12PSD12C PSD15PSD15C PSD18PSD18C PSD24PSD24C PSD36PSD36CA GB HC JD KE L G NF M R T4.04.06.06.08.58.513.313.316.716.720.020.026.726.740.040.06.57.09.89.813.413.419.019.024.024.029.029.043.043.060.060.010.9V @ 43.0A 10.9V @ 39.0A 13.5V @ 42.0A 14.5V @ 28.0A 16.9V @ 34.0A 18.5V @ 17.0A 25.9V @ 21.0A 29.5V @ 14.0A 30.0V @ 17.0A 33.0V @ 12.0A 40.0V @ 9.0A 40.0V @ 9.0A 49.0V @ 12.0A 46.2V @ 9.0A 75.0V @ 5.0A 75.0V @ 5.0A5002003501752501501505010040904088407535MAXIMUM LEAKAGE CURRENT@V WMI D µA 125125101010101111111111RATED ST AND-OFF VOLTAGEV WM VOLTS3.33.35.05.08.08.012.012.015.015.018.018.024.024.036.036.0PSD24CFIGU RE 50 1 2 3 4 5 6V R - Reverse Voltage - VoltsC - C a p a c i t a n c e - p F100200300400FIGU RE 2FIGU RE 1PEAK PULSE POWER VS PULSE TIME0.01 1 10 100 1,000 10,000t d - Pulse Duration - µs0 5 10 15 20 25 30t - Time - µs20406080100120I P P - P e a kP u l s e C u r r e n t - % o f I P P101001,00010,000P P P - P e ak P u l s e C u r r e n t - W a t t sGRAPHSFIGU RE 4OVERSHOOT & CLAMPING VOLTAGE FOR PSD03ESD Test Pulse: 25 kilovolt, 1/30ns (waveform)5 V o l t s p e r D i v i s i o n-55152535T L - Lead Temperature - °C20406080100% O f R a t e d P o w e rFIGU RE 3PSD24CCOPYRIGHT © ProTek Devices 2003SPECIFICATIONS: ProT ek reserves the right to change the electrical and or mechanical characteristics described herein without notice (except JEDEC).DESIGN CHANGES: ProT ek reserves the right to discontinue product lines without notice, and that the final judgement concerning selection and specifications is the buyer’s and that in furnishing engineering and technical assistance, ProTek assumes no responsibility with respect to the selection or specifications of such products.P ACKAGE OUTLINE & DIMENSIONSProTek Devices2929 South Fair Lane, Tempe, AZ 85282Tel: 602-431-8101 Fax: 602-431-2288E-Mail: sales@ Web Site: 。

6N134中文资料

6N134中⽂资料FeaturesDual Marked with Device Part Number and DSCC Drawing NumberManufactured and Tested on a MIL-PRF-38534 Certified LineQML-38534, Class H and K Five Hermetically Sealed Package Configurations Performance Guaranteed over -55°C to +125°C ? High Speed: 10 M Bit/sCMR: > 10,000 V/µs Typical 1500 Vdc Withstand Test Voltage2500 Vdc Withstand Test Voltage for HCPL-565X High Radiation Immunity 6N137, HCPL-2601, HCPL-2630/-31 Function Compatibility ? Reliability DataTTL Circuit CompatibilityApplicationsMilitary and SpaceHigh Reliability SystemsTransportation, Medical, and Life Critical SystemsLine ReceiverVoltage Level ShiftingIsolated Input Line Receiver Isolated Output Line Driver Logic Ground Isolation Harsh Industrial EnvironmentsIsolation for Computer,Communication, and Test Equipment SystemsDescriptionThese units are single, dual and quad channel, hermetically sealed optocouplers. The products are capable of operation and storage over the full military temperature range and can be purchased as either standard product or with full MIL-PRF-38534 Class Level H or K testing or from the appropri-ate DSCC Drawing. All devices are manufactured and tested on a MIL-PRF-38534 certified line and are included in the DSCC Quali-fied Manufacturers List QML-38534 for Hybrid Microcircuits.Quad channel devices areavailable by special order in the 16 pin DIP through hole packages.Truth Table(Positive Logic)Multichannel DevicesInput Output On (H)L Off (L)HFunctional DiagramMultiple Channel Devices AvailableSingle Channel DIP Input Enable Output On (H)H L Off (L)H H On (H)L H Off (L)LH*See matrix for available extensions.Hermetically Sealed, High Speed,High CMR, Logic Gate Optocouplers Technical Data6N134*81028HCPL-563X HCPL-663X HCPL-565X 5962-98001HCPL-268K HCPL-665X 5962-90855HCPL-560XCAUTION: It is advised that normal static precautions be taken in handling and assembly of this component to prevent damage and/or degradation which may be induced by ESD.V CC V OUTV E GNDThe connection of a 0.1 µF bypass capacitor between V CC and GND is recommended.Selection Guide–Package Styles and Lead Configuration OptionsPackage16 Pin DIP 8 Pin DIP 8 Pin DIP 8 Pin DIP 16 Pin Flat Pack 20 Pad LCCC Lead Style Through Hole Through Hole Through Hole Through Hole Unformed Leads Surface MountChannels 212242Common Channel V CC , GND None V CC , GND V CC , GND V CC , GND None WiringWithstand Test Voltage 1500 Vdc 1500 Vdc 1500 Vdc 2500 Vdc 1500 Vdc 1500 Vdc Agilent Part # & Options Commercial6N134*HCPL-5600HCPL-5630HCPL-5650HCPL-6650HCPL-6630MIL-PRF-38534, Class H 6N134/883BHCPL-5601HCPL-5631HCPL-5651HCPL-6651HCPL-6631MIL-PRF-38534, Class K HCPL-268K HCPL-560K HCPL-563K HCPL-665K HCPL-663K Standard Lead Finish Gold Plate Gold Plate Gold Plate Gold Plate Gold PlateSolder PadsSolder Dipped Option #200Option #200Option #200Option #200Butt Cut/Gold Plate Option #100Option #100Option #100Gull Wing/Soldered Option #300Option #300Option #300Class H SMD Part #Prescript for all below None 5962-None None None None Either Gold or Solder 8102801EX 9085501HPX 8102802PX 8102805PX 8102804FX 81028032XGold Plate 8102801EC 9085501HPC 8102802PC 8102805PC 8102804FCSolder Dipped 8102801EA 9085501HPA 8102802PA 8102805PA81028032A Butt Cut/Gold Plate 8102801UC 9085501HYC 8102802YC Butt Cut/Soldered 8102801UA 9085501HYA 8102802YA Gull Wing/Soldered 8102801TA 9085501HXA8102802ZA Class K SMD Part #Prescript for all below 5962-5962-5962-5962-5962-Either Gold or Solder 9800101KEX 9085501KPX 9800102KPX 9800104KFX 9800103K2XGold Plate 9800101KEC 9085501KPC 9800102KPC 9800104KFCSolder Dipped 9800101KEA 9085501KPA 9800102KPA 9800103K2AButt Cut/Gold Plate 9800101KUC 9085501KYC 9800102KYC Butt Cut/Soldered 9800101KUA 9085501KYA 9800102KYA Gull Wing/Soldered9800101KTA 9085501KXA 9800102KZA*JEDEC registered part.Each channel contains a GaAsP light emitting diode which isoptically coupled to an integrated high speed photon detector. The output of the detector is an open collector Schottky clamped transistor. Internal shields provide a guaranteed common mode transient immunityspecification of 1000 V/µs. For Isolation Voltage applications requiring up to 2500 Vdc, the HCPL-5650 family is also available. Package styles for these parts are 8 and 16 pin DIP through hole (case outlines P andE respectively), and 16 pin surface mount DIP flat pack(case outline F), leadless ceramic chip carrier (case outline 2).Devices may be purchased with a variety of lead bend and plating options. See Selection Guide Table for details. Standard Microcircuit Drawing (SMD)parts are available for each package and lead style.Because the same electrical die (emitters and detectors) are used for each channel of each device listed in this data sheet, absolute maximum ratings, recommended operating conditions, electrical specifications, and performance characteristics shown in the figures are identical for all parts.Occasional exceptions exist due to package variations and limitations,and are as noted. Additionally, the same package assembly processes and materials are used in all devices. These similarities give justification for the use of data obtained from one part torepresent other parts’ performance for reliability and certain limited radiation test results.Outline Drawings16 Pin DIP Through Hole, 2 ChannelsFunctional DiagramsNote: All DIP and flat pack devices have common V CC and ground. Single channel DIP has an enable pin 7. LCCC (leadless ceramic chip carrier) package has isolated channels with separate VCC and ground connections. All diagrams are “top view.”Leaded Device MarkingLeadless Device MarkingNOTE: DIMENSIONS IN MILLIMETERS (INCHES).COMPLIANCE INDICATOR,*DATE CODE, SUFFIX (IF NEEDED)COUNTRY OF MFR.Agilent CAGE CODE*Agilent DESIGNATORDSCC SMD*PIN ONE/ ESD IDENTAgilent P/N DSCC SMD** QUALIFIED PARTS ONLYCOMPLIANCE INDICATOR,*DATE CODE, SUFFIX (IF NEEDED)DSCC SMD*Agilent CAGE CODE*Agilent DESIGNATORCOUNTRY OF MFR.Agilent P/N PIN ONE/ ESD IDENTDSCC SMD** QUALIFIED PARTS ONLYOutline Drawings (continued)16 Pin Flat Pack, 4 Channels8 Pin DIP Through Hole, 2 Channels 2500 Vdc Withstand Test Voltage20 Terminal LCCC Surface Mount,2Channels8 Pin DIP Through Hole, 1 and 2 Channels0.36 (0.014)NOTE: DIMENSIONS IN MILLIMETERS (INCHES).2.29 (0.090) 2.79 (0.110)NOTE: DIMENSIONS IN MILLIMETERS (INCHES).NOTE: DIMENSIONS IN MILLIMETERS (INCHES).NOTE: DIMENSIONS IN MILLIMETERS (INCHES). SOLDER THICKNESS 0.127 (0.005) MAX.Hermetic Optocoupler OptionsRecommended Operating ConditionsParameterSymbol Min.Max.Units Input Current, Low Level, Each Channel I FL 0250µA Input Current, High Level, Each Channel*I FH 1020mA Supply Voltage, OutputV CC 4.55.5VFan Out (TTL Load) Each ChannelN6*Meets or exceeds DSCC SMD and JEDEC requirements.Absolute Maximum Ratings(No derating required up to +125°C)Storage Temperature Range, T S ...................................-65°C to +150°C Operating Temperature, T A..........................................-55°C to +125°C Case Temperature, T C ................................................................+170°C Junction Temperature, T J ...........................................................+175°C Lead Solder Temperature ...............................................260°C for 10 s Peak Forward Input Current, I F PK , (each channel,≤1 ms duration)......................................................................40 mA Average Input Forward Current, I F AVG (each channel)................20 mA Input Power Dissipation (each channel).....................................35 mW Reverse Input Voltage, V R (each channel).........................................5 V Supply Voltage, V CC (1 minute maximum)........................................7 V Output Current, I O (each channel)...............................................25 mA Output Power Dissipation (each channel). (40)mW Output Voltage, V O (each channel)..................................................7 V*Package Power Dissipation, P D (each channel)........................200 mW*Selection for higher output voltages up to 20 V is available.Single Channel Product OnlyEmitter Input Voltage, V E ...............................................................5.5 VNote enable pin 7. An external 0.01 µF to 0.1 µF bypass capacitor must be connected between V CC and ground for each package type.8 Pin Ceramic DIP Single Channel SchematicESD Classification(MIL-STD-883, Method 3015)HCPL-5600/01/0K ...............................................................(?), Class 16N134, 6N134/883B, HCPL-5630/31/3K, HCPL-5650/51, HCPL-6630/31/3K and HCPL-6650/51/5K.......................(Dot), Class 3Electrical Characteristics (T= -55°C to +125°C, unless otherwise specified)*Identified test parameters for JEDEC registered parts.**All typical values are at V CC = 5 V , T A = 25°C. Recommended Operating Conditions (cont’d.)Single Channel Product Only [10]ParameterSymbol Min.Max.Units High Level Enable Voltage V EH 2.0V CC V Low Level Enable VoltageV EL0.8VElectrical Characteristics, (Contd.) T= -55°C to +125°C unless otherwise specifiedSingle Channel Product Only Low Level I EL V CC = 5.5 V,1, 2, 3-1.45-2.0mA Enable Current V E = 0.5 V High Level V EH 1, 2, 3 2.0V10Enable Voltage Low Level V EL 1, 2, 30.8VEnable Voltage*Identified test parameters for JEDEC registered part.**All typical values are at V CC = 5 V , T A = 25°C.Typical Characteristics, T = 25°C, V = 5 VDual and Quad Channel Product Only Input-Input I I-I 0.5nA Relative Humidity = 45%4Leakage CurrentV I-I = 500 V, t = 5 s Resistance (Input-Input)R I-I 1012V I-I = 500 V 4Capacitance (Input-Input)C I-I0.55pF f = 1 MHz4Notes:1. Each channel.2. All devices are considered two-terminal devices; I I-O is measured between all input leads or terminals shorted together and alloutput leads or terminals shorted together.3. Measured between each input pair shorted together and all output connections for that channel shorted together.4. Measured between adjacent input pairs shorted together for each multichannel device.5. t PHL propagation delay is measured from the 50% point on the leading edge of the input pulse to the 1.5 V point on the leadingedge of the output pulse. The t PLH propagation delay is measured from the 50% point on the trailing edge of the input pulse to the1.5 V point on the trailing edge of the output pulse.6. The HCPL-6630, HCPL-6631, and HCPL-663K dual channel parts function as two independent single channel units. Use the singlechannel parameter limits for each channel.7. CM L is the maximum rate of rise of the common mode voltage that can be sustained with the output voltage in the logic low state(V O < 0.8 V). CM H is the maximum rate of fall of the common mode voltage that can be sustained with the output voltage in the logic high state (V O > 2.0 V).8. This is a momentary withstand test, not an operating condition.9. It is essential that a bypass capacitor (0.01 to 0.1 µF, ceramic) be connected from V CC to ground. Total lead length between bothends of this external capacitor and the isolator connections should not exceed 20 mm.10. No external pull up is required for a high logic state on the enable input.11. The t ELH enable propagation delay is measured from the 1.5 V point on the trailing edge of the enable input pulse to the 1.5 Vpoint on the trailing edge of the output pulse.12. The t EHL enable propagation delay is measured from the 1.5 V point on the leading edge of the enable input pulse tothe 1.5 Vpoint on the leading edge of the output pulse.13. Standard parts receive 100% testing at 25°C (Subgroups 1 and 9). SMD and 883B parts receive 100% testing at 25, 125, and-55°C (Subgroups 1 and 9, 2 and 10, 3 and 11, respectively).14. Parameters are tested as part of device initial characterization and after design and process changes. Parameters are guaranteedto limits specified for all lots not specifically tested.15. Not required for 6N134, 6N134/883B, 8102801, HCPL-268K and 5962-9800101 types.16. Required for 6N134, 6N134/883B, 8102801, HCPL-268K and 5962-9800101 types.17. Not required for HCPL-5650, HCPL-5651 and 8102805 types.18. Required for HCPL-5650, HCPL-5651 and 8102805 types only.Figure 1. High Level Output Currentvs. Temperature.5 VV O * C L INCLUDES PROBE AND STRAY WIRING CAPACITANCE. Figure 4. Test Circuit for t PHL and t PLH .*I +5 V OUTPUT V O MONITORING NODEFigure 7. Test Circuit for Common Mode Transient Immunity and Typical Waveforms.11OUTPUT V OMONITORINGNODET A = +125 °C* ALL CHANNELS TESTED SIMULTANEOUSLY.V CCI O = 25 mAFigure 10. Operating Circuit for Burn-In and Steady State Life Tests. Figure 8. Test Circuit for t EHL and t ELH.Figure 9. Enable Propagation Delayvs. Temperature.MIL-PRF-38534 Class H,Class K, and DSCC SMDTest ProgramAgilent’s Hi-Rel Optocouplers arein compliance with MIL-PRF-38534 Classes H and K. Class Hand Class K devices are also incompliance with DSCC drawings81028, 5962-90855 and 5962-98001.Testing consists of 100% screen-ing and quality conformanceinspection to MIL-PRF-38534./doc/4e2d970a03d8ce2f006623a8.htmlData subject to change.Copyright ? 1999 Agilent TechnologiesObsoletes 5968-4743E5968-9407E (10/00)。

1SMA5918BT3G中文资料

1SMA5913BT3 Series1.5 Watt PlasticSurface MountZener Voltage RegulatorsThis complete new line of 1.5 Watt Zener Diodes offers the following advantages.Features•Standard Zener Breakdown V oltage Range − 3.3 V to 68 V •ESD Rating of Class 3 (>16 kV) per Human Body Model •Flat Handling Surface for Accurate Placement •Package Design for Top Slide or Bottom Circuit Board Mounting •Low Profile Package•Ideal Replacement for MELF Packages•Pb−Free Packages are AvailableMechanical Characteristics:CASE:V oid-free, transfer-molded plasticFINISH:All external surfaces are corrosion resistant with readily solderable leadsMAXIMUM CASE TEMPERATURE FOR SOLDERING PURPOSES: 260°C for 10 secondsPOLARITY:Cathode indicated by molded polarity notch or cathode bandFLAMMABILITY RATING:UL 94 V−0 @ 0.125 inMAXIMUM RATINGSRating Symbol Value UnitDC Power Dissipation @ T L = 75°C, Measured Zero Lead Length (Note 1) Derate above 75°CThermal Resistance, Junction−to−LeadP DR q JL1.52050WmW/°C°C/WDC Power Dissipation @ T A = 25°C (Note 2) Derate above 25°CThermal Resistance, Junction−to−AmbientP DR q JA0.54.0250WmW/°C°C/WOperating and Storage Temperature Range T J, T stg−65 to+150°CStresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.1. 1 in square copper pad, FR−4 board.2.FR−4 Board, using ON Semiconductor minimum recommended footprint.Device Package Shipping†ORDERING INFORMATION1SMA59xxBT3SMA5000/Tape & Reel1SMA59xxBT3G SMA(Pb−Free)5000/Tape & Reel†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our T ape and Reel Packaging Specifications Brochure, BRD8011/D.See specific marking information in the device marking column of the Electrical Characteristics table on page 2 of this data sheet.DEVICE MARKING INFORMATIONELECTRICAL CHARACTERISTICS (T A = 25°C unlessotherwise noted, V F = 1.5 V Max. @ I F = 200 mA for all types)Symbol ParameterV Z Reverse Zener Voltage @ I ZT I ZT Reverse CurrentZ ZT Maximum Zener Impedance @ I ZT I ZK Reverse CurrentZ ZK Maximum Zener Impedance @ I ZK I R Reverse Leakage Current @ V R V R Reverse Voltage I F Forward Current V F Forward Voltage @ I F I ZMMaximum DC Zener CurrentELECTRICAL CHARACTERISTICS (T A = 25°C unless otherwise noted, V F = 1.5 V Max. @ I F = 200 mA for all types)Device* (Note 3)Device Marking Zener Voltage (Note 4)Zener Impedance Leakage CurrentI ZM V Z (Volts)@ I ZT Z ZT @ I ZTZ ZK @ I ZK I R @ V R Min Nom Max mA W W mA m A Volts mA(dc)1SMA5913BT3, G 813B 3.13 3.3 3.47113.610500 1.050 1.04551SMA5914BT3, G 814B 3.42 3.6 3.78104.29.0500 1.035.5 1.04171SMA5915BT3, G 815B 3.70 3.9 4.1096.17.5500 1.012.5 1.03851SMA5916BT3, G 816B 4.08 4.3 4.5287.2 6.0500 1.0 2.5 1.03491SMA5917BT3, G 817B 4.46 4.7 4.9479.8 5.0500 1.0 2.5 1.53191SMA5918BT3, G 818B 4.84 5.1 5.3673.5 4.0350 1.0 2.5 2.02941SMA5919BT3, G 819B 5.32 5.6 5.8866.9 2.0250 1.0 2.5 3.02681SMA5920BT3, G 820B 5.89 6.2 6.5160.5 2.0200 1.0 2.5 4.02421SMA5921BT3, G 821B 6.46 6.87.1455.1 2.5200 1.0 2.5 5.22211SMA5922BT3, G 822B 7.127.57.8850 3.04000.5 2.5 6.02001SMA5923BT3, G 823B 7.798.28.6145.7 3.54000.5 2.5 6.51831SMA5924BT3, G 824B 8.649.19.5641.2 4.05000.5 2.57.01651SMA5925BT3, G 825B 9.51010.537.5 4.55000.25 2.58.01501SMA5926BT3, G 826B 10.451111.5534.1 5.55500.250.58.41361SMA5927BT3, G 827B 11.41212.631.2 6.55500.250.59.11251SMA5928BT3, G 828B 12.351313.6528.87.05500.250.59.91151SMA5929BT3, G 829B 14.251515.75259.06000.250.511.41001SMA5930BT3, G 830B 15.21616.823.4106000.250.512.2941SMA5931BT3, G 831B 17.11818.920.8126500.250.513.7831SMA5932BT3, G 832B 19202118.7146500.250.515.2751SMA5933BT3, G 833B 20.92223.11717.56500.250.516.7681SMA5934BT3, G 834B 22.82425.215.6197000.250.518.2631SMA5935BT3, G 835B 25.652728.3513.9237000.250.520.6561SMA5936BT3, G 836B 28.53031.512.5267500.250.522.8501SMA5937BT3, G 837B 31.353334.6511.4338000.250.525.1451SMA5938BT3, G 838B 34.23637.810.4388500.250.527.4421SMA5939BT3, G 839B 37.053940.959.6459000.250.529.7381SMA5940BT3, G840B40.854345.158.7539500.250.532.7351SMA5941BT3, G 841B 44.654749.358.06710000.250.535.8321SMA5942BT3, G 842B 48.455153.557.37011000.250.538.8291SMA5943BT3, G 843B 53.25658.8 6.78613000.250.542.6271SMA5944BT3, G 844B 58.96265.1 6.010015000.250.547.1241SMA5945BT3, G 845B 64.66871.4 5.512017000.250.551.7223.Tolerance and Voltage Regulation Designation − The type number listed indicates a tolerance of ±5%.4.V Z limits are to be guaranteed at thermal equilibrium.*The “G” suffix indicates Pb−Free package available.Figure 1. Steady State Power DeratingFigure 2. V Z − 3.3 thru 10 VoltsT, TEMPERATURE (°C)Figure 3. V Z = 12 thru 68 VoltsP D , M A X I M U MP O W E R D I S S I P A T I O N (W A T T S )I Z , Z E N E R C U R R E N T (m A )Z Z , D Y N A M I C I M P ED A N CE (O H M S )1002468101010.1V Z , ZENER VOLTAGE (VOLTS)1001010.1010203040V Z , ZENER VOLTAGE (VOLTS)V Z , ZENER VOLTAGE (VOLTS)1001050Figure 4. Zener Voltage − 3.3 to 12 VoltsFigure 5. Zener Voltage − 12 to 68 Volts Figure 6. Effect of Zener VoltageI Z , Z E N E R C U R R E N T (m A )6070801086420−2−4V Z , ZENER VOLTAGE (VOLTS), T E M P E R A T U R E C O E F F I C I E N T (m V / C )°θV Z 10070503020101020305070100V Z , ZENER VOLTAGE (VOLTS), T E M P E R A T U R E C O E F F I C I E N T (m V / C )°θV ZPACKAGE DIMENSIONSSMACASE 403D−02ISSUE Cǒmm inchesǓSCALE 8:1*For additional information on our Pb−Free strategy and solderingdetails, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.SOLDERING FOOTPRINT*DIM A MIN NOM MAX MINMILLIMETERS1.912.16 2.410.075INCHES A10.050.100.150.002b 1.27 1.45 1.630.050c 0.150.280.410.006D 2.29 2.60 2.920.090E 4.06 4.32 4.570.160L0.761.14 1.520.0300.0850.0950.0040.0060.0570.0640.0110.0160.1030.1150.1700.1800.0450.060NOM MAX 4.83 5.21 5.590.1900.2050.220H E STYLE 1:PIN 1.CATHODE (POLARITY BAND)2.ANODENOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: INCH.3.403D−01 OBSOLETE, NEW STANDARD IS 403D−02.ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

Q65110A1458中文资料

LB W5SG,LV W5SGGolden Dragon®Vorläufige Daten /Preliminary Data2003-10-291Besondere Merkmale•Gehäusetyp:weißes SMD-Gehäuse,farbloser klarer Verguss•Besonderheit des Bauteils:Punktlichtquelle mit hoher Lichtausbeute bei geringem Platzbedarf•Wellenlänge:470nm (blau),503nm (verde)•Abstrahlwinkel:Lambertscher Strahler (120°)•Technologie:InGaN•optischer Wirkungsgrad:6lm/W (blau),25lm/W (verde)•Gruppierungsparameter:Lichtstärke,Wellenlänge•Verarbeitungsmethode:für alle SMT-Bestücktechniken geeignet •Lötmethode:IR Reflow Löten•Vorbehandlung:nach JEDEC Level 4•Gurtung:24-mm Gurt mit 800/Rolle,ø180mm •ESD-Festigkeit:ESD-sicher bis 2kV nach JESD22-A114-B Anwendungen•Ampelanwendung (verde)•Hinterleuchtung (LCD,Schalter,Tasten,Displays,Werbebeleuchtung,Allgemeinbeleuchtung)•Innenbeleuchtung im Automobilbereich (z.B.Instrumentenbeleuchtung,u.ä.)•Ersatz von Kleinst-Glühlampen•Markierungsbeleuchtung (z.B.Stufen,Fluchtwege,u.ä.)•Signal-und Symbolleuchten •ScannerFeatures•package:white SMD package,colorless clear •feature of the device:point lightsource with high luminous efficiency and low space•wavelength:470nm (blue),503nm (verde)•viewing angle:Lambertian Emitter (120°)•technology:InGaN•optical efficiency:6lm/W (blue),25lm/W (verde)•grouping parameter:luminous intensity,wavelength•assembly methods:suitable for all SMT assembly methods•soldering methods:IR reflow soldering •preconditioning:acc.to JEDEC Level 4•taping:24-mm tape with 800/reel,ø180mm •ESD-withstand voltage:up to 2kV acc.to JESD22-A114-BApplications•traffic lights (verde)•backlighting (LCD,switches,keys,displays,illuminated advertising,general lighting)•interior automotive lighting (e.g.dashboard backlighting,etc.)•substitution of micro incandescent lamps •marker lights (e.g.steps,exit ways,etc.)•signal and symbol luminaire •scanners2003-10-292Anm.:-35gesamter Farbbereich,Lieferung in Einzelgruppen (siehe Seite 5)Note:-35Total color tolerance range,delivery in single groups (please see page 5)Bestellinformation Ordering Information TypTypeEmissions-farbe Color of EmissionLichtstrom 1)Seite 14Luminous Flux 1)page 14I F =350mA ΦV (mlm)Lichtst ärke 2)Seite 14Luminous Intensity 2)page 14I F =350mA I V (mcd)BestellnummerOrdering CodeLB W5SG-DYEZ-35blue 5200...112002700(typ.)Q65110A1470LV W5SG-GYHY-35verde21000 (45000)11000(typ.)Q65110A14582003-10-293Maximum Ratings Bezeichnung ParameterSymbol SymbolWerte ValuesEinheit Unit BetriebstemperaturOperating temperature range T op –40…+100°C LagertemperaturStorage temperature range T stg –40…+100°C Sperrschichttemperatur Junction temperature T j 110°C Durchlassstrom Forward current (T A =25°C)I F500mASto ßstrom Surge currentt ≤ 10µs,D =0.005,T A =25°C I FM1500mASperrspannung 3)Seite 14Reverse voltage 3)page 14(T A =25°C)V R1.2VLeistungsaufnahme Power consumption (T A =25°C)P tot1.5WW ärmewiderstand 4)Seite 14Thermal resistance 4)page 14Sperrschicht/L ötpad Junction/solder pointR th JS9K/W2003-10-294*Einzelgruppen siehe Seite 5Individual groups on page 5Characteristics (T A =25°C)Bezeichnung ParameterSymbol SymbolWerte ValuesEinheit Unit LBLV Wellenl änge des emittierten Lichtes (typ.)Wavelength at peak emission I F =350mAλpeak 465501nmDominantwellenl änge 5)Seite 14Dominant wavelength 5)page 14I F =350mAλdom470*±6503*±6nmSpektrale Bandbreite bei 50%I rel max (typ.)Spectral bandwidth at 50%I rel max I F =350mA∆λ2530nmAbstrahlwinkel bei 50%I V (Vollwinkel)(typ.)Viewing angle at 50%I V 2ϕ120120Grad deg.Durchlassspannung 6)Seite 14(min.)Forward voltage 6)page 14(typ.)I F =350mA (max.)V F V F V F 3.13.84.0 3.13.84.0V V VSperrstromReverse current (max.)V R =1.2VI R 100100µATemperaturkoeffizient von λpeak (typ.)Temperature coefficient of λpeak I F =350mA;–10°C ≤ T ≤ 100°C TC λpeak 0.050.03nm/KTemperaturkoeffizient von λdom (typ.)Temperature coefficient of λdom I F =350mA;–10°C ≤ T ≤ 100°C TC λdom 0.040.05nm/KTemperaturkoeffizient von V F (typ.)Temperature coefficient of V F I F =350mA;–10°C ≤ T ≤ 100°C TC V–5.0–3.6mV/KOptischer Wirkungsgrad (typ.)Optical efficiency I F =350mAηopt625lm/W2003-10-295Anm.:Die Standardlieferform von Serientypen beinhaltet eine Familiengruppe.Diese besteht aus4Helligkeitsdrittelgruppen.Einzelne Helligkeitsdrittelgruppen sind nicht bestellbar.Note:The standard shipping format for serial types includes a family group of 4individual brightnessthird groups.Individual brightness third groups cannot be ordered.Anm.:In einer Verpackungseinheit /Gurt ist immer nur eine Gruppe f ür jede Selektion enthalten.Note:No packing unit /tape ever contains more than one group for each selection.Wellenl ängengruppen (Dominantwellenl änge)5)Seite 14Wavelength Groups (Dominant Wavelength)5)page 14Gruppe Group blueverdeEinheit Unitmin.max.min.max.3463467497501nm 4467471501505nm 5471475505509nmHelligkeits-Gruppierungsschema Brightness Groups Helligkeitsdrittelgruppe Brightness Third Group Lichtstrom 1)Seite 14Luminous Flux 1)page 14ΦV (mlm)Lichtst ärke 2)Seite 14Luminous Intensity 2)page 14I V (mcd)DY DZ EX EY EZ GY GZ HX HY5200...61006100...71007100...82008200...97009700...1120021000...2400024000...2800028000...3300033000 (39000)1800(typ.)2200(typ.)2500(typ.)2900(typ.)3400(typ.)7500(typ.)8600(typ.)10100(typ.)12000(typ.)Gruppenbezeichnung auf Etikett Group Name on Label Beispiel:GY-4Example:GY-4Helligkeitsdrittelgruppe Brightness Third Group Wellenl änge Wavelength GY4Relative spektrale Emission2)Seite14Relative Spectral Emission2)page14V(λ)=spektrale Augenempfindlichkeit/Standard eye response curve Irel=f(λ);T=25°C;I=350mAAbstrahlcharakteristik2)Seite14Radiation Characteristic2)page14I rel =f(2003-10-296Durchlassstrom2)Seite14Forward Current2)page14=f(V);T=25°CRelative Lichtstärke2)Seite14 Relative Luminous Intensity2)page14Relative Lichtstärke2)7)Seite14 Relative Luminous Intensity2)7)page142003-10-297Dominante Wellenlänge2)Seite14 Dominant Wavelength2)page14LB,λdom=f(I F);T A=25°CMaximal zulässiger Durchlassstrom Max.Permissible Forward CurrentI F =f(T)Dominante Wellenlänge2)Seite14Dominant Wavelength2page14)LV,λdom=f(I F);T A=25°C2003-10-298Zulässige Impulsbelastbarkeit I F=f(t p) Permissible Pulse Handling Capability Duty cycle D=parameter,T A=25°C,LB Zulässige Impulsbelastbarkeit I F=f(t p) Permissible Pulse Handling Capability Duty cycle D=parameter,T A=25°C,LV Zulässige Impulsbelastbarkeit I F=f(t p) Permissible Pulse Handling Capability Duty cycle D=parameter,T A=85°C,LB Zulässige Impulsbelastbarkeit I F=f(t p) Permissible Pulse Handling Capability Duty cycle D=parameter,T A=85°C,LV2003-10-299Maßzeichnung8)Seite14Package Outlines8)page14Kathodenkennung:MarkierungCathode mark:markGewicht/Approx.weight:200mgGurtung/Polarität und Lage8)Seite14Verpackungseinheit800/Rolle,ø180mm Method of Taping/Polarity and Orientation8)page14Packing unit800/reel,ø180mm2003-10-2910Empfohlenes Lötpaddesign8)Seite14IR Reflow Löten8)page142003-10-2911Lötbedingungen Vorbehandlung nach JEDEC Level4 Soldering Conditions Preconditioning acc.to JEDEC Level4 IR-Reflow Lötprofil(nach IPC9501)IR Reflow Soldering Profile(acc.to IPC9501)2003-10-29122003-10-2913Attention please!The information describes the type of component and shall not be considered as assured characteristics.Terms of delivery and rights to change design reserved.Due to technical requirements components may contain dangerous substances.For information on the types in question please contact our Sales Organization.If printed or downloaded,please find the latest version in the Internet.PackingPlease use the recycling operators known to you.We can also help you –get in touch with your nearest sales office.By agreement we will take packing material back,if it is sorted.You must bear the costs of transport.For packing material that is returned to us unsorted or which we are not obliged to accept,we shall have to invoice you for any costs incurred.Components used in life-support devices or systems must be expressly authorized for such purpose!Critical components 9)page 14may only be used in life-support devices or systems 10)page 14with the express written approval of OSRAM OS.Revision History:2003-10-29Previous Version:-PageSubjects (major changes since last revision)Date of changeFußnoten:1)Helligkeitswerte werden mit einerStromeinprägedauer von25ms und einer Genauigkeit von±11%ermittelt.2)Wegen der besonderen Prozessbedingungen bei derHerstellung von LED können typische oder abgeleitete technische Parameter nur aufgrund statistischer Werte wiedergegeben werden.Diese stimmen nicht notwendigerweise mit den Werten jedes einzelnen Produktesüberein,dessen Werte sich von typischen und abgeleiteten Werten oder typischen Kennlinien unterscheiden können.Falls erforderlich,z.B.aufgrund technischer Verbesserungen,werden diese typischen Werte ohne weitere Ankündigung geändert.3)Die LED kann in Sperrichtung kurzzeitig betriebenwerden.4)RthJA ergibt sich bei Montage auf PC-Board-Metallkernplatine,l= 1.3W/(m*K),für weitere Informationen siehe Applikationsschrift im Internet ().5)Wellenlängen werden mit einer Stromeinprägedauervon25ms und einer Genauigkeit von±1nm ermittelt.6)Spannungswerte werden mit einerStromeinprägedauer von1ms und einer Genauigkeit von±0,1V ermittelt.7)Im gestrichelten Bereich der Kennlinien muss miterhöhten Helligkeitsunterschieden zwischen Leuchtdioden innerhalb einer Verpackungseinheit gerechnet werden.8)Maße werden wie folgt angegeben:mm(inch).9)Ein kritisches Bauteil ist ein Bauteil,das inlebenserhaltenden Apparaten oder Systemen eingesetzt wird und dessen Defekt voraussichtlich zu einer Fehlfunktion dieses lebenserhaltenden Apparates oder Systems führen wird oder die Sicherheit oder Effektivität dieses Apparates oder Systems beeinträchtigt.10)Lebenserhaltende Apparate oder Systeme sind für(a)die Implantierung in den menschlichen Körperoder(b)für die Lebenserhaltung bestimmt.Falls sie versagen,kann davon ausgegangen werden, dass die Gesundheit und das Leben des Patienten in Gefahr ist.Published by OSRAM Opto Semiconductors GmbH Wernerwerkstrasse2,D-93049Regensburg©All Rights Reserved.Remarks:1)Brightness groups are tested at a current pulseduration of25ms and a tolerance of±11%.2)Due to the special conditions of the manufacturingprocesses of LED,the typical data or calculated correlations of technical parameters can only reflect statistical figures.These do not necessarily correspond to the actual parameters of each single product,which could differ from the typical data and calculated correlations or the typical characeristic line.If requested,e.g.because of technical improvements, these typ.data will be changed without any further notice.3)Driving the LED in reverse direction is suitable forshort term application.4)RthJAresults from mounting on PC board-metall core PCB,l=1.3W/(m*K),for further Information please find the application note on our web site ().5)Wavelengths are tested at a current pulse duration of25ms and a tolerance of±1nm.6)Forward voltages are tested at a current pulseduration of1ms and a tolerance of±0.1V.7)In the range where the line of the graph is broken,youmust expect higher brightness differences between single LEDs within one packing unit.8)Dimensions are specified as follows:mm(inch).9)A critical component is a component used in alife-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system,or to affect its safety or the effectiveness of that device or system.10)Life support devices or systems are intended(a)to be implanted in the human body,or(b)to support and/or maintain and sustain human life.If they fail,it is reasonable to assume that the health and the life of the user may be endangered.2003-10-2914。

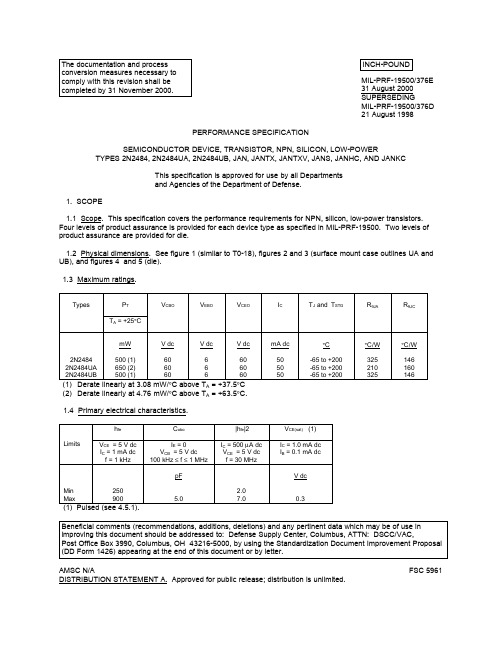

MIL-PRF-19500中文资料