CAT25C128VE-1.8-GT3中文资料

ICT使用手册gr228ieS

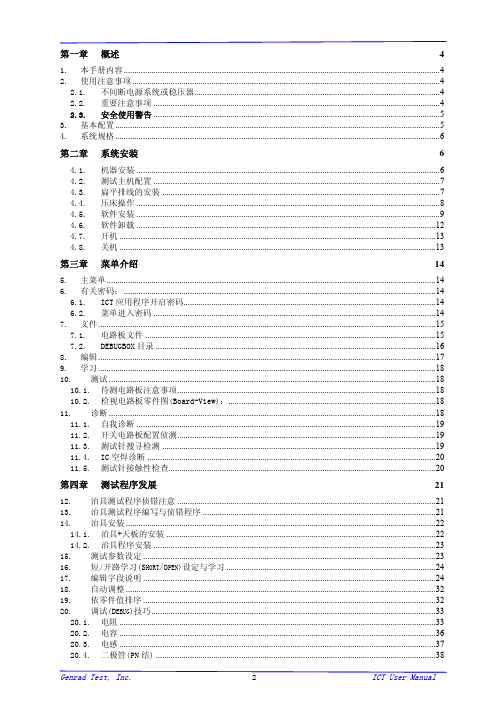

使用手册GR-228IEIn-Circuit Test SystemUSER MANUALGenrad Test, Inc.06-07-19-01第一章概述41.本手册内容 (4)2.使用注意事项 (4)2.1.不间断电源系统或稳压器 (4)2.2.重要注意事项 (4)2.3.安全使用警告 (5)3.基本配置 (5)4.系统规格 (6)第二章系统安装64.1.机器安装 (6)4.2.测试主机配置 (7)4.3.扁平排线的安装 (7)4.4.压床操作 (8)4.5.软件安装 (9)4.6.软件卸载 (12)4.7.开机 (13)4.8.关机 (13)第三章菜单介绍 145.主菜单 (14)6.有关密码: (14)6.1.ICT应用程序开启密码 (14)6.2.菜单进入密码 (14)7.文件 (15)7.1.电路板文件 (15)7.2.DEBUGBOX目录 (16)8.编辑 (17)9.学习 (18)10.测试 (18)10.1.待测电路板注意事项 (18)10.2.检视电路板零件图(Board-View): (18)11.诊断 (18)11.1.自我诊断 (19)11.2.开关电路板配置侦测 (19)11.3.测试针搜寻检测 (19)11.4.IC空焊诊断 (20)11.5.测试针接触性检查 (20)第四章测试程序发展 2112.治具测试程序侦错注意 (21)13.治具测试程序编写与侦错程序 (21)14.治具安装 (22)14.1.治具+天板的安装 (22)14.2.治具程序安装 (23)15.测试参数设定 (23)16.短/开路学习(S HORT/O PEN)设定与学习 (24)17.编辑字段说明 (24)18.自动调整 (32)19.依零件值排序 (32)20.调试(D EBUG)技巧 (33)20.1.电阻 (33)20.2.电容 (36)20.3.电感 (37)20.4.二极管(PN结) (38)20.5.晶体管 (40)20.6.场效应晶体管(FET) (42)20.7.晶闸管(SCR,TRIAC) (43)20.8.跳线、保险丝、开关 (43)20.9.光电耦合器 (44)20.10.电容极性 (45)20.11.编辑零件稳定度测试 (45)20.12.IC保护二极管设定与学习 (46)20.13.IC空焊设定与学习 (47)20.14.开路及短路 (50)21.开始测试 (51)第五章理论探讨 5222.开路及短路的测量原理 (52)23.电路隔离(G UARDING)测试技术 (53)24.零件测试原理 (53)25.测试延迟时间与储能元件充放电对测试的影响 (55)25.1.时间常数τ (55)25.2.测试所需的延时须充分 (56)25.3.储能元件对测试的影响 (56)第六章压床结构及治具说明 5725.4.压床结构 (57)25.5.气压调整 (58)25.6.压床冲程调整 (58)25.7.压床速度调整 (59)25.8.压床保养 (59)25.9.治具说明 (60)第七章附录6126.技术规格 (61)27.常见问题解答(FAQ) (62)28.常见异常排除 (65)29.治具调试注意事项(应用工程师经验参考): (67)30.零件名称(P ART N AME)未尾标注统一约定参考 (69)31.ICT测试出的不良PCB维修培训 (70)32.系统定期保养内容 (71)33.ICT在线测试设备日保养记录表 (73)第一章 概述1.本手册内容本手册包括概述、系统安装、菜单介绍、测试程序发展、理论探讨等内容,您可以根据需要查看相关内容,获得相应的帮助。

B18系列产品说明书

*(XXX)CO

4

MC/AC

4

1/2" [13] & 3/4" [19]

Attaches to 1/8" [3] through 1/4" [6] flange.

4

1" [25]

4

MC/AC

4

1/2" [13] & 3/4" [19]

other purpose.

NOTE: All load ratings are for static conditions and do not account for dynamic loading such as wind, water or seismic loads, unless otherwise noted.

Pentair, CADDY, ERICO CADWELD, ERICO CRITEC, ERICO, ERIFLEX, and LENTON are owned by Pentair or its global affiliates. All other trademarks are the property of their respective owners. Pentair reserves the right to change specifications without prior notice.

CADDY B18 series with threaded rod going through both

the B18 and the box, this single support is appropriate.

Mitsubishi Electric 工业机器人 MELFA RV-8CRL 产品介绍说明书

FACTORY AUTOMATIONMITSUBISHI ELECTRICINDUSTRIAL ROBOTMELFA RV-8CRLAllied Automation 800-214-0322Pursuing practical performanceUses an HK motor, the latest servomotor from Mitsubishi Electric. This allows improved torque characteristics, accuracy, and responsiveness while substantially reducing the size and weight. This adds up to much better robot performance and greater compactness.Continuous operation performanceLighter weight and improved heat release translate to improved continuous operation performance.Beltless coaxial drive mechanismA coaxial drive mechanism without belts is used for transmission to each axis (excluding the J4 and J5 axes).Simplification of the structure has improved transmission efficiency and reliability while also improving the ease of maintenance.No backup batteryThe use of the new HK motor eliminates the need for a battery to back up the robot’s internal encoder.This eliminates the cost and effort of regularreplacement as well as the risk of losing origin coordinates due to battery failure.A signal wire and air piping that can be used for gripper control, etc., are built in from the base to the forearm. Both ends of the signal wire haveuniversal D-sub connectors for use in various applications.Highest-in-class load capacityFeaturing a highest-in-class maximum load capacity of 8 kg, these robots boast a lighter-weight structure and reduced unit weight thanks to their simplified drive system and optimized arm structure, resulting in enhanced load capacity.Largest-in-class effective working areaOffers highest-in-class maximum reach radius of 931 mm. The use of a no-offset lower arm structure eliminating the J2-axis joint offset minimizes the interference region in the minimum turning radius and provides the largest-in-class effective working area.Standard IP65 supportComes standard with environmental resistance features allowing installation in plants and equipment where dust or oil mist is present.Can be used in oil mist environmentsJ6-axis motorJ3-axismotor J2-axismotorJ1-axismotor Slim & Compact Robot Offering a High Level of Utility and DesignSlim & compactA smooth, curved design complements the slim arm and compact joints. The external design is marked by minimalist, functional design.*Installation pitch:□160 mm (same as RV-4FR and 20% less than RV-7FR)Protrusionless structureIn addition to a slim, compact exterior and small robot base, its structure features minimal protrusions to the front, back, and sides, resulting in reduced interference with surroundings when the robot operates. This makes it suited to integration with automation cells and manufacturing equipment.1High-performance Controller Makes MELFA More IntelligentSafety monitoring functionWe will prepare a safety function compliant with international standards that simplifies risk assessments.Safety I/OExtends redundant safety I/O to 8 inputs and 4 outputs. Enablesdevelopment of various safety systems.Safety logic editingSimplifies development and operation of safety systems with safety logic editing.●Program editing and debugging ●Simulation function ●3D viewer●Monitoring function●Melfa RXM.ocx communication middlewareTrackingRobot tracks workpiece on conveyor, allowing transfer, alignment, and assembly without stopping conveyor.Additional axis controlBuild user mechanism controlling additional axes simultaneously with robot such as robot drive axis or turntable or separate from robot such as loader or positioning device. Control up to 8 axes. Our MELSERVO (MR-J4-B)servomotor can be used with additional axes.Robot mechanism thermal compensation functionMeasures the temperature of the robot arm and automatically corrects errors arising from thermal expansion of the arm.Callibration assistance functionAutomated calibration translates to simplification of installation of two-dimensional vision sensor and improvement of operational accuracy.Coordinated control of additional axesLinks robot and travel base for high-accuracy processing and assembly at specific speed.Also supports optional MELFA SmartPlusfunctional enhancement *1Comes standard with tracking and additional axis control PC software supporting everything from robot system designto installation, debugging, operation, and maintenance●Vision sensor configuration tool allows easy calibration of robot and camera ●Easy connection of robot and camera via Ethernet ●Easy control via robot program vision control commandSimultaneous controlmechanismsMechanism 1Mechanism 2Mechanism 3Up to 3Additional axesVision sensorSupports multiple conveyors simultaneously (up to 8)*1: Coming soonRobot controllerRobotLaser scannerTeaching boxRT ToolBox3Emergency stopArea sensorLamp2SpecificationsMechanical interfaceInternal wiring/pipingWiring/pipingInstallation dimensionsExternal dimensions/operating rangeMain Specifications15-pin D-sub AWG#24 (0.2mm ) ×15φ6 air joint (2)φ6 hose (2)Black Green Red Brown Yellow OrangeBlue Purple Gray Pink Light blue (Black)/Yellow (Black)/White (Black)/Blue 123456789101112131415123456789101112131415①②Baseφ6 air joint ①Tool wiring connector (15-pin D-sub)Tool wiring connector (15-pin D-sub)φ6 air joint ②Air pipe (2)φ6 air joint ①BaseUpper armForearmView A15-pin D-subForearmφ6 air joint ②Tool wiring (15)Tool wiring connectorRz25R z 25(Installation reference plane)(I n s t a l l a t i o n r e f e r e n c e p l a n e )1908080(160)978080(160)9797φ40h 8φ20H 7D6P .C.D .φ31.545°4-M5 thread depth 8φ5H7D84-φ9 installation hole*1: The wall mounting specifications are special specifications that restrict the operating range of the J1 axis.*2: “Maximum load capacity” is the maximum weight that can be loaded under the limitation of a mechanical interface having a downward attitude (within ±10° of the vertical position).View BP point operating areaP pointR 930.5-170°+170°R 219.315071R 150930.5930.51320.5244.4634.4930.585470390450100R 930.5+110°-110°Control point (R point)P point operating areaP point Downward limit of wristR 219.3102028020A71BWrist's downward singularity boundarySpace for the cable connectionMinimum: 310250256White 3External dimensions*2: Power supply voltage variability is within 10%.*3: Power capacity is recommended value.Note that power capacity does not include making current when turning on. Power capacity is an estimate.*4: Grounding work is to be performed by the customer.*5: Recommended USB cable (USB Type A, USB Mini-B Type): MR-J3USBCBL3M (Mitsubishi Electric), GT09-C30USB-5P (Mitsubishi Electric System & Service)*6: Mode select switch is to be provided by the customer.Controller specificationsStand-alone robot controllerRobot controller can be used for centralized control.430(30)30(3.5)37099.59642534045(40)(45)CR800-D4System configurationParallelinput-output interfaceinput-output unitExternal input-output cableCC-Link <Standard devices>GOT Pulse encoderServo Network R56TBR32TBsupport(SmartPlus)Machine cableController protection box<Functional options>Force sensor set MELFA-3D Vision⑨⑥RT ToolBox3 mini RT ToolBox3RT ToolBox3 Pro⑭②Encoder interfaceRobotRobot controller*1: Coming soon5OptionsController optionsFunctional optionsExpanded software functions*1: Coming soon6L (NA )09102ENG-BAll trademarks acknowledged.Printed December 2019HEAD OFFICE: TOKYO BLDG., 2-7-3 MARUNOUCHI,CHIYODA-KU, TOKYO 100-8310, JAPANMitsubishi Electric Corporation Nagoya Works is a factory certified for ISO 14001 (standards for environmental management systems) and ISO 9001(standards forquality assurance management systems)Global Partner. Local Friend.Allied Automation 800-214-0322。

CAT1023WI-25-GT3资料

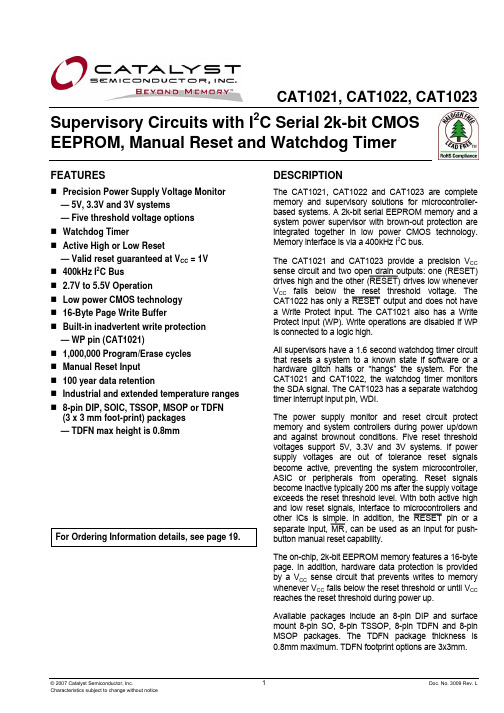

CAT1021, CAT1022, CAT1023Supervisory Circuits with I 2C Serial 2k-bit CMOS EEPROM, Manual Reset and Watchdog TimerFEATURESPrecision Power Supply Voltage Monitor — 5V, 3.3V and 3V systems — Five threshold voltage options Watchdog TimerActive High or Low Reset— Valid reset guaranteed at V CC = 1V 400kHz I 2C Bus 2.7V to 5.5V Operation Low power CMOS technology 16-Byte Page Write BufferBuilt-in inadvertent write protection — WP pin (CAT1021)1,000,000 Program/Erase cycles Manual Reset Input 100 year data retentionIndustrial and extended temperature ranges 8-pin DIP, SOIC, TSSOP, MSOP or TDFN (3 x 3 mm foot-print) packages — TDFN max height is 0.8mmFor Ordering Information details, see page 19.DESCRIPTIONThe CAT1021, CAT1022 and CAT1023 are complete memory and supervisory solutions for microcontroller-based systems. A 2k-bit serial EEPROM memory and a system power supervisor with brown-out protection are integrated together in low power CMOS technology. Memory interface is via a 400kHz I 2C bus.The CAT1021 and CAT1023 provide a precision V CC sense circuit and two open drain outputs: one (RESET)drives high and the other (RESET¯¯¯¯¯¯) drives low whenever V CC falls below the reset threshold voltage. TheCAT1022 has only a RESET¯¯¯¯¯¯ output and does not have a Write Protect input. The CAT1021 also has a Write Protect input (WP). Write operations are disabled if WP is connected to a logic high.All supervisors have a 1.6 second watchdog timer circuit that resets a system to a known state if software or a hardware glitch halts or “hangs” the system. For the CAT1021 and CAT1022, the watchdog timer monitors the SDA signal. The CAT1023 has a separate watchdog timer interrupt input pin, WDI.The power supply monitor and reset circuit protect memory and system controllers during power up/down and against brownout conditions. Five reset threshold voltages support 5V, 3.3V and 3V systems. If power supply voltages are out of tolerance reset signals become active, preventing the system microcontroller, ASIC or peripherals from operating. Reset signals become inactive typically 200 ms after the supply voltage exceeds the reset threshold level. With both active high and low reset signals, interface to microcontrollers andother ICs is simple. In addition, the RESET¯¯¯¯¯¯ pin or a separate input, MR¯¯¯, can be used as an input for push-button manual reset capability.The on-chip, 2k-bit EEPROM memory features a 16-byte page. In addition, hardware data protection is provided by a V CC sense circuit that prevents writes to memory whenever V CC falls below the reset threshold or until VCC reaches the reset threshold during power up.Available packages include an 8-pin DIP and surface mount 8-pin SO, 8-pin TSSOP, 8-pin TDFN and 8-pin MSOP packages. The TDFN package thickness is 0.8mm maximum. TDFN footprint options are 3x3mm.CAT1021, CAT1022, CAT1023BLOCK DIAGRAMTHRESHOLD VOLTAGE OPTIONPart DashNumberMinimum ThresholdMaximum Threshold-45 4.50 4.75 -42 4.25 4.50 -30 3.00 3.15 -28 2.85 3.00 -25 2.55 2.70PIN CONFIGURATIONDIP Package (L ) SOIC Package (W ) TSSOP Package (Y ) MSOP Package (Z )MR ¯¯¯ 1 8V CC RESET¯¯¯¯¯¯ 2 7 RESET WP 3 6 SCLV SS 45 SDACAT1021MR ¯¯¯ 1 8 V CC RESET¯¯¯¯¯¯ 2 7 NC NC 3 6 SCLV SS 45 SDACAT1022MR ¯¯¯ 1 8 V CC RESET¯¯¯¯¯¯ 2 7 WDI RESET 3 6 SCLV SS 45 SDACAT1023(Bottom View)TDFN Package: 3mm x 3mm 0.8mm maximum height - (ZD4)V CCMR ¯¯¯ RESET RESET ¯¯¯¯¯¯ SCL WPSDA V SSV CC MR ¯¯¯ RESET ¯¯¯¯¯¯ SCL NCSDA V SSV CCMR ¯¯¯ WDI RESET ¯¯¯¯¯¯ SCL RESETSDA V SSEXTERNAL LO ADSCLRESET(CAT1021/23)CAT1021, CAT1022, CAT1023PIN DESCRIPTIONRESET/RESET¯¯¯¯¯¯: RESET OUTPUT(RESET CAT1021/23 Only)These are open drain pins and RESET¯¯¯¯¯¯ can be used as a manual reset trigger input. By forcing a reset condition on the pin the device will initiate and maintain a reset condition. The RESET pin must be connected through a pull-down resistor, and the RESET¯¯¯¯¯¯ pin must be connected through a pull-up resistor.SDA: SERIAL DATA ADDRESSThe bidirectional serial data/address pin is used to transfer all data into and out of the device. The SDA pin is an open drain output and can be wire-ORed with other open drain or open collector outputs.SCL: SERIAL CLOCKSerial clock input.MR¯¯¯: MANUAL RESET INPUTManual Reset input is a debounced input that can be connected to an external source for Manual Reset. Pulling the MR input low will generate a Reset condition. Reset outputs are active while MR input is low and for the reset timeout period after MR returns to high. The input has an internal pull up resistor.WP (CAT1021 Only): WRITE PROTECT INPUT When WP input is tied to V SS or left unconnected write operations to the entire array are allowed. When tied to V CC, the entire array is protected. This input has an internal pull down resistor.WDI (CAT1023 Only): WATCHDOG TIMER INTERRUPT Watchdog Timer Interrupt Input is used to reset the watchdog timer. If a transition from high to low or lowto high does not occur every 1.6 seconds, the RESET outputs will be driven active. PIN FUNCTIONPinNameFunctionNC No ConnectRESET¯¯¯¯¯¯Active Low Reset Input/OutputV SS GroundSDA Serial Data/AddressSCL Clock InputRESET Active High Reset Output (CAT1021/23) V CC Power SupplyWP Write Protect (CAT1021 only)MR¯¯¯Manual Reset InputWDI Watchdog Timer Interrupt (CAT1023) OPERATING TEMPERATURE RANGEIndustrial-40ºC to 85ºCExtended -40ºC to 125ºCCAT102X FAMILY OVERVIEWDeviceManualResetInput PinWatchdogWatchdogMonitorPinWriteProtectionPinIndependentAuxiliaryVoltage SenseRESET:Active Highand LOWEEPROMCAT1021 SDA 2k CAT1022 SDA 2k CAT1023 WDI 2k CAT1024 2k CAT1025 2k CAT1026 2k CAT1027 WDI 2kFor supervisory circuits with embedded 16k EEPROM, please refer to the CAT1161, CAT1162 and CAT1163 data sheets.CAT1021, CAT1022, CAT1023ABSOLUTE MAXIMUM RATINGS(1)Parameters Ratings UnitsTemperature Under Bias –55 to +125 ºCStorage Temperature –65 to +150 ºCVoltage on any Pin with Respect to Ground(2)–2.0 to V CC + 2.0 VV CC with Respect to Ground –2.0 to 7.0 VPackage Power Dissipation Capability (T A = 25°C) 1.0 WLead Soldering Temperature (10 secs) 300 ºCOutput Short Circuit Current(3) 100mA D.C. OPERATING CHARACTERISTICSV CC = 2.7V to 5.5V and over the recommended temperature conditions unless otherwise specified.Symbol Parameter TestConditions Min Typ Max UnitsI LI Input Leakage Current V IN = GND to Vcc -2 10 µAI LO Output Leakage Current V IN = GND to Vcc -10 10 µAI CC1Power Supply Current (Write) f SCL = 400kHzV CC = 5.5V3 mAI CC2Power Supply Current (Read) f SCL = 400kHzV CC = 5.5V1 mAI SB StandbyCurrent Vcc = 5.5V,V IN = GND or Vcc60 µAV IL(4)Input Low Voltage -0.5 0.3 x Vcc V V IH(4)Input High Voltage 0.7 x Vcc Vcc + 0.5 VV OL Output Low Voltage(SDA, RESET¯¯¯¯¯¯)I OL = 3mAV CC = 2.7V0.4 VV OH Output High Voltage(RESET)I OH = -0.4mAV CC = 2.7VVcc - 0.75 VCAT102x-45(V CC = 5.0V)4.50 4.75 VCAT102x-42(V CC = 5.0V)4.25 4.50CAT102x-30(V CC = 3.3V)3.00 3.15CAT102x-28(V CC = 3.3V)2.853.00V TH ResetThresholdCAT102x-25(V CC = 3.0V)2.55 2.70V RVALID Reset Output Valid V CC Voltage 1.00 V V RT(5)Reset Threshold Hysteresis 15 mV Notes:(1) Stresses above those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratingsonly, and functional operation of the device at these or any other conditions outside of those listed in the operational sections of this specification is not implied. Exposure to any absolute maximum rating for extended periods may affect device performance and reliability.(2) The minimum DC input voltage is –0.5V. During transitions, inputs may undershoot to –2.0V for periods of less than 20 ns. Maximum DCvoltage on output pins is V CC +0.5V, which may overshoot to V CC +2.0V for periods of less than 20 ns.(3) Output shorted for no more than one second. No more than one output shorted at a time.(4) V IL min and V IH max are reference values only and are not tested.(5) This parameter is tested initially and after a design or process change that affects the parameter. Not 100% tested.CAT1021, CAT1022, CAT1023CAPACITANCET A = 25ºC, f = 1.0MHz, V CC = 5VSymbol Test TestConditions Max Units Capacitance V OUT = 0V 8 pFC OUT(1) OutputC IN(1)Input Capacitance V IN = 0V 6 pFAC CHARACTERISTICSV CC = 2.7V to 5.5V and over the recommended temperature conditions, unless otherwise specified.Memory Read & Write Cycle(2)Symbol Parameter Min Max Units Frequency 400 kHzf SCL Clockt SP Input Filter Spike Suppression (SDA, SCL) 100 ns t LOW Clock Low Period 1.3 µsPeriod 0.6 µs t HIGH ClockHight R(1)SDA and SCL Rise Time 300 ns t F(1)SDA and SCL Fall Time 300 ns t HD; STA Start Condition Hold Time 0.6 µs t SU; STA Start Condition Setup Time (for a Repeated Start) 0.6 µs t HD; DAT Data Input Hold Time 0 ns t SU; DAT Data Input Setup Time 100 ns t SU; STO Stop Condition Setup Time 0.6 µs t AA SCL Low to Data Out Valid 900 ns t DH Data Out Hold Time 50 ns t BUF(1)Time the Bus must be Free Before a New Transmission Can Start 1.3 µs t WC(3)Write Cycle Time (Byte or Page) 5 ms Notes:(1) This parameter is characterized initially and after a design or process change that affects the parameter. Not 100% tested.(2) Test Conditions according to “AC Test Conditions” table.(3) The write cycle time is the time from a valid stop condition of a write sequence to the end of the internal program/erase cycle. During thewrite cycle, the bus interface circuits are disabled, SDA is allowed to remain high and the device does not respond to its slave address.CAT1021, CAT1022, CAT1023RESET CIRCUIT AC CHARACTERISTICSConditions Min Typ Max Units Symbol Parameter Testt PURST Power-Up Reset Timeout Note 2 130 200 270 ms t RDP V TH to RESET output Delay Note 3 5 µs t GLITCH V CC Glitch Reject Pulse Width Note 4, 5 30 nsMR Glitch Manual Reset Glitch Immunity Note 1 100 ns t MRW MR Pulse Width Note 1 5 µs t MRD MR Input to RESET Output Delay Note 1 1 µs t WD Watchdog Timeout Note 1 1.0 1.6 2.1 sec POWER-UP TIMING (5), (6)Symbol Parameter Test Conditions Min Typ Max Units t PUR Power-Up to Read Operation 270 ms t PUW Power-Up to Write Operation 270 msAC TEST CONDITIONSParameter Test ConditionsInput Pulse Voltages 0.2V CC to 0.8V CCInput Rise and Fall times 10nsInput Reference Voltages 0.3V CC , 0.7V CCOutput Reference Voltages 0.5V CCOutput Load Current Source: I OL = 3mA; C L = 100pFRELIABILITY CHARACTERISTICSSymbol Parameter Reference Test Method Min Max Units N END(5)Endurance MIL-STD-883, Test Method 1033 1,000,000 Cycles/Byte T DR(5)Data Retention MIL-STD-883, Test Method 1008 100 Years V ZAP(5)ESD Susceptibility MIL-STD-883, Test Method 3015 2000 VoltsI LTH(5)(7)Latch-Up JEDEC Standard 17 100 mA Notes:(1) Test Conditions according to “AC Test Conditions” table.(2) Power-up, Input Reference Voltage V CC = V TH, Reset Output Reference Voltage and Load according to “AC Test Conditions” Table(3) Power-Down, Input Reference Voltage V CC = V TH, Reset Output Reference Voltage and Load according to “AC Test Conditions” Table(4) V CC Glitch Reference Voltage = V THmin; Based on characterization data(5) This parameter is characterized initially and after a design or process change that affects the parameter. Not 100% tested.(6) t PUR and t PUW are the delays required from the time V CC is stable until the specified memory operation can be initiated.(7) Latch-up protection is provided for stresses up to 100mA on input and output pins from -1V to V CC + 1V.CAT1021, CAT1022, CAT1023DEVICE OPERATIONReset Controller DescriptionThe CAT1021/22/23 precision RESET controllers ensure correct system operation during brownout and power up/down conditions. They are configured with open drain RESET outputs.During power-up, the RESET outputs remain active until V CC reaches the V TH threshold and will continue driving the outputs for approximately 200ms (t PURST) after reaching V TH. After the t PURST timeout interval, the device will cease to drive the reset outputs. At this point the reset outputs will be pulled up or down by their respective pull up/down resistors.During power-down, the RESET outputs will be active when V CC falls below V TH. The RESET¯¯¯¯¯¯ output will be valid so long as V CC is >1.0V (V RVALID). The device is designed to ignore the fast negative going V CC transient pulses (glitches).Reset output timing is shown in Figure 1.Manual Reset OperationThe RESET¯¯¯¯¯¯ pin can operate as reset output and manual reset input. The input is edge triggered; that is, the RESET¯¯¯¯¯¯ input will initiate a reset timeout after detecting a high to low transition.When RESET¯¯¯¯¯¯ I/O is driven to the active state, the 200 msec timer will begin to time the reset interval. If external reset is shorter than 200ms, Reset outputs will remain active at least 200ms.The CAT1021/22/23 also have a separate manual reset input. Driving the MR¯¯¯ input low by connecting a pushbutton (normally open) from MR¯¯¯ pin to GND will generate a reset condition. The input has an internal pull up resistor.Reset remains asserted while MR¯¯¯ is low and for the Reset Timeout period after MR¯¯¯ input has gone high. Glitches shorter than 100ns on MR¯¯¯ input will not ge-nerate a reset pulse. No external debouncing circuits are required. Manual reset operation using MR¯¯¯ input is shown in Figure 2. Hardware Data ProtectionThe CAT1021/22/23 supervisors have been designed to solve many of the data corruption issues that have long been associated with serial EEPROMs. Data corruption occurs when incorrect data is stored in a memory location which is assumed to hold correct data. Whenever the device is in a Reset condition, the embedded EEPROM is disabled for all operations, including write operations. If the Reset output(s) are active, in progress communications to the EEPROM are aborted and no new communications are allowed. In this condition an internal write cycle to the memory can not be started, but an in progress internal non-volatile memory write cycle can not be aborted. An internal write cycle initiated before the Reset condition can be successfully finished if there is enough time (5ms) before V CC reaches the minimum value of 2V.In addition, the CAT1021 includes a Write Protection Input which when tied to V CC will disable any write operations to the device.Watchdog TimerThe Watchdog Timer provides an independent protection for microcontrollers. During a system failure, CAT1021/22/23 devices will provide a reset signal after a time-out interval of 1.6 seconds for a lack of activity. The CAT1023 is designed with the Watchdog timer feature on the WDI pin. The CAT1021 and CAT1022 monitor the SDA line. If WDI or SDA does not toggle within a 1.6 second interval, the reset condition will be generated on the reset outputs. The watchdog timer is cleared by any transition on a monitored line.As long as reset signal is asserted, the watchdog timer will not count and will stay cleared.CAT1021, CAT1022, CAT1023Figure 1. RESET Output TimingFigure 2: MR¯¯¯ Operation and TimingCAT1021, CAT1022, CAT1023EMBEDDED EEPROM OPERATIONThe CAT1021/22/23 feature a 2-kbit embedded serial EEPROM that supports the I 2C Bus data transmission protocol. This Inter-Integrated Circuit Bus protocol defines any device that sends data to the bus to be a transmitter and any device receiving data to be a receiver. The transfer is controlled by the Master device which generates the serial clock and all START and STOP conditions for bus access. Both the Master device and Slave device can operate as either transmitter or receiver, but the Master device controls which mode is activated. I 2C BUS PROTOCOLThe features of the I 2C bus protocol are defined as follows:(1) Data transfer may be initiated only when the busis not busy.(2) During a data transfer, the data line must remainstable whenever the clock line is high. Any changes in the data line while the clock line is high will be interpreted as a START or STOP condition. START CONDITIONThe START Condition precedes all commands to the device, and is defined as a HIGH to LOW transition ofSDA when SCL is HIGH. The CAT1021/22/23 monitor the SDA and SCL lines and will not respond until this condition is met. STOP CONDITIONA LOW to HIGH transition of SDA when SCL is HIGH determines the STOP condition. All operations must end with a STOP condition.DEVICE ADDRESSINGThe Master begins a transmission by sending a START condition. The Master sends the address of the particular slave device it is requesting. The four most significant bits of the 8-bit slave address are programmable in metal and the default is 1010. The last bit of the slave address specifies whether a Read or Write operation is to be performed. When this bit is set to 1, a Read operation is selected, and when set to 0, a Write operation is selected.After the Master sends a START condition and the slave address byte, the CAT1021/22/23 monitors the bus and responds with an acknowledge (on the SDA line) when its address matches the transmitted slave address. The CAT1021/22/23 then perform a Read orWrite operation depending on the R/W¯¯ bit.Figure 3. Bus TimingFigure 4. Write Cycle TimingSCLSDA INSDA OUTSTOPCONDITIONSTARTCONDITIONADDRESSSCLSDACAT1021, CAT1022, CAT1023ACKNOWLEDGEAfter a successful data transfer, each receiving device is required to generate an acknowledge. The acknowledging device pulls down the SDA line during the ninth clock cycle, signaling that it received the 8 bits of data.All devices respond with an acknowledge after receiving a START condition and its slave address. If the device has been selected along with a write operation, it responds with an acknowledge after receiving each 8-bit byte.When a device begins a READ mode it transmits 8 bits of data, releases the SDA line and monitors the line for an acknowledge. Once it receives this acknowledge, the device will continue to transmit data. If no acknowledge is sent by the Master, the device terminates data transmission and waits for a STOP condition.WRITE OPERATIONSByte WriteIn the Byte Write mode, the Master device sends the START condition and the slave address information(with the R/W¯¯ bit set to zero) to the Slave device. After the Slave generates an acknowledge, the Master sends a 8-bit address that is to be written into the address pointers of the device. After receiving another acknow-ledge from the Slave, the Master device transmits the data to be written into the addressed memory location. The device acknowledges once more and the Master generates the STOP condition. At this time, the device begins an internal programming cycle to non-volatile memory. While the cycle is in progress, the device will not respond to any request from the Master device.Figure 5. Start/Stop TimingFigure 6. Acknowledge TimingFigure 7: Slave Address BitsSTART BITSDASTOP BITSCLACKNOWLEDGESTARTSCL FROM MASTERDATA OUTPUTFROM TRANSMITTERDATA OUTPUT FROM RECEIVER1010000R/WDefault ConfigurationCAT1021, CAT1022, CAT1023Page WriteThe CAT1021/22/23 writes up to 16 bytes of data in a single write cycle, using the Page Write operation. The page write operation is initiated in the same manner as the byte write operation, however instead of terminating after the initial byte is transmitted, the Master is allowed to send up to 15 additional bytes. After each byte has been transmitted, the CAT1021/22/23 will respond with an acknowledge and internally increment the lower order address bits by one. The high order bits remain unchanged. If the Master transmits more than 16 bytes before sending the STOP condition, the address counter ‘wraps around,’ and previously transmitted data will be overwritten.When all 16 bytes are received, and the STOP condition has been sent by the Master, the internal programming cycle begins. At this point, all received data is written to the CAT1021/22/23 in a single write cycle.Figure 8. Byte Write TimingFigure 9: Page Write TimingBYTEADDRESSSLAVEADDRESSSACKACKDA T AACKSTOPPBUS ACTIVITY:MASTERSDA LINE S T A R TBUS ACTIVITY:MASTERSDA LINEBYTECKCKCKSTOCKCKSTARSLAVECAT1021, CAT1022, CAT1023Doc. No. 3009 Rev. L12© 2007 Catalyst Semiconductor, Inc.Acknowledge PollingDisabling of the inputs can be used to take advantage of the typical write cycle time. Once the stop condition is issued to indicate the end of the host’s write opration, the CAT1021/22/23 initiates the internal write cycle. ACK polling can be initiated immediately. This involves issuing the start condition followed by the slave address for a write operation. If the device is still busy with the write operation, no ACK will be returned. If a write operation has completed, an ACK will be returned and the host can then proceed with the next read or write operation.WRITE PROTECTION PIN (WP)The Write Protection feature (CAT1021 only) allows the user to protect against inadvertent memory array programming. If the WP pin is tied to V CC , the entire memory array is protected and becomes read only. The CAT1021 will accept both slave and byte addre-sses, but the memory location accessed is protected from programming by the device’s failure to send an acknowledge after the first byte of data is received. READ OPERATIONSThe READ operation for the CAT1021/22/23 is initiated in the same manner as the write operation with oneexception, the R/W¯¯ bit is set to one. Three different READ operations are possible: Immediate/Current Address READ, Selective/Random READ and Sequential READ.Figure 10. Immediate Address Read TimingSCL SDA 8TH BI T STOPNO ACKDATA OUT89SLAVE ADDRESSSA C KDA TAN O A C K S T O P PBUS ACTIVIT Y:MASTERSDA LINES T A R TCAT1021, CAT1022, CAT1023Immediate/Current Address ReadThe CAT1021/22/23 address counter contains the address of the last byte accessed, incremented by one. In other words, if the last READ or WRITE access was to address N, the READ immediately following would access data from address N + 1. For N = E = 255, the counter will wrap around to zero and continue to clock out valid data. After the CAT1021/22/23 receives its slave address infor-mation (with the R/W¯¯ bit set to one), it issues an acknowledge, then transmits the 8-bit byte requested. The master device does not send an acknowledge, but will generate a STOP condition. Selective/Random ReadSelective/Random READ operations allow the Master device to select at random any memory location for a READ operation. The Master device first performs a ‘dummy’ write operation by sending the START condition, slave address and byte addresses of the location it wishes to read. After the CAT1021/22/23 acknowledges, the Master device sends the START condition and the slave addressagain, this time with the R/W¯¯ bit set to one. The CAT1021/22/23 then responds with its acknowledge and sends the 8-bit byte requested. The master device does not send an acknowledge but will generate a STOP condition.Sequential ReadThe Sequential READ operation can be initiated by either the Immediate Address READ or Selective READ operations. After the CAT1021/22/23 sends the inital 8-bit byte requested, the Master will responds with an acknowledge which tells the device it requires more data. The CAT1021/22/23 will continue to output an 8-bit byte for each acknowledge, thus sending the STOP condition.The data being transmitted from the CAT1021/22/23 is sent sequentially with the data from address N followed by data from address N + 1. The READ operation address counter increments all of the CAT1021/22/23 address bits so that the entire memory array can be read during one operation.Figure 11. Selective Read TimingFigure 12. Sequential Read TimingSLAVE ADDRESSSA C KN O A C KS T O P PBUS ACTIVITY:MASTERSDA LINES T A R T BYTE ADDRESS (n)SA C KDA T A nSLAVE ADDRESSA C KS T A RT BUS ACTIVITY:MASTERSDA LINEC KC KC KS T O O A C KC KSLAVECAT1021, CAT1022, CAT1023 Doc. No. 3009 Rev. L14© 2007 Catalyst Semiconductor, Inc.PACKAGE OUTLINES8-LEAD 300 MIL WIDE PLASTIC DIP (L)Notes :(1) All dimensions are in millimeters.(2) Complies with JEDEC Publication 95 MS001 dimensions; however, some of the dimensions may be more stringent.ecSYMBOLA A1b b2D E E1e eB LMIN 0.380.369.027.626.09 6.357.872.923.81NOM 0.46 1.771.147.872.54 BSCMAX 4.57A2 3.05 3.810.56c 0.210.260.3510.168.257.119.65CAT1021, CAT1022, CAT10238-LEAD 150 MIL SOIC (W)Notes:(1) All dimensions are in millimeters.(2) Complies with JEDEC specification MS-012 dimensions.SYMBOLA1A b C D E E1h L MIN 0.101.350.334.805.803.800.250.40NOM 0.250.19MAX 0.251.750.515.006.204.00e 1.27 BSC0.501.27q10°8°eCCAT1021, CAT1022, CAT1023Doc. No. 3009 Rev. L16© 2007 Catalyst Semiconductor, Inc.8-LEAD TSSOP (V)Notes:(1) All dimensions are in millimeters. (2) Complies with JEDEC Standard MO-153q1SEE DETAIL AcSYMBOL A A1A2b c D E E1e L q1MIN 0.050.800.092.906.30 6.44.300.008.00NOM 0.900.300.19 3.004.400.600.750.50MAX 1.200.151.050.203.106.504.500.65 BSCCAT1021, CAT1022, CAT10238-LEAD MSOP (Z)Notes:(1) All dimensions are in millimeters.(2) This part is compliant with JEDEC Specification MO-187 Variations AA.SYMBOLMIN NOMMAX A 1.1A10.050.100.15A20.750.850.95b 0.280.330.38c D 2.90 3.00 3.10E 4.80 4.90 5.00E1 2.903.00 3.10e 0.65BSCL 0.350.450.55L1L2Ө0º6ºCAT1021, CAT1022, CAT1023Doc. No. 3009 Rev. L18© 2007 Catalyst Semiconductor, Inc.TDFN 3 x 3 PACKAGE (ZD4)Notes: (1) All dimentions in mm. Angels in degrees. (2) Complies to JEDEC MO-229 / WEEC. (3) Coplanarity shall not exceed 0.10mm. (4) Warpage shall not exceed 0.10mm.(5)Package lenght / package width are considered as special characteristic(s).。

IDEC GT3系

451備有OFF 延遲、星形/三角形等各種類型。

100~240V AC 通用電源。

採用壓電陶瓷片震盪計時方式,精度更高。

備有高可視性的動作顯示燈。

通過48mm DIN 方形轉接器可轉變為嵌入型。

符合國際主要的安全標準。

經UL、c-UL 認證,符合EN 標準。

[多模式型(類比設定)]具有0刻度瞬時動作功能。

一個計時器實現多模式/多時間計時/通用電源等96種功能。

❏ 類型星形/三角形•••••••詳細記載頁:460~461頁詳細記載頁:462~463頁GT3系列多模式型.類比設定方式動作模式切換(3)刻度數位設定0〜1、0452GT3系列多模式型.類比設定方式453GT3系列多模式(附輸入功能.11 針腳)型.類比設定方式動作模式切換(3)刻度數位設定0〜1、0454455GT3系列 多模式(附輸入功能.11針腳)型.類比設定方式GT3系列多模式(附輸入功能.11 針腳)型.類比設定方式456457GT3系列 多模式(附輸入功能.11針腳)型.類比設定方式GT3系列電源OFF延遲型刻度數位設定、0〜3、0〜18、0〜60(2 1S458GT3系列電源OFF延遲型459GT3系列星形三角形〜100 460GT3系列星形三角形461GT3系列多功能計時器[雙節點型]型號462GT3系列多功能計時器[雙節點型]463464GT3系列 多功能計時器[配件]SR2P-06A SR3P-05A SR3P-06A 21背面接線用插座嵌入安裝用轉接器和背面接線用插座8針腳螺絲端子••((螺絲式8針腳插座螺絲式11針腳插座SR6P-M11G 型465GT3系列多功能計時器[共通]GT3系列多功能計時器[共通]466GT3系列多功能計時器[使用注意事項]動作模式切換開關模式記號和動作模式型號GT3A-1、-2、-3GT3A-4GT3A-5467GT3系列多功能計時器[使用注意事項]設定旋鈕→△切換時間設定開關時間刻度數位以內的一字形螺絲起子,通過時間刻度設定開關,5、0~10、0~50、0~100顯示於設定旋鈕個刻度數字顯示窗中,由此可選擇最合適的時間刻度→△切換時間設定開關,即可從468469GT3系列多功能計時器[使用注意事項]GT3系列多功能計時器[使用注意事項]溫度誤差以動作時間的變化來表示使用周圍溫度範圍內的溫度變化對動作時的影響。

28口三层交换机核心交换机工业交换机说明书

28口三层交换机核心交换机工业交换机说明书28口全千兆三层路由网管型工业以太网交换机采用高强度IP40防护外壳,工业级EMC设计,包括CRS9128-8TX、CRS9128-8FX、CRS9128-8SFP三款,是深圳市讯记科技有限公司自主研发的三层路由以太网交换机。

提供管理功能,可通过CLI进行管理。

产品提供16个固定10/100/1000M自适应以太网端口、4个固定1000M SFP接口(选配1000Base- 或1000Base-T模块)和可选8个1000Base- 光口(默认SC接口,可选FC、ST)或8个1000M SFP接口(选配1000Base- 或1000Base-T模块)或或8个10/100/1000M自适应以太网端口。

基于工业安装需求,提供1U标准机架式安装方式。

本产品同时采用无风扇、低功耗、工业级设计,-40~85℃工作温度范围,能够满足各种工业现场的要求,提供便捷的以太网通讯解决方案。

传统交换特性* 符合IEEE802.3/802.3u/802.3ab/802.3z标准,存储转发交换方式* 提供16个固定10/100/1000M自适应以太网端口,支持端口自动翻转* 提供4个固定1000M SFP接口(选配1000Base或1000Base-T 模块)* 提供可选8个1000Base光口(默认SC接口,可选FC、ST)或8个1000M SFP接口(选配1000Base或1000Base-T模块)或8个10/100/1000M自适应以太网端口* 采用IP40外壳及工业级EMC设计* 支持冗余宽电压100~240V AC电源输入(220V DC和48V DC 可选)* -40~75℃工作温度范围工业冗余以太网联网* 支持CLI管理方式* 支持存储转发机制* 支持静态路由功能* 支持RIP动态路由功能* 支持OSPF动态路由功能* 支持端口MAC地址学习* 支持VLAN配置;* 支持基于VLAN的IP地址配置;* 支持按钮复位和工厂默认配置;* 支持软件升级技术* 标准:IEEE802.3、IEEE802.3u、IEEE 802.3ab、IEEE 802.3z、IEEE802.3x、IEEE802.1Q、IEEE802.1p 、IEEE802.1d、IEEE802.1w接口* RJ45电口:10/100/1000Base-T速率自适应、全/半双工模式,支持端口自动翻转* SFP接口:1000Base- 或SFP Copper 1000Base-T(支持双绞线传输)* 光口:1000Base- 千兆全双工,默认SC接口,可选FC、ST,可传输120公里* Console口:RS-232(RJ45连接头)调试串口交换属性* 十兆转发速度:14881pps* 百兆转发速度:148810pps* 千兆转发速度:1488096pps* 传输方式:存储转发* 系统交换带宽:56Gbps* 缓存大小:1.5Mbits* MAC地址表:16K电源* 交流电源:冗余宽电压100~240V AC(50~60Hz 1.2A)电源输入,采用三线单相电源线* 直流电源:冗余宽电压220V DC(48V DC可选)电源输入,采用2芯7.62mm间距标准工业端子,电源支持防反接和无极性功能继电器* 继电器告警输出:端口故障、电源故障和环网故障的告警输出* 触点容量:1A 24VDC机械特性* 尺寸(W×H×D):482.6mm×44mm×275mm* 净重:3.15kg* 外壳:IP40等级保护,金属外壳* 安装:1U标准机架工作环境* 工作温度:-40℃~85℃* 存储温度:-40℃~85℃* 相对湿度:5%~95%(无凝露)保修* 保修期:5年符合标准* IEC61000-4-2(ESD):±6KV接触放电,±15KV空气放电* IEC61000-4-3(RS):10V/M(80-1000MHZ)* IEC61000-4-4(EFT):电源端:±4KV,信号端:±2KV* IEC61000-4-5(Surge):电源端:±4KV CM/±2KV DM,信号端:±4KV* IEC61000-4-6(射频传导):3V(10KHZ-150KHZ),10V (150KHZ-80MHZ)* IEC61000-4-16(共模传导):30V(cont.),300V(1s)* IEC60068-2-6(振动)* IEC60068-2-27(冲击)* IEC60068-2-32(自由跌落)* IEC61000-6-2(通用工业标准),IEC61750-3(变电站),IEEE1613(电力分站)* EN50121-4(轨道交通)。

CAT325C挖掘机技术参数

325C 详细规格发动机发动机型号3126B ATAAC 电控单体喷油器(HEUI)™ 燃油系统飞轮功率188 hp / 140 kW ISO 9249 188 hp / 140 kW SAE J1349 186 hp / 139 kW EEC 80/1269 188 hp / 140 kW 缸径 4.3 in / 110 mm 冲程 5 in / 127 mm 排量440 in3 / 7.2 L重量工作重量- 标准行走装置59300 lb / 26900 kg 工作重量- 加长行走装置63100 lb / 28600 kg传动最大挂钩牵引力54853 lb / 244 kN 最高行驶速度 3.3 mph / 5.3 kph液压系统主工装系统-最大流量(2x)62 gal/min / 235 L/min 最高压力- 机具(全时间)4980 psi / 34300 kPa 最高压力- 行驶4980 psi / 34300 kPa最高压力- 回转3988 psi / 27500 kPa 先导油系统- 最大流量10 gal/min / 36 L/min 先导油系统- 最大压力597 psi / 4120 kPa 动臂油缸- 缸径 5.51 in / 140 mm 动臂油缸- 行程55 in / 1407 mm 斗杆油缸- 缸径 5.91 in / 150 mm 斗杆油缸- 行程65 in / 1646 mm C 系列铲斗油缸- 缸径 5.12 in / 130 mmC 系列铲斗油缸- 行程46 in / 1156 mmD 系列铲斗油缸- 缸径 5.91 in / 150 mm D 系列铲斗油缸- 行程46 in / 1156 mm保养加注容量燃油箱容量132 gal / 500 L 冷却系统7.9 gal / 30 L 发动机机油7.9 gal / 30 L 回转驱动 2.1 gal / 8 L 最终传动(每边) 2.1 gal / 8 L 液压系统(包括油箱)82 gal / 310 L 液压油箱68 gal / 257 L噪声性能性能ANSI/SAE标准制动器SAE J1026 APR90 驾驶室/落物保护系统SAE J1356 FEB88 ISO 10262回转机构回转速度10.2 RPM / 10.2 RPM 回转力矩60628 lb ft / 82.2 kN.m履带标准宽度/标准行走装置24 in / 600 mm 标准宽度/加长行走装置- 三抓地齿履板32 in / 800 mm 选项件24 in / 600 mm 选项件28 in / 700 mm 选项件32 in / 800 mm。

CAT24C256WI-GT3中文资料

256-Kb I 2C CMOS Serial EEPROMCAT24C256PIn COnfIguRATIOn funCTIOnAl SyMbOlfEATuRESn Supports Standard and fast I 2C Protocol n 1.8 V to 5.5 V Supply Voltage Range n 64-byte Page Write buffern Hardware Write Protection for entire memory n Schmitt Triggers and noise Suppression filterson I 2C bus Inputs (SCl and SDA).n low power CMOS technology n 1,000,000 program/erase cycles n 100 year data retention n Industrial temperature rangen RoHS-compliant 8-pin PDIP and SOIC packagesPDIP (l)SOIC (W, X)VSSSD ASCL WPA 2, A 1, A 0DEVICE DESCRIPTIOnThe CAT24C256 is a 256-Kb Serial CMOS EEPROM, internally organized as 5 2 pages of 64 bytes each, for a total of 32,768 bytes of 8 bits each.It features a 64-byte page write buffer and supports both the Standard ( 00 kHz) as well as Fast (400 kHz) I 2C protocol.Write operations can be inhibited by taking the WP pin High (this protects the entire memory).External address pins make it possible to address up to eight CAT24C256 devices on the same bus.8765V CC WP SCL SDAA 2A 0A 1V SS1234For the location of Pin , please consult the corresponding package drawing.PIn funCTIOnSA 0, A, A 2Device Address SDA Serial Data SCL Serial Clock WP Write Protect V CC Power Supply V SSGround* Catalyst carries the I 2C protocol under a license from the Philips Corporation.for Ordering Information details, see page 13.CAT24C256AbSOluTE MAXIMuM RATIngS(1)Storage Temperature-65°C to + 50°C Voltage on Any Pin with Respect to Ground(2)-0.5 V to +6.5 VRElIAbIlITy CHARACTERISTICS(3)Symbol Parameter Min unitsN END(4)Endurance ,000,000Program/ Erase Cycles T DR Data Retention 00YearsD.C. OPERATIng CHARACTERISTICSV CC = .8 V to 5.5 V, T A = -40°C to 85°C, unless otherwise specified.Symbol Parameter Test Conditions Min Max unitsI CC Supply Current Read or Write at 400 kHz mAI SB Standby Current All I/O Pins at GND or V CC µAI L I/O Pin Leakage Pin at GND or V CC µAV IL Input Low Voltage-0.5V CC x 0.3V V IH Input High Voltage V CC x 0.7V CC + 0.5V V OL Output Low Voltage V CC > 2.5 V, I OL = 3.0 mA0.4V V OL2Output Low Voltage V CC > .8 V, I OL = .0 mA0.2VPIn IMPEDAnCE CHARACTERISTICST A = 25°C, f = 400 kHz, V CC = 5 VSymbol Parameter Conditions Min Max unitsC IN(3)SDA I/O Pin Capacitance V IN = 0 V8pFC IN(3)Input Capacitance (other pins)V IN = 0 V6pFnotes:( ) Stresses above those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions outside of those listed in the operational sections of this specification is not implied. Exposure to any absolute maximum rating for extended periods may affect device performance and reliability.(2) The DC input voltage on any pin should not be lower than -0.5 V or higher than V CC + 0.5 V. During transitions, the voltage on any pin mayundershoot to no less than - .5 V or overshoot to no more than V CC + .5 V, for periods of less than 20 ns.(3) These parameters are tested initially and after a design or process change that affects the parameter according to appropriate AEC-Q 00and JEDEC test methods.(4) Page Mode, V CC = 5 V, 25°CCAT24C256A.C. CHARACTERISTICS(1)V CC = .8 V to 5.5 V, T A = -40°C to 85°C, unless otherwise specified.Symbol Parameter1.8 V - 5.5 V2.5 V - 5.5 Vunits Min Max Min MaxF SCL Clock Frequency 00400kHzT I(2)Noise Suppression Time Constant atSCL, SDA Inputs0. 0. µst AA SCL Low to SDA Data Out 3.50.9µs t BUF(2)Time the Bus Must be Free Before aNew Transmission Can Start4.7 .3µst HD:STA Start Condition Hold Time40.6µs t LOW Clock Low Period 4.7 .3µs t HIGH Clock High Period40.6µs t SU:STA Start Condition Setup Time 4.70.6µs t HD:DAT Data In Hold Time00µs t SU:DAT Data In Setup Time0.250. µs t R(2)SDA and SCL Rise Time 0.3µs t F(2)SDA and SCL Fall Time0.30.3µs t SU:STO Stop Condition Setup Time40.6µs t DH Data Out Hold Time0. 0. µs t WR Write Cycle Time55ms t PU(2), (3)Power-up to Ready Mode ms notes:( ) Test conditions according to “A.C. Test Conditions” table.(2) Tested initially and after a design or process change that affects this parameter.(3) t PU is the delay between the time V CC is stable and the device is ready to accept commands.A.C. TEST COnDITIOnSInput Levels0.2 x V CC to 0.8 x V CCInput Rise and Fall Times≤ 50 nsInput Reference Levels0.3 x V CC, 0.7 x V CCOutput Reference Levels0.5 x V CCOutput Load Current Source: I OL = 3 mA (V CC≥ 2.5 V); I OL = mA (V CC < 2.5 V); C L = 00 pFCAT24C256PIn DESCRIPTIOnSCl:The Serial Clock input pin accepts the Serial Clock generated by the Master.SDA: The Serial Data I/O pin receives input data and transmits data stored in EEPROM. In transmit mode, this pin is open drain. Data is acquired on the positive edge, and is delivered on the negative edge of SCL.A0, A1 and A2: The Address pins accept the device ad-dress. These pins have on-chip pull-down resistors. WP: The Write Protect input pin inhibits all write op-erations, when pulled HIGH. This pin has an on-chip pull-down resistor.funCTIOnAl DESCRIPTIOnThe CAT24C256 supports the Inter-Integrated Circuit (I2C) Bus data transmission protocol, which defines a device that sends data to the bus as a transmitter and a device receiving data as a receiver. Data flow is controlled by a Master device, which generates the serial clock and all START and STOP conditions. The CAT24C256 acts as a Slave device. Master and Slave alternate as either transmitter or receiver. Up to 8 devices may be connected to the bus as determined by the device ad-dress inputs A0, A , and A2.I2C buS PROTOCOlThe I2C bus consists of two ‘wires’, SCL and SDA. The two wires are connected to the V CC supply via pull-up resistors. Master and Slave devices connect to the 2-wire bus via their respective SCL and SDA pins. The transmitting device pulls down the SDA line to ‘transmit’ a ‘0’ and releases it to ‘transmit’ a ‘ ’.Data transfer may be initiated only when the bus is not busy (see A.C. Characteristics).During data transfer, the SDA line must remain stable while the SCL line is HIGH. An SDA transition while SCL is HIGH will be interpreted as a START or STOP condition (Figure ).STARTThe START condition precedes all commands. It consists of a HIGH to LOW transition on SDA while SCL is HIGH. The START acts as a ‘wake-up’ call to all receivers. A bsent a START, a Slave will not respond to commands. STOPThe STOP condition completes all commands. It consists of a LOW to HIGH transition on SDA while SCL is HIGH. The STOP starts the internal Write cycle (when follow-ing a Write command) or sends the Slave into standby mode (when following a Read command).Device AddressingThe Master initiates data transfer by creating a START condition on the bus. The Master then broadcasts an 8-bit serial Slave address. The first 4 bits of the Slave address are set to 0 0, for normal Read/Write opera-tions (Figure 2). The next 3 bits, A2, A and A0, select one of 8 possible Slave devices. The last bit, R/W, specifies whether a Read (1) or Write (0) operation is to be performed.AcknowledgeAfter processing the Slave address, the Slave responds with an acknowledge (ACK) by pulling down the SDA line during the 9th clock cycle (Figure 3). The Slave will also acknowledge the byte address and every data byte presented in Write mode. In Read mode the Slave shifts out a data byte, and then releases the SDA line during the 9th clock cycle. If the Master acknowledges the data, then the Slave continues transmitting. The Master terminates the session by not acknowledging the last data byte (NoACK) and by sending a STOP to the Slave. Bus timing is illustrated in Figure 4.CAT24C256figure 3. Acknowledge Timingfigure 2. Slave Address bitsfigure 1. Start/Stop Timingfigure 4. bus TimingSCLSDA INSDA OUTCAT24C256WRITE OPERATIOnSbyte WriteIn Byte Write mode the Master sends a START, followed by Slave address, two byte address and data to be written (Figure 5). The Slave acknowledges all 4 bytes, and the Master then follows up with a STOP, which in turn starts the internal Write operation (Figure 6). During internal Write, the Slave will not acknowledge any Read or Write request from the Master.Page WriteThe CAT24C256 contains 32,768 bytes of data, arranged in 5 2 pages of 64 bytes each. A two byte address word, following the Slave address, points to the first byte to be written. The most significant bit of the address word is ‘don’t care’, the next 9 bits identify the page and the last 6 bits identify the byte within the page. Up to 64 bytes can be written in one Write cycle (Figure 7).The internal byte address counter is automatically in-cremented after each data byte is loaded. If the Master transmits more than 64 data bytes, then earlier bytes will be overwritten by later bytes in a ‘wrap-around’ fashion (within the selected page). The internal Write cycle starts immediately following the STOP.Acknowledge PollingAcknowledge polling can be used to determine if the CAT24C256 is busy writing or is ready to accept com-mands. Polling is implemented by interrogating the device with a ‘Selective Read’ command (see READ OPERATIONS).The CAT24C256 will not acknowledge the Slave address, as long as internal Write is in progress.Hardware Write ProtectionWith the WP pin held HIGH, the entire memory is pro-tected against Write operations. If the WP pin is left floating or is grounded, it has no impact on the operation of the CAT24C256.CAT24C256 figure 5. byte Write Timingfigure 6. Write Cycle Timingfigure 7. Page Write TimingCAT24C256READ OPERATIOnSImmediate Address ReadIn standby mode, the CAT24C256 internal address counter points to the data byte immediately following the last byte accessed by a previous operation. If that ‘previ-ous’ byte was the last byte in memory, then the address counter will point to the st memory byte, etc. When, following a START, the CAT24C256 is presented with a Slave address containing a ‘ ’ in the R/W bit position (Figure 8), it will acknowledge (ACK) in the 9th clock cycle, and will then transmit data being pointed at by the internal address counter. The Master can stop further transmission by issuing a NoACK, followed by a STOP condition.Selective ReadThe Read operation can also be started at an address different from the one stored in the internal address counter. The address counter can be initialized by per-forming a ‘dummy’ Write operation (Figure 9). Here the START is followed by the Slave address (with the R/W bit set to ‘0’) and the desired two byte address. Instead of following up with data, the Master then issues a 2nd START, followed by the ‘Immediate Address Read’ se-quence, as described earlier.Sequential ReadIf the Master acknowledges the st data byte transmitted by the CAT24C256, then the device will continue trans-mitting as long as each data byte is acknowledged by the Master (Figure 0). If the end of memory is reached during sequential Read, then the address counter will ‘wrap-around’ to the beginning of memory, etc. Sequential Read works with either ‘Immediate Address Read’ or ‘Selective Read’, the only difference being the starting byte address.CAT24C256 figure 8. Immediate Address Read Timingfigure 9. Selective Read Timingfigure 10. Sequential Read TimingCAT24C2568-lEAD 300 MIl WIDE PlASTIC DIP (l)notes:( ) Complies with JEDEC Standard MS00 .(2) All dimensions are in millimeters.(3) Dimensioning and tolerancing per ANSI Y 4.5M- 982ecSYMBOLA A1b b2D E E1e eB LMIN 0.380.369.027.626.09 6.357.872.923.81NOM 0.46 1.771.147.872.54 BSCMAX 4.57A2 3.05 3.810.56c 0.210.260.3510.168.257.119.65For current Tape and Reel information, download the PDF file from:/documents/tapeandreel.pdfPACKAgE OuTlInESCAT24C256Doc No. 04, Rev. D© 2007 by Catalyst Semiconductor, Inc.Characteristics subject to change without notice8-lEAD 150 MIl WIDE SOIC (W)notes:(1) Complies with JEDEC specification MS-012 dimensions.(2) All linear dimensions are in millimeters.SyMbOl A A b C D E E h L MIn 0. 0 .350.334.805.803.800.250.40nOM 0.250. 9MAX 0.25 .750.5 5.006.204.00e .27 BSC0.50 .27Ө10°8°eFor current Tape and Reel information, download the PDF file from:/documents/tapeandreel.pdfCAT24C2562Doc. No. 04, Rev. D© 2007 by Catalyst Semiconductor, Inc.Characteristics subject to change without notice8-lEAD 208 MIl WIDE SOIC, EIAJ (X)notes:(1) Complies with EIAJ specification.(2) All linear dimensions are in millimeters.θcSYMBOLA1A b c D E E1e L MIN 0.050.365.137.755.130.51NOM 0.250.19 1.27 BSCMAX 0.252.030.485.338.265.380.76θ10°8°For current Tape and Reel information, download the PDF file from:/documents/tapeandreel.pdfCAT24C2563Doc No. 04, Rev. D© 2007 by Catalyst Semiconductor, Inc.Characteristics subject to change without noticeORDERIng InfORMATIOnNotes:( ) All packages are RoHS-compliant (Lead-free, Halogen-free). (2) The standard lead finish is NiPdAu.(3) The device used in the above example is a CAT24C256WI-GT3 (SOIC-JEDEC, Industrial Temperature, NiPdAu, Tape & Reel). (4) For SOIC, EIAJ (X) package the standard lead finish is Matte-Tin. This package is available in 2000 pcs/reel, i.e. CAT24C256XI-T2. (5) For additional package and temperature options, please contact your nearest Catalyst Semiconductor Sales office.Catalyst Semiconductor, Inc.Corporate Headquarters 2975 Stender Way Santa Clara, CA 95054Phone: 408.542. 000Fax: 408.542. Copyrights, Trademarks and PatentsTrademarks and registered trademarks of Catalyst Semiconductor include each of the following: Beyond Memory™, DPP™, EZDim™, MiniPot™, and Quad-Mode™Catalyst Semiconductor has been issued U.S. and foreign patents and has patent applications pending that protect its products.CATALYST SEMICONDUCTOR MAKES NO WARRANTY , REPRESENTATION OR GUARANTEE, EXPRESS OR IMPLIED, REGARDING THE SUITABILITY OF ITS PRODUCTS FOR ANY PARTICULAR PURPOSE, NOR THAT THE USE OF ITS PRODUCTS WILL NOT INFRINGE ITS INTELLECTUAL PROPERTY RIGHTS OR THE RIGHTS OF THIRD PARTIES WITH RESPECT TO ANY PARTICULAR USE OR APPLICATION AND SPECIFICALLY DISCLAIMS ANY AND ALL LIABILITY ARISING OUT OF ANY SUCH USE OR APPLICATION, INCLUDING BUT NOT LIMITED TO, CONSEQUENTIAL OR INCIDENTAL DAMAGES.Catalyst Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Catalyst Semiconductor product could create a situation where personal injury or death may occur.Catalyst Semiconductor reserves the right to make changes to or discontinue any product or service described herein without notice. Products with data sheets labeled “Advance Information” or “Preliminary” and other products described herein may not be in production or offered for sale.Catalyst Semiconductor advises customers to obtain the current version of the relevant product information before placing orders. Circuit diagrams illustrate typical semiconductor applications and may not be complete.Publication #: 04Revison: D Issue date: 0 / 2/07REVISIOn HISTORyDate Revision Comments0/07/05A Initial Issue/ 6/05B Update Ordering Information Add Tape and Reel Specifications 02/02/06CUpdate Ordering Information0 / 2/07DUpdate Package Outlines. Add SOIC, EIAJ Package Outlines Update A.C. Characteristics. Add A.C. Test ConditionsUpdate Figures , 3 and 4Delete Package Marking. Deleted Tape and Reel Updated Ordering Information。

SP-DM13A-chinese

DM13A

单位 V V mA V

MHz mA

W

°C/W

°C °C

推荐工作参数

特性 电源电压

输出电压 输出电压

输出电流

输入电压

输入时钟频率 锁存信号(LAT)脉波宽度 数据信号(DCK)脉波宽度 串行输入数据(DAI) 的启动时间 串行输入数据(DAI) 的保持时间 锁存信号(LAT) 的启动时间 锁存信号(LAT) 的保持时间

Page 7

时序图

1. DCK-DAI, DAO

DM13A

2. DCK-LAT 3. LAT-OUT0

16 位 LED 恒流驱动芯片

Version:A.003

未经授权而径予重制、复制、使用或公开本文件,行为人得被追究侵权之相关民刑事责任 Unauthorized reproduction, duplication, use or disclosure of this document will be deemed as infringement.

⎯

单位 V uA V

±3

%

±6

%

±0.5 %/V

±4

4

6

6

mA

10

10

*1 输出电流差异(通道与通道间)定义为”任意 Iout - 平均 Iout” 与 ”平均 Iout”的比率。平均 Iout =(Imax+Imin)/2 *2 输出电流差异(芯片与芯片间) 定义为任选两芯片之最大输出电流与最小输出电流的落差范围。 *3 IO 除外。VDD = Nhomakorabea5.0V

最小值 3.3

1.0

⎯ 5 ⎯ ⎯ 0.8VDD 0.0 ⎯ 15 15 10 10 10 10

HC网络设备产品参数

安全产品技术规范杭州华三通信技术有限公司目录1.防火墙系列 (4)1.1.M9000防火墙核心引导指标说明: (4)1.2.M9006 (4)1.3.M9010 (7)1.4.M9014 (10)1.5.新一代防火墙F50X0核心引导指标说明: (13)1.6.F5040防火墙招标参数 (13)1.7.F5020防火墙招标参数 (14)1.8.F5000-S防火墙招标参数 (16)1.9.F5000-C防火墙招标参数 (17)1.10.新一代F10X0防火墙核心引导指标说明: (19)1.11.H3C SecPath F1020防火墙招标参数 (19)1.12.H3C SecPath F1030防火墙招标参数 (21)1.13.H3C SecPath F1050防火墙招标参数 (23)1.14.H3C SecPath F1060防火墙招标参数 (25)1.15.H3C SecPath F1070防火墙招标参数 (28)1.16.H3C SecPath F1080防火墙招标参数 (30)1.17.三款新千兆防火墙核心引导指标说明: (32)1.18.F1000-E (32)1.19.F1000-E-SI (33)1.20.F1000-A-EI (35)1.21.F1000-S-AI (36)1.22.SecBlade FW Enhanced招标参数 (37)1.23.SecBlade FW招标参数 (39)1.24.SecBlade FW Lite防火墙招标参数 (41)1.25.新一代F1000-C-SI、F100-A/M-SI防火墙核心引导指标说明: (42)1.26.F1000-C-SI防火墙招标参数 (43)1.27.F100-A-SI防火墙招标参数 (44)1.28.F100-M-SI防火墙招标参数 (45)2.VPN系列................................................................................................................. 错误!未定义书签。

C 华三交换机招标参数 V

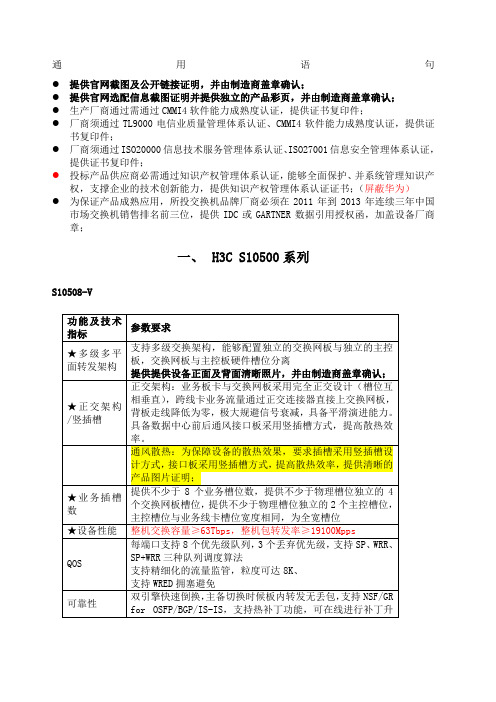

通用语句●提供官网截图及公开链接证明,并由制造商盖章确认;●提供官网选配信息截图证明并提供独立的产品彩页,并由制造商盖章确认;●生产厂商通过需通过CMMI4软件能力成熟度认证,提供证书复印件;●厂商须通过TL9000电信业质量管理体系认证、CMMI4软件能力成熟度认证,提供证书复印件;●厂商须通过ISO20000信息技术服务管理体系认证、ISO27001信息安全管理体系认证,提供证书复印件;●投标产品供应商必需通过知识产权管理体系认证,能够全面保护、并系统管理知识产权,支撑企业的技术创新能力,提供知识产权管理体系认证证书;(屏蔽华为)●为保证产品成熟应用,所投交换机品牌厂商必须在2011年到2013年连续三年中国市场交换机销售排名前三位,提供IDC或GARTNER数据引用授权函,加盖设备厂商章;一、H3C S10500系列S10508-VS10506二、S7500E系列S10508-VS7510E-XS7506E-XS7506E-VS7506E-NOPOES7506E-SS7503E-S三、S5800系列S5800-60C-PWR-H35800-56C-H3S5800-32F-H3S5800-32C-H3四、H3C S5560-EI系列S5560-30S-EIS5560-30C-EIS5560-30F-EIS5560-34C-EIS5560-54C-EI五、H3C S5130-EI系列S5130-28S-EIS5130-28TP-EIS5130-28F-EIS5130-52S-EIS5130-52TP-EIS5130-28S-PWR-EIS5130-28TP-PWR-EI六、H3C S5110 系列S5110-10PS5110-28PS5110-52PS5110-10P-PWRS5110-28P-PWRS5110-52P-PWRSFP-GE-SX-MM850-ASFP-STACK-Kit 堆叠线缆七、H3C S3110系列LS-S3110-10TPLS-S3110-26TPLS-S3110-52TPLS-S3110-10TP-PWRLS-S3110-26TP-PWR八、H3C S3100 V2系列LS-3100V2-8TP-EILS-3100V2-16TP-EILS-3100V2-26TP-EILS-3100V2-52TPLS-3100V2-16TP-PWR-EILS-3100V2-26TP-PWR-EI九、H3C SMB分销系列SMB-S2626SMB-S2652。

1253C中英说明书

1253C泵控说明书Content目录1. Scope应用场合This specification specifies the Curtis 1253C motor speed controllers which are designed for series pump motors. Its typical applications include the hydraulic systems of material handling vehicles and other industrial vehicles.SHINGKO 1253C 电机速度控制器是为串励泵控电机而设计的。

广泛应用于液压系统的重型托盘车和其它工业车辆。

2. Description 概述1253C offers smooth, silent, cost effective motor speed and torque control according to the signals of lifting, tilt, power steering, sideward move (forward move). They will prolong the life of the motors, contactors, batteries and reduce maintenances of the systems as it greatly reduces high current impact.The output PWM can be programmed with speed select inputs SS1-SS4 and analog throttle input. So the 1253C controllers can ensure not only the lifting speed control but also the system stability and safety. These controllers are fully programmable by means of the 1311 programmer, with diagnostic and test capability. System status can also be indicated via an external LED.The 1253C controllers have completely protection functions such as current limit, reverse polarity protection, startup lockout, over voltage protection, low voltage protection, and so on.They can provide lift lockout function with Curtis meters (such as 906, 803, ENGAGE Ⅳ) when battery is deep discharger.CAN communication feature is added to the 1253C, so it can work with other CAN devices such as CAN tiller head which will greatly simplify the wiring.1253C 根据上升、下降、转向、前进信号提供了平稳、安静、有效的电机速度和扭矩控制。

工业以太网交换机Carat1008TXCarat5008EFC2卓越品质

⼯业以太⽹交换机Carat1008TXCarat5008EFC2卓越品质Carat1008TX 8⼝10/100Base-TX,卡轨式⼯业以太⽹交换机,18~36VDC(可选85~265V AC/DC)Carat1008FC 7⼝10/100Base-TX, 1⼝100Base-FX(多模,2公⾥,SC),卡轨式⼯业以太⽹交换机,18~36VDC(可选85~265V AC/DC)Carat1008FC-20 7⼝10/100Base-TX, 1⼝100Base-FX(单模,20公⾥,SC),卡轨式⼯业以太⽹交换机,18~36VDC(可选85~265V AC/DC)Carat1008FC2 6⼝10/100Base-TX,2⼝100Base-FX(多模,2公⾥,SC),卡轨式⼯业以太⽹交换机,18~36VDC(可选85~265V AC/DC)Carat1008FC2-20 6⼝10/100Base-TX,2⼝100Base-FX(单模,20公⾥,SC),卡轨式⼯业以太⽹交换机,18~36VDC(可选85~265V AC/DC) 注1:85~265V AC/DC型号列表价格⽐相应的18~36VDC型号多150元。

注2:单模光⼝传输距离可选40~120KM。

Carat1006ETX 6⼝ 10/100Base-TX,卡轨式⼯业以太⽹交换机,冗余电源18~36VDC Carat1007EFC6⼝ 10/100Base-TX,1⼝100Base-FX(多模,2公⾥,SC),卡轨式⼯业以太⽹交换机,冗余电源18~36VDCCarat1007EFC-20 6⼝10/100Base-TX, 1⼝100Base-FX(单模,20公⾥,SC),卡轨式⼯业以太⽹交换机,冗余电源18~36VDCCarat1008EFC26⼝ 10/100Base-TX,2⼝100Base-FX(多模,2公⾥,SC),卡轨式⼯业以太⽹交换机,冗余电源18~36VDCCarat1008EFC2-206⼝ 10/100Base-TX,2⼝100Base-FX(单模,20公⾥,SC),卡轨式⼯业以太⽹交换机,冗余电源18~36VDCCarat1010ETX10⼝ 10/100Base-TX,卡轨式⼯业以太⽹交换机,冗余电源18~36VDCCarat1010EFC9⼝ 10/100Base-TX,1⼝100Base-FX(多模,2公⾥,LC),卡轨式⼯业以太⽹交换机,冗余电源18~36VDCCarat1010EFC-20 9⼝10/100Base-TX, 1⼝100Base-FX(单模,20公⾥,LC),卡轨式⼯业以太⽹交换机,冗余电源18~36VDCCarat1010EFC28⼝ 10/100Base-TX,2⼝100Base-FX(多模,2公⾥,LC),卡轨式⼯业以太⽹交换机,冗余电源18~36VDCCarat1010EFC2-20 8⼝10/100Base-TX, 2⼝100Base-FX(单模,20公⾥,LC),卡轨式⼯业以太⽹交换机,冗余电源18~36VDCCarat1010EGC9⼝ 10/100Base-TX,1⼝1000Base-SX(多模,2公⾥,LC),卡轨式⼯业以太⽹交换机,冗余电源18~36VDCCarat1010EGC-20 9⼝10/100Base-TX, 1⼝1000Base-LX(单模,20公⾥,LC),卡轨式⼯业以太⽹交换机,冗余电源18~36VDCCarat1010EGC28⼝ 10/100Base-TX,2⼝1000Base-SX(多模,2公⾥,LC),卡轨式⼯业以太⽹交换机,冗余电源18~36VDCCarat1010EGC2-20 8⼝10/100Base-TX, 2⼝1000Base-LX(单模,20公⾥,LC),卡轨式⼯业以太⽹交换机,冗余电源18~36VDCCarat1018ETX18⼝ 10/100Base-TX,卡轨式⼯业以太⽹交换机,18~36VDC,冗余电源IP40防护等级Carat1018EFC17⼝ 10/100Base-TX,1⼝100Base-FX(多模,2公⾥,LC),卡轨式⼯业以太⽹交换机,冗余电源18~36VDCCarat1018EFC-20 17⼝10/100Base-TX, 1⼝100Base-FX(单模,20公⾥,LC),卡轨式⼯业以太⽹交换机,冗余电源18~36VDCCarat1018EFC216⼝ 10/100Base-TX,2⼝100Base-FX(多模,2公⾥,LC),卡轨式⼯业以太⽹交换机,冗余电源18~36VDCCarat1018EFC2-20 16⼝10/100Base-TX, 2⼝100Base-FX(单模,20公⾥,LC),卡轨式⼯业以太⽹交换机,冗余电源18~36VDCCarat1018EGC17⼝ 10/100Base-TX,1⼝1000Base-SX(多模,0.5公⾥,LC),卡轨式⼯业以太⽹交换机,冗余电源18~36VDCCarat1018EGC-20 17⼝10/100Base-TX, 1⼝1000Base-LX(单模,20公⾥,LC),卡轨式⼯业以太⽹交换机,冗余电源18~36VDCCarat1018EGC216⼝ 10/100Base-TX,2⼝1000Base-SX(多模,0.5公⾥,LC),卡轨式⼯业以太⽹交换机,冗余电源18~36VDCCarat1018EGC2-20 16⼝10/100Base-TX, 2⼝1000Base-LX(单模,20公⾥,LC),卡轨式⼯业以太⽹交换机,冗余电源18~36VDC 注1:单模光⼝传输距离可选40~120KM。

RC28F128J3A-150资料