IDT74LVC573APY中文资料

74LVC3G07中文资料

Table 5: Function table [1] Input nA L H

[1] H = HIGH voltage level; L = LOW voltage level; Z = high-impedance OFF-state.

9. Limiting values

Output nY L Z

input diode current output diode current output sink current VCC or GND current storage temperature power dissipation

VI < 0 V VO < 0 V VO = 0 V to 6.5 V

74AC573介绍

74HC573和74LS373原理一样,8数据锁存器。

主要用于数码管、按键等等的控制1. 真值表参见74LS373的PDF的第2页:Dn LE OE OnH H L HL H L LX L L QoX X H Z这个就是真值表,表示这个芯片在输入和其它的情况下的输出情况。

每个芯片的数据手册(datasheet)中都有真值表。

布尔逻辑比较简单,在此不赘述;2. 高阻态就是输出既不是高电平,也不是低电平,而是高阻抗的状态;在这种状态下,可以多个芯片并联输出;但是,这些芯片中只能有一个处于非高阻态状态,否则会将芯片烧毁;高阻态的概念在RS232和RS422通讯中还可以用到。

3. 数据锁存当输入的数据消失时,在芯片的输出端,数据仍然保持;这个概念在并行数据扩展中经常使用到。

4. 数据缓冲加强驱动能力。

74LS244/74LS245/74LS373/74LS573都具备数据缓冲的能力。

OE:output_enable,输出使能;LE:latch_enable,数据锁存使能,latch是锁存的意思;Dn:第n路输入数据;On:第n路输出数据;再看这个真值表,意思如下:第四行:当OE=1是,无论Dn、LE为何,输出端为高阻态;第三行:当OE=0、LE=0时,输出端保持不变;第二行第一行:当OE=0、LE=1时,输出端数据等于输入端数据;结合下面的波形图,在实际应用的时候是这样做的:a. OE=0;b.先将数据从单片机的口线上输出到Dn;c.再将LE从0->1->0d.这时,你所需要输出的数据就锁存在On上了,输入的数据在变化也影响不到输出的数据了;实际上,单片机现在在忙着干别的事情,串行通信、扫描键盘……单片机的资源有限啊。

在单片机按照RAM方式进行并行数据的扩展时,使用movx @dptr, A这条指令时,这些时序是由单片机来实现的。

后面的表格中还有需要时间的参数,你不需要去管它,因为这些参数都是几十ns级别的,对于单片机在12M下的每个指令周期最小是1us的情况下,完全可以实现;如果是你自己来实现这个逻辑,类似的指令如下:mov P0,A ;将数据输出到并行数据端口clr LEsetb LEclr LE ;上面三条指令完成LE的波形从0->1->0的变化74ls573跟74LS373逻辑上完全一样,只不过是管脚定义不一样,数据输入和输出端。

SN74LVC573APW(表贴三态输出八D锁存器)

IMPORTANT NOTICETexas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER’S RISK.In order to minimize risks associated with the customer’s applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI’s publication of information regarding any third party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.Copyright © 1998, Texas Instruments Incorporated。

SN74LVC573A中文资料

元器件交易网IMPORTANT NOTICETexas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinueany product or service without notice, and advise customers to obtain the latest version of relevant informationto verify, before placing orders, that information being relied on is current and complete. All products are soldsubject to the terms and conditions of sale supplied at the time of order acknowledgement, including thosepertaining to warranty, patent infringement, and limitation of liability.TI warrants performance of its semiconductor products to the specifications applicable at the time of sale inaccordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extentTI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarilyperformed, except those mandated by government requirements.CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OFDEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICALAPPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, ORWARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHERCRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TOBE FULLY AT THE CUSTOMER’S RISK.In order to minimize risks associated with the customer’s applications, adequate design and operatingsafeguards must be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance or customer product design. TI does not warrant or representthat any license, either express or implied, is granted under any patent right, copyright, mask work right, or otherintellectual property right of TI covering or relating to any combination, machine, or process in which suchsemiconductor products or services might be or are used. TI’s publication of information regarding any thirdparty’s products or services does not constitute TI’s approval, warranty or endorsement thereof.Copyright © 1998, Texas Instruments Incorporated。

74hc573中文资料_数据手册_参数

PACKAGE OUTLINES See "74HC/HCT!HCU!HCMOS Logic Package Outlines".

7 December 1990

万联芯城

万联芯城 电子元器件物料全国供应,专业提 供电子元器件原装现货产品,1 片起订,价格优势明显,电子元 器件采购网万联芯城目前为长电科技,顺络电子,先科 ST 等多 家知名原厂的指定授权代理商,专为客户提供电子元器件配单业 务,提交物料清单即可当天报价当天发货,点击进入万联芯城。

1990年12月 2飞利浦半导体产品SPECI FI CATION八进制D型透明锁存器;三态 74HC / 74HC573特征 ?74hc573相反的输入和输出包装的两侧容易与微处理器接口 ?用作输入或 输出端口微处理器/微计算机 ?3态非反74HC573相输出总线应用 ?共用3态输出使能输 入 ?在功能上与“563”和“373” ?输出能力:总线驱动程序 ?74hc573我 CC 类别:MSI 一般描述 74HC / HCT573是高速的硅栅CMOS器件和引脚兼容低功耗肖特基 TTL(LSTTL).他们在中指定符合JEDEC标准NO. 7A. 74HC / HCT573是八进制D型透 明闩锁特色每个锁存器都有独立的D型输入和面向公共汽车的三态输出应用.一个锁存 使能(LE)输入和一个输出使能(OE)74HC573输入是常见的到所有的锁存器. “573”由8个D型组成透明锁存器与三态真74hc573实输74HC573出.当LE为高时,数据 在 D N 输入进入锁存器. 在这条件锁存器是透明的,即锁存输出将改变状态每次都有 相应的D输入变化.当LE为低电平时,锁存器存储信息出现在 D - 74HC573输入一个设 定时间 LE的高到低转换.当OE为低时,74hc573内容为输出端有8个锁存器.当OE为高电 平时,74HC573输出将转至高阻抗关闭状态. OE输入的操作没有影响锁存器的状态. “573”与功能相同 “563”和“373”,74hc573但“563”却有倒相输出和“373”有一 个不同的引脚排列.快速参考数据 GND = 0 V; T AMB = 25℃; T R = T F = 6NS笔记 1. C PD 用于确定动态功耗(P D ,单位为μW): P D = C PD ×V CC2 ×F I +Σ(C L ×V CC2 ×F O )其中: F I =以MHZ为单位的输入频率; F O =以MHZ为单位的输出频率 Σ(C L ×V CC2 ×F O )=输出之和 C L 74HC573=输出负载电容,单位PF; V CC = V 中的电源电压 2.对于HC,条件是V I = GND到V CC ; 对于HCT,条件是V I = GND到V CC - 1.5 V订购信息看到 “74HC / HCT / HCU / HCMOS逻辑封装信息” .74HC573符号 参数条件典型单元 H

74LVC573APW-T中文资料

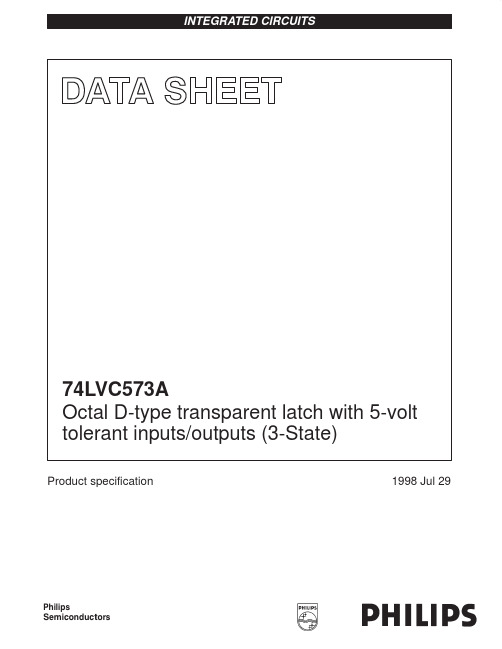

74LVC573AOctal D-type transparent latch with 5 V tolerantinputs/outputs; 3-stateRev. 04.00 — 18 May 2006Product data sheet1.General descriptionThe 74LVC573A consists of eight D-type transparent latches, featuring separate D-typeinputs for each latch and 3-state true outputs for bus-oriented applications. A LatchEnable (LE) input and an Output Enable (OE) input are common to all internal latches.When LE is HIGH, data at the Dn inputs enters the latches. In this condition, the latchesare transparent, that is, a latch output will change each time its corresponding D-inputchanges. When LE is LOW, the latches store the information that was present at theD-inputs one setup time preceding the HIGH-to-LOW transition of LE.When OE is LOW, the contents of the eight latches are available at the outputs. When OEis HIGH, the outputs go to the high impedance OFF-state. Operation of the OE input doesnot affect the state of the latches.It is a high-performance, low-power, low-voltage, Si-gate CMOS device, superior to mostadvanced CMOS compatible TTL families.Inputs can be driven from either 3.3V or5V devices. When disabled, up to 5.5 V can beapplied to the outputs. This feature allows the use of these devices as translators in mixed3.3V or5V applications.The 74LVC573A is functionally identical to the 74LVC373A, but has a different pinarrangement.2.Features5 V tolerant inputs/outputs, for interfacing with 5V logicSupply voltage range from 1.2V to3.6VCMOS low power consumptionDirect interface with TTL levelsHigh-impedance when V CC = 0 VFlow-through pin-out architectureComplies with JEDEC standard JESD8-B/JESD36ESD protection:HBM JESD22-A114-C exceeds 2000VCDM JESD22-C101-C exceeds 1000VSpecified from −40°C to +85°C and −40°C to 125°C3.Ordering information4.Functional diagramTable 1:Ordering informationType numberPackage Temperature rangeNameDescriptionVersion74LVC573AD−40 °C to +125 °C SO20plastic small outline package; 20leads; body width 7.5mm SOT163-174LVC573ADB −40 °C to +125 °C SSOP20plastic shrink small outline package; 20leads; body width 5.3mmSOT339-174LVC573APW −40 °C to +125 °C TSSOP20plastic thin shrink small outline package; 20leads; body width 4.4mmSOT360-174LVC573ABQ −40 °C to +125 °C DHVQFN20plastic dual in-line compatible thermal enhanced very thin quad flat package; no leads; 20terminals; body 2.5×4.5×0.85mmSOT764-15.Pinning information5.1Pinning5.2Pin descriptionTable 2:Pin descriptionSymbol Pin DescriptionOE1output enable input (active LOW) D0 - D7 2 - 9data inputGND10ground (0 V)LE11latch enable input (active HIGH) Q7 - Q012 - 19data outputV CC20supply voltage6.Functional description[1]H = HIGH voltage levelh = HIGH voltage level one setup time prior to the HIGH-to-LOW LE transition L = LOW voltage levell = LOW voltage level one setup time prior to the HIGH-to-LOW LE transition Z = High-impedance OFF-state.7.Limiting values[1]The input and output voltage ratings may be exceeded if the input and output current ratings are observed.[2]For SO20 packages: above 70°C the value of P tot derates linearly with 8mW/K.For (T)SSOP20 packages: above 60°C the value of P tot derates linearly with 5.5mW/K.For DHVQFN20 packages: above 60°C the value of P tot derates linearly with 4.5mW/K.Table 3:Functional table [1]Operating modes Input Internal latch OutputOE LE Dn QnEnable and read register (transparent mode)L H L L L L H H H H Latch and read register L L l L L L L h H H Latch register and disable outputsH L l L Z HLhHZTable 4:Limiting valuesIn accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V).Symbol Parameter Conditions Min Max Unit V CC supply voltage −0.5+6.5V I IK input clamping current V I < 0-−50mA V I input voltage[1]−0.5+6.5V I OK output clamping current V O > V CC or V O < 0-±50mA V O output voltage [1]−0.5V CC + 0.5V I O output current V O = 0 to V CC-±50mA I CC supply current -+100mA I GND ground current -−100mA T stg storage temperature −65+150°C P tottotal power dissipationT amb = −40 °C to +125 °C[2]-500mW8.Recommended operating conditions9.Static characteristicsTable 5:Recommended operating conditions Symbol Parameter ConditionsMin Typ Max Unit V CC supply voltage 1.2- 3.6V V I input voltage 0- 5.5V V O output voltage output HIGH- or LOW-state 0-V CC V output 3-state 0- 5.5V T amb ambient temperature in free air−40-+125°C ∆t/∆Vinput transition riseand fall rateV CC = 1.65 V to 2.7 V 0-20ns/V V CC = 2.7 V to 3.6 V 0-10ns/VTable 6:Static characteristicsAt recommended operating conditions voltages are referenced to GND (ground = 0 V). Symbol Parameter Conditions Min Typ [1]Max Unit T amb =−40 °C to +85°C V IHHIGH-level input voltageV CC = 1.2 V1.08--V V CC = 1.65 V to 1.95 V 0.65 × V CC --V V CC = 2.3 V to 2.7 V 1.7--V V CC = 2.7 V to 3.6 V2.0--V V ILLOW-level input voltageV CC = 1.2 V--0.12V V CC = 1.65 V to 1.95 V --0.35 × V CC VV CC = 2.3 V to 2.7 V --0.7V V CC = 2.7 V to 3.6 V--0.8V V OHHIGH-level output voltageV I =V IH or V ILI O =−100µA; V CC = 1.65 V to 3.6 V V CC −0.2V CC -V I O =−4mA; V CC = 1.65 V V CC −0.45--V I O =−8mA; V CC = 2.3 V V CC −0.5--V I O =−12mA; V CC = 2.7 V V CC −0.5--V I O =−18mA; V CC = 3.0 V V CC −0.6--V I O =−24mA; V CC = 3.0 VV CC −0.8--V V OLLOW-level output voltageV I =V IH or V ILI O =100µA; V CC = 1.65 V to 3.6 V --0.20V I O =4mA; V CC = 1.65 V --0.45V I O =8mA; V CC = 2.3 V --0.6V I O =12mA; V CC = 2.7 V --0.4V I O =24mA; V CC = 3.0 V--0.55V I I input leakage current V CC = 3.6 V; V I =5.5V or GND [2]-±0.1±5µA I OZ OFF-state output current V CC =3.6V;V I =V IH or V IL ; V O =5.5V or GND-0.1±10µA I OFFpower off leakage supplyV CC =0.0V;V I or V O =5.5V-0.1±10µA[1]All typical values are measured at V CC = 3.3 V (unless stated otherwise) and T amb =25°C.[2]The specified overdrive current at the data input forces the data input to the opposite logic input state.I CC supply currentV CC = 3.6 V; V I =V CC or GND; I O =0-0.110µA ∆I CC additional supply current per input pin V CC = 2.7 V to 3.6 V; V I =V CC −0.6V; I O =0-5500µA C I input capacitance V CC =0 V to 3.6V; V I = GND to V CC - 5.0-pF T amb =−40 °C to +125°CV IHHIGH-level input voltageV CC = 1.2 V1.08--V V CC = 1.65 V to 1.95 V 0.65 × V CC --V V CC = 2.3 V to 2.7 V 1.7--V V CC = 2.7 V to 3.6 V2.0--V V ILLOW-level input voltageV CC = 1.2 V--0.12V V CC = 1.65 V to 1.95 V --0.35 × V CC VV CC = 2.3 V to 2.7 V --0.7V V CC = 2.7 V to 3.6 V--0.8V V OHHIGH-level output voltageV I =V IH or V ILI O =−100µA; V CC = 1.65 V to 3.6 V V CC −0.3--V I O =−4mA; V CC = 1.65 V V CC −0.6--V I O =−8mA; V CC = 2.3 V V CC −0.65--V I O =−12mA; V CC = 2.7 V V CC −0.65--V I O =−18mA; V CC = 3.0 V V CC −0.75--V I O =−24mA; V CC = 3.0 VV CC −1--V V OLLOW-level output voltageV I =V IH or V ILI O =100µA; V CC = 1.65 V to 3.6 V --0.3V I O =4mA; V CC = 1.65 V --0.65V I O =8mA; V CC = 2.3 V --0.8V I O =12mA; V CC = 2.7 V --0.6V I O =24mA; V CC = 3.0 V--0.8V I I input leakage current V CC = 3.6 V; V I =5.5V or GND --±20µA I CC supply currentV CC = 3.6 V; V I =V CC or GND; I O =0--40µA ∆I CCadditional supply current per input pinV CC = 2.7 V to 3.6 V; V I =V CC −0.6V; I O =0--5000µATable 6:Static characteristics …continuedAt recommended operating conditions voltages are referenced to GND (ground = 0 V). Symbol Parameter ConditionsMin Typ [1]Max Unit10.Dynamic characteristicsTable 7:Dynamic characteristicsVoltages are referenced to GND (ground=0V). For test circuit see Figure11.Symbol Parameter Conditions Min Typ[1]Max Unit T amb=−40°C to+85 °Ct PHL, t PLH HIGH to LOW, LOW to HIGH propagation delayDn to Qn see Figure7V CC= 1.2 V-16.0-nsV CC= 1.65V to 1.95 V 1.97.814.8nsV CC= 2.3V to 2.7 V 1.3 4.17.7nsV CC= 2.7V 2.0 4.17.2nsV CC= 3.0V to3.6V 1.6 3.4 6.2ns LE to Qn see Figure8V CC= 1.2 V-16.0-nsV CC= 1.65V to 1.95 V 1.97.714.6nsV CC= 2.3V to 2.7 V 1.3 4.17.5nsV CC= 2.7V 1.7 3.77.0nsV CC= 3.0V to3.6V 1.6 3.4 6.3nst PZH, t PZL OFF-state to HIGH, OFF-state toLOW propagation delay OE to Qn see Figure9V CC= 1.2 V-18.0-ns V CC = 1.65 V to 1.95 V 1.57.516ns V CC = 2.3 V to 2.7 V 1.2 4.28.8ns V CC = 2.7 V 2.1 4.27.5ns V CC = 3.0 V to 3.6 V 1.5 3.47.0nst PHZ, t PLZ HIGH to OFF-state,LOW to OFF-state propagationdelay OE to Qn see Figure9V CC= 1.2 V-8.0-ns V CC = 1.65 V to 1.95 V0.4 3.38.1ns V CC = 2.3 V to 2.7 V0.3 1.8 4.6ns V CC = 2.7 V 1.8 3.0 5.2ns V CC = 3.0 V to 3.6 V 1.5 2.5 4.9nst W pulse width, LE HIGH see Figure8V CC = 1.65 V to 1.95 V8.0--nsV CC = 2.3 V to 2.7 V 4.0--nsV CC = 2.7 V 3.2--nsV CC = 3.0 V to 3.6 V 3.2 1.6-ns t su setup time, nD to nCP see Figure10V CC = 1.65 V to 1.95 V 5.0--nsV CC = 2.3 V to 2.7 V 3.7--nsV CC = 2.7 V 1.7--nsV CC = 3.0 V to 3.6 V 1.7--nst hhold time, Dn to LEsee Figure 10V CC = 1.65 V to 1.95 V 3.0--ns V CC = 2.3 V to 2.7 V 1.9--ns V CC = 2.7 V 1.5--ns V CC = 3.0 V to 3.6 V1.4--ns t sk(0)output skew timeV CC = 3.0 V to 3.6 V[2]--1.0nsT amb =−40°C to +125 °Ct PHL , t PLHHIGH to LOW, LOW to HIGH propagation delay Dn to Qnsee Figure 7V CC = 1.2 V---ns V CC = 1.65V to 1.95 V 1.9-18.5ns V CC = 2.3V to 2.7 V 1.3-10.0ns V CC = 2.7V 2.0-9.5ns V CC = 3.0V to 3.6V1.6-8.0nsLE to Qnsee Figure 8V CC = 1.2 V---ns V CC = 1.65V to 1.95 V 1.9-18.5ns V CC = 2.3V to 2.7 V 1.3-9.5ns V CC = 2.7V 1.7-9.0ns V CC = 3.0V to 3.6V1.6-8.0nst PZH , t PZLOFF-state to HIGH, OFF-state to LOW propagation delay OE to Qnsee Figure 9V CC = 1.2 V---ns V CC = 1.65 V to 1.95 V 1.5-20ns V CC = 2.3 V to 2.7 V 1.2-11ns V CC = 2.7 V 2.1-9.5ns V CC = 3.0 V to 3.6 V1.5-9.0nst PHZ , t PLZHIGH to OFF-state,LOW to OFF-state propagation delay OE to Qnsee Figure 9V CC = 1.2 V---ns V CC = 1.65 V to 1.95 V 0.4-10.5ns V CC = 2.3 V to 2.7 V 0.3- 6.0ns V CC = 2.7 V 1.8- 6.5ns V CC = 3.0 V to 3.6 V1.5- 6.5nst Wpulse width, LE HIGHsee Figure 8V CC = 1.65 V to 1.95 V 8.0--ns V CC = 2.3 V to 2.7 V 4.0--ns V CC = 2.7 V 3.2--ns V CC = 3.0 V to 3.6 V3.2--nsTable 7:Dynamic characteristics …continuedVoltages are referenced to GND (ground =0V). For test circuit see Figure 11.Symbol Parameter Conditions Min Typ [1]Max Unit[1]Typical values are measured at T amb =25°C and V CC = 1.8 V, 2.5 V, 2.7 V, and 3.3 V respectively.[2]Skew between any two outputs of the same package switching in the same direction. This parameter is guaranteed by design.[3]C PD is used to determine the dynamic power dissipation (P D in µW).P D =C PD ×V CC 2×f i ×N +Σ(C L ×V CC 2×f o )where:f i = input frequency in MHz,f o =output frequency in MHz,C L =output load capacitance in pF,V CC =supply voltage in V,N =number of inputs,Σ(C L ×V CC 2×f o )=sum of the outputs.11.AC waveformst susetup time, nD to nCPsee Figure 10V CC = 1.65 V to 1.95 V 5.0--ns V CC = 2.3 V to 2.7 V 3.7--ns V CC = 2.7 V 1.7--ns V CC = 3.0 V to 3.6 V1.7--ns t hhold time, Dn to LEsee Figure 10V CC = 1.65 V to 1.95 V 3.0--ns V CC = 2.3 V to 2.7 V 1.9--ns V CC = 2.7 V 1.5--ns V CC = 3.0 V to 3.6 V1.4--ns t sk(o)output skew timeV CC = 3.0 V to 3.6 V[2]--1.0nsT amb = 25 °C C PDpower dissipation capacitance per latch.V I = GND to V CC[3]V CC = 1.65 V to 1.95 V -7-pF V CC = 2.3 V to 2.7 V -10-pF V CC = 3.0 V to 3.6 V-13-pFTable 7:Dynamic characteristics …continuedVoltages are referenced to GND (ground =0V). For test circuit see Figure 11.Symbol ParameterConditions Min Typ [1]Max UnitTable 8:Test dataSupply voltage Input Load V EXTV I t r, t f C L R L t PLH, t PHL t PLZ, t PZL t PHZ, t PZH1.65V to1.95V V CC≤ 2 ns30pF 1 kΩopen 2 × V CC GND2.3V to2.7V V CC≤ 2 ns30pF500Ωopen 2 × V CC GND2.7V 2.7V≤ 2.5ns50pF500Ωopen6V GND12.Package outlineSO20: plastic small outline package; 20 leads; body width 7.5 mm SOT163-1SSOP20: plastic shrink small outline package; 20 leads; body width 5.3 mm SOT339-1TSSOP20: plastic thin shrink small outline package; 20 leads; body width 4.4 mm SOT360-1SOT764-1DHVQFN20: plastic dual in-line compatible thermal enhanced very thin quad flat package; no leads;20 terminals; body 2.5 x 4.5 x 0.85 mm13.Abbreviations14.Revision historyTable 9.AbbreviationsAcronym DescriptionCDM Charged Device ModelCMOS Complementary Metal Oxide Semiconductor DUT Device Under Test ESD ElectroStatic Discharge HBM Human Body Model TTLTransistor Transistor LogicTable 10.Revision historyDocument ID Release date Data sheet status Change notice Supersedes 74LVC573A_4<tbd>Product data sheet-74LVC573A_3Modifications:•The format of this data sheet is redesigned to comply with the current presentation and information standard of Philips Semiconductors.•Table 4, Table 5, Table 6, Table 7 and Table 8: values added for lower voltage ranges.74LVC573A_3 (939775011938)20031003Product specification -74LVC573A_274LVC573A_2 (939775010494)20030526Product specification -74LVC573A_174LVC573A_1 (939775004513)19980729Product specification--15.Legal information15.1Data sheet status[1]Please consult the most recently issued document before initiating or completing a design. [2]The term ‘short data sheet’ is explained in section “Definitions”.[3]The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL .15.2DefinitionsDraft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. Philips Semiconductors does not give any representations or warranties as to the accuracy or completeness ofinformation included herein and shall have no liability for the consequences of use of such information.Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local Philips Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.15.3DisclaimersGeneral — Information in this document is believed to be accurate andreliable. However, Philips Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.Right to make changes — Philips Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.Suitability for use — Philips Semiconductors products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure ormalfunction of a Philips Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmentaldamage. Philips Semiconductors accepts no liability for inclusion and/or use of Philips Semiconductors products in such equipment or applications and therefore such inclusion and/or use is for the customer’s own risk.Applications — Applications that are described herein for any of theseproducts are for illustrative purposes only. Philips Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) may cause permanent damage to the device. Limiting values are stress ratings only and andoperation of the device at these or any other conditions above those given in the Characteristics sections of this document is not implied. Exposure to limiting values for extended periods may affect device reliability.Terms and conditions of sale — Philips Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at /profile/terms , including thosepertaining to warranty, intellectual property rights infringement and limitation of liability, unless explicitly otherwise agreed to in writing by PhilipsSemiconductors. In case of any inconsistency or conflict between information in this document and such terms and conditions, the latter will prevail.No offer to sell or license — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.15.4TrademarksNotice: All referenced brands, product names, service names and trademarks are the property of their respective owners.16.Contact informationFor additional information, please visit: For sales office addresses, send an email to: sales.addresses@Document status [1][2]Product status [3]DefinitionObjective [short] data sheet Development This document contains data from the objective specification for product development. Preliminary [short] data sheet Qualification This document contains data from the preliminary specification. Product [short] data sheetProductionThis document contains the product specification.17.Contents1General description. . . . . . . . . . . . . . . . . . . . . . 12Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13Ordering information. . . . . . . . . . . . . . . . . . . . . 24Functional diagram . . . . . . . . . . . . . . . . . . . . . . 25Pinning information. . . . . . . . . . . . . . . . . . . . . . 45.1Pinning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45.2Pin description . . . . . . . . . . . . . . . . . . . . . . . . . 46Functional description . . . . . . . . . . . . . . . . . . . 57Limiting values. . . . . . . . . . . . . . . . . . . . . . . . . . 58Recommended operating conditions. . . . . . . . 69Static characteristics. . . . . . . . . . . . . . . . . . . . . 610Dynamic characteristics. . . . . . . . . . . . . . . . . . 811AC waveforms . . . . . . . . . . . . . . . . . . . . . . . . . 1012Package outline. . . . . . . . . . . . . . . . . . . . . . . . 1313Abbreviations. . . . . . . . . . . . . . . . . . . . . . . . . . 1714Revision history. . . . . . . . . . . . . . . . . . . . . . . . 1715Legal information. . . . . . . . . . . . . . . . . . . . . . . 1815.1Data sheet status . . . . . . . . . . . . . . . . . . . . . . 1815.2Definitions. . . . . . . . . . . . . . . . . . . . . . . . . . . . 1815.3Disclaimers. . . . . . . . . . . . . . . . . . . . . . . . . . . 1815.4Trademarks. . . . . . . . . . . . . . . . . . . . . . . . . . . 1816Contact information. . . . . . . . . . . . . . . . . . . . . 1817Contents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19Please be aware that important notices concerning this document and the product(s)described herein, have been included in section ‘Legal information’.© Koninklijke Philips Electronics N.V.2006.All rights reserved.。

74ls573中文资料

74ls573中文资料三态总线驱动输出·置数全并行存取·缓冲控制输入·使能输入有改善抗扰度的滞后作用原理:74LS573 的八个锁存器都是透明的D 型锁存器,当使能(G)为高时,Q 输出将随数据(D)输入而变。

当使能为低时,输出将锁存在已建立的数据电平上。

输出控制不影响锁存器的内部工作,即老数据可以保持,甚至当输出被关闭时,新的数据也可以置入。

这种电路可以驱动大电容或低阻抗负载,可以直接与系统总线接口并驱动总线,而不需要外接口。

特别适用于缓冲寄存器,I/O 通道,双向总线驱动器和工作寄存器。

H=高电平 L=低电平×=不定 Z=高阻态QO=建立稳态输入条件前Q的电平引脚图及功能图Operating Conditions 操作条件Symbol 符号Parameter 参数DM74LS最小典型最大VCC Supply Voltage 电源电压 4.75 5 5.25VIH High Level Input Voltage输入高电平电压 2 - -VIL LOW Level Input Voltage 输入低电平电压- - 0.8IOH HIGH Level Input Current输入高电平电流- - −2.6IOL LOW Level Output Current低电平输出电流- - 24TA Free Air Operating Temperature工作温度0 - 70Note 1: The “Absolute Maximum Ratings” are those values beyond which the safety of th cannot be guaranteed. The device should not be operated at these limits. The parametri defined in the “Electrical Characteristics” table are not guaranteed at the absolute ratings. The “Recommended Operating Conditions” table will define the conditions fo device operation.Electrical Characteristics 直流电气特性Over recommended operating free air temperature range (unless otherwise noted)Symbol 符号Parameter 参数Conditions 条件最小典型最大单VI Input Clamp Voltage输入钳位电压VCC=最小, II=−18 mA - - −1.5VOH High Level OutputVoltage输出高电平电压VCC = 最小, IOH=最大,VIL = 最大2.73.4 -VOL Low Level OutputVoltage输出低电平电压VCC = 最小, IOL=最大- 0.35 0.5VIH = 最小- - -。

74LV573A中文资料

74LV573A中⽂资料PACKAGING INFORMATIONOrderable Device Status (1)Package Type Package Drawing Pins Package Qty Eco Plan (2)Lead/Ball Finish MSL Peak Temp (3)SN74LV573ADBR ACTIVE SSOP DB 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573ADBRE4ACTIVE SSOPDB 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573ADGVR ACTIVE TVSOP DGV 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573ADGVRE4ACTIVE TVSOP DGV 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573ADW ACTIVE SOIC DW 2025Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573ADWE4ACTIVE SOIC DW 2025Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573ADWR ACTIVE SOIC DW 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573ADWRE4ACTIVE SOIC DW 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573AGQNRACTIVEBGA MI CROSTA R JUNI ORGQN201000TBDSNPBLevel-1-240C-UNLIMSN74LV573ANSR ACTIVE SO NS 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573ANSRE4ACTIVE SO NS 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573APW ACTIVE TSSOP PW 2070Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573APWE4ACTIVE TSSOP PW 2070Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573APWR ACTIVE TSSOP PW 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573APWRE4ACTIVE TSSOP PW 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573APWRG4ACTIVE TSSOP PW 202000Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573APWT ACTIVE TSSOP PW 20250Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573APWTE4ACTIVE TSSOP PW 20250Green (RoHS &no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74LV573ARGYR ACTIVE QFN RGY 201000Green (RoHS &no Sb/Br)CU NIPDAU Level-2-260C-1YEAR SN74LV573ARGYRG4ACTIVE QFN RGY 201000Green (RoHS &no Sb/Br)CU NIPDAU Level-2-260C-1YEAR SN74LV573AZQNRACTIVEBGA MI CROSTA R JUNI ORZQN201000Green (RoHS &no Sb/Br)SNAGCULevel-1-260C-UNLIM(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part ina new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan-The planned eco-friendly classification:Pb-Free(RoHS),Pb-Free(RoHS Exempt),or Green(RoHS&no Sb/Br)-please check /doc/c811093619.html/productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free(RoHS):TI's terms"Lead-Free"or"Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all6substances,including the requirement that lead not exceed0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free(RoHS Exempt):This component has a RoHS exemption for either1)lead-based flip-chip solder bumps used between the die and package,or2)lead-based die adhesive used between the die and leadframe.The component is otherwise considered Pb-Free(RoHS compatible)as defined above.Green(RoHS&no Sb/Br):TI defines"Green"to mean Pb-Free(RoHS compatible),and free of Bromine(Br)andAntimony(Sb)based flame retardants(Br or Sb do not exceed0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.。

74ls573中文资料

74ls573中文资料三态总线驱动输出·置数全并行存取·缓冲控制输入·使能输入有改善抗扰度的滞后作用原理:74LS573 的八个锁存器都是透明的D 型锁存器,当使能(G)为高时,Q 输出将随数据(D)输入而变。

当使能为低时,输出将锁存在已建立的数据电平上。

输出控制不影响锁存器的内部工作,即老数据可以保持,甚至当输出被关闭时,新的数据也可以置入。

这种电路可以驱动大电容或低阻抗负载,可以直接与系统总线接口并驱动总线,而不需要外接口。

特别适用于缓冲寄存器,I/O 通道,双向总线驱动器和工作寄存器。

H=高电平 L=低电平×=不定 Z=高阻态QO=建立稳态输入条件前Q的电平引脚图及功能图Operating Conditions 操作条件Symbol 符号Parameter 参数DM74LS最小典型最大VCC Supply Voltage 电源电压 4.75 5 5.25VIH High Level Input Voltage输入高电平电压 2 - -VIL LOW Level Input Voltage 输入低电平电压- - 0.8IOH HIGH Level Input Current输入高电平电流- - −2.6IOL LOW Level Output Current低电平输出电流- - 24TA Free Air Operating Temperature工作温度0 - 70Note 1: The “Absolute Maximum Ratings” are those values beyond which the safety of th cannot be guaranteed. The device should not be operated at these limits. The parametri defined in the “Electrical Characteristics” table are not guaranteed at the absolute ratings. The “Recommended Operating Conditions” table will define the conditions fo device operation.Electrical Characteristics 直流电气特性Over recommended operating free air temperature range (unless otherwise noted)Symbol 符号Parameter 参数Conditions 条件最小典型最大单VI Input Clamp Voltage输入钳位电压VCC=最小, II=−18 mA - - −1.5VOH High Level OutputVoltage输出高电平电压VCC = 最小, IOH=最大,VIL = 最大2.73.4 -VOL Low Level OutputVoltage输出低电平电压VCC = 最小, IOL=最大- 0.35 0.5VIH = 最小- - -。

74hc573完整中文资料

74hc573中文资料参数-74hc573引脚图-功能原理-74hC573的作用-应用电路-74hC563-54hC57高性能硅门CMOS器件SL74HC573跟LS/AL573的管脚一样。

器件的输入是和标准CMOS输出兼容的;加上拉电阻,他们能和LS/ALSTTL输出兼容。

当锁存使能端为高时,这些器件的锁存对于数据是透明的(也就是说输出同步)。

当锁存使能变低时,符合建立时间和保持时间的数据会被锁存。

×输出能直接接到CMOS,NMOS和TTL接口上×操作电压范围:~×低输入电流:×CMOS器件的高噪声抵抗特性·三态总线驱动输出·置数全并行存取·缓冲控制输入·使能输入有改善抗扰度的滞后作用原理说明:M54HC563/74HC563/M54HC573/74HC573的八个锁存器都是透明的D 型锁存器,当使能(G)为高时,Q 输出将随数据(D)输入而变。

当使能为低时,输出将锁存在已建立的数据电平上。

输出控制不影响锁存器的内部工作,即老数据可以保持,甚至当输出被关闭时,新的数据也可以置入。

这种电路可以驱动大电容或低阻抗负载,可以直接与系统总线接口并驱动总线,而不需要外接口。

特别适用于缓冲寄存器,I/O 通道,双向总线驱动器和工作寄存器。

HC563引脚功能表:HC573引脚功能表:图1 HC573引脚图图2 HC573 国际电工委员会逻辑符号图3 HC563引脚图图4 HC563 国际电工委员会逻辑符号图5 HC563 逻辑图图6 HC573 逻辑图图7 输入输出等效电路真值表:ABSOLUTE MAXIMUM RATINGS绝对最大额定值:Top Operating Temperature: M54HC Series M74HC Series 操作温度:M54HC 系列M74HC系列-55 to +125 -40 to +85℃tr,tf Input Rise and Fall Time输入上升和下降时间VCC = 2V0 to 1000ns VCC =0 to 500VCC = 6V0 to 400VOHHigh Level Output Voltage输出高电平电压 VI = VIH or VILIO=-20μ 4.54.44 Level Output Voltage输出低电平电压VI = VIH or VILIO=20 μLeakage Current输入漏电流=VCC or GND--±±1±1μAIOZState Output Off State Current关断状态3态输出电流=VIH or VIL VO =VCC or GND--±±±10μAICCQuiescent Supply Current静态电源电流=VCC or GND--4-40-80μA应用电路图:点击图片查看大图图8。

74HC573_74HCT573

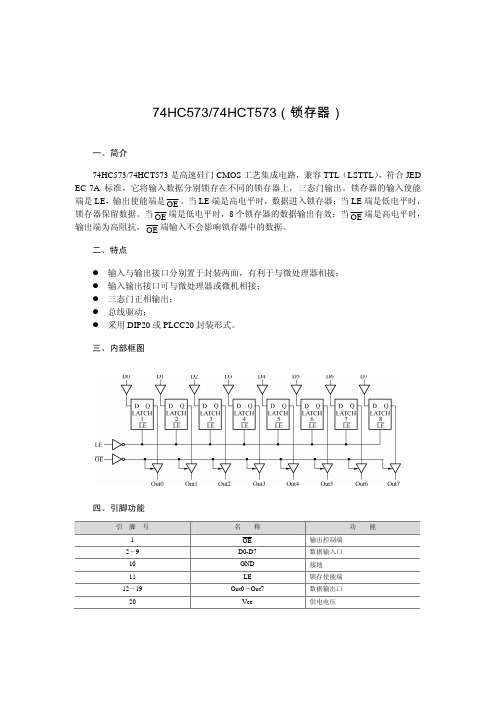

74HC573/74HCT573(锁存器)

一、简介

74HC573/74HCT573是高速硅门CMOS工艺集成电路,兼容TTL(LSTTL),符合JED EC-7A标准,它将输入数据分别锁存在不同的锁存器上,三态门输出。

锁存器的输入使能端是LE,输出使能端是OE。

当LE端是高电平时,数据进入锁存器;当LE端是低电平时,锁存器保留数据。

当OE端是低电平时,8个锁存器的数据输出有效;当OE端是高电平时,输出端为高阻抗,OE端输入不会影响锁存器中的数据。

二、特点

z输入与输出接口分别置于封装两面,有利于与微处理器相接;

z输入输出接口可与微处理器或微机相接;

z三态门正相输出;

z总线驱动;

z采用DIP20或PLCC20封装形式。

三、内部框图

四、引脚功能。

74H573规格书

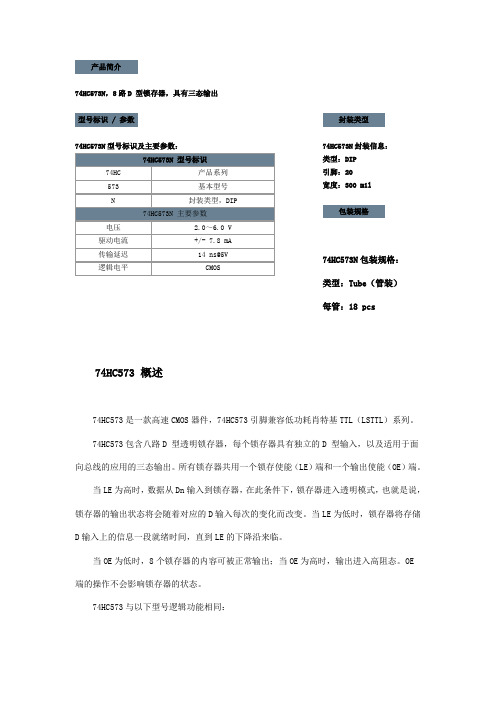

74HC573N,8路D 型锁存器,具有三态输出74HC573N型号标识及主要参数:74HC573N封装信息:类型:DIP引脚:20宽度:300 mil74HC573N包装规格:类型:Tube(管装)每管:18 pcs74HC573 概述74HC573是一款高速CMOS器件,74HC573引脚兼容低功耗肖特基TTL(LSTTL)系列。

74HC573包含八路D 型透明锁存器,每个锁存器具有独立的D 型输入,以及适用于面向总线的应用的三态输出。

所有锁存器共用一个锁存使能(LE)端和一个输出使能(OE)端。

当LE为高时,数据从Dn输入到锁存器,在此条件下,锁存器进入透明模式,也就是说,锁存器的输出状态将会随着对应的D输入每次的变化而改变。

当LE为低时,锁存器将存储D输入上的信息一段就绪时间,直到LE的下降沿来临。

当OE为低时,8个锁存器的内容可被正常输出;当OE为高时,输出进入高阻态。

OE端的操作不会影响锁存器的状态。

74HC573与以下型号逻辑功能相同:74HC563,但输出为反相74HC373,但引脚布局不同74HC573 特性∙输入输出分布在芯片封装的两侧,为微处理器提供简便的接口∙用于微控制器和微型计算机的输入输出口∙三态正相输出,用于面向总线的应用∙共用三态输出使能端∙逻辑功能与74HC563、74HC373相同∙遵循JEDEC标准no.7A∙ESD保护o HBM EIA/JESD22-A114-C超过2000 Vo MM EIA/JESD22-A115-A超过200 V∙温度范围o-40~+85 ℃o-40~+125。

HD74LVC573AT资料

HD74LVC573AOctal D-type Transparent Latches with 3-state OutputsADE-205-116B(Z)3rd EditionDecember 1996 DescriptionThe HD74LVC573A has eight D type latches with three state outputs in a 20 pin package. When the latch enable input is high, the Q outputs will follow the D inputs. When the latch enable goes low, data at the D inputs will be retained at the outputs until latch enable returns high again. When a high logic level is applied to the output control input, all outputs go to a high impedance state, regardless of what signals are present at the other inputs and the state of the storage elements. Low voltage and high speed operation is suitable at the battery drive product (note type personal computer) and low power consumption extends the life of a battery for long time operation.Features•V CC = 2.0 V to 5.5 V•All inputs V IH (Max.) = 5.5 V (@V CC = 0 V to 5.5 V)•All outputs V OUT (Max.) = 5.5 V (@V CC = 0 V or output off state)•Typical V OL ground bounce < 0.8 V (@V CC = 3.3 V, Ta = 25°C)•Typical V OH undershoot > 2.0 V (@V CC = 3.3 V, Ta = 25°C)•High output current ±24 mA (@V CC = 3.0 V to 5.5 V)HD74LVC573ARev.3, Dec. 1996, page 2 of 11Function TableInputsOC LE D Output Q L H H H L H L L L L X Q 0H XXZH :High level L :Low level X :ImmaterialZ :High impedanceQ 0 :Level of Q before the indicated steady input conditions were established.Pin ArrangementHD74LVC573ARev.3, Dec. 1996, page 3 of 11Absolute Maximum RatingsItemSymbol Ratings Unit ConditionsSupply voltage V CC –0.5 to 6.0V Input diode current I IK –50mA V I = –0.5 V Input voltage V I –0.5 to 6.0V Output diode current I OK –50mA V O = –0.5 V 50mA V O = V CC +0.5 V Output voltage V O –0.5 to V CC +0.5V Output "H" or "L"–0.5 to 6.0V Output "Z" or V CC :OFF Output current I O±50mA V CC , GND current / pin I CC or I GND 100mA Storage temperatureTstg–65 to +150°CNote:The absolute maximum ratings are values which must not individually be exceeded, and furthermore,no two of which may be realized at the same time.Recommended Operating ConditionsItemSymbol Ratings Unit Conditions Supply voltage V CC 1.5 to 5.5V Data hold 2.0 to 5.5V At operation Input / output voltageV I 0 to 5.5V OC , LE, D V O0 to V CC V Output "H" or "L"0 to 5.5V Output "Z" or V CC :OFFOperating temperature Ta –40 to 85°C Output currentI OH –12mA V CC = 2.7 V –24*2mA V CC = 3.0 V to 5.5 V I OL12mA V CC = 2.7 V 24*2mA V CC = 3.0 V to 5.5 V Input rise / fall time *1t r , t f10ns/VNotes: 1.This item guarantees maximum limit when one input switches.Waveform : Refer to test circuit of switching characteristics.2.duty cycle ≤ 50%HD74LVC573ARev.3, Dec. 1996, page 4 of 11Electrical CharacteristicsTa = –40 to 85°CItem Symbol V CC (V)Min Max Unit Test Conditions Input voltageV IH 2.7 to 3.6 2.0—V 4.5 to 5.5V CC ×0.7—V V IL2.7 to3.6—0.8V 4.5 to 5.5—V CC ×0.3V Output voltageV OH2.7 to 5.5V CC –0.2—V I OH = –100 µA 2.7 2.2—V I OH = –12 mA3.0 2.4—V 3.0 2.2—V I OH = –24 mA4.53.8—V V OL2.7 to 5.5—0.2V I OL = 100 µA 2.7—0.4V I OL = 12 mA3.0—0.55V I OL = 24 mA4.5—0.55V Input currentI IN 0 to 5.5—±5.0µA V IN = 5.5 V or GND Off state output current I OZ 2.7 to 5.5—±5.0µA V IN = V CC , GNDV OUT = 5.5 V or GND Output leak currentI OFF0—20µA V IN / V OUT = 5.5 V Quiescent supply current I CC2.7 to3.6—±10µA V IN / V OUT = 3.6 to 5.5 V 2.7 to 5.5—10µA V IN = V CC or GND∆I CC3.0 to 3.6—500µAV IN = one input at(V CC –0.6)V,other inputs at V CC or GNDHD74LVC573ARev.3, Dec. 1996, page 5 of 11Switching CharacteristicsTa = –40 to 85°CItemSymbol V CC (V)Min Typ Max Unit From (Input)To (Output)Propagation delay timet PLH 2.7——9.0ns DQt PHL 3.3±0.3 1.5—8.0ns 5.0±0.5—— 6.5ns t PLH 2.7——9.5ns LEQt PHL3.3±0.3 1.5—8.5ns 5.0±0.5——7.0ns Output enable timet ZH 2.7——9.5ns OCQt ZL3.3±0.3 1.5—8.5ns 5.0±0.5——7.0ns Output disable timet HZ 2.7——8.5ns OCQt LZ3.3±0.3 1.5—7.5ns 5.0±0.5—— 6.5ns Setup timet su2.7 2.0——ns3.3±0.3 2.0——ns 5.0±0.52.0——ns Hold timet h2.7 1.5——ns3.3±0.3 1.5——ns 5.0±0.51.5——ns Pulse widtht w2.73.3——ns 3.3±0.3 3.3——ns 5.0±0.53.3——ns Between output pins skew *1t OSLH 2.7———ns t OSHL3.3±0.3—— 1.0ns 5.0±0.5—— 1.0ns Input capacitance C IN 2.7— 3.0—pF Output capacitance C O2.7—15.0—pFNote:1.This parameter is characterized but not tested.tos LH = | t PLHm - t PLHn |, tos HL = | t PHLm - t PHLn |HD74LVC573ATest CircuitWaveforms – 1Rev.3, Dec. 1996, page 6 of 11HD74LVC573A Waveforms – 2Waveforms – 3Rev.3, Dec. 1996, page 7 of 11HD74LVC573A Waveforms – 4Rev.3, Dec. 1996, page 8 of 11HD74LVC573A Package DimensionsRev.3, Dec. 1996, page 9 of 11HD74LVC573ARev.3, Dec. 1996, page 10 of 11HD74LVC573ARev.3, Dec. 1996, page 11 of 11Disclaimer1.Hitachi neither warrants nor grants licenses of any rights of Hitachi’s or any third party’s patent,copyright, trademark, or other intellectual property rights for information contained in this document.Hitachi bears no responsibility for problems that may arise with third party’s rights, including intellectual property rights, in connection with use of the information contained in this document.2.Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.3.Hitachi makes every attempt to ensure that its products are of high quality and reliability. However,contact Hitachi’s sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation,traffic, safety equipment or medical equipment for life support.4.Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installationconditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.5.This product is not designed to be radiation resistant.6.No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.7.Contact Hitachi’s sales office for any questions regarding this document or Hitachi semiconductor products.Sales OfficesHitachi, Ltd.Semiconductor & Integrated Circuits.Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Tel: Tokyo (03) 3270-2111 Fax: (03) 3270-5109Copyright Hitachi, Ltd., 2000. All rights reserved. Printed in Japan.Hitachi Asia Ltd. Hitachi Tower16 Collyer Quay #20-00, Singapore 049318Tel : <65>-538-6533/538-8577 Fax : <65>-538-6933/538-3877URL : .sg URLNorthAmerica : /Europe : /hel/ecg Asia : Japan : http://www.hitachi.co.jp/Sicd/indx.htmHitachi Asia Ltd.(Taipei Branch Office)4/F, No. 167, Tun Hwa North Road, Hung-Kuo Building, Taipei (105), Taiwan Tel : <886>-(2)-2718-3666 Fax : <886>-(2)-2718-8180 Telex : 23222 HAS-TPURL : Hitachi Asia (Hong Kong) Ltd.Group III (Electronic Components) 7/F., North Tower, World Finance Centre,Harbour City, Canton Road Tsim Sha Tsui, Kowloon, Hong KongTel : <852>-(2)-735-9218 Fax : <852>-(2)-730-0281URL : Hitachi Europe Ltd.Electronic Components Group.Whitebrook ParkLower Cookham Road MaidenheadBerkshire SL6 8YA, United Kingdom Tel: <44> (1628) 585000Fax: <44> (1628) 585160Hitachi Europe GmbHElectronic Components Group Dornacher Stra ße 3D-85622 Feldkirchen, Munich GermanyTel: <49> (89) 9 9180-0Fax: <49> (89) 9 29 30 00Hitachi Semiconductor (America) Inc.179 East Tasman Drive,San Jose,CA 95134 Tel: <1> (408) 433-1990Fax: <1>(408) 433-0223For further information write to:Colophon 2.0。

74LVC1G57GW中文资料

74LVC1G57Low-power configurable multiple function gateRev. 01 — 6 September 2004Product data sheet1.General descriptionThe 74LVC1G57 is a high-performance, low-power, low-voltage, Si-gate CMOS device,superior to most advanced CMOS compatible TTL families.Inputs can be driven from either 3.3 V or5V devices. This feature allows the use of thisdevice in a mixed 3.3 V and5V environment.This device is fully specified for partial power-down applications using I off.The I off circuitrydisables the output,preventing the damaging backflow current through the device when itis powered down.The 74LVC1G57 provides configurable multiple functions. The output state is determinedby eight patterns of3-bit input.The user can choose the logic functions AND,OR,NAND,NOR, XNOR, inverter and buffer. All inputs can be connected to V CC or GND.All inputs (A, B and C) have Schmitt-trigger action. They are capable of transformingslowly changing input signals into sharply defined, jitter-free output signals.2.Featuress Wide supply voltage range from 1.65 V to5.5Vs5V tolerant input/output for interfacing with 5V logics High noise immunitys Complies with JEDEC standard:x JESD8-7 (1.65V to1.95V)x JESD8-5 (2.3 V to2.7V)x JESD8B/JESD36 (2.7 V to3.6V).s±24mA output drive (V CC=3.0V)s ESD protection:x HBM EIA/JESD22-A114-B exceeds 2000Vx MM EIA/JESD22-A115-A exceeds 200V.s CMOS low power consumptions Latch-up performance exceeds 250mAs Direct interface with TTL levelss Inputs accept voltages up to 5Vs Multiple package optionss Specified from−40°C to+85°C and−40°C to+125°C.3.Quick reference data[1]C PD is used to determine the dynamic power dissipation (P D in µW).P D =C PD ×V CC 2×f i ×N +Σ(C L ×V CC 2×f o ) where:f i =input frequency in MHz;f o =output frequency in MHz;C L =output load capacitance in pF;V CC =supply voltage in V;N =total load switching outputs;Σ(C L ×V CC 2×f o )=sum of the outputs.[2]The condition is V I =GND to V CC .4.Ordering information5.MarkingTable 1:Quick reference dataGND =0V; T amb =25°C; t r =t f ≤2.5ns.SymbolParameterConditionsMin Typ Max Unit t PHL , t PLH propagation delayinput A, B and C to output YC L =30pF; R L =1k Ω;V CC =1.8V- 6.0-ns C L =30pF; R L =500Ω;V CC =2.5V- 3.5-ns C L =50pF; R L =500Ω;V CC =2.7V- 4.2-ns C L =50pF; R L =500Ω;V CC =3.3V- 3.8-ns C L =50pF; R L =500Ω;V CC =5.0V;- 3.0-ns C I input capacitance -2.5-pF C PDpower dissipationcapacitance per bufferV CC =3.3V[1][2]-22-pFTable 2:Ordering informationType numberPackageTemperature rangeName DescriptionVersion 74LVC1G57GW −40°C to +125°C -plastic surface mounted package; 6 leads SOT36374LVC1G57GV −40°C to +125°C -plastic surface mounted package; 6 leads SOT45774LVC1G57GM−40°C to +125°CXSON6plastic extremely thin small outline package;no leads; 6 terminals; body 1×1.45×0.5mmSOT886Table 3:MarkingType number Marking code 74LVC1G57GW YC 74LVC1G57GV V5774LVC1G57GMYC6.Functional diagram7.Pinning information7.1Pinning7.2Pin descriptionFig 1.Logic symbol.YCBA6134001aab583Fig 2.Pin configuration SOT363 andSOT457.Fig 3.Pin configuration SOT886.57B CGNDAY001aab5911236V CC 5457GND001aab592BAV CCCYTransparent top view231546Table 4:Pin descriptionSymbol Pin Description B 1data input B GND 2ground (0V)A 3data input A Y 4data output Y V CC 5supply voltage C6data input C8.Functional description8.1Function table[1]H =HIGH voltage level;L =LOW voltage level.8.2Logic configurationsTable 5:Function table [1]Input OutputC B A Y L L L H L L H L L H L H L H H L H L L L H L H L H H L H HHHHTable 6:Function selection tableLogic function Figure 2-input ANDsee Figure 42-input AND with both inputs inverted see Figure 72-input NAND with inverted input see Figure 5 and 62-input OR with inverted input see Figure 5 and 62-input NORsee Figure 72-input NOR with both inputs inverted see Figure 42-input XNOR see Figure 8Inverter see Figure 9Buffersee Figure 10Fig 4.2-input AND gate or 2-input NORgate with both inputs inverted.Fig 5.2-input NAND gate with input Binverted or 2-input OR gate with inverted C input.001aab584B B6YC15243YYC B CV CC001aab585B B6YC15243Y YCB CV CC9.Limiting valuesFig 6.2-input NAND gate with input Cinverted or 2-input OR gate with inverted A input.Fig 7.2-input NOR gate or 2-input ANDgate with both inputs inverted.Fig 8.2-input XNOR gate.Fig 9.Inverter.Fig 10.Buffer.001aab586A A6YC15243Y YCA CV CC001aab587A6C15243Y V CCA YCYA C001aab588B6C15243Y V CCYB C001aab589AA6Y15243YV CC001aab590BB6Y15243YV CCTable 7:Limiting valuesIn accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V).Symbol Parameter Conditions Min Max Unit V CC supply voltage −0.5+6.5V I IK input diode current V I <0V-−50mA V I input voltage [1]−0.5+6.5V I OK output diode current V O >V CC or V O <0V -±50mA V O output voltage active mode [1][2]−0.5+6.5V Power-down mode [1][2]−0.5+6.5V I Ooutput source or sink currentV O =0V to V CC-±50mA[1]The input and output voltage ratings may be exceeded if the input and output current ratings are observed.[2]When V CC =0V (Power-down mode), the output voltage can be 5.5V in normal operation.10.Recommended operating conditions11.Static characteristicsI CC , I GND V CC or GND current -±100mA T stg storage temperature −65+150°C P totpower dissipationT amb =−40°C to +125°C-300mWTable 7:Limiting values …continuedIn accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to GND (ground = 0 V).Symbol Parameter Conditions Min Max Unit Table 8:Recommended operating conditions Symbol Parameter ConditionsMin Typ Max Unit V CC supply voltage 1.65- 5.5V V I input voltage 0- 5.5V V Ooutput voltageactive mode0-V CC V V CC =0V; Power-down mode0- 5.5V T amboperating ambient temperature−40-+125°CTable 9:Static characteristicsAt recommended operating conditions; voltages are referenced to GND (ground = 0 V).Symbol ParameterConditions MinTypMaxUnitT amb =−40°C to +85°C [1]V OLLOW-level output voltageV I =V CC or GNDI O =100µA; V CC = 1.65 V to 5.5 V --0.1V I O =4mA; V CC = 1.65 V --0.45V I O =8mA; V CC = 2.3 V --0.3V I O =12mA; V CC = 2.7 V --0.4V I O =24mA; V CC = 3.0 V --0.55V I O =32mA; V CC = 4.5 V--0.55VV OHHIGH-level output voltage V I =V CC or GNDI O =−100µA; V CC = 1.65 V to 5.5 V V CC −0.1--V I O =−4mA; V CC = 1.65 V 1.2--V I O =−8mA; V CC = 2.3 V 1.9--V I O =−12mA; V CC = 2.7 V 2.2--V I O =−24mA; V CC = 3.0 V 2.3--V I O =−32mA; V CC = 4.5 V3.8--V I LIinput leakage currentV I =5.5V or GND; V CC = 3.6 V-±0.1±5µA[1]Typical values are measured at maximum V CC and T amb =25°C.I off power OFF leakage currentV I or V O =5.5V; V CC = 0 V -±0.1±10µA I CC quiescent supply current V I =V CC or GND; I O =0A;V CC =5.5V-0.110µA ∆I CC additional quiescent supply current per pin V I =V CC −0.6V; I O =0A;V CC =2.3V to 5.5 V-5500µA C I input capacitance -2.5-pFT amb =−40°C to +125°CV OLLOW-level output voltageV I =V CC or GNDI O =100µA; V CC = 1.65 V to 5.5 V --0.1V I O =4mA; V CC = 1.65 V --0.7V I O =8mA; V CC = 2.3 V --0.45V I O =12mA; V CC = 2.7 V --0.6V I O =24mA; V CC = 3.0 V --0.8V I O =32mA; V CC = 4.5 V--0.8V V OHHIGH-level output voltage V I =V CC or GNDI O =−100µA; V CC = 1.65 V to 5.5 V V CC −0.1--V I O =−4mA; V CC = 1.65 V 0.95--V I O =−8mA; V CC = 2.3 V 1.7--V I O =−12mA; V CC = 2.7 V 1.9--V I O =−24mA; V CC = 3.0 V 2.0--V I O =−32mA; V CC = 4.5 V3.4--V I LI input leakage current V I =5.5V or GND; V CC = 3.6 V --±100µA I off power OFF leakage currentV I or V O =5.5V; V CC = 0 V --±200µA I CC quiescent supply current V I =V CC or GND; I O =0A;V CC =5.5V--200µA ∆I CCadditional quiescent supply current per pinV I =V CC −0.6V; I O =0A;V CC =2.3V to 5.5 V--5000µATable 9:Static characteristics …continuedAt recommended operating conditions; voltages are referenced to GND (ground = 0 V).Symbol Parameter ConditionsMin Typ Max Unit12.Dynamic characteristics[1]Typical values are measured at nominal V CC and T amb =25°C.[2]C PD is used to determine the dynamic power dissipation (P D in µW).P D =C PD ×V CC 2×f i ×N +Σ(C L ×V CC 2×f o ) where:f i =input frequency in MHz;f o =output frequency in MHz;C L =output load capacitance in pF;V CC =supply voltage in V;N =total load switching outputs;Σ(C L ×V CC 2×f o )=sum of the outputs.[3]The condition is V I =GND to V CC .Table 10:Dynamic characteristics GND = 0 V .Symbol ParameterConditionsMin Typ Max UnitT amb =−40°C to +85°C [1]t PHL , t PLHpropagation delay A, B, C to Ysee Figure 11and 12V CC = 1.65 V to 1.95 V 1.0 6.014.4ns V CC = 2.3 V to 2.7 V 0.5 3.58.3ns V CC = 2.7 V 0.5 4.28.5ns V CC = 3.0 V to 3.6 V 0.5 3.8 6.3ns V CC = 4.5 V to 5.5 V0.5 3.0 5.1ns C PDpower dissipation capacitance per bufferV CC =3.3V[2][3]-22-pFT amb =−40°C to +125°C t PHL , t PLHpropagation delay A, B, C to Ysee Figure 11and 12V CC = 1.65 V to 1.95 V 1.0-18ns V CC = 2.3 V to 2.7 V 0.5-10.4ns V CC = 2.7 V 0.5-10.6ns V CC = 3.0 V to 3.6 V 0.5-7.9ns V CC = 4.5V to 5.5 V0.5-6.4ns13.WaveformsMeasurement points are given in Table 11.V OL and V OH are typical output voltage drop that occur with the output load.Fig 11.Input A, B and C to output Y propagation delay times.Table 11:Measurement pointsSupply voltageInput Output V CCV M V I V M 1.65V to 1.95V 0.5×V CC V CC 0.5×V CC 2.3V to 2.7V 0.5×V CC V CC 0.5×V CC 2.7V 1.5V 2.7V 1.5V 3.0V to 3.6V 1.5V 2.7V 1.5V 4.5V to 5.5V0.5×V CCV CC0.5×V CCY outputA, B, C inputY outputGNDV IV OHV OHV OLV OLV MV MV Mt PLHt PLHt PHLt PHL001aab59314.Transfer characteristicsMeasurement points are given in Table 12.Definitions test circuit:R T = Termination resistance should be equal to output impedance Z o of the pulse generator.C L = Load capacitance including jig and probe capacitance.R L = Load resistance.V EXT =Test voltage for switching times.Fig 12.Load circuitry for switching times.Table 12:Measurement pointsSupply voltageInput Load V EXTV CCV I t r =t f C L R L t PLH , t PHL t PZH , t PHZ t PZL , t PLZ 1.65V to 1.95V V CC ≤2.0ns 30pF 1k Ωopen GND 2×V CC 2.3to 2.7V V CC ≤2.0ns 30pF 500Ωopen GND 2×V CC 2.7V 2.7V ≤2.5ns 50pF 500Ωopen GND 6V 3.0V to 3.6V 2.7V ≤2.5ns 50pF 500Ωopen GND 6V 4.5V to 5.5VV CC≤2.5ns50pF500ΩopenGND2×V CCV EXTV CCV IV Omna616D.U.T.C LR TR LR LPULSE GENERATORTable 13:Transfer characteristicsAt recommended operating conditions; voltages are referenced to GND (ground = 0 V).Symbol ParameterConditionsMinTypMaxUnitT amb =−40°C to +85°C [1]V T+positive-going threshold voltagesee Figure 13,14,15 and 16V CC = 1.8 V 0.70 1.02 1.20V V CC = 2.3 V 1.11 1.42 1.60V V CC = 3.0 V 1.50 1.79 2.00V V CC = 4.5 V 2.16 2.52 2.74V V CC = 5.5 V2.612.993.33VV T −negative-going threshold voltagesee Figure 13,14,15 and 16V CC = 1.8 V 0.300.530.72V V CC = 2.3 V 0.580.77 1.00V V CC = 3.0 V 0.80 1.04 1.30V V CC = 4.5 V 1.21 1.55 1.90V V CC = 5.5 V1.451.862.29V[1]Typical values are measured at T amb =25°C.15.Waveforms transfer characteristicsV Hhysteresis voltage (V T+−V T −)see Figure 13,14,15 and 16V CC = 1.8 V 0.300.480.62V V CC = 2.3 V 0.400.640.80V V CC = 3.0 V 0.500.75 1.00V V CC = 4.5 V 0.710.97 1.20V V CC = 5.5 V0.711.131.40VT amb =−40°C to +125°C V T+positive-going threshold voltagesee Figure 13,14,15 and 16V CC = 1.8 V 0.67- 1.20V V CC = 2.3 V 1.08- 1.60V V CC = 3.0 V 1.47- 2.00V V CC = 4.5 V 2.13- 2.74V V CC = 5.5 V2.58-3.33V V T −negative-going threshold voltagesee Figure 13,14,15 and 16V CC = 1.8 V 0.30-0.75V V CC = 2.3 V 0.58- 1.03V V CC = 3.0 V 0.80- 1.33V V CC = 4.5 V 1.21- 1.93V V CC = 5.5 V1.45-2.32V V Hhysteresis voltage (V T+−V T −)see Figure 13,14,15 and 16V CC = 1.8 V 0.23-0.62V V CC = 2.3 V 0.34-0.80V V CC = 3.0 V 0.44- 1.00V V CC = 4.5 V 0.65- 1.20V V CC = 5.5 V0.65-1.40VTable 13:Transfer characteristics …continuedAt recommended operating conditions; voltages are referenced to GND (ground = 0 V).Symbol ParameterConditionsMin Typ Max Unit V T+ and V T − limits are at 70% and 20%.Fig 13.Transfer characteristic.Fig 14.Definition of V T+, V T − and V H .mna207V O V IV H V T +V T −mna208V OV IV HV T +V T −V T+ and V T − limits are at 70% and 20%.Fig 15.Transfer characteristic.Fig 16.Definition of V T+, V T − and V H .Fig 17.Typical 74LVC1G57 transfer characteristic; V CC =3.0V.mnb154V OV HV IV T −V T +mnb155V OV IV HV T +V T −001aab594V I (V)0321841216I CC (mA)16.Package outlineFig 18.Package outline SOT363.REFERENCESOUTLINE VERSION EUROPEAN PROJECTIONISSUE DATE IECJEDECEIAJ SOT363SC-88w BM b pD e 1epin 1indexAA 1L pQdetail XH EE v M AA B y01 2 mmscalecX132456Plastic surface mounted package; 6 leadsSOT363UNIT A 1max b p c D E e 1H E L p Q y w v mm0.10.300.202.21.80.250.101.351.150.65e 1.32.22.00.20.10.2DIMENSIONS (mm are the original dimensions)0.450.150.250.15A 1.10.897-02-28Fig 19.Package outline SOT457.REFERENCESOUTLINE VERSION EUROPEAN PROJECTIONISSUE DATE IECJEDECEIAJ SOT457SC-74w BM b pD epin 1indexAA 1L pQdetail XH EE v M AA B y01 2 mmscalecX132456Plastic surface mounted package; 6 leads SOT457UNIT A 1b p c D E H E L p Q y w v mm0.10.0130.400.253.12.70.260.101.71.3e 0.953.02.50.20.10.2DIMENSIONS (mm are the original dimensions)0.60.20.330.23A 1.10.997-02-2801-05-04Fig 20.Package outline SOT886 (XSON6).terminal 1index areaREFERENCESOUTLINE VERSION EUROPEAN PROJECTIONISSUE DATE IECJEDEC JEITASOT886MO-252SOT88604-07-1504-07-22DIMENSIONS (mm are the original dimensions)XSON6: plastic extremely thin small outline package; no leads; 6 terminals; body 1 x 1.45 x 0.5 mm DEe 1eA 1bLL 1e 11 2 mmscaleNotes1. Including plating thickness.2. Can be visible in some manufacturing processes.UNIT mm0.250.171.51.40.350.27A 1max b E 1.050.95D e e 1L 0.400.32L 10.50.6A (1)max 0.50.041625346×(2)4×(2)A17.Revision historyTable 14:Revision historyDocument ID Release date Data sheet status Change notice Doc. number Supersedes 74LVC1G57_120040906Product data sheet-9397 750 13722-18.Data sheet status[1]Please consult the most recently issued data sheet before initiating or completing a design.[2]The product status of the device(s) described in this data sheet may have changed since this data sheet was published. The latest information is available on the Internet at URL .[3]For data sheets describing multiple type numbers, the highest-level product status determines the data sheet status.19.DefinitionsShort-form specification —The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 60134). Stress above one or more of the limiting values may cause permanent damage to the device.These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.Application information — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.20.DisclaimersLife support —These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.Right to make changes —Philips Semiconductors reserves the right to make changes in the products - including circuits, standard cells, and/or software - described or contained herein in order to improve design and/or performance. When the product is in full production (status ‘Production’),relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). Philips Semiconductors assumes noresponsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to theseproducts,and makes no representations or warranties that these products are free from patent,copyright,or mask work right infringement,unless otherwise specified.21.Contact informationFor additional information, please visit: For sales office addresses, send an email to: sales.addresses@Level Data sheet status [1]Product status [2][3]DefinitionI Objective data Development This data sheet contains data from the objective specification for product development. Philips Semiconductors reserves the right to change the specification in any manner without notice.IIPreliminary dataQualificationThis data sheet contains data from the preliminary specification.Supplementary data will be published at a later date.Philips Semiconductors reserves the right to change the specification without notice,in order to improve the design and supply the best possible product.III Product data ProductionThis data sheet contains data from the product specification. Philips Semiconductors reserves the right to make changes at any time in order to improve the design,manufacturing and supply.Relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN).22.Contents1General description. . . . . . . . . . . . . . . . . . . . . . 12Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13Quick reference data. . . . . . . . . . . . . . . . . . . . . 24Ordering information. . . . . . . . . . . . . . . . . . . . . 25Marking. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26Functional diagram . . . . . . . . . . . . . . . . . . . . . . 37Pinning information. . . . . . . . . . . . . . . . . . . . . . 37.1Pinning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37.2Pin description . . . . . . . . . . . . . . . . . . . . . . . . . 38Functional description . . . . . . . . . . . . . . . . . . . 48.1Function table. . . . . . . . . . . . . . . . . . . . . . . . . . 48.2Logic configurations . . . . . . . . . . . . . . . . . . . . . 49Limiting values. . . . . . . . . . . . . . . . . . . . . . . . . . 510Recommended operating conditions. . . . . . . . 611Static characteristics. . . . . . . . . . . . . . . . . . . . . 612Dynamic characteristics . . . . . . . . . . . . . . . . . . 813Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 914Transfer characteristics. . . . . . . . . . . . . . . . . . 1015Waveforms transfer characteristics. . . . . . . . 1116Package outline . . . . . . . . . . . . . . . . . . . . . . . . 1317Revision history. . . . . . . . . . . . . . . . . . . . . . . . 1618Data sheet status. . . . . . . . . . . . . . . . . . . . . . . 1719Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1720Disclaimers. . . . . . . . . . . . . . . . . . . . . . . . . . . . 1721Contact information . . . . . . . . . . . . . . . . . . . . 17© Koninklijke Philips Electronics N.V.2004All rights are reserved.Reproduction in whole or in part is prohibited without the priorwritten consent of the copyright owner.The information presented in this document doesnot form part of any quotation or contract,is believed to be accurate and reliable and maybe changed without notice.No liability will be accepted by the publisher for anyconsequence of its use.Publication thereof does not convey nor imply any license underpatent- or other industrial or intellectual property rights.Date of release: 6 September 2004Document number: 9397 750 13722。

LVC573A中文资料

元器件交易网SO20:plastic small outline package; 20 leads; body width 7.5 mm SOT163-1SSOP20:plastic shrink small outline package; 20 leads; body width 5.3 mm SOT339-1TSSOP20:plastic thin shrink small outline package; 20 leads; body width 4.4 mm SOT360-1NOTES 1998 Jul 2911DefinitionsShort-form specification — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.Application information — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.DisclaimersLife support — These products are not designed for use in life support appliances, devices or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.Right to make changes — Philips Semiconductors reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.Philips Semiconductors811 East Arques AvenueP.O. Box 3409Sunnyvale, California 94088–3409Telephone 800-234-7381© Copyright Philips Electronics North America Corporation 1998All rights reserved. Printed in U.S.A.print code Date of release: 08-98。

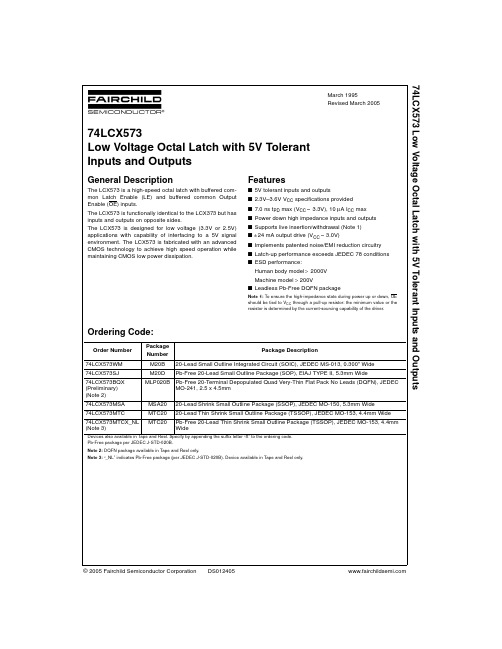

74LCX573WM资料

© 2005 Fairchild Semiconductor Corporation DS012405March 1995Revised March 200574LCX573 Low Voltage Octal Latch with 5V Tolerant Inputs and Outputs74LCX573Low Voltage Octal Latch with 5V Tolerant Inputs and OutputsGeneral DescriptionThe LCX573 is a high-speed octal latch with buffered com-mon Latch Enable (LE) and buffered common Output Enable (OE) inputs.The LCX573 is functionally identical to the LCX373 but has inputs and outputs on opposite sides.The LCX573 is designed for low voltage (3.3V or 2.5V)applications with capability of interfacing to a 5V signal environment. The LCX573 is fabricated with an advanced CMOS technology to achieve high speed operation while maintaining CMOS low power dissipation.Featuress 5V tolerant inputs and outputs s 2.3V–3.6V V CC specifications provided s 7.0 ns t PD max (V CC 3.3V), 10 P A I CC max s Power down high impedance inputs and outputs s Supports live insertion/withdrawal (Note 1)s r 24 mA output drive (V CC 3.0V)s Implements patented noise/EMI reduction circuitry s Latch-up performance exceeds JEDEC 78 conditions s ESD performance:Human body model ! 2000V Machine model ! 200Vs Leadless Pb-Free DQFN packageNote 1: To ensure the high-impedance state during power up or down, OE should be tied to V CC through a pull-up resistor: the minimum value or the resistor is determined by the current-sourcing capability of the driver.Ordering Code:Devices also available in T ape and Reel. Specify by appending the suffix letter “X ” to the ordering code.Pb-Free package per JEDEC J-STD-020B.Note 2: DQFN package available in Tape and Reel only.Note 3: “_NL ” indicates Pb-Free package (per JEDEC J-STD-020B). Device available in Tape and Reel only.Order Number Package Package DescriptionNumber 74LCX573WM M20B 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" Wide 74LCX573SJ M20DPb-Free 20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide74LCX573BQX (Preliminary)(Note 2)MLP020B Pb-Free 20-Terminal Depopulated Quad Very-Thin Flat Pack No Leads (DQFN), JEDECMO-241, 2.5 x 4.5mm 74LCX573MSA MSA2020-Lead Shrink Small Outline Package (SSOP), JEDEC MO-150, 5.3mm Wide 74LCX573MTC MTC2020-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide 74LCX573MTCX_NL (Note 3)MTC20Pb-Free 20-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide 274L C X 573Logic SymbolConnection DiagramsPin Assignments for SOIC, SOP, SSOP , TSSOPPad Assignments for DQFN(Top View)Pin DescriptionsTruth TableH HIGH Voltage L LOW Voltage Z High Impedance X ImmaterialO 0 Previous O 0 before HIGH-to-LOW transition of Latch EnableFunctional DescriptionThe LCX573 contains eight D-type latches with 3-STATE output buffers. When the Latch Enable (LE) input is HIGH,data on the D n inputs enters the latches. In this condition the latches are transparent, i.e., a latch output will change state each time its D input changes. When LE is LOW the latches store the information that was present on the D inputs a setup time preceding the HIGH-to-LOW transition of LE. The 3-STATE buffers are controlled by the Output Enable (OE) input. When OE is LOW, the buffers are enabled. When OE is HIGH the buffers are in the high impedance mode but this does not interfere with entering new data into the latches.Logic DiagramPlease note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.Pin Names DescriptionD 0–D 7Data Inputs LE Latch Enable InputOE 3-STATE Output Enable Input O 0–O 73-STATE Latch OutputsInputsOutputs OE LE D O n L H H H L H L L L L X O 0HXXZ74LCX573Absolute Maximum Ratings (Note 4)Recommended Operating Conditions (Note 6)Note 4: The Absolute Maximum Ratings are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the Absolute Maximum Ratings. The “Recom-mended Operating Conditions ” table will define the conditions for actual device operation.Note 5: I O Absolute Maximum Rating must be observed.Note 6: Unused (inputs or I/O's) must be held HIGH or LOW. They may not float.DC Electrical CharacteristicsSymbol ParameterValueConditionsUnits V CC Supply Voltage 0.5 to 7.0V V I DC Input Voltage 0.5 to 7.0VV O DC Output Voltage 0.5 to 7.0Output in 3-STATEV 0.5 to V CC 0.5Output in HIGH or LOW State (Note 5)I IK DC Input Diode Current 50V I GND mA I OK DC Output Diode Current 50V O GND mA 50V O ! V CCI O DC Output Source/Sink Current r 50mA I CC DC Supply Current per Supply Pin r 100mA I GND DC Ground Current per Ground Pin r 100mAT STGStorage Temperature65 to 150q CSymbol ParameterMin Max Units V CC Supply Voltage Operating 2.0 3.6V Data Retention1.5 3.6V I Input Voltage 0 5.5V V O Output Voltage HIGH or LOW State0V CC V3-STATE5.5I OH /I OLOutput CurrentV CC 3.0V 3.6V r 24mAV CC 2.7V 3.0V r 12V CC 2.3V 2.7Vr 8T AFree-Air Operating Temperature4085q C 't/'VInput Edge Rate, V IN 0.8V 2.0V, V CC 3.0V10ns/VSymbol ParameterConditionsV CC T A 40q C to 85q C Units (V)Min MaxV IH HIGH Level Input Voltage 2.3 2.7 1.7V 2.7 3.6 2.0V IL LOW Level Input Voltage 2.3 2.70.7V2.73.60.8V OHHIGH Level Output VoltageI OH 100 P A 2.3 3.6V CC 0.2VI OH 8 mA 2.3 1.8I OH 12 mA 2.7 2.2I OH 18 mA 3.0 2.4I OH 24 mA3.0 2.2V OLLOW Level Output VoltageI OL 100 P A 2.3 3.60.2V I OL 8 mA 2.30.6I OL 12 mA 2.70.4I OL 16 mA 3.00.4I OL 24 mA3.00.55I I Input Leakage Current 0 d V I d 5.5V 2.3 3.6r 5.0P A I OZ 3-STATE Output Leakage 0 d V O d 5.5V 2.3 3.6r 5.0P A V I V IH or V IL I OFFPower-Off Leakage CurrentV I or V O 5.5V10P A 474L C X 573DC Electrical Characteristics (Continued)Note 7: Outputs disabled or 3-STATE only.AC Electrical CharacteristicsNote 8: Skew is defined as the absolute value of the difference between the actual propagation delay for any two separate outputs of the same device. The specification applies to any outputs switching in the same direction, either HIGH-to-LOW (t OSHL ) or LOW-to-HIGH (t OSLH ).Dynamic Switching CharacteristicsCapacitanceSymbol ParameterConditionsV CC T A 40q C to 85q C Units (V)MinMax I CC Quiescent Supply Current V I V CC or GND2.33.610P A 3.6V d V I , V O d 5.5V (Note 7) 2.3 3.6r 10'I CCIncrease in I CC per InputV IH V CC 0.6V2.33.6500P ASymbolParameterT A 40q C to 85q C, R L 500 :UnitsV CC 3.3V r 0.3VV CC 2.7V V CC 2.5 r 0.2V C L 50pF C L 50pF C L 30pF MinMax Min Max Min Max t PHL Propagation Delay 1.58.0 1.59.0 1.59.6ns t PLH D n to O n1.58.0 1.59.0 1.59.6t PHL Propagation Delay 1.58.5 1.59.5 1.510.5ns t PLH LE to O n1.58.5 1.59.5 1.510.5t PZL Output Enable Time1.58.5 1.59.5 1.510.5ns t PZH 1.58.5 1.59.5 1.510.5t PLZ Output Disable Time 1.5 6.5 1.57.0 1.57.8ns t PHZ 1.5 6.51.57.01.57.8t S Setup Time, D n to LE 2.5 2.5 4.0ns t H Hold Time, D n to LE 1.5 1.5 2.0ns t W LE Pulse Width3.33.34.0ns t OSHL Output to Output Skew (Note 8) 1.0ns t OSLH1.0Symbol ParameterConditionsV CC T A 25q C Units (V)Typical V OLP Quiet Output Dynamic Peak V OL C L 50 pF, V IH 3.3V, V IL 0V 3.30.8V C L 30 pF, V IH 2.5V, V IL 0V 2.50.6V OLVQuiet Output Dynamic Valley V OLC L 50 pF, V IH 3.3V, V IL 0V 3.3 0.8VC L 30 pF, V IH 2.5V, V IL 0V2.50.6Symbol ParameterConditionsTypical Units C IN Input Capacitance V CC Open, V I 0V or V CC 7pF C OUT Output CapacitanceV CC 3.3V, V I 0V or V CC8pF C PDPower Dissipation CapacitanceV CC 3.3V, V I 0V or V CC , f 10 MHz25pF74LCX573AC LOADING and WAVEFORMS Generic for LCX FamilyFIGURE 1. AC Test Circuit (C L includes probe and jig capacitance)Waveform for Inverting and Non-Inverting FunctionsPropagation Delay. Pulse Width and t rec Waveforms3-STATE Output Low Enable andDisable Times for Logic3-STATE Output High Enable andDisable Times for LogicSetup Time, Hold Time and Recovery Time for Logict rise and t fallFIGURE 2. Waveforms(Input Characteristics; f =1MHz, t r = t f = 3ns)Test Switch t PLH , t PHL Opent PZL , t PLZ 6V at V CC 3.3 r 0.3V V CC x 2 at V CC 2.5 r 0.2Vt PZH ,t PHZGNDSymbol V CC3.3V r 0.3V2.7V 2.5V r 0.2V V mi 1.5V 1.5V V CC /2V mo 1.5V 1.5V V CC /2V x V OL 0.3V V OL 0.3V V OL 0.15V V yV OH 0.3VV OH 0.3VV OH 0.15V 674L C X 573Schematic DiagramGeneric for LCX Family74LCX573Tape and Reel SpecificationTape Format for DQFNTAPE DIMENSIONS inches (millimeters)REEL DIMENSIONS inches (millimeters)PackageTape Number Cavity Cover Tape DesignatorSection Cavities Status Status Leader (Start End)125 (typ)Empty Sealed BQXCarrier 3000Filled Sealed Trailer (Hub End)75 (typ)EmptySealedTape SizeA B C D N W1W212 mm13.00.0590.5120.795 2.1650.4880.724(330.0)(1.50)(13.00)(20.20)(55.00)(12.4)(18.4) 874L C X 573Physical Dimensionsinches (millimeters) unless otherwise noted20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300" WidePackage Number M20B 74LCX573Physical Dimensions inches (millimeters) unless otherwise noted (Continued)Pb-Free 20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm WidePackage Number M20D 1074L C X 573Physical Dimensionsinches (millimeters) unless otherwise noted (Continued)Pb-Free 20-Terminal Depopulated Quad Very-Thin Flat Pack No Leads (DQFN), JEDEC MO-241, 2.5 x 4.5mmPackage Number MLP020B 74LCX573Physical Dimensions inches (millimeters) unless otherwise noted (Continued)20-Lead Shrink Small Outline Package (SSOP), JEDEC MO-150, 5.3mm WidePackage Number MSA20 1274L C X 573 L o w V o l t a g e O c t a l L a t c h w i t h 5V T o l e r a n t I n p u t s a n d O u t p u t sPhysical Dimensions inches (millimeters) unless otherwise noted (Continued)20-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm WidePackage Number MTC20Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.LIFE SUPPORT POLICYFAIRCHILD ’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:1.Life support devices or systems are devices or systemswhich, (a) are intended for surgical implant into thebody, or (b) support or sustain life, and (c) whose failureto perform when properly used in accordance withinstructions for use provided in the labeling, can be rea-sonably expected to result in a significant injury to theuser.2. A critical component in any component of a life support device or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system, or to affect its safety or 。

74VHCT573ATTR资料