A 40-Gbps integrated clock and data recovery circuit in a 50-GHz FT silicon bipolar technology

泰克-信号完整性设计以及测试分析1

13

2013/11/6

常用的端接方法--串联源端端接

串联源端端接要求加一个电阻与输出缓冲器串联。要求缓冲器阻抗和电阻值的 和等于传输线的特征阻抗 通常设计输出缓冲器I-V曲线产生一个极低阻抗,以至于从源端看进去的阻抗 的大部分都包含在电阻,因此选择精密电阻可以使总偏差降到很低,因为电阻 包含了大部分的阻抗。这种方法的缺点就是电阻增加了板的成本并且占用有效 的板面积。

数据传输中不同码型会有不同的损耗

30

June 5, 2012

Tektronix Confidential

通过发送端对信号进行预加重来补偿信号的衰减

2-Tap –6dB Pre-emphasis

3.

18

使用TDR的方法可以传输线的阻抗匹配问题

TDR (80E04)

+ + - + + Rcv

Voltage

Sampling Scope display of two TDR waveforms

Time

19

Two TDR sampling channels allow the differential impedance between the DATA+ and DATAserial paths to be measured.

V1.0 Confidential

硬件系统不稳定的根源-误码(Bit Error)

•误码的根源: 1.信号采样的时候建立保持时间不足(水平方向) 2.信号的幅度不够(垂直方向)

时钟(Clock) 时钟采样点

数据(Data)

建立时间Setup time

4

保持时间Hold time

由于各种原因引起的误码

ADSP-21266_07资料

SHARC and the SHARC logo are registered trademarks of Analog Devices, Inc.SHARC®Embedded ProcessorADSP-21266Rev. CInformation furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for anyinfringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: FAX: 781.461.3113 ©2007 Analog Devices, Inc. All rights reserved.SUMMARYHigh performance 32-bit/40-bit floating-point processor optimized for high performance audio processingCode compatibility—at assembly level, uses the same instruction set as other SHARC DSPsProcesses high performance audio while enabling low system costsAudio decoders and postprocessor algorithms support nonvolatile memory that can be configured to contain a combination of PCM 96 kHz, Dolby® Digital, Dolby Digital Surround EX TM, DTS-ES TM Discrete 6.1, DTS-ES Matrix 6.1, DTS® 96/24 5.1, MPEG2 AAC LC, MPEG2 BC 2ch, WMA-PRO V7.1, Dolby Pro Logic II, Dolby Pro Logic 2x, and DTS Neo:6TMVarious multichannel surround-sound decoders are con-tained in ROM. For configurations of decoder algorithms, see Table2 on Page6.Single-instruction multiple-data (SIMD) computational archi-tecture—two 32-bit IEEE floating-point/32-bit fixed-point/ 40-bit extended precision floating-point computational units, each with a multiplier, ALU, shifter, and register file High bandwidth I/O—a parallel port, an SPI port, six serial ports, a digital audio interface (DAI), and JTAGDAI incorporates two precision clock generators (PCGs), an input data port (IDP) that includes a parallel data acquisi-tion port (PDAP), and three programmable timers, all under software control by the signal routing unit (SRU) On-chip memory—2M bits on-chip SRAM and a dedicated 4M bits on-chip mask-programmable ROMThe ADSP-21266 is available with a 150 MHz or a 200 MHz core instruction rate. For complete ordering information, see Ordering Guide on Page44.Figure 1.Functional Block DiagramADSP-21266 KEY FEATURESSerial ports offer left-justified sample-pair and I2S support via 12 programmable and simultaneous receive or trans-mit pins, which support up to 24 transmit or 24 receive I2S channels of audio when all 6 serial ports (SPORTs) are enabled or 6 full duplex TDM streams of up to 128 channels per frameAt 200 MHz (5 ns) core instruction rate, the ADSP-21266 operates at 1200 MFLOPS peak/800 MFLOPS sustained performance whether operating on fixed- or floating-point data; 400 MMACS sustained performance at 200 MHz Super Harvard Architecture—three independent buses for dual data fetch, instruction fetch, and nonintrusive, zero-overhead I/O2M bits on-chip dual-ported SRAM (1M bit block 0, 1M bit block 1) for simultaneous access by core processor and DMA4M bits on-chip dual-ported mask-programmable ROM(2M bits in block 0 and 2M bits in block 1)Dual data address generators (DAGs) with modulo and bit-reverse addressingZero-overhead looping with single-cycle loop setup, providing efficient program sequencingSingle instruction multiple data (SIMD) architecture provides:Two computational processing elementsConcurrent execution—each processing element executes the same instruction, but operates on different data Parallelism in buses and computational units allows single cycle executions (with or without SIMD) of a multiplyoperation; an ALU operation; a dual memory read orwrite; and an instruction fetchTransfers between memory and core at up to four 32-bit floating- or fixed-point words per cycle, sustained2.4 GBps bandwidth at 200 MHz core instruction rate; 900 Mbps is available via DMAAccelerated FFT butterfly computation through a multiply with add and subtract instructionDMA controller supports:22 zero-overhead DMA channels for transfers between theADSP-21266 internal memory and serial ports (12), the input data ports (IDP) (eight), the SPI-compatible port(one), and the parallel port (one)32-bit background DMA transfers at core clock speed, inparallel with full-speed processor executionJTAG background telemetry for enhanced emulation featuresIEEE 1149.1 JTAG standard test access port and on-chip emulationDual voltage: 3.3 V I/O, 1.2 V coreAvailable in 136-ball BGA and 144-lead LQFP packages; avail-able in RoHS compliant packagesDigital audio interface includes six serial ports, two precision clock generators, an input data port, three programmable timers, and a signal routing unit Asynchronous parallel/external port provides:Access to asynchronous external memory16 multiplexed address/data lines that can support 24-bitaddress external address range with 8-bit data or 16-bit address external address range with 16-bit data66M byte/sec transfer rate for 200 MHz core rate50M byte/sec transfer rate for 150 MHz core rate256 word page boundariesExternal memory access in a dedicated DMA channel8- to 32-bit and 16- to 32-bit word packing options Programmable wait state options: 2 to 31 CCLKsSerial ports provide:Six dual data line serial ports that operate at up to50M bits/sec for a 200 MHz core and up to 37.5M bits/sec for a 150 MHz core on each data line—each has a clock, frame sync, and two data lines that can be configured as either a receiver or transmitter pairLeft-justified sample-pair and I2S support, programmable direction for up to 24 simultaneous receive or transmit channels using two I2S-compatible stereo devices perserial portTDM support for telecommunications interfaces including 128 TDM channel support for newer telephony inter-faces such as H.100/H.110Up to 12 TDM stream support, each with 128 channelsper frameCompanding selection on a per channel basis in TDM mode Input data port provides an additional input path to the SHARC core configurable as either eight channels of I2S or serial data or as seven channels plus a single 20-bit wide synchronous parallel data acquisition portSupports receive audio channel data in I2S, left-justifiedsample pair, or right-justified modeSignal routing unit (SRU) provides configurable and flexible connections between all DAI components, six serial ports, two precision clock generators, three timers, an input data port/parallel data acquisition port, 10 interrupts, six flag inputs, six flag outputs, and 20 SRU I/O pins (DAI_Px) Serial peripheral interface (SPI)Master or slave serial boot through SPIFull-duplex operationMaster-slave mode multimaster supportOpen-drain outputsProgrammable baud rates, clock polarities, and phases3 muxed flag/IRQ lines1 muxed flag/timer expired lineROM-based security features:JTAG access to memory permitted with a 64-bit key Protected memory regions that can be assigned to limitaccess under program control to sensitive codePLL has a wide variety of software and hardware multi-plier/divider ratiosRev. C|Page 2 of 44|October 2007ADSP-21266Rev. C |Page 3 of 44|October 2007TABLE OF CONTENTSSummary ............................................................... 1Key Features ........................................................... 2Table of Contents .................................................... 3Revision History ...................................................... 3General Description ................................................. 4ADSP-21266 Family Core Architecture ...................... 4ADSP-21266 Memory and I/O Interface Features ......... 6Target Board JTAG Emulator Connector .................... 9Development Tools ............................................... 9Evaluation Kit ..................................................... 10Designing an Emulator-Compatible DSP Board (Target)10Additional Information ......................................... 10Pin Function Descriptions ........................................ 11Address Data Pins as Flags ..................................... 14Core Instruction Rate to CLKIN Ratio Modes ............. 14Address Data Modes ............................................. 14ADSP-21266 Specifications ....................................... 15Operating Conditions ........................................... 15Electrical Characteristics ........................................ 15Package Information ............................................ 16ESD Caution ...................................................... 16Absolute Maximum Ratings ................................... 16Timing Specifications ........................................... 16Output Drive Currents .......................................... 37Test Conditions ................................................... 37Capacitive Loading ............................................... 37Environmental Conditions ..................................... 38Thermal Characteristics ........................................ 38136-Ball BGA Pin Configurations ............................... 39144-Lead LQFP Pin Configurations ............................. 42Package Dimensions ................................................ 43Surface-Mount Design .......................................... 44Ordering Guide (44)REVISION HISTORY9/07—Rev. B to Rev. CCorrected all outstanding document errata.Added new section Package Information .................. 16Revised Timing Specifications ................................ 16Ordering Guide .. (44)ADSP-21266 GENERAL DESCRIPTIONThe ADSP-21266 SHARC DSP is a member of the SIMDSHARC family of DSPs featuring Analog Devices Super Har-vard Architecture. The ADSP-21266 is source code compatible with the ADSP-2126x, ADSP-21160, and ADSP-21161 DSPs as well as with first generation ADSP-2106x SHARC processors in SISD (single-instruction, single-data) mode. Like other SHARC DSPs, the ADSP-21266 is a 32-bit/40-bit floating-point proces-sor optimized for high performance audio applications with its dual-ported on-chip SRAM, mask-programmable ROM, multi-ple internal buses to eliminate I/O bottlenecks, and an innovative digital audio interface.As shown in the functional block diagram in Figure1 on Page1, the ADSP-21266 uses two computational units to deliver a 5 to 10 times performance increase over previous SHARC proces-sors on a range of DSP algorithms. Fabricated in a state-of-the-art, high speed, CMOS process, the ADSP-21266 DSP achieves an instruction cycle time of 5 ns at 200 MHz or 6.6 ns at150 MHz. With its SIMD computational hardware, the ADSP-21266 can perform 1200 MFLOPS running at 200 MHz, or 900 MFLOPS running at 150 MHz.Table1 shows performance benchmarks for the ADSP-21266. The ADSP-21266 continues SHARC’s industry-leading stan-dards of integration for DSPs, combining a high performance 32-bit DSP core with integrated, on-chip system features. These features include 2M bit dual-ported SRAM memory, 4M bit dual-ported ROM, an I/O processor that supports 22 DMA channels, six serial ports, an SPI interface, external parallel bus,and digital audio interface.The block diagram of the ADSP-21266 in on Page1 illustrates the following architectural features:•Two processing elements, each containing an ALU, multi-plier, shifter, and data register file•Data address generators (DAG1, DAG2)•Program sequencer with instruction cache•PM and DM buses capable of supporting four 32-bit data transfers between memory and the core at every core pro-cessor cycle•Three programmable interval timers with PWM genera-tion, PWM capture/pulse width measurement, andexternal event counter capabilities•On-chip dual-ported SRAM (2M bit)•On-chip dual-ported, mask-programmable ROM(4M bit)•JTAG test access port•8- or 16-bit parallel port that supports interfaces to off-chip memory peripherals•DMA controller•Six full-duplex serial ports•SPI-compatible interface•Digital audio interface that includes two precision clockgenerators (PCG), an input data port (IDP), six serial ports, eight serial interfaces, a 20-bit synchronous parallel input port, 10 interrupts, six flag outputs, six flag inputs, threeprogrammable timers, and a flexible signal routing unit(SRU)Figure2 shows one sample configuration of a SPORT using the precision clock generator to interface with an I2S ADC and an I2S DAC with a much lower jitter clock than the serial port would generate itself. Many other SRU configurations are possible.ADSP-21266 FAMILY CORE ARCHITECTUREThe ADSP-21266 is code compatible at the assembly level with the ADSP-2136x and ADSP-2116x, and with the first generation ADSP-2106x SHARC DSPs. The ADSP-21266 shares architec-tural features with the ADSP-2136x and ADSP-2116x SIMD SHARC family of DSPs, as detailed in the following sections. SIMD Computational EngineThe ADSP-21266 contains two computational processing ele-ments that operate as a single-instruction multiple-data (SIMD) engine. The processing elements are referred to as PEX and PEY and each contains an ALU, multiplier, shifter, and register file. PEX is always active, and PEY may be enabled by setting the PEYEN mode bit in the MODE1 register. When this mode is enabled, the same instruction is executed in both processing ele-ments, but each processing element operates on different data. This architecture is efficient at executing math intensive audio algorithms.Entering SIMD mode also has an effect on the way data is trans-ferred between memory and the processing elements. When in SIMD mode, twice the data bandwidth is required to sustain computational operation in the processing elements. Because of this requirement, entering SIMD mode also doubles the band-width between memory and the processing elements. When using the DAGs to transfer data in SIMD mode, two data values are transferred with each access of memory or the register file.Table 1.ADSP-21266 Benchmarks (at 200 MHz)Benchmark Algorithm Speed(at 200 MHz)1024 Point Complex FFT (Radix 4, with reversal)61.3 μsFIR Filter (per tap)11Assumes two files in multichannel SIMD mode.3.3 nsIIR Filter (per biquad)113.3 ns Matrix Multiply (pipelined)[3×3] × [3×1] [4×4] × [4×1]30 ns 53.3 nsDivide (y/x)20 nsInverse Square Root30 nsRev. C|Page 4 of 44|October 2007ADSP-21266Rev. C |Page 5 of 44|October 2007Independent, Parallel Computation UnitsWithin each processing element is a set of computational units. The computational units consist of an arithmetic/logic unit (ALU), multiplier, and shifter. These units perform all opera-tions in a single cycle. The three units within each processing element are arranged in parallel, maximizing computational throughput. Single multifunction instructions execute parallel ALU and multiplier operations. In SIMD mode, the parallel ALU and multiplier operations occur in both processing ele-ments. These computation units support IEEE 32-bit single precision floating-point, 40-bit extended precision floating-point, and 32-bit fixed-point data formats.Data Register FileA general-purpose data register file is contained in eachprocessing element. The register files transfer data between the computation units and the data buses, and store intermediate results. These 10-port, 32-register (16 primary, 16 secondary) register files, combined with the ADSP-2126x enhanced Har-vard architecture, allow unconstrained data flow between computation units and internal memory. The registers in PEX are referred to as R0–R15 and in PEY as S0–S15.Single-Cycle Fetch of Instruction and Four Operands The ADSP-21266 features an enhanced Harvard architecture in which the data memory (DM) bus transfers data and the pro-gram memory (PM) bus transfers both instructions and data (see Figure 1 on Page 1). With the ADSP-21266’s separate pro-gram and data memory buses and on-chip instruction cache, the processor can simultaneously fetch four operands (two over each data bus) and one instruction (from the cache), all in a single cycle.Instruction CacheThe ADSP-21266 includes an on-chip instruction cache that enables three-bus operation for fetching an instruction and four data values. The cache is selective—only the instructions whose fetches conflict with PM bus data accesses are cached. This cache allows full-speed execution of core, looped operations such as digital filter multiply-accumulates, and FFT butterfly processing.Data Address Generators with Zero-Overhead Hardware Circular Buffer SupportThe ADSP-21266’s two data address generators (DAGs) are used for indirect addressing and implementing circular data buffers in hardware. Circular buffers allow efficient program-ming of delay lines and other data structures required in digital signal processing, and are commonly used in digital filters andFigure 2.ADSP-21266 System Sample ConfigurationADSP-21266Fourier transforms. The two DAGs of the ADSP-21266 contain sufficient registers to allow the creation of up to 32 circular buff-ers (16 primary register sets, 16 secondary). The DAGs automatically handle address pointer wraparound, reduce over-head, increase performance, and simplify implementation. Circular buffers can start and end at any memory location. Flexible Instruction SetThe 48-bit instruction word accommodates a variety of parallel operations for concise programming. For example, theADSP-21266 can conditionally execute a multiply, an add, and a subtract in both processing elements while branching and fetch-ing up to four 32-bit values from memory—all in a single instruction.ADSP-21266 MEMORY AND I/O INTERFACE FEATURESThe ADSP-21266 adds the following architectural features to the SIMD SHARC family core:Dual-Ported On-Chip MemoryThe ADSP-21266 contains two megabits of internal SRAM and four megabits of internal mask-programmable ROM. Each block can be configured for different combinations of code and data storage (see memory map, Figure3). Each memory block is dual-ported for single-cycle, independent accesses by the core processor and I/O processor. The dual-ported memory, in com-bination with three separate on-chip buses, allows two data transfers from the core and one from the I/O processor, in a sin-gle cycle.The ADSP-21266 is available with a variety of multichannel surround-sound decoders, preprogrammed in on-chip ROM memory. Table2 indicates the configurations of decoder algo-rithms provided.The ADSP-21266’s SRAM can be configured as a maximum of 64K words of 32-bit data, 128K words of 16-bit data, 42K words of 48-bit instructions (or 40-bit data), or combinations of differ-ent word sizes up to two megabits. All of the memory can be accessed as 16-bit, 32-bit, 48-bit, or 64-bit words. A 16-bit float-ing-point storage format is supported that effectively doubles the amount of data that can be stored on-chip. Conversion between the 32-bit floating-point and 16-bit floating-point for-mats is performed in a single instruction. While each memory block can store combinations of code and data, accesses are most efficient when one block stores data using the DM bus for transfers, and the other block stores instructions and data using the PM bus for transfers.Using the DM bus and PM buses, with one dedicated to each memory block, assures single-cycle execution with two data transfers. In this case, the instruction must be available inthe cache.DMA ControllerThe ADSP-21266’s on-chip DMA controller allows zero-over-head data transfers without processor intervention. The DMA controller operates independently and invisibly to the processor core, allowing DMA operations to occur while the core is simul-taneously executing its program instructions. DMA transfers can occur between the ADSP-21266’s internal memory and its serial ports, the SPI-compatible (serial peripheral interface) port, the IDP (input data port), parallel data acquisition port (PDAP), or the parallel port. Twenty-two channels of DMA are available on the ADSP-21266—one for the SPI interface, 12 via the serial ports, eight via the input data port, and one via the processor’s parallel port. Programs can be downloaded to the ADSP-21266 using DMA transfers. Other DMA features include interrupt generation upon completion of DMA trans-fers, and DMA chaining for automatic linked DMA transfers. Digital Audio Interface (DAI)The digital audio interface provides the ability to connect vari-ous peripherals to any of the SHARC DSP’s DAI pins(DAI_P20–1).Connections are made using the signal routing unit (SRU, shown in the block diagram on Page1).The SRU is a matrix routing unit (or group of multiplexers) that enables the peripherals provided by the DAI to be intercon-nected under software control. This allows easy use of the DAI associated peripherals for a much wider variety of applications by using a larger set of algorithms than is possible with noncon-figurable signal paths.The DAI also includes six serial ports, two precision clock gen-erators (PCGs), an input data port (IDP), six flag outputs and six flag inputs, and three timers. The IDP provides an additional input path to the ADSP-21266 core, configurable as either eight channels of I2S or serial data, or as seven channels plus a single 20-bit wide synchronous parallel data acquisition port. Each data channel has its own DMA channel that is independent from the ADSP-21266’s serial ports.For complete information on using the DAI, see theADSP-2126x SHARC DSP Peripherals Manual.Serial PortsThe ADSP-21266 features six full duplex synchronous serial ports that provide an inexpensive interface to a wide variety of digital and mixed-signal peripheral devices such as the Analog Devices AD183x family of audio codecs, ADCs, and DACs. TheTable 2.Multichannel Surround-Sound Decoder Algorithmsin On-Chip ROMAlgorithms B ROM C ROM D ROMPCM Yes Yes YesAC-3Yes Yes YesDTS 96/24v2.2v2.3v2.3AAC (LC)Yes Yes Coefficients onlyWMAPRO 7.1 96 KHz No No YesMPEG2 BC 2ch Yes Yes NoNoise Yes Yes YesDPL2x/EX DPL2Yes YesNeo:6/ES (v2.5046)Yes Yes YesRev. C|Page 6 of 44|October 2007ADSP-21266Rev. C|Page 7 of 44|October 2007serial ports are made up of two data lines, a clock, and frame sync. The data lines can be programmed to either transmit or receive and each data line has its own dedicated DMA channel.Serial ports are enabled via 12 programmable and simultaneous receive or transmit pins that support up to 24 transmit or 24 receive channels of audio data when all six SPORTs are enabled, or six full duplex TDM streams of 128 channels per frame.The serial ports operate at up to one-quarter of the DSP core clock rate, providing each with a maximum data rate of 50M bits/sec for a 200 MHz core and 37.5M bits/sec for a150MHz core. Serial port data can be automatically transferred to and from on-chip memory via a dedicated DMA. Each of theserial ports can work in conjunction with another serial port to provide TDM support. One SPORT provides two transmit sig-nals while the other SPORT provides two receive signals. The frame sync and clock are shared.Serial ports operate in four modes: •Standard DSP serial mode •Multichannel(TDM)mode •I 2S mode•Left-justified sample pair modeFigure 3.ADSP-21266 Memory MapADSP-21266Left-justified sample pair mode is a mode where in each frame sync cycle, two samples of data are transmitted/received—one sample on the high segment of the frame sync, the other on the low segment of the frame sync. Programs have control over var-ious attributes of this mode.Each of the serial ports supports the left-justified sample-pair and I2S protocols (I2S is an industry-standard interface com-monly used by audio codecs, ADCs, and DACs) with two data pins, allowing four left-justified sample-pair or I2S channels (using two stereo devices) per serial port with a maximum of up to 24 audio channels. The serial ports permit little-endian or big-endian transmission formats and word lengths selectable from 3 bits to 32 bits. For the left-justified sample pair and I2S modes, data-word lengths are selectable between 8 bits and 32 bits. Serial ports offer selectable synchronization and transmit modes as well as optional μ-law or A-law companding selection on a per channel basis. Serial port clocks and frame syncs can be internally or externally generated.Serial Peripheral (Compatible) InterfaceSerial peripheral interface is an industry-standard synchronous serial link, enabling the ADSP-21266 SPI-compatible port to communicate with other SPI-compatible devices. SPI is an interface consisting of two data pins, one device select pin, and one clock pin. It is a full-duplex synchronous serial interface, supporting both master and slave modes. The SPI port can operate in a multimaster environment by interfacing with up to four other SPI-compatible devices, either acting as a master or slave device. The ADSP-21266 SPI-compatible peripheral implementation also features programmable baud rates at up to 50 MHz for a core clock of 200 MHz and up to 37.5 MHz for a core clock of 150 MHz, clock phases, and polarities. The ADSP-21266 SPI-compatible port uses open-drain drivers to support a multimaster configuration and to avoid data contention. Parallel PortThe parallel port provides interfaces to SRAM and peripheral devices. The multiplexed address and data pins (AD15–0) can access 8-bit devices with up to 24 bits of address, or 16-bit devices with up to 16 bits of address. In either mode, 8- or 16-bit, the maximum data transfer rate is one-third the core clock speed. As an example, a clock rate of 200 MHz is equivalent to 66M byte/sec, and a clock rate of 150 MHz is equivalent to50M byte/sec.DMA transfers are used to move data to and from internal memory. Access to the core is also facilitated through the paral-lel port register read/write functions. The RD, WR, and ALE (address latch enable) pins are the control pins for the parallel port.TimersThe ADSP-21266 has a total of four timers: a core timer able to generate periodic software interrupts, and three general-pur-pose timers that can generate periodic interrupts and be independently set to operate in one of three modes:•Pulse waveform generation mode•Pulse width count/capture mode•External event watchdog modeThe core timer can be configured to use flag3 as a timer expired output signal, and each general-purpose timer has one bidirec-tional pin and four registers that implement its mode of operation: a 6-bit configuration register, a 32-bit count register, a 32-bit period register, and a 32-bit pulse width register. A sin-gle control and status register enables or disables all three general-purpose timers independently.ROM-Based SecurityThe ADSP-21266 has a ROM security feature that provides hardware support for securing user software code by preventing unauthorized reading from the internal code when enabled. When using this feature, the DSP does not boot-load any exter-nal code, executing exclusively from internal SRAM/ROM. Additionally, the DSP is not freely accessible via the JTAG port. Instead, a unique 64-bit key, which must be scanned in through the JTAG or test access port, will be assigned to each customer. The device will ignore a wrong key. Emulation features and external boot modes are only available after the correct key is scanned.Program BootingThe internal memory of the ADSP-21266 boots at system power-up from an 8-bit EPROM via the parallel port, an SPI master, an SPI slave, or an internal boot. Booting is determined by the boot configuration (BOOT_CFG1–0) pins. Selection of the boot source is controlled via the SPI as either a master or slave device, or it can immediately begin executing from ROM. Phase-Locked LoopThe ADSP-21266 uses an on-chip phase-locked loop (PLL) to generate the internal clock for the core. On power-up, the CLK_CFG1–0 pins are used to select ratios of 16:1, 8:1, and 3:1. After booting, numerous other ratios can be selected via soft-ware control. The ratios are made up of software configurable numerator values from 1 to 64 and software configurable divi-sor values of 2, 4, 8, and 16.Power SuppliesThe ADSP-21266 has separate power supply connections for the internal (V DDINT), external (V DDEXT), and analog (A VDD/A VSS) power supplies. The internal and analog supplies must meet the 1.2 V requirement. The external supply must meet the 3.3 V requirement. All external supply pins must be connected to the same power supply.Note that the analog supply pin (A VDD) powers theADSP-21266’s internal clock generator PLL. To produce a sta-ble clock, it is recommended that PCB designs use an externalRev. C|Page 8 of 44|October 2007。

Extreme Networks Summit X460-G2 数据手册说明书

The Summit® X460-G2 series is based on Extreme Networks® revolutionaryExtremeXOS®, a highly resilient OS that provides continuous uptime, manageability and operational efficiency. Each switch offers the same high-performance, non-blocking hardware technology, in the Extreme Networks tradition of simplifying network deployments through the use of common hardware and software throughout the network.The Summit X460-G2 switches are effective campus edge switches that support Energy Efficient Ethernet (EEE – IEEE 802.3az) with IEEE 802.3at PoE-plus and can also serve as aggregation switches for traditional enterprise networks. The Summit X460-G2 series is also an option for DSLAM or CMTS aggregation, or for active Ethernet access.The Summit X460-G2 can also be used as a top-of-rack switch for many data center environments with features such as high-density Gigabit Ethernet for concentrated data center environments; XNV™ (ExtremeXOS Network Virtualization) for centralized network-based Virtual Machine (VM) inventory, VM location history and VM provisioning; Direct Attach™ to offload VM switching from servers, thereby improving performance; high-capacity Layer 2/Layer 3 scalability for highly virtualized data centers; and intra-rack and cross-rack stacking with industry-leading flexibility.Comprehensive Security Management• User policy and host integrity enforcement, and identity management • Universal Port Dynamic Security Profiles to provide fine granular securitypolicies in the network• Threat detection and response instrumentation to react to network intrusion with CLEAR-Flow Security Rules Engine• Denial of Service (DoS) protection and IP security against man-in-the-middle and DoS attacks to harden the network infrastructureFlexible Port ConfigurationSummit X460-G2 offers flexible port configurations. For Summit X460-G2 24 port copper models with 10Gb uplinks with four dedicated Gigabit Ethernet fiber ports and four shared Gigabit Ethernet fiber ports, the switch can have up to 8 fiber GbE ports, while still providing 20 Gigabit Ethernet copper ports (PoE-plus or non-PoE). The Summit X460-G2 24 port copper models with 1Gb uplinks can provide up to 12 SFP ports with 20 Gigabit Ethernet ports or eight SFP ports with 24 copper GbE ports.All models come equipped with either 4 ports of SFP+ 10 GbE or 4 ports of SFP 1GbE resident on the faceplate of each model. Through an optional VIM slot, Summit X460-G2 switches can be equipped with an additional 2 ports of 10 GbE for a total of six 10 Gigabit Ethernet ports on the 10Gb uplink models.As another option, each unit can be equipped with 2 ports of QSFP+ 40 Gigabit Ethernet for uplinks or stacking.High-Performance StackingUp to eight Summit X460-G2 switches can be stacked using three different methods of stacking: SummitStack, SummitStack-V, and SummitStack-V160.SUMMITSTACK — STACKING USING COPPER CX4 CONNECTIONSThe Summit X460-G2 supports SummitStack by using the Summit X460-G2-VIM-2ss module, which offers high-speed 40 Gbps stacking performance and provides compatibility with the Summit X440, X460, X460-G2 and X480 stackable switches running the same version of ExtremeXOS.SUMMITSTACK-V — FLEXIBLE STACKING OVER 10GbEExtremeXOS supports the SummitStack-V capability using 2 of the native 10 GbE ports on the faceplate as stacking ports, enabling the use of standard cabling and optics technologies used for 10 GbE SFP+, SummitStack-V provides long-distance 40 Gbps stacking connectivity of up to 40 km while reducing the cable complexity of implementing a stacking solution. SummitStack-V is compatible with SummitX440, X460, X460-G2, X480, X670, X670V, X670-G2 and X770 switches running the same version of ExtremeXOS. SummitStack-V enabled 10 GbE ports must be physically direct-connected.Note: Stacking will NOT be supported on the 10GbE fiber VIM and the 10GbE copperVIM with initial X460-G2 shipments.Note: SummitStack-V is NOT supported on the 1GbE (SFP) front panel faceplateports of non-10Gb X460-G2 models.SUMMITSTACK-V160 — FLEXIBLE STACKING OVER 40GbEThe Summit X460-G2 also supports high-speed 160 Gbps stacking, which is idealfor demanding applications where a high volume of traffic traverses through the stacking links, yet bandwidth is not compromised through stacking.SummitStack-V160 can support passive copper cable (up to 3m), active multi-mode fiber cable (up to 100m), and QSFP+ optical transceivers for 40 GbE up to 10km. With SummitStack-V160, the Summit X460-G2 provides a flexible stacking solution inside the data center or central office to create a virtualized switching infrastructure across rows of racks. SummitStack-V160 is compatible with Summit X460-G2, X480, X670V, X670-G2 and X770 switches running the same version of ExtremeXOS.Intelligent Switching and MPLS/H-VPLS SupportSummit X460-G2 supports sophisticated and intelligent Layer 2 switching, as well as Layer 3 IPv4/IPv6 routing including policy-based switching/routing, Provider Bridges, bidirectional ingress and egress Access Control Lists, and bandwidth control by 8 Kbps granularity both for ingress and egress.T o provide scalable network architectures used mainly for Carrier Ethernet network deployment, Summit X460-G2 supports MPLS LSP-based Layer 3 forwarding and Hierarchical VPLS (H-VPLS) for transparent LAN services. WithH-VPLS, transparent Layer 3 networks can be extended throughout the Layer 3 network cloud by using a VPLS tunnel between the regional transparent LAN services typically built by Provider Bridges (IEEE 802.1ad) technologyIEEE 802.3at PoE-plusIEEE 802.3af Power over Ethernet has been widely used in the campus enterprise edge network for Ethernet-powered devices such as wireless access points, Voice over IP phones, and security cameras. Ethernet port extenders such as Extreme Networks ReachNXT™ 100-8t can also utilize PoE, making installation and management easier and reducing maintenance costs. The newer IEEE 802.3at PoE-plus standard expands upon Power over Ethernet by increasing the power limitup to 30 watts, and by standardizing power negotiation by using LLDP. SummitX460-G2 supports IEEE 802.3at PoE-plus and supports standards-compliant PoE devices today and into the future.1588 Precision Time Protocol (PTP)Summit X460-G2 offers Boundary Clock (BC), Transparent Clock (TC), and Ordinary Clock (OC) for synchronizing phase and frequency and allowing the network and the connected devices to be synchronized down to microseconds of accuracy over Ethernet connection.Audio Video Bridging (AVB)The X460-G2 series supports IEEE 802.1 Audio Video Bridging to enable reliable, real-time audio/video transmission over Ethernet. AVB technology delivers the quality of service required for today’s high-definition and time-sensitive multimedia streams.Ordering NotesThe X460-G2 base switches do not ship with fan trays or power supplies. The fan tray and power supplies must be ordered separately as well as any of the optional VIMS. There is only one optional VIM slot on each X460-G2 switch. The optional Timing Module has a separate dedicated slot on the back of the X460-G2 switch.CPU/MEMORY• 64-bit MIPS Processor, 1 GHz clock• 1GB ECC DDR3 DRAM• 4GB eMMC Flash• 4MB packet bufferLED INDICATORS• Per port status LED including power status• System Status LEDs: management, fan and powerENVIRONMENTAL SPECIFICATIONS• EN/ETSI 300 019-2-1 v2.1.2 - Class 1.2 Storage• EN/ETSI 300 019-2-2 v2.1.2 - Class 2.3 Transportation • EN/ETSI 300 019-2-3 v2.1.2 - Class 3.1e Operational• EN/ETSI 300 753 (1997-10) - Acoustic Noise• ASTM D3580 Random Vibration Unpackaged 1.5 G OPERATING CONDITIONS• T emp: 0° C to 50° C (32° F to 122° F)• Humidity: 10% to 95% relative humidity, non-condensing • Altitude: 0 to 3,000 meters (9,850 feet)• Shock (half sine): 30 m/s2 (3 G), 11 ms, 60 shocks• Random vibration: 3 to 500 Hz at 1.5 G rms PACKAGING AND STORAGE SPECIFICATIONS • T emp: -40° C to 70° C (-40° F to 158° F)• Humidity: 10% to 95% relative humidity, non-condensing• Packaged Shock (half sine): 180 m/s2 (18 G), 6 ms, 600shocks• Packaged Vibration: 5 to 62 Hz at velocity 5 mm/s, 62 to 500 Hz at 0.2 G• Packaged Random Vibration: 5 to 20 Hz at 1.0 ASD w/–3 dB/oct. from 20 to 200 Hz• Packaged Drop Height: 14 drops minimum on sides and corners at 42 inches (<15 kg box)REGULATORY AND SAFETYNorth American ITE• UL 60950-1 2nd Ed., Listed Device (U.S.)• CSA 22.2 #60950-1-03 2nd Ed. (Canada)• Complies with FCC 21CFR 1040.10 (U.S. Laser Safety)• CDRH Letter of Approval (US FDA Approval) European ITE• EN 60950-1:2007 2nd Ed.• EN 60825-1+A2:2001 (Lasers Safety)• TUV-R GS Mark by German Notified Body• 2006/95/EC Low Voltage DirectiveInternational ITE• CB Report & Certificate per IEC 60950-1 2nd Ed. +National Differences• AS/NZX 60950-1 (Australia /New Zealand)EMI/EMC STANDARDSNorth American EMC for ITE• FCC CFR 47 part 15 Class A (USA)• ICES-003 Class A (Canada)European EMC Standards• EN 55022:2006+A1:2007 Class A• EN 55024:A2-2003 Class A includes IEC 61000-4-2, 3, 4, 5, 6, 11• EN 61000-3-2,8-2006 (Harmonics)• EN 61000-3-3 2008 (Flicker)• ETSI EN 300 386 v1.4.1, 2008-04 (EMC T elecommunications)• 2004/108/EC EMC DirectiveInternational EMC Certifications• CISPR 22: 2006 Ed 5.2, Class A (International Emissions)• CISPR 24:A2:2003 Class A (International Immunity)• IEC 61000-4-2:2008/EN 61000-4-2:2009 ElectrostaticDischarge, 8kV Contact, 15 kV Air, Criteria A• IEC 61000-4-3:2008/EN 61000-4-3:2006+A1:2008 Radiated Immunity 10V/m, Criteria A• IEC 61000-4-4:2004 am1 ed.2./EN 61000-4-4:2004/A1:2010 Transient Burst, 1 kV, Criteria A• IEC 61000-4-5:2005 /EN 61000-4-5:2006 Surge, 2 kV L-L, 2 kV L-G, Level 3, Criteria A• IEC 61000-4-6:2008/EN 61000-4-6:2009 ConductedImmunity, 0.15-80 MHz, 10V/m unmod. RMS, Criteria A• IEC/EN 61000-4-11:2004 Power Dips & Interruptions, >30%,25 periods, Criteria CCOUNTRY SPECIFIC• VCCI Class A (Japan Emissions)• ACMA (C-Tick) (Australia Emissions)• CCC Mark• KCC Mark, EMC Approval (Korea)TELECOM STANDARDS• ETSI EN 300 386:2001 (EMC T elecommunications)• ETSI EN 300 019 (Environmental for T elecommunications)• NEBS Level 3 compliant to portions of GR-1089 Issue 4 &GR-63 Issue 3 as defined in SR3580 with exception to filter requirement• CE 2.0 CompliantIEEE 802.3 MEDIA ACCESS STANDARDS• IEEE 802.3ab 1000BASE-T• IEEE 802.3z 1000BASE-X• IEEE 802.3ae 10GBASE-X• IEEE 802.3at PoE Plus• IEEE 802.3az (EEE)* Bystander Sound Pressure is presented for comparison to other products measured using Bystander Sound Pressure. **Declared Sound Power is presented in accordance with ISO-7779:2010(E), ISO 9296:2010 per ETSI/EN 300 753:2012-01SUMMIT X460-G2 VIM-2T2-port 10 Gigabit Ethernet module, provides two 10GBase-T copper ports. SUMMIT X460-G2 VIM-2SSSummitStack module has two SummitStack stacking ports, and provides a 40 Gigabit stacking solution. This stacking module offers compatibility with other Extreme Networks stackable switches, which are Summit X440, Summit X460, and SummitX480.Ordered EmptyRequired: First Power Supply with Air Flow Direction ordered separatelyOptional:Redundant/Additive Power Supply with Air Flow Direction ordered separatelyOptional: Timing Module for SyncE and 1588 PTP ordered separatelyRequired: Fan Tray with Air Flow Direction ordered separatelyOptional: VIM Cardsordered separately* = data networking, not stacking/contact Phone +1-408-579-2800©2014 Extreme Networks, Inc. All rights reserved. Extreme Networks and the Extreme Networks logo are trademarks or registered trademarks of Extreme Networks, Inc. in the United States and/or other countries. All other names are the property of their respective owners. For additional information on Extreme Networks Trademarks。

IGLOO2 FPGAs商品说明书

IGLOO®2 FPGAsThe Industry’s Lowest-Power FPGAs/FPGA2IGLOO ®2 FPGAsIGLOO ®2 FPGAs Offer More Resources in Low-Density Devices With the Lowest Power, Proven Security and Exceptional ReliabilityIGLOO2 FPGAs are ideal for general-purpose functions such as Gigabit Ethernet or dual-PCI Express control planes, bridgingfunctions, (I/O) expansion and conversion, video/image processing, system management and secure connectivity. FPGAs are used in communications, industrial, medical, defense and aviation markets.IGLOO2 FeaturesMore Resources in Low-Density Devices• PCIe ® Gen 2 support in 10K LE• High-performance memory subsystem • Highest I/O densityWith Clear Advantages• Lowest power• Reduces total power by up to 50% • 70 mW per 5G SERDES (PCIe Gen 2) • Proven security• Protection from overbuilding and cloning • Secure boot for FPGA and processors • Exceptional reliability• SEU immune zero FIT Flash FPGA configuration •Reliable safety-critical and mission-critical systemsIGLOO2 FPGA ArchitectureIGLOO2 FPGAs offer 5K–150K LEs with a high-performance memory subsystem, up to 512 KB embedded Flash, 2 × 32 KB embedded SRAM, two Direct Memory Access (DMA) engines and two Double Data Rate (DDR) memory controllers. Architecture highlights include:• Up to 16× transceiver lanes • PCIe Gen 2, XAUI/XGXS+, generic ePCS mode at 3.2G • Up to 150K LEs, 5 Mbits SRAM, 4 Mbits eNVM• Hard 667 Mbps DDR2/3 controllers• Integrated DSP processing blocks• Power as low as 7 mW standby, typical• DPA-hardened, AES256, SHA256, on-demand NVM dataintegrity check • SEU-protected/tolerant memories: eSRAMs, DDR bridgesPCI ExpressDDR3 ControllerSecure FlashIGLOO2 FPGAs3PCIe 1G Control Plane• PCIe Gen 2 in 10K LE devices With I/O expansionMulti-Axis Motor Control• Deterministic and secure multi-axis/high-RPM solutions • Motor control IP and development kitAudio Processing, Storage, and Retrieval• I 2S-to-SPI bridge allows multiple audio recordings and playbacks/FPGA4Bridging and Co-Processing• SERDES to bridge CPRI, ADC/DACSecure Connectivity• Best-in-class security data communications and anti-tamper • Ultra-low static power for portabilityBoard Initialization• PMBus, instant-onIGLOO2 FPGAs5IGLOO2 FPGA FeaturesHigh-Performance Memory Subsystem• 64 KB embedded SRAM (eSRAM)• Up to 512 KB embedded nonvola -tile memory (eNVM)• One SPI/COMM_BLK• DDR bridge (2 port) with 64-bit AXI interface• Non-blocking, multi-layer AHB bus matrix allowing multi-master scheme supporting 4 masters and 8 slaves• Two AHB/APB interfaces to FPGA fabric (master/slave capable)• Two DMA controllers to offload data transactions• 8-channel peripheral DMA (PDMA) for data transfer between softperipherals in fabric and embedded eSRAMs, as well as support for memory-to-memory transfers• eSRAM and external DDR memory for efficient data movement between embedded real-time memoriesIGLOO2 FPGA SERDES• Up to 16 lanes at up to 5 Gbps • Dual-based reference clocks with single-lane rate granularity• Tx and Rx PLLs programmable for each lane• Reference clock is shared by groups of two lanes• Transmitter features• Programmable pre/post-emphasis • Programmable impedance • Programmable amplitude• Receiver features • Programmable termination• Programmable linear equalization• Built-in system debug features• PRBS gen/chk • Constant patterns • LoopbacksIGLOO2 FPGA Math Block• High-performance and power-optimized multiplication operations • Supports 18 × 18-signed multiplica -tion (natively)• Supports 17×17 unsigned multiplication• Supports dot product: the multi-plier computes (A[8:0] × B[17:9] + A[17:9] × B[8:0]) × 29 independent third input C with data width 44-bits completely registered• Supports both registered and unregistered inputs and outputs• Internal cascade signals(44-bit CDIN and CDOUT)enable cascading of the Math Blocks to supportlarger accumulator, adder,and subtractor withoutextra logic • Supports loopback capability• Adder support: (A×B) + C or (A×B) +D or (A×B) + C + D • Clock-gated inputand output registers for poweroptimizationsSUBA [17:0]B [17:0]C [43:0]CARRYIN ARSHFT17CDSELFDBKSELIGLOO2 FPGA Logic Element• A fully permutable 4-input LUT • A dedicated carry chain based on the carry look-ahead technique• A separate flip-flop that can be used independently from the LUT • Clock-gated input and output registers for power optimizationsA B C D CINLUT_BYPENSYNC_SRCLK RSTCO LORO/FPGA6Design ResourcesLibero ® SoC Design SoftwareLibero SoC Design Suite offers high productivity with its comprehensive, easy-to-learn, easy-to-adopt development tools that are used for designing with Microchip’s power-efficient Flash-based IGLOO2 devices. The suite integrates industry-standard Synopsys Synplify Pro synthesis and Mentor Graphics ModelSim simulation with best-in-class constraints management, debug capabilities, timing analysis, power analysis, secure production programming and push button design flow.This comprehensive suite features an intuitive design flow with GUI wizards to guide the design process. Its easy-to-adopt single-click synthesis to programming flow integrates industry-standard third-party tools, a rich IP library of DirectCores and Companion -Cores and supports complete reference designs and development kits.https:///product-directory/design-resources/1750-libero-socIGLOO2 Evaluation Kit• Gives designers access to IGLOO2 FPGAs that offer leadership in I/O density, security, reliability and low power for mainstream applications • Supports industry-standard interfaces including Gigabit Ethernet, USB 2.0 OTG, SPI, I 2C and UART• Can be powered by a 12V power supply or the PCIe connector and includes a FlashPro4 programmerBoard features• IGLOO2 FPGA in the FGG484 package (M2GL010T -1FGG484)• JTAG/SPI programming interface• Gigabit Ethernet PHY and RJ45 connector • USB 2.0 OTG interface connector • 1 GB LPDDR, 64 MB SPI Flash • Headers for I 2C, UART, SPI, GPIOs • ×1 Gen2 PCIe edge connector •Tx/Rx/Clk SMP pairs/existing-parts/parts/143976Intellectual PropertyMicrochip enhances your design productivity by providing an extensive suite of proven and optimized IP cores for use with FPGAs. Our extensive suite of IP cores covers all key markets and applications. Our cores are organized as either Microchip-developed DirectCores or third-party-developed CompanionCores. Most DirectCores are available for free within our Libero tool suite and include common communications interfaces, peripherals, and processing elements.Below are a few key DirectCores and CompanionCores. Click the below link for more details on IP Cores./product-directory/design-resources/5092-ip-coresIGLOO2 FPGA Product Family*Feature availablility is package dependent.Highlighted devices can migrate vertically in the same packageIGLOO2 FPGAs7SupportMicrochip is committed to supporting its customers in de-veloping products faster and more efficiently. We maintain a worldwide network of field applications engineers and technical support ready to provide product and system assistance. For more information, please visit :• Technical Support: /support • Evaluation samples of any Microchip device: /sample • Knowledge base and peer help: /forums• Sales and Global Distribution: /salesTrainingIf additional training interests you, Microchip offers several resources including in-depth technical training and reference material, self-paced tutorials and significant online resources.• Overview of Technical Training Resources: /training • MASTERs Conferences: /masters • Developer Help Website:/developerhelp • Technical Training Centers: /seminarsMicrochip Technology Inc. | 2355 W. Chandler Blvd. | Chandler AZ, 85224-6199Sales Office ListingAMERICASAtlanta, GATel: 678-957-9614Austin, TXTel: 512-257-3370Boston, MATel: 774-760-0087Chandler, AZ (HQ) Tel: 480-792-7200Chicago, ILTel: 630-285-0071Dallas, TXTel: 972-818-7423Detroit, MITel: 248-848-4000Houston, TXTel: 281-894-5983Indianapolis, IN Tel: 317-773-8323 Tel: 317-536-2380Los Angeles, CA Tel: 949-462-9523 Tel: 951-273-7800Raleigh, NCTel: 919-844-7510New York, NY Tel: 631-435-6000San Jose, CA Tel: 408-735-9110 Tel: 408-436-4270Canada - Toronto Tel: 905-695-1980EUROPEAustria - WelsTel: 43-7242-2244-39Denmark - Copenhagen Tel: 45-4450-2828Finland - Espoo Tel: 358-9-4520-820France - ParisTel: 33-1-69-53-63-20Germany - Garching Tel: 49-8931-9700Germany - HaanTel: 49-2129-3766-400Germany - Heilbronn Tel: 49-7131-67-3636Germany - Karlsruhe Tel: 49-721-62537-0Germany - Munich Tel: 49-89-627-144-0Germany - Rosenheim Tel: 49-8031-354-560EUROPEIsrael - Ra’anana Tel: 972-9-744-7705Italy - MilanTel: 39-0331-742611Italy - PadovaTel: 39-049-7625286Netherlands - Drunen Tel: 31-416-690399Norway - Trondheim Tel: 47-7289-7561Poland - Warsaw Tel: 48-22-3325737Romania - Bucharest Tel: 40-21-407-87-50Spain - MadridTel: 34-91-708-08-90Sweden - Gothenberg Tel: 46-31-704-60-40Sweden - Stockholm Tel: 46-8-5090-4654UK - Wokingham Tel: 44-118-921-5800ASIA/PACIFICAustralia - Sydney Tel: 61-2-9868-6733China - BeijingTel: 86-10-8569-7000China - Chengdu Tel: 86-28-8665-5511China - Chongqing Tel: 86-23-8980-9588China - Dongguan Tel: 86-769-8702-9880China - Guangzhou Tel: 86-20-8755-8029China - Hangzhou Tel: 86-571-8792-8115China - Hong Kong SAR Tel: 852-2943-5100China - NanjingTel: 86-25-8473-2460China - QingdaoTel: 86-532-8502-7355China - Shanghai Tel: 86-21-3326-8000China - Shenyang Tel: 86-24-2334-2829China - Shenzhen Tel: 86-755-8864-2200China - SuzhouTel: 86-186-6233-1526China - WuhanTel: 86-27-5980-5300China - Xiamen Tel: 86-592-2388138China - XianTel: 86-29-8833-7252ASIA/PACIFICChina - ZhuhaiTel: 86-756-321-0040India - Bangalore Tel: 91-80-3090-4444India - New Delhi Tel: 91-11-4160-8631India - PuneTel: 91-20-4121-0141Japan - Osaka Tel: 81-6-6152-7160Japan - TokyoTel: 81-3-6880-3770Korea - Daegu Tel: 82-53-744-4301Korea - Seoul Tel: 82-2-554-7200Malaysia - Kuala Lumpur Tel: 60-3-7651-7906Malaysia - Penang Tel: 60-4-227-8870Philippines - Manila Tel: 63-2-634-9065SingaporeTel: 65-6334-8870Taiwan - Hsin Chu Tel: 886-3-577-8366Taiwan - Kaohsiung Tel: 886-7-213-7830Taiwan - TaipeiTel: 886-2-2508-8600Thailand - Bangkok Tel: 66-2-694-1351Vietnam - Ho Chi Minh Tel: 84-28-5448-21005/15/19The Microchip name and logo, the Microchip logo, IGLOO and Libero are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries. All other trademarks mentioned herein are property of their respective companies.© 2019, Microchip Technology Incorporated. All Rights Reserved. 11/19 DS00003294A。

富士通笔记本电脑LIFEBOOK E4412产品说明书

Data Sheet Fujitsu Notebook LIFEBOOK E4412Fujitsu recommends Windows 11 Pro.Data SheetFujitsu Notebook LIFEBOOK E4412Your Well-Equipped Everyday PartnerThe Fujitsu LIFEBOOK E4412 is exclusively designed for office workers needing a powerful and well-equipped notebook that offers a fair price-performance ratio. Great connectivity options such as 4 G/LTE or Intel® Thunderbolt™ 4, an integrated fingerprint sensor and a modern robust design help you to work efficiently wherever you are.Modern and robust designReliable mobility, ease of use and modern looks for everyday business demands Ultra slim 19.9 mm entry notebook starting at 1.35 kg with magnesium LCD lid Enjoy an ergonomic viewing experience with an anti-glare 14.0-inch FHD display Reliable and secure performanceProtect your notebook and business data from unauthorized access at all times Fingerprint sensorBuilt-in Privacy Camera Shutter: Protecting your privacyInfrared Camera: Allows face recognistion with Windows Hello Intel® Iris® Xe GraphicsBest in class connectivityBe flexible and stay productive wherever you areFull set of ports with a full-sized HDMI, LAN connector and USB Type-C with Intel® Thunderbolt™ 4 Embedded 4G/LTE enables you to access and transfer data fasterConvenient serviceability and upgradeabilityEasy access to key components to reduce upgrade time and costsBattery, memory, internal storage and connectivity components can be changed with easeComponentsBase unit LIFEBOOK E4412Operating systemsOperating system pre-installed Windows 11 Pro. Fujitsu recommends Windows 11 Pro for business.Windows 11 HomeWindows 10 Pro. Fujitsu recommends Windows 11 Pro for business.Microsoft OS support information Windows 11 requires for first device setup:- Internet connectivity- Microsoft account for Home editions or organizational account (e.g. ADD) for Pro editionsAfter product end of life, Fujitsu continues to test and support new Windows releases for max. 5 years, depending onextension of hardware services through warranty top ups.For more details please visit our Fujitsu Service Statement under https:///IndexProdSupport.asp?lng=com&OpenTab=Operating system notes The use of Windows Operating System is subject to acceptance of the End User License Agreement of Microsoft asapplicable under the relevant Microsoft program.Processor Intel® Core™ i7-1255U processor (10C, up to 4.7 GHz) *, ***Intel® Core™ i5-1235U processor (10C, up to 4.4 GHz) *, ***Intel® Core™ i3-1215U processor (6C, up to 4.4 GHz) ** Processor only for retail, SMB, education and government***Processor supports Intel® vPro® EssentialMemory modules 4 GB (1 module(s) 4 GB) DDR4, 3,200 MT/s, SO DIMM8 GB (1 module(s) 8 GB) DDR4, 3,200 MT/s, SO DIMM16 GB (1 module(s) 16 GB) DDR4, 3,200 MT/s, SO DIMM32 GB (1 module(s) 32 GB) DDR4, 3,200 MT/s, SO DIMMHard disk drives (internal)PCIe-SSD, 512 GB M.2 NVMe module, SEDPCIe-SSD, 256 GB M.2 NVMe module, SEDPCIe-SSD, 1 TB M.2 NVMe module, SEDHard disk notes Durability in accordance with the manufacturer’s indications on read and write cycles.Interface add on cards/components(optional)4G/ LTE (optional)Quectel EM120R-GL (4G Cat.12) (Downlink speed 600 MB/s, Uplink speed 150 MB/s)LTE Sierra Wireless EM7421B (Cat.7) (Downlink speed up to 300 Mbit/s, Uplink speed up to 150 Mbit/s)Display35.6 cm (14.0-inch), FHD, 1,920 x 1,080 pixel, Anti-glare IPS display, 250 cd/m² (FHD), 700:1 (FHD)MultimediaCamera Built-in webcam (HD) with Status LED Built-in Infrared webcam (HD) with Status LED Camera notes720p, 1 megapixels, 1280 x 720, with Privacy Camera ShutterMicrophone dual digital array microphoneBase unitBase unit LIFEBOOK E4412General system informationChipset Integrated in CPUSupported capacity RAM (min.) 4 GBSupported capacity RAM (max.)64 GBMemory slots 2 SO DIMM (DDR4, 3200 MHz)General system informationMemory notes Dual channel supportLAN10/100/1,000 MBit/s Intel® I219LMIntegrated WLAN Intel WiFi 6E AX211 - WLAN, BT, SRD cat. 2BIOS version UEFI Specification 2.8BIOS features InsydeH2O BIOSAudio type On boardAudio codec Realtek ALC257Audio features2x built-in speakers (stereo)MIL-STD tested Yes, selected MIL-STD-810H tests passed.MIL-STD-810H test results are not a guarantee of future performance under identified test conditions.Accidental damage is not covered under standard international limited warranty.GraphicsBase unit LIFEBOOK E4412Graphics brand name Intel® UHD Graphics (with Single channel memory), Intel® Iris® Xe Graphics (with Dual channel memory) Graphics notes Shared memory depending on main memory size and operating systemInterfacesAudio: line-in / line-out1Internal microphones2x digital array microphones (optional)USB 3.2 Gen1 (5 Gbps) total2x Type-A (1 with Anytime USB charge functionality)Thunderbolt™ 4 total2x Type-C with USB4 (40 Gbps, Power Delivery (15W), DP 1.4 out)HDMI*************************************Ethernet (RJ-45) 1 (with status LED)Memory card slots 1 microSD 3.0 StandardmicroSD card: 2GBmicroSDHC card: 32GBmicroSDXC card: 2TBSpeed Class: up to UHS-I (104MB/s)SIM card slot 1 (Nano-SIM, only for models with configuration WWAN ready or with 4G LTE modules)eSIM card eSIM integrated in 4G LTE module - Dual SIM (DSSA) supportedKensington Lock support 1 - Recommendation: Kensington’s Micro Security SaverPort Replicator interfaces (optional)USB Type-C PR Thunderbolt™ 4 PRDC-in 1 (19V/90W required) 1 (20V/170W required)Power on switch11Audio: line-in / line-out11Audio: comments Combo jack for headset usage Combo jack for headset usageUSB 3.2 Gen1 (5 Gbps) total3x Type-A - 5V/0.9A, 4.5W1x Type-C - 15W---USB 3.2 Gen2 (10 Gbps) total---2x Type-A - 5 V/0.9 A, 4.5 W1x Type-A - 5 V/2.4 A, 12 W2x Type-C - 5 V/1.5 A, 4.5 W charging portUSB 4.0 Gen3 (20 Gbps) total---1x Type-C - TBT4 up to 60 W (PD v2.0-1.1), 5-20 V/3. 0Aupstream (PC), Intel AMT support (vPRO) to client1x Type-C - TBT4 up to 15 W (PD v2.0-1.1), 5 V/3.0 Adownstream, power output to peripheral DisplayPort1x v1.2 2x v1.4++VGA1---HDMI text****************************************************************************Interface Notes1x USB Type-C to Client - Up to 60 W (PD v2.0-1.1) poweroutput to client or 4.5W input 1x USB Type-C to Client - Thunderbolt™ 4 up to 60 W (PD v2.0-1.1), 5-20V/3.0A upstream (PC), Intel AMT support (vPRO)Kensington Lock support no1Ethernet (RJ-45) 1 (10/100/1000) 1 (10/100/1000 Mbit/s, 2,5 Gbps)Port Replicator interfaces (optional)Notes Number of simultaneous used displays and its possible resolutions and frequencies depend on mobile system anddisplay interface type.Please consult always also the manual of the connected client.Keyboard and pointing devicesSpill-resistant keyboard, Available with standard keyboard or backlit keyboardNumber of keyboard keys: 85, Keyboard pitch: 19 mm, Keyboard stroke: 1.7 mmMulti gesture touchpad with two mouse buttonsWireless technologiesAntennas 2 Dual band WLAN antennas, +2 4G LTE antennas optionalBluetooth v5.3 hardware ready but may run at lower version due to OS limitationIntegrated WLAN Intel WiFi 6E AX211 - WLAN, BT, SRD cat. 2WLAN encryption WPA/WPA2/WPA3 (Wi-Fi Protected Access)WLAN notes WiFi 6E is supported by Windows 11 OS only - Windows 10 OS supports WiFi 6 only.Import and usage according to country-specific regulations.Integrated LTE or UMTS(4G) LTE Quectel EM120R-GL (Cat.12) - eSIM integrated - UMTS,LTE(4G) LTE Quectel EM05-G (Cat.4) - eSIM integrated - UMTS,LTE(4G) LTE Sierra Wireless EM7421B (Cat.7) - eSIM integrated - UMTS,LTELTE/UMTS/GPS notes OptionalNFC NoGPS Embedded in 4G module if configured with WWANPower supplyAC Adapter20 V / 65 W (3.25 A), 100 V - 240 V, 50 Hz - 60 Hz, 3-pin (grounded) Type-C AC-Adapter slim&lightAC Adapter20 V / 65 W (3.25 A), 100 V - 240 V, 50 Hz - 60 Hz, 3-pin (grounded) Type-C AC-Adapter standard1st battery options Li-Ion battery 4-cell, 3,915 mAh, 60 Wh1st battery Lithium polymer battery 4-cell, 60 Wh, 3915 mAhBattery features Quick Charge: 80% in 1hRuntime 1st battery10h 30min (up to)Battery notes Battery runtime information is based on worldwide acknowledged BAPCo® MobileMark® 2018. Refer to www.bapco.com for additional details.The BAPCo® MobileMark® Benchmark provides results that enable direct product comparisons betweenmanufacturers. It does not guarantee any specific battery runtime which actually can be lower and may varydepending on product model, configuration, application and power management settings. The battery capacitydecreases slightly with every re-charge and over its lifetime.Noise emissionNoise emission Please refer to the Eco DeclarationDimensions / Weight / EnvironmentalDimensions (W x D x H)322 x 211 x 19.9 mm12.68 x 8.31 x 0.78 inchWeight 1.35 kg (starting from)Weight (lbs)starting from 2.98 lbsWeight notes Weight may vary depending on actual configurationOperating ambient temperature 5 - 35 °C (41 - 95 °F)ComplianceProduct LIFEBOOK E4412Model5E14A3Europe CECBGlobal TCO Certified 9.0ENERGY STAR® 8.0EPEAT® Gold (dedicated regions)Compliance link https:///sites/certificatesAdditional SoftwareAdditional software (preinstalled)Fujitsu Plugfree Network (network management utility)Fujitsu Anytime USB Charge UtilityFujitsu Battery UtilityFujitsu Function ManagerFujitsu DeskUpdate (driver and utility tool)Additional software (notes)Use of accompanying and/or additional Software is subject to proactive acceptance of the respective LicenseAgreements /EULAs/ Subscription and support terms of the Software manufacturer as applicable for the relevantSoftware whether preinstalled or optional. The software may only be available bundled with a software supportsubscription which – depending on the Software - may be subject to separate remuneration.ManageabilityManageability technology PXE Boot codeWake-on-LANManageability software DeskView ClientDeskView Instant BIOS ManagementSupported standards WMI (Windows Management Instrumentation)PXE (Preboot Execution Environment)DMI (Desktop Management Interface)SMBIOS (System Management BIOS)CIM (Common Information Model)BootP (made4you)Manageability link https:///global/products/computing/pc/manageability/SecurityPhysical Security Kensington Lock supportSystem and BIOS Security User and supervisor BIOS passwordUser Security Embedded fingerprint sensor (optional)TPM 2.0Hard disk passwordSecurity Notes The properties of the product provide a baseline for product security and therefore end-customer IT security.However, these properties are not sufficient on their own to protect the product from all existing threats, such asintrusion attempts, data exfiltration and other forms of cyberattacks. To customize security settings, please usethe configuration options as available for the respective product. During operation, the IT security of this productis within the responsibility of the respective administrator/end-user of the product. Please note, that Fujitsu as amanufacturer does not make any policy prescriptions or advocacy statements regarding IT security best practicesand/or general product operation.WarrantyWarranty period 1 year (for countries in EMEIA)Warranty type Bring-in Service / Collect & Return Service (depending on country)Warranty Terms & Conditions /warrantyDigital bug fixes Subject to availability and following their generic release for the product, bug fixes and function-preserving patchesfor product-related software (firmware) can be downloaded from the technical support at: https://support.ts.fujitsu.com/ free of charge by entering the respective product serial number. For application software supplied togetherwith the product, please directly refer to the support websites of the respective software manufacturer.Product Support - the perfect extensionRecommended Service9x5, Onsite Response Time: Next Business DaySpare Parts availability at least 5 years after shipment, for details see https:///Service Weblink/emeia/products/product-support-services/Recommended AccessoriesPLEVIER TACAN 14The Plevier Tacan 14 leather notebook bag provides a diverse range offeatures to optimize your carrier needs. With a shoulder strap, fast access pocket on the rear side and two compartments for your device and additional accessories, the bag provides multifunctional and protective space for your belongings. Its brown leather design creates a sleek finish to create a carrier that is high quality in both functionality and appearance.Order Code: S26391-F1193-L64Prestige Trolley 17The Fujitsu Prestige Trolley 17 protects and transports notebooks withup to 17 inch screens, along with clothes and toiletries. It is the perfectcompanion in a city environment or for overnight stays with four spacious compartments. Smooth running wheels and a telescopic handle ensure convenience, while the central section protects your notebook with shock-absorbing foam.Order Code: S26391-F1194-L130Top Case 14 (2021)The FUJITSU Accessories Top Case 14 protects notebooks with up to 14-inch screens. A padded top-loading notebook compartment with shock-absorbing foam provides excellent protection for your notebook. The bag is equipped with a front compartment for storage of power adapters, office supplies or personal items.Order Code: S26391-F20-L120Wireless Mouse WI860 BTCThe Wireless Mouse WI860 BTC can be paired with up to 3 different clients, 2x Bluetooth and 1x wireless USB Type-C dongle.With the blue optical sensor, it works on nearly all surfaces with an 3-step adjustable DPI selector (800/1600/2400).The mouse charges wirelessly through Qi or by USB Type-C cable.A utility button on the side is programmable. The default functions are optimized for Teams calls.Order Code:S26381-K474-L100ContactFujitsu Technology Solutions GmbH Website: 2023-11-27 EM-ENworldwide project for reducing burdens on the environment.Using our global know-how, we aim to contribute to the creation of a sustainable environment for future generations through IT.Please find further information at http://www./global/about/environmenttechnical specification with the maximum selection of components for the named system and not the detailed scope ofdelivery. The scope of delivery is defined by the selection of components at the time of ordering.Technical data is subject to modification and delivery subject to availability. Any liability that the data and illustrations are complete, actual or correct is excluded. Designations may be trademarks and/or copyrights of the respective owner, the use of which by third parties for their own purposes may infringe the rights of such owner.The overall product has been designed and manufactured for general office use, regular personal use and ordinary industrial use.More informationAll rights reserved, including intellectual property rights. Designations may be trademarks and/or copyrights of therespective owner, the use of which by third parties for their own purposes may infringe the rights of such owner. For further information see https:///global/about/resources/terms/ Copyright 2023 Fujitsu Technology Solutions GmbH。

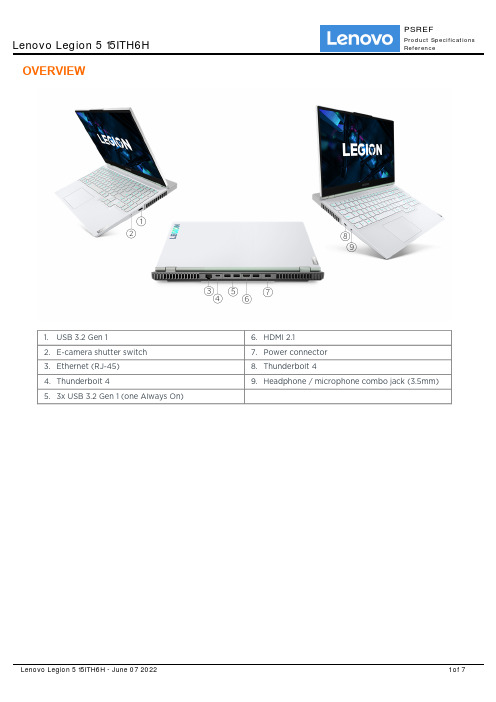

联想Legion 5 15ITH6H 产品规格参考 1 of 7

OVERVIEWB 3.2 Gen 1 6.HDMI2.12.E-camera shutter switch7.Power connector3.Ethernet (RJ-45)8.Thunderbolt 44.Thunderbolt 49.Headphone / microphone combo jack (3.5mm)5.3x USB 3.2 Gen 1 (one Always On)PERFORMANCEProcessorProcessor Family11th Generation Intel® Core™ i5 / i7 ProcessorProcessor**Operating SystemOperating System**Windows® 11 Pro 64••Windows 11 Home 64Windows 10 Pro 64••Windows 10 Home 64•No operating systemGraphicsGraphics**Monitor SupportMonitor SupportSupports up to 4 independent displays (native display and 3 external monitors via HDMI® and USB-C®)• HDMI supports up to 7680x4320@60Hz• USB-C supports up to 5120x3200@60HzChipsetChipsetIntel HM570 chipsetMemoryMax Memory[1]•Up to 32GB DDR4-2933 offering•Up to 32GB DDR4-3200 offeringMemory SlotsTwo DDR4 SO-DIMM slots, dual-channel capableMemory Type**•DDR4-2933•DDR4-3200Notes:1.The max memory is based on the test results with current Lenovo® memory offerings. The system may support more memory as the technology develops.StorageStorage Support[1]Up to two drives, 2x M.2 SSD• M.2 2242 SSD up to 512GB• M.2 2280 SSD up to 1TBStorage SlotTwo M.2 slots• One M.2 2280 PCIe® Gen 3x4 slot, supports M.2 2242/2280 SSD• One M.2 2280 PCIe Gen 4x4 slot, supports M.2 2242/2280 SSDStorage Type**Notes:1.The storage capacity supported is based on the test results with current Lenovo storage offerings. The system may support larger storage as the technology develops.Removable StorageOpticalNoneCard ReaderNo card readerMulti-MediaAudio ChipHigh Definition (HD) Audio, Realtek® ALC3306 codecSpeakersStereo speakers, 2W x2, Nahimic AudioMicrophoneDual array microphoneCameraHD 720p, with E-camera shutter, fixed focusBatteryBattery**Integrated Li-Polymer 60Wh battery, supports Rapid Charge Pro (charge up to 50% in 30min)••Integrated Li-Polymer 80Wh battery, supports Rapid Charge Pro (charge up to 50% in 30min)Max Battery Life[1]MobileMark® 2018: 7.5 hrNotes:1.All battery life claims are approximate maximum and based on results using the MobileMark 2014, MobileMark 2018, JEITA 2.0, continuous 1080p video playback (with 150nits brightness and default volume level) or Google Power Load Test (PLT) battery-life benchmark tests. Actual battery life will vary and depends on many factors such as product configuration and usage, software use, wireless functionality, power management settings, and screen brightness. The maximum capacity of the battery will decrease with time and use.Power AdapterPower Adapter**[1]•230W slim tip (3-pin) AC adapter, 100-240V, 50-60Hz•300W slim tip (3-pin) AC adapter, 100-240V, 50-60HzNotes:1.AC adapter offerings depend on the country.DisplayDisplay**[1]TouchscreenNon-touchNotes:California Electronic Waste Recycling Fee1.In California, per state law, Lenovo charges an electronic waste recycling fee on this covered device at the time of sale of the product.For more information, go to https:///Electronics/ConsumerInput DeviceKeyboard**•Phantom blue model: 6-row, multimedia Fn keys, numeric keypad, black keycap•Stingray model: 6-row, multimedia Fn keys, numeric keypad, moon white keycapKeyboard Backlight**Blue backlight••White backlight•4-Zone RGB backlightTouchpadButtonless Mylar® surface multi-touch touchpad, 69 x 104 mm (2.72 x 4.09 inches)Mechanical[1]Dimensions (WxDxH)362.56 x 260.61 x 22.5-25.75 mm (14.27 x 10.26 x 0.89-1.01 inches)Weight2.4 kg (5.3 lbs)Case Color**•Phantom blue (top), shadow black (bottom)•Stingray (top), dove grey (bottom)Surface TreatmentPaintingCase MaterialPC + ABS (top), PC + ABS (bottom)System LightingNo system lightingNotes:1.The system dimensions and weight vary depending on configurations.CONNECTIVITYNetworkOnboard EthernetGigabit Ethernet, 1x RJ-45WLAN + Bluetooth®[1][2]Wi-Fi® 6, 802.11ax 2x2 Wi-Fi + Bluetooth 5.1, M.2 cardNotes:1.Bluetooth 5.2 is hardware ready but may run at a lower version due to OS limitation2.Wi-Fi 6 full features might be limited by country-level restrictions.Ports[1]Standard Ports3x USB 3.2 Gen 1••1x USB 3.2 Gen 1 (Always On)•1x Thunderbolt™ 4 / USB4® 40Gbps (support data transfer and DisplayPort™ 1.4)1x Thunderbolt 4 / USB4 40Gbps (support data transfer, Power Delivery and DisplayPort 1.4)••1x HDMI 2.1•1x Ethernet (RJ-45)•1x Headphone / microphone combo jack (3.5mm)•1x Power connectorNotes:1.The transfer speed of following ports will vary and, depending on many factors, such as the processing speed of the host device, file attributes and other factors related to system configuration and your operating environment, will be slower than theoretical speed.USB 2.0: 480 Mbit/s;USB 3.2 Gen 1 (SuperSpeed USB 5Gbps, formerly USB 3.0 / USB 3.1 Gen 1): 5 Gbit/s;USB 3.2 Gen 2 (SuperSpeed USB 10Gbps, formerly USB 3.1 Gen 2): 10 Gbit/s;USB 3.2 Gen 2x2 (SuperSpeed USB 20Gbps): 20 Gbit/s;Thunderbolt 3/4: 40 Gbit/sSECURITY & PRIVACYSecuritySecurity ChipFirmware TPM 2.0 integrated in SoCFingerprint ReaderNo fingerprint readerBIOS Security•Power-on password•Supervisor passwordHard disk password•Other SecurityE-Camera shutterSERVICEWarrantyBase Warranty**[1]•1-year depot service1-year depot with 2-year system board service (Korea only)••2-year (1-yr battery) depot service•3-year (1-yr battery) depot service•No base warrantyNotes:1.More information of warranty policy, please access https:///warrantyENVIRONMENTALOperating EnvironmentTemperature[1]•At altitudes up to 2438 m (8,000 ft)- Operating: 5°C to 35°C (41°F to 95°F)- Storage: 5°C to 43°C (41°F to 109°F)•At altitudes above 2438 m (8,000 ft)- Maximum temperature when operating under the unpressurized condition: 31.3°C (88°F)HumidityOperating: 8% to 95% at wet-bulb temperature 23°C (73°F)••Storage: 5% to 95% at wet-bulb temperature 27°C (81°F)AltitudeMaximum altitude (without pressurization): 3048 m (10,000 ft)Notes:1.When you charge the battery, its temperature must be no lower than 10°C (50°F).ACCESSORIESBundled AccessoriesBundled AccessoriesLenovo Legion™ M300 RGB Gaming Mouse (USB connector)••NoneCERTIFICATIONSGreen CertificationsGreen Certifications•ErP Lot 3•RoHS compliant•Feature with ** means that only one offering listed under the feature is configured on selected models.Lenovo reserves the right to change specifications or other product information without notice. Lenovo is not •responsible for photographic or typographical errors. LENOVO PROVIDES THIS PUBLICATION “AS IS,”WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. Some jurisdictions do not allowdisclaimer of express or implied warranties in certain transactions, therefore this disclaimer may not apply to you.•The specifications on this page may not be available in all regions, and may be changed or updated without notice.。

思科Meraki MR42 802.11ac Wave 2无线接入点说明书