AD9581

ad修改原理库修改

ad修改原理库修改

AD修改原理库的修改流程大致如下:

1. 首先,在进行原理库修改之前,需要备份原始的原理库,以便出现问题时能够恢复。

2. 打开原理库文件,根据需要修改的内容进行编辑。

注意,要确保所做的修改与标题部分无关,以避免出现重复的文字。

3. 修改完毕后,保存原理库文件,并关闭编辑器。

4. 运行电子设计自动化(EDA)软件,例如Cadence或Altium Designer等,打开相关的电路设计项目。

5. 在EDA软件中导入修改后的原理库文件。

通常,会有特定

的导入功能或选项可以使用。

6. 检查导入后的原理库文件,确保所有修改都成功地应用到了相关的电路设计项目中。

7. 如果修改未生效或出现了问题,可以使用之前备份的原始原理库文件进行恢复,并重新进行修改。

需要注意的是,在进行任何修改之前,建议先阅读相关的文档和教程,以确保正确地进行修改操作。

同时,修改后的原理库应经过充分的测试和验证,以确保其功能和性能符合设计要求。

AD业务

电话广告AD业务1. AD业务概述AD业务也称为电话广告业务,一般由厂家(业务申请者,也称为业务用户)申请一个AD电话号码,然后可以在拨打此AD号码的电话中播放自己的广告。

普通电话用户拨打该AD号码,在听取了厂商的广告后,根据语音提示可以拨打自己想要拨打的电话号码,免费通话(此时该通话费用由厂商支付),或只付部分费用而其余的费用由厂家分担。

如果用户在拨打该电话时想进一步了解广告的内容或厂家的详细情况,则可按提示方便地获得,通话费用由厂家全部负责。

在AD业务中,一个AD业务号码可配置多条广告词,这样可几个厂家共同申请一个AD号码,然后按一定的比例负担这部分费用。

2. AD业务的功能AD业务除了具有减免电话费用的功能外,还具有以下的功能:2.1. 目的号码限制即对使用该业务的普通电话用户,对其可以呼出的目的地号码进行限制。

例如,只准拨打本地、只准拨打国内长途、只准拨打某些地区等。

2.2. 主叫用户地区限制如果业务用户只想在某些地区做广告,或者其销售范围限制在某些地区,则可以限制主叫用户(即普通电话用户)所在的地区,对来自其它地区的呼叫进行阻止。

2.3. 用户呼叫次数/费用的限制它是指业务电话用户可以事先规定在一段时间内(一天、一星期、或一个月)可以进行的呼叫次数或呼叫费用(二者选一)的最大限值,当到达此限值时,则不予普通电话用户接续,并向主叫用户送录音通知。

2.4. 话音提示它是向使用本业务的呼叫者发出提示,请求用户按照提示进一步操作,或向用户送录音通知,通知某种情况等。

即业务用户可要求主叫用户进行呼叫前必须拨入密码。

2.6. 费用分摊功能当业务用户不打算完全承担话费时,可以由主叫用户(业务使用者)和业务用户共同分摊通话费用。

2.7. 统计功能向业务用户随时提供详细的统计报告,包括,主叫用户收听广告的次数、该业务目前所累积的通话费用等。

电信部门定期将统计结果送给业务用户,业务用户也可随时通过电话查询统计结果。

杜月笙的名言上等人有本事没脾气

杜月笙的名言上等人有本事没脾气1.杜月笙有哪些名言杜月笙的名言:1、存钱再多不过金山银海,交情用起来好比天地难量! 2、不要怕被别人利用,人家利用你说明你还有用。

3、吃是实功,赌是对冲,嫖是落空。

4、杯中酒常满,桌上无虚席。

5、沦陷时上海无正义,胜利后上海无公道。

杜月笙(1888年——1951年),男,原名杜月生,后由章太炎建议,改名镛,号月笙,江苏川沙人(今上海浦东新区),是近代上海青帮中的一员。

1902年,杜月笙进入时为青帮上海龙头的黄金荣公馆,负责经营法租界的赌场“公兴俱乐部”。

1925年7月,杜月笙成立“三鑫公司”,垄断法租界鸦片提运。

1927年4月,杜月笙与黄金荣、张啸林组织中华共进会。

1929年,杜月笙任公董局华董,这是华人在法租界最高的位置。

1929年,杜月笙创办中汇银行,涉足上海金融业。

1949年4月,杜月笙前往香港。

1951年8月16日,于香港病逝,终年63岁。

扩展资料:杜月笙自始至终都热心支持中国人的斗争,并提出了六大主张:释放被捕学生;抚恤;道歉;取消印刷附律;取消码头捐;收回会审公廨(即收回司法权)。

在抗战中,杜月笙曾多年担任中国红十字会副会长,做过一些有益的慈善事业,曾设立了很多医院。

同时还投身教育,创设许多学校,如上海大公职业学校(江苏科技大学前身)等,向学校捐款。

特别是他任副会长时正值抗战前后,于救助伤兵输送物资、建立抵抗部队。

抗战开始后,杜月笙参加了上海各界抗敌后援会,任主席团成员兼筹募委员会主任。

仅月余时间,杜月笙主持的筹募会就筹集到救国捐款150余万元,有力地支援了前方的抗战。

1938年春,中国红十字会总会理事室迁移香港,杜月笙亲自主持工作,并设立总办e799bee5baa6e59b9ee7ad9431333365666239事处,以接受海外捐助的物资,并同时筹措救护事业的经费。

1942年,杜月笙筹建了重庆医院,是当时最先进的战时后方医院,受到舆论的称赞。

抗战胜利后,杜月笙返回上海,督促上海复员工作,并协助恢复、加强了上海红十字会分会的组织。

AD及DA实验报告

微机原理及接口技术之AD及DA实验一. 实验目的:1. 了解A/D芯片ADC0809和D/A芯片DAC0832的电气性能;外围电路的应用性搭建及有关要点和注意事项;与CPU的接口和控制方式;相关接口参数的确定等;2. 了解数据采集系统中采样保持器的作用和采样频率对拾取信号失真度的影响, 了解香农定理;3.了解定时计数器Intel 8253和中断控制器Intel 8259的原理、工作模式以及控制方式, 训练控制定时器和中断控制器的方法, 并学习如何编写中断程序。

4.熟悉X86汇编语言的程序结构和编程方法, 训练深入芯片编写控制程序的编程能力。

二. 实验项目:1. 完成0~5v的单极性输入信号的A/D转换, 并与实际值(数字电压表的测量值)比较, 确定误差水平。

要求全程至少10个点。

2.完成-5v~+5v的双极性输入信号的A/D转换, 并与实际值(数字电压表的测量值)比较, 确定误差水平。

要求全程至少20个点。

3.把0~FF的数据送入DAC0832并完成D/A转换, 然后用数字电压表测量两个模拟量输出口(OUT1为单极性, OUT2双极性)的输出值, 并与计算值比较, 确定误差水平。

要求全程至少16个点。

三. 仪器设备:Aedk-ACT实验箱1套(附电源线1根、通信线1根、实验插接线若干、跳线子若干);台式多功能数字表1台(附电源线1根、表笔线1付(2根)、);PC机1台;实验用软件: Windows98+LcaACT(IDE)。

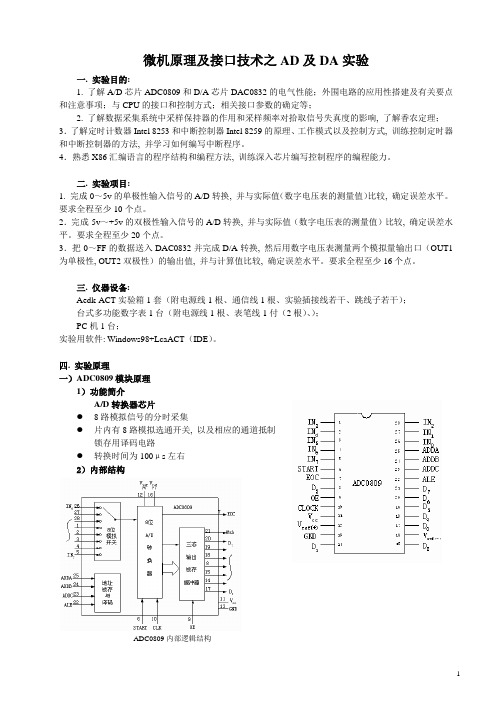

四. 实验原理一)ADC0809模块原理1)功能简介A/D转换器芯片●8路模拟信号的分时采集●片内有8路模拟选通开关, 以及相应的通道抵制锁存用译码电路●转换时间为100μs左右2)内部结构ADC0809内部逻辑结构1图中多路开关可选通8个模拟通道, 允许8路模拟量分时输入, 共用一个A/D转换器进行转换, 这是一种经济的多路数据采集方法。

地址锁存与译码电路完成对A.B.C 3个地址位进行锁存和译码, 其译码输出用于通道选择, 其转换结果通过三态输出锁存器存放、输出, 因此可以直接与系统数据总线相连。

电气检测技术(新9)AD转换原理

25

1) ai为输入数字量,接CPU的DBUS。可选用 不同的代码,常用的DAC采用二进制码。

2)触发器构成的缓冲寄存器(锁存器),锁存 CPU送来的数据。得到和暂存对应的输出电压。

压分辨率为5V/255≈20mV;10位DAC的分辨率为 5V/1023≈5mV。 位数越多,分辩率越高,转换的精度也越高。

2

测量系统用ADC的主要类型:

1、适用于数字仪器、仪表的ADC; 这类产品多半设计成BCD码输出,转换速度 一般较低(每秒转换十几次)。

2、适用测量系统作模/数接口部件的ADC。 这类产品的转换速度较高,多半以二进制代码 (含双极性代码)输出,常设计成带有三态 输出锁存器,能方便实现与微处理器直接接口。

18

3、应用

产品种类多,转换能力有很大的差异; 有8Bit、10Bit、12Bit、14Bit、16Bit等。 在这些不同转换能力的ADC中,又包括有并行输 出的ADC,以及输出为串行的ADC。 常见的8Bit的有NS公司的ADC0801、DC0802、 ADC0803、ADC0804系列及ADC0808、 ADC0809系列 10Bit有AD公司的AD574,MAXIM公司 MAX1425、MAX1426 12Bit有AD公司的AD7888,MAXIM公司 MAX170、MAX172

有些DAC芯片内无缓冲寄存器,此时须外接, 如74LS273、373等锁存器。

26

3) 模拟开关按输入的数字量接通或断开解码 网相应支路的电流或电压;对它的要求比接通或 断开开关量的电子开关更高。希望动作快;接通 电阻很小,断开电阻很大,且稳定性好。在DAC 中有电压型开关和恒流型电流开关之分。

AD元件库中常用元件

AD软件元件库中常用元件Altium下Miscellaneous Devices.Intlib元件库中常用元件有:电阻系列(res*)排组(res pack*)电感(inductor*)电容(cap*,capacitor*)二极管系列(diode*,d*)三极管系列(npn*,pnp*,mos*,MOSFET*,MESFET*,jfet*,IGBT*)运算放大器系列(op*)继电器(relay*)8位数码显示管(dpy*)电桥(bri*bridge)光电耦合器( opto* ,optoisolator )光电二极管、三极管(photo*)模数转换、数模转换器(adc-8,dac-8)晶振(xtal)电源(battery)喇叭(speaker)麦克风(mic*)小灯泡(lamp*)响铃(bell)天线(antenna)保险丝(fuse*)开关系列(sw*)跳线(jumper*)变压器系列(trans*)晶振(crystal oscillator)的元件库名称是Miscellaneous Devices.Intlib, 在search栏中输入*soc 即可。

Altium下Miscellaneous connectors.Intlib元件库中常用元件有:(con*,connector*)(header*)(MHDR*)定时器NE555P 在库TI analog timer circit.Intlib中电阻AXIAL无极性电容RAD电解电容RB-电位器VR二极管DIODE三极管TO电源稳压块78和79系列TO-126H和TO-126V场效应管和三极管一样整流桥D-44 D-37 D-46单排多针插座CON SIP双列直插元件DIP晶振XTAL1电阻:RES1,RES2,RES3,RES4;封装属性为axial系列无极性电容:cap;封装属性为RAD-0.1到rad-0.4电解电容:electroi;封装属性为rb.2/.4到rb.5/1.0电位器:pot1,pot2;封装属性为vr-1到vr-5二极管:封装属性为diode-0.4(小功率)diode-0.7(大功率)三极管:常见的封装属性为to-18(普通三极管)to-22(大功率三极管)to-3(大功率达林顿管)电源稳压块有78和79系列;78系列如7805,7812,7820等79系列有7905,7912,7920等常见的封装属性有to126h和to126v整流桥:BRIDGE1,BRIDGE2: 封装属性为D系列(D-44,D-37,D-46)电阻: AXIAL0.3-AXIAL0.7 其中0.4-0.7指电阻的长度,一般用AXIAL0.4瓷片电容:RAD0.1-RAD0.3. 其中0.1-0.3指电容大小,一般用RAD0.1电解电容:RB.1/.2-RB.4/.8 其中.1/.2-.4/.8指电容大小.一般<100uF用RB.1/.2,100uF-470uF用RB.2/.4,>470uF用RB.3/.6二极管: DIODE0.4-DIODE0.7 其中0.4-0.7指二极管长短,一般用DIODE0.4发光二极管:RB.1/.2集成块: DIP8-DIP40, 其中8-40指有多少脚,8脚的就是DIP8贴片电阻0603表示的是封装尺寸与具体阻值没有关系但封装尺寸与功率有关通常来说0201 1/20W0402 1/16W0603 1/10W0805 1/8W1206 1/4W电容电阻外形尺寸与封装的对应关系是:0402=1.0x0.50603=1.6x0.80805=2.0x1.21206=3.2x1.61210=3.2x2.51812=4.5x3.22225=5.6x6.5关于零件封装我们在前面说过,除了DEVICE.LIB库中的元件外,其它库的元件都已经有了固定的元件封装,这是因为这个库中的元件都有多种形式:以晶体管为例说明一下:晶体管是我们常用的的元件之一,在DEVICE.LIB库中,简简单单的只有NPN与PNP之分,但实际上,如果它是NPN的2N3055那它有可能是铁壳子的TO—3,如果它是NPN的2N3054,则有可能是铁壳的TO-66或TO-5,而学用的CS9013,有TO-92A,TO-92B,还有TO-5,TO-46,TO-52等等,千变万化.还有一个就是电阻,在DEVICE库中,它也是简单地把它们称为RES1和RES2,不管它是100Ω还是470KΩ都一样,对电路板而言,它与欧姆数根本不相关,完全是按该电阻的功率数来决定的我们选用的1/4W和甚至1/2W的电阻,都可以用AXIAL0.3元件封装,而功率数大一点的话,可用AXIAL0.4,AXIAL0.5等等.现将常用的元件封装整理如下:电阻类及无极性双端元件AXIAL0.3-AXIAL1.0无极性电容RAD0.1-RAD0.4有极性电容RB.2/.4-RB.5/1.0二极管DIODE0.4及DIODE0.7石英晶体振荡器XTAL1晶体管、FET、UJT TO-xxx(TO-3,TO-5)可变电阻(POT1、POT2) VR1-VR5当然,我们也可以打开C:\Client98\PCB98\library\advpcb.lib库来查找所用零件的对应封装.这些常用的元件封装,大家最好能把它背下来,这些元件封装,大家可以把它拆分成两部分来记如电阻AXIAL0.3可拆成AXIAL和0.3,AXIAL翻译成中文就是轴状的,0.3则是该电阻在印刷电路板上的焊盘间的距离也就是300mil(因为在电机领域里,是以英制单位为主的.同样的,对于无极性的电容,RAD0.1-RAD0.4也是一样;对有极性的电容如电解电容,其封装为R B.2/.4,RB.3/.6等,其中“.2”为焊盘间距,“.4”为电容圆筒的外径.对于晶体管,那就直接看它的外形及功率,大功率的晶体管,就用TO—3,中功率的晶体管,如果是扁平的,就用TO-220,如果是金属壳的,就用TO-66,小功率的晶体管,就用TO-5,TO-46,TO-92A等都可以,反正它的管脚也长,弯一下也可以.对于常用的集成IC电路,有DIPxx,就是双列直插的元件封装,DIP8就是双排,每排有4个引脚,两排间距离是300mil,焊盘间的距离是100mil.SIPxx就是单排的封装.等等.值得我们注意的是晶体管与可变电阻,它们的包装才是最令人头痛的,同样的包装,其管脚可不一定一样.例如,对于TO-92B之类的包装,通常是1脚为E(发射极),而2脚有可能是B极(基极),也可能是C(集电极);同样的,3脚有可能是C,也有可能是B,具体是那个,只有拿到了元件才能确定.因此,电路软件不敢硬性定义焊盘名称(管脚名称),同样的,场效应管,MOS管也可以用跟晶体管一样的封装,它可以通用于三个引脚的元件.Q1-B,在PCB里,加载这种网络表的时候,就会找不到节点(对不上).在可变电阻上也同样会出现类似的问题;在原理图中,可变电阻的管脚分别为1、W、及2, 所产生的网络表,就是1、2和W,在PCB电路板中,焊盘就是1,2,3.当电路中有这两种元件时,就要修改PCB与SCH之间的差异最快的方法是在产生网络表后,直接在网络表中,将晶体管管脚改为1,2,3;将可变电阻的改成与电路板元件外形一样的1,2,3即可。

ad采集单片机课程设计

ad采集单片机课程设计一、课程目标知识目标:1. 让学生理解单片机的基本原理和功能,掌握AD采集的相关知识;2. 学会使用单片机进行AD转换,并能阅读相关程序代码;3. 了解AD采集在实际应用中的重要性,如传感器数据采集、模拟信号处理等。

技能目标:1. 培养学生动手实践能力,能够独立完成单片机AD采集电路的设计与搭建;2. 提高学生编程能力,学会编写和调试AD采集相关程序;3. 培养学生团队协作和问题解决能力,能够共同完成具有一定难度的AD采集项目。

情感态度价值观目标:1. 激发学生对电子技术和单片机应用的兴趣,培养其探索精神和创新意识;2. 培养学生严谨的科学态度,注重实验数据的准确性和可靠性;3. 增强学生的环保意识,了解电子产品在实际应用中应遵循的环保原则。

课程性质:本课程为实践性较强的课程,注重理论知识与实践操作相结合,旨在培养学生的动手能力、编程能力和实际应用能力。

学生特点:学生具有一定的单片机基础知识,对AD采集相关内容感兴趣,但实践经验不足。

教学要求:教师需采用启发式教学,引导学生主动探索,注重理论与实践相结合,提高学生的实践操作能力。

同时,关注学生的个体差异,给予个性化指导,确保课程目标的实现。

在教学过程中,将目标分解为具体的学习成果,便于教学设计和评估。

二、教学内容1. 单片机基础回顾:包括单片机的结构、工作原理、指令系统等,为学生后续学习AD采集打下基础。

相关教材章节:第一章 单片机基础2. AD转换原理及芯片选型:介绍AD转换的基本原理,各类AD转换芯片的特点和应用。

相关教材章节:第二章 AD转换技术3. 单片机与AD转换芯片的接口技术:讲解单片机与AD转换芯片的连接方法,电路设计和编程技巧。

相关教材章节:第三章 单片机接口技术4. AD采集程序设计与调试:学习AD采集程序的设计方法,掌握编程工具和调试技巧。

相关教材章节:第四章 单片机编程与调试5. 实践项目:设计并实现一个简单的AD采集系统,如温度传感器数据采集、光照强度检测等。

AD9880中文数据手册

AD9880中文数据手册全文翻译自:ADI公司AD9880B 数据手册英文AD9880数据手册版本号: Rev. 0简单描述AD9880是一个集模拟接口和HDMI接口于一体单个芯片,并且还支持HDCP。

1.1模拟接口AD9880是一个真正8位的150MSPS的单片模拟接口,用于对复合视频(YPbPr)和RGB图像信号的采集。

有150MSPS的编码速率和330MHz的带宽,所以支持全部HDTV 格式(最高1080p)和最高SXGA(1280*1024@75Hz)的FED。

Ad9880模拟接口内部包含有一个带1.25V基准的3态ADC,一个锁相环(PLL),增益、偏置、箝位控制均可编程。

用户只需提供1.8V和3.3V电压、模拟输入和Hsync信号。

三态CMOS输出的供电范围1.8V到3.3V。

片内锁相环从Hsync信号可以产生像素时钟信号,输出频率从12MHz到150MHz。

时钟抖动(clock jitter)在150MHz情况下,小于700ps p-p。

AD9880还能为复合同步以及sync-on-green(SOG)提供全同步处理。

1.2数字接口AD9880接收器符合HDMI 1.1规范,支持所有HDTV格式和显示公式。

The receiver features an intrapair skew tolerance of up to one full clock cycle。

在HDCP方案下,显示器可以接收加密的视频信号。

AD9880可以应用于视频接收的认证,在接收端对编码后的视频信号进行解密。

借助于先进的CMOS工艺,AD9880提供100管脚的LQFP表贴无铅封装。

温度范围0-70摄氏度。

2.管脚功能描述Table 5. pin function descriptions管脚号说明输入管脚R AIN0红色模拟输入通道0G AIN0绿色模拟输入通道0B AIN0蓝色模拟输入通道0R AIN0红色模拟输入通道1G AIN0绿色模拟输入通道1B AIN0蓝色模拟输入通道1红、绿、蓝三个模拟色彩信号输入通道都是高阻抗输入。

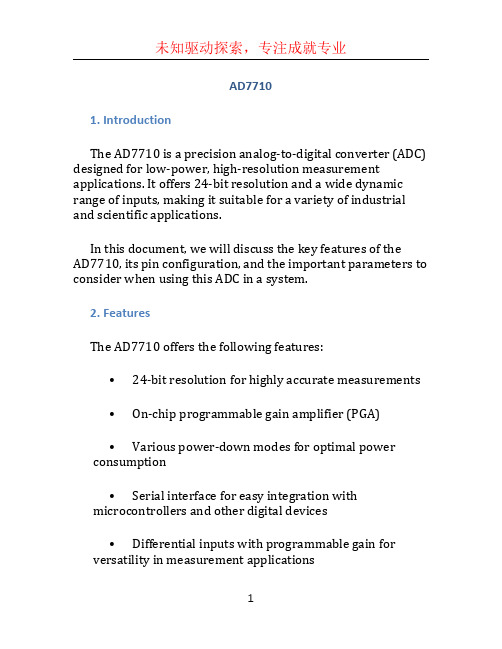

AD7710

AD77101. IntroductionThe AD7710 is a precision analog-to-digital converter (ADC) designed for low-power, high-resolution measurement applications. It offers 24-bit resolution and a wide dynamic range of inputs, making it suitable for a variety of industrial and scientific applications.In this document, we will discuss the key features of theAD7710, its pin configuration, and the important parameters to consider when using this ADC in a system.2. FeaturesThe AD7710 offers the following features:•24-bit resolution for highly accurate measurements•On-chip programmable gain amplifier (PGA)•Various power-down modes for optimal power consumption•Serial interface for easy integration with microcontrollers and other digital devices•Differential inputs with programmable gain for versatility in measurement applications•Internal reference voltage for precisionmeasurements•High-speed, high-resolution sigma-delta ADC architecture for accuracy and noise immunity3. Pin ConfigurationThe AD7710 has a total of 20 pins, each serving a specific purpose. The pins are organized as follows:1.AGND: Analog ground reference.2.IN-: Negative input terminal.3.IN+: Positive input terminal.4.AINCOM: Common-mode voltage reference fordifferential inputs.5.VREF/BUF: Reference voltage input or buffer output.6.DVDD: Digital supply voltage.7.DB6-DB0: Data bus for serial communication.8.DIN: Serial data input.9.DOUT: Serial data output.10.SCLK: Serial clock input.11.CS: Chip select input.12.DRDY: Data ready output.The remaining pins include power supply pins and auxiliary pins for better integration with the system.4. Important ParametersWhen using the AD7710, it is crucial to consider the following parameters to ensure accurate and reliable measurements:4.1 ResolutionThe AD7710 offers 24-bit resolution, allowing for precise measurements with a wide dynamic range.4.2 Programmable Gain Amplifier (PGA)The on-chip PGA allows for signal amplification and attenuation, enabling the ADC to measure both small and large input signals accurately.4.3 Power ConsumptionThe AD7710 offers various power-down modes to minimize power consumption in low-power applications. It is important to consider the power requirements and choose the appropriate mode to optimize energy efficiency.4.4 Serial InterfaceThe AD7710 features a serial interface that simplifies integration with microcontrollers and other digital devices. It is crucial to understand the timing diagrams and communication protocols to ensure successful data transfer.4.5 Differential Inputs with Programmable GainThe differential inputs of the AD7710 allow for precise measurements in differential modes, and the programmable gain feature enhances versatility by providing adjustable input ranges.4.6 Internal Reference VoltageThe AD7710 includes an internal reference voltage that ensures precise measurements. It is essential to consider the characteristics and stability of the internal reference when designing the system.4.7 Sigma-Delta ADC ArchitectureThe high-speed, high-resolution sigma-delta ADC architecture of the AD7710 offers accurate measurements with excellent noise immunity. It is important to understand the implications of this architecture on the system’s performance and design.ConclusionThe AD7710 is a precision ADC designed for high-resolution measurement applications. With its 24-bit resolution, programmable gain amplifier, and serial interface, it offers versatility and accuracy. Understanding its pin configuration and important parameters ensures optimal integration and reliable measurements in various systems.For detailed information on the AD7710, including electrical characteristics, timing diagrams, and programming instructions, please refer to the official datasheet provided by the manufacturer.。

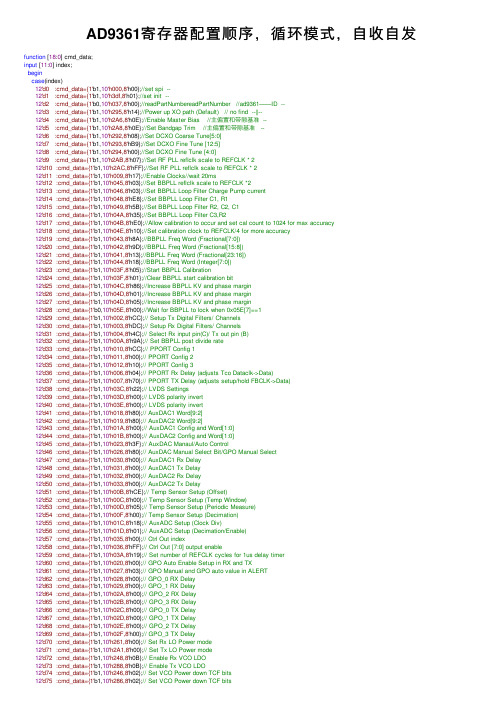

AD9361寄存器配置顺序,循环模式,自收自发

AD9361寄存器配置顺序,循环模式,⾃收⾃发function [18:0] cmd_data;input [11:0] index;begincase(index)12'd0 :cmd_data={1'b1,10'h000,8'h00};//set spi --12'd1 :cmd_data={1'b1,10'h3df,8'h01};//set init --12'd2 :cmd_data={1'b0,10'h037,8'h00};//readPartNumbereadPartNumber //ad9361——ID --12'd3 :cmd_data={1'b1,10'h295,8'h14};//Power up XO path (Default) // no find --||--12'd4 :cmd_data={1'b1,10'h2A6,8'h0E};//Enable Master Bias //主偏置和带隙基准 --12'd5 :cmd_data={1'b1,10'h2A8,8'h0E};//Set Bandgap Trim //主偏置和带隙基准 --12'd6 :cmd_data={1'b1,10'h292,8'h08};//Set DCXO Coarse Tune[5:0]12'd7 :cmd_data={1'b1,10'h293,8'hB9};//Set DCXO Fine Tune [12:5]12'd8 :cmd_data={1'b1,10'h294,8'h00};//Set DCXO Fine Tune [4:0]12'd9 :cmd_data={1'b1,10'h2AB,8'h07};//Set RF PLL reflclk scale to REFCLK * 212'd10 :cmd_data={1'b1,10'h2AC,8'hFF};//Set RF PLL reflclk scale to REFCLK * 212'd11 :cmd_data={1'b1,10'h009,8'h17};//Enable Clocks//wait 20ms12'd12 :cmd_data={1'b1,10'h045,8'h03};//Set BBPLL reflclk scale to REFCLK *212'd13 :cmd_data={1'b1,10'h046,8'h03};//Set BBPLL Loop Filter Charge Pump current12'd14 :cmd_data={1'b1,10'h048,8'hE8};//Set BBPLL Loop Filter C1, R112'd15 :cmd_data={1'b1,10'h049,8'h5B};//Set BBPLL Loop Filter R2, C2, C112'd16 :cmd_data={1'b1,10'h04A,8'h35};//Set BBPLL Loop Filter C3,R212'd17 :cmd_data={1'b1,10'h04B,8'hE0};//Allow calibration to occur and set cal count to 1024 for max accuracy12'd18 :cmd_data={1'b1,10'h04E,8'h10};//Set calibration clock to REFCLK/4 for more accuracy12'd19 :cmd_data={1'b1,10'h043,8'h8A};//BBPLL Freq Word (Fractional[7:0])12'd20 :cmd_data={1'b1,10'h042,8'h9D};//BBPLL Freq Word (Fractional[15:8])12'd21 :cmd_data={1'b1,10'h041,8'h13};//BBPLL Freq Word (Fractional[23:16])12'd22 :cmd_data={1'b1,10'h044,8'h18};//BBPLL Freq Word (Integer[7:0])12'd23 :cmd_data={1'b1,10'h03F,8'h05};//Start BBPLL Calibration12'd24 :cmd_data={1'b1,10'h03F,8'h01};//Clear BBPLL start calibration bit12'd25 :cmd_data={1'b1,10'h04C,8'h86};//Increase BBPLL KV and phase margin12'd26 :cmd_data={1'b1,10'h04D,8'h01};//Increase BBPLL KV and phase margin12'd27 :cmd_data={1'b1,10'h04D,8'h05};//Increase BBPLL KV and phase margin12'd28 :cmd_data={1'b0,10'h05E,8'h00};//Wait for BBPLL to lock when 0x05E[7]==112'd29 :cmd_data={1'b1,10'h002,8'hCC};// Setup Tx Digital Filters/ Channels12'd30 :cmd_data={1'b1,10'h003,8'hDC};// Setup Rx Digital Filters/ Channels12'd31 :cmd_data={1'b1,10'h004,8'h4C};// Select Rx input pin(C)/ Tx out pin (B)12'd32 :cmd_data={1'b1,10'h00A,8'h9A};// Set BBPLL post divide rate12'd33 :cmd_data={1'b1,10'h010,8'hCC};// PPORT Config 112'd34 :cmd_data={1'b1,10'h011,8'h00};// PPORT Config 212'd35 :cmd_data={1'b1,10'h012,8'h10};// PPORT Config 312'd36 :cmd_data={1'b1,10'h006,8'h04};// PPORT Rx Delay (adjusts Tco Dataclk->Data)12'd37 :cmd_data={1'b1,10'h007,8'h70};// PPORT TX Delay (adjusts setup/hold FBCLK->Data)12'd38 :cmd_data={1'b1,10'h03C,8'h22};// LVDS Settings12'd39 :cmd_data={1'b1,10'h03D,8'h00};// LVDS polarity invert12'd40 :cmd_data={1'b1,10'h03E,8'h00};// LVDS polarity invert12'd41 :cmd_data={1'b1,10'h018,8'h80};// AuxDAC1 Word[9:2]12'd42 :cmd_data={1'b1,10'h019,8'h80};// AuxDAC2 Word[9:2]12'd43 :cmd_data={1'b1,10'h01A,8'h00};// AuxDAC1 Config and Word[1:0]12'd44 :cmd_data={1'b1,10'h01B,8'h00};// AuxDAC2 Config and Word[1:0]12'd45 :cmd_data={1'b1,10'h023,8'h3F};// AuxDAC Manaul/Auto Control12'd46 :cmd_data={1'b1,10'h026,8'h80};// AuxDAC Manual Select Bit/GPO Manual Select12'd47 :cmd_data={1'b1,10'h030,8'h00};// AuxDAC1 Rx Delay12'd48 :cmd_data={1'b1,10'h031,8'h00};// AuxDAC1 Tx Delay12'd49 :cmd_data={1'b1,10'h032,8'h00};// AuxDAC2 Rx Delay12'd50 :cmd_data={1'b1,10'h033,8'h00};// AuxDAC2 Tx Delay12'd51 :cmd_data={1'b1,10'h00B,8'hCE};// Temp Sensor Setup (Offset)12'd52 :cmd_data={1'b1,10'h00C,8'h00};// Temp Sensor Setup (Temp Window)12'd53 :cmd_data={1'b1,10'h00D,8'h05};// Temp Sensor Setup (Periodic Measure)12'd54 :cmd_data={1'b1,10'h00F,8'h00};// Temp Sensor Setup (Decimation)12'd55 :cmd_data={1'b1,10'h01C,8'h18};// AuxADC Setup (Clock Div)12'd56 :cmd_data={1'b1,10'h01D,8'h01};// AuxADC Setup (Decimation/Enable)12'd57 :cmd_data={1'b1,10'h035,8'h00};// Ctrl Out index12'd58 :cmd_data={1'b1,10'h036,8'hFF};// Ctrl Out [7:0] output enable12'd59 :cmd_data={1'b1,10'h03A,8'h19};// Set number of REFCLK cycles for 1us delay timer12'd60 :cmd_data={1'b1,10'h020,8'h00};// GPO Auto Enable Setup in RX and TX12'd61 :cmd_data={1'b1,10'h027,8'h03};// GPO Manual and GPO auto value in ALERT12'd62 :cmd_data={1'b1,10'h028,8'h00};// GPO_0 RX Delay12'd63 :cmd_data={1'b1,10'h029,8'h00};// GPO_1 RX Delay12'd64 :cmd_data={1'b1,10'h02A,8'h00};// GPO_2 RX Delay12'd65 :cmd_data={1'b1,10'h02B,8'h00};// GPO_3 RX Delay12'd66 :cmd_data={1'b1,10'h02C,8'h00};// GPO_0 TX Delay12'd67 :cmd_data={1'b1,10'h02D,8'h00};// GPO_1 TX Delay12'd68 :cmd_data={1'b1,10'h02E,8'h00};// GPO_2 TX Delay12'd69 :cmd_data={1'b1,10'h02F,8'h00};// GPO_3 TX Delay12'd70 :cmd_data={1'b1,10'h261,8'h00};// Set Rx LO Power mode12'd71 :cmd_data={1'b1,10'h2A1,8'h00};// Set Tx LO Power mode12'd76 :cmd_data={1'b1,10'h249,8'h8E};// Set VCO cal length12'd77 :cmd_data={1'b1,10'h289,8'h8E};// Set VCO cal length12'd78 :cmd_data={1'b1,10'h23B,8'h80};// Enable Rx VCO cal12'd79 :cmd_data={1'b1,10'h27B,8'h80};// Enable Tx VCO cal12'd80 :cmd_data={1'b1,10'h243,8'h0D};// Set Rx prescaler bias12'd81 :cmd_data={1'b1,10'h283,8'h0D};// Set Tx prescaler bias12'd82 :cmd_data={1'b1,10'h23D,8'h00};// Clear Half VCO cal clock setting12'd83 :cmd_data={1'b1,10'h27D,8'h00};// Clear Half VCO cal clock setting12'd84 :cmd_data={1'b1,10'h015,8'h04};// Set Dual Synth mode bit12'd85 :cmd_data={1'b1,10'h014,8'h0D};// Set Force ALERT State bit12'd86 :cmd_data={1'b1,10'h013,8'h01};// Set ENSM FDD mode,// wait 1 ms12'd87 :cmd_data={1'b1,10'h23D,8'h04};// Start RX CP cal12'd88 :cmd_data={1'b0,10'h244,8'h00};// Wait for CP cal to complete when 0x244[7]==112'd89 :cmd_data={1'b1,10'h27D,8'h04};// Start TX CP cal12'd90 :cmd_data={1'b0,10'h284,8'h00};// Wait for CP cal to complete when 0x284[7]==112'd91 :cmd_data={1'b1,10'h23A,8'h4A};// Set VCO Output level[3:0]12'd92 :cmd_data={1'b1,10'h239,8'hC0};// Set Init ALC Value[3:0] and VCO Varactor[3:0]12'd93 :cmd_data={1'b1,10'h242,8'h0D};// Set VCO Bias Tcf[1:0] and VCO Bias Ref[2:0]12'd94 :cmd_data={1'b1,10'h238,8'h70};// Set VCO Cal Offset[3:0]12'd95 :cmd_data={1'b1,10'h245,8'h00};// Set VCO Cal Ref Tcf[2:0]12'd96 :cmd_data={1'b1,10'h251,8'h09};// Set VCO Varactor Reference[3:0]12'd97 :cmd_data={1'b1,10'h250,8'h70};// Set VCO Varactor Ref Tcf[2:0] and VCO Varactor Offset[3:0] 12'd98 :cmd_data={1'b1,10'h23B,8'h93};// Set Synth Loop Filter charge pump current (Icp)12'd99 :cmd_data={1'b1,10'h23E,8'hF4};// Set Synth Loop Filter C2 and C112'd100 :cmd_data={1'b1,10'h23F,8'hDF};// Set Synth Loop Filter R1 and C312'd101 :cmd_data={1'b1,10'h240,8'h0A};// Set Synth Loop Filter R312'd102 :cmd_data={1'b1,10'h27A,8'h4A};// Set VCO Output level[3:0]12'd103 :cmd_data={1'b1,10'h279,8'hC0};// Set Init ALC Value[3:0] and VCO Varactor[3:0]12'd104 :cmd_data={1'b1,10'h282,8'h0D};// Set VCO Bias Tcf[1:0] and VCO Bias Ref[2:0]12'd105 :cmd_data={1'b1,10'h278,8'h70};// Set VCO Cal Offset[3:0]12'd106 :cmd_data={1'b1,10'h285,8'h00};// Set VCO Cal Ref Tcf[2:0]12'd107 :cmd_data={1'b1,10'h291,8'h09};// Set VCO Varactor Reference[3:0]12'd108 :cmd_data={1'b1,10'h290,8'h70};// Set VCO Varactor Ref Tcf[2:0] and VCO Varactor Offset[3:0] 12'd109 :cmd_data={1'b1,10'h27B,8'h93};// Set Synth Loop Filter charge pump current (Icp)12'd110 :cmd_data={1'b1,10'h27E,8'hF4};// Set Synth Loop Filter C2 and C112'd111 :cmd_data={1'b1,10'h27F,8'hDF};// Set Synth Loop Filter R1 and C312'd112 :cmd_data={1'b1,10'h280,8'h0A};// Set Synth Loop Filter R312'd113 :cmd_data={1'b1,10'h233,8'h72};// Write Rx Synth Fractional Freq Word[7:0]12'd114 :cmd_data={1'b1,10'h234,8'h62};// Write Rx Synth Fractional Freq Word[15:8]12'd115 :cmd_data={1'b1,10'h235,8'h27};// Write Rx Synth Fractional Freq Word[22:16]12'd116 :cmd_data={1'b1,10'h232,8'h00};// Write Rx Synth Integer Freq Word[10:8]12'd117 :cmd_data={1'b1,10'h231,8'hBA};// Write Rx Synth Integer Freq Word[7:0]12'd118 :cmd_data={1'b1,10'h005,8'h11};// Set LO divider setting12'd119 :cmd_data={1'b1,10'h273,8'h72};// Write Tx Synth Fractional Freq Word[7:0]12'd120 :cmd_data={1'b1,10'h274,8'h62};// Write Tx Synth Fractional Freq Word[15:8]12'd121 :cmd_data={1'b1,10'h275,8'h27};// Write Tx Synth Fractional Freq Word[22:16]12'd122 :cmd_data={1'b1,10'h272,8'h00};// Write Tx Synth Integer Freq Word[10:8]12'd123 :cmd_data={1'b1,10'h271,8'hBA};// Write Tx Synth Integer Freq Word[7:0] (starts VCO cal)12'd124 :cmd_data={1'b1,10'h005,8'h11};// Set LO divider setting12'd125 :cmd_data={1'b0,10'h247,8'h00};// Check RX RF PLL lock status (0x247[1]==1 is locked)12'd126 :cmd_data={1'b0,10'h287,8'h00};// Check TX RF PLL lock status (0x287[1]==1 is locked)12'd127 :cmd_data={1'b1,10'h13F,8'h02};// Start Clock12'd128 :cmd_data={1'b1,10'h138,8'h0F};// Addr Table Index12'd129 :cmd_data={1'b1,10'h139,8'h78};// Gain12'd130 :cmd_data={1'b1,10'h13A,8'h00};// Bias12'd131 :cmd_data={1'b1,10'h13B,8'h00};// GM12'd132 :cmd_data={1'b1,10'h13F,8'h06};// Write Words12'd133 :cmd_data={1'b1,10'h13C,8'h00};// Delay for 3 ADCCLK/16 clock cycles (Dummy Write)12'd134 :cmd_data={1'b1,10'h13C,8'h00};// Delay ~1us (Dummy Write)12'd135 :cmd_data={1'b1,10'h138,8'h0E};// Addr Table Index12'd136 :cmd_data={1'b1,10'h139,8'h74};// Gain12'd137 :cmd_data={1'b1,10'h13A,8'h00};// Bias12'd138 :cmd_data={1'b1,10'h13B,8'h0D};// GM12'd139 :cmd_data={1'b1,10'h13F,8'h06};// Write Words12'd140 :cmd_data={1'b1,10'h13C,8'h00};// Delay for 3 ADCCLK/16 clock cycles (Dummy Write)12'd141 :cmd_data={1'b1,10'h13C,8'h00};// Delay ~1us (Dummy Write)12'd142 :cmd_data={1'b1,10'h138,8'h0D};// Addr Table Index12'd143 :cmd_data={1'b1,10'h139,8'h70};// Gain12'd144 :cmd_data={1'b1,10'h13A,8'h00};// Bias12'd145 :cmd_data={1'b1,10'h13B,8'h15};// GM12'd146 :cmd_data={1'b1,10'h13F,8'h06};// Write Words12'd147 :cmd_data={1'b1,10'h13C,8'h00};// Delay for 3 ADCCLK/16 clock cycles (Dummy Write)12'd148 :cmd_data={1'b1,10'h13C,8'h00};// Delay ~1us (Dummy Write)12'd149 :cmd_data={1'b1,10'h138,8'h0C};// Addr Table Index12'd150 :cmd_data={1'b1,10'h139,8'h6C};// Gain12'd151 :cmd_data={1'b1,10'h13A,8'h00};// Bias12'd152 :cmd_data={1'b1,10'h13B,8'h1B};// GM12'd153 :cmd_data={1'b1,10'h13F,8'h06};// Write Words12'd154 :cmd_data={1'b1,10'h13C,8'h00};// Delay for 3 ADCCLK/16 clock cycles (Dummy Write)12'd155 :cmd_data={1'b1,10'h13C,8'h00};// Delay ~1us (Dummy Write)12'd160 :cmd_data={1'b1,10'h13F,8'h06};// Write Words12'd161 :cmd_data={1'b1,10'h13C,8'h00};// Delay for 3 ADCCLK/16 clock cycles (Dummy Write) 12'd162 :cmd_data={1'b1,10'h13C,8'h00};// Delay ~1us (Dummy Write)12'd163 :cmd_data={1'b1,10'h138,8'h0A};// Addr Table Index12'd164 :cmd_data={1'b1,10'h139,8'h64};// Gain12'd165 :cmd_data={1'b1,10'h13A,8'h00};// Bias12'd166 :cmd_data={1'b1,10'h13B,8'h25};// GM12'd167 :cmd_data={1'b1,10'h13F,8'h06};// Write Words12'd168 :cmd_data={1'b1,10'h13C,8'h00};// Delay for 3 ADCCLK/16 clock cycles (Dummy Write) 12'd169 :cmd_data={1'b1,10'h13C,8'h00};// Delay ~1us (Dummy Write)12'd170 :cmd_data={1'b1,10'h138,8'h09};// Addr Table Index12'd171 :cmd_data={1'b1,10'h139,8'h60};// Gain12'd172 :cmd_data={1'b1,10'h13A,8'h00};// Bias12'd173 :cmd_data={1'b1,10'h13B,8'h29};// GM12'd174 :cmd_data={1'b1,10'h13F,8'h06};// Write Words12'd175 :cmd_data={1'b1,10'h13C,8'h00};// Delay for 3 ADCCLK/16 clock cycles (Dummy Write) 12'd176 :cmd_data={1'b1,10'h13C,8'h00};// Delay ~1us (Dummy Write)12'd177 :cmd_data={1'b1,10'h138,8'h08};// Addr Table Index12'd178 :cmd_data={1'b1,10'h139,8'h5C};// Gain12'd179 :cmd_data={1'b1,10'h13A,8'h00};// Bias12'd180 :cmd_data={1'b1,10'h13B,8'h2C};// GM12'd181 :cmd_data={1'b1,10'h13F,8'h06};// Write Words12'd182 :cmd_data={1'b1,10'h13C,8'h00};// Delay for 3 ADCCLK/16 clock cycles (Dummy Write) 12'd183 :cmd_data={1'b1,10'h13C,8'h00};// Delay ~1us (Dummy Write)12'd184 :cmd_data={1'b1,10'h138,8'h07};// Addr Table Index12'd185 :cmd_data={1'b1,10'h139,8'h58};// Gain12'd186 :cmd_data={1'b1,10'h13A,8'h00};// Bias12'd187 :cmd_data={1'b1,10'h13B,8'h2F};// GM12'd188 :cmd_data={1'b1,10'h13F,8'h06};// Write Words12'd189 :cmd_data={1'b1,10'h13C,8'h00};// Delay for 3 ADCCLK/16 clock cycles (Dummy Write) 12'd190 :cmd_data={1'b1,10'h13C,8'h00};// Delay ~1us (Dummy Write)12'd191 :cmd_data={1'b1,10'h138,8'h06};// Addr Table Index12'd192 :cmd_data={1'b1,10'h139,8'h54};// Gain12'd193 :cmd_data={1'b1,10'h13A,8'h00};// Bias12'd194 :cmd_data={1'b1,10'h13B,8'h31};// GM12'd195 :cmd_data={1'b1,10'h13F,8'h06};// Write Words12'd196 :cmd_data={1'b1,10'h13C,8'h00};// Delay for 3 ADCCLK/16 clock cycles (Dummy Write) 12'd197 :cmd_data={1'b1,10'h13C,8'h00};// Delay ~1us (Dummy Write)12'd198 :cmd_data={1'b1,10'h138,8'h05};// Addr Table Index12'd199 :cmd_data={1'b1,10'h139,8'h50};// Gain12'd200 :cmd_data={1'b1,10'h13A,8'h00};// Bias12'd201 :cmd_data={1'b1,10'h13B,8'h33};// GM12'd202 :cmd_data={1'b1,10'h13F,8'h06};// Write Words12'd203 :cmd_data={1'b1,10'h13C,8'h00};// Delay for 3 ADCCLK/16 clock cycles (Dummy Write) 12'd204 :cmd_data={1'b1,10'h13C,8'h00};// Delay ~1us (Dummy Write)12'd205 :cmd_data={1'b1,10'h138,8'h04};// Addr Table Index12'd206 :cmd_data={1'b1,10'h139,8'h4C};// Gain12'd207 :cmd_data={1'b1,10'h13A,8'h00};// Bias12'd208 :cmd_data={1'b1,10'h13B,8'h34};// GM12'd209 :cmd_data={1'b1,10'h13F,8'h06};// Write Words12'd210 :cmd_data={1'b1,10'h13C,8'h00};// Delay for 3 ADCCLK/16 clock cycles (Dummy Write) 12'd211 :cmd_data={1'b1,10'h13C,8'h00};// Delay ~1us (Dummy Write)12'd212 :cmd_data={1'b1,10'h138,8'h03};// Addr Table Index12'd213 :cmd_data={1'b1,10'h139,8'h48};// Gain12'd214 :cmd_data={1'b1,10'h13A,8'h00};// Bias12'd215 :cmd_data={1'b1,10'h13B,8'h35};// GM12'd216 :cmd_data={1'b1,10'h13F,8'h06};// Write Words12'd217 :cmd_data={1'b1,10'h13C,8'h00};// Delay for 3 ADCCLK/16 clock cycles (Dummy Write) 12'd218 :cmd_data={1'b1,10'h13C,8'h00};// Delay ~1us (Dummy Write)12'd219 :cmd_data={1'b1,10'h138,8'h02};// Addr Table Index12'd220 :cmd_data={1'b1,10'h139,8'h30};// Gain12'd221 :cmd_data={1'b1,10'h13A,8'h00};// Bias12'd222 :cmd_data={1'b1,10'h13B,8'h3A};// GM12'd223 :cmd_data={1'b1,10'h13F,8'h06};// Write Words12'd224 :cmd_data={1'b1,10'h13C,8'h00};// Delay for 3 ADCCLK/16 clock cycles (Dummy Write) 12'd225 :cmd_data={1'b1,10'h13C,8'h00};// Delay ~1us (Dummy Write)12'd226 :cmd_data={1'b1,10'h138,8'h01};// Addr Table Index12'd227 :cmd_data={1'b1,10'h139,8'h18};// Gain12'd228 :cmd_data={1'b1,10'h13A,8'h00};// Bias12'd229 :cmd_data={1'b1,10'h13B,8'h3D};// GM12'd230 :cmd_data={1'b1,10'h13F,8'h06};// Write Words12'd231 :cmd_data={1'b1,10'h13C,8'h00};// Delay for 3 ADCCLK/16 clock cycles (Dummy Write) 12'd232 :cmd_data={1'b1,10'h13C,8'h00};// Delay ~1us (Dummy Write)12'd233 :cmd_data={1'b1,10'h138,8'h00};// Addr Table Index12'd234 :cmd_data={1'b1,10'h139,8'h00};// Gain12'd235 :cmd_data={1'b1,10'h13A,8'h00};// Bias12'd236 :cmd_data={1'b1,10'h13B,8'h3E};// GM12'd237 :cmd_data={1'b1,10'h13F,8'h06};// Write Words12'd238 :cmd_data={1'b1,10'h13C,8'h00};// Delay for 3 ADCCLK/16 clock cycles (Dummy Write) 12'd239 :cmd_data={1'b1,10'h13C,8'h00};// Delay ~1us (Dummy Write)12'd244 :cmd_data={1'b1,10'h137,8'h1A};// Start Gain Table Clock12'd245 :cmd_data={1'b1,10'h130,8'h00};// Gain Table Index12'd246 :cmd_data={1'b1,10'h131,8'h00};// Ext LNA, Int LNA, & Mixer Gain Word12'd247 :cmd_data={1'b1,10'h132,8'h00};// TIA & LPF Word12'd248 :cmd_data={1'b1,10'h133,8'h20};// DC Cal bit & Dig Gain Word12'd249 :cmd_data={1'b1,10'h137,8'h1E};// Write Words12'd250 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay 3 ADCCLK/16 cycles 12'd251 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay ~1us12'd252 :cmd_data={1'b1,10'h130,8'h01};// Gain Table Index12'd253 :cmd_data={1'b1,10'h131,8'h00};// Ext LNA, Int LNA, & Mixer Gain Word12'd254 :cmd_data={1'b1,10'h132,8'h00};// TIA & LPF Word12'd255 :cmd_data={1'b1,10'h133,8'h00};// DC Cal bit & Dig Gain Word12'd256 :cmd_data={1'b1,10'h137,8'h1E};// Write Words12'd257 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay 3 ADCCLK/16 cycles 12'd258 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay ~1us12'd259 :cmd_data={1'b1,10'h130,8'h02};// Gain Table Index12'd260 :cmd_data={1'b1,10'h131,8'h00};// Ext LNA, Int LNA, & Mixer Gain Word12'd261 :cmd_data={1'b1,10'h132,8'h00};// TIA & LPF Word12'd262 :cmd_data={1'b1,10'h133,8'h00};// DC Cal bit & Dig Gain Word12'd263 :cmd_data={1'b1,10'h137,8'h1E};// Write Words12'd264 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay 3 ADCCLK/16 cycles 12'd265 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay ~1us12'd266 :cmd_data={1'b1,10'h130,8'h03};// Gain Table Index12'd267 :cmd_data={1'b1,10'h131,8'h00};// Ext LNA, Int LNA, & Mixer Gain Word12'd268 :cmd_data={1'b1,10'h132,8'h01};// TIA & LPF Word12'd269 :cmd_data={1'b1,10'h133,8'h00};// DC Cal bit & Dig Gain Word12'd270 :cmd_data={1'b1,10'h137,8'h1E};// Write Words12'd271 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay 3 ADCCLK/16 cycles 12'd272 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay ~1us12'd273 :cmd_data={1'b1,10'h130,8'h04};// Gain Table Index12'd274 :cmd_data={1'b1,10'h131,8'h00};// Ext LNA, Int LNA, & Mixer Gain Word12'd275 :cmd_data={1'b1,10'h132,8'h02};// TIA & LPF Word12'd276 :cmd_data={1'b1,10'h133,8'h00};// DC Cal bit & Dig Gain Word12'd277 :cmd_data={1'b1,10'h137,8'h1E};// Write Words12'd278 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay 3 ADCCLK/16 cycles 12'd279 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay ~1us12'd280 :cmd_data={1'b1,10'h130,8'h05};// Gain Table Index12'd281 :cmd_data={1'b1,10'h131,8'h00};// Ext LNA, Int LNA, & Mixer Gain Word12'd282 :cmd_data={1'b1,10'h132,8'h03};// TIA & LPF Word12'd283 :cmd_data={1'b1,10'h133,8'h00};// DC Cal bit & Dig Gain Word12'd284 :cmd_data={1'b1,10'h137,8'h1E};// Write Words12'd285 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay 3 ADCCLK/16 cycles 12'd286 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay ~1us12'd287 :cmd_data={1'b1,10'h130,8'h06};// Gain Table Index12'd288 :cmd_data={1'b1,10'h131,8'h00};// Ext LNA, Int LNA, & Mixer Gain Word12'd289 :cmd_data={1'b1,10'h132,8'h04};// TIA & LPF Word12'd290 :cmd_data={1'b1,10'h133,8'h00};// DC Cal bit & Dig Gain Word12'd291 :cmd_data={1'b1,10'h137,8'h1E};// Write Words12'd292 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay 3 ADCCLK/16 cycles 12'd293 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay ~1us12'd294 :cmd_data={1'b1,10'h130,8'h07};// Gain Table Index12'd295 :cmd_data={1'b1,10'h131,8'h00};// Ext LNA, Int LNA, & Mixer Gain Word12'd296 :cmd_data={1'b1,10'h132,8'h05};// TIA & LPF Word12'd297 :cmd_data={1'b1,10'h133,8'h00};// DC Cal bit & Dig Gain Word12'd298 :cmd_data={1'b1,10'h137,8'h1E};// Write Words12'd299 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay 3 ADCCLK/16 cycles 12'd300 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay ~1us12'd301 :cmd_data={1'b1,10'h130,8'h08};// Gain Table Index12'd302 :cmd_data={1'b1,10'h131,8'h01};// Ext LNA, Int LNA, & Mixer Gain Word12'd303 :cmd_data={1'b1,10'h132,8'h03};// TIA & LPF Word12'd304 :cmd_data={1'b1,10'h133,8'h20};// DC Cal bit & Dig Gain Word12'd305 :cmd_data={1'b1,10'h137,8'h1E};// Write Words12'd306 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay 3 ADCCLK/16 cycles 12'd307 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay ~1us12'd308 :cmd_data={1'b1,10'h130,8'h09};// Gain Table Index12'd309 :cmd_data={1'b1,10'h131,8'h01};// Ext LNA, Int LNA, & Mixer Gain Word12'd310 :cmd_data={1'b1,10'h132,8'h04};// TIA & LPF Word12'd311 :cmd_data={1'b1,10'h133,8'h00};// DC Cal bit & Dig Gain Word12'd312 :cmd_data={1'b1,10'h137,8'h1E};// Write Words12'd313 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay 3 ADCCLK/16 cycles 12'd314 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay ~1us12'd315 :cmd_data={1'b1,10'h130,8'h0A};// Gain Table Index12'd316 :cmd_data={1'b1,10'h131,8'h01};// Ext LNA, Int LNA, & Mixer Gain Word12'd317 :cmd_data={1'b1,10'h132,8'h05};// TIA & LPF Word12'd318 :cmd_data={1'b1,10'h133,8'h00};// DC Cal bit & Dig Gain Word12'd319 :cmd_data={1'b1,10'h137,8'h1E};// Write Words12'd320 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay 3 ADCCLK/16 cycles 12'd321 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay ~1us12'd322 :cmd_data={1'b1,10'h130,8'h0B};// Gain Table Index12'd323 :cmd_data={1'b1,10'h131,8'h01};// Ext LNA, Int LNA, & Mixer Gain Word12'd332 :cmd_data={1'b1,10'h133,8'h00};// DC Cal bit & Dig Gain Word12'd333 :cmd_data={1'b1,10'h137,8'h1E};// Write Words12'd334 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay 3 ADCCLK/16 cycles 12'd335 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay ~1us12'd336 :cmd_data={1'b1,10'h130,8'h0D};// Gain Table Index12'd337 :cmd_data={1'b1,10'h131,8'h01};// Ext LNA, Int LNA, & Mixer Gain Word12'd338 :cmd_data={1'b1,10'h132,8'h08};// TIA & LPF Word12'd339 :cmd_data={1'b1,10'h133,8'h00};// DC Cal bit & Dig Gain Word12'd340 :cmd_data={1'b1,10'h137,8'h1E};// Write Words12'd341 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay 3 ADCCLK/16 cycles 12'd342 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay ~1us12'd343 :cmd_data={1'b1,10'h130,8'h0E};// Gain Table Index12'd344 :cmd_data={1'b1,10'h131,8'h01};// Ext LNA, Int LNA, & Mixer Gain Word12'd345 :cmd_data={1'b1,10'h132,8'h09};// TIA & LPF Word12'd346 :cmd_data={1'b1,10'h133,8'h00};// DC Cal bit & Dig Gain Word12'd347 :cmd_data={1'b1,10'h137,8'h1E};// Write Words12'd348 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay 3 ADCCLK/16 cycles 12'd349 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay ~1us12'd350 :cmd_data={1'b1,10'h130,8'h0F};// Gain Table Index12'd351 :cmd_data={1'b1,10'h131,8'h01};// Ext LNA, Int LNA, & Mixer Gain Word12'd352 :cmd_data={1'b1,10'h132,8'h0A};// TIA & LPF Word12'd353 :cmd_data={1'b1,10'h133,8'h00};// DC Cal bit & Dig Gain Word12'd354 :cmd_data={1'b1,10'h137,8'h1E};// Write Words12'd355 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay 3 ADCCLK/16 cycles 12'd356 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay ~1us12'd357 :cmd_data={1'b1,10'h130,8'h10};// Gain Table Index12'd358 :cmd_data={1'b1,10'h131,8'h01};// Ext LNA, Int LNA, & Mixer Gain Word12'd359 :cmd_data={1'b1,10'h132,8'h0B};// TIA & LPF Word12'd360 :cmd_data={1'b1,10'h133,8'h00};// DC Cal bit & Dig Gain Word12'd361 :cmd_data={1'b1,10'h137,8'h1E};// Write Words12'd362 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay 3 ADCCLK/16 cycles 12'd363 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay ~1us12'd364 :cmd_data={1'b1,10'h130,8'h11};// Gain Table Index12'd365 :cmd_data={1'b1,10'h131,8'h01};// Ext LNA, Int LNA, & Mixer Gain Word12'd366 :cmd_data={1'b1,10'h132,8'h0C};// TIA & LPF Word12'd367 :cmd_data={1'b1,10'h133,8'h00};// DC Cal bit & Dig Gain Word12'd368 :cmd_data={1'b1,10'h137,8'h1E};// Write Words12'd369 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay 3 ADCCLK/16 cycles 12'd370 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay ~1us12'd371 :cmd_data={1'b1,10'h130,8'h12};// Gain Table Index12'd372 :cmd_data={1'b1,10'h131,8'h01};// Ext LNA, Int LNA, & Mixer Gain Word12'd373 :cmd_data={1'b1,10'h132,8'h0D};// TIA & LPF Word12'd374 :cmd_data={1'b1,10'h133,8'h00};// DC Cal bit & Dig Gain Word12'd375 :cmd_data={1'b1,10'h137,8'h1E};// Write Words12'd376 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay 3 ADCCLK/16 cycles 12'd377 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay ~1us12'd378 :cmd_data={1'b1,10'h130,8'h13};// Gain Table Index12'd379 :cmd_data={1'b1,10'h131,8'h01};// Ext LNA, Int LNA, & Mixer Gain Word12'd380 :cmd_data={1'b1,10'h132,8'h0E};// TIA & LPF Word12'd381 :cmd_data={1'b1,10'h133,8'h00};// DC Cal bit & Dig Gain Word12'd382 :cmd_data={1'b1,10'h137,8'h1E};// Write Words12'd383 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay 3 ADCCLK/16 cycles 12'd384 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay ~1us12'd385 :cmd_data={1'b1,10'h130,8'h14};// Gain Table Index12'd386 :cmd_data={1'b1,10'h131,8'h02};// Ext LNA, Int LNA, & Mixer Gain Word12'd387 :cmd_data={1'b1,10'h132,8'h09};// TIA & LPF Word12'd388 :cmd_data={1'b1,10'h133,8'h20};// DC Cal bit & Dig Gain Word12'd389 :cmd_data={1'b1,10'h137,8'h1E};// Write Words12'd390 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay 3 ADCCLK/16 cycles 12'd391 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay ~1us12'd392 :cmd_data={1'b1,10'h130,8'h15};// Gain Table Index12'd393 :cmd_data={1'b1,10'h131,8'h02};// Ext LNA, Int LNA, & Mixer Gain Word12'd394 :cmd_data={1'b1,10'h132,8'h0A};// TIA & LPF Word12'd395 :cmd_data={1'b1,10'h133,8'h00};// DC Cal bit & Dig Gain Word12'd396 :cmd_data={1'b1,10'h137,8'h1E};// Write Words12'd397 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay 3 ADCCLK/16 cycles 12'd398 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay ~1us12'd399 :cmd_data={1'b1,10'h130,8'h16};// Gain Table Index12'd400 :cmd_data={1'b1,10'h131,8'h02};// Ext LNA, Int LNA, & Mixer Gain Word12'd401 :cmd_data={1'b1,10'h132,8'h0B};// TIA & LPF Word12'd402 :cmd_data={1'b1,10'h133,8'h00};// DC Cal bit & Dig Gain Word12'd403 :cmd_data={1'b1,10'h137,8'h1E};// Write Words12'd404 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay 3 ADCCLK/16 cycles 12'd405 :cmd_data={1'b1,10'h134,8'h00};// Dummy Write to delay ~1us12'd406 :cmd_data={1'b1,10'h130,8'h17};// Gain Table Index12'd407 :cmd_data={1'b1,10'h131,8'h02};// Ext LNA, Int LNA, & Mixer Gain Word。

ad减压阀

Ad减压阀提高自主研发能力。

到目前为止,财政部已经会同有关部门对核电设备、高速列车、掘进机、纺织机械、输变电设备、数控机床等多个领域的制造企业,进行了实地调研或召开由企业、行业协会参加的座谈会,相关行业的进口税收政策具体实施方案的试点工作也已经陆续展开。

阀门20%市场为外企占领我国每年阀门市场成交额高达500亿元左右,但其中却有100多亿元的市场被国外阀门企业占领。

据统计,我国目前阀门企业约6000余家,其中年产值超过500万元的有900家。

国内上市的阀门公司3家,即中核科技、洪城股份、广东明珠。

2005年,中核科技主营业务收入2.35亿元,洪城股份业务收入1.46亿元,广东明珠主营业务收入1.5亿元。

但这些企业,无论是其规模,还是产品质量,目前都无法与国外同类企业抗衡。

业内人士分析,造成目前我国阀门市场被动的原因主要有两方面:一是国产阀门产品和进口产品相比还有差距,质量有待提高。

二是某些用户国产化意识不强,甚至人为地设置门槛,一、产品[高灵敏度蒸汽减压阀]的详细资料:产品型号:YG43H/Y型产品名称:高灵敏度蒸汽减压阀产品特点:本产品主要用于蒸汽管路,适用于进口压力变化大,流量变化大的蒸汽管路。

二、结构特点和用处:本系列减压阀属于先导活塞式减压阀。

由主阀和导阀两部分组成。

主阀主要由阀座、主阀盘、活塞、弹簧等零件组成。

导阀主要由阀座、阀瓣、膜片、弹簧、调节弹簧等零件组成。

通过调节调节弹簧压力设定出口压力、利用膜片传感出口压力变化,通过导阀启闭驱动活塞调节主阀节流部位过流面积的大小,实现减压稳压功能。

本系列产品在普通减压阀基础上做了以下改进,加大了活塞面积,改变了节流结构,改变了密封形式,改进了导阀结构和调节弹簧形式,从而从以下几方面提高了产品的性能。

1、提高了对出口压力变化的传感效能,提高了灵敏度,大大降低了因上游压力变化,流量变化等因素引起的压力偏差。

2、改善了流线分布,降低了噪声。

3、改进了密封面结构,延长了密封面寿命。

微机接口课件第9章AD与DA转换

CSEG ENDS

END /D转换器概述

将连续变化的模拟信号转换为数字信号的 装置称为A/D转换器,简称ADC。

1.ADC原理

A/D转换器按照工作原理可分为计数式A/D 转换器、双积分式A/D转换器和逐次比较式 A/D转换器三种。

(1)计数式A/D转换器

微机原理与接口技术

作者:徐建平 成贵学

第9章 A/D与D/A转换

在微型计算机的输入/输出系统中,常 需要把外界连续变化的模拟信号送入计 算机进行运算,或者把计算机中经过处 理的数字信号输出控制某些外设。

完成由模拟信号到数字信号或由数字 信号到模拟信号转换的过程分别称为模 /数(A/D)转换或数/模(D/A)转换。

其中,若Di=1,则开关Si闭合;若Di=0, 则开关Si断开。

(2)T型电阻网络

常用的方法是采用T型电阻网络,这种方法 只使用两种阻值的电阻(R和2R),如图9-3 所示。各处的电压依次为:

2.DAC技术指标

(1)分辨率 分辨率指的是输出电压的最小变化量与满量

程输出电压之比,表明了D/A转换器的一个 最低有效位(LSB)使输出变化的程度。 分辨率也常用输入二进制数的位数来描述, 位数越多,则分辨率越高,转换时对应输入 模拟信号的电压值越小。

(5)温度灵敏度

温度灵敏度指的是,在满量程时,温度每升 高1℃,输出模拟值变化的百分数。它反映 了D/A转换器对温度变化的灵敏程度。

(6)输出范围

所谓输出范围,指的是D/A转换器输出电压 的最大范围,一般为5V~10V。输出电压一般 与参考电压、运算放大器的连接方式等有关。

9.1.2 D/A转换器芯片 DAC0832

(1)单缓冲方式

单缓冲方式是指,使输入寄存器或DAC寄存器 中的一个处于直通状态,即输入数据经过一 级缓冲就送入D/A转换器。

ADI AD9652 快速入门指南说明书

Quick Start Guide for testing theAD9652 Analog-to-Digital Converter (ADC) Engineering Evaluation Board Using the FPGA based CaptureBoard HSC-ADC-EVALCZFigure 1: AD9652 Evaluation Board with HSC-ADC-EVALCZ Data Capture BoardEquipment Needed►Analog signal source and anti-aliasing filter►Analog Clock Source►PC►USB 2.0 port recommended (USB 1.1-compatible)►AD9652 customer evaluation board with 6VDC, 2A AC adapter.►HSC-ADC-EVALCZ FPGA Based Data Capture Board with 6VDC, 2A AC adapter.Documents Needed►AD9652 Datasheet►VisualAnalog Converter Evaluation Tool User Manual, AN-905►High Speed ADC SPI Control Software User Manual, AN-878►Interfacing to High Speed ADCs via SPI, AN-877Software Needed►VisualAnalog►SPIControllerAll documents and software are available at /fifo.For any questions please send an email to*******************************.Install software from the ADI website1.Download and install VisualAnalog, Rev 1.9.45.21 or later.2.Download and install SPI Control Software, Rev 4.0.4.4031 or later.Setup hardware and software1.Connect the AD9652 Customer evaluation board and the HSC-ADC-EVALCZ boardtogether as shown in Figure 1. (Note these instructions are for Board HSC12048, Rev. C)2.Connect one 6V, 2A AC Adapter to the HSC-ADC-EVALCZ board.3.Connect the HSC-ADC-EVALCZ board to the PC with a USB cable. (Connect to J6)4.Verify Jumpers on the AD9652 evaluation board:a.Place Power supply jumpers: P204, P13, P206, P5, P205, P9, P209, P202b.Disable Amp: P16 and P31, jumper pins 1&2c.P15 jumper pins 2&3d.JP3 jumper should be installed5.Connect power to the AD9652 Evaluation board using the provided 6V switching wall mountAC/DC power supply adaptor.6.On the ADC evaluation board, provide a clean, low jitter clock source to connector J6 at thedesired ADC conversion rate. Note: The AD9652 has an input clock divider circuit which allows generators to drive a higher frequency clock, for this case apply the high frequency clock to J6 and program the proper divide using SPIController when it is used in a later step.The input clock level should be between 10dBm and 16dBm.a.For the AD9652 evaluation board number 12048 Rev C, the Clock Duty Cyclestabilizer should be disabled when using an input clock above 620 MHz.7.Open VisualAnalog on the PC. “AD9652” should be listed in the status bar of the “NewCanvas” window. Select the template that corresponds to the type of testing that you are performing, commonly “Average FFT”.8.If an error occurs during the automatic loading of the FPGA program file, the program can beloaded manually.a.To load the FPGA program manually, select the ADC Data Capture Settings windowand click on the ‘Capture Board’ tab (see the red box in the figure below). In theFPGA box select the program “AD9652_fifo5.bin” to configure the FPGA. Afterselecting the file, click the “Program” button to download the file to the FPGA. The‘DONE’ LED (D6) should illuminate on the HSC-ADC-EVALCZ board indicatingthat the FPGA has been correctly programmed.9.Next open the SPI Controller software. Note that pressing the Read button in the CHIP ID(1)box, the field should report the AD9652 if it is connected properly.Note AD9652in title bar.10.By default the AD9652 is configured for 2.5 Vpp input of 155 MHz or less. The ADCBase 0tabe can be used to change both of these settings.11.On the ADC evaluation board, use a clean signal generator with low phase noise to providean input signal to the analog input at connector J1 (Channel A) and/or J4 (Channel B). Use a1 m, shielded, RG-58, 50 Ω coaxial cable to connect the signal generator. For best results usea narrow-band, band-pass filter with 50 Ω terminations and an appropriate center frequency.(ADI uses TTE, Allen Avionics, and K&L band-pass filters.) In order for the input level to be near the ADC’s full scale, the generator level should be set to around 12dBm; this level depends on the input frequency and any losses in bandpass filters.12.Click the Run button () in VisualAnalog.13.Connect or enable the input signal and adjust the amplitude of the input signal so that thefundamental is at the desired level. (Examine the “Fund Power” reading in the left panel of the VisualAnalog FFT window.)14.If desired, click on File>Save Form as in the FFT window to save the FFT plot.Troubleshooting►The FFT plot appears abnormal...✓If you see a normal noise floor when you disconnect the signal generator from the analog input, be sure you are not overdriving the ADC. Reduce input level ifnecessary.✓In VisualAnalog, Click on the Settings button in the “Input Formatter” block. Check that “Number Format” is set to the correct encoding (2’s compliment by default).►The FFT plot appears normal, but performance is poor.✓Make sure you are using an appropriate filter on the analog input.✓Make sure the signal generators for the clock and the analog input are clean (low phase noise).✓If you are using non-coherent sampling, change the analog input frequency slightly.✓Make sure the SPI config file matches the product being evaluated.►The FFT window remains blank after the Run button is clicked.✓Make sure the evaluation board is securely connected to the HSC-ADC-EVALDZ board✓Disconnect power from both the ADC evaluation board and the HSC-ADC-EVALDZ board, disconnect the USB cable from the HSC-ADC-EVALDZ board and beginagain at Step 1.✓Make sure the FPGA has been programmed by verifying that the ‘CONFIG_DONE’ LED is illuminated on the HSC-ADC-EVALDZ board.✓Make sure the correct FPGA program was installed.►VisualAnalog indicates that the “FIFO capture timed out.”✓Make sure all power and USB connections are secure.✓Double check that the encode clock source is present at connector J505.AD9652 Revision: 0 April 30, 2014。

ad 设置器件规则

在AD(Advanced Design)中设置器件规则主要涉及以下步骤:

1.启动AD软件,创建一个新的设计项目。

2.在项目浏览器中,右键单击设计项目并选择“Edit Design Options”(编辑设计选项)。

3.在弹出的对话框中,选择“Rules”(规则)选项卡。

4.在规则列表中,可以看到不同类型的规则,如“Electrical Rules”(电气规则)、“Physical Rules”(物理规则)等。

5.选择需要设置规则的类别,例如“Electrical Rules”。

6.在右侧的属性面板中,可以看到该类别下的所有规则。

例如,“Net”规则用于指定网络之间的连接关系,“Clearance”规则用于设置安全间距等。

7.选择一个规则,然后单击“Edit”按钮打开规则编辑器。

8.在规则编辑器中,可以设置该规则的具体参数,例如安全间距、导线宽度等。

根据需要进行设置。

9.设置完成后,点击“OK”按钮保存更改。

10.重复上述步骤,根据需要设置其他规则。

需要注意的是,以上步骤仅涵盖了AD软件中设置器件规则的一般流程。

具体操作可能会因软件版本和设计需求而有所不同。

建议参考AD软件的官方文档或教程以获取更详细和准确的指导。

微型计算机控制技术课后答案及解析

习题一1,微型计算机控制系统的硬件由哪几部分组成?各部分的作用是什么?答:CPU,接口电路及外部设备组成。

CPU,这是微型计算机控制系统的核心,通过接口它可以向系统的各个部分发出各种命令,同时对被控对象的被控参数进行实时检测及处理.接口电路,微机和生产对象之间进行信息交换的桥梁和纽带。

外部设备:这是实现微机和外界进行信息交换的设备2,微型计算机控制系统软件有什么作用?说出各部分软件的作用。

答:软件是指能够完成各种功能的计算机程序的总和。

整个计算机系统的动作,都是在软件的指挥下协调进行的,因此说软件是微机系统的中枢神经。

就功能来分,软件可分为系统软件、应用软件1)系统软件:它是由计算机设计者提供的专门用来使用和管理计算机的程序.对用户来说,系统软件只是作为开发应用软件的工具,是不需要自己设计的。

2)应用软件:它是面向用户本身的程序,即指由用户根据要解决的实际问题而编写的各种程序。

3,常用工业控制机有几种?它们各有什么用途?4,操作指导、DDC和SCC系统工作原理如何?它们之间有何区别和联系?答:(1)操作指导控制系统:在操作指导控制系统中,计算机的输出不直接作用于生产对象,属于开环控制结构。

计算机根据数学模型、控制算法对检测到的生产过程参数进行处理,计算出各控制量应有的较合适或最优的数值,供操作员参考,这时计算机就起到了操作指导的作用。

(2)直接数字控制系统(DDC系统):DDC(Direct Digital Control)系统就是通过检测元件对一个或多个被控参数进行巡回检测,经输入通道送给微机,微机将检测结果与设定值进行比较,再进行控制运算,然后通过输出通道控制执行机构,使系统的被控参数达到预定的要求。

DDC系统是闭环系统,是微机在工业生产过程中最普遍的一种应用形式。

(3)计算机监督控制系统(SCC系统):SCC(Supervisory Computer Control)系统比DDC 系统更接近生产变化的实际情况,因为在DDC系统中计算机只是代替模拟调节器进行控制,系统不能运行在最佳状态,而SCC系统不仅可以进行给定值控制,并且还可以进行顺序控制、最优控制以及自适应控制等SCC是操作指导控制系统和DDC系统的综合与发展。

AD9851信号发生器电路图原理

AD9851信号发生器电路图原理本文基于直接数字频率合成(DDS)原理,采用AD9851型DDS器件设计一个信号发生器,实现50Hz~60MHz范围内的正弦波输出。

通过功率放大,在50Ω负载的情况下,该信号发生器在50Hz~10MHz范围内输出稳定正弦波,电压峰峰值为0~5V±0.3V。

0引言直接数字合成(Direct Digital Synthesis—DDS)是近年来新的电子技术。

单片集成的DDS产品是一种可代替锁相环的快速频率合成器件。

DDS是产生高精度、快速变换频率、输出波形失真小的优先选用技术。

DDS以稳定度高的参考时钟为参考源,通过精密的相位累加器和数字信号处理,通过高速D/A变换器产生所需的数字波形(通常是正弦波形),这个数字波经过一个模拟滤波器后,得到最终的模拟信号波形。

DDS系统一个显著的特点就是在数字处理器的控制下能够精确而快速地处理频率和相位。

除此之外,DDS的固有特性还包括:相当好的频率和相位分辨率(频率的可控范围达μHz级,相位控制小于0.09°),能够进行快速的信号变换(输出DAC的转换速率百万次/秒)。

1AD9851集成芯片简介AD9851是在AD9850的基础上,做了一些改进以后生成的具有新功能的DDS芯片。

AD9851相对于AD9850的内部结构,只是多了一个6倍参考时钟倍乘器,当系统时钟为180MHz时,在参考时钟输入端,只需输入30MHz的参考时钟即可。

AD9851是由数据输入寄存器、频率/相位寄存器、具有6倍参考时钟倍乘器的DDS芯片、10位的模/数转换器、内部高速比较器这几个部分组成。

其中具有6倍参考时钟倍乘器的DDS芯片是由32位相位累加器、正弦函数功能查找表、D/A变换器以及低通滤波器集成到一起。

这个高速DDS芯片时钟频率可达180MHz,输出频率可达70MHz,分辨率为0.04Hz。

AD9851可以产生一个频谱纯净、频率和相位都可编程控制且稳定性很好的模拟正弦波,这个正弦波能够直接作为基准信号源,或通过其内部高速比较器转换成标准方波输出,作为灵敏时钟发生器来使用。

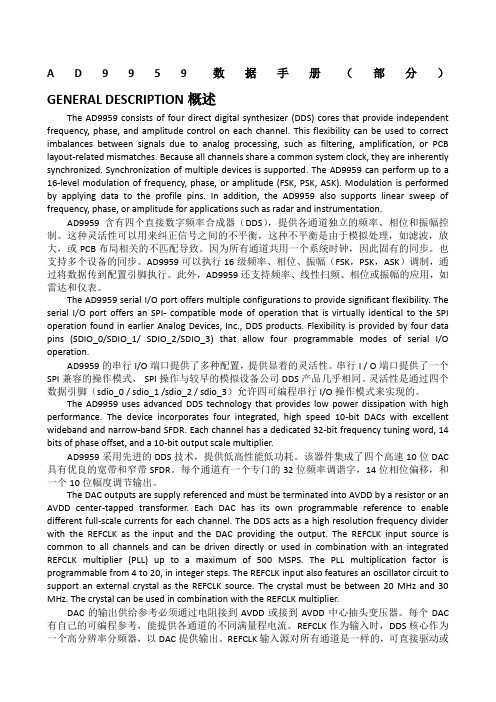

AD9959数据手册部分内容中文翻译

A D9959数据手册(部分)GENERAL DESCRIPTION概述The AD9959 consists of four direct digital synthesizer (DDS) cores that provide independent frequency, phase, and amplitude control on each channel. This flexibility can be used to correct imbalances between signals due to analog processing, such as filtering, amplification, or PCB layout-related mismatches. Because all channels share a common system clock, they are inherently synchronized. Synchronization of multiple devices is supported. The AD9959 can perform up to a 16-level modulation of frequency, phase, or amplitude (FSK, PSK, ASK). Modulation is performed by applying data to the profile pins. In addition, the AD9959 also supports linear sweep of frequency, phase, or amplitude for applications such as radar and instrumentation.AD9959含有四个直接数字频率合成器(DDS),提供各通道独立的频率、相位和振幅控制。

ad布线规则自己整理

一、PCB板的元素1、工作层面对于印制板来说,工作层面可以分为6大类,信号层(signal layer)内部/接地层(internal plane layer)机械层(mechanical layer)主要用来放置物理边界和放置尺寸标注等信息,起到相应的提示作用。

EDA软件可以提供16层的机械层。

防护层(mask layer)包括锡膏层和阻焊层两大类。

锡膏层主要用于将表面贴粘贴在PCB上,阻焊层用于防止焊锡镀在不应该焊接的地方。

丝印层(silkscreen layer)在PCB板的TOP和BOTTOM层表面绘制元器件的外观轮廓和放置字符串等。

例如元器件的标识、标称值等以及放置厂家标志,生产日期等。

同时也是印制电路板上用来焊接元器件位置的依据,作用是使PCB板具有可读性,便于电路的安装和维修。

其他工作层(other layer)禁止布线层Keep Out Layer钻孔导引层 drill guide layer钻孔图层 drill drawing layer复合层 multi-layer2、元器件是实际元器件焊接到PCB板时的焊接位置与焊接形状,包括了实际元器件的外形尺寸,所占空间位置,各管脚之间的间距等。

元器件封装是一个空间的功能,对于不同的元器件可以有相同的封装,同样相同功能的元器件可以有不同的封装。

因此在制作PCB板时必须同时知道元器件的名称和封装形式。

(1)元器件封装分类通孔式元器件封装(THT,through hole technology)表面贴封装(SMT Surface mounted technology)另一种常用的分类方法是从封装外形分类:SIP单列直插封装DIP双列直插封装PLCC塑料引线载体封装PQFP塑料四方扁平封装SOP 小尺寸封装TSOP薄型小尺寸封装PPGA塑料针状栅格阵列封装PBGA塑料球栅阵列封装CSP 芯片级封装(2)元器件封装编号编号原则:元器件类型+引脚距离(或引脚数)+元器件外形尺寸例如AXIAL-0.3 DIP14 RAD0.1 RB7.6-15 等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

AD9851

概述:

AD9851是ADI公司采用先进的DDS技术推出的高集成度DDS频率合成器,它内部包括可编程DDS系统、高性能DAC及高速比较器,能实现全数字编程控制的频率合成和时钟发生。

AD9851接口功能控制简单,可以用8位并行口或串行口直接输入频率、相位等控制数据。

32位频率控制字,在180MHz时钟下,输出频率分辨率达0.0372Hz。

先进的CMOS工艺使AD9851不仅性能指标一流,而且功耗低,在3. 3V供电时,功耗仅为155mW。

各引脚介绍:

D0~D7: 8位数据输入口,可给内部寄存器装入40位控制数据。

PGND:6倍参考时钟倍频器的地。

PVCC:6倍参考时钟倍频器电源。

W—CLK:字装入信号,上升沿有效。

FQ—UD:频率更新控制信号,时钟上升沿确认输入数据有效。

REFCLOCK:外部参考时钟输入。

AGND:模拟地。

AVDD:模拟电源(+5V)。

DGND:数字地。

DVDD:数字电源(+5V)。

RSET:外部复位连接端。

VOUTN:内部比较器负向输出端。

VOUTP:内部比较器正向输出端。

VINN:内部比较器负向输入端。

VINP:内部比较器正向输入端。

DACBP:DAC旁路连接端。

IOUTB:”互补“DAC输出。

IOUT:内部DAC输出端。

RESET:复位端。

原理分析:

AD9851采用直接数字合成(DDS)技术,以数字控制振荡器(DCO)的形式产生频率/相位可变的正弦波,经过内部10位的高速数/ 模转换输出模拟信号。

片内高速比较器可以将模拟正弦波信号转变为稳定的TTL/CMOS兼容的方波输出。

AD9851高速DD5内核可接收32位的频率控制字输入,在180MHz的系统时钟下可输出的频率分辨率为180MHz/(2的32次方)。

AD9851内部提供一个6倍频的REFCLK倍频器,可以通过外接一个较低频率的基准时钟产生180MHz的内部个哦难过时钟,具有较好的无杂散动态范围和相位噪声特性。

芯片内部提供了5位可编程相位调制精度,可使得输出波形的相位偏移小于11.25度;AD9851内部华提供了一个高速比较器,内部D/A转换器输出的正弦波可以通过它转换为方波输出。

AD9851频率控制字、相位调节字以及可以采用并行或串行方式异步加载到芯片内部。

并行加载模式有连续5个8位字节构成,其中第一个8位字节包括5位相位调节字、1位6*REFCLK倍频器控制、1位电源休眠使能和一位加载模式;其余4个字节表示32位的频率控制字。

串行加载模式由40位的数据流构成。

DDS电路可以看成是一个由系统时钟和N位频率控制字决定的数字分频器,相位累加器相当于模值可变的计数器。

由频率控制字决定该计数器的模值,在下一个时钟脉冲开始相位累加器以新的相位增量进行累加。

设置的相位增量越大,累加器循环一周就越快,从而输出的频率就越高。