EDA3

eda技术及应用第三版课后答案谭会生

eda技术及应用第三版课后答案谭会生【篇一:《eda技术》课程大纲】>一、课程概述1.课程描述《eda技术》是通信工程专业的一门重要的集中实践课,是通信工程专业学生所必须具备的现代电子设计技术技能知识。

eda是电子技术的发展方向,也是电子技术教学中必不可少的内容。

本课程主要介绍可编程逻辑器件在电子电路设计及实现上的应用,介绍电路原理图和pcb图的设计技术。

开设该课程,就是要让学生了解大规模专用集成电路fpga和cpld的结构,熟悉一种以上的硬件描述语言,掌握一种以上的开发工具的使用等,掌握电路原理图和pcb图的现代设计技术与方法,从而提高学生应用计算机对电子电路和高速智能化系统进行分析与设计的能力。

2.设计思路本课程坚持“以学生为中心”的原则,以项目任务驱动的方式,采取理论知识与案例相结合的方式授课,提高学生的学习主动性。

通过必要的理论知识讲授、大量的实践训练和案例分析,培养学生的动手设计和实践能力,掌握eda开发的整个流程和基本技巧。

课程采用演示讲授和实践相结合,边讲边练的方法,让学生切身体会并掌握eda开发产品的流程和方法。

本课程集中2周时间开设,注重实践性,边讲边练,让学生切身体会并掌握eda开发技术。

3.实践要求(1)纪律和安全要求①不得将食物带入实验室,每次实训后请将使用后的废弃物带走。

违反者每次扣罚平时分2分。

②实训期间不得做与实训无关的其他事情,不得大声喧哗或做其他影响实训正常进行的事宜。

违反者每次扣罚平时分2分。

③实训期间,若学生有事不能正常参加实训,须提前以书面形式请假,并按指导教师的安排补做实训。

未经指导教师许可,学生不得任意调换实训时间和实训地点。

违反者每次扣罚平时分4分。

④学生不得以任何理由替代他人进行实训,违者直接取消实训成绩。

⑤学生除操作自己所分配的计算机外,不得操作实验室内其他任何设备。

违者每次扣罚平时分2分。

(2)业务要求实训所使用的软件protel和quartus ii,所有数据均通过服务器中转以及储存在服务器上,所以重启自己所用的电脑不会造成数据丢失。

EDA技术及其应用(3)

1.4 EDA的优势

手工设计方法

●复杂电路的设计、调试十分困 难;

●无法进行硬件系统仿真,若某 一过程存在错误,查找和修改十 分不便;

●设计过程中产生大量文档,不 易管理;

●对于IC设计而言,设计实现过 程与具体生产工艺直接相关,因 此可移植性差;

●只有在设计出样机或生产出芯 片后才能进行实测;

EDA技术

在设计时加入用于测试的部分逻辑,即进行可测性设计(DFT ,Design For Test),在设计完成后用来测试关键逻辑。

在ASIC设计中的扫描寄存器,是可测性设计的一种,原理是 把ASIC中关键逻辑部分的普通寄存器用测试扫描寄存器来代替, 在测试中可以动态地测试、分析设计其中寄存器所处的状态,甚至 对某个寄存器加以激励信号,改变该寄存器的状态。

1.6.3 GAL

GAL的OLMC单元设有多种组态,可配置成专用组合输出、专 用输入、组合输出双向口、寄存器输出、寄存器输出双向口等, 为逻辑电路设计提供了极大的灵活性。由于具有结构重构和输出 端的任何功能均可移到另一输出引脚上的功能,在一定程度上, 简化了电路板的布局布线,使系统的可靠性进一步地提高。GAL 的出现是复杂PLD的里程碑。

1.11 编程与配置

目前常见的大规模可编程逻辑器件的编程工艺有三种: 1.基于电可擦除存储单元的EEPROM或Flash技术。 2.基于SRAM查找表的编程单元。 3.基于反熔丝编程单元。

1.12 FPGA配置器件

主动配置方式

由FPGA器件引导配置操作过程,它控 制着外部存储器和初始化过程

被动配置方式

1.2 EDA技术应用对象

全定制或半定制ASIC

实现目标 ASIC的设计和实现

FPGA/CPLD(或称可编程ASIC)开发应用

EDA课件第三章

tmp2:=d1 AND (NOT sel); tmp3:=tmp1 OR tmp2; tmp<=tmp3;

q<=tmp AFTER m; END PROCESS cale;

END ARCHITECTURE connect;

(2) 端口方向

端口方向用来定义外部引脚的信号方向是输入还 是输出。

凡是用“IN”进行方向说明的端口,其信号自端口 输入到构造体,而构造体内部的信号不能从该端口输 出。相反,凡是用“OUT”进行方向说明的端口,其信 号将从构造体内经端口输出,而不能通过该端口向构 造体输入信号。

实体说明

一个模块中仅有一 个设计实体。

实体 提供设计模块的接口信息,是VHDL设计电 路的最基本部分。

实体说明具有如下的结构:

ENTITY 实体名 IS

实体说明以“ENTITTY 实体名

[类属参数说明];

IS”开始至“END ENTITTY实体 名”结束。这里大写字母表示

实体说明的框架。实际上,对

此例中的外部引脚

ARCHITECTURE connect OF mux IS SIGNAL tmp:BIT; BEGIN

cale:PROCESS(d0,d1,sel) IS VARIABLE tmp1,tmp2,tmp3:BIT;

BEGIN tmp1:=d0 AND sel;

为d0,d1,sel,q 。

库(Library)是经编译后的数据的集合,它存放包集合 定义、实体定义、构造体定义和配置定义。

设计中的子程序和 公用数据类型的集合。

程序包

IEEE标准的标准程序包 设计者自身设计的程序包

包和库具有这样的关系:多个过程和函数汇集在一起构成包 集合,而几个包汇集在一起就形成一个库。

数码管动态显示EDA实验三

实验三数码管动态显示姓名:赵佳伟学号:1002100449一、实验目的l、实现实现0~9十个数的动态显示。

2、掌握数码管的工作状态。

二、实验的硬件要求1、输入:CLK时钟信号2、输出:LED灯3、主芯片:ALTERA下载板三、实验内容用VHDL语言输入法设计一个数码管动态显示电路,要求能够使之在0~9循环显示。

四、实验步骤(1)进入windows操作系统,打开MAX+PLUSⅡ10.0。

1、启动File/Project Name菜单,输入设计项目的名字。

点Assign/Device菜单,选择器件(本设计全选用EPM7128) 。

见图2.2.1。

2、启动菜单File/New,选择Text Editor file,打开编程编辑器,进行原理图设计输入。

图2.2.1(2)输入代码(下图2.2.2)3、保存单击保存按钮,扩展名为.vhd,本实验中取名为:p4_5.vhd。

(3)编译启动MAX+PLUS II\COMPILER菜单,按START开始编译,生成.SOF和.POF等文件,以便硬件下载和编程时调用,同时生成.RPT文件,如图2.2.3。

图2.2.3(4)仿真1、创建波形文件:①首先,将设计指定为当前项目。

②创建一个波形文件。

选择菜单MAX+PLUSⅡ\Waveform Editor,打开仿真工具Waveform Editor,或选择新建一个Waveform Editor文件,将创建一个新的无标题波形文件,如图2.2.4所示:③储存波形文件。

选择File\Save As,在File Name框中,输入相应文件名,单击OK 按钮存盘。

④设定时间轴网格大小。

选择菜单Option\Grid Size,输入时间间隔(20ns),单击OK 按钮。

⑤设定时间轴长度。

选择菜单File\End Time并输入文件的结束时间(1s )。

图2.2.42、选择欲仿真的引线端子:①选择菜单Node\Enter Nodes Nodes from SNF出现如图2.2.5所示对话框。

EDA技术3-QUARTUS使用方法

厦门理工学院通信系 刘虹

26

3.4 LPM_ROM宏模块应用

使用Quartus II 的MegeWizard Plug-In Manager中的宏功能模块可以帮助用户完成一些复 杂系统的设计,并可以方便地对现有的设计文件 进行修改。这些宏功能模块包括LPM(Library Parameterized Megafunction)、MegaCore(例 如FFT、FIR等)和AMMP(Altera Megafunction Partners Program,例如PCI、DDS等)。下面以 波形发生器的设计为例,介绍Quartus II宏功能 模块的使用方法。

厦门理工学院通信系 刘虹 2

为了方便电路设计,设计者首先应当在计 算机中建立自己的工程目录(如d:\myeda)。 将自己的全部EDA设计文件放在文件夹中。

注意:工程文件夹的名称不要使用汉字,最好 也不要使用数字。

厦门理工学院通信系 刘虹

3

Quartus II原理图输入的基本操作

编辑原理图

引脚锁定

厦门理工学院通信系 刘虹

24

在设计中嵌入SignalTap Ⅱ逻辑分析

仪有两种方法:第一种方法是建立一个

SignalTap Ⅱ文件(.stp),然后定义STP文

件的详细内容;第二种方法是用

MegaWizard Plug-InManager建立并配臵

STP文件,然后用MegaWizard实例化一个

HDL输出模块。

厦门理工学院通信系 刘虹

29

1. 加入计数器元件 用鼠标双击原理图编辑窗, 在弹出的元件选择窗的 “Libraries”栏目中选择 “arithmetic”的 “lpm_counter”(计数器) LPM元件。LPM是参数化的多功 能库元件,每一种LPM元件都 具有许多端口和参数,通过对 端口的选择与参数的设臵得到 设计需要的元件。

EDA三巨头的前世今生之Altium Designer

EDA三巨头的前世今生之Altium Designer“工欲善其事必先利其器”,作为电子硬件工程师,EDA软件的熟练使用是必备的专业技能。

电子行业发展至今,EDA软件可谓功不可没,从芯片的设计到电路板的设计,EDA软件发挥着重要作用。

电子行业内,EDA软件一直被国外三巨头所垄断:Altium、Mentor、Candence,国内EDA软件的发展仍处于萌芽状态,比如立创EDA。

所谓“知耻而后勇”,了解对手,向对手学习,方能超越对手!今天我们先来了解一下Altium公司的前世今生。

一、Altium公司简介Altium是EDA软件行业中的资深领导者,在EDA行业领域有超过25年的经验。

自1985年以来,Altium一直在研发、创作和销售电子设计工具(软件以及硬件)来帮助电子设计工程师利用最新设备及科技,在辽阔的设计“生态系统”中管理自己的项目,从而设计出互连、智能的产品。

二、Altium公司发展历程1985年:Nick Martin 创建Altium Designer的首个版本- Protel PCB,开创Altium公司。

1988年:Altium在美国设立设立办事处销售Protel,并发行AutoTrax。

1991年:Altium将总部迁到美国并发行了Protel for Windows--世界上首款基于Microsoft Windows运行的PCB设计系统。

1994年:EDA/客户端(DXP 1.0) Altium 提出EDA 设计工具集成的客户端/服务器架构。

1997年:Kayvan Oboudyiat 加入Altium公司,计划带领Altium在1999年末于澳大利亚证券交易所(ASX)成功完成IPO。

1998年:Altium 发布了Protel 98 -- 针对Microsoft Windows NT/95/98的全套32位设计组件。

1999年:Altium成功完成了IPO,在澳大利亚证券交易所(ASX)上市。

EDA技术实用教程第三版(潘松著)课后答案下载

EDA技术实用教程第三版(潘松著)课后答案下载

《EDA技术实用教程(第三版)》是xx年01月科学出版社出版的图书,作者是潘松、黄继业。

下面是由分享的EDA技术实用教程第三版(潘松著)课后答案下载,希望对你有用。

???点击此处下载???EDA技术实用教程第三版(潘松著)课后答案

全书包括四部分内容。

第一部分对EDA的基本知识、常用EDA 工具的使用方法和目标器件的结构原理做了介绍:第二部分以向导的形式和实例为主的方法介绍了三种不同的设计输入方法;第三部分对VHDL的设计优化做了介绍:第四部分详述了基于EDA技术的典型设计项目。

各章都安排了习题和针对性较强的实验与设计。

书中列举的大部分VHDL设计实例和实验示例实现的EDA工具平台是QuartusII6.0,硬件平台是CycloneIIFPGA,并在EDA实验系统上通过了硬件测试。

第1章概述

第2章EDA设计流程及其工具

第3章FPGA/CPLD结构与应用

第4章VHDL设计初步

第5章QuartusII应用向导

第6章VHDL设计进阶

第7章宏功能模块与IP应用

第8章状态设计

第9章VHDL结构与要素

第10章VHDL基本语句

第11章优化和时序分析

第12章系统仿真

第13章电子系统设计实践

附录EDA实验系统简介

主要参考文献

2.0实用教程C#版崔良海课后答案人民邮电出版社

2.计算机网络教程第三版吴功宜吴英著课后答案电子工业出版社

3.Java语言程序设计第三版谭浩强主编课后答案清华大学出版社

4.数据库系统教程(第三版)施伯乐丁宝康汪卫课后答案下载。

电子系统设计自动化EDA第3章 Altium Designer原理图设计实例

3.2.5 放置导线

(4)将光标移到要连接的元件引脚上单击,这两 个引脚的电气点就用导线连接起来了

(5)系统默认放置导线时,用鼠标单击的两个电 气点为导线的起点和终点,即第一个电气点为导线 的起点,第二个电气点为终点

1. 原理图上元件参数的直接标识

双击所要 编辑的元 件即可弹 出元件属 性对话框

3.3.3 元件参数的直接标识和编辑

元件属性对话框上“Properties”栏中 “Comment”项的“Visible” “Parameters for...”栏中“Value”

3.3.3 元件参数的直接标识和编辑

第3章 原理图设计实例

本章通过实例,学习Altium Designer电 路原理图的绘制方法。

第3章 原理图设计实例

3.1 原理图设计流程 3.2 原理图的设计 3.3 原理图的编辑与调整 3.4 原理图的检查 3.5 原理图的报表 3.6 原理图的打印输出

3.1 原理图设计流程

3.2 原理图的设计

(2)把元件移动到合适的位置放开左键,元件就 被移动到该位置

3.2.5 放置导线

(1)执行菜单命令【Place】/【Wire】或单击 布线工具栏的 按钮

(2)光标移动到元件的引脚端 (电气点)时,光标中心的“×” 号变为一个红连接 (3)单击,导线的起点就与元件 的引脚连接在一起了

本节通过一个一个接触式防盗报警电路实 例来讲解电路原理图设计的基本过程。

3.2.1 创建一个项目

(1)启动Atium Designer系统。 (2)执行菜单命令【File】/【New】/【PCB Project】,弹出项目面板 (3)执行菜单命令【File】/ 【Save Project】, 在弹出的保存文件的对话框中输入文件名

eda 实验 3

分频器(偶数次分频)一、实验目的1.学习分频器的设计,进一步了解、熟悉和掌握 FPGA开发软件 QuartusII 的使用方法2.学习 Verilog HDL 和 VHDL 的编程方法3.学会使用Vector Wave 功能仿真4.掌握使用多种方法分配管脚二、实验内容编写一个分频器的 Verilog 代码和 VHDL 代码并仿真,编译下载验证。

三、实验原理在数字电路中,时钟信号的分频是很常见的电路。

分频器除了可以对时钟信号频率做除以二的计算外,分频器同时很类似涟波计数器。

涟波计数器是计数器的一种,它属于异步设计。

因为触发器并非皆由同一个时钟信号同步操作,所以它非常节省电路面积。

本实验要设一个带选择的分 SEL[1:0]用于选择是几分频。

分频器设计原理框图如图所示:图1 设计原理框图从原理图中可见,核心板的时钟是50MHz,通过sel[1:0]选择分频数,00:不分频;01:12.5M分频;10:25M 四分频;11:50M 分频。

采用 SW1‐SW2 设置分频值,SW3 复位。

LED1 为时钟的输出,通过调整 SW1、SW2,可以得到不同的闪烁频率。

引脚分配情况表1 引脚分配设计端口芯片引脚开发平台模块设计端口芯片引脚开发平台模块clk PIN_P2 CLK1 rst PIN_W10 SW3sel[1] PIN_Y13 SW2 sel[0] PIN_AA16 SW1clkout PIN_AB20 LED1四、实验步骤1.新建工程,取名为 frediv2.新建 VHDL 设计文件,选择“File|New”,在 New对话框中选择 DeviceDesignFiles 下的 VHDLFile,单击 OK,完成新建设计文件。

3.在新建设计文件中输入 VHDL 程序,源代码如下:Library ieee;Use ieee.std_logic_1164.all;Use ieee.std_logic_arith.all;Use ieee.std_logic_unsigned.all;entity frediv isport( clk :in std_logic;rst :in std_logic;sel :in std_logic_vector(1 downto 0);clkout:out std_logic);end frediv;architecture rt1 of frediv isbeginprocess(rst,clk)variable cn1,cn2,cn3:integer range 0 to 50000000;beginif rst='1'thenclkout<='0';elsif clk'event and clk='1'thenif sel="01"thenif cn1=12499999 thencn1:=0;elsecn1:=cn1+1;if cn1<=6249999 thenclkout<='1';elseclkout<='0';end if;end if;elsif sel="10" thenif cn2=24999999 thencn2:=0;elsecn2:=cn2+1;if cn2<=12499999 thenclkout<='1';elseclkout<='0';end if;end if;elsif sel="11" thenif cn3=49999999 thencn3:=0;elsecn3:=cn3+1;if cn3<=24999999 thenclkout<='1';elseclkout<='0';end if;end if;elseclkout<=clk;end if;end if;end process;end rt1;4.生成“Symbol”文件,新建“Block Diagram/Schematic File”文件,在文件中添加刚2所示刚生成的“Symbol”以及输入输出管脚,最后完整的系统顶层模块图如图图2顶层模块图5.保存文件,使用 qsf或者 tcl 进行管脚分配6.对该工程文件进行全程编译处理,若在编译过程中发现错误,则找出并更正错误,直至编译成功为止。

eda3-8译码器实验报告

eda3-8译码器实验报告EDA实验报告三(3-8译码器的设计)实验三:3-8译码器的设计一、实验目的1、学习Quartus II 7.2软件设计平台。

2、了解EDA的设计过程。

3、通过实例,学习和掌握Quartus II 7.2平台下的文本输入法。

4、学习和掌握3-8译码器的工作和设计原理。

5、初步掌握该实验的软件仿真过程。

二、实验仪器PC机,操作系统为Windows7/XP,本课程所用系统均为WindowsXP(下同),Quartus II 7.2设计平台。

三、实验步骤1、创建工程,在File菜单中选择New Project Wizard,弹出对话框如下图所示在这个窗口中第一行为工程保存路径,第二行为工程名,第三行为顶层文件实体名,和工程名一样。

2、新建设计文本文件,在file中选择new,出现如下对话框:选择VHDL File 点击OK。

3、文本输入,在文本中输入如下程序代码:library ieee;use ieee.std_logic_1164.all;entity variable_decoder isport(A:in STD_LOGIC;B:in STD_LOGIC;C:in STD_LOGIC;Y:out STD_LOGIC_VECTOR(7 downto 0));end variable_decoder;architecture rtl of variable_decoder isbeginprocess(A,B,C)variable COMB:std_logic_vector(2 downto 0); beginCOMB:=C&B&A;case COMB iswhen 000=Y=11111110;when 001=Y=11111101;when 010=Y=11111011;when 011=Y=11110111;when 100=Y=11101111;when 101=Y=11011111;when 110=Y=10111111;when 111=Y=01111111;when others=Y=XXXXXXXX;end case;end process;end rtl;然后保存到工程中,结果如下图所示:4、编译,如果有多个文件要把这个文件设为当前顶层实体,这样软件编译时就只编译这个文件。

EDA 3-8译码器的设计

《EDA技术》课程实验报告学生姓名:**所在班级:**指导教师:** 老师记分及评价:报告满分3分得分一、实验名称实验4:3-8译码器的设计二、任务及要求【基本部分】1、在QuartusII平台上,采用文本输入设计方法,通过编写VHDL语言程序,完成3-8译码器的设计并进行时序仿真。

2、设计完成后生成一个元件,以供更高层次的设计调用。

3、实验箱上进行验证。

【发挥部分】设计4-16译码器,完成仿真并封装成一个元件;新建原理图,调用一片74161和所设计的4-16译码器,完成具有16种花样的循环LED灯控制器的设计,并在实验箱上进行验证。

三、实验程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity decode38 isport(abc:in std_logic_vector(2 downto 0);y:out std_logic_vector(7 downto 0));end;architecture one of decode38 isbeginprocess(abc)begincase abc iswhen"000" => y<="00000001";when"001" => y<="00000010";when"010" => y<="00000100";when"011" => y<="00001000";when"100" => y<="00010000";when"101" => y<="00100000";when"110" => y<="01000000";when"111" => y<="10000000";when others => y<="00000000";end case;end process;end;四、仿真及结果分析五、硬件验证1、引脚锁定情况表:六、小结通过本次实验,提高了自己独立思考问题、自己动手操作的能力,让我们对QuartusII 软件的操作更加了解。

EDA三分频器设计

EDA课程设计实验题目:占空比可调节的三分频器班级:电子081学号:***姓名:**1:实验要求:实现一个占空比可调节的三分频器,占空比可调节为1:3和1:2,时钟信号输入为CLK,带使能输入ENABLEBLE。

2:源代码:library ieee;use ieee.std_logic_1164.all;gned.all;use ieee.std_logic_arith.all;entity div isport(clk,enable:in std_logic;qout1,qout2:buffer std_logic;clk1,clk2:out std_logic) ;end entity div;architecture behave of div isbeginprocess(clk,enable)isvariable cnt:integer range 0 to 2;beginif clk'event and clk='1' thenif enable='1' thenif cnt=2 thencnt:=0;qout1<='1';elsecnt:=cnt+1;qout1<='0';end if;clk1<=qout1;end if;end if;end process;process(clk,enable)isvariable cnt:integer range 0 to 2;beginif clk'event and clk='0' then if enable='0' thenif cnt=2 thencnt:=0;qout2<='1';elsecnt:=cnt+1;qout2<='0';end if;end if;end if;end process;clk2<= qout1 or qout2;end behave;3:仿真波形:图(1)clk1为1:2占空比、clk2为1:3的占空比:4:结果分析:为了实现三分频,必需保证输出波形周期是原信号周期的三倍。

EDA 第3章 VHDL语言 3.3全加器的VHDL描述

3.3 全加器的VHDL描述

3.3.2 CASE语句

1. CASE语句

CASE <表达式> IS When <选择值或标识符> => <顺序语句>; ... ; <顺序语句> ; When <选择值或标识符> => <顺序语句>; ... ; <顺序语句> ; ...

WHEN OTHERS => <顺序语句>;

component元件名port端口名表endcomponent文件名33vhdl333例化语句在组件映射部分其中的端口名是在元件组件定义语句中的端口名表中已定义好的元件端口的名字或者说是顶层文件中待连接的各个元件本身的端口名

3.3 全加器的VHDL描述

目的:进一步学习VHDL的语法

重点:1、CASE语句的用法

3.3 全加器的VHDL描述

【例3-17】 LIBRARY IEEE ; --或门逻辑描述 USE IEEE.STD_LOGIC_1164.ALL; ENTITY or2a IS PORT (a, b :IN STD_LOGIC; c : OUT STD_LOGIC ); END ENTITY or2a; ARCHITECTURE one OF or2a IS BEGIN c <= a OR b ; END ARCHITECTURE one ;

3.3 全加器的VHDL描述

3.3.1 半加器描述 –真值表描述方法

【例3-16】 LIBRARY IEEE; --半加器描述(2):真值表描述方法 USE IEEE.STD_LOGIC_1164.ALL; ENTITY h_adder IS PORT (a, b : IN STD_LOGIC; co, so : OUT STD_LOGIC); END ENTITY h_adder; ARCHITECTURE fh1 OF h_adder is SIGNAL abc : STD_LOGIC_VECTOR(1 DOWNTO 0) ; --定义标准逻辑位矢量数据类型 BEGIN abc <= a & b ; --a相并b,即a与b并置操作 PROCESS(abc) BEGIN CASE abc IS --类似于真值表的CASE语句 WHEN "00" => so<='0'; co<='0' ; WHEN "01" => so<='1'; co<='0' ; WHEN "10" => so<='1'; co<='0' ; WHEN "11" => so<='0'; co<='1' ; WHEN OTHERS => NULL ; END CASE; END PROCESS; END ARCHITECTURE fh1 ;

eda第三次实验(10进制计数器数码管显示)

--------顶层文件counter十进制计数并显示在LED上LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY count ISPORT(CLK, RST, EN, LOAD :IN STD_LOGIC;DATA : IN STD_LOGIC_VECTOR (3 DOWNTO 0);COUT : OUT STD_LOGIC;LED7S:OUT STD_LOGIC_VECTOR (6 DOWNTO 0));END count;ARCHITECTURE BEHAVE OF count ISCOMPONENT CNT10 ISPORT(CLK, RST, EN, LOAD :IN STD_LOGIC;DATA : IN STD_LOGIC_VECTOR (3 DOWNTO 0);DOUT : OUT STD_LOGIC_VECTOR (3 DOWNTO 0);COUT : OUT STD_LOGIC);END COMPONENT CNT10;COMPONENT DECL7S ISPORT (A:IN STD_LOGIC_VECTOR (3 DOWNTO 0);LED7S:OUT STD_LOGIC_VECTOR (6 DOWNTO 0));END COMPONENT DECL7S;SIGNAL S:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINU1:CNT10PORT MAP (CLK=>CLK,RST=>RST,EN=>EN,LOAD=>LOAD,DATA=>DATA,DOUT=>S,COUT=>COUT);U2:DECL7S PORT MAP (A=>S,LED7S=>LED7S);END ARCHITECTURE BEHAVE;---------------------cnt10 10进制计数LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT10 ISPORT(CLK, RST, EN, LOAD :IN STD_LOGIC;DATA : IN STD_LOGIC_VECTOR (3 DOWNTO 0);DOUT : OUT STD_LOGIC_VECTOR (3 DOWNTO 0);COUT : OUT STD_LOGIC);END CNT10;ARCHITECTURE BEHAVE OF CNT10 ISBEGINPROCESS(CLK, RST, EN,LOAD)VARIABLE Q : STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINIF RST = '0' THEN Q := (OTHERS=>'0');ELSIF CLK'EVENT AND CLK= '1' THENIF EN= '1' THENIF (LOAD= '0') THEN Q :=DATA;ELSEIF Q<15 THEN Q := Q+1;ELSE Q := (OTHERS=>'0');END IF;END IF;END IF;END IF;IF Q="1010" THEN COUT<='1';ELSE COUT<='0'; END IF;DOUT<=Q;END PROCESS;END BEHAVE;---------------------驱动LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; ENTITY DECL7S ISPORT (A:IN STD_LOGIC_VECTOR (3 DOWNTO 0);LED7S:OUT STD_LOGIC_VECTOR (6 DOWNTO 0));END;ARCHITECTURE ONE OF DECL7S ISBEGINPROCESS (A) BEGINCASE A ISWHEN "0000" => LED7S <= "1000000";WHEN "0001" => LED7S <= "1111001";WHEN "0010" => LED7S <= "0100100";WHEN "0011" => LED7S <= "0110000";WHEN "0100" => LED7S <= "0011001";WHEN "0101" => LED7S <= "0010010";WHEN "0110" => LED7S <= "0000010";WHEN "0111" => LED7S <= "1111000";WHEN "1000" => LED7S <= "0000000"; WHEN "1001" => LED7S <= "0010000"; WHEN "1010" => LED7S <= "0001000"; WHEN "1011" => LED7S <= "0000011"; WHEN "1100" => LED7S <= "1000110"; WHEN "1101" => LED7S <= "0100001"; WHEN "1110" => LED7S <= "0000110"; WHEN "1111" => LED7S <= "0001110"; WHEN OTHERS => NULL;END CASE;END PROCESS;END;生成门电路图波形仿真图引脚锁定。

EDA 技术实用教程第3章

std_logic; OUT std_logic

•

同一结构体的多个进程之间是并行执行的关系。如下面三个进程: P1:PROCESS(a,b) P2:PROCESS(c,d) P3:PROCESS(d,e) 当d 发生变化时,执行P2,P3进程

3.1 多路选择器的VHDL描述

3.1.1 2选1多路选择器的VHDL描述

3.1 多路选择器的VHDL描述

3.1.2 相关语句结构和语法说明

5. 数据类型: integer boolean std_logic bit

6. 结构体表达

【例4-5】 ARCHITECTURE arch_name OF e_name IS [说明语句] BEGIN (功能描述语句) END ARCHITECTURE arch_name ; 说明语句说明与定义数据对象,类型,元件调用声明等 ,不是必须的。而功能描述语句必须,可并行语句、顺序 语句或其混合。

图3-3 mux21a功能时序波形

3.1 多路选择器的VHDL描述

3.1.2 相关语句结构和语法说明

1. 实体 描述器件外部情况及各信号端口基本性质

【例3-4】 ENTITY e_name IS PORT ( p_name : port_m data_type; ... p_namei : port_mi data_type ); END ENTITY e_name;

EDA 技术实用教程

第 3 章 VHDL设计初步

是什么是VHDL?

Very high speed integrated Hardware Description Language (VHDL)

是IEEE、工业标准硬件描述语言 用语言的方式而非图形等方式描述硬件电路

EDA第3章

[ GENERIC ( 常数名:数据类型 [ : 设定值] ) ] 类属参量 GENERIC是一种端口界面常

PORT ( 端口名:端口模式 数据类型; ⁞

数,用来规定端口的大小、实体中子 元件的数目及实体的定时特性等。 GENERIC ( cntwidth: integer :=4 )

端口名:端口模式 数据类型;); 端口语句PORT( );描述电路的端口及其

该程序是具有异步清零、 进位输入输出功能的4位 计数器。

PORT ( ci: IN STD_LOGIC; Nreset: IN STD_LOGIC; clk: IN STD_LOGIC;

实体部分

co: OUT STD_LOGIC;

qcnt: BUFFER STD_LOGIC_VECTOR (cntwidth-1 DOWNTO 0)

);

END ENTITY counter4;

ARCHITECTURE behave OF counter4 IS

BEGIN

co <= ‘1’ WHEN (qcnt = “1111” AND ci = ‘1’) ELSE ‘0’;

PROCESS (clk, nreset)

Ci

Co

BEGIN

Nreset CLK

std_logic 类型包含的数据: (’U’, ’X’ , ’0’ , ’1’ , ’Z’ , ’W’ , ’L’ , ’H’ , ’-’)

举例:4位计数器的实体描述

Ci Nreset

CLK

COUNTER4

Co Qcnt[3..0]

ENTITY counter4 IS

GENERIC (cntwidth : integer : =4)

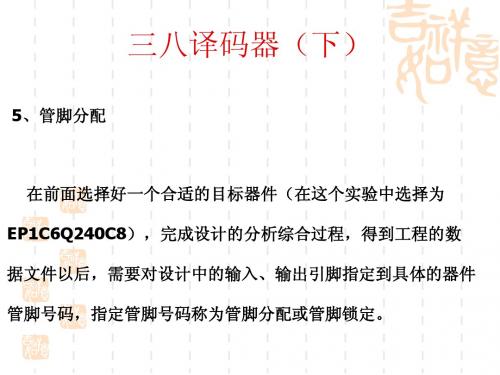

初识EDA--3三八译码器(下)

5-14

进入引脚分配界面

首先将要分配管脚的信号放置在To下方。双击To下方的 《New》,如图5-14所示则会出现如图5-15所示界面。

5-15

信号选择对话框

选择Node Finder…进入如图5-16所示的Node Finder对话框界面。 按图5-16中样例设置参数。在Filter窗口选择Pins:all,在Named窗 口中输入“*”,点击List在Nodes Found窗口出现所有信号的名称, 点击中间的 按钮则Selected Nodes窗口下方出现被选择的端口 名称。

5)如果软件已运行一个工程,则在打开编程器的时候,编程器 窗口会自动出现这个工程文件要加载到目标器件的文件,如果要加 载其它文件可以从其它地方进行添加更改。选好加载文件后,再点 选Progam/Configure,编程模式选取JTAG模式,点击STRAT进 行文件加载,直到加载进度变为100%,文件成功加载完成。 6)手动控制实验箱上的K1、K2、K3即可观察到实验结果

步骤一:在Assignment Name栏内双击后,在下拉菜单中选中Location (Accepts wildcards/groups)选项

步骤二:在Value栏下填入实验箱管脚121,注意各实验箱对应的管脚也不同, 也可选择该实验箱上其他任意不同的管脚

步骤三:管脚填写完毕后,字体颜色自动变黑,则填写正确 5-18 给A端口进行管脚分配

器件EP1C6Q240C8进行加载的方法。

在程序加载之前,注意,一定要先完成管脚的分配和 定义,然后将管脚分配的文件保存,让 图标上方的*消失后,再进行编译,编译正确无误之后, 才可以进行程序下载!

1)将实验箱插上电源插头。 2)使用USB下载电缆插入USB-Blaster端口中,用手轻轻握住 USB-Blaster 连接盒,注意在没有下载完成前不要轻易放下,以免 连接盒磕碰后造成USB指示灯熄灭。观察连接盒上中间的USB指示 灯点亮后,则可进入到下一步设置。若不亮则需要重新拔出下载电 缆,再重新操作,直至USB指示灯点亮。 3)选择QUARTUSII软件的Tool>Programmer命令,弹出编 程器窗口,无论图中的No Hardware项,是否曾经设置,都需要 对其进行重新设置,如图5-32所示。

eda三个阶段cmos asic

eda三个阶段cmos asic

EDA技术伴随着计算机。

集成电路。

电子系统设计的发展,经历了三个发展阶段。

1、计算机辅助设计,简称CAD.20世纪70年代,集成电路制作方面MOS工艺已得到广泛的应用。

可编程逻辑技术及其器件已经问世,计算机作为一种运算工具已在科研领域得到广泛的应用。

人们开始用计算机进行IC版图编辑和H@I布局布线&取代了手工操作。

2、计算机辅助工程阶段,简称CAE.80年代为CAE阶段,此时的EDA工具可以完成原理图输入。

逻辑综合。

逻辑仿真。

电路分析。

自动布局布线。

尽管EDA技术取得了巨大的成功,但是从设计输入到设计输出的各个软件工具都是互相独立的,互不兼容,影响设计环节的衔接。

而且软件界面千差万别,学习使用困难。

3、电子设计自动化简称EDA进入20世纪90年代,随着计算机辅助工程。

辅助分析和辅助设计在电子技术领域获得更加广泛的应用,与此同时电子技术在通信。

计算机及家电产品生产中的市场需求和技术需求,极大地推动了全新的电子设计自动化技术的应用和发展。

这时的EDA工具不仅具有电子设计的能力,而且能够提供独立于工艺和厂家的系统设计能力,具有高级抽象的设计构思手段。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

VHDL中有两种方式描述状态机 ⑴符号状态机——用符号表示每个状态。 例如:type week is(mon,tue,wed,sur,fri,sat,sun); type state is(s0,s1,s2); type light is(red,green,yellow); ⑵编码状态机——要求设计每个状态的状态寄存器的值 (二进制编码状态机、格雷码编码状态机、一个有效 编码状态机)。 二进制编码状态机:每一个状态用二进制位来编码 例:实现4状态的状态机,四个状态分别为 “00”, “01” “10”, “11” 特点:触发器使用较少,速度较慢,可能产生两位 同时翻转的情况。如:“01”->“10”。 格雷码状态机:每次仅一个状态位的值发生变化 例:四状态状态机的状态分别为“00”, “01” “11”, “10” 特点:触发器使用较少,速度较慢,不会产生两 位同时翻转的情况。当状态位的输出被异步应用时, 格雷码编码是特别有益的。

q0<=“1111110” when tc(3 downto 0)=“0000” else “0110000” when tc(3 downto 0)=“0001 else … “0000000”; q1<=“1111110” when tc(7 downto 4)=“0000” else “0110000” when tc(7 downto 4)=“0001 else … “0000000”;

简单交通灯 红、黄、绿灯分别亮25、5、25秒。 计数用BCD码,计数结果接数码管 Entity light4 is Port(cp,clr:in std_logic; Q:out std_logic_vector(2 downto 0); q0,q1:out std_logic_vector(6 downto 0)); End light4; Architecture a of light4 is type state is(s0,s1,s2); signal nowstate:state; Singal tc:std_logic_vector(7 downto 0); Begin Process(cp,clr) Begin

如交通灯的电路,三个状态,之间的转换关系如下: RESET (asynchronous)

RED

TIMER2

TIMER3

TIMER1

GREEN

TIMER2

YELLOW

TIMER1 R='1'

⑵编码状态机——要求设计每个状态的状态寄存器的值(二进制 编码状态机、格雷码编码状态机、一个有效编码状态机)。 ONE HOT的编码方案:对每一个状态采用一个触发器。 例:实现4状态的状态机,其ONE HOT编码可为 状态1=“0001”状态2=“0010”状态3=“0100”状态4=“1000” 特点:触发器使用较多,但逻辑简单,速度快

If clr=„1‟ then Nowstate<=s0;Tc<=“00000000”; Elsif cp‟event and cp=„1‟ then case a is when s0=> … when s1=> … when s2=> … when others=> nowstate<=s0; tc<=“000000000”; end case; End if; End process; Q<=“100” when nowstate=s0 else “010” when nowstate=s1 else “001”;

4分频电路

Type 列举名称 is(元素1…元素n); For example: type state is(s0,s1,s2,s3); signal a:state; case a is when s0=> when s1=> when s2=> when other s => ; Entity fenpin4 is Port(cp,clr:in std_logic; Q:out std_logic); End fepin4;

第三部分内容,数组、状态、循环、元件例化等4学时

列举数据类型

Type 列举名称 is(元素1,元素2,元素n); For example: type state is(s0,s1,s2,s3); signal a:state; case a is when s0=> when s1=> when s2=> when others;

Architecture a of fenpin4 is type state is(s0,s1,s2,s3); signal nowstate:state; Begin Process(cp,clr) Begin If clr=„1‟ then Nowstate<=s0; Elsif cp‟event and cp=„1‟ then case Nowstate is when s0=> nowstate<=s1; when s1=>nowstate<=s2; when s2=> nowstate<=s3; when others=>nowstate<=s0; end case; End if; End process; Q<=„1‟ when nowstate=s3 else „0‟; End a;

If clr=„1‟ then Nowstate<=s0;Tc<=“00000000”; 简单交通灯 Elsif cp‟event and cp=„1‟ then case nowstate is 红、黄、绿灯分别亮25、5、25秒。 when s0=> 计数用BCD码 if tc=“00100100” then nowstate<=s1; tc<=“00000000”; elsif tc(3 downto 0)=“1001” then Entity light3 is tc(3 downto 0)<=“0000”; Port(cp,clr:in std_logic; tc(7 downto 4)<=tc(7 downto 4)+1; Q:out std_logic_vector(2 downto 0)); else tc<=tc+1; end if; End light3; when s1=> if tc=“00100” then nowstate<=s2; tc<=“00000”; Architecture a of light3 is else tc<=tc+1; end if; type state is(s0,s1,s2); when s2=> signal nowstate:state; … when others=> Singal tc:std_logic_vector(7 downto 0); nowstate<=s0; tc<=“000000000”; Begin end case; Process(cp,clr) End if; Begin End process; Q<=“100” when nowstate=s0 else “010” when nowstate=s1 else “001”; End a;

• 根据状态机复杂程度 状态特别多的系统只能采用2进制编码或格雷码编码 • 根据器件类型 FPGA一般采用ONE HOT编码,CPLD一般采用2进制编码或 格雷码编码 • 从非法状态中退出 在选择编码方案时,必须考虑状态机可能进入的潜在的 非法状态数目。如果违反了状态位触发器的建立或保持时间, 又没有定义所有可能出现的状态,则你的设计会终止在非法 状态上。

End a;

练习 1、红、黄、绿灯分别亮25、5、25秒。计数用 BCD码,计数结果接数码管,计数用减法。 2、双向交通灯设计,只要求灯亮,不要求显示时 间。

3、双向交通等设计,要求显示时间。

4、彩灯变化000-001-010-100-111 (两种实现方式:状态,计数)

状态机设计 1有限状态机(FSM,Finite Nowstate<=s0;Tc<=“00000”; 简单交通灯 Elsif cp‟event and cp=„1‟ then case nowstate is 红、黄、绿灯分别亮25、5、25秒。 when s0=> if tc=“11000” then Entity light2 is nowstate<=s1; tc<=“00000”; Port(cp,clr:in std_logic; else tc<=tc+1; end if; Q:out std_logic_vector(2 downto 0)); when s1=> End light2; if tc=“00100” then nowstate<=s2; tc<=“00000”; else tc<=tc+1; end if; when s2=> if tc=“11000” then Architecture a of light2 is nowstate<=s0; tc<=“00000”; type state is(s0,s1,s2); else tc<=tc+1;end if; signal nowstate:state; when others=> nowstate<=s0; tc<=“00000”; Singal tc:std_logic_vector(5 downto 0); end case; Begin End if; Process(cp,clr) End process; Begin Q<=“100” when nowstate=s0 else “010” when nowstate=s1 else “001”; End a;

时序电路的设计 ①逻辑抽象,绘制状态转换图; ②状态化简; ③状态编码; ④选定触发器,求出状态方程、驱动方程、输出方程。 时序电路的时序操作(控制)过程是由状态转换图或状态 转换表来反映 抛开电路的具体含义,时序电路的通用模型就是有限状态机 利用VHDL语言将时序电路的状态转换关系进行描述。在 VHDL中,所有状态均可表达为case_when结构中的一条case 语句,而状态的转移可以通过if_then_else语句实现。