dsp——cpu计数器中断

dsp 第11章 三级中断系统

第3步 中断函数的处理

interrupt void TINT0_ISR(void) // CPU-Timer0中断函数 {

…… …… CpuTimer0Regs.TCR.bit.TIF=1; //清除定时器中断标志位 PieCtrl.PIEACK.bit.ACK1=1; //响应同组其他中断 EINT; //开全局中断 }

INTx.8

INTx.7

INTx.6

INTx.5

INTx.4

INTx.3

INTx.2

INTx.1

WAKEINT

TINT0

ADCINT

XINT2

XINT1

PDPINTB

PDPINTA

T1OFINT

T1UFINT

T1CINT

T1PINT

CMP3INT

CMP2INT

CMP1INT

CAPINT3

CAPINT2

22位的cpu中断向量一共可以支持32个cpu中断其中每一个中断都是一个32位的中断向量中断向量绝对地址优先级说明vmap0vmap1reset000000h3fffc0h1最高复位中断int1000002h3fffc2h可屏蔽中断1int2000004h3fffc4h可屏蔽中断2int3000006h3fffc6h可屏蔽中断3int4000008h3fffc8h可屏蔽中断4int500000ah3fffcah可屏蔽中断5int600000ch3fffcch10可屏蔽中断6int700000eh3fffceh11可屏蔽中断7int8000010h3fffd0h12可屏蔽中断8int9000012h3fffd2h13可屏蔽中断9int10000014h3fffd4h14可屏蔽中断10int11000016h3fffd6h15可屏蔽中断11int12000018h3fffd8h16可屏蔽中断12int1300001ah3fffdah17可屏蔽中断13int1400001ch3fffdch18可屏蔽中断14dlogint00001eh3fffdeh19最低可屏蔽数据标志中断rtosint000020h3fffe0h可屏蔽实时操作系统中断reserved000022h3fffe2h保留nmi000024h3fffe4h不可屏蔽硬件中断illegal000026h3fffe6h非法指令捕获ier寄存器ifr寄存器可屏蔽中断的响应过程多个中断申请时cpu响应过程中断a和中断b同时提出申请cpu如何处理

dsp原理与应用技术中的中断

DSP原理与应用技术中的中断什么是中断中断是指当处理器执行某个任务时,受到一个信号或事件的触发而暂停当前任务,跳转到指定的中断处理程序执行,处理完成后再返回原来的任务。

在DSP(数字信号处理)领域中,中断机制起着重要的作用。

中断可以分为硬件中断和软件中断两种。

硬件中断是由外部设备或芯片发出的中断信号触发,如计时器中断、外部设备输入中断等。

而软件中断是由程序的执行过程中的特殊指令或软件的调用而产生的中断。

DSP中的中断在DSP中,中断主要用于处理实时要求较高的应用,如音频处理、实时图像处理等。

中断的出现可以有效地降低系统的响应时间,提高系统的实时性。

DSP芯片通常提供多个中断向量,每个中断向量对应一个特定的中断源。

中断向量用来指示中断处理程序的入口地址,当中断发生时,处理器会根据中断向量跳转到相应的中断处理程序。

DSP中的中断优先级在DSP中,不同的中断有不同的优先级。

当多个中断同时发生时,处理器会根据中断优先级决定响应哪个中断。

中断优先级通常通过特定的寄存器配置。

处理器会根据中断触发的先后顺序以及中断优先级来决定响应的中断。

DSP中的中断处理过程中断处理过程通常包括以下几个步骤:1.中断触发:当中断源产生中断信号时,处理器会检测中断信号,并做出响应。

2.中断优先级判断:处理器会根据中断优先级判断是否响应当前中断请求。

3.中断向量跳转:如果中断请求被接受,处理器会根据中断向量找到相应的中断处理程序的入口地址,并跳转到该地址处执行中断处理程序。

4.中断处理程序:中断处理程序是中断的实际执行部分,它会处理中断所需的任务,如保存寄存器状态、处理中断源的数据等。

5.中断结束:当中断处理程序执行完成后,处理器会返回到原来的任务继续执行,完成中断的处理过程。

DSP中的中断应用技术中断在DSP应用中有广泛的应用,如音频处理、图像处理、通信等方面。

下面列举几个常见的DSP中的中断应用技术:1.实时音频处理:中断机制可以使得DSP实时响应音频输入信号,实现实时的音频处理,如音效处理、语音识别、语音合成等。

DSP(TMS320C6713)入门之旅三、中断的理解和使用

学习一个芯片的功能时,我的建议是先学会如何用C语言点亮一个LED灯,然后就是学习一下使用他的中断,因为在做芯片的时候,各个厂家有自己的一套自己的方法。

所以使用中断的就必须了解很多概念,比如如何打开中断,如何安装自己的中断子服务程序,等等!先介绍一下什么叫中断:你在下象棋,突然电话响了,你回屋接电话,然后回来继续下象棋,这个过程就叫做中断响应过程(中断过程)。

CPU执行正常任务———————下象棋保护现场———————————-你已经想好要―将军‖,先在脑海中记下来。

中断发生———————————-电话响-中断服务程序—————————-接电话恢复现场———————————-回来后恢复刚才想法中断返回———————————-你回来继续下象棋中断屏蔽———————————-Boss 正在训话,要求所有电话关机,你不能接电话了。

非屏蔽中断——————————-你内急,即使是Boss 在训话,你还是得到外面去嘘嘘。

可屏蔽中断——————————-你在―闭关修炼‖,可以不受外界干扰所以我们在使用中断之前先得告诉CPU,我们要使用那个中断,当中断发生的时候,你的执行程序的去向(也就是中断服务子程序),最后在返回我们被中断的函数。

这样就完成了我们的中断历程!看看6713执行中断的流程:一、使能了全局中断和子中断,那么CPU每执行一条指令之前就去查询一下有没有中断被置位,如果有产生的,那么CPU就要跳转!二、软件把CPU内部的寄存器A0~A15,B0~B15,等等这些寄存器的值推入堆栈保存,把当前PC寄存器的值放入IRP寄存器中以备中断返回能找到当前被打断的位置(保存现场,中断函数前面得加interrupt关键字)三、CPU的PC指针读出中断向量表的地址,也就是把(ISTP寄存器的值+子中断向量偏移量)装入PC寄存器,这样就执行跳转。

四、在中断向量表里一般有就用跳转指令,这样就可以跳转到我们用C语言编写的中断服务子程序中。

DSP中断使用

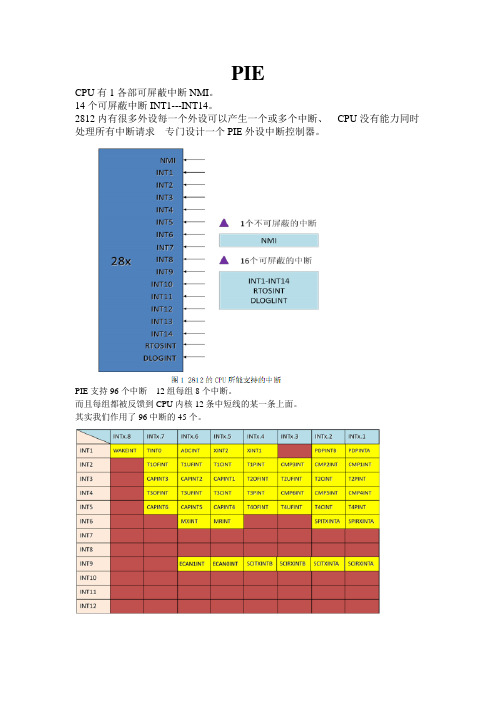

PIECPU有1各部可屏蔽中断NMI。

14个可屏蔽中断INT1---INT14。

2812内有很多外设每一个外设可以产生一个或多个中断、CPU没有能力同时处理所有中断请求专门设计一个PIE外设中断控制器。

PIE支持96个中断12组每组8个中断。

而且每组都被反馈到CPU内核12条中短线的某一条上面。

其实我们作用了96中断的45个。

CPU是3级中断机制外设级PIE 级CPU级。

对于一个具体的外设中断请求,一个不许可CPU不会执行该中断。

当某个外设中断事件发生了,这个外设某个寄存器和该中断标志置1如果该中断的中断使能位被置1 外设就会向PIE发送中断请求,否则不会往PIE发送中断请求。

不管什么情况下外设中断标志寄存器中断中断标志必须手动清除例如每一组PIE 都有个标志寄存器PIEIFRx 使能寄存器PIEIERx 还有个相应寄存器ACK一组同时一个中断被响应因为PIEACK 寄存器12位对应INT1 --12有中断PIEACK对应位置 1 等待手动清除(标志寄存器自动清除)才能响应同组下一个中断(如果中断请求还在)。

DINT; //禁止中断在设置某些寄存器的时候EINT; // Enable Global interrupt INTMERTM; // Enable Global realtime interrupt DBGMEALLOW; // This is needed to write to EALLOW protected registers 写自由EDIS; // This is needed to disable write to EALLOW protected registers 禁止写某些特殊寄存器下列寄存器受EALLOW 保护:·器件仿真寄存器·闪存寄存器· CSM 寄存器· PIE 矢量表·系统控制寄存器· GPIO MUX 寄存器·某些eCAN 寄存器所以简单点说,就是有些寄存器受到写保护的,你要写它,就首先要用EALLOW禁止写保护.写完了之后别忘了用EDIS再是能写保护.CPU级也有IFR IER CPU接到中断请求暂停现在执行的程序清除IER IFR EALLOW 、INTM置位就不响应其他中断1、PieVectTable.T1PINT = &eva_timer1_isr;2、// Enable PIE group 2 interrupt 4 for T1PINTPieCtrl.PIEIER2.all = M_INT4;3、IER |= (M_INT2 | M_INT3 | M_INT4 | M_INT5);4、interrupt void eva_timer1_isr(void)。

DSP中断设置简明教程

DSP中断设置简明教程DSP中断是一种用于处理实时信号的技术,允许处理器在执行其他任务时,响应外部事件或处理即时数据。

中断是一种非常重要的工具,用于实时系统中,例如音频处理、图像处理等领域。

本文将为您提供一个简明的DSP中断设置教程,帮助您了解如何在DSP中实现中断处理。

首先,我们需要了解DSP中断的基本原理和概念。

DSP中断是一种在执行主线程任务的过程中,当特定的事件发生时,系统自动中止主线程,并转而执行预定义的中断服务子程序(ISR)。

当ISR执行完毕后,系统将返回到主线程继续执行之前的任务。

因此,中断允许DSP准时响应外部事件,并在需要时采取必要的动作。

在DSP中,中断是通过中断控制器实现的。

中断控制器是一种硬件模块,用于检测外部事件并触发相应的中断。

通常,中断控制器有多个中断通道,每个通道可以连接一个外设,如定时器、ADC、UART等。

当外设的中断条件满足时,中断控制器会发送一个中断请求信号给DSP处理器。

下面是一个简单的DSP中断设置步骤:1.确定中断请求源:首先,确定哪个外设将触发中断。

例如,如果您想设置一个定时器中断,那么您需要选择一个定时器作为中断请求源。

2.配置中断控制器:将中断请求源连接到中断控制器的中断通道上。

这通常需要在DSP的寄存器中写入相应的配置值来选择中断通道。

3.编写中断服务子程序(ISR):中断服务子程序是一个函数,用于处理中断事件。

当中断发生时,DSP将暂停正在执行的主线程,并转而执行ISR。

在ISR中,您可以编写自己的处理逻辑,例如读取数据、计算、更新状态等。

4.配置中断向量表:中断向量表是一个存储中断服务子程序地址的表格。

在DSP启动或重新配置中断时,需要将ISR的地址写入中断向量表,以便DSP能够正确调用ISR。

5.启用中断:在DSP的控制寄存器中,设置相应的中断使能位,以启用中断功能。

这将使DSP能够接收到来自中断控制器的中断请求。

6.处理中断请求:当外设满足中断条件时,中断控制器会发送中断请求信号给DSP。

第6章 DSP中断系统

• •

2.不可屏蔽中断(NMI) 不可屏蔽中断(NMI)为第二优先级的中断,通常用来向CPU发出类似突然掉电 之类的硬件问题告警。为了处理该中断,中断使能寄存器中的NMIE位必须置 1。如果NMIE位置1,阻止NMI处理的唯一条件是在分支跳转的延迟时间段内 发生不可屏蔽中断。

3.可屏蔽中断(INT4~INT15) 假设一个可屏蔽中断不在分支跳转的延迟阶段发生,则必须满足如下条件时可

屏蔽中断才能被处理:

控制状态寄存器(CSR)中的全局中断使能位(GIE)置1;

中断使能寄存器(IER)中的NMIE位置1;

IER中的相应中断使能位置1; 相应的中断发生,将中断标志寄存器(IFR)的相应为置1,且在IFR中设置更高

优先级的中断标志(IF)位。

4.中断应答(IACK和INUMX) IACK和INUMX信号通知TMS320C6000外部硬件,正在对发生的中断进行处理。 IACK信号指出CPU已经开始处理一个中断。INUMX信号(INUM3~INUM0)指出正在 处理的是哪个中断。 例如: INUM3 = 0 (MSB) INUM2 = 1 INUM1 = 1 INUM0 = 1 (LSB)

5~9

HPEINT

10~31

ISTB

【例6.1】 中断服务部的重定位。 (1)重定位IST到800h: 将地址为0h~200h的IST复制到地址800h~A00h之间。 写800h到ISTP寄存器: MVK 800h, A2 MVC A2, ISTP ISTP = 800h = 1000 0000 0000b (2)ISTP引导CPU到重定位的IST对应的ISFP: 假设:IFR = BBC0h = 1011 1011 1100 0000b IER = 1230h = 0001 0010 0011 0001b

2)DSP系统控制及中断

void InitSysCtrl(void) {

// Disable the watchdog

DisableDog();

// Initialize the PLLCR to 0xA

实验时,注意使能所使用的 外设模块时钟,否则无法读 写相应的外设寄存器。 PLLCR通常设为10,即CPU 的时钟频率为30MHz×5。

oscclkn2锁相环控制寄存器pllcr0x0000702130mhz15mhz15150mhz20151225hispcphispcphispcp高速外设时钟设置寄存器pllcrpll控制寄存lospcp慢速外设时钟设置寄存器scsr系统控制和状态寄存器pclkcr外设时钟控制寄存器wdcntr看门狗计数寄存器lpmcr0低功耗模式控制寄存器0wdkey看门狗复位key寄存器lpmcrl低功耗模式控制寄存器1wdcr看门狗控制寄存器第第22章章cpucpu内部结构与时钟系统内部结构与时钟系统第第22章章cpucpu内部结构与时钟系统内部结构与时钟系统20151225数据存储空间0x0000701c时钟寄存器高低速外设时钟寄存器hispcplospcp0x0000701ab数据存储空间0x00007022保留d15d14d13d12d11d10d9d8ecanenclkmcbspenclkscibenclkspienclkr0rw0r0rw0rw0reservedd15d3d2d1d0wdintswdenintwdoverrider0r1rw0rw1c1sciaenclk保留保留保留adcenclk保留evaenclkevbenenclkd7d4d3d2d1d0r0rw0r0rw0rw0rw0r0rw0reservedd15d3d2d0hspcklspckr0rw010第第22章章cpucpu内部结构与时钟系统内部结构与时钟系统第第22章章cpucpu内部结构与时钟系统内部结构与时钟系统10设置系统时钟clkinfunctioninitializespllcrregister

DSP实验-定时器中断实验

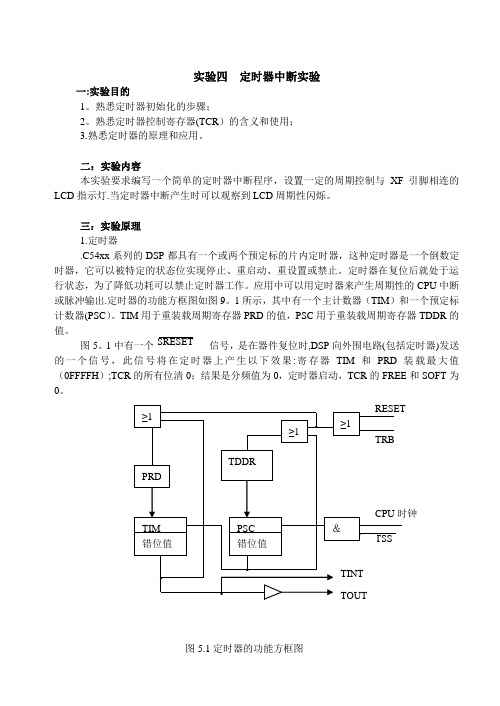

实验四 定时器中断实验一:实验目的1。

熟悉定时器初始化的步骤;2。

熟悉定时器控制寄存器(TCR )的含义和使用;3.熟悉定时器的原理和应用。

二:实验内容本实验要求编写一个简单的定时器中断程序,设置一定的周期控制与XF 引脚相连的LCD 指示灯.当定时器中断产生时可以观察到LCD 周期性闪烁。

三:实验原理1.定时器.C54xx 系列的DSP 都具有一个或两个预定标的片内定时器,这种定时器是一个倒数定时器,它可以被特定的状态位实现停止、重启动、重设置或禁止。

定时器在复位后就处于运行状态,为了降低功耗可以禁止定时器工作。

应用中可以用定时器来产生周期性的CPU 中断或脉冲输出.定时器的功能方框图如图9。

1所示,其中有一个主计数器(TIM )和一个预定标计数器(PSC )。

TIM 用于重装载周期寄存器PRD 的值,PSC 用于重装载周期寄存器TDDR 的值。

图5。

1信号,是在器件复位时,DSP 向外围电路(包括定时器)发送的一个信号,此信号将在定时器上产生以下效果:寄存器TIM 和PRD 装载最大值(0FFFFH );TCR 的所有位清0;结果是分频值为0,定时器启动,TCR 的FREE 和SOFT 为0。

定时器实际上是有20bit 的周期寄存器.它对CLKOUT 信号计数,先将PSC (TCR 中的D6~D9位)减1,直至PSC 为0,然后把TDDR (TCR 中的低4位)重新装载入PSC,同时将TIM 减1,直到TIM 减为0.这时CPU 发出TINT 中断,同时在TOUT 引脚输出一个脉冲信号,脉冲宽度与CLKOUT 一致,然后将PRD 重新装入TIM ,重复下去直到系统或定时器复位.定时器产生中断的计算公式如下:TINT t c 为 CLKOUT 的周期)TIM :定时器寄存器,用于装载周期寄存器值并自减1。

PRD :周期寄存器,用于装载定时器寄存器。

TCR :定时器控制寄存器,包含定时器的控制状态位。

DSP 第3讲 中断系统

§3.11 中断和中断向量表

中断号(K) 优先级 名 称 向量位置 功 能

16

17 18 19 20 21 22

3

4 5 6 7 8 9

INT0/SINT0

INT1/SINT1 IN12/SINT2 TINT0/SINT3 BRINT0/SINT4 BXINT0/SINT5 DMAC0/SINT6

§3.12 VC5402的中断向量表文件—续

RESET: ;复位中断,优先级最高 BD _c_int00 ;执行完该语句下面的一条语句后,跳转到_c_int00处 STM #128,SP ;设置堆栈大小为128个字 nmi:RETE ;nmi非屏蔽中断返回,下面依次为VC5402的各个中断, NOP ;每个只占4个字节 NOP NOP sint17 .space 4*16 ;VC5402的软中断 sint18 .space 4*16 ;.space表示开辟空间(单位:bit) sint19 .space 4*16 sint20 .space 4*16 sire21 .space 4*16 sint22 .space 4*16 sint23 .space 4*16 sint24 .space 4*16 sint25 .space 4*16 sint26 .space 4*16 sint27 .space 4*16 sint28 .space 4*16 sint29 .space 4*16 sint30 .space 4*16 ;这部分可以直接写为 .space 14*4*16

(3)IMR屏蔽位为1。(使能一个中断)

§3.6 执行中断服务程序(ISR)

当应答中断后,CPU会采取如下的操作:

DSP芯片的中断系统

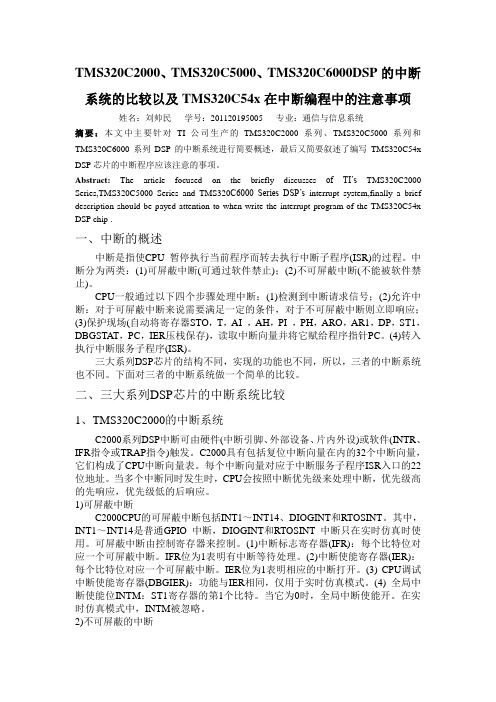

TMS320C2000、TMS320C5000、TMS320C6000DSP的中断系统的比较以及TMS320C54x在中断编程中的注意事项姓名:刘帅民学号:201120195005 专业:通信与信息系统摘要:本文中主要针对TI公司生产的TMS320C2000系列、TMS320C5000系列和TMS320C6000系列DSP的中断系统进行简要概述,最后又简要叙述了编写TMS320C54x DSP芯片的中断程序应该注意的事项。

Abstract:The article focused on the briefly discusses of TI’s TMS320C2000 Series,TMS320C5000 Series and TMS320C6000 Series DSP’s interrupt system,finally a brief description should be payed attention to when write the interrupt program of the TMS320C54x DSP chip .一、中断的概述中断是指使CPU 暂停执行当前程序而转去执行中断子程序(ISR)的过程。

中断分为两类:(1)可屏蔽中断(可通过软件禁止);(2)不可屏蔽中断(不能被软件禁止)。

CPU一般通过以下四个步骤处理中断:(1)检测到中断请求信号;(2)允许中断:对于可屏蔽中断来说需要满足一定的条件,对于不可屏蔽中断则立即响应;(3)保护现场(自动将寄存器STO,T,AI ,AH,PI ,PH,ARO,AR1,DP,ST1,DBGSTAT,PC,IER压栈保存),读取中断向量并将它赋给程序指针PC。

(4)转入执行中断服务子程序(ISR)。

三大系列DSP芯片的结构不同,实现的功能也不同,所以,三者的中断系统也不同。

下面对三者的中断系统做一个简单的比较。

二、三大系列DSP芯片的中断系统比较1、TMS320C2000的中断系统C2000系列DSP中断可由硬件(中断引脚、外部设备、片内外设)或软件(INTR、IFR指令或TRAP指令)触发。

DSP中断设置示例简明教程

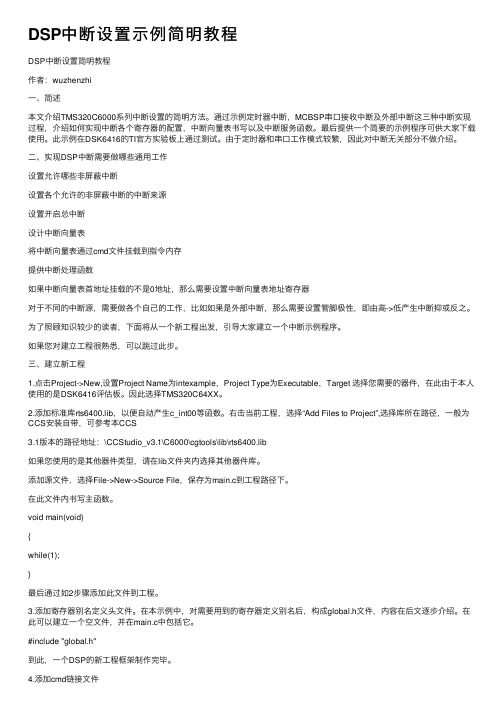

DSP中断设置⽰例简明教程DSP中断设置简明教程作者:wuzhenzhi⼀、简述本⽂介绍TMS320C6000系列中断设置的简明⽅法。

通过⽰例定时器中断,MCBSP串⼝接收中断及外部中断这三种中断实现过程,介绍如何实现中断各个寄存器的配置,中断向量表书写以及中断服务函数。

最后提供⼀个简要的⽰例程序可供⼤家下载使⽤。

此⽰例在DSK6416的TI官⽅实验板上通过测试。

由于定时器和串⼝⼯作模式较繁,因此对中断⽆关部分不做介绍。

⼆、实现DSP中断需要做哪些通⽤⼯作设置允许哪些⾮屏蔽中断设置各个允许的⾮屏蔽中断的中断来源设置开启总中断设计中断向量表将中断向量表通过cmd⽂件挂载到指令内存提供中断处理函数如果中断向量表⾸地址挂载的不是0地址,那么需要设置中断向量表地址寄存器对于不同的中断源,需要做各个⾃⼰的⼯作,⽐如如果是外部中断,那么需要设置管脚极性,即由⾼->低产⽣中断抑或反之。

为了照顾知识较少的读者,下⾯将从⼀个新⼯程出发,引导⼤家建⽴⼀个中断⽰例程序。

如果您对建⽴⼯程很熟悉,可以跳过此步。

三、建⽴新⼯程1.点击Project->New,设置Project Name为intexample,Project Type为Executable,Target 选择您需要的器件,在此由于本⼈使⽤的是DSK6416评估板。

因此选择TMS320C64XX。

2.添加标准库rts6400.lib,以便⾃动产⽣c_int00等函数。

右击当前⼯程,选择“Add Files to Project”,选择库所在路径,⼀般为CCS安装⾃带,可参考本CCS3.1版本的路径地址:\CCStudio_v3.1\C6000\cgtools\lib\rts6400.lib如果您使⽤的是其他器件类型,请在lib⽂件夹内选择其他器件库。

添加源⽂件,选择File->New->Source File,保存为main.c到⼯程路径下。

DSP系统配置和中断_图文(精)

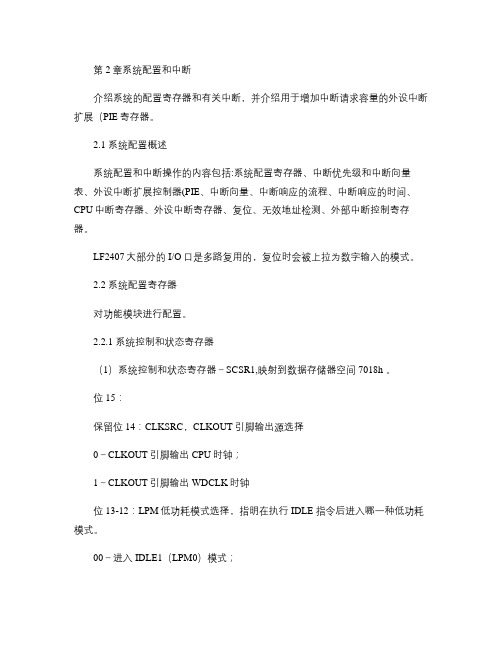

第2章系统配置和中断介绍系统的配置寄存器和有关中断,并介绍用于增加中断请求容量的外设中断扩展(PIE寄存器。

2.1 系统配置概述系统配置和中断操作的内容包括:系统配置寄存器、中断优先级和中断向量表、外设中断扩展控制器(PIE、中断向量、中断响应的流程、中断响应的时间、CPU中断寄存器、外设中断寄存器、复位、无效地址检测、外部中断控制寄存器。

LF2407大部分的I/O口是多路复用的,复位时会被上拉为数字输入的模式。

2.2 系统配置寄存器对功能模块进行配置。

2.2.1 系统控制和状态寄存器(1)系统控制和状态寄存器-SCSR1,映射到数据存储器空间7018h 。

位15:保留位14:CLKSRC,CLKOUT引脚输出源选择0-CLKOUT引脚输出CPU时钟;1-CLKOUT引脚输出WDCLK时钟位13-12:LPM低功耗模式选择,指明在执行IDLE 指令后进入哪一种低功耗模式。

00-进入IDLE1(LPM0)模式;01-进入IDLE2(LPM1)模式;1x -进入HALT (LPM2)模式。

位11-9:PLL时钟预定标选择,对输入时钟选择倍频系数。

000-4;001-2;010-1.33;011-1;100-0.8;101-0.66;110-0.57;111-0.5位8:保留位7:ADC CLKEN,ADC模块时钟使能控制位位6:SCICLKEN, SCI模块时钟使能控制位位5:SPICLKEN, SPI模块时钟使能控制位位4:CANCLKEN, CAN模块时钟使能控制位位3:EVBCLKEN, EVB模块时钟使能控制位位2:EVACLKEN, EVA模块时钟使能控制位0:禁止模块时钟(节能);1:使能模块时钟,且运行位1:保留位0:ILLADR, 无效地址检测位当检测到一个无效地址时,该位被置1,该位需软件清除,写0即可。

初始化时该位写0。

注意:任何无效的地址会导致NMI事件发生。

(2)系统控制和状态寄存器2-SCSR2映射到数据存储器空间7019h 。

DSP的中断学习

(2)、中断初始化 • 中断标志寄存器IFR中的定时中断位TINT=1,清除未 处理完的定时中断。 • 中断屏蔽寄存器IMR中的定时屏蔽位TINT=1,开放定 时中断。 • 状态控制寄存器ST1中的中断标志位INTM清0,开放 全部中断。 (3)、程序清单:

2、脉冲频率检测

其中,定时器控制寄存器TCR包括:预标定分频系 数TDDR,预标定计数器PSC、控制位TRB和TSS等及相 应的逻辑控制电路组成。

TCR中包含有定时器的控制位和状态位:

注1:

• 正常工作情况下,当TIM减到0后,PRD中的时间常 数自动地加载到TIM。当系统复位或定时器单独复位 时,PRD中的时间常数重新加载到TIM。 • 复位后,定时器控制积存器(TCR)的停止状态位 TSS=0,定时器启动工作,时钟信号CLKOUT加到预 定标计数器PSC。 • PSC也是一个减1计数器,每当复位或减到0后,自动 将定时器分频系数TDDR加载到PSC。 所以,定时中断的周期为: CLKOUT*(TDDR+1)*(PRD+1) • 若要关闭定时器,只要将TCR的TSS置1,就能切断时 钟输入,定时器停止工作。

二、时钟发生器

时钟发生器为C54X提供时钟信号。时钟发生器由 内部振荡器和锁相环(PLL)电路两部分组成。时钟发 生器要求有一个参考时钟输入,可以有两种方法提供:

C54X内部的PLL兼有频率放大和信 号提纯的功能。用高稳定的参考振荡器 锁定,可以提供高稳定的频率源。所以, C54X的外部频率源的频率可以比CPU的 机器周期CLKOUT的速率低,这样就能 降低因高速开关时钟所造成的高频噪声。

3、中断服务程序

CPU执行中断服务程序的步骤如下: • 保护现场,将PC值压入栈顶; • 载入中断矢量表,将中断矢量表地址送入PC; • 执行中断矢量表中指令,程序进入中断入口; • 执行中断服务程序,直至遇到返回指令; • 恢复现场,将栈顶值弹回PC; • 继续主程序。

DSP中断概述及中断源

DSP中断概述及中断源

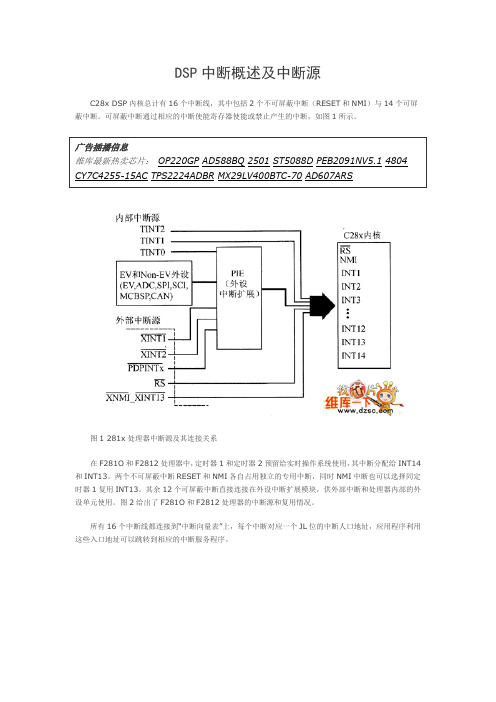

C28x DSP内核总计有16个中断线,其中包括2个不可屏蔽中断(RESET和NMI)与14个可屏蔽中断。

可屏蔽中断通过相应的中断使能寄存器使能或禁止产生的中断,如图1所示。

图1 281x处理器中断源及其连接关系

在F281O和F2812处理器中,定时器1和定时器2预留给实时操作系统使用,其中断分配给INT14和INT13。

两个不可屏蔽中断RESET和NMI各自占用独立的专用中断,同时NMI中断也可以选择同定时器1复用INT13。

其余12个可屏蔽中断直接连接在外设中断扩展模块,供外部中断和处理器内部的外设单元使用。

图2给出了F281O和F2812处理器的中断源和复用情况。

所有16个中断线都连接到“中断向量表”上,每个中断对应一个JL位的中断人口地址,应用程序利用这些入口地址可以跳转到相应的中断服务程序。

图2 F2810和F2812的中断源和复用情况

欢迎转载,信息来源维库电子市场网()。

DSP中断

2、中断矢量表 DSP产生中断时,要使得程序能跳转到中断服务子

程序执行,则需要在中断矢量处放置一条跳转指令。 如:

RS B _c_int00 (占2个字) 对于多个中断时,注意地址的对应。如系统中断有:

中断号0(RS)、中断号3(SINT18)。跳转指令如 下:

RS B _c_int00

.word 0,0,0,0,0,0,0,0,0,0

1、vectors.asm文件编写

.ref _c_int00, _NMI_INT,_SOFT_INT,_add_INT

RS NMI SINT2 SINT3 SINT4

.sect ".vectors"

B

_c_int00

NOPNΒιβλιοθήκη PB_NMI_INT

NOP

NOP

B

_SOFT_INT

NOP

NOP

B

_SOFT_INT

SINT18 B

_sint18

.sect ".vectors"

RS NMI SINT2 SINT3 SINT4 SINT5

B NOP NOP

NOP NOP B NOP NOP B NOP NOP B NOP NOP B NOP NOP

_c_int00

B

_NMI_INT

_SOFT_INT

_SOFT_INT

Void interrupt _SOFT_INT() {return;}

Int add(int x1,int x2,int x3,int x4,int x5) {int y; Y=x1+x2+x3+x4+x5; Return y; }

练习:

当INT0引脚出现中断请求时,要求DSP能响 应该中断,并使得XF引脚状态取反。

DSP 4 中断处理

DSP与嵌入式系统

代码解释

END OF PART IV

DSP与嵌入式系统

0.2 中断的重要性

• 中断是外界通知嵌入式系统的重要通 道,是嵌入式系统获取外界信息的重要 来源。 • 如果没有中断,嵌入式系统就成为一个 封闭的,非实时的孤立的系统。 • 系统内部调度的重要依据!

DSP与嵌入式系统

1 中断的概念与重要性

• 类比于单片机系统: 中断重要性 中断处理过程 处理要求 涉及外围硬件 单片机系统 非常重要 相对简单 短、平、快 数量不多 嵌入式系统 非常重要 比较复杂,分 上、下层处理 短、平、快 情况复杂,数 量巨大

DSP与嵌入式系统

中断处理的学习方法

• 相关基础知识的储备,对处理过程的 理解; • 对中断处理代码的阅读; • 实际动手操作;

嵌入式的最大特点就是实践性!

DSP与嵌入式系统

5 其他深入的课题讨论

零地址重映射 • 可重入中断 • 上述中断概念的代码表述

•

DSP与嵌入式系统

remap

• ARM体系结构要求在“0地址”建立 异常向量表; • 实际产品中,“0地址”必须事先放置 好上电启动所需的代码; 是否矛盾??

User mode r0-r12, r15, and cpsr

User mode r0-r12, r15, and cpsr

r13 (sp) r14 (lr)

r13 (sp) r14 (lr)

r13 (sp) r14 (lr)

r13 (sp) r14 (lr)

注意: System 模式使用的是 User 模式下的寄存器组

《DSP与嵌入式系统》

--4 中断处理 电子科学与工程学院 肖建

DSP与嵌入式系统

DSP6000中断概述_2

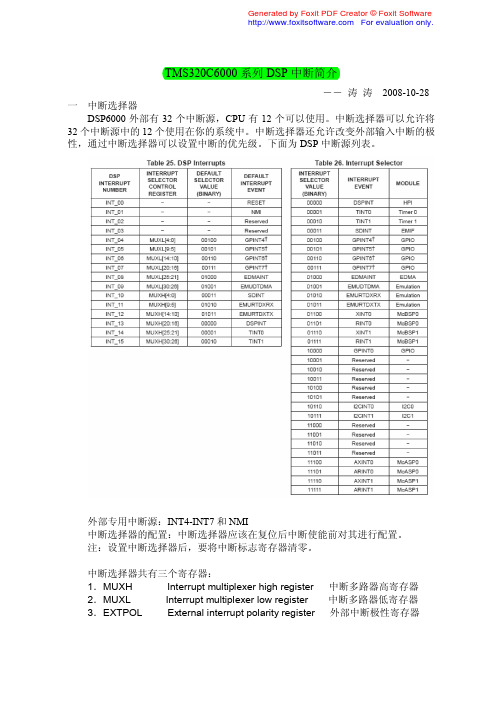

TMS320C6000系列DSP中断简介――涛涛2008-10-28 一中断选择器DSP6000外部有32个中断源,CPU有12个可以使用。

中断选择器可以允许将32个中断源中的12个使用在你的系统中。

中断选择器还允许改变外部输入中断的极性,通过中断选择器可以设置中断的优先级。

下面为DSP中断源列表。

外部专用中断源:INT4-INT7和NMI中断选择器的配置:中断选择器应该在复位后中断使能前对其进行配置。

注:设置中断选择器后,要将中断标志寄存器清零。

中断选择器共有三个寄存器:1.MUXH Interrupt multiplexer high register 中断多路器高寄存器2.MUXL Interrupt multiplexer low register 中断多路器低寄存器3.EXTPOL External interrupt polarity register 外部中断极性寄存器中断多路器高寄存器各位详细定义如上,具体定义了中断10到15的映射关系。

中断多路器低寄存器各位详细定义如上,具体定义了中断4到9的映射关系。

中断极性寄存器用来设置外部中断INT4-INT7触发DSP中断的时钟沿,当相应位设置为“0”时,为上升沿触发;当设为“1”时,为下即沿触发。

二.中断的类型C6000的中断可以分为3类:1.RESET2.非屏蔽中断3.可屏蔽中断RESET是优先级最高的中断,它连接到外部的RESET/管脚,非屏蔽中断NMI为第二优先级的中断,它对应外部的NMI管脚。

INT4-INT15为较低优先级的中断(INT15为最低)。

1.RESET复位是最高优先级的中断,用来将CPU返回到固定的状态复位是一个低有效信号,所有别的中断信号是高有效。

为了使CPU正确的初始化,复位低电平必须保持10个时钟周期。

正在执行的指令停止,寄存器回到默认状态复位的ISFP必须在地址“0”2.NMI非屏蔽中断要使能NMI中断,需将IER中的NMIE位置“1”,跳转的延迟等待会阻止NMI中断的进程。

C54x DSP中断

Copyright © 2003 Texas Instruments. All rights reserved.

中断分类

每个C54x DSP的中断,无论是硬件中断还是软件中断, 可以分成如下两大类: ☆ 可屏蔽中断——这些都是可以用软件来屏蔽或使能 的硬件和软件中断。 C54x DSP最多可以支持16个用户可屏 蔽中断。每种处理器只使用其中的一个子集。 ☆ 非屏蔽中断——这些中断是不能够屏蔽的。 C54x DSP总是响应这一类中断,并从程序转移到中断服务程序。 C54x DSP的非屏蔽中断包括所有的软件中断,以及两个外 部硬件中断/RS和/NMI。 /RS是一个对C54x DSP所有操作 方式产生影响的非屏蔽中断;而/NMI中断不会对C54x DSP 的任何操作模式产生影响。

中断是由硬件驱动或者软件驱动的信号,中断信号使C54x DSP暂停正在执行的程序,并进入中断服务程序(ISR)。 C54x DSP既支持软件中断,也支持硬件中断: ☆ 由程序指令(INTR、TRAP或RESET)请求的软件中断; ☆ 由外部物理设备信号请求的硬件中断,这种硬件中断有 两种形式: ◆ 受外部中断口信号触发的外部硬件中断; ◆ 受片内外设信号触发的内部硬件中断。 当同时有多个硬件中断被触发时, C54x DSP按照中断优 先级别的高低对它们进行服务。

Copyright © 2003 Texas Instruments. All rights reserved.

IFR 寄存器

Copyright © 2003 Texas Instruments. All rights reserved.

中断屏蔽寄存器

中断屏蔽寄存器也是一个存储器映射的CPU寄存器,主要用 来屏蔽外部和内部中断。如果状态寄存器ST1中的INTM位=0, IMR寄存器中的某一位为1,就使能相应的中断。 /RS和/NMI都 不包括在IMR中。