关于建立时间(setup-time)保持时间(hold-time)以及时序的一些问题集合

建立时间(setuptime)与保持时间(holdtime)---相关内容

建⽴时间(setuptime)与保持时间(holdtime)---相关内容静态时序分析:通过穷举分析每⼀条路径的延时,⽤以确定最⾼⼯作频率,检查时序约束是否满⾜,分析时钟质量。

动态时序分析:通过给定输⼊信号,模拟设计在器件实际⼯作的功能和延时情况。

1.什么是建⽴时间、保持时间? 建⽴时间指在触发器的时钟采样沿到来之前,数据保持稳定不变的时间。

保持时间指在触发器的时钟采样沿到来之后,数据保持稳定不变的时间。

因为时钟偏斜,到达DFF2为CLK2建⽴时间分析:取各组块最⼤延时计算考虑时钟到达DFF2的时钟偏斜Tskew,则建⽴时间余量为Tset_slack=Tclk-Tcq-Tco-Tsetup+Tskew,使DFF2建⽴时间不违例,需保证Tset_slack>0。

其中Tcq为DFF1的时钟端到输出延迟,为器件固定属性;Tco是组合逻辑电路的延时,可以通过优化逻辑设计改变其值,使其满⾜建⽴保持时间不违例;Tsetup为触发器固有属性,定值。

Thold为触发器固有属性,定值。

若不考虑DFF2的时钟偏斜,则建⽴时间裕量为Tset_slack=Tclk-Tcq-Tco-Tsetup。

保持时间分析:取各组块最⼩延时计算考虑时钟到达DFF2的时钟偏斜Tskew,则保持时间余量:Tskew+Thold+Thold_slack=Tcq+Tco,因此可推出Thold_slack=Tcq+Tco-Tskew-Thold,使保持时间不违例,则需Thold_slack>0。

若不考虑时钟偏斜,则Thold_slack=Tcq+Tco-Thold。

扩展:时钟抖动:两个时钟周期之间存在的差值,这种误差发⽣在时钟发⽣器内部,和晶振和PLL内部有关,布线对其没有影响。

主要表现在时钟频率上的不⼀定。

时钟偏斜:同样的时钟产⽣的多个⼦时钟信号之间的延时差异。

主要表现在时钟相位上的不确定。

影响时钟偏斜的原因:布线长度及负载,时钟偏斜⽆法避免。

DC 概论

Synopsys DC概论DC 概论之一setup time 与hold timesetup time 与hold time 在四楼有进一步的讨论。

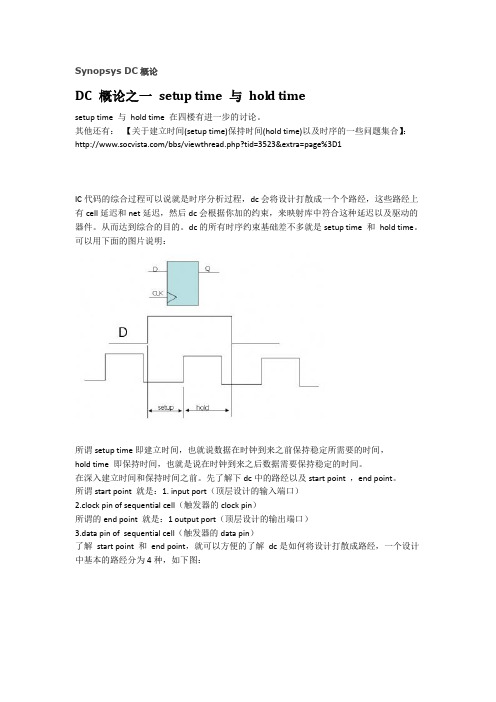

其他还有:【关于建立时间(setup time)保持时间(hold time)以及时序的一些问题集合】:/bbs/viewthread.php?tid=3523&extra=page%3D1IC代码的综合过程可以说就是时序分析过程,dc会将设计打散成一个个路经,这些路经上有cell延迟和net延迟,然后dc会根据你加的约束,来映射库中符合这种延迟以及驱动的器件。

从而达到综合的目的。

dc的所有时序约束基础差不多就是setup time 和hold time。

可以用下面的图片说明:所谓setup time即建立时间,也就说数据在时钟到来之前保持稳定所需要的时间,hold time 即保持时间,也就是说在时钟到来之后数据需要保持稳定的时间。

在深入建立时间和保持时间之前。

先了解下dc中的路经以及start point ,end point。

所谓start point 就是:1. input port(顶层设计的输入端口)2.clock pin of sequential cell(触发器的clock pin)所谓的end point 就是:1 output port(顶层设计的输出端口)3.data pin of sequential cell(触发器的data pin)了解start point 和end point,就可以方便的了解dc是如何将设计打散成路经,一个设计中基本的路经分为4种,如下图:path1:input port to data pin of sequential cellpath2:input port to output portpath3:clock pin to data pin of next sequential cellpath4:clock pin to output port所有的设计也就这四种类型的路径。

时序分析基础:Setuphold,跨时钟域处理和亚稳态

时序分析基础:Setuphold,跨时钟域处理和亚稳态⼀、建⽴时间和保持时间Setup/holdTsetup和Thold内数据都稳定时,data1和data2才会正常被D触发器采样⼆、什么是亚稳态百度百科上说亚稳态是指触发器⽆法在某个规定时间段内达到⼀个可确认的状态。

当⼀个触发器进⼊亚稳态时,既⽆法预测该单元的输出电平,也⽆法预测何时输出才能稳定在某个正确的电平上。

讲⼈话就是,亚稳态就是在建⽴时间或保持时间⾥数据处于不够稳定的状态、正在变化的状态,下⾯以单bit跨时钟域处理为例⼦。

三、单bit跨时钟域中的亚稳态处理先说什么是时钟域,打个⽐⽅,FPGA的主控芯⽚⼯作在系统时钟之下,系统时钟由晶振产⽣为50MHz,如果不分频,板内的所有资源都⼯作在系统时钟之下,那么这就是⼀个时钟域clk_a。

同⼀个时钟域下的信号,综合以及布线⼯具可以在data路径或者clock路径上插⼊buffer使得每⼀个D触发器的setup/hold时间都满⾜,这个时候可以简化⼀下模型,把系统时钟看成clk_a域的理想时钟,并在时钟上升沿D触发器采样(实际上是建⽴时间这个时间段采样的)。

那么当另⼀个时钟域的信号data_b来了(⼀般是外设的标志位或者数据组),就是跨时钟域了,就可能发⽣下图情况。

这时就产⽣了亚稳态,这个数据是不稳定的,可能采样到0,也可能采样到1。

可能会导致信号⽑刺、逻辑判断混乱、振荡等问题。

消除亚稳态有三种⽅法,⼀是⽤多级DFF来延时,俗称打两拍。

打⼀拍的verlog代码如下always@(posedge clk or negedge rst_n)if(!rst_n)data_r<=0;elsedata_r<=data_b;View Code这样就会发⽣下图情况在时钟的上升沿对clk_b域的data_b采样,并将其值赋给clk_a域的data_r。

亚稳态判读出的是1值,data_r就像上图中的data_r,是⼀个稳态值,亚稳态已经消去;亚稳态判读出的是0值,data_r就像上图中的data_r‘,也是⼀个稳态值,亚稳态已经消去。

关于建立时间(setup time)保持时间(hold time)以及时序的一些问题集合

建立时间和保持时间giltch1.jpg图1建立时间(setup time)是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器;保持时间(hold time)是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被打入触发器。

如图1 。

数据稳定传输必须满足建立和保持时间的要求,当然在一些情况下,建立时间和保持时间的值可以为零。

QUOTE:DC,建立时间不满足,只能重新综合设计,并以违例路径为目标进行优化,以及对涉及到违例的组合逻辑以及子模块加紧约束。

保持时间不满足,可在布图前或者布图后再修改这些违例,通常布图后再修改。

因为布图前综合,时序分析采用统计线载模型,在布局前修正保持时间违例可能会导致布图后建立时间违例。

QUOTE:1、setup time的意义:为什么Data需要在Clock到达之前到达?其实在实际的问题中,setup time并不一定是大于零的,因为Clock到达时刻并不等同于latch的传输门A关闭的时刻(更何况这种关闭并不是绝对的和瞬间完成的),这之间有一个未知的延迟时间。

为使问题简化,假设Clock的到达时刻为传输门A关闭、传输们B打开的时刻。

如果Data没有在这之前足够早的时刻到达,那么很有可能内部的feedback线路上的电压还没有达到足够使得inv1翻转的地步(因为inv0有延时,Data有slope,传输门B打开后原来的Q值将通过inv2迫使feedback保持原来的值)。

如果这种竞争的情况发生,Q的旧值将有可能获胜,使Q不能够寄存住正确的Data值;当然如果feedback上的电压已经达到了足够大的程度也有可能在竞争中取胜,使得Q能够正确输出。

如果inv0、inv1和inv2的延时较大(Data的变化影响feedback和Q的时间越长),那么为了保证正确性就需要更大的setup time。

微电子笔试题

亚稳态Setup/hold time 是测试芯片对输入信号和时钟信号之间的时间要求。

建立时间是指触发器的时钟信号上升沿到来以前,数据稳定不变的时间。

输入信号应提前时钟上升沿(如上升沿有效)T时间到达芯片,这个T就是建立时间-Setup time.如不满足setup time,这个数据就不能被这一时钟打入触发器,只有在下一个时钟上升沿,数据才能被打入触发器。

保持时间是指触发器的时钟信号上升沿到来以后,数据稳定不变的时间。

如果hold time不够,数据同样不能被打入触发器。

建立时间(Setup Time)和保持时间(Hold time)。

建立时间是指在时钟边沿前,数据信号需要保持不变的时间。

保持时间是指时钟跳变边沿后数据信号需要保持不变的时间。

如果不满足建立和保持时间的话,那么DFF将不能正确地采样到数据,将会出现亚稳态(metastability)的情况。

如果数据信号在时钟沿触发前后持续的时间均超过建立和保持时间,那么超过量就分别被称为建立时间裕量和保持时间裕量。

在数字集成电路中,触发器要满足setup/hold的时间要求。

当一个信号被寄存器锁存时,如果信号和时钟之间不满足这个要求,Q端的值是不确定的,并且在未知的时刻会固定到高电平或低电平。

这个过程称为亚稳态(Metastability)。

一些关于微电子方面的笔试题(zz)1.FPGA和ASIC的概念,他们的区别。

(未知)答案:FPGA是可编程ASIC。

ASIC:专用集成电路,它是面向专门用途的电路,专门为一个用户设计和制造的。

根据一个用户的特定要求,能以低研制成本,短、交货周期供货的全定制,半定制集成电路。

与门阵列等其它ASIC(Application Specific IC)相比,它们又具有设计开发周期短、设计制造成本低、开发工具先进、标准产品无需测试、质量稳定以及可实时在线检验等优点.2.建立时间是指触发器的时钟信号上升沿到来以前,数据稳定不变的时间。

建立时间、保持时间和时序约束条件

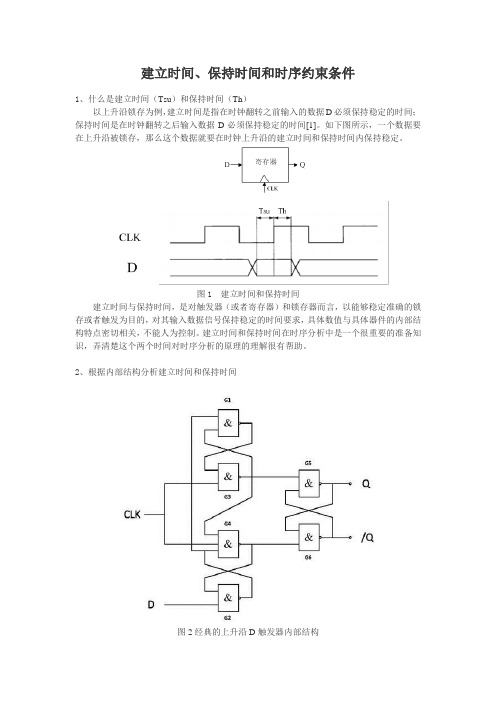

建立时间、保持时间和时序约束条件1、什么是建立时间(Tsu)和保持时间(Th)以上升沿锁存为例,建立时间是指在时钟翻转之前输入的数据D必须保持稳定的时间;保持时间是在时钟翻转之后输入数据D必须保持稳定的时间[1]。

如下图所示,一个数据要在上升沿被锁存,那么这个数据就要在时钟上升沿的建立时间和保持时间内保持稳定。

图1 建立时间和保持时间建立时间与保持时间,是对触发器(或者寄存器)和锁存器而言,以能够稳定准确的锁存或者触发为目的,对其输入数据信号保持稳定的时间要求,具体数值与具体器件的内部结构特点密切相关,不能人为控制。

建立时间和保持时间在时序分析中是一个很重要的准备知识,弄清楚这个两个时间对时序分析的原理的理解很有帮助。

2、根据内部结构分析建立时间和保持时间图2 经典的上升沿D触发器内部结构关于为什么会有建立时间和保持时间,我曾试图从触发器或锁存器内部的结构去分析和证实,但是看了许多资料,由于触发器的内部结构有很多,所以分析方法很多,说法也很多。

下面我选两个比较经典的结构来分析一下建立时间和保持时间。

以经典边沿触发的D触发器为例子,从内部结构上分析一下D触发器建立时间和保持时间。

这个说明主要来源于EETOP的一篇帖子,其结构在维基百科的触发器词条可以得到验证。

如上图所示,这是一个上升沿触发的D触发器,需要注意的是,图中的6个与非门都是有延迟的,也就是在某一时刻输入组合逻辑的数据,在一段时间之后才能影响其输出,这是产生建立时间和保持时间要求的最根本原因。

首先,我们在假设所有的与非门的延迟为0,叙述一下这个触发器的整体工作流程。

当CLK=0时,与非门G3和G4的输出均为1,输出的1反馈到G1和G2作为输入,导致G1和G2的输出分别为D和/D,输出的D和/D又反馈到G3和G4;而G5和G6在此期间一直锁存着之前的数据,不受输入影响。

图3 CLK=0时触发器内部信号详情当CLK=1时,与非门G3和G4的输出变为/D和D,输出到G5和G6作为输入,根据锁存器的原理,G5和G6最终会稳定的输出Q和/Q。

建立时间和保持时间关系详解

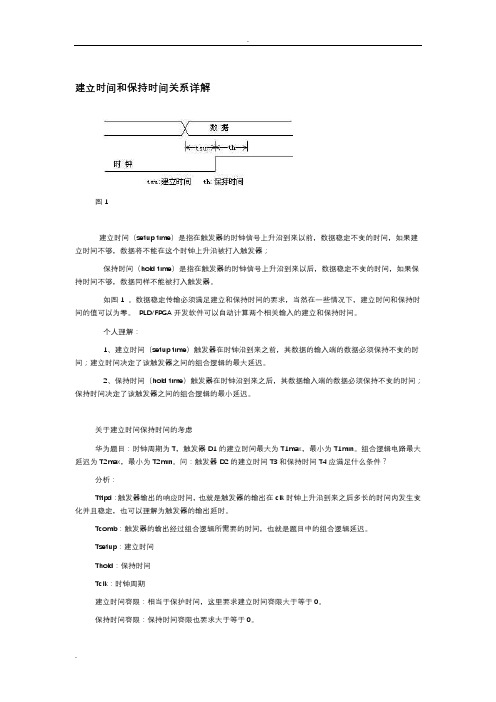

建立时间和保持时间关系详解图1建立时间(setup time)是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器;保持时间(hold time)是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被打入触发器。

如图1 。

数据稳定传输必须满足建立和保持时间的要求,当然在一些情况下,建立时间和保持时间的值可以为零。

PLD/FPGA开发软件可以自动计算两个相关输入的建立和保持时间。

个人理解:1、建立时间(setup time)触发器在时钟沿到来之前,其数据的输入端的数据必须保持不变的时间;建立时间决定了该触发器之间的组合逻辑的最大延迟。

2、保持时间(hold time)触发器在时钟沿到来之后,其数据输入端的数据必须保持不变的时间;保持时间决定了该触发器之间的组合逻辑的最小延迟。

关于建立时间保持时间的考虑华为题目:时钟周期为T,触发器D1的建立时间最大为T1max,最小为T1min。

组合逻辑电路最大延迟为T2max,最小为T2min。

问:触发器D2的建立时间T3和保持时间T4应满足什么条件?分析:Tffpd:触发器输出的响应时间,也就是触发器的输出在clk时钟上升沿到来之后多长的时间内发生变化并且稳定,也可以理解为触发器的输出延时。

Tcomb:触发器的输出经过组合逻辑所需要的时间,也就是题目中的组合逻辑延迟。

Tsetup:建立时间Thold:保持时间Tclk:时钟周期建立时间容限:相当于保护时间,这里要求建立时间容限大于等于0。

保持时间容限:保持时间容限也要求大于等于0。

由上图可知,建立时间容限=Tclk-Tffpd(max)-Tcomb(max)-Tsetup,根据建立时间容限≥0,也就是Tclk-Tffpd(max)-Tcomb(max)-Tsetup≥0,可以得到触发器D2的Tsetup≤Tclk-Tffpd(max)-Tcomb(max),由于题目没有考虑Tffpd,所以我们认为Tffpd=0,于是得到Tsetup≤T-T2max。

setup time 与 hold time

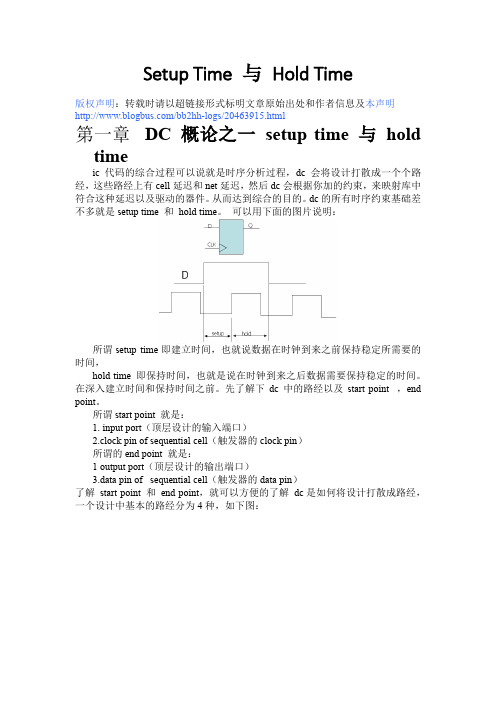

Setup Time 与 Hold Time版权声明:转载时请以超链接形式标明文章原始出处和作者信息及本声明 /bb2hh-logs/20463915.html第一章 DC 概论之一 setup time 与 hold timeic 代码的综合过程可以说就是时序分析过程, dc 会将设计打散成一个个路经, 这些路经上有 cell 延迟和 net 延迟,然后 dc 会根据你加的约束,来映射库中符 合这种延迟以及驱动的器件。

从而达到综合的目的。

dc 的所有时序约束基础差 不多就是 setup time 和 hold time。

可以用下面的图片说明:所谓 setup time 即建立时间,也就说数据在时钟到来之前保持稳定所需要的 时间, hold time 即保持时间,也就是说在时钟到来之后数据需要保持稳定的时间。

在深入建立时间和保持时间之前。

先了解下 dc 中的路经以及 start point ,end point。

所谓 start point 就是: 1. input port(顶层设计的输入端口) 2.clock pin of sequential cell(触发器的 clock pin) 所谓的 end point 就是: 1 output port(顶层设计的输出端口) 3.data pin of sequential cell(触发器的 data pin) 了解 start point 和 end point,就可以方便的了解 dc 是如何将设计打散成路经, 一个设计中基本的路经分为 4 种,如下图:path1: input port to data pin of sequential cell path2:input port to output port path3:clock pin to data pin of next sequential cell path4:clock pin to output port 所有的设计也就这四种类型的路径。

建立时间保存时间详解

0 技术交流fpga欢迎您的加入什么是Setup 和Holdup时间?a) 什么是Setup 和Holdup时间?建立时间(setup time)是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器;保持时间(hold time)是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被打入触发器。

b) 什么是竞争与冒险现象?怎样判断?如何消除?信号在FPGA器件内部通过连线和逻辑单元时,都有一定的延时。

延时的大小与连线的长短和逻辑单元的数目有关,同时还受器件的制造工艺、工作电压、温度等条件的影响。

信号的高低电平转换也需要一定的过渡时间。

由于存在这两方面因素,多路信号的电平值发生变化时,在信号变化的瞬间,组合逻辑的输出有先后顺序,并不是同时变化,往往会出现一些不正确的尖峰信号,这些尖峰信号称为"毛刺"。

如果一个组合逻辑电路中有"毛刺"出现,就说明该电路存在"冒险"。

用D触发器,格雷码计数器,同步电路等优秀的设计方案可以消除。

c) 请画出用D触发器实现2倍分频的逻辑电路?就是把D触发器的输出端加非门接到D端。

d) 什么是"线与"逻辑,要实现它,在硬件特性上有什么具体要求?将几个OC门结构与非门输出并联,当每个OC门输出为高电平时,总输出才为高,这种连接方式称为线与。

e) 什么是同步逻辑和异步逻辑?整个设计中只有一个全局时钟成为同步逻辑。

多时钟系统逻辑设计成为异步逻辑。

f) 请画出微机接口电路中,典型的输入设备与微机接口逻辑示意图(数据接口、控制接口、所存器/缓冲器)。

是不是结构图?g) 你知道那些常用逻辑电平?TTL与COMS电平可以直接互连吗?TTL,cmos,不能直连LVDS:LVDS(Low Voltage Differential Signal)即低电压差分信号,LVDS接口又称RS644总线接口,是20世纪90年代才出现的一种数据传输和接口技术。

电子通讯 笔试题 大全 附答案

a)什么是Setup 和Holdup时间?Setup/hold time 是测试芯片对输入信号和时钟信号之间的时间要求。

建立时间是指触发器的时钟信号上升沿到来以前,数据稳定不变的时间。

输入信号应提前时钟上升沿(如上升沿有效)T时间到达芯片,这个T就是建立时间-Setup time.如不满足setup time,这个数据就不能被这一时钟打入触发器,只有在下一个时钟上升沿,数据才能被打入触发器。

保持时间是指触发器的时钟信号上升沿到来以后,数据稳定不变的时间。

如果hold time不够,数据同样不能被打入触发器。

建立时间(Setup Time)和保持时间(Hold time)。

建立时间是指在时钟边沿前,数据信号需要保持不变的时间。

保持时间是指时钟跳变边沿后数据信号需要保持不变的时间。

如果不满足建立和保持时间的话,那么DFF将不能正确地采样到数据,将会出现stability的情况。

如果数据信号在时钟沿触发前后持续的时间均超过建立和保持时间,那么超过量就分别被称为建立时间裕量和保持时间裕量。

b) 什么是竞争与冒险现象?怎样判断?如何消除?当一个门的输入有两个或两个以上的变量发生改变时,由于这些变量是经过不同组合逻辑路径产生的,使得它们状态改变的时刻有先有后,这种时差引起的现象称为竞争(Race)。

竞争的结果若导致冒险或险象(Hazard)发生(例如毛刺(glitch)),并造成错误的后果,那么就称这种竞争为临界竞争。

若竞争的结果没有导致冒险发生,或虽有冒险发生,但不影响系统的工作,那么就称这种竞争为非临界竞争。

输入信号变化前后,输出的稳态值是一样的,但在输入信号变化时,输出信号产生了毛刺,这种冒险是静态冒险。

输入信号变化前后,输出的稳态值不同,并在边沿处出现了毛刺,称为动态险象(冒险)。

从引起冒险的具体原因上,冒险可以分为函数冒险和逻辑冒险。

函数冒险是逻辑函数本身固有的,当多个输入变量发生变化时,常常会发生逻辑冒险。

建立时间和保持时间关系详解

建立时间和保持时间关系详解图 1建立时间(setup time)是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器;保持时间(hold time)是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被打入触发器。

如图1 。

数据稳定传输必须满足建立和保持时间的要求,当然在一些情况下,建立时间和保持时间的值可以为零。

PLD/FPGA 开发软件可以自动计算两个相关输入的建立和保持时间。

个人理解:1、建立时间(setup time)触发器在时钟沿到来之前,其数据的输入端的数据必须保持不变的时间;建立时间决定了该触发器之间的组合逻辑的最大延迟。

2、保持时间(hold time)触发器在时钟沿到来之后,其数据输入端的数据必须保持不变的时间;保持时间决定了该触发器之间的组合逻辑的最小延迟。

关于建立时间保持时间的考虑华为题目:时钟周期为T,触发器D1 的建立时间最大为T1max,最小为T1min 。

组合逻辑电路最大延迟为T2max,最小为T2min 。

问:触发器D2 的建立时间T3 和保持时间T4 应满足什么条件?分析:Tffpd :触发器输出的响应时间,也就是触发器的输出在clk 时钟上升沿到来之后多长的时间内发生变化并且稳定,也可以理解为触发器的输出延时。

Tcomb:触发器的输出经过组合逻辑所需要的时间,也就是题目中的组合逻辑延迟。

Tsetup:建立时间Thold:保持时间Tclk:时钟周期建立时间容限:相当于保护时间,这里要求建立时间容限大于等于0。

保持时间容限:保持时间容限也要求大于等于0。

由上图可知,建立时间容限=Tclk-Tffpd(max)-Tcomb(max)-Tsetup ,根据建立时间容限≥0,也就是Tclk-Tffpd(max)-Tcomb(max)-Tsetup ≥0,可以得到触发器D2 的Tsetup≤Tclk-Tffpd(max)-Tcomb(max) ,由于题目没有考虑Tffpd ,所以我们认为Tffpd =0,于是得到Tsetup≤T-T2max。

保持和建立时间详解

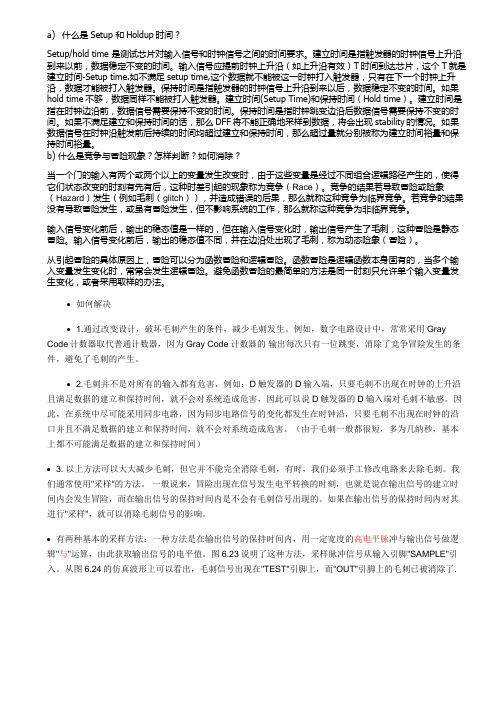

这几天经常看到有关数字电路中建立时间(setup time)、保持时间(holdup time)以及延迟时间(delay)的讨论。

自己也高不清楚,查了相关的资料,总算了解了一些。

首先:建立时间和保持时间都是器件要求的特性。

其中建立时间是器件输入端在时钟信号有效沿到来前,要求输入信号稳定不变的时间。

保持时间是器件输入端要求输入信号在时钟信号有效沿到来后保持稳定不变的时间。

如果输入信号不满足建立时间和保持时间的要求,就可能导致数据锁存错误。

延迟时间是器件本身或布线的物理特性,其含义是信号从器件或布线经过所需的时间。

这里主要讨论器件的延迟时间。

通常器件的延迟时间由两部分组成。

一个是触发器输出响应时间(tffpd)。

可以理解为触发器输出在clk有效沿到来后的时间内发生变化, 之后稳定,也可以理解输出延迟。

另一个触发器输出的变化经过组合逻辑元件所需的附加时间,一般是组合逻辑延迟(tcomb)。

如下图所示:再来解释两个概念:建立时间容限和保持时间容限。

所谓建立时间容限是指器件允许的安全的建立时间长度范围。

同样保持时间也就是器件允许的安全的保持时间长度范围。

一般来说建立时间容限和保持时间容限都大于等于0。

根据这个要求,如上图所示,就有以下约束:tclk = tffpd + tcomb + 建立时间容限 + tsetup所以建立时间容限 = tclk - tffpd(max) - tcomb(max) - tsetup >=0tsetup <= tclk - tffpd (max)- tcomb(max)再来看保持时间容限首先对于数据接收端来说,任何时钟沿采样的数据,都是发送端前一时钟周期发送的数据。

发送端可能每个时钟周期都要发送数据,那么对于接收端来说,任何一个时钟沿后一段时间,数据线上的数据都会被发送端第二次发送的数据改变,所以保持时间容限其实是由于下一个时钟节拍上的数据引起的。

有效数据在tffpd + tcomb之后到达触发器,如果tholdup > tffpd + tcomb,则下一个有效数据到达后,tholdup仍然没结束,但前一个数据已经被破坏,所以必须tholdup <= tffpd + tcomb。

时序分析的建立时间和保持时间详解

1:概念2:对建立时间的约束3:对保持时间约束4:对于保持时间的理解:5: 建立时间保持时间的考虑—华为题目6:positive skew和negative skew的考虑。

7:latency的分析。

8:考虑latency、skew的建立时间和保持时间---很详细8.1:建立时间(setup time)的到达时间和要求时间。

8.2:保持时间(hold time)的到达时间和要求时间。

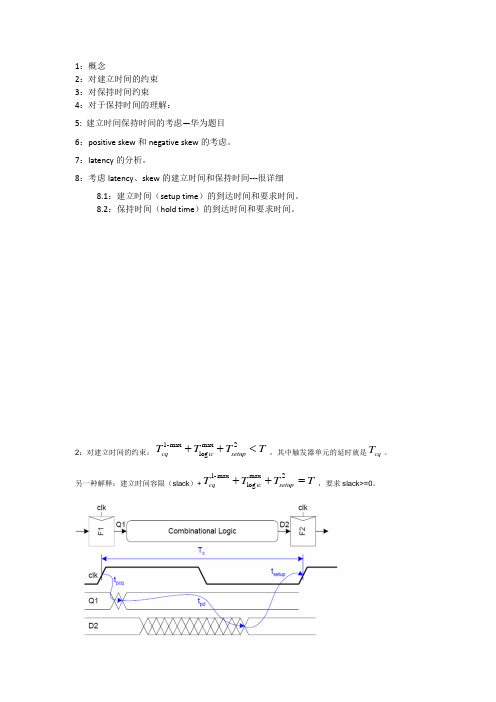

2:对建立时间的约束:1-max max2logcq ic setupT T T T++<,其中触发器单元的延时就是cqT。

另一种解释:建立时间容限(slack)+1-max max2logcq ic setupT T T T++=,要求slack>=0。

3:对保持时间约束:1-minmin 2log cqic hold T T T +>另一种解释:1-min min 2log cq ic hold T T T +=+保持时间容限(slack ),要求slack>=0。

4:对于保持时间的理解:(1) My_idea: the two meanings of my ideas are in similar !!!解释1:输入数据只有满足一定的保持时间后,下一个周期的输入数据才可以被打入。

当skew>0时,从min minholdcq comb T T T δ+≤+这个式子我们可以理解为实际Thold 变小了(要求的hold time 是没变的,但现在的hold time 比你要求的小了一点),则下个周期的数据可能会提前打入触发器导致和触发器原有的信号产生竞争。

当skew<0时,从min minholdcq comb T T T δ+≤+这个式子我们可以理解为Thold 变大了,则此时实际的hold time 肯定比之前的hold time 大(也就是说我现在的hold time 比你要求的大了一些),所以肯定满足保持时间要求。

SDRAM?layout之等长理解

SDRAM layout之等长理解layout的时候,对SDRAM之类的,虽然走线可以不等长,但误差余量是多少却是一直都没有搞明白,结合SDRAM的控制时序作个简单的分析。

首先明白几个感念:1.建立时间和保持时间,这里说的建立时间和保持时间是针对接收端而言的,建立时间(SetupTime)指的是数据在时钟沿到达之前必须保持稳定的最小时间,保持时间指的是数据在时钟沿到达之后必须保持稳定的最小时间,建立时间和保持时间对接收端的IC来说是个必须要满足的参数,否则采集就会出错或不成功,因为IC内部采集和处理数据的逻辑门和连线需要时间,否则触发器在数据还没有稳定的时候会有误触发。

2.发送端和接收端的时序,对于发送端来说,每个时钟周期都要发送数据,并且是时钟沿到来就启动发送,但对接收端来说,任何时钟沿采样的数据,都是发送端前一个时钟发送的数据,理解这一点是非常重要的。

3.建立时间容限和保持时间容限,了解layout导线延时就必须理解建立时间容限和保持时间容限,因为满足建立时间容限和保持时间容限的的导线延时都是可以接受的,不会影响电路逻辑关系的,理解这些关系,参考下图理解:上图为网上截取。

建立时间容限如图,保持时间容限为tffpd + tcomb - thold,上图上中间的表示的是输出端的时序,最后一个表示的是接收端的时序。

layout导线延时的容许范围就是:|data - clock| <= 建立时间容限与保持时间容限的最小值具体以SDRAM为例子加以说明:1.SDRAM的时序如下图首先看,DATA(OUT) 图中tTENDAT = 0,即对发送端而言,时钟沿到达立即发送数据,tDSDAT = 4ns,说明数据正在发送时在时钟沿到后的4ns时发送的,即保持时间容限 = 4ns - 0.8ns(保持时间tSDAT),建立时间容限 = 7.5ns(tSCLK时钟周期) - 4ns(总线上有新的发送数据的真正时刻) - 1.5ns(tSSDAT建立时间) = 2ns以6inch/ns的传播速度计算,数据线和时钟线的导线长度可以相差2*6=12inch,这是个非常大的容差范围,所以SDRAM根本无需做等长处理。

建立时间和保持时间

建立时间和保持时间信号经过传输线到达接收端之后,就牵涉到建立时间和保持时间这两个时序参数,Setup/Hold time 是测试芯片对输入信号和时钟信号之间的时间要求,也就是它们表征了时钟边沿触发前后数据需要在锁存器的输入持续时间,是芯片本身的特性。

建立时间是指触发器的时钟信号上升沿到来以前,数据稳定不变的时间。

输入信号应提前时钟上升沿(如上升沿有效)T时间到达芯片,这个T就是建立时间Setup time.如不满足Setup time,这个数据就不能被这一时钟打入触发器,只有在下一个时钟上升沿,数据才能被打入触发器;保持时间是指触发器的时钟信号上升沿到来以后,数据也必须保持一段时间,数据保持不变以便能够稳定读取(信号在器件内部通过连线和逻辑单元时,都有一定的延时。

延时的大小与连线的长短和逻辑单元的数目有关,同时还受器件的制造工艺、工作电压、温度等条件的影响。

信号的高低电平转换也需要一定的过渡时间。

)。

如果holdtime 不够,数据便不能被有效读取并转换为输出。

如果数据信号在时钟边沿触发前后持续的时间分别超过建立时间和保持时间,那么这部分超过的分量分别称为建立时间裕量和保持时间裕量。

(这期间其实还涉及到竞争冒险的问题,也就是毛刺,稍后在研究,建立保持时间的存在即是触发器内部的特性又在屏蔽毛刺方面起到了一定的作用。

)其实建立时间就是在脉冲信号到来时,输入信号已经稳定等待的时间;而保持时间是信号脉冲到来后,而输入信号还没有到达下降沿的时间。

举个例子:建立时间就是你到朋友家做客去早了,但是主人还没回来,你等待的时间就是建立时间;保持时间就是进入房子后,逗留的(有效)时间。

当然在实际测试中我发现时钟信号也是存在抖动和偏移的虽然系统时序设计中对时钟信号的要求非常严格,因为我们所有的时序计算都是以恒定的时钟信号为基准。

但实际中时钟信号往往不可能那么理想,常会出现抖动(Jitter)和偏移(Skew)问题。

(估计没有真正稳定的信号)。

建立时间、保持时间、传播延时、组合逻辑延时都是什么呢?

建立时间、保持时间、传播延时、组合逻辑延时都是什么呢?建立时间(Setup Time)是指触发器的时钟信号上升沿到来之前,数据保持稳定不变的时间。

输入信号应该提前时钟上升沿(如上升沿有效)T su 时间到达芯片,这个 T su 就是建立时间。

如果不满足建立时间要求,这个数据就不能被这一时钟打入触发器,只有在下一个时钟上升沿,数据才能被打入触发器,或者说,该数据就会被永久“跳过”而未被“采样”。

举个例子:坐火车时需要提前到站检票安检,而不是一到火车站就可以乘坐,必须的提前到站的时间就是建立时间。

如果数据信号在时钟沿触发前的持续时间超过了建立时间 T su,那么这个时间间隔就叫做建立时间裕量。

保持时间(Hold Time)是指触发器的时钟信号上升沿到来之后,数据保持稳定不变的时间(数据保持不变以便能够稳定读取,如果保持时间不满足的话,那么数据便不能被有效读取并转换为输出)。

如果数据信号在时钟沿触发后的持续时间超过了保持时间T h,那么这个时间间隔就叫做保持时间裕量。

总结(Summary):建立时间和保持时间这两个时序参数是测试芯片对输入信号和时钟信号之间的时间要求,也就是它们表征了时钟边沿触发前后数据需要在锁存器的输入持续时间,是芯片本身的特性。

其实,这期间其实还涉及到竞争冒险的问题,也就是毛刺,建立保持时间的存在即是触发器内部的特性又在屏蔽毛刺方面起到了一定的作用。

传播延迟(Propagation Delay)是指一个数字信号从器件(一般是DFF,符号表示为T cq)的输入端到输出端所需的时间。

一般在FPGA 中是指时钟上升沿之后延时T cq的时间,数据才到达寄存器Q 端。

区别于门传播延时:证明其对输入信号变化响应有多快,表示为信号通过该门所经历的时间,定义为输入信号和输出信号波形在50% 翻转点之间的时间。

组合逻辑延时(Combinational Logic Delay)是指两级寄存器之间的输出端 Q 到输入端 D 之间的组合逻辑延时,符号表示为 T logic 。

2021年微电子一些面试问题

亚稳态Setup/hold time 是测试芯片对输入信号和时钟信号之间时间规定。

建立时间是指触发器时钟信号上升沿到来此前,数据稳定不变时间。

输入信号应提前时钟上升沿(如上升沿有效)T时间到达芯片,这个T就是建立时间-Setup time.如不满足setup time,这个数据就不能被这一时钟打入触发器,只有在下一种时钟上升沿,数据才干被打入触发器。

保持时间是指触发器时钟信号上升沿到来后来,数据稳定不变时间。

如果hold time不够,数据同样不能被打入触发器。

建立时间(Setup Time)和保持时间(Hold time)。

建立时间是指在时钟边沿前,数据信号需要保持不变时间。

保持时间是指时钟跳变边沿后数据信号需要保持不变时间。

如果不满足建立和保持时间话,那么DFF将不能对的地采样到数据,将会浮现亚稳态(metastability)状况。

如果数据信号在时钟沿触发先后持续时间均超过建立和保持时间,那么超过量就分别被称为建立时间裕量和保持时间裕量。

在数字集成电路中,触发器要满足setup/hold时间规定。

当一种信号被寄存器锁存时,如果信号和时钟之间不满足这个规定,Q端值是不拟定,并且在未知时刻会固定到高电平或低电平。

这个过程称为亚稳态(Metastability)。

某些关于微电子方面笔试题(zz)1.FPGA和ASIC概念,她们区别。

(未知)答案:FPGA是可编程ASIC。

ASIC:专用集成电路,它是面向专门用途电路,专门为一种顾客设计和制造。

依照一种顾客特定规定,能以低研制成本,短、交货周期供货全定制,半定制集成电路。

与门阵列等其他ASIC(Application Specific IC)相比,它们又具备设计开发周期短、设计制导致本低、开发工具先进、原则产品无需测试、质量稳定以及可实时在线检查等长处.2.建立时间是指触发器时钟信号上升沿到来此前,数据稳定不变时间。

输入信号应提前时钟上升沿(如上升沿有效)T 时间到达芯片,这个T就是建立时间-Setup time.如不满足setup time,这个数据就不能被这一时钟打入触发器,只有在下一种时钟上升沿,数据才干被打入触发器。

时序分析中建立时间,保持时间,时钟到输出,PIN到PIN延时的说明

时序分析中建立时间,保持时间,时钟到输出,PIN到PIN延时的说明Clock Setup Time (tsu) 要想正确采样数据,就必须使数据和使能信号在有效时钟沿到达前就准备好,所谓时钟建立时间就是指时钟到达前,数据和使能已经准备好的最小时间间隔。

如下图所示:这里定义Setup时间是站在同步时序整个路径上的,需要区别的是另一个概念Micro tsu。

Micro tsu指的是一个触发器内部的建立时间,它是触发器的固有属性,一般典型值小于1~2ns。

在Xilinx等的时序概念中,称Altera的Micro tsu为setup时间,用Tsetup表示,请大家区分一下。

回到Altera的时序概念,Altera的tsu定义如下:tsu = Data Delay – Clock Delay + Micro tsuClock Hold Time (tH)时钟保持时间是只能保证有效时钟沿正确采用的数据和使能信号的最小稳定时间。

其定义如下图所示:tH示意图定义的公式为:tH= Clock Delay – Data Delay + Micro tH注:其中Micro tH是指寄存器内部的固有保持时间,同样是寄存器的一个固有参数,典型值小于1~2ns。

Clock-to-Output Delay(tco)这个时间指的是当时钟有效沿变化后,将数据推倒同步时序路径的输出端的最小时间间隔。

如下图所示:tco示意图其中Micor tco也是一个寄存器的固有属性,指的是寄存器相应时钟有效沿,将数据送到输出端口的内部时间参数。

它与Xilinx的时序定义中,有一个概念叫T cko是同一个概念。

Pin to Pin Delay (tpd)tpd指输入管脚通过纯组合逻辑到达输出管脚这段路径的延时,特别需要说明的是,要求输入到输出之间只有组合逻辑,才是tpd延时。

Slack是表示设计是否满足时序的一个称谓,正的slack表示满足时序(时序的余量),负的slack表示不满足时序(时序的欠缺量)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

建立时间和保持时间giltch1.jpg图1建立时间(setup time)是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器;保持时间(hold time)是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被打入触发器。

如图1 。

数据稳定传输必须满足建立和保持时间的要求,当然在一些情况下,建立时间和保持时间的值可以为零。

QUOTE:DC,建立时间不满足,只能重新综合设计,并以违例路径为目标进行优化,以及对涉及到违例的组合逻辑以及子模块加紧约束。

保持时间不满足,可在布图前或者布图后再修改这些违例,通常布图后再修改。

因为布图前综合,时序分析采用统计线载模型,在布局前修正保持时间违例可能会导致布图后建立时间违例。

QUOTE:1、setup time的意义:为什么Data需要在Clock到达之前到达?其实在实际的问题中,setup time并不一定是大于零的,因为Clock到达时刻并不等同于latch的传输门A关闭的时刻(更何况这种关闭并不是绝对的和瞬间完成的),这之间有一个未知的延迟时间。

为使问题简化,假设Clock的到达时刻为传输门A关闭、传输们B打开的时刻。

如果Data没有在这之前足够早的时刻到达,那么很有可能内部的feedback线路上的电压还没有达到足够使得inv1翻转的地步(因为inv0有延时,Data有slope,传输门B打开后原来的Q值将通过inv2迫使feedback保持原来的值)。

如果这种竞争的情况发生,Q的旧值将有可能获胜,使Q不能够寄存住正确的Data值;当然如果feedback上的电压已经达到了足够大的程度也有可能在竞争中取胜,使得Q能够正确输出。

如果inv0、inv1和inv2的延时较大(Data的变化影响feedback和Q的时间越长),那么为了保证正确性就需要更大的setup time。

所以在实际测量setup time的时候,需要选取工艺中最慢的corner进行仿真测量。

2、、hold time的意义:为什么Data在Clock到达之后仍然要保持一段时间?和setuptime的情况不一样,因为Clock到达时刻并不等同于latch的传输门A完全关闭的时刻。

所以如果Data没有在Clock到达之后保持足够长的时间,那么很有可能在传输门A完全关闭之前Data就已经变化了,并且引起了feedback的变化。

如果这种变化足够大、时间足够长的话,很有可能将feedback 从原本正确的低电压拉到较高电压的电压。

甚至如果这种错误足够剧烈,导致了inv1和inv2组成的keeper 发生了翻转,从而彻底改变了Q的正确值,就会导致输出不正确。

当然,如果这种错误电压不是足够大到能够改变keeper的值,就不会影响到Q的正确输出。

如果inv0、inv1和inv2的延时较小(Data的变化影响feedback和Q的时间越短),那么为了保证正确性,就需要更大的hold time。

所以在实际测量hold time的时候,需要选取工艺中最快的corner进行仿真测量。

QUOTE:时钟周期为T,触发器D1的时钟沿到来到触发器Q变化的时间Tco(CLK--Q)最大为T1max,最小为T1min,逻辑组合电路的延迟时间最大为T2max,最小为T2min,问触发器D2的建立时间和保持时间。

最终答案:T3setup<T-T1max-T2max,T3hold<T1min+T2minmaxbird:D2的保持时间就是时钟沿到来之后,D2的数据输入端要保持数据不变的时间,这个时间是由D1和D2之间的组合逻辑时延决定的。

例如:假设D1和D2之间的组合逻辑时延为2ns,时钟周期为10ns,这意味着在时钟沿来到后,D1输出的新数据要过2ns才会到达D2的数据输入端,那么在这2ns内,D2的数据输入端保持的还是上一次的旧数据,其值不会立即更新,假设D2的最小保持时间为3ns,这意味时钟沿到来后,D2的数据输入端的值在3ns内不能有变化,回到问题的关键,由于D1在时钟沿到来后的输出结果,经过2ns的组合逻辑延时便到达了D2的输入端,而D2要求在时钟沿到来后的3ns内其输入端的值不能改变,这样D2的保持时间就得不到满足,所以D2的保持时间必须小于等于2ns。

至于说T2min为0时的情况,其实T2min是永远不能为0的,即使是一根导线其时延也是不可能为0的,这就是为什么移位寄存器的两个触发器之间连的只是一根导线,导线后端触发器的保持时间却还是可以满足的原因,其实移位寄存器中触发器的保持时间可以看成是小于等于其间导线的时延。

建立时间:触发器在时钟沿来到前,其数据输入端的数据必须保持不变的时间;保持时间:触发器在时钟沿来到后,其数据输入端的数据必须保持不变的时间。

因为触发器内部数据的形成是需要一定的时间的,如果不满足建立和保持时间,触发器将进入亚稳态,进入亚稳态后触发器的输出将不稳定,在0和1之间变化,这时需要经过一个恢复时间,其输出才能稳定,但稳定后的值并不一定是你的输入值。

这就是为什么要用两级触发器来同步异步输入信号。

这样做可以防止由于异步输入信号对于本级时钟可能不满足建立保持时间而使本级触发器产生的亚稳态传播到后面逻辑中,导致亚稳态的传播。

两级触发器可防止亚稳态传播的原理:假设第一级触发器的输入不满足其建立保持时间,它在第一个脉冲沿到来后输出的数据就为亚稳态,那么在下一个脉冲沿到来之前,其输出的亚稳态数据在一段恢复时间后必须稳定下来,而且稳定的数据必须满足第二级触发器的建立时间,如果都满足了,在下一个脉冲沿到来时,第二级触发器将不会出现亚稳态,因为其输入端的数据满足其建立保持时间。

同步器有效的条件:第一级触发器进入亚稳态后的恢复时间+ 第二级触发器的建立时间< = 时钟周期。

(编者注:maxbird在该部分详细说明了建立时间和保持时间的概念,以及如果不满足二者可能导致的亚稳态的传播。

注意这里说的建立时间和保持时间都是针对时钟而言的,在进行时序约束时所指的就是这种,而很多网友以前学习的建立时间保持时间的概念是针对信号而言的,所指的对象不同,分析出来的结论完全相反,一定注意不要混淆。

)lh1688:不考虑CLOCK SKEW情况下。

D2的建立时间要求:Tco1+T1(logic delay)+Tsetup2 < Tc (CLOCK周期) 。

那么Tsetup2 < Tc(CLOCK 周期) -(Tco1+T1)。

这个应该比较容易理解。

相对的保持时间实际就是路径的总延时(Tco1+T1)。

保持时间Thold2 < (Tco1+T1)。

建立时间与保持时间概述(EETOP)关于建立时间和保持时间,如下图普及一下基础知识先:其中Tcq 触发器时钟到数据输出的延时,Tcd 时钟的延时参数Tpd 组合逻辑的延时,Tsetup 触发器的保持时间。

因为数据到达触发器的时间至少要比时钟沿早一个建立时间,则有Tcq+Tpd+Tsetup+T,建立时间裕量=T时钟周期+Tcd,由于T建立时间裕量>0。

所以要求的最小时钟周期即为T=Tcq+Tpd+Tsetup-Tcd时钟周期为T,触发器D1的时钟沿到来到触发器Q变化的时间Tco(CLK--Q)最大为T1max,最小为T1min,逻辑组合电路的延迟时间最大为T2max,最小为T2min,问触发器D2的建立时间和保持时间。

该题最终答案:T3setup< FONT>maxbird:D2的保持时间就是时钟沿到来之后,D2的数据输入端要保持数据不变的时间,这个时间是由D1和D2之间的组合逻辑时延决定的。

例如:假设D1和D2之间的组合逻辑时延为2ns,时钟周期为10ns,这意味着在时钟沿来到后,D1输出的新数据要过2ns才会到达D2的数据输入端,那么在这2ns内,D2的数据输入端保持的还是上一次的旧数据,其值不会立即更新,假设D2的最小保持时间为3ns,这意味时钟沿到来后,D2的数据输入端的值在3ns内不能有变化,回到问题的关键,由于D1在时钟沿到来后的输出结果,经过2ns的组合逻辑延时便到达了D2的输入端,而D2要求在时钟沿到来后的3ns内其输入端的值不能改变,这样D2的保持时间就得不到满足,所以D2的保持时间必须小于等于2ns。

至于说T2min 为0时的情况,其实T2min是永远不能为0的,即使是一根导线其时延也是不可能为0的,这就是为什么移位寄存器的两个触发器之间连的只是一根导线,导线后端触发器的保持时间却还是可以满足的原因,其实移位寄存器中触发器的保持时间可以看成是小于等于其间导线的时延。

建立时间:触发器在时钟沿来到前,其数据输入端的数据必须保持不变的时间;保持时间:触发器在时钟沿来到后,其数据输入端的数据必须保持不变的时间。

如下图:因为触发器内部数据的形成是需要一定的时间的,如果不满足建立和保持时间,触发器将进入亚稳态,进入亚稳态后触发器的输出将不稳定,在0和1之间变化,这时需要经过一个恢复时间,其输出才能稳定,但稳定后的值并不一定是你的输入值。

这就是为什么要用两级触发器来同步异步输入信号。

这样做可以防止由于异步输入信号对于本级时钟可能不满足建立保持时间而使本级触发器产生的亚稳态传播到后面逻辑中,导致亚稳态的传播。

两级触发器可防止亚稳态传播的原理:假设第一级触发器的输入不满足其建立保持时间,它在第一个脉冲沿到来后输出的数据就为亚稳态,那么在下一个脉冲沿到来之前,其输出的亚稳态数据在一段恢复时间后必须稳定下来,而且稳定的数据必须满足第二级触发器的建立时间,如果都满足了,在下一个脉冲沿到来时,第二级触发器将不会出现亚稳态,因为其输入端的数据满足其建立保持时间。

同步器有效的条件:第一级触发器进入亚稳态后的恢复时间 + 第二级触发器的建立时间 < = 时钟周期。

maxbird在该部分详细说明了建立时间和保持时间的概念,以及如果不满足二者可能导致的亚稳态的传播。

注意这里说的建立时间和保持时间都是针对时钟而言的,在进行时序约束时所指的就是这种,而很多网友以前学习的建立时间保持时间的概念是针对信号而言的,所指的对象不同,分析出来的结论完全相反,一定注意不要混淆。

不考虑CLOCK SKEW情况下。

D2的建立时间要求:Tco1+T1(logic delay)+Tsetup2 <Tc(CLOCK 周期) 。

那么Tsetup2 < Tc(CLOCK 周期)-(Tco1+T1)。

这个应该比较容易理解。

相对的保持时间实际就是路径的总延时(Tco1+T1)。

保持时间Thold2 <(Tco1+T1)。