第五章DSP芯片的程序结构

DSP芯片的基本结构和特征ppt课件

• 学习DSP芯片的结构和特征,对于深入理解

DSP芯片的操作过程,掌握DSP芯片的开发 和应用技术具有很重要的意义

二、基本结构

程序 存储器

程序地址 发生单元

数据 存储器

外部存储器 接口

数据总线

程序总线

数据地址 发生单元

指令缓存

DMA 处理器

定时器

时钟单元

等待状态 发生器

DSP芯片的基本结构和特征

1. 引言 2. 基本结构 3. 中央处理单元CPU 4. 总线结构和流水线 5. 片内存储器 6. 片内外设

7. TI定点DSP芯片 8. TI浮点DSP芯片 9. 其他DSP芯片简介 10.小结 11.习题与思考题

一、引 言

• 在DSP芯片操作中,许多特殊功能是与DSP

C20x

(ns) (字) (字) (字) 串口 串口

C203

25/35/50

-

544

-

1

1

C204

25/35/50

4K

544

-

1

1

C205

25/35/50

-

4.5K

-

1

1

F206

25/35/50

-

4.5K

32 K

1

1

F207

25/35/50

-

4.5K

32 K

2

1

C209

35/50

4K

4.5K

-

-

-

七、TI定点DSP芯片

三、CPU

3.4 乘累加单元

CB15-CB0 DB15-DB0 PB15-PB0

40 累加器A

DSP芯片介绍(精)

DSP 芯片介绍1 什么是DSP 芯片DSP 芯片,也称数字信号处理器,是一种具有特殊结构的微处理器。

DSP芯片的内部采用程序和数据分开的哈佛结构,具有专门的硬件乘法器,广泛采用流水线操作,提供特殊的DSP 指令,可以用来快速地实现各种数字信号处理算法。

根据数字信号处理的要求,DSP芯片一般具有如下的一些主要特点:(1)在一个指令周期内可完成一次乘法和一次加法。

(2)程序和数据空间分开,可以同时访问指令和数据。

(3)片内具有快速RAM,通常可通过独立的数据总线在两块中同时访问。

(4)具有低开销或无开销循环及跳转的硬件支持。

(5)快速的中断处理和硬件I/O支持。

(6)具有在单周期内操作的多个硬件地址产生器。

(7)可以并行执行多个操作。

(8)支持流水线操作,使取指、译码和执行等操作可以重叠执行。

与通用微处理器相比,DSP芯片的其他通用功能相对较弱些。

2 DSP芯片的发展世界上第一个单片DSP 芯片是1978年AMI 公司宣布的S2811,1979年美国Iintel 公司发布的商用可编程期间2920是DSP 芯片的一个主要里程碑。

这两种芯片内部都没有现代DSP 芯片所必须的单周期芯片。

1980年。

日本NEC 公司推出的μPD7720是第一个具有乘法器的商用DSP 芯片。

第一个采用CMOS 工艺生产浮点DSP 芯片的是日本的Hitachi 公司,它于1982年推出了浮点DSP 芯片。

1983年,日本的Fujitsu 公司推出的MB8764,其指令周期为120ns ,且具有双内部总线,从而处理的吞吐量发生了一个大的飞跃。

而第一个高性能的浮点DSP 芯片应是AT&T公司于1984年推出的DSP32。

在这么多的DSP 芯片种类中,最成功的是美国德克萨斯仪器公司(Texas Instruments,简称TI)的一系列产品。

TI公司灾982年成功推出启迪一代DSP 芯片TMS32010及其系列产品TMS32011、TMS32C10/C14/C15/C16/C17等,之后相继推出了第二代DSP 芯片TMS32020、TMS320C25/C26/C28,第三代DSP 芯片TMS32C30/C31/C32,第四代DSP 芯片TMS32C40/C44,第五代DSP 芯片TMS32C50/C51/C52/C53以及集多个DSP 于一体的高性能DSP 芯片TMS32C80/C82等。

第五章 DSP系统设计

随着大规模集成芯片和可编程逻辑芯片的发展,使硬

件原理设计的难度得以降低,但它依然是DSP系统集成 中关键的一步。原理图设计的成功与否是DSP系统能否

正常工作的最重要的一个因素。

16/39

第五章

DSP系统设计

5.1 系统设计— DSP系统硬件设计

第四步:PCB设计

PCB图的设计要求DSP系统的设计人员既要熟悉系

流之间留有一定余量,因为峰值电流会更大,余量至少

是20%。 现有的电源模块分AC/DC型和DC/DC型。DSP设计中常用 DC/DC型。 DC/DC型中又分开关型和线性低压降型(LDO)。开关型效

率高,但体积大、纹波大。线性LDO型体积小巧,但效率

低,其效率相当于输出电压和输入电压之比,例如5V转 1.8V的效率仅32%,只适用于电流较小的场合。

的电流消耗。 以AD6P21060/ADSP 21062为例,其进行FFT运算时,需 要的电源电流最大,这一峰值电流约是700 mA,但这是 在最“坏”情况下,真正的电流消耗比这小很多。

19/39

第五章

DSP系统设计

5.2 电路设计— 电源设计

因此在设计电源时,必须考虑在电源电流和实际需用电

出现问题时,一般采用修改软件的方法,如果软件修改

无法解决问题,则必须调整硬件,这时问题就严重了。

18/39

第五章

DSP系统设计

5.2 电路设计— 电源设计

DSP使用的电源是数字电源,这些电源必须满足一定要 求,一般要求纹波不超过10%;还应准确估算出DSP及

其外围器件的功耗。DSP数据手册给出了各种情况下DSP

电路设计时有必要采用多层印刷板,一般建议其中 一层是地层。优点:减少干扰;布线时省去了大量 器件管脚接地的工作量。注意:现在DSP等元件广泛 采用表贴封装,在器件布线时,将尽可能多的网络

DSP原理与应用2011-第五章 TMS320F28335片内外设_ad转换SCI

掌握TMS320F28335内核结构,例如A/D转换、串行通信接口、 串行 外设接口。

重点:

TMS320F28335内部A/DC的正确使用,串行通信接口应用。

难点:

TMS320F28335的ADC寄存器操作和串行通信寄存器操作。

教学内容分两部分

§5.1:TMS320F28335内模拟/数字转换 §5.2 :TMS320F28335系列串行通信接口SCI和Modbus协议介绍

7

§5.1 .2 ADC有关的寄存器

控制寄存器

通道顺序选 择寄存器

结 果 寄 存 器

DSP原理与应用

2012年9月3日

8

ADC有关的寄存器(序)

控制寄存器 状态寄存器

参考电压选择寄存器 偏移电压调整寄存器

DSP原理与应用

2012年9月3日

9

§5.1.3 ADC 操作模式

根据采样模式划分,包括顺序采样和同步采样 1) 顺序采样模式(Sequential Sampling Mode)

DSP原理与应用

2012年9月3日

10

2) 同步采样模式(Simultaneous Sampling Mode)

DSP原理与应用

2012年9月3日

11

根据转换模式划分,包括: 级联模式转换和和双序列模式转换 1) 级联模式转换

DSP原理与应用

2012年9月3日

12

2) 双序列模式转换

DSP原理与应用

DSP原理与应用

4

Sequencer can be operated as two independent 8-state sequencers or as one large 16-state sequencer (i.e., two cascaded 8-state sequencers).

DSP芯片制造工艺流程

DSP芯片制造工艺流程DSP(Digital Signal Processing)芯片是一种专门用于数字信号处理的集成电路芯片。

它可以通过算法来解析、处理和转换数字信号,广泛应用于音频、视频和无线通信等领域。

下面将介绍DSP芯片的制造工艺流程。

首先,DSP芯片的制造工艺流程包括概念设计、前期设计、制造工艺设计、掩膜制作、晶圆加工、封装测试等多个环节。

首先是概念设计阶段。

在这个阶段,芯片设计工程师会根据芯片的功能需求和性能指标进行初步的设计方案制定。

他们会选择适合的处理器核心、内存、接口等组件,并进行电路图设计和模拟仿真以验证设计的可行性。

接下来是前期设计阶段。

在这个阶段,芯片设计工程师会使用专业的EDA(Electronic Design Automation)软件工具进行详细的电路设计和布局。

他们会将电路图转换为物理结构,考虑电路元件的大小、位置和连接方式,以及电源分配和信号路由等。

在此过程中,他们还会进行各种静态和动态的电性能分析和优化。

然后是制造工艺设计阶段。

在这个阶段,芯片制造工程师会根据芯片设计图纸,选择合适的制造工艺流程,并确定各种加工步骤和参数。

这些包括光刻、薄膜沉积、腐蚀、离子注入、扩散、金属化和封装测试等。

随后是掩膜制作阶段。

掩膜是制造芯片的重要工具,它是一种透明薄膜,上面印刷有电路图案。

掩膜制作工程师会根据制造工艺设计的要求,通过光刻技术将电路图案转移到掩膜上。

然后是晶圆加工阶段。

晶圆是制造芯片的基材,它通常是用纯度极高的硅材料制成。

晶圆加工工程师会使用掩膜将电路图案印刷到晶圆表面上,并通过一系列的工艺步骤,将掩膜中的电路图案转移到晶圆上。

这些步骤包括光刻、薄膜沉积、腐蚀、离子注入、扩散、金属化等。

最后是封装测试阶段。

在这个阶段,芯片封装工程师会将晶圆上的芯片切割成单独的芯片,并将其封装到塑料、陶瓷或金属封装中。

接下来进行测试,以确保芯片的功能和性能符合设计要求。

总结起来,DSP芯片的制造工艺流程包括概念设计、前期设计、制造工艺设计、掩膜制作、晶圆加工、封装测试等多个环节。

dsp芯片的原理与开发应用课件

DSP芯片的原理与开发应用课件1. 什么是DSP芯片DSP芯片(Digital Signal Processing Chip)是一种专门用于数字信号处理的集成电路芯片。

它具有强大的计算能力和高速处理速度,广泛应用于音频信号处理、图像处理、通信系统、雷达信号处理等领域。

2. DSP芯片的工作原理DSP芯片通过高效的算法和硬件加速器,对输入的数字信号进行采样、压缩、编码、滤波、频谱分析、解调、解码等处理,得到所需的输出信号。

其工作原理大致如下:1.信号采样:DSP芯片将输入的连续模拟信号通过采样电路转换为离散数字信号。

2.数字信号处理:DSP芯片使用内置的运算器和指令集,对采样到的数字信号进行各种算法处理,如滤波、频域变换、时域变换等。

3.运算加速:为了提高处理速度,DSP芯片通常配备专门的硬件加速器,如DSP协处理器、FPGA等,来协助完成复杂的计算任务。

4.输出处理:处理后的数字信号经过解码、解调等步骤后,再通过解调电路将其还原为模拟信号,输出到外部设备或其他系统中。

3. DSP芯片的开发应用3.1 音频信号处理DSP芯片在音频领域的应用非常广泛,可以用于音频编解码、音效处理、语音识别等。

通过采用各种数字算法,DSP芯片可以实现高质量音频信号处理和实时音效增强,提升用户体验。

在音频编解码方面,DSP芯片支持各种音频格式的解码和编码,如MP3、AAC、WAV等。

通过对音频信号进行压缩和解压缩,可以有效减小音频文件的大小,提高存储和传输效率。

3.2 图像处理DSP芯片在图像处理领域的应用日益重要。

利用DSP芯片的高速计算能力和并行处理能力,可以实现图像的滤波、边缘检测、图像增强、图像压缩等功能。

图像处理算法包括傅里叶变换、离散余弦变换、边缘检测、图像分割等。

这些算法可以在DSP芯片上进行高效的实现,帮助用户快速获得满足各种图像处理需求的结果。

3.3 通信系统DSP芯片在通信系统中起到了关键作用。

通信系统中需要对信号进行调制、解调、滤波、编解码等处理。

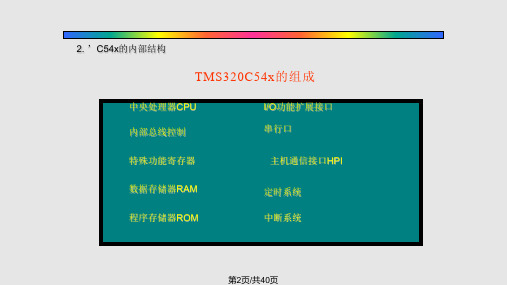

DSP原理及应用DSP芯片的硬件结构节讲稿

特殊功能 寄存器

TMS320C54x的硬件结构图

PAB

程序存储器

PB

数据存储器

CAB

串行口

CB

并行口

DAB

定时器

DB

计数器

EAB

中断

EB

外部 存储器 接口

外部 设备 接口

乘法

C累PU加器

算术/逻辑 运算单元

比较器

桶形 移位器

第3页/共40页

2.2 ’C54x的主要特性和外部引 脚2.2.1 ’C54x的主要特性 1、CPU 2、存储器 3、指令系统 其特性还将在后面章节专门介绍

1 9 BIT0 1 8 BIT1 1 7 BIT2 1 6 BIT3 1 5 BIT4 1 4 BIT5 1 3 BIT6 1 2 BIT7

10

GND

GND

15 14 13 12 11 10 9 7

SEG0 1 1 SEG1 7 SEG2 4 SEG3 2 SEG4 1 SEG5 1 0 SEG6 5 SEG7 3

SEG0 1 1 SEG1 7 SEG2 4 SEG3 2 SEG4 1 SEG5 1 0 SEG6 5 SEG7 3

U2 A 2

3

7 4HC0 2 1

U2 B 5

6

7 4HC0 2 4

U2 C 8

9

7 4HC0 2 10

U2 D 11

12

7 4HC0 2 13

a

DS1

b

c

d

e

f

g

dp

a

DS2

b

c

d

第32页/共40页

8. 测试引脚 TCK:测试时钟输入引脚; TDI:测试数据输入引脚; TDO:测试数据输出引脚; TMS:测试方式选择引脚; TRST:测试复位引脚; EMU0:仿真器中断0引脚; EMU1/OFF:仿真器中断1引脚/关断所有 输出引脚。

DSP芯片原理课件

3 FIR滤波器的设计和实现

4 IIR滤波器的设计和实现

学习如何设计和实现FIR滤法,以及其在 DSP中的应用。

数字降噪技术

1 语音信号处理的基本方法

探索在语音信号处理中使用的基本方法和技 术。

2 视频图像处理的基本方法

了解视频图像处理中常用的基本方法和技术。

解释DSP芯片在无线通信系统中的关键角色和应用 案例。

图像识别

描述DSP芯片如何实现高效的图像识别算法。

DSP芯片的未来发展趋势

1 DSP芯片与人工智能的结合

探讨DSP芯片与人工智能的结合,以及在AI领域的应用前景。

2 DSP芯片的应用前景分析

分析DSP芯片在不同领域中的应用前景,并展望未来的发展方向。

3 滤波器的基本概念和设计方法

介绍滤波器的基本概念、种类和设计方法。

4 浮点数和定点数表示方式

讲解数字信号处理中浮点数和定点数表示方 式的区别和应用场景。

DSP算法的分类

1 DSP算法分析和评价指标

探讨不同DSP算法的分类和如何评价其性能 指标。

2 FFT算法的实现原理

详细解释FFT算法的实现原理和在信号处理 中的应用。

3 DSP芯片的开发环境和工具介绍

介绍DSP芯片的开发环境和常用工具,帮助 开发者更好地进行应用开发。

4 DSP系统的设计和实现

深入研究DSP系统的设计原理和实际实现过 程。

DSP芯片应用案例分享

音频处理

介绍DSP芯片在音频处理中的应用案例。

视频压缩

展示DSP芯片在视频压缩领域的成功案例。

无线通信

DSP芯片原理课件

这个DSP芯片原理课件将深入讲解DSP芯片的概述、历史和发展、基本组成 和工作原理,以及在各个应用领域的应用。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2008-10-8

汇编器对块的处理

未初始化块 .bss 变量存放空间 .usect 用户自定义的未初始化段初始化块 .text 汇编指令代码 .data 常数数据(比如对变量的初始化数据) .sect 用户自定义的已初始化段 .asect 通.sect,多了绝对地址定位功能,一般 不用

2008-10-8

C语言的段

未初始化块(data) .bss 存放全局和静态变量 .ebss 长调用的.bss(超过了64K地址 限制) .stack 存放C语言的栈 .sysmem 存放C语言的堆 .esysmem 长调用的.sysmem(超过了 64K地址限制)

2008-10-8

1、栈区(stack)— 由编译器自动分配释 放 ,存放函数的参数值,局部变量的值等。 其操作方式类似于数据结构中的栈。 2、堆区(heap) — 一般由程序员分配释 放, 若程序员不释放,程序结束时可能由 OS回收 。

2008-10-8

连接命令文件(CMD)

MEMORY指定存储空间 MEMORY { PAGE 0: name 0 [attr] : origin = constant, length = constant PAGE n: name n [attr] : origin = constant, length = constant } PAGE n:标示存储空间,n<255;PAGE 0为程序存储空间; PAGE 1为程序存储空间 name:存储空间名称 attr:存储空间属性:只读R,只写W,可包含可执行代码X, 可以被初始化I。 orgin:用来定义存储空间的起始地址 Lenth:用来定义存储空间的长度 2008-10-8

2008-10-8

自定义段(C语言)

#pragma DATA_SECTION(函数名或全局变 量名,"用户自定义在数据空间的段名");

#pragma CODE_SECTION(函数名或全 局变量名,"用户自定义在程序空间的段名"); 不能在函数体内声明。 必须在定义和使用前声明 #pragma可以阻止对未调用的函数的优化

2008-10-8

COFF格式:详细的COFF文件格式包括段 头,可执行代码和初始化数据,可重定 位信息,行号入口,符号表,字符串表 等,这些属于编写操作系统和编译器人 员关心范畴。而对于C只需要了解定义段 和给段分配空间就可以了。 采用COFF更有利于模块化编程,程序员 可以自由决定愿意把哪些代码归属到哪 些段,然后加以不同的处理。

2008-10-8

SDJU

第五章DSP芯片的程序结构

重点与难点及要求 重点:CMD文件的编写 难点:COFF文件的含义 要求:理解COFF文件,掌握CMD文 件的编写。

2008-10-8

CMD文件的编写

COFF格式 通用目标文件格式(Common Object File Format)是一种流行的二进制可执 行文件格式,二进制可执行文件包括库 文件(lib),目标文件(obj)最终可 执行文件(out)。现今PC机上的 Windows95和NT4.0以后的操作系统的二 进制文件格式(PE)就是在COFF格NS分配段

SECTIONS

{ name : [property,property,……] } PAGE = n,段位于那个存储页面空间。

2008-10-8

直接写编译命令 -l rts2800_ml.lib 连接系统文件 rts2800_ml.lib -o filename.out 最终生成的二进制 文件命名为filename.out -m filename.map 生成映射文件 filename.map -stack 0x200 堆栈为512字

2008-10-8

初始化块 .text 可执行代码和常数(program) .switch switch语句产生的常数表格(program/ 低64K数据空间) .cinit 用来存放对全局和静态变量的初始化常 数值(program) .const 全局和静态的const变量初始化值和字 符串常数,(data) .econst 长.const(可定位到任何地方)(data)

2008-10-8

2008-10-8

Section

Section目标文件中最小单位称为块。一个 块就是最终在存储器映象中占据连续空间 的一段代码或数据。

2008-10-8

COFF目标文件包含三个默认的块: .text可执行代码 .data已初始化数据 .bss为未初始化数据保留的空间