MC74AC20DG中文资料

MC74HC00ADR2G,MC74HC00ADTR2G,MC74HC00ADG,MC74HC00ANG,规格书,Datasheet 资料

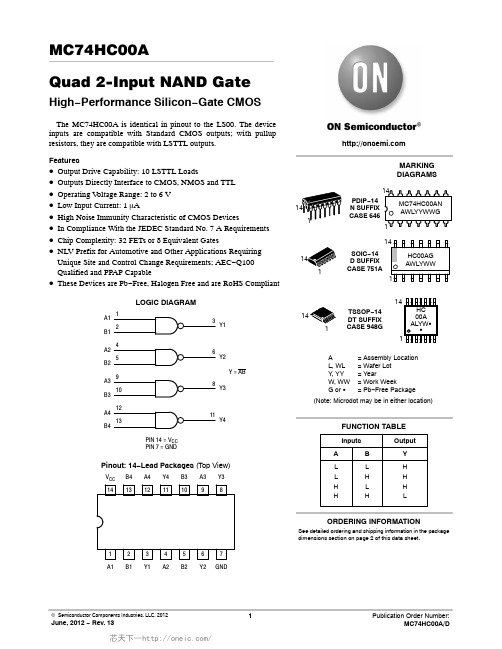

MC74HC00AQuad 2-Input NAND GateHigh −Performance Silicon −Gate CMOSThe MC74HC00A is identical in pinout to the LS00. The device inputs are compatible with Standard CMOS outputs; with pullup resistors, they are compatible with LSTTL outputs.Features•Output Drive Capability: 10 LSTTL Loads•Outputs Directly Interface to CMOS, NMOS and TTL •Operating V oltage Range: 2 to 6 V •Low Input Current: 1 m A•High Noise Immunity Characteristic of CMOS Devices•In Compliance With the JEDEC Standard No. 7 A Requirements •Chip Complexity: 32 FETs or 8 Equivalent Gates•NLV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC −Q100Qualified and PPAP Capable•These Devices are Pb −Free, Halogen Free and are RoHS CompliantY1A1PIN 14 = V CC PIN 7 = GNDLOGIC DIAGRAMB1Y2A2B2Y3A3B3Y4A4B4Y = AB Pinout: 14−Lead Packages (Top View)1314121110982134567V CC B4A4Y4B3A3Y3A1B1Y1A2B2Y2GNDL L H HLH L HFUNCTION TABLEInputs Output AB H H H LY See detailed ordering and shipping information in the package dimensions section on page 2 of this data sheet.ORDERING INFORMATIONMARKING DIAGRAMSA = Assembly Location L, WL = Wafer Lot Y , YY = YearW, WW = Work WeekG or G = Pb −Free PackageTSSOP −14DT SUFFIX CASE 948GSOIC −14D SUFFIX CASE 751AHC 00A ALYW G G114PDIP −14N SUFFIX CASE 646MC74HC00AN AWLYYWWG114(Note: Microdot may be in either location)MAXIMUM RATINGSSymbol Parameter Value Unit V CC DC Supply Voltage (Referenced to GND)– 0.5 to + 7.0V V in DC Input Voltage (Referenced to GND)– 0.5 to V CC + 0.5V V out DC Output Voltage (Referenced to GND)– 0.5 to V CC + 0.5VI in DC Input Current, per Pin±20mA I out DC Output Current, per Pin±25mA I CC DC Supply Current, V CC and GND Pins ±50mAP DPower Dissipation in Still Air,Plastic DIP†SOIC Package†TSSOP Package†750500450mWT stg Storage Temperature – 65 to + 150_C T LLead Temperature, 1 mm from Case for 10 SecondsPlastic DIP , SOIC or TSSOP Package260_CStresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.†Derating —Plastic DIP: – 10 mW/_C from 65_ to 125_CSOIC Package: – 7 mW/_C from 65_ to 125_C TSSOP Package: − 6.1 mW/_C from 65_ to 125_CRECOMMENDED OPERATING CONDITIONSSymbol Parameter Min Max Unit V CC DC Supply Voltage (Referenced to GND)2.0 6.0V V in , V out DC Input Voltage, Output Voltage (Referenced to GND)0V CCVT AOperating Temperature, All Package Types – 55+ 125_C t r , t fInput Rise and Fall TimeV CC = 2.0 V(Figure 1)V CC = 4.5 V V CC = 6.0 V001000500400nsORDERING INFORMATIONDevicePackage Shipping †MC74HC00ANG PDIP −14(Pb −Free)25 Units / Rail MC74HC00ADG SOIC −14(Pb −Free)55 Units / Rail MC74HC00ADR2G SOIC −14(Pb −Free)2500 / Tape & Reel MC74HC00ADTR2G TSSOP −14(Pb −Free)2500 / Tape & Reel NLV74HC00ADG*SOIC −14(Pb −Free)55 Units / Rail NLV74HC00ADR2G*SOIC −14(Pb −Free)2500 / Tape & Reel NLV74HC00ADTR2G*TSSOP −14(Pb −Free)2500 / Tape & Reel NLV74HC00ANG*PDIP −14(Pb −Free)25 Units / Rail†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.*NLV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC −Q100 Qualified and PPAP CapableThis device contains protection circuitry to guard against damage due to high static voltages or electric fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated voltages to this high −impedance cir-cuit. For proper operation, V in and V out should be constrained to the range GND v (V in or V out ) v V CC .Unused inputs must always be tied to an appropriate logic voltage level (e.g., either GND or V CC ).Unused outputs must be left open.DC CHARACTERISTICS(Voltages Referenced to GND)V CC V Guaranteed LimitSymbol Parameter Condition−55 to 25°C≤85°C≤125°C UnitV IH Minimum High−Level InputVoltage V out = 0.1V or V CC−0.1V|I out| ≤ 20m A2.03.04.56.01.502.103.154.201.502.103.154.201.502.103.154.20VV IL Maximum Low−Level InputVoltage V out = 0.1V or V CC− 0.1V|I out| ≤ 20m A2.03.04.56.00.500.901.351.800.500.901.351.800.500.901.351.80VV OH Minimum High−Level OutputVoltage V in = V IH or V IL|I out| ≤ 20m A2.04.56.01.94.45.91.94.45.91.94.45.9VV in =V IH or V IL|I out| ≤ 2.4mA|I out| ≤ 4.0mA|I out| ≤ 5.2mA3.04.56.02.483.985.482.343.845.342.203.705.20V OL Maximum Low−Level OutputVoltage V in = V IH or V IL|I out| ≤ 20m A2.04.56.00.10.10.10.10.10.10.10.10.1VV in = V IH or V IL|I out| ≤ 2.4mA|I out| ≤ 4.0mA|I out| ≤ 5.2mA3.04.56.00.260.260.260.330.330.330.400.400.40I in Maximum Input LeakageCurrentV in = V CC or GND 6.0±0.1±1.0±1.0m AI CC Maximum Quiescent SupplyCurrent (per Package)V in = V CC or GNDI out = 0m A6.0 1.01040m AAC CHARACTERISTICS(C L = 50 pF, Input t r = t f = 6 ns)V CC V Guaranteed LimitSymbol Parameter−55 to 25°C≤85°C≤125°C Unitt PLH, t PHL Maximum Propagation Delay, Input A or B to Output Y(Figures 1 and 2)2.03.04.56.07530151395401916110552219nst TLH, t THL Maximum Output Transition Time, Any Output(Figures 1 and 2)2.03.04.56.07527151395321916110362219nsC in Maximum Input Capacitance101010pFC PD Power Dissipation Capacitance (Per Buffer)*Typical @ 25°C, V CC = 5.0 V, V EE = 0 VpF22*Used to determine the no−load dynamic power consumption: P D = C PD V CC f + I CC V CC.Figure 1. Switching WaveformsGNDV CCOUTPUT YINPUT A OR BC L **Includes all probe and jig capacitanceTESTPOINTFigure 2. Test CircuitYA BFigure 3. Expanded Logic Diagram(1/4 of the Device)PDIP−14 N SUFFIX CASE 646−06 ISSUE PDIM MIN MAX MIN MAXMILLIMETERSINCHESA0.7150.77018.1619.56B0.2400.260 6.10 6.60C0.1450.185 3.69 4.69D0.0150.0210.380.53F0.0400.070 1.02 1.78G0.100 BSC 2.54 BSCH0.0520.095 1.32 2.41J0.0080.0150.200.38K0.1150.135 2.92 3.43LM−−−10 −−−10N0.0150.0390.38 1.01__NOTES:1.DIMENSIONING AND TOLERANCING PER ANSIY14.5M, 1982.2.CONTROLLING DIMENSION: INCH.3.DIMENSION L TO CENTER OF LEADS WHENFORMED PARALLEL.4.DIMENSION B DOES NOT INCLUDE MOLD FLASH.5.ROUNDED CORNERS OPTIONAL.KM0.13 (0.005)0.2900.3107.377.87CASE 751A −03ISSUE KNOTES:1.DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.2.CONTROLLING DIMENSION: MILLIMETERS.3.DIMENSION b DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE PROTRUSION SHALL BE 0.13 TOTAL IN EXCESS OF AT MAXIMUM MATERIAL CONDITION.4.DIMENSIONS D AND E DO NOT INCLUDE MOLD PROTRUSIONS.5.MAXIMUM MOLD PROTRUSION 0.15 PERSIDE.DETAIL ADIM MIN MAX MIN MAX INCHESMILLIMETERS D 8.558.750.3370.344E 3.80 4.000.1500.157A 1.35 1.750.0540.068b 0.350.490.0140.019L 0.40 1.250.0160.049e 1.27 BSC 0.050 BSC A30.190.250.0080.010A10.100.250.0040.010M0 7 0 7 H 5.80 6.200.2280.244h 0.250.500.0100.019____14X0.581.27PITCH*For additional information on our Pb −Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.DT SUFFIX CASE 948G −01ISSUE BDIM MIN MAX MIN MAX INCHESMILLIMETERS A 4.90 5.100.1930.200B 4.30 4.500.1690.177C −−− 1.20−−−0.047D 0.050.150.0020.006F 0.500.750.0200.030G 0.65 BSC 0.026 BSC H 0.500.600.0200.024J 0.090.200.0040.008J10.090.160.0040.006K 0.190.300.0070.012K10.190.250.0070.010L 6.40 BSC 0.252 BSC M0 8 0 8 NOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSION A DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE.4.DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 (0.010) PER SIDE.5.DIMENSION K DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08(0.003) TOTAL IN EXCESS OF THE K DIMENSION AT MAXIMUM MATERIAL CONDITION.6.TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY .7.DIMENSION A AND B ARE TO BE DETERMINED AT DATUM PLANE −W −.____14X REF 14X0.360.65PITCHSOLDERING FOOTPRINT**For additional information on our Pb −Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

MC74ACT640DWG资料

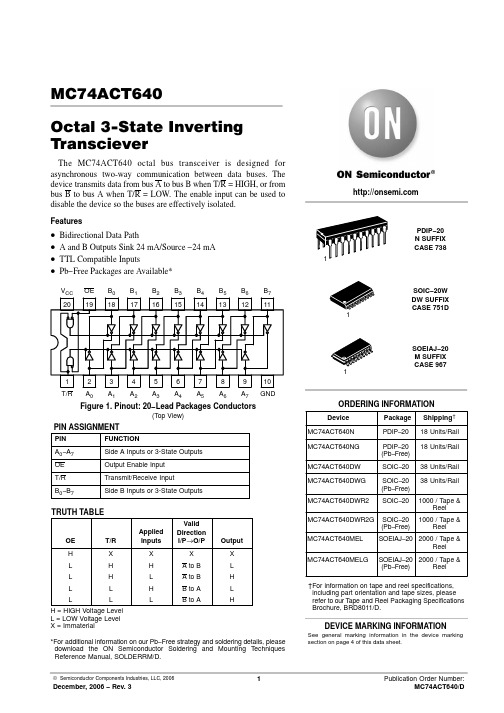

MC74ACT640Octal 3−State Inverting TranscieverThe MC74ACT640 octal bus transceiver is designed for asynchronous two-way communication between data buses. The device transmits data from bus A to bus B when T/R = HIGH, or from bus B to bus A when T/R = LOW. The enable input can be used to disable the device so the buses are effectively isolated.Features•Bidirectional Data Path•A and B Outputs Sink 24 mA/Source −24 mA•TTL Compatible Inputs•Pb−Free Packages are Available*V OE B B B B B B B BT/R A0A1A2A3A4A5A6A7GNDFigure 1. Pinout: 20−Lead Packages Conductors(Top View)PIN ASSIGNMENTPIN FUNCTIONA0−A7Side A Inputs or 3-State OutputsOE Output Enable InputT/R Transmit/Receive InputB0−B7Side B Inputs or 3-State OutputsTRUTH TABLEOE T/R AppliedInputsValidDirectionI/P→O/P OutputH X X X XL H H A to B LL H L A to B H L L H B to A LL L L B to A H H = HIGH Voltage LevelL = LOW Voltage LevelX = Immaterial*For additional information on our Pb−Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.See general marking information in the device marking section on page 4 of this data sheet.DEVICE MARKING INFORMATIONMAXIMUM RATINGSSymbol Parameter Value Unit V CC DC Supply Voltage*0.5 to )7.0V V I DC Input Voltage*0.5 v V I v V CC)0.5V V O DC Output Voltage(Note 1)*0.5 v V O v V CC)0.5VI IK DC Input Diode Current$20mAI OK DC Output Diode Current$50mAI O DC Output Sink/Source Current$50mAI CC DC Supply Current per Output Pin$50mAI GND DC Ground Current per Output Pin$50mAT STG Storage Temperature Range*65 to )150_C T L Lead temperature, 1 mm from Case for 10 Seconds260_C T J Junction temperature under Bias)150_Cq JA Thermal resistance PDIPSOIC 6796_C/WP D Power Dissipation in Still Air at 85_C PDIPSOIC 750500mWMSL Moisture Sensitivity Level 1F R Flammability Rating Oxygen Index: 30% − 35%UL 94 V−0 @ 0.125 inV ESD ESD Withstand Voltage Human Body Model (Note 2)Machine Model (Note 3)Charged Device Model (Note 4)> 2000> 200> 1000VI Latchup Latchup Performance Above V CC and Below GND at 85_C (Note 5)$100mA Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.1.I O absolute maximum rating must be observed.2.Tested to EIA/JESD22−A114−A.3.Tested to EIA/JESD22−A115−A.4.Tested to JESD22−C101−A.5.Tested to EIA/JESD78.RECOMMENDED OPERATING CONDITIONSSymbol Parameter Min Typ Max Unit V CC DC Input Voltage (Referenced to GND) 4.5 5.5V V in, V out DC Input Voltage, Output Voltage (Referenced to GND)0V CC V T A Operating Temperature, All Package Types−4025+85°Ct r, t f Input Rise and Fall Time (Note 7)V CC = 4.5 VV CC = 5.5 V 0108.0108.0ns/VT J Junction Temperature (PDIP)140°CI OH Output Current − High−24mAI OL Output Current − Low24mA6.Unused Inputs may not be left open. All inputs must be tied to a high voltage level or low logic voltage level.7.V in from 0.8 V to 2.0 V; refer to individual Data Sheets for devices that differ from the typical input rise and fall times.DC CHARACTERISTICSSymbol Parameter V CC(V)T A = +255CT A = −405C to+855CUnit Conditions Typ Guaranteed LimitsV IH Minimum High Level Input Voltage 4.55.51.51.52.02.02.02.0VVV OUT = 0.1 VorV CC − 0.1 VV IL Maximum Low Level Input Voltage 4.55.51.51.50.80.80.80.8VVV OUT = 0.1 VorV CC − 0.1 VV OH Minimum High Level Output Voltage 4.55.54.495.494.45.44.45.4VVI OUT = −50 m A4.55.53.864.863.764.76VV*V IN = V IL or V IH−24 mAI OH−24 mAV OL Maximum Low Level Output Voltage 4.55.50.0010.0010.10.10.10.1VVI OUT = 50 m A4.55.50.360.360.440.44VV*V IN = V IL or V IH−24 mAI OH−24 mAI IN Maximum Input Leakage Current 5.5±0.1±1.0m A V I = V CC, GND D I CCT Additional Max. I CC/Input 5.50.6 1.5mA V I = V CC − 2.1 V I OZ Maximum 3−State Current 5.5±0.5±5.0m A V I (OE) = V IL, V IHV I = V CC, GNDV O = V CC, GNDI OLD I OHD †Minimum Dynamic Output Current 5.55.575−75mAmAV OLD = 1.65 V MaxI CC Maximum Quiescent Supply Current 5.58.080m A V IN = V CC or GND *All outputs loaded; thresholds on input associated with output under test.†Maximum test duration 2.0 ms, one output loaded at a time.AC CHARACTERISTICS t r = t f = 3.0 ns (For Figures and Waveforms, See Figures 2 and 3.)Symbol Parameter V CC*(V)T A = +255CC L = 50 pFT A = −405C to +855CC L = 50 pFUnit Min Max Min Maxt PLH Propagation Delay An to Bn or Bn to An 5.0 1.58.0 1.08.5ns t PHL Propagation Delay An to Bn or Bn to An 5.0 1.58.0 1.09.0ns t PZH Output Enable Time OE to An or Bn 5.0 1.510.0 1.011.0ns t PZL Output Enable Time OE to An or Bn 5.0 1.510.0 1.011.0ns t PHZ Output Disable Time T/R or OE to An or Bn 5.0 1.510.0 1.011.0ns t PLZ Output Disable Time T/R or OE to An or Bn 5.0 1.510.0 1.011.0ns *Voltage Range 5.0 V is 5.0 V ±0.5 VCAPACITANCESymbol Parameter Value Typ Unit Test ConditionsC IN Input Capacitance 4.5pF V CC = 5.0 VC I/O Input/Output Capacitance15pF V CC = 5.0 VC PD Power Dissipation Capacitance45pF V CC = 5.0 VSWITCHING WAVEFORMSFigure 2. Figure 3.*Includes all probe and jig capacitance50 W SCOPE TEST POINTFigure 4. Test CircuitINPUT3.0 VGNDINPUT A or BOUTPUT A or BGNDV OL V OHA OR BA OR BHIGHIMPEDANCE OEHIGHIMPEDANCE 3.0 V3.0 VGNDT/RMARKING DIAGRAMSPDIP−20SOIC−20WSOEIAJ−201A = Assembly Location WL = Wafer Lot YY, Y = YearWW = Work WeekG = Pb−Free PackagePACKAGE DIMENSIONSPDIP−20N SUFFIXPLASTIC DIP PACKAGECASE 738−03ISSUE ENOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: INCH.3.DIMENSION L TO CENTER OF LEAD WHEN FORMED PARALLEL.4.DIMENSION B DOES NOT INCLUDE MOLD FLASH.DIM MIN MAX MIN MAX MILLIMETERSINCHES A 25.6627.171.010 1.070B 6.10 6.600.2400.260C 3.81 4.570.1500.180D 0.390.550.0150.022G 2.54 BSC 0.100 BSC J 0.210.380.0080.015K 2.80 3.550.1100.140L 7.62 BSC 0.300 BSC M 0 15 0 15 N0.51 1.010.0200.040____E 1.27 1.770.0500.070F 1.27 BSC 0.050 BSC SOIC−20WDW SUFFIX CASE 751D−05ISSUE GPACKAGE DIMENSIONSSOEIAJ−20M SUFFIX CASE 967−01ISSUE ADIM MIN MAX MIN MAX INCHES−−− 2.05−−−0.081MILLIMETERS 0.050.200.0020.0080.350.500.0140.0200.150.250.0060.01012.3512.800.4860.5045.10 5.450.2010.2151.27 BSC 0.050 BSC 7.408.200.2910.3230.500.850.0200.0331.10 1.500.0430.0590 0.700.900.0280.035−−−0.81−−−0.032A 1H E Q 1L E _10 _0 _10 _NOTES:1.DIMENSIONING AND TOLERANCING PER ANSIY14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSIONS D AND E DO NOT INCLUDEMOLD FLASH OR PROTRUSIONS AND AREMEASURED AT THE PARTING LINE. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.15(0.006) PER SIDE.4.TERMINAL NUMBERS ARE SHOWN FORREFERENCE ONLY.5.THE LEAD WIDTH DIMENSION (b) DOES NOTINCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 (0.003)TOTAL IN EXCESS OF THE LEAD WIDTHDIMENSION AT MAXIMUM MATERIAL CONDITION.DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACEBETWEEN PROTRUSIONS AND ADJACENT LEAD TO BE 0.46 ( 0.018).A b c D E e L M ZON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

MC74ACT14DR2G,MC74AC14DG,MC74ACT14DG,MC74AC14NG,MC74ACT14DR2G,MC74ACT14DR2G, 规格书,Datasheet 资料

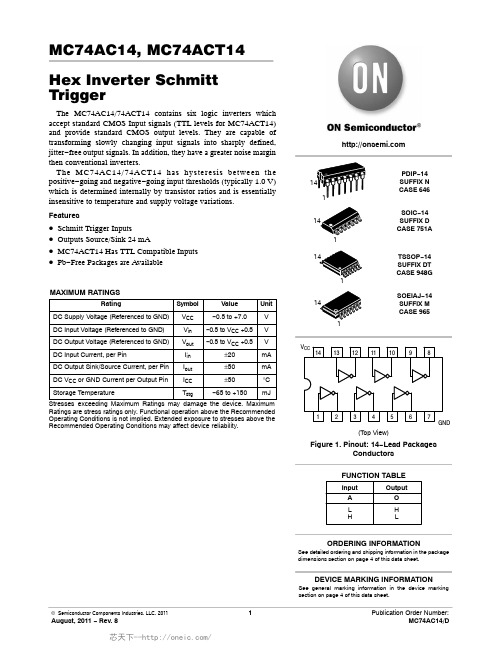

MC74AC14, MC74ACT14 Hex Inverter Schmitt TriggerThe MC74AC14/74ACT14 contains six logic inverters which accept standard CMOS Input signals (TTL levels for MC74ACT14) and provide standard CMOS output levels. They are capable of transforming slowly changing input signals into sharply defined, jitter−free output signals. In addition, they have a greater noise margin then conventional inverters.The MC74AC14/74ACT14 has hysteresis between the positive−going and negative−going input thresholds (typically 1.0 V) which is determined internally by transistor ratios and is essentially insensitive to temperature and supply voltage variations.Features•Schmitt Trigger Inputs•Outputs Source/Sink 24 mA•MC74ACT14 Has TTL Compatible Inputs•Pb−Free Packages are AvailableMAXIMUM RATINGSRating Symbol ValueUnit DC Supply Voltage (Referenced to GND)V CC−0.5 to +7.0V DC Input Voltage (Referenced to GND)V in−0.5 to V CC +0.5V DC Output Voltage (Referenced to GND)V out−0.5 to V CC +0.5V DC Input Current, per Pin I in±20mA DC Output Sink/Source Current, per Pin I out±50mA DC V CC or GND Current per Output Pin I CC±50°C Storage Temperature T stg−65 to +150mJ Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.SOEIAJ−14SUFFIX MCASE 965TSSOP−14SUFFIX DTCASE 948GSOIC−14SUFFIX DCASE 751APDIP−14SUFFIX NCASE 646See detailed ordering and shipping information in the package dimensions section on page 4 of this data sheet.ORDERING INFORMATIONSee general marking information in the device marking section on page 4 of this data sheet.DEVICE MARKING INFORMATION(Top View)Figure 1. Pinout: 14−Lead PackagesConductorsFUNCTION TABLEInputAOutputOLHHLRECOMMENDED OPERATING CONDITIONSSymbol Parameter Min Typ Max UnitV CC Supply Voltage ′AC 2.0 5.0 6.0V ′ACT 4.5 5.0 5.5V in, V out DC Input Voltage, Output Voltage (Ref. to GND)0−V CC Vt r, t f Input Rise and Fall Time (Note 1)′AC Devices except Schmitt InputsV CC @ 3.0 V−150−V CC @ 4.5 V−40−ns/VV CC @ 5.5 V−25−t r, t f Input Rise and Fall Time (Note 2)′ACT Devices except Schmitt InputsV CC @ 4.5 V−10−ns/VV CC @ 5.5 V−8.0−T J Junction Temperature (PDIP)−−140°C T A Operating Ambient Temperature Range−402585°CI OH Output Current − High−−−24mAI OL Output Current − Low−−24mA1.V in from 30% to 70% V CC; see individual Data Sheets for devices that differ from the typical input rise and fall times.2.V in from 0.8 V to 2.0 V; see individual Data Sheets for devices that differ from the typical input rise and fall times.DC CHARACTERISTICSSymbol Parameter V CC(V)74AC74ACUnit Conditions T A = +25°C T A = −40°C to +85°CTyp Guaranteed LimitsV OH Minimum High Level Output Voltage 3.0 2.99 2.9 2.9I OUT = −50 m A4.5 4.49 4.4 4.4V5.5 5.49 5.4 5.4V *V IN = V IL or V IH3.0− 2.56 2.46−12 mA4.5− 3.86 3.76I OH−24 mA5.5− 4.86 4.76−24 mA V OL Maximum Low Level Output Voltage 3.00.0020.10.1I OUT = 50 m A4.50.0010.10.1V5.50.0010.10.1V *V IN = V IL or V IH3.0−0.360.4412 mA4.5−0.360.44I OL24 mA5.5−0.360.4424 mAI IN Maximum Input Leakage Current5.5−±0.1±1.0m A V I = V CC, GNDI OLD†Minimum Dynamic Output Current 5.5−−75mA V OLD = 1.65 V MaxI OHD 5.5−−−75mA V OHD = 3.85 V MinI CC Maximum Quiescent Supply Current 5.5− 4.040m A V IN = V CC or GND *All outputs loaded; thresholds on input associated with output under test.†Maximum test duration 2.0 ms, one output loaded at a time.NOTE:I IN and I CC @ 3.0 V are guaranteed to be less than or equal to the respective limit @ 5.5 V V CC.AC CHARACTERISTICS(For Figures and Waveforms − See Section 3 of the ON Semiconductor FACT Data Book, DL138/D)Symbol Parameter V CC*(V)74AC74ACUnitFigureNo.T A = +25°C C L = 50 pFT A = −40°C to+85°C C L = 50 pFMin Typ Max Min Maxt PLH Propagation Delay 3.3 1.59.513.5 1.515.0ns3−5 5.0 1.57.010.0 1.511.0t PHL Propagation Delay 3.3 1.57.511.5 1.513.0ns3−5 5.0 1.5 6.08.5 1.59.5*Voltage Range 3.3 V is 3.3 V ±0.3 V. Voltage Range 5.0 V is 5.0 V ±0.5 V.INPUT CHARACTERISTICS (unless otherwise specified)Symbol Parameter V CC(V)74AC74ACT Test ConditionsMaximum Positive Threshold 3.0 2.2−V t+ 4.5 3.2 2.0V T A = Worst Case5.5 3.9 2.0Minimum Negative Threshold 3.00.5−V t− 4.50.90.8V T A = Worst Case5.5 1.10.83.0 1.2−V h(max)Maximum Hysteresis 4.5 1.4 1.2V T A = Worst Case5.5 1.6 1.23.00.3−V h(min)Minimum Hysteresis 4.50.40.4V T A = Worst Case5.50.50.4DC CHARACTERISTICSSymbol Parameter V CC(V)74ACT74ACTUnit Conditions T A = +25°C T A = −40°C to +85°CTyp Guaranteed LimitsV OH Minimum High Level Output Voltage 4.5 4.49 4.4 4.4V I OUT = −50 m A5.5 5.49 5.4 5.4*V IN = V IL or V IH4.5− 3.86 3.76V I OH−24 mA5.5− 4.86 4.76−24 mAV OL Maximum Low Level Output Voltage 4.50.0010.10.1V I OUT = 50 m A5.50.0010.10.1*V IN = V IL or V IH4.5−0.360.44VI OL 24 mA5.5−0.360.4424 mAI IN Maximum Input Leakage Current5.5−±0.1±1.0m A V I = V CC, GNDD I CCT Additional Max. I CC/Input 5.50.6− 1.5mA V I = V CC−2.1 VI OLD†Minimum Dynamic Output Current 5.5−−75mA V OLD = 1.65 V MaxI OHD 5.5−−−75mA V OHD = 3.85 V MinI CC Maximum Quiescent Supply Current 5.5− 4.040m A V IN = V CC or GND *All outputs loaded; thresholds on input associated with output under test.†Maximum test duration 2.0 ms, one output loaded at a time.AC CHARACTERISTICS(For Figures and Waveforms − See Section 3 of the ON Semiconductor FACT Data Book, DL138/D)Symbol Parameter V CC*(V)74ACT74ACTUnitFigureNo.T A = +25°C C L = 50 pFT A = −40°C to+85°C C L = 50 pFMin Typ Max Min Maxt PLH Propagation Delay 5.0 1.5−11.5 1.012.5ns3−5 t PHL Propagation Delay 5.0 1.5−10.0 1.011.0ns3−5 *Voltage Range 5.0 V is 5.0 V ±0.5 V.CAPACITANCESymbol Parameter Value Typ Unit Test ConditionsC IN Input Capacitance 4.5pF V CC = 5.0 VC PD Power Dissipation Capacitance25pF V CC = 5.0 VORDERING INFORMATIONDevicePackage Shipping †MC74AC14NG PDIP −14(Pb −Free)25 Units / RailMC74ACT14NG PDIP −14(Pb −Free)MC74AC14D SOIC −1455 Units / Rail MC74AC14DG SOIC −14(Pb −Free)MC74AC14DR2G SOIC −14(Pb −Free)2500 / Tape & Reel MC74ACT14DG SOIC −14(Pb −Free)55 Units / RailMC74ACT14DR2SOIC −142500 / Tape & Reel MC74ACT14DR2G SOIC −14(Pb −Free)MC74AC14DTR2TSSOP −14*MC74AC14DTR2G TSSOP −14*MC74ACT14DTR2TSSOP −14*MC74ACT14DTR2G TSSOP −14*MC74AC14MEL SOEIAJ −142000 / Tape & Reel MC74AC14MELG SOEIAJ −14(Pb −Free)MC74ACT14MELGSOEIAJ −14(Pb −Free)†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.*This package is inherently Pb −Free.MARKING DIAGRAMSSOEIAJ −1474AC14ALYWG TSSOP −14SOIC −14AC 14ALYW G G A =Assembly Location WL, L =Wafer Lot YY , Y =YearWW, W =Work Week G or G = Pb −Free Package(Note: Microdot may be in either location)PDIP −14MC74AC14N AWLYYWWG 11411411474ACT14ALYWG ACT 14ALYW G GMC74ACT14N AWLYYWWG 114114114PDIP−14 CASE 646−06 ISSUE PDIM MIN MAX MIN MAXMILLIMETERSINCHESA0.7150.77018.1619.56B0.2400.260 6.10 6.60C0.1450.185 3.69 4.69D0.0150.0210.380.53F0.0400.070 1.02 1.78G0.100 BSC 2.54 BSCH0.0520.095 1.32 2.41J0.0080.0150.200.38K0.1150.135 2.92 3.43LM−−−10 −−−10N0.0150.0390.38 1.01__NOTES:1.DIMENSIONING AND TOLERANCING PER ANSIY14.5M, 1982.2.CONTROLLING DIMENSION: INCH.3.DIMENSION L TO CENTER OF LEADS WHENFORMED PARALLEL.4.DIMENSION B DOES NOT INCLUDE MOLD FLASH.5.ROUNDED CORNERS OPTIONAL.M0.13 (0.005)0.2900.3107.377.87SOIC −14 NB CASE 751A −03ISSUE KNOTES:1.DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.2.CONTROLLING DIMENSION: MILLIMETERS.3.DIMENSION b DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE PROTRUSION SHALL BE 0.13 TOTAL IN EXCESS OF AT MAXIMUM MATERIAL CONDITION.4.DIMENSIONS D AND E DO NOT INCLUDE MOLD PROTRUSIONS.5.MAXIMUM MOLD PROTRUSION 0.15 PERSIDE.DETAIL ADIM MIN MAX MIN MAX INCHESMILLIMETERS D 8.558.750.3370.344E 3.80 4.000.1500.157A 1.35 1.750.0540.068b 0.350.490.0140.019L 0.40 1.250.0160.049e 1.27 BSC 0.050 BSC A30.190.250.0080.010A10.100.250.0040.010M0 7 0 7 H 5.80 6.200.2280.244h 0.250.500.0100.019____14X0.581.27PITCH*For additional information on our Pb −Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.TSSOP −14CASE 948G −01ISSUE BDIM MIN MAX MIN MAX INCHESMILLIMETERS A 4.90 5.100.1930.200B 4.30 4.500.1690.177C −−− 1.20−−−0.047D 0.050.150.0020.006F 0.500.750.0200.030G 0.65 BSC 0.026 BSC H 0.500.600.0200.024J 0.090.200.0040.008J10.090.160.0040.006K 0.190.300.0070.012K10.190.250.0070.010L 6.40 BSC 0.252 BSC M0 8 0 8 NOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSION A DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE.4.DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 (0.010) PER SIDE.5.DIMENSION K DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBARPROTRUSION SHALL BE 0.08 (0.003) TOTAL IN EXCESS OF THE K DIMENSION AT MAXIMUM MATERIAL CONDITION.6.TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY.7.DIMENSION A AND B ARE TO BEDETERMINED AT DATUM PLANE −W −.____14X REF 14X0.360.65PITCHSOLDERING FOOTPRINT**For additional information on our Pb −Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.SOEIAJ −14M SUFFIX CASE 965−01ISSUE BDIM MIN MAX MIN MAX INCHES --- 2.05---0.081MILLIMETERS 0.050.200.0020.0080.350.500.0140.0200.100.200.0040.0089.9010.500.3900.4135.10 5.450.2010.2151.27 BSC 0.050 BSC 7.408.200.2910.3230.500.850.0200.0331.10 1.500.0430.0590 0.700.900.0280.035--- 1.42---0.056A 1H E Q 1L E _10 _0 _10 _NOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSIONS D AND E DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS AND ARE MEASURED AT THE PARTING LINE. MOLD FLASH ORPROTRUSIONS SHALL NOT EXCEED 0.15 (0.006)PER SIDE.4.TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY.5.THE LEAD WIDTH DIMENSION (b) DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 (0.003)TOTAL IN EXCESS OF THE LEAD WIDTHDIMENSION AT MAXIMUM MATERIAL CONDITION.DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACEBETWEEN PROTRUSIONS AND ADJACENT LEAD TO BE 0.46 ( 0.018).DETAIL PA b c D E e L M ZON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

MC74ACT02DG,MC74AC02DG,MC74ACT02DG,MC74AC02DR2G,MC74AC02DTR2G,MC74ACT02DR2G, 规格书,Datasheet 资料

MC74AC02, MC74ACT02 Quad 2−Input NOR GateFeatures•Outputs Source/Sink 24 mA•′ACT02 Has TTL Compatible Inputs•Pb−Free Packages are AvailableGNDVFigure 1. Pinout: 14−Lead Packages Conductors(Top View)MAXIMUM RATINGSRating Symbol Value Unit DC Supply Voltage (Referenced to GND)V CC−0.5 to+7.0VDC Input Voltage (Referenced to GND)V in−0.5 toV CC +0.5VDC Output Voltage (Referenced to GND)V out−0.5 toV CC +0.5V DC Input Current, per Pin I in±20mA DC Output Sink/Source Current, per Pin I out±50mA DC V CC or GND Current per Output Pin I CC±50mAStorage Temperature T stg−65 to+150°CStresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.See detailed ordering and shipping information in the package dimensions section on page 5 of this data sheet.ORDERING INFORMATIONRECOMMENDED OPERATING CONDITIONSSymbol Parameter Min Typ Max UnitV CC Supply Voltage′AC 2.0 5.0 6.0V ′ACT 4.5 5.0 5.5V in, V out DC Input Voltage, Output Voltage (Ref. to GND)0−V CC Vt r, t f Input Rise and Fall Time (Note 1)′AC Devices except Schmitt Inputs V CC @ 3.0 V−150−V CC @ 4.5 V−40−ns/V V CC @ 5.5 V−25−t r, t f Input Rise and Fall Time (Note 2)′ACT Devices except Schmitt Inputs V CC @ 4.5 V−10−ns/V V CC @ 5.5 V−8.0−T J Junction Temperature (PDIP)−−140°C T A Operating Ambient Temperature Range−402585°C I OH Output Current − High−−−24mAI OL Output Current − Low−−24mA1.V in from 30% to 70% V CC; see individual Data Sheets for devices that differ from the typical input rise and fall times.2.V in from 0.8 V to 2.0 V; see individual Data Sheets for devices that differ from the typical input rise and fall times.DC CHARACTERISTICSSymbol Parameter V CC(V)74AC74ACUnit Conditions T A = +25°CT A =−40°C to+85°CTyp Guaranteed LimitsV IH Minimum High LevelInput Voltage 3.0 1.5 2.1 2.1V OUT = 0.1 V4.5 2.25 3.15 3.15V or V CC− 0.1 V5.5 2.75 3.85 3.85V IL Maximum Low LevelInput Voltage 3.0 1.50.90.9V OUT = 0.1 V4.5 2.25 1.35 1.35V or V CC− 0.1 V5.5 2.75 1.65 1.65V OH Minimum High LevelOutput Voltage 3.0 2.99 2.9 2.9I OUT = −50 μA4.5 4.49 4.4 4.4V5.5 5.49 5.4 5.4V*V IN = V IL or V IH3.0− 2.56 2.46−12 mA4.5− 3.86 3.76I OH−24 mA5.5− 4.86 4.76−24 mAV OL Maximum Low LevelOutput Voltage 3.00.0020.10.1I OUT = 50 μA4.50.0010.10.1V5.50.0010.10.1V*V IN = V IL or V IH3.0−0.360.4412 mA4.5−0.360.44I OL24 mA5.5−0.360.4424 mAI IN Maximum InputLeakage Current 5.5−±0.1±1.0μA V I = V CC, GNDI OLD†Minimum DynamicOutput Current 5.5−−75mA V OLD = 1.65 V MaxI OHD 5.5−−−75mA V OHD = 3.85 V Min I CC Maximum QuiescentSupply Current 5.5− 4.040μA V IN = V CC or GND *All outputs loaded; thresholds on input associated with output under test.†Maximum test duration 2.0 ms, one output loaded at a time.NOTE:I IN and I CC @ 3.0 V are guaranteed to be less than or equal to the respective limit @ 5.5 V V CC.Symbol Parameter V CC*(V)UnitFig.No.T A = +25°CC L = 50 pFT A = −40°Cto +85°CC L = 50 pFMin Typ Max Min Maxt PLH Propagation Delay 3.3 1.5 5.07.5 1.08.0ns3−5 5.0 1.5 4.0 6.0 1.0 6.5t PHL Propagation Delay 3.3 1.5 5.07.5 1.08.0ns3−5 5.0 1.5 4.5 6.5 1.07.0*Voltage Range 3.3 V is 3.3 V ±0.3 V. Voltage Range 5.0 V is 5.0 V ±0.5 V.DC CHARACTERISTICSSymbol Parameter V CC(V)74ACT74ACTUnit Conditions T A = +25°CT A =−40°C to+85°CTyp Guaranteed LimitsV IH Minimum High LevelInput Voltage 4.5 1.5 2.0 2.0VV OUT = 0.1 V 5.5 1.5 2.0 2.0or V CC− 0.1 VV IL Maximum Low LevelInput Voltage 4.5 1.50.80.8VV OUT = 0.1 V 5.5 1.50.80.8or V CC− 0.1 VV OH Minimum High LevelOutput Voltage 4.5 4.49 4.4 4.4VI OUT = −50 μA5.5 5.49 5.4 5.4*V IN = V IL or V IH4.5− 3.86 3.76VI OH−24 mA 5.5− 4.86 4.76−24 mAV OL Maximum Low LevelOutput Voltage 4.50.0010.10.1VI OUT = 50 μA5.50.0010.10.1*V IN = V IL or V IH4.5−0.360.44VI OL24 mA 5.5−0.360.4424 mAI IN Maximum InputLeakage Current 5.5−±0.1±1.0μA V I = V CC, GND ΔI CCT Additional Max. I CC/Input 5.50.6− 1.5mA V I = V CC−2.1 VI OLD†Minimum DynamicOutput Current 5.5−−75mA V OLD = 1.65 V MaxI OHD 5.5−−−75mA V OHD = 3.85 V Min I CC Maximum QuiescentSupply Current 5.5− 4.040μA V IN = V CC or GND *All outputs loaded; thresholds on input associated with output under test.†Maximum test duration 2.0 ms, one output loaded at a time.Symbol Parameter V CC*(V)UnitFig.No.T A = +25°CC L = 50 pFT A = −40°Cto +85°CC L = 50 pFMin Typ Max Min Maxt PLH Propagation Delay 5.0 1.5−8.5 1.09.0ns3−6 t PHL Propagation Delay 5.0 1.5−9.5 1.010ns3−6 *Voltage Range 5.0 V is 5.0 V ±0.5 V.CAPACITANCESymbol Parameter ValueTyp Unit Test ConditionsC IN Input Capacitance 4.5pF V CC = 5.0 V C PD Power Dissipation Capacitance30pF V CC = 5.0 VDEVICE ORDERING INFORMATIONDevicePackage Shipping †MC74AC02N PDIP −1425 Units/RailMC74AC02NG PDIP −14(Pb −Free)MC74ACT02N PDIP −14MC74ACT02NG PDIP −14(Pb −Free)MC74AC02D SOIC −1455 Units/Rail MC74AC02DG SOIC −14(Pb −Free)MC74AC02DR2SOIC −142500/Tape & Reel MC74AC02DR2G SOIC −14(Pb −Free)MC74ACT02D SOIC −1455 Units/Rail MC74ACT02DG SOIC −14(Pb −Free)MC74ACT02DR2SOIC −142500/Tape & Reel MC74ACT02DR2G SOIC −14(Pb −Free)MC74AC02DT TSSOP −14*96 Units/Rail MC74AC02DTR2TSSOP −14*2500/Tape & Reel MC74AC02DTR2G TSSOP −14*MC74ACT02DT TSSOP −14*96 Units/Rail MC74ACT02DTR2TSSOP −14*2500/Tape & Reel MC74ACT02DTR2G TSSOP −14*MC74AC02M SOEIAJ −1450 Units/Rail MC74AC02MEL SOEIAJ −142000/Tape & ReelMC74AC02MELG SOEIAJ −14(Pb −Free)MC74ACT02MEL SOEIAJ −14MC74ACT02MELGSOEIAJ −14(Pb −Free)†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.*This package is inherently Pb −Free.MARKING DIAGRAMSA = Assembly Location WL, L = Wafer Lot YY, Y = YearWW, W = Work WeekG or G = Pb −Free PackagePDIP −14TSSOP −14MC74AC02N AWLYYWWG AC 02ALYW G G MC74ACT02N AWLYYWWG 74AC02ALYWG SOEIAJ −1474ACT02ALYWG 111114141141414ACT 02ALYW G G 114(Note: Microdot may be in either location)PACKAGE DIMENSIONSPDIP−14CASE 646−06ISSUE PSOIC −14CASE 751A −03ISSUE HNOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.4.MAXIMUM MOLD PROTRUSION 0.15 (0.006)PER SIDE.5.DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127(0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.DIM MIN MAX MIN MAX INCHESMILLIMETERS A 8.558.750.3370.344B 3.80 4.000.1500.157C 1.35 1.750.0540.068D 0.350.490.0140.019F 0.40 1.250.0160.049G 1.27 BSC 0.050 BSC J 0.190.250.0080.009K 0.100.250.0040.009M 0 7 0 7 P 5.80 6.200.2280.244R0.250.500.0100.019____DIMENSIONS: MILLIMETERS*For additional information on our Pb −Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.TSSOP −14CASE 948G −01ISSUE BDIM MIN MAX MIN MAX INCHES MILLIMETERS A 4.90 5.100.1930.200B 4.30 4.500.1690.177C −−− 1.20−−−0.047D 0.050.150.0020.006F 0.500.750.0200.030G 0.65 BSC 0.026 BSC H 0.500.600.0200.024J 0.090.200.0040.008J10.090.160.0040.006K 0.190.300.0070.012K10.190.250.0070.010L 6.40 BSC 0.252 BSC M 0 8 0 8 NOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSION A DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE.4.DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 (0.010) PER SIDE.5.DIMENSION K DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08(0.003) TOTAL IN EXCESS OF THE K DIMENSION AT MAXIMUM MATERIAL CONDITION.6.TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY .7.DIMENSION A AND B ARE TO BE DETERMINED AT DATUM PLANE −W −.____14X REF K14X0.360.65PITCHSOLDERING FOOTPRINT**For additional information on our Pb −Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.SOEIAJ −14CASE 965−01ISSUE ANOTES:1.DIMENSIONING AND TOLERANCING PER ANSIY14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

74系列各个芯片详细介绍

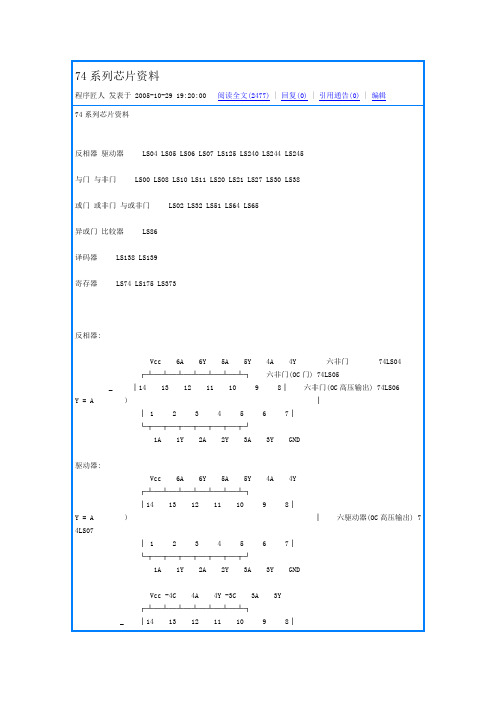

74系列芯片资料程序匠人发表于 2005-10-29 19:20:00 阅读全文(2477) | 回复(0) | 引用通告(0) | 编辑74系列芯片资料反相器驱动器 LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245与门与非门 LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38或门或非门与或非门 LS02 LS32 LS51 LS64 LS65异或门比较器 LS86译码器 LS138 LS139寄存器 LS74 LS175 LS373反相器:Vcc 6A 6Y 5A 5Y 4A 4Y 六非门 74LS04┌┴─┴─┴─┴─┴─┴─┴┐六非门(OC门) 74LS05_ │14 13 12 11 10 9 8│六非门(OC高压输出) 74LS06Y = A )││ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1Y 2A 2Y 3A 3Y GND驱动器:Vcc 6A 6Y 5A 5Y 4A 4Y┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│Y = A )│六驱动器(OC高压输出) 74LS07│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1Y 2A 2Y 3A 3Y GNDVcc -4C 4A 4Y -3C 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐_ │14 13 12 11 10 9 8│Y =A+C )│四总线三态门 74LS125│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘-1C 1A 1Y -2C 2A 2Y GNDVcc -G B1 B2 B3 B4 B8 B6 B7 B8┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐ 8位总线驱动器 74LS245 │20 19 18 17 16 15 14 13 12 11│)│ DIR=1 A=>B│ 1 2 3 4 5 6 7 8 9 10│ DIR=0 B=>A└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘DIR A1 A2 A3 A4 A5 A6 A7 A8 GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器正逻辑与门,与非门:Vcc 4B 4A 4Y 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│Y = AB )│ 2输入四正与门 74LS08 │ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 4B 4A 4Y 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐__ │14 13 12 11 10 9 8│Y = AB )│ 2输入四正与非门 74LS00 │ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 1C 1Y 3C 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐___ │14 13 12 11 10 9 8│Y = ABC )│ 3输入三正与非门 74LS10 │ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 2A 2B 2C 2Y GNDVcc H G Y┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│)│ 8输入与非门 74LS30│ 1 2 3 4 5 6 7│ ________└┬─┬─┬─┬─┬─┬─┬┘ Y = ABCDEFGHA B C D E F GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器正逻辑或门,或非门:Vcc 4B 4A 4Y 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐ 2输入四或门 74LS32│14 13 12 11 10 9 8│)│ Y = A+B│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 4Y 4B 4A 3Y 3B 3A┌┴─┴─┴─┴─┴─┴─┴┐ 2输入四或非门 74LS02│14 13 12 11 10 9 8│ ___)│ Y = A+B│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1Y 1A 1B 2Y 2A 2B GNDVcc 2Y 2B 2A 2D 2E 1F┌┴─┴─┴─┴─┴─┴─┴┐双与或非门 74S51│14 13 12 11 10 9 8│ _____)│ 2Y = AB+DE│ 1 2 3 4 5 6 7│ _______└┬─┬─┬─┬─┬─┬─┬┘ 1Y = ABC+DEF1Y 1A 1B 1C 1D 1E GNDVcc D C B K J Y┌┴─┴─┴─┴─┴─┴─┴┐ 4-2-3-2与或非门 74S64 74S65(OC门) │14 13 12 11 10 9 8│ ______________)│ Y = ABCD+EF+GHI+JK│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘A E F G H I GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器2输入四异或门 74LS86Vcc 4B 4A 4Y 3Y 3B 3A┌┴─┴─┴─┴─┴─┴─┴┐│14 13 12 11 10 9 8│)│ _ _│ 1 2 3 4 5 6 7│ Y=AB+AB└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2Y 2A 2B GND8*2输入比较器 74LS688_Vcc Y B8 A8 B7 A7 B6 A6 B5 A5┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐ 8*2输入比较器 74LS688│20 19 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘CE A1 B1 A2 B2 A3 B3 A4 B4 GND_Y=A1⊙B1+A2⊙B2+A3⊙B3+A4⊙B4+A5⊙B5+A6⊙B6+A7⊙B7+A8⊙B8页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器3-8译码器 74LS138Vcc -Y0 -Y1 -Y2 -Y3 -Y4 -Y5 -Y6 __ _ _ _ __ _ _ __ _ _ __ _ ┌┴─┴─┴─┴─┴─┴─┴─┴┐ Y0=A B C Y1=A B B Y2=A B C Y3=A B C │16 15 14 13 12 11 10 9 │)│ __ _ _ __ _ __ _ __│ 1 2 3 4 5 6 7 8│ Y4=A B C Y5=A B C Y6=A B C Y7=A B C └┬─┬─┬─┬─┬─┬─┬─┬┘A B C -CS0 -CS1 CS2 -Y7 GND双2-4译码器 74LS139Vcc -2G 2A 2B -Y0 -Y1 -Y2 -Y3 __ __ __ __ __ __ __ __┌┴─┴─┴─┴─┴─┴─┴─┴┐ Y0=2A 2B Y1=2A 2B Y2=2A 2B Y3=2A 2B │16 15 14 13 12 11 10 9 │)│ __ __ __ __ __ __ __ __│ 1 2 3 4 5 6 7 8│ Y0=1A 1B Y1=1A 1B Y2=1A 1B Y3=1A 1B └┬─┬─┬─┬─┬─┬─┬─┬┘-1G 1A 1B -Y0 -Y1 -Y2 -Y3 GND8*2输入比较器 74LS688_Vcc Y B8 A8 B7 A7 B6 A6 B5 A5┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐ 8*2输入比较器 74LS688│20 19 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘CE A1 B1 A2 B2 A3 B3 A4 B4 GND_Y=A1⊙B1+A2⊙B2+A3⊙B3+A4⊙B4+A5⊙B5+A6⊙B6+A7⊙B7+A8⊙B8寄存器:Vcc 2CR 2D 2Ck 2St 2Q -2Q┌┴─┴─┴─┴─┴─┴─┴┐双D触发器 74LS74│14 13 12 11 10 9 8 │)││ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1Cr 1D 1Ck 1St 1Q -1Q GNDVcc 8Q 8D 7D 7Q 6Q 6D 5D 5Q ALE┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐ 8位锁存器 74LS373│20 19 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘-OE 1Q 1D 2D 2Q 3Q 3D 4D 4Q GND型号器件名称厂牌[数据表]SN7400四2输入端与非门 TI[DATA]SN7401四2输入端与非门(OC) SN7402四2输入端或非门 TI[DATA]SN7403四2输入端与非门(OC)TI[DATA]SN7404六反相器 TI[DATA]SN7405六反相器(OC)TI[DATA]SN7406六高压输出反相器 (OC,30V)TI[DATA]SN7407六高压输出缓冲,驱动器(OC,30V)TI[DATA]SN7408四2输入端与门 TI[DATA]SN7409四2输入端与门(OC)TI[DATA]SN7410三3输入端与非门 TI[DATA]SN7412三3输入端与非门(OC)TI[DATA]SN7413双4输入端与非门 TI[DATA]SN7414六反相器TI[DATA]SN7416六高压输出反相缓冲/驱动器 I[DATA]SN7417六高压输出缓冲/驱动器(OC,15V)TI[DATA]SN7420双4输入端与非门 TI[DATA]SN7422双4输入端与非门(OC)TI[DATA]SN7423可扩展双4输入端或非门 TI[DATA]SN7425双4输入端或非门TI[DATA]SN7426四2输入端高压输出与非缓冲器 [DATA]SN7427三3输入端或非门TI[DATA]SN7428四2输入端或非缓冲器 I[DATA]SN74308输入端与非门TI[DATA]SN7432四2输入端或门。

MM74HC20中文资料

2 A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness

Features

Y Y Y Y Y

Typical propagation delay 8 ns Wide power supply range 2 – 6V Low quiescent current 20 mA maximum (74HC Series) Low input current 1 mA maximum Fanout of 10 LS-TTL loads

TA e 25 C Typ

Units

Guaranteed Limits ns ns ns ns ns ns pF pF

tPHL tPLH

Maximum Propagation Delay Maximum Output Rise and Fall Time Power Dissipation Capacitance Note Maximum Input Capacitance

Max VCC

Units V V

a a

MC74ACT08N中文资料

1. Vin from 30% to 70% VCC; see individual Data Sheets for devices that differ from the typical input rise and fall times. 2. Vin from 0.8 V to 2.0 V; see individual Data Sheets for devices that differ from the typical input rise and fall times.

* Maximum Ratings are those values beyond which damage to the device may occur. Functional operation should be restricted to the Recommended Operating Conditions.

FACT DATA 5-3

元器件交易网

MC74AC08 MC74ACT08

AC CHARACTERISTICS (For Figures and Waveforms — See Section 3)

74ACT Symbol Parameter VCC* (V) Min tPLH tPHL Propagation Delay Propagation Delay 5.0 5.0 1.0 1.0 TA = +25°C CL = 50 pF Typ Max 9.0 9.0 74ACT TA = –40°C to +85°C CL = 50 pF Min 1.0 1.0 Max 10.0 10.0 ns ns 3-5 3-5 Unit Fig. No.

VIL

Maximum Low Level Input Voltage

MC74ACT20D中文资料

FACT DATA 5-2

元器件交易网

MC74AC20 MC74ACT20

AC CHARACTERISTICS

74AC Symbol Parameter VCC* (V) Min tPLH tPHL Propagation Delay Propagation Delay 3.3 5.0 3.3 5.0 2.0 1.5 1.5 1.5 TA = +25°C CL = 50 pF Typ 6.0 5.0 5.0 4.0 Max 8.5 7.0 7.0 6.0 74AC TA = –40°C to +85°C CL = 50 pF Min 1.5 1.0 1.0 1.0 Max 10.0 8.0 9.0 7.0 ns ns Unit

1. Vin from 30% to 70% VCC; see individual Data Sheets for devices that differ from the typical input rise and fall times. 2. Vin from 0.8 V to 2.0 V; see individual Data Sheets for devices that differ from the typical input rise and fall times.

元器件交易网

MC74AC20 MC74ACT20 Dual 4 Input NAND Gate

• Outputs Source/Sink 24 mA • ′ACT20 Has TTL Compatible Inputs Pinout: 14-Lead Packages (Top View)

Guaranteed Limits 2.0 2.0 0.8 0.8 4.4 5.4 3.86 4.86 0.1 0.1 0.36 0.36 ±0.1 2.0 2.0 0.8 0.8 4.4 5.4 3.76 4.76 0.1 0.1 0.44 0.44 ±1.0 1.5 75 –75 40 V V V VOUT = 0.1 V or VCC – 0.1 V VOUT = 0.1 V or VCC – 0.1 V IOUT = – 50 µA *VIN = VIL or VIH – 24 mA IOH – 24 mA IOUT = 50 µA *VIN = VIL or VIH 24 mA IOH 24 mA VI = VCC, GND VI = VCC – 2.1 V VOLD = 1.65 V Max VOHD = 3.85 V Min VIN = VCC or GND

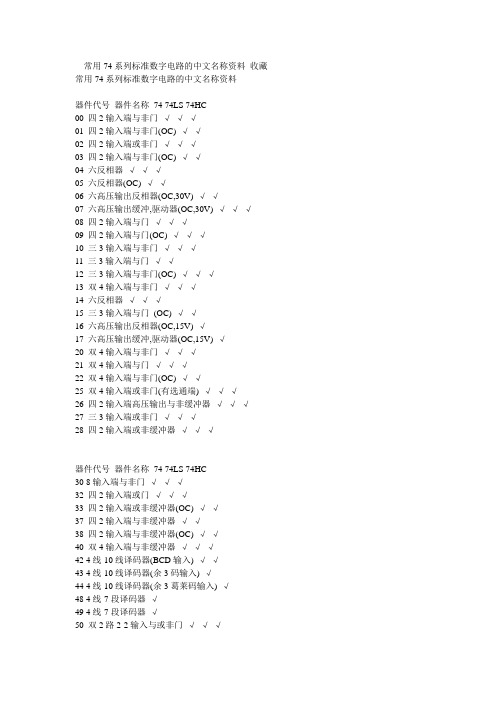

74系列芯片功能大全

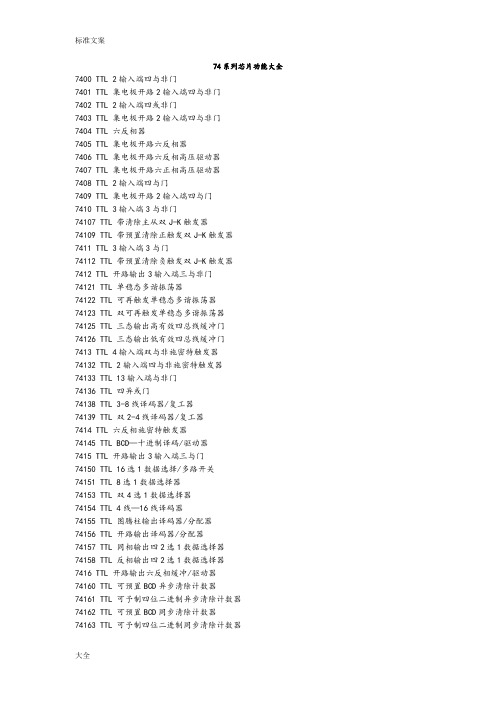

74系列芯片功能大全7400 TTL 2输入端四与非门7401 TTL 集电极开路2输入端四与非门7402 TTL 2输入端四或非门7403 TTL 集电极开路2输入端四与非门7404 TTL 六反相器7405 TTL 集电极开路六反相器7406 TTL 集电极开路六反相高压驱动器7407 TTL 集电极开路六正相高压驱动器7408 TTL 2输入端四与门7409 TTL 集电极开路2输入端四与门7410 TTL 3输入端3与非门74107 TTL 带清除主从双J-K触发器74109 TTL 带预置清除正触发双J-K触发器7411 TTL 3输入端3与门74112 TTL 带预置清除负触发双J-K触发器7412 TTL 开路输出3输入端三与非门74121 TTL 单稳态多谐振荡器74122 TTL 可再触发单稳态多谐振荡器74123 TTL 双可再触发单稳态多谐振荡器74125 TTL 三态输出高有效四总线缓冲门74126 TTL 三态输出低有效四总线缓冲门7413 TTL 4输入端双与非施密特触发器74132 TTL 2输入端四与非施密特触发器74133 TTL 13输入端与非门74136 TTL 四异或门74138 TTL 3-8线译码器/复工器74139 TTL 双2-4线译码器/复工器7414 TTL 六反相施密特触发器74145 TTL BCD—十进制译码/驱动器7415 TTL 开路输出3输入端三与门74150 TTL 16选1数据选择/多路开关74151 TTL 8选1数据选择器74153 TTL 双4选1数据选择器74154 TTL 4线—16线译码器74155 TTL 图腾柱输出译码器/分配器74156 TTL 开路输出译码器/分配器74157 TTL 同相输出四2选1数据选择器74158 TTL 反相输出四2选1数据选择器7416 TTL 开路输出六反相缓冲/驱动器74160 TTL 可预置BCD异步清除计数器74161 TTL 可予制四位二进制异步清除计数器74162 TTL 可预置BCD同步清除计数器74163 TTL 可予制四位二进制同步清除计数器74164 TTL 八位串行入/并行输出移位寄存器74165 TTL 八位并行入/串行输出移位寄存器74166 TTL 八位并入/串出移位寄存器74169 TTL 二进制四位加/减同步计数器7417 TTL 开路输出六同相缓冲/驱动器74170 TTL 开路输出4×4寄存器堆74173 TTL 三态输出四位D型寄存器74174 TTL 带公共时钟和复位六D触发器74175 TTL 带公共时钟和复位四D触发器74180 TTL 9位奇数/偶数发生器/校验器74181 TTL 算术逻辑单元/函数发生器74185 TTL 二进制—BCD代码转换器74190 TTL BCD同步加/减计数器74191 TTL 二进制同步可逆计数器74192 TTL 可预置BCD双时钟可逆计数器74193 TTL 可预置四位二进制双时钟可逆计数器74194 TTL 四位双向通用移位寄存器74195 TTL 四位并行通道移位寄存器74196 TTL 十进制/二-十进制可预置计数锁存器74197 TTL 二进制可预置锁存器/计数器7420 TTL 4输入端双与非门7421 TTL 4输入端双与门7422 TTL 开路输出4输入端双与非门74221 TTL 双/单稳态多谐振荡器74240 TTL 八反相三态缓冲器/线驱动器74241 TTL 八同相三态缓冲器/线驱动器74243 TTL 四同相三态总线收发器74244 TTL 八同相三态缓冲器/线驱动器74245 TTL 八同相三态总线收发器74247 TTL BCD—7段15V输出译码/驱动器74248 TTL BCD—7段译码/升压输出驱动器74249 TTL BCD—7段译码/开路输出驱动器74251 TTL 三态输出8选1数据选择器/复工器74253 TTL 三态输出双4选1数据选择器/复工器74256 TTL 双四位可寻址锁存器74257 TTL 三态原码四2选1数据选择器/复工器74258 TTL 三态反码四2选1数据选择器/复工器74259 TTL 八位可寻址锁存器/3-8线译码器7426 TTL 2输入端高压接口四与非门74260 TTL 5输入端双或非门74266 TTL 2输入端四异或非门7427 TTL 3输入端三或非门74273 TTL 带公共时钟复位八D触发器74279 TTL 四图腾柱输出S-R锁存器7428 TTL 2输入端四或非门缓冲器74283 TTL 4位二进制全加器74290 TTL 二/五分频十进制计数器74293 TTL 二/八分频四位二进制计数器74295 TTL 四位双向通用移位寄存器74298 TTL 四2输入多路带存贮开关74299 TTL 三态输出八位通用移位寄存器7430 TTL 8输入端与非门7432 TTL 2输入端四或门74322 TTL 带符号扩展端八位移位寄存器74323 TTL 三态输出八位双向移位/存贮寄存器7433 TTL 开路输出2输入端四或非缓冲器74347 TTL BCD—7段译码器/驱动器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74373 TTL 三态同相八D锁存器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74373 TTL 三态同相八D锁存器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器74447 TTL BCD—7段译码器/驱动器7445 TTL BCD—十进制代码转换/驱动器74450 TTL 16:1多路转接复用器多工器74451 TTL 双8:1多路转接复用器多工器74453 TTL 四4:1多路转接复用器多工器7446 TTL BCD—7段低有效译码/驱动器74460 TTL 十位比较器74461 TTL 八进制计数器74465 TTL 三态同相2与使能端八总线缓冲器74466 TTL 三态反相2与使能八总线缓冲器74467 TTL 三态同相2使能端八总线缓冲器74468 TTL 三态反相2使能端八总线缓冲器74469 TTL 八位双向计数器7447 TTL BCD—7段高有效译码/驱动器7448 TTL BCD—7段译码器/内部上拉输出驱动74490 TTL 双十进制计数器74491 TTL 十位计数器74498 TTL 八进制移位寄存器7450 TTL 2-3/2-2输入端双与或非门74502 TTL 八位逐次逼近寄存器74503 TTL 八位逐次逼近寄存器7451 TTL 2-3/2-2输入端双与或非门74533 TTL 三态反相八D锁存器74534 TTL 三态反相八D锁存器7454 TTL 四路输入与或非门74540 TTL 八位三态反相输出总线缓冲器7455 TTL 4输入端二路输入与或非门74563 TTL 八位三态反相输出触发器74564 TTL 八位三态反相输出D触发器74573 TTL 八位三态输出触发器74574 TTL 八位三态输出D触发器74645 TTL 三态输出八同相总线传送接收器74670 TTL 三态输出4×4寄存器堆7473 TTL 带清除负触发双J-K触发器7474 TTL 带置位复位正触发双D触发器7476 TTL 带预置清除双J-K触发器7483 TTL 四位二进制快速进位全加器7485 TTL 四位数字比较器7486 TTL 2输入端四异或门7490 TTL 可二/五分频十进制计数器7493 TTL 可二/八分频二进制计数器7495 TTL 四位并行输入\输出移位寄存器7497 TTL 6位同步二进制乘法器常用74系列标准数字电路的中文名称资料器件代号器件名称 74 74LS 74HC00 四2输入端与非门√√√01 四2输入端与非门(OC) √√02 四2输入端或非门√√√03 四2输入端与非门(OC) √√04 六反相器√√√05 六反相器(OC) √√06 六高压输出反相器(OC,30V) √√07 六高压输出缓冲,驱动器(OC,30V) √√√08 四2输入端与门√√√09 四2输入端与门(OC) √√√10 三3输入端与非门√√√11 三3输入端与门√√12 三3输入端与非门(OC) √√√13 双4输入端与非门√√√14 六反相器√√√15 三3输入端与门 (OC) √√16 六高压输出反相器(OC,15V) √17 六高压输出缓冲,驱动器(OC,15V) √20 双4输入端与非门√√√21 双4输入端与门√√√22 双4输入端与非门(OC) √√25 双4输入端或非门(有选通端) √√√26 四2输入端高压输出与非缓冲器√√√27 三3输入端或非门√√√28 四2输入端或非缓冲器√√√30 8输入端与非门√√√32 四2输入端或门√√√33 四2输入端或非缓冲器(OC) √√37 四2输入端与非缓冲器√√38 四2输入端与非缓冲器(OC) √√40 双4输入端与非缓冲器√√√42 4线-10线译码器(BCD输入) √√43 4线-10线译码器(余3码输入) √44 4线-10线译码器(余3葛莱码输入) √48 4线-7段译码器√49 4线-7段译码器√50 双2路2-2输入与或非门√√√51 2路3-3输入,2路2-2输入与或非门√√√52 4路2-3-2-2输入与或门√53 4路2-2-2-2输入与或非门√54 4路2-3-3-2输入与或非门√√55 2路4-4输入与或非门√60 双4输入与扩展器√√61 三3输入与扩展器√62 4路2-3-3-2输入与或扩展器√64 4路4-2-3-2输入与或非门√65 4路4-2-3-2输入与或非门(OC) √70 与门输入J-K触发器√71 与或门输入J-K触发器√72 与门输入J-K触发器√74 双上升沿D型触发器√√78 双D型触发器√√85 四位数值比较器√86 四2输入端异或门√√√87 4位二进制原码/反码√95 4位移位寄存器√101 与或门输入J-K触发器√102 与门输入J-K触发器√107 双主-从J-K触发器√108 双主-从J-K触发器√109 双主-从J-K触发器√110 与门输入J-K触发器√111 双主-从J-K触发器√√112 双下降沿J-K触发器√113 双下降沿J-K触发器√114 双下降沿J-K触发器√116 双4位锁存器√120 双脉冲同步驱动器√121 单稳态触发器√√√122 可重触发单稳态触发器√√√123 可重触发双稳态触发器√√√125 四总线缓冲器√√√126 四总线缓冲器√√√128 四2输入端或非线驱动器√√√132 四2输入端与非门√√√。

MC74AC4040中文资料

FUNCTION TABLE

Clock Reset L L X H Output State No Change Advance to next state All Outputs are low CLOCK

LOGIC DIAGRAM

9 7 6 5 10 3 2 4 13 12 14 15 1 11 Q1 Q2 Q3 Q4 Q5 Q6 Q7 Q8 Q9 Q10 Q11 Q12

VIL

Maximum Low Level Input Voltage

V

VOH

Minimum High Level Output Voltage

V

V

µA mA mA

* All outputs loaded; thresholds on input associated with output under test. ** Maximum test duration 2.0 ms, one output loaded at a time.

FACT DATA 5-2

元器件交易网

MC74AC4040

DC CHARACTERISTICS (unless otherwise specified)

Symbol ICC Parameter Maximum Quiescent Supply Voltage Value 80 Unit µA Vin = VCC or GND VCC = 5.5 V, TA = Worst Case Vin = VCC or GND VCC = 5.5 V, TA = 25°C

VCC 16 Q11 15 Q10 14 Q8 13 Q9 12 RESET CLK 11 10 Q1 9

12-STAGE BINARY RIPPLE COUNTER

74AC20PC中文资料

Note 1: Absolute maximum ratings are those values beyond which damage to the device may occur. The databook specifications should be met, without exception, to ensure that the system design is reliable over its power supply, temperature, and output/input loading variables. Fairchild does not recommend operation of FACT circuits outside databook specifications.

Device also available in Tape and Reel. Specify by appending suffix letter “X” to the ordering code.

Logic Symbol

IEEE/IEC

Connection Diagram

Pin Descriptions

2

元器件交易网

74AC20

AC Electrical Characteristics

VCC Symbol tPLH tPHL Parameter Propagation Delay Propagation Delay (V) (Note 5) 3.3 5.0 3.3 5.0

Note 5: Voltage Range 3.3 is 3.3V ± 0.3V Voltage Range 5.0 is 5.0V ± 0.5V

TA = +25°C CL = 50 pF Min 2.0 1.5 1.5 1.5 Typ 6.0 5.0 5.0 4.0 Max 8.5 7.0 7.0 6.0

常用74系列标准数字电路的中文名称资料

常用74系列标准数字电路的中文名称资料收藏常用74系列标准数字电路的中文名称资料器件代号器件名称74 74LS 74HC00 四2输入端与非门√√√01 四2输入端与非门(OC) √√02 四2输入端或非门√√√03 四2输入端与非门(OC) √√04 六反相器√√√05 六反相器(OC) √√06 六高压输出反相器(OC,30V) √√07 六高压输出缓冲,驱动器(OC,30V) √√√08 四2输入端与门√√√09 四2输入端与门(OC) √√√10 三3输入端与非门√√√11 三3输入端与门√√12 三3输入端与非门(OC) √√√13 双4输入端与非门√√√14 六反相器√√√15 三3输入端与门(OC) √√16 六高压输出反相器(OC,15V) √17 六高压输出缓冲,驱动器(OC,15V) √20 双4输入端与非门√√√21 双4输入端与门√√√22 双4输入端与非门(OC) √√25 双4输入端或非门(有选通端) √√√26 四2输入端高压输出与非缓冲器√√√27 三3输入端或非门√√√28 四2输入端或非缓冲器√√√器件代号器件名称74 74LS 74HC30 8输入端与非门√√√32 四2输入端或门√√√33 四2输入端或非缓冲器(OC) √√37 四2输入端与非缓冲器√√38 四2输入端与非缓冲器(OC) √√40 双4输入端与非缓冲器√√√42 4线-10线译码器(BCD输入) √√43 4线-10线译码器(余3码输入) √44 4线-10线译码器(余3葛莱码输入) √48 4线-7段译码器√49 4线-7段译码器√50 双2路2-2输入与或非门√√√51 2路3-3输入,2路2-2输入与或非门√√√52 4路2-3-2-2输入与或门√53 4路2-2-2-2输入与或非门√54 4路2-3-3-2输入与或非门√√55 2路4-4输入与或非门√60 双4输入与扩展器√√61 三3输入与扩展器√62 4路2-3-3-2输入与或扩展器√64 4路4-2-3-2输入与或非门√65 4路4-2-3-2输入与或非门(OC) √70 与门输入J-K触发器√71 与或门输入J-K触发器√72 与门输入J-K触发器√器件代号器件名称74 74LS 74HC74 双上升沿D型触发器√√78 双D型触发器√√85 四位数值比较器√86 四2输入端异或门√√√87 4位二进制原码/反码√95 4位移位寄存器√101 与或门输入J-K触发器√102 与门输入J-K触发器√107 双主-从J-K触发器√108 双主-从J-K触发器√74F74是高速的TTL芯片和74HC一样就是速度高109 双主-从J-K触发器√110 与门输入J-K触发器√111 双主-从J-K触发器√√112 双下降沿J-K触发器√113 双下降沿J-K触发器√114 双下降沿J-K触发器√116 双4位锁存器√120 双脉冲同步驱动器√121 单稳态触发器√√√122 可重触发单稳态触发器√√√123 可重触发双稳态触发器√√√125 四总线缓冲器√√√126 四总线缓冲器√√√128 四2输入端或非线驱动器√√√132 四2输入端与非门√√√d触发器芯片有:74HC74 74LS90 双D触发器74LS7474LS364八D触发器(三态)7474、74 H74、74F74、74ALS74、74L74、74LS74A、74S74、74HC73、74C74双D型正沿触发器(带预置和清除端)74174、74LS174、74F174、74ALS174、74S174、74HC174、74C174六D型触发器(带清除端)74175、74LS175、74F175、74ALS175、74S175、74HC175、74C175 四D型触发器(带清除端)74273、74LS273、74S273、74F273、74ALS273、74HC273 八D型触发器(带清除端)74LS364八D触发器(三态)74LS377、74F377、74S3777八D 触发器74LS378、74F378、74S378、74HC378六D 触发器74LS379、74F379、74S379、74HC379八D 触发器。

MC74ACT32D中文资料

FACT DATA 5-4

元器件交易网

MC74AC32 MC74ACT32

OUTLINE DIMENSIONS

N SUFFIX PLASTIC DIP PACKAGE CASE 646–06 ISSUE L

* Voltage Range 5.0 V is 5.0 V ±0.5 V.

CAPACITANCE

Symbol CIN CPD Input Capacitance Power Dissipation Capacitance Parameter Value Typ 4.5 20 Unit pF pF Test Conditions VCC = 5.0 V VCC = 5.0 V

Guaranteed Limits 2.0 2.0 0.8 0.8 4.4 5.4 3.86 4.86 0.1 0.1 0.36 0.36 ±0.1 2.0 2.0 0.8 0.8 4.4 5.4 3.76 4.76 0.1 0.1 0.44 0.44 ±1.0 1.5 75 –75 40 V V V VOUT = 0.1 V or VCC – 0.1 V VOUT = 0.1 V or VCC – 0.1 V IOUT = –50 µA *VIN = VIL or VIH –24 mA IOH –24 mA IOUT = 50 µA *VIN = VIL or VIH 24 mA IOL 24 mA VI = VCC, GND VI = VCC – 2.1 V VOLD = 1.65 V Max VOHD = 3.85 V Min VIN = VCC or GND

FACT DATA 5-3

元器件交易网

MC74AC32 MC74ACT32

AC CHARACTERISTICS (For Figures and Waveforms — See Section 3)

74系列各个芯片详细介绍

74系列芯片资料程序匠人发表于 2005-10-29 19:20:00 阅读全文(2477) | 回复(0) | 引用通告(0) | 编辑74系列芯片资料反相器驱动器 LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245与门与非门 LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38或门或非门与或非门 LS02 LS32 LS51 LS64 LS65异或门比较器 LS86译码器 LS138 LS139寄存器 LS74 LS175 LS373反相器:Vcc 6A 6Y 5A 5Y 4A 4Y 六非门74LS04 ┌┴─┴─┴─┴─┴─┴─┴┐六非门(OC门) 74LS05_ │1413 12 11 10 9 8│六非门(OC高压输出) 74LS06Y = A )││ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1Y 2A 2Y 3A 3Y GND驱动器:Vcc 6A 6Y 5A 5Y 4A 4Y┌┴─┴─┴─┴─┴─┴─┴┐│1413 12 11 10 9 8│Y = A )│六驱动器(OC高压输出) 7 4LS07│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1Y 2A 2Y 3A 3Y GNDVcc -4C 4A 4Y -3C 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐_ │1413 12 11 10 9 8│Y =A+C )│四总线三态门 74LS125 │ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘-1C 1A 1Y -2C 2A 2Y GNDVcc -G B1 B2 B3 B4 B8 B6 B7 B8┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐8位总线驱动器 74LS245│2019 18 17 16 15 14 13 12 11│)│DIR =1 A=>B│ 1 2 3 4 5 6 7 8 9 10│DIR=0 B=>A└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘DIR A1 A2 A3 A4 A5 A6 A7 A8 GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器正逻辑与门,与非门:Vcc 4B 4A 4Y 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐│1413 12 11 10 9 8│Y = AB )│2输入四正与门 74LS08 │ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 4B 4A 4Y 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐__ │1413 12 11 10 9 8│Y = AB )│2输入四正与非门 74LS 00│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 1C 1Y 3C 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐___ │1413 12 11 10 9 8│Y = ABC )│3输入三正与非门 74LS 10│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 2A 2B 2C 2Y GNDVcc H G Y┌┴─┴─┴─┴─┴─┴─┴┐│1413 12 11 10 9 8│)│8输入与非门 74LS30│ 1 2 3 4 5 6 7│________└┬─┬─┬─┬─┬─┬─┬┘Y = ABCDEFGHA B C D E F GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器正逻辑或门,或非门:Vcc 4B 4A 4Y 3B 3A 3Y┌┴─┴─┴─┴─┴─┴─┴┐2输入四或门 74LS32│1413 12 11 10 9 8│)│Y = A+B│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2A 2B 2Y GNDVcc 4Y 4B 4A 3Y 3B 3A┌┴─┴─┴─┴─┴─┴─┴┐2输入四或非门 74LS02│1413 12 11 10 9 8│ ___)│ Y = A+B│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1Y 1A 1B 2Y 2A 2B GNDVcc 2Y 2B 2A 2D 2E 1F┌┴─┴─┴─┴─┴─┴─┴┐双与或非门 74S51│1413 12 11 10 9 8│ _____)│2Y = AB+DE│ 1 2 3 4 5 6 7│ _______└┬─┬─┬─┬─┬─┬─┬┘1Y = ABC+DEF1Y 1A 1B 1C 1D 1E GNDVcc D C B K J Y┌┴─┴─┴─┴─┴─┴─┴┐4-2-3-2与或非门 74S64 74S65(OC门)│1413 12 11 10 9 8│______________)│Y = ABCD+EF+GHI+JK│ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘A E F G H I GND页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器2输入四异或门 74LS86Vcc 4B 4A 4Y 3Y 3B 3A┌┴─┴─┴─┴─┴─┴─┴┐│1413 12 11 10 9 8│)│_ _│ 1 2 3 4 5 6 7│Y=AB+AB└┬─┬─┬─┬─┬─┬─┬┘1A 1B 1Y 2Y 2A 2B GND8*2输入比较器 74LS688_Vcc Y B8 A8 B7 A7 B6 A6 B5 A5┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐8*2输入比较器 74LS688│2019 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘CE A1 B1 A2 B2 A3 B3 A4 B4 GND_Y=A1⊙B1+A2⊙B2+A3⊙B3+A4⊙B4+A5⊙B5+A6⊙B6+A7⊙B7+A8⊙B8页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器3-8译码器 74LS138Vcc -Y0 -Y1 -Y2 -Y3 -Y4 -Y5 -Y6 __ _ _ _ __ _ _ __ _ _ __ _ ┌┴─┴─┴─┴─┴─┴─┴─┴┐Y0=A B C Y1=A B B Y2=A B C Y3=A B C│1615 14 13 12 11 10 9 │)│__ _ _ ___ __ _ __│ 1 2 3 4 5 6 7 8│Y4=A B C Y5=A B C Y6=A B C Y 7=A B C└┬─┬─┬─┬─┬─┬─┬─┬┘A B C -CS0 -CS1 CS2 -Y7 GND双2-4译码器 74LS139Vcc -2G 2A 2B -Y0 -Y1 -Y2 -Y3 __ __ __ __ __ __ __ __┌┴─┴─┴─┴─┴─┴─┴─┴┐Y0=2A 2B Y1=2A 2B Y2=2A 2B Y3=2A 2B│1615 14 13 12 11 10 9 │)│__ __ __ __ __ __ __ __│ 1 2 3 4 5 6 7 8│Y0=1A 1B Y1=1A 1B Y2=1A 1B Y 3=1A 1B└┬─┬─┬─┬─┬─┬─┬─┬┘-1G 1A 1B -Y0 -Y1 -Y2 -Y3 GND8*2输入比较器 74LS688_Vcc Y B8 A8 B7 A7 B6 A6 B5 A5┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐8*2输入比较器 74LS688│2019 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘CE A1 B1 A2 B2 A3 B3 A4 B4 GND_Y=A1⊙B1+A2⊙B2+A3⊙B3+A4⊙B4+A5⊙B5+A6⊙B6+A7⊙B7+A8⊙B8寄存器:Vcc 2CR 2D 2Ck 2St 2Q -2Q┌┴─┴─┴─┴─┴─┴─┴┐双D触发器 74LS74│1413 12 11 10 9 8 │)││ 1 2 3 4 5 6 7│└┬─┬─┬─┬─┬─┬─┬┘1Cr 1D 1Ck 1St 1Q -1Q GNDVcc 8Q 8D 7D 7Q 6Q 6D 5D 5Q ALE┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐8位锁存器 74LS373│2019 18 17 16 15 14 13 12 11│)││ 1 2 3 4 5 6 7 8 9 10│└┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘-OE 1Q 1D 2D 2Q 3Q 3D 4D 4Q GND型号器件名称厂牌[数据表]SN7400四2输入端与非门 TI[DATA]SN7401四2输入端与非门(OC) SN7402四2输入端或非门 TI[DATA]SN7403四2输入端与非门(OC)TI[DATA]SN7404六反相器 TI[DATA]SN7405六反相器(O C)TI[DATA]SN7406六高压输出反相器(OC,30V)TI[DATA]SN7407六高压输出缓冲,驱动器(OC,30V)TI[DATA]SN7408四2输入端与门TI[DATA]SN7409四2输入端与门(OC)TI[DATA]SN7410三3输入端与非门 TI[DATA]SN7412三3输入端与非门(OC)TI[DATA]SN7413双4输入端与非门TI[DATA]SN7414六反相器TI[DATA]SN7416六高压输出反相缓冲/驱动器 I[DATA]SN7417六高压输出缓冲/驱动器(OC,15V)TI[DATA]SN7420双4输入端与非门 TI[DATA]SN7422双4输入端与非门(OC)TI[DATA]SN7423可扩展双4输入端或非门 TI[DATA]SN7425双4输入端或非门TI[DATA]SN7426四2输入端高压输出与非缓冲器 [DATA]SN7427三3输入端或非门TI[DATA]SN7428四2输入端或非缓冲器 I[DATA]SN74308输入端与非门TI[DATA]SN7432四2输入端或门。

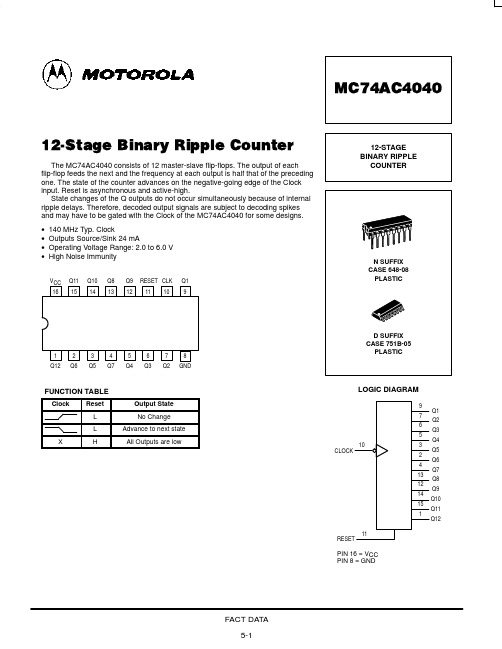

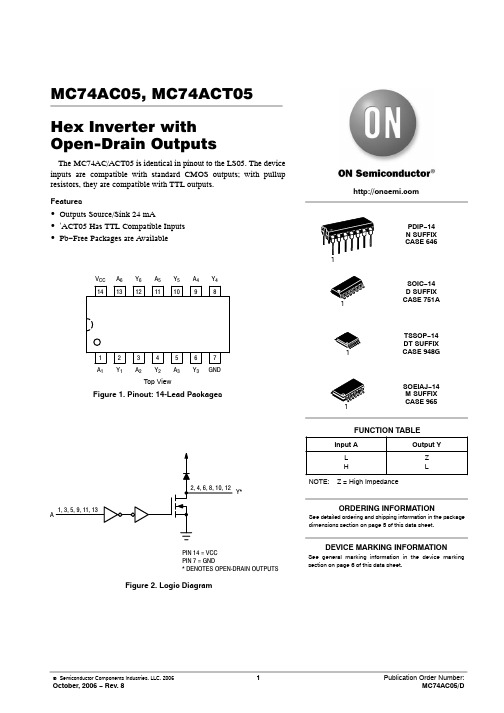

MC74ACT05MELG资料

MC74AC05, MC74ACT05Hex Inverter with Open−Drain OutputsThe MC74AC/ACT05 is identical in pinout to the LS05. The device inputs are compatible with standard CMOS outputs; with pullup resistors, they are compatible with TTL outputs.Features•Outputs Source/Sink 24 mA•′ACT05 Has TTL Compatible Inputs •Pb −Free Packages are AvailableGNDFigure 1. Pinout: 14-Lead Packages1314121110982134567V CC A 6Y 6A 5Y 5A 4Y 4A 1Y 1A 2Y 2A 3Y 3Top ViewFigure 2. Logic DiagramY*APIN 14 = VCC PIN 7 = GND* DENOTES OPEN-DRAIN OUTPUTSSee general marking information in the device marking section on page 6 of this data sheet.DEVICE MARKING INFORMATIONSee detailed ordering and shipping information in the package dimensions section on page 5 of this data sheet.ORDERING INFORMATIONTSSOP −14DT SUFFIX CASE 948GSOEIAJ −14M SUFFIX CASE 965SOIC −14D SUFFIX CASE 751APDIP −14N SUFFIX CASE 646FUNCTION TABLEInput A L HOutput YZ LNOTE:Z = High ImpedanceMAXIMUM RATINGSSymbol Parameter Value Unit V CC DC Supply Voltage (Referenced to GND)−0.5 to +7.0V V in DC Input Voltage (Referenced to GND)−0.5 to V CC + 0.5V V out DC Output Voltage (Referenced to GND)−0.5 to V CC + 0.5VI in DC Input Current, per Pin± 20mAI out DC Output Sink/Source Current, per Pin± 50mAI CC DC V CC or GND Current per Output Pin± 50mAT stg Storage Temperature−65 to +150°C Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above theRecommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.RECOMMENDED OPERATING CONDITIONSSymbol Parameter Min Typ Min UnitV CC Supply Voltage′AC 2.0 5.0 6.0V ′ACT 4.5 5.0 5.5VREG DC Regulated Power Voltage (Ref. to GND)0−V CC Vt r, t f Input Rise and Fall Time (Note 1)′AC Devices except Schmitt InputsV CC @ 3.0 V−150−V CC @ 4.5 V−40−ns/VV CC @ 5.5 V−25−t r, t f Input Rise and Fall Time (Note 2)′ACT Devices except Schmitt InputsV CC @ 4.5 V−10−ns/VV CC @ 5.5 V−8.0−T J Junction Temperature (PDIP)−−140°C T A Operating Ambient Temperature Range−402585°CI OH Output Current − HIGH−−−24mAI OL Output Current − LOW−−24mA1.V in from 30% to 70% V CC; see individual Data Sheets for devices that differ from the typical input rise and fall times.2.V in from 0.8 V to 2.0 V; see individual Data Sheets for devices that differ from the typical input rise and fall times.DC CHARACTERISTICSSymbol Parameter V CC(V)74AC74ACUnit Conditions T A = +25°C T A = −40°C to +85°CTyp Guaranteed LimitsV IH Minimum High Level Input Voltage 3.0 1.5 2.1 2.1V OUT = 0.1 V4.5 2.25 3.15 3.15V or V CC− 0.1 V5.5 2.75 3.85 3.85V IL Maximum Low Level Input Voltage 3.0 1.50.90.9V OUT = 0.1 V4.5 2.25 1.35 1.35V or V CC− 0.1 V5.5 2.75 1.65 1.65V OL Maximum Low Level Output Voltage 3.00.0020.10.1I OUT = 50 m A4.50.0010.10.1V5.50.0010.10.1V *V IN = V IL or V IH3.0−0.360.4412 mA4.5−0.360.44I OL24 mA5.5−0.360.4424 mAI IN Maximum Input Leakage Current 5.5−±0.1±1.0m A V I = V CC, GNDI OLD†Minimum DynamicOutput Current 5.5−−75mA V OLD = 1.65 V MaxI OHD 5.5−−−75mA V OHD = 3.85 V MinI CC Maximum Quiescent Supply Current 5.5− 4.040m A V IN = V CC or GND *All outputs loaded; thresholds on input associated with output under test.†Maximum test duration 2.0 ms, one output loaded at a time.NOTE:I IN and I CC @ 3.0 V are guaranteed to be less than or equal to the respective limit @ 5.5 V.AC CHARACTERISTICSSymbol Parameter V CC*(V)74AC74ACUnit T A = +25°C C L = 50 pF T A = −40°C to +85°C C L = 50 pFMin Typ Max Min Maxt PZL Propagation Delay Output Enable 3.3 1.5−8.0 1.09.0ns5.0 1.5−6.0 1.0 6.5t PLZ Propagation Delay Output Enable 3.3 1.5−8.0 1.09.0ns5.0 1.5−6.0 1.0 6.5*Voltage Range 3.3 V is 3.3 V ±0.3 V.Voltage Range 5.0 V is 5.0 V ±0.5 V.DC CHARACTERISTICSSymbol Parameter V CC(V)74ACT74ACTUnit Conditions T A = +25°C T A = −40°C to +85°CTyp Guaranteed LimitsV IH Minimum High Level Input Voltage 4.55.51.51.52.02.02.02.0VV OUT = 0.1 Vor V CC− 0.1 VV IL Maximum Low Level Input Voltage 4.55.51.51.50.80.80.80.8VV OUT = 0.1 Vor V CC− 0.1 VV OL Maximum Low Level Output Voltage 4.55.50.0010.0010.10.10.10.1VI OUT = 50 m A4.55.5−−0.360.360.440.440.44*V IN = V IL or V IHI OH24 mAI IN Maximum Input Leakage Current 5.5−±0.1±1.0m A V I = V CC, GND D I CCT Additional Max. I CC/Input 5.50.6− 1.5mA V I = V CC−2.1 VI OLD I OHD †Minimum Dynamic Output Current 5.55.5−−−−75−75mAmAV OLD = 1.65 V MaxV OHD = 3.85 V MinI CC Maximum Quiescent Supply Current 5.5− 4.040m A V IN = V CC or GND *All outputs loaded; thresholds on input associated with output under test.†Maximum test duration 2.0 ms, one output loaded at a time.AC CHARACTERISTICSSymbol Parameter V CC*(V)74ACT74ACTUnit T A = +25°C C L = 50 pF T A = −40°C to +85°C C L = 50 pFMin Typ Max Min Maxt PZL Propagation Delay Output Enable 5.0 1.5−8.0 1.08.5ns t PLZ Propagation Delay Output Enable 5.0 1.5−8.5 1.09.0ns *Voltage Range 5.0 V is 5.0 V ±0.5 V.CAPACITANCESymbol Parameter Value Typ Unit Test ConditionsC IN Input Capacitance 4.5pF V CC = 5.0 VC PD Power Dissipation Capacitance30pF V CC = 5.0 VORDERING INFORMATIONDevicePackage Shipping †MC74AC05N PDIP −1425 Units / Rail MC74AC05NG PDIP −14(Pb −Free)MC74AC05D SOIC −1455 Units / Rail MC74AC05DG SOIC −14(Pb −Free)MC74AC05DR2SOIC −142500 / Tape & Reel MC74AC05DR2G SOIC −14(Pb −Free)MC74AC05MEL SOEIAJ −142000 / Tape & Reel MC74AC05MELG SOEIAJ −14(Pb −Free)MC74ACT05N PDIP −1425 Units / Rail MC74ACT05NG PDIP −14(Pb −Free)MC74ACT05D SOIC −1455 Units / Rail MC74ACT05DG SOIC −14(Pb −Free)MC74ACT05DR2SOIC −142500 / Tape & Reel MC74ACT05DR2G SOIC −14(Pb −Free)MC74ACT05DTR2TSSOP −14*MC74ACT05DTR2G TSSOP −14*MC74ACT05MEL SOEIAJ −142000 / Tape & Reel MC74ACT05MELGSOEIAJ −14(Pb −Free)†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.*These packages are inherently Pb −Free.MARKING DIAGRAMSPDIP −14SOIC −14TSSOP −14SOEIAJ −1411474ACT05ALYWG ACT 05ALYW G G114A = Assembly Location WL, L = Wafer Lot YY, Y = YearWW, W = Work WeekG or G = Pb −Free Package(Note: Microdot may be in either location)11474AC05ALYWG MC74AC05N AWLYYWWG 114MC74ACT05N AWLYYWWG 114PACKAGE DIMENSIONSPDIP−14CASE 646−06ISSUE PPACKAGE DIMENSIONSSOIC −14CASE 751A −03ISSUE HNOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.4.MAXIMUM MOLD PROTRUSION 0.15 (0.006)PER SIDE.5.DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127(0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.DIM MIN MAX MIN MAX INCHESMILLIMETERS A 8.558.750.3370.344B 3.80 4.000.1500.157C 1.35 1.750.0540.068D 0.350.490.0140.019F 0.40 1.250.0160.049G 1.27 BSC 0.050 BSC J 0.190.250.0080.009K 0.100.250.0040.009M 0 7 0 7 P 5.80 6.200.2280.244R0.250.500.0100.019____DIMENSIONS: MILLIMETERS*For additional information on our Pb −Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.PACKAGE DIMENSIONSTSSOP −14CASE 948G −01ISSUE ADIM MIN MAX MIN MAX INCHESMILLIMETERS A 4.90 5.100.1930.200B 4.30 4.500.1690.177C −−− 1.20−−−0.047D 0.050.150.0020.006F 0.500.750.0200.030G 0.65 BSC 0.026 BSC H 0.500.600.0200.024J 0.090.200.0040.008J10.090.160.0040.006K 0.190.300.0070.012K10.190.250.0070.010L 6.40 BSC 0.252 BSC M0 8 0 8 NOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSION A DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE.4.DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 (0.010) PER SIDE.5.DIMENSION K DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBARPROTRUSION SHALL BE 0.08 (0.003) TOTAL IN EXCESS OF THE K DIMENSION AT MAXIMUM MATERIAL CONDITION.6.TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY .7.DIMENSION A AND B ARE TO BEDETERMINED AT DATUM PLANE −W −.____14X REFPACKAGE DIMENSIONSSOEIAJ −14CASE 965−01ISSUE AON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

MC74ACT574DW中文资料

1. Vin from 30% to 70% VCC; see individual Data Sheets for devices that differ from the typical input rise and fall times. 2. Vin from 0.8 V to 2.0 V; see individual Data Sheets for devices that differ from the typical input rise and fall times.

RECOMMENDED OPERATING CONDITIONS

Symbol VCC Vin, Vout Supply Voltage DC Input Voltage, Output Voltage (Ref. to GND) VCC @ 3.0 V tr, tf Input Rise and Fall Time (Note 1) ′AC Devices except Schmitt Inputs VCC @ 4.5 V VCC @ 5.5 V tr, tf TJ TA IOH IOL Input Rise and Fall Time (Note 2) ′ACT Devices except Schmitt Inputs Junction Temperature (PDIP) Operating Ambient Temperature Range Output Current — High Output Current — Low –40 25 VCC @ 4.5 V VCC @ 5.5 V Parameter ′AC ′ACT Min 2.0 4.5 0 150 40 25 10 ns/V 8.0 140 85 –24 24 °C °C mA mA ns/V Typ 5.0 5.0 Max 6.0 5.5 VCC V Unit V

74HC20D中文资料

December 1990

6

Product specification

74HC/HCT20

DC CHARACTERISTICS FOR 74HC

For the DC characteristics see “74HC/HCT/HCU/HCMOS Logic Family Specifications”.

Output capability: standard ICC category: SSI

Philips Semiconductors

Dual 4-input NAND gate

PIN DESCRIPTION

PIN NO. 1, 9 2, 10 3, 11 4, 12 5, 13 6, 8 7 14

SYMBOL 1A, 2A 1B, 2B n.c. 1C, 2C 1D, 2D 1Y, 2Y GND VCC

28 90

115

nA, nB, nC, nD to nY

10 18

23

8 15

20

tTHL/ tTLH output transition time

19 75

95

7 15

19

6 13

16

TEST CONDITIONS

−40 to +125

UNIT

VCC (V)

WAVEFORMS

min. max.

135 ns 27 23

INPUT nA, nB, nC, nD

UNIT LOAD COEFFICIENT 0.3

AC CHARACTERISTICS FOR 74HCT GND = 0 V; tr = tf = 6 ns; CL = 50 pF

74系列功能大全(中文)

74系列功能大全(中文)74、74HC、74LS系列芯片资料,从网上下的,集合了一下系列电平典型传输延迟ns 最大驱动电流(-Ioh/Lol)mAAHC CMOS 8.5 -8/8AHCT COMS/TTL 8.5 -8/8HC COMS 25 -8/8HCT COMS/TTL 25 -8/8ACT COMS/TTL 10 -24/24F TTL 6.5 -15/64ALS TTL 10 -15/64LS TTL 18 -15/24注:同型号的74系列、74HC系列、74LS系列芯片,逻辑功能上是一样的。

74LSxx的使用说明如果找不到的话,可参阅74xx或74HCxx的使用说明。

有些资料里包含了几种芯片,如74HC161资料里包含了74HC160、74HC161、74HC162、74HC163四种芯片的资料。

找不到某种芯片的资料时,可试着查看一下临近型号的芯片资料。