6803中文资料

OPA680中文资料

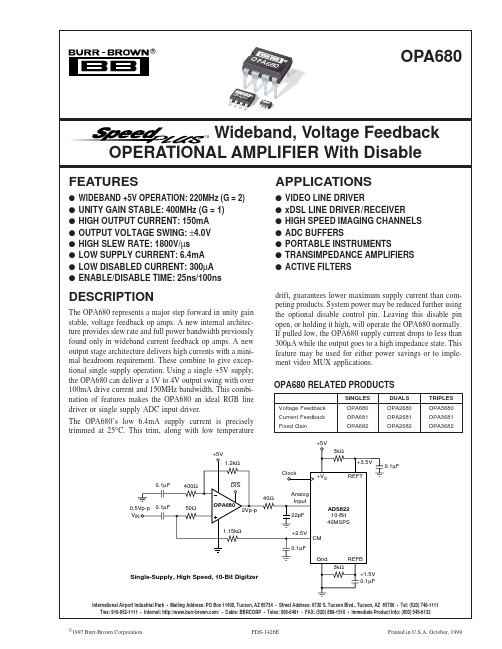

UNITS MHz MHz MHz MHz MHz dB MHz V/µs ns ns ns ns dBc dBc dBc dBc nV/√Hz pA/√Hz % deg dB mV µV/°C µA nA/°C µA nA/°C V dB kΩ || pF MΩ || pF

Gain-Bandwidth Product Bandwidth for 0.1dB Gain Flatness Peaking at a Gain of +1 Large-Signal Bandwidth Slew Rate Rise/Fall Time Settling Time to 0.02% 0.1% Harmonic Distortion 2nd Harmonic 3rd Harmonic Input Voltage Noise Input Current Noise Differential Gain Differential Phase DC PERFORMANCE(4) Open-Loop Voltage Gain (AOL ) Input Offset Voltage Average Offset Voltage Drift Input Bias Current Average Bias Current Drift (magnitude) Input Offset Current Average Offset Current Drift INPUT Common-Mode Input Range (CMIR)(5) Common-Mode Rejection Ratio (CMRR) Input Impedance Differential-Mode Common-Mode OUTPUT Voltage Output Swing Current Output, Sourcing Current Output, Sinking Closed-Loop Output Impedance DISABLE (Disabled Low) Power Down Supply Current (+VS) Disable Time Enable Time Off Isolation Output Capacitance in Disable Turn On Glitch Turn Off Glitch Enable Voltage Disable Voltage Control Pin Input Bias Current (VDIS) POWER SUPPLY Specified Operating Voltage Maximum Operating Voltage Range Max Quiescent Current Min Quiescent Current Power Supply Rejection Ratio (+PSRR) THERMAL CHARACTERISTICS Specified Operating Range P, U, N Package Thermal Resistance, θJA P 8-Pin DIP U SO-8 N SOT23-6

9163中文资料

Copyright 1997, 1999 by Capital Advanced Technologies, Inc. All rights reserved. Surfboards Are a registered trademark of Capital Advanced technologies, Inc. All other trademarks or registered trademarks are property of their respective owners. Availability, specifications, and prices are subject to change without notice. All information given is believed to be accurate but is not guaranteed. The user of information given or products represented by such information is responsible for determin-ing the suitability of said information or products for a given purpose. 685)%2$5'6 R 7+(%5($'%2$5',1*0(',80)25$&# & %% 6(5,(6)25, & V %2$5'0$7(5,$/ ,Q 7KLFN * )5 *ODVV (SR[\RU HTXLYDOHQW &,5&8,76 R]&RSSHU ZLWK VROGHU FRDWHG SDGV 72/(5$1&(6 *LYHQ LQ LQFKHV %RDUG 6L]H 2$/ &LU FXLW SDWWHUQ SRVLWLRQ %2$5'63(&,),&$7,216&$3,7$/$'9$1&('7(&+12/2*,(6 ,1&&$52/675($0 ,//,12,6 86$ 3+21( ::: &DSLWDO$GYDQFHG &RP )$; 21 '(0$1' )2,/02',),&$7,216(;3$1'9(56$7,/,7<7\SLFDO RI PDQ\6XUIERDUGV DUH ODUJH SDG DUHDV ZKLFK ZKLFKPD\EH PRGLILHG WR FUHDWH DGGLWLRQDO SDUWPRXQWLQJ ]RQHV RU H[SDQG OD\RXW RU FRQQHFWLRQ RSWLRQV6FRUH IRLO ZLWK VKDUS UD]RU WR GHILQH QHZ ]RQH$SSO\KHDW ZLWK LURQ WR GHODPLQDWH IRLO VHFWLRQ1HZ PRXQWLQJ ]RQH KDV EHHQ FUHDWHG 6ROGHU FRPSRQHQW WR QHZ PRXQWLQJ ]RQH675$''/(, & SLQV IDQ RXW WR SHULSKHUDO SDUW PRXQWLQJ DUHDV FDSDEOH RI DFFHSWLQJ VHYHUDO VXUIDFH PRXQW GHYLFHV 02'(/$&&(37621( 25 3,16 2 , & #7:2 3,162,&V',5(&73,128725$''$'',7,21$/&20321(1763,7&+ LQ PPLQ PP , & )22735,17DFFHSWV RQH RU SLQ 62,& RU WZR SLQ 62,&V LQ LQ ,Q ,QFKHV $ % & ' ( 3,163(&,),&$7,216 72/(5$1&(6-867$''3$576$1'3/8*,1 706,1*/( ,1 /,1( 6,3 3,1621 LQ &(17(567KH SURYLGHV GLUHFW SLQ RXW RI , & WR 6,3SLQV ,I GHVLUHG FRPSRQHQWV FDQ EH PRXQWHG DFURVV DGMRLQLQJ FLUFXLWV VWUDGGOH PRXQWHG RU QHZ PRXQWLQJ ]RQHV FDQ EH FUHDWHG LQ WKH ODUJH FLUFXLW IRLOV 7KH ODUJH IRLOV SURYLGH VSDFH IRU VLJQLILFDQW PRGLILFDWLRQV RU DGGLWLRQ RI MXPSHUV LI QHHGHG 7KH ILQLVKHG SURWRW\SH RI VXE DVVHPEO\FDQ EH SOXJJHG LQWR D VROGHUOHVV EUHDGERDUG RU VRFNHW RU VROGHUHG LQWR D FRQYHQWLRQDO EUHDGERDUG IDS9163A 3-9-99元器件交易网。

LPD6803中文资料

5:SOP16/TSSOP16封装下,LPD6803可直接替换ZQL9712(恒压模式)

引脚布局:

NO.

引脚名称

I/O

功能

1

DIN

输入

串行数据输入,内度矫正方式:GMODE=1,采用线性调制,GMODE=0,采用反伽码256级非线性调制。内置上拉

15

DOUT

输出

串行数据输出,经内部前驱动输出

16

VCC

--

电源

恒流模式下反馈输出

11

OUT3

输出

三路PWM驱动输出

12

DCLKO

输出

串行时钟输出,经内部锁相再生和强驱动输出

13

CMODE

输入

选择内部灰度时钟源GCLK:CMODE=0, GCLK=DCLK, CMODE=1, GCLK二内部振荡器输出。内置上拉

14

VOUT

输出

VCC>5V时,5V稳压输出,VCC<5V时,VOCT=VCC,同时作内部工作电压,建议外接一个0.0 1 uF-0. 1 uF的退藕电容到地

简化外围配套,可扩充性好,也可作为PWM发生器控制大电流器件驱动大功率LED灯

与ZQL9712性能比较:

注1:测试条件为数据时钟2M,长度200级,32级灰度,LPD6803扫描频率与长度无关;

2:显示同样内容,LPD6803的数据量为ZQL9712的1/5-1/3;

3:FREE-RUN功能指停止控制信号输入后,保持原有灰度显示的能力;

直接PWM输出,无亮度损失,降低数据传输量,有效减少电磁干扰(EMI)

支持32级灰度/256级灰度(内置反伽码校正逻辑)两种模式,扫描频率高(>4000HZ)

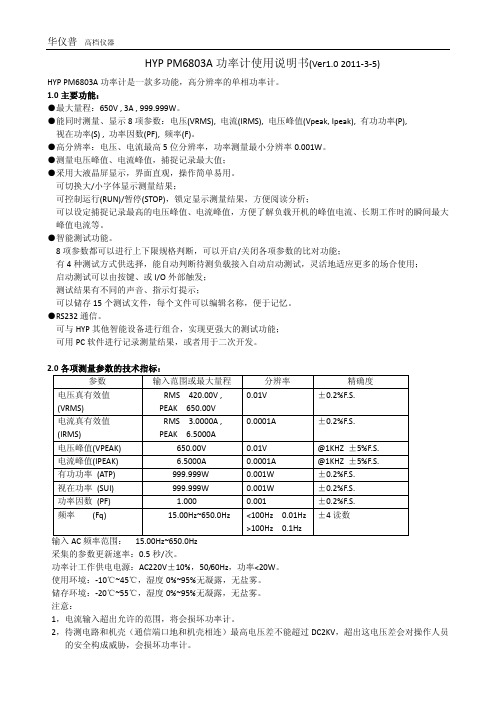

华仪普 HYP PM6803A 功率计使用说明书

HYP PM6803A功率计使用说明书(Ver1.0 2011‐3‐5)HYP PM6803A功率计是一款多功能,高分辨率的单相功率计。

1.0主要功能:●最大量程:650V , 3A , 999.999W。

●能同时测量、显示8项参数:电压(VRMS), 电流(IRMS), 电压峰值(Vpeak, Ipeak), 有功功率(P),视在功率(S) , 功率因数(PF), 频率(F)。

●高分辨率:电压、电流最高5位分辨率,功率测量最小分辨率0.001W。

●测量电压峰值、电流峰值,捕捉记录最大值;●采用大液晶屏显示,界面直观,操作简单易用。

可切换大/小字体显示测量结果;可控制运行(RUN)/暂停(STOP),锁定显示测量结果,方便阅读分析;可以设定捕捉记录最高的电压峰值、电流峰值,方便了解负载开机的峰值电流、长期工作时的瞬间最大峰值电流等。

●智能测试功能。

8项参数都可以进行上下限规格判断,可以开启/关闭各项参数的比对功能;有4种测试方式供选择,能自动判断待测负载接入自动启动测试,灵活地适应更多的场合使用;启动测试可以由按键、或I/O外部触发;测试结果有不同的声音、指示灯提示;可以储存15个测试文件,每个文件可以编辑名称,便于记忆。

●RS232通信。

可与HYP其他智能设备进行组合,实现更强大的测试功能;可用PC软件进行记录测量结果,或者用于二次开发。

2.0各项测量参数的技术指标:参数 输入范围或最大量程 分辨率 精确度电压真有效值 (VRMS)RMS 420.00V ,PEAK 650.00V0.01V ±0.2%F.S.电流真有效值 (IRMS)RMS 3.0000A ,PEAK 6.5000A0.0001A ±0.2%F.S.电压峰值(VPEAK) 650.00V 0.01V @1KHZ ±5%F.S.电流峰值(IPEAK) 6.5000A 0.0001A @1KHZ ±5%F.S.有功功率 (ATP) 999.999W 0.001W ±0.2%F.S.视在功率 (SUI) 999.999W 0.001W ±0.2%F.S.功率因数 (PF) 1.000 0.001 ±0.2%F.S.频率 (Fq) 15.00Hz~650.0Hz <100Hz 0.01Hz>100Hz 0.1Hz±4读数输入AC频率范围: 15.00Hz~650.0Hz采集的参数更新速率:0.5秒/次。

AU6803 Twin PLL specifications ED3

5.3 Measures for Eliminating Noise 5.4 Constructing a Fail-safe System 5.5 Encoder Application Appendix Outline drawing of IC chip

--- --- --- --- --- --- --- --- --- --- --- --- --- --- --- ------ --- --- 30 --- --- --- --- --- --- --- --- --- --- --- --- --- --- --- ------ --- --- 31 --- --- --- --- --- --- --- --- --- --- --- --- --- --- --- --- --- --- --- 32

Setting register

Twin-PLL Smartcoder AU6803 Specifications Table of Contents

1. Scope 2. Related Documents 3. Requirements --- --- --- --- --- --- --- --- --- --- --- --- --- --- --- --- --- ------ --- --- 3 --- --- --- --- --- --- --- --- --- --- --- --- --- --- --- --- --- ------ --- --- 3 --- --- --- --- --- --- --- --- --- --- --- --- --- --- --- --- --- ------ --- --- 3 --- --- --- --- --- ------ --- --- --- --- --- --- --- --- --- --- -- 3

CY7C68013A中文资料

EZ-USB FX2LP™ USB MicrocontrollerCY7C68013A/CY7C68014A CY7C68015A/CY7C68016A1.0Features (CY7C68013A/14A/15A/16A)•USB 2.0–USB-IF high speed certified (TID # 40440111)•Single-chip integrated USB 2.0 transceiver, smart SIE, and enhanced 8051 microprocessor•Fit, form and function compatible with the FX2—Pin-compatible—Object-code-compatible—Functionally-compatible (FX2LP is a superset)•Ultra Low power: I CC no more than 85 mA in any mode —Ideal for bus and battery powered applications •Software: 8051 code runs from:—Internal RAM, which is downloaded via USB —Internal RAM, which is loaded from EEPROM —External memory device (128 pin package)•16 KBytes of on-chip Code/Data RAM•Four programmable BULK/INTERRUPT/ISOCHRO-NOUS endpoints—Buffering options: double, triple, and quad•Additional programmable (BULK/INTERRUPT) 64-byte endpoint•8- or 16-bit external data interface •Smart Media Standard ECC generation •GPIF (General Programmable Interface)—Allows direct connection to most parallel interface—Programmable waveform descriptors and configu-ration registers to define waveforms—Supports multiple Ready (RDY) inputs and Control (CTL) outputs•Integrated, industry-standard enhanced 8051—48-MHz, 24-MHz, or 12-MHz CPU operation —Four clocks per instruction cycle —Two USARTS—Three counter/timers—Expanded interrupt system —Two data pointers•3.3V operation with 5V tolerant inputs•Vectored USB interrupts and GPIF/FIFO interrupts •Separate data buffers for the Set-up and Data portions of a CONTROL transfer•Integrated I 2C controller, runs at 100 or 400 kHz •Four integrated FIFOs—Integrated glue logic and FIFOs lower system cost —Automatic conversion to and from 16-bit buses —Master or slave operation—Uses external clock or asynchronous strobes —Easy interface to ASIC and DSP ICs•Available in Commercial and Industrial temperature grade (all packages except VFBGA)A d d r e s s (16)x20PLL/0.5/1.0/2.08051 Core 12/24/48 MHz,four clocks/cycleI 2CVCC1.5kD+D–A d d r e s s (16) / D a t aB u s (8)FX2LPGPIFCY Smart USB 1.1/2.0EngineUSB 2.0XCVR16 KB RAM4 kB FIFOIntegrated full- and high-speedXCVRAdditional I/Os (24)ADDR (9)CTL (6)RDY (6)8/16D a t a (8)24 MHz Ext. XTALEnhanced USB core Simplifies 8051 code “Soft Configuration”Easy firmware changes FIFO and endpoint memory (master or slave operation)Up to 96 MBytes/s burst rateGeneralprogrammable I/F to ASIC/DSP or bus standards such as ATAPI, EPP , etc.Abundant I/Oincluding two USARTS High-performance micro using standard toolswith lower-power optionsMasterFigure 1-1. Block Diagramconnected for full speedECC1.1Features (CY7C68013A/14A only)•CY7C68014A: Ideal for battery powered applications —Suspend current: 100 µA (typ)•CY7C68013A: Ideal for non-battery powered applica-tions—Suspend current: 300 µA (typ)•Available in five lead-free packages with up to 40 GPIOs —128-pin TQFP (40 GPIOs), 100-pin TQFP (40 GPIOs),56-pin QFN (24 GPIOs), 56-pin SSOP (24 GPIOs), and 56-pin VFBGA (24 GPIOs)1.2Features (CY7C68015A/16A only)•CY7C68016A: Ideal for battery powered applications—Suspend current: 100 µA (typ)•CY7C68015A: Ideal for non-battery powered applica-tions—Suspend current: 300 µA (typ)•Available in lead-free 56-pin QFN package (26 GPIOs)—2 more GPIOs than CY7C68013A/14A enabling addi-tional features in same footprintCypress Semiconductor Corporation’s (Cypress’s) EZ-USB FX2LP™ (CY7C68013A/14A) is a low-power version of the EZ-USB FX2™ (CY7C68013), which is a highly integrated, low-power USB 2.0 microcontroller. By integrating the USB 2.0 transceiver, serial interface engine (SIE), enhanced 8051 microcontroller, and a programmable peripheral interface in a single chip, Cypress has created a very cost-effective solution that provides superior time-to-market advantages with low power to enable bus powered applications.The ingenious architecture of FX2LP results in data transfer rates of over 53 Mbytes per second, the maximum-allowable USB 2.0 bandwidth, while still using a low-cost 8051 microcon-troller in a package as small as a 56 VFBGA (5mm x 5mm). Because it incorporates the USB 2.0 transceiver, the FX2LP is more economical, providing a smaller footprint solution than USB 2.0 SIE or external transceiver implementations. With EZ-USB FX2LP, the Cypress Smart SIE handles most of the USB 1.1 and 2.0 protocol in hardware, freeing the embedded microcontroller for application-specific functions and decreasing development time to ensure USB compatibility. The General Programmable Interface (GPIF) and Master/Slave Endpoint FIFO (8- or 16-bit data bus) provides an easy and glueless interface to popular interfaces such as ATA, UTOPIA, EPP, PCMCIA, and most DSP/processors. The FX2LP draws considerably less current than the FX2 (CY7C68013), has double the on-chip code/data RAM and is fit, form and function compatible with the 56-, 100-, and 128-pin FX2.Five packages are defined for the family: 56VFBGA, 56 SSOP, 56 QFN, 100 TQFP, and 128 TQFP.2.0 Applications•Portable video recorder•MPEG/TV conversion•DSL modems•ATA interface•Memory card readers•Legacy conversion devices•Cameras•Scanners•Home PNA•Wireless LAN•MP3 players•NetworkingThe “Reference Designs” section of the Cypress web site provides additional tools for typical USB 2.0 applications. Each reference design comes complete with firmware source and object code, schematics, and documentation. Please visit for more information.3.0Functional Overview3.1USB Signaling SpeedFX2LP operates at two of the three rates defined in the USB Specification Revision 2.0, dated April 27, 2000:•Full speed, with a signaling bit rate of 12 Mbps •High speed, with a signaling bit rate of 480 Mbps.FX2LP does not support the low-speed signaling mode of 1.5Mbps.3.28051 MicroprocessorThe 8051 microprocessor embedded in the FX2LP family has 256 bytes of register RAM, an expanded interrupt system,three timer/counters, and two USARTs.3.2.18051 Clock FrequencyFX2LP has an on-chip oscillator circuit that uses an external 24-MHz (±100-ppm) crystal with the following characteristics:•Parallel resonant •Fundamental mode •500-µW drive level•12-pF (5% tolerance) load capacitors.An on-chip PLL multiplies the 24-MHz oscillator up to 480MHz, as required by the transceiver/PHY , and internal counters divide it down for use as the 8051 clock. The default 8051 clock frequency is 12 MHz. The clock frequency of the 8051 can be changed by the 8051 through the CPUCS register, dynamically.The CLKOUT pin, which can be three-stated and inverted using internal control bits, outputs the 50% duty cycle 8051clock, at the selected 8051 clock frequency—48, 24, or 12MHz.3.2.2USARTSFX2LP contains two standard 8051 USARTs, addressed via Special Function Register (SFR) bits. The USART interface pins are available on separate I/O pins, and are not multi-plexed with port pins.UART0 and UART1 can operate using an internal clock at 230KBaud with no more than 1% baud rate error. 230-KBaud operation is achieved by an internally derived clock source that generates overflow pulses at the appropriate time. The internal clock adjusts for the 8051 clock rate (48, 24, 12 MHz)such that it always presents the correct frequency for 230-KBaud operation.[1]3.2.3Special Function RegistersCertain 8051 SFR addresses are populated to provide fast access to critical FX2LP functions. These SFR additions are shown in Table 3-1. Bold type indicates non-standard,enhanced 8051 registers. The two SFR rows that end with “0”and “8” contain bit-addressable registers. The four I/O ports A–D use the SFR addresses used in the standard 8051 for ports 0–3, which are not implemented in FX2LP . Because of the faster and more efficient SFR addressing, the FX2LP I/O ports are not addressable in external RAM space (using the MOVX instruction).3.3I 2C BusFX2LP supports the I 2C bus as a master only at 100-/400-KHz.SCL and SDA pins have open-drain outputs and hysteresis inputs. These signals must be pulled up to 3.3V, even if no I 2C device is connected.3.4BusesAll packages: 8- or 16-bit “FIFO” bidirectional data bus, multi-plexed on I/O ports B and D. 128-pin package: adds 16-bit output-only 8051 address bus, 8-bit bidirectional data bus.Figure 3-1. Crystal Configuration12 pf12 pf24 MHz20 × PLLC1C212-pF capacitor values assumes a trace capacitanceof 3 pF per side on a four-layer FR4 PCANote:1.115-KBaud operation is also possible by programming the 8051 SMOD0 or SMOD1 bits to a “1” for UART0 and/or UART1, respectively.3.5USB Boot MethodsDuring the power-up sequence, internal logic checks the I2C port for the connection of an EEPROM whose first byte is either 0xC0 or 0xC2. If found, it uses the VID/PID/DID values in the EEPROM in place of the internally stored values (0xC0), or it boot-loads the EEPROM contents into internal RAM (0xC2). If no EEPROM is detected, FX2LP enumerates using internally stored descriptors. The default ID values for FX2LP are VID/PID/DID (0x04B4, 0x8613, 0xAxxx where xxx = Chip revision).[2]3.6ReNumeration™Because the FX2LP’s configuration is soft, one chip can take on the identities of multiple distinct USB devices.When first plugged into USB, the FX2LP enumerates automat-ically and downloads firmware and USB descriptor tables over the USB cable. Next, the FX2LP enumerates again, this time as a device defined by the downloaded information. This patented two-step process, called ReNumeration™, happens instantly when the device is plugged in, with no hint that the initial download step has occurred.Two control bits in the USBCS (USB Control and Status) register control the ReNumeration process: DISCON and RENUM. To simulate a USB disconnect, the firmware sets DISCON to 1. To reconnect, the firmware clears DISCON to 0. Before reconnecting, the firmware sets or clears the RENUM bit to indicate whether the firmware or the Default USB Device will handle device requests over endpoint zero: if RENUM = 0, the Default USB Device will handle device requests; if RENUM = 1, the firmware will.3.7Bus-powered ApplicationsThe FX2LP fully supports bus-powered designs by enumer-ating with less than 100 mA as required by the USB 2.0 speci-fication.3.8Interrupt System3.8.1INT2 Interrupt Request and Enable RegistersFX2LP implements an autovector feature for INT2 and INT4. There are 27 INT2 (USB) vectors, and 14 INT4 (FIFO/GPIF) vectors. See EZ-USB Technical Reference Manual (TRM) for more details.3.8.2USB-Interrupt AutovectorsThe main USB interrupt is shared by 27 interrupt sources. To save the code and processing time that normally would be required to identify the individual USB interrupt source, the FX2LP provides a second level of interrupt vectoring, called Autovectoring. When a USB interrupt is asserted, the FX2LP pushes the program counter onto its stack then jumps to address 0x0043, where it expects to find a “jump” instruction to the USB Interrupt service routine.Table 3-1. Special Function Registersx8x9x Ax Bx Cx Dx Ex Fx 0IOA IOB IOC IOD SCON1PSW ACC B 1SP EXIF INT2CLR IOE SBUF12DPL0MPAGE INT4CLR OEA3DPH0OEB4DPL1OEC5DPH1OED6DPS OEE7PCON8TCON SCON0IE IP T2CON EICON EIE EIP 9TMOD SBUF0A TL0AUTOPTRH1EP2468STAT EP01STAT RCAP2LB TL1AUTOPTRL1EP24FIFOFLGS GPIFTRIG RCAP2HC TH0reserved EP68FIFOFLGS TL2D TH1AUTOPTRH2GPIFSGLDATH TH2E CKCON AUTOPTRL2GPIFSGLDATLXF reserved AUTOPTRSET-UP GPIFSGLDATLNOXTable 3-2. Default ID Values for FX2LPDefault VID/PID/DIDVendor ID0x04B4Cypress SemiconductorProduct ID0x8613EZ-USB FX2LPDevice release0xAnnn Depends on chip revision(nnn = chip revision where firstsilicon = 001)Note:2.The I2C bus SCL and SDA pins must be pulled up, even if an EEPROM is not connected. Otherwise this detection method does not work properly.The FX2LP jump instruction is encoded as follows.If Autovectoring is enabled (AV2EN = 1 in the INTSET-UP register), the FX2LP substitutes its INT2VEC byte. Therefore, if the high byte (“page”) of a jump-table address is preloaded at location 0x0044, the automatically-inserted INT2VEC byte at 0x0045 will direct the jump to the correct address out of the 27 addresses within the page.3.8.3FIFO/GPIF Interrupt (INT4)Just as the USB Interrupt is shared among 27 individual USB-interrupt sources, the FIFO/GPIF interrupt is shared among 14 individual FIFO/GPIF sources. The FIFO/GPIF Interrupt, like the USB Interrupt, can employ autovectoring. Table3-4 shows the priority and INT4VEC values for the 14 FIFO/GPIF interrupt sources.Table 3-3. INT2 USB InterruptsUSB INTERRUPT TABLE FOR INT2 Priority INT2VEC Value Source Notes1 00SUDAV Set-up Data Available2 04 SOF Start of Frame (or microframe)3 08SUTOK Set-up Token Received4 0C SUSPEND USB Suspend request5 10USB RESET Bus reset6 14HISPEED Enteredhigh speed operation7 18 EP0ACK FX2LP ACK’d the CONTROL Handshake8 1C reserved9 20 EP0-IN EP0-IN ready to be loaded with data10 24 EP0-OUT EP0-OUT has USB data11 28 EP1-IN EP1-IN ready to be loaded with data12 2C EP1-OUT EP1-OUT has USB data13 30 EP2 IN: buffer available. OUT: buffer has data14 34 EP4 IN: buffer available. OUT: buffer has data15 38 EP6 IN: buffer available. OUT: buffer has data16 3C EP8 IN: buffer available. OUT: buffer has data17 40 IBN IN-Bulk-NAK (any IN endpoint)18 44reserved19 48 EP0PING EP0 OUT was Pinged and it NAK’d20 4C EP1PING EP1 OUT was Pinged and it NAK’d21 50 EP2PING EP2 OUT was Pinged and it NAK’d22 54 EP4PING EP4 OUT was Pinged and it NAK’d23 58 EP6PING EP6 OUT was Pinged and it NAK’d24 5C EP8PING EP8 OUT was Pinged and it NAK’d25 60 ERRLIMIT Bus errors exceeded the programmed limit26 6427 68 reserved28 6C reserved29 70 EP2ISOERR ISO EP2 OUT PID sequence error30 74 EP4ISOERR ISO EP4 OUT PID sequence error31 78 EP6ISOERR ISO EP6 OUT PID sequence error32 7C EP8ISOERR ISO EP8 OUT PID sequence errorIf Autovectoring is enabled (AV4EN = 1 in the INTSET-UP register), the FX 2LP substitutes its INT4VEC byte. Therefore, if the high byte (“page”) of a jump-table address is preloaded at location 0x0054, the automatically-inserted INT4VEC byte at 0x0055 will direct the jump to the correct address out of the 14 addresses within the page. When the ISR occurs, the FX2LP pushes the program counter onto its stack then jumps to address 0x0053, where it expects to find a “jump” instruction to the ISR Interrupt service routine.3.9Reset and Wakeup3.9.1Reset PinThe input pin, RESET#, will reset the FX2LP when asserted. This pin has hysteresis and is active LOW. When a crystal is used with the CY7C680xxA the reset period must allow for the stabilization of the crystal and the PLL. This reset period should be approximately 5 ms after VCC has reached 3.0V. If the crystal input pin is driven by a clock signal the internal PLL stabilizes in 200 µs after VCC has reached 3.0V[3]. Figure3-2 shows a power-on reset condition and a reset applied during operation. A power-on reset is defined as the time reset is asserted while power is being applied to the circuit. A powered reset is defined to be when the FX2LP has previously been powered on and operating and the RESET# pin is asserted. Cypress provides an application note which describes and recommends power on reset implementation and can be found on the Cypress web site. For more information on reset imple-mentation for the FX2 family of products visit the .Table 3-4. Individual FIFO/GPIF Interrupt SourcesPriority INT4VEC Value Source Notes 180EP2PF Endpoint 2 Programmable Flag2 84 EP4PF Endpoint 4 Programmable Flag388EP6PF Endpoint 6 Programmable Flag48C EP8PF Endpoint 8 Programmable Flag590EP2EF Endpoint 2 Empty Flag694EP4EF Endpoint 4 Empty Flag798EP6EF Endpoint 6 Empty Flag89C EP8EF Endpoint 8 Empty Flag9A0 EP2FF Endpoint 2 Full Flag10A4EP4FF Endpoint 4 Full Flag11 A8EP6FF Endpoint 6 Full Flag12AC EP8FF Endpoint 8 Full Flag13 B0GPIFDONE GPIF Operation Complete14 B4GPIFWF GPIF WaveformNote:3.If the external clock is powered at the same time as the CY7C680xxA and has a stabilization wait period, it must be added to the 200 µs.3.9.2Wakeup PinsThe 8051 puts itself and the rest of the chip into a power-down mode by setting PCON.0 = 1. This stops the oscillator and PLL. When WAKEUP is asserted by external logic, the oscil-lator restarts, after the PLL stabilizes, and then the 8051receives a wakeup interrupt. This applies whether or not FX2LP is connected to the USB.The FX2LP exits the power-down (USB suspend) state using one of the following methods:•USB bus activity (if D+/D– lines are left floating, noise on these lines may indicate activity to the FX2LP and initiate a wakeup).•External logic asserts the WAKEUP pin •External logic asserts the PA3/WU2 pin.The second wakeup pin, WU2, can also be configured as a general purpose I/O pin. This allows a simple external R-C network to be used as a periodic wakeup source. Note that WAKEUP is by default active LOW.3.10Program/Data RAM3.10.1SizeThe FX2LP has 16 KBytes of internal program/data RAM,where PSEN#/RD# signals are internally ORed to allow the 8051 to access it as both program and data memory. No USB control registers appear in this space.Two memory maps are shown in the following diagrams:Figure 3-3 Internal Code Memory, EA = 0Figure 3-4 External Code Memory, EA = 1.3.10.2Internal Code Memory, EA = 0This mode implements the internal 16-KByte block of RAM (starting at 0) as combined code and data memory. When external RAM or ROM is added, the external read and write strobes are suppressed for memory spaces that exist inside the chip. This allows the user to connect a 64-KByte memory without requiring address decodes to keep clear of internal memory spaces.Only the internal 16 KBytes and scratch pad 0.5 KBytes RAM spaces have the following access:•USB download •USB upload •Set-up data pointer •I 2C interface boot load.3.10.3External Code Memory, EA = 1The bottom 16 KBytes of program memory is external, and therefore the bottom 16 KBytes of internal RAM is accessible only as data memory.Figure 3-2. Reset Timing PlotsV IL 0V3.3V 3.0VT RESETVCCRESET#Power on ResetT RESETVCCRESET#V IL Powered Reset3.3V0VTable 3-5. Reset Timing ValuesConditionT RESET Power-on Reset with crystal 5 msPower-on Reset with external clock200 µs + Clock stability timePowered Reset 200 µsFigure 3-3. Internal Code Memory, EA = 0Inside FX2LPOutside FX2LP7.5 KBytes USB regs and 4K FIFO buffers (RD#,WR#)0.5 KBytes RAM Data (RD#,WR#)*(OK to populate data memory here—RD#/WR#strobes are not active)40 KBytes External Data Memory (RD#,WR#)(Ok to populate data memory here—RD#/WR#strobes are not active)16 KBytes RAM Code and Data(PSEN#,RD#,WR#)*48 KBytes External Code Memory (PSEN#)(OK to populate programmemory here—PSEN# strobe is not active)*SUDPTR, USB upload/download, I 2C interface boot accessFFFFE200E1FF E0003FFF0000DataCodeFigure 3-4. External Code Memory, EA = 1Inside FX2LPOutside FX2LP7.5 KBytes USB regs and 4K FIFO buffers (RD#,WR#)0.5 KBytes RAM Data (RD#,WR#)*(OK to populatedata memory here—RD#/WR#strobes are not active)40 KBytes External Data Memory (RD#,WR#)(Ok to populate data memory here—RD#/WR#strobes are not active)16 KBytes RAM Data(RD#,WR#)*64 KBytes External Code Memory (PSEN#)*SUDPTR, USB upload/download, I 2C interface boot accessFFFFE200E1FFE0003FFF0000DataCode3.11Register Addresses3.12Endpoint RAM3.12.1Size•3× 64 bytes (Endpoints 0 and 1)•8 × 512 bytes (Endpoints 2, 4, 6, 8)3.12.2Organization•EP0•Bidirectional endpoint zero, 64-byte buffer •EP1IN, EP1OUT•64-byte buffers, bulk or interrupt •EP2,4,6,8•Eight 512-byte buffers, bulk, interrupt, or isochronous. EP4 and EP8 can be double buffered, while EP2 and 6 can be either double, triple, or quad buffered. For high-speed end-point configuration options, see Figure 3-5.3.12.3Set-up Data BufferA separate 8-byte buffer at 0xE6B8-0xE6BF holds the Set-up data from a CONTROL transfer.3.12.4Endpoint Configurations (High-speed Mode)Endpoints 0 and 1 are the same for every configuration.Endpoint 0 is the only CONTROL endpoint, and endpoint 1 can be either BULK or INTERRUPT. The endpoint buffers can be configured in any 1 of the 12 configurations shown in the vertical columns. When operating in full-speed BULK mode only the first 64 bytes of each buffer are used. For example in high-speed, the max packet size is 512 bytes but in full-speed it is 64 bytes. Even though a buffer is configured to be a 512byte buffer, in full-speed only the first 64 bytes are used. The unused endpoint buffer space is not available for other opera-tions. An example endpoint configuration would be:FFFFE800E7BF E740E73F E700E6FF E500E4FF E480E47F E400E200E1FFE000E3FF EFFF2 KBytes RESERVED64 Bytes EP0 IN/OUT 64 Bytes RESERVED 8051 Addressable RegistersReserved (128)128 bytes GPIF Waveforms512 bytes 8051 xdata RAMF000(512)Reserved (512)E78064 Bytes EP1OUT E77F 64 Bytes EP1IN E7FF E7C0 4 KBytes EP2-EP8buffers(8 x 512)EP2–1024 double buffered; EP6–512 quad buffered (column 8).3.12.5Default Full-Speed Alternate Settings3.12.6Default High-Speed Alternate Settings6464645125121024102410241024102410241024512512512512512512512512512512EP0 IN&OUTEP1 IN EP1 OUTFigure 3-5. Endpoint Configuration1024102410245125125125125125125125125125125125125125125125125125125125125125125125125125125125125125121024102410241024102410245125121024102451251251251251251251251210241024512512512512512512646464646464646464646464646464646464646464646464646464646464646464123456789101112Table 3-6. Default Full-Speed Alternate Settings [4, 5]Alternate Setting 0123ep064646464ep1out 064 bulk 64 int 64 int ep1in 064 bulk 64 int 64 int ep2064 bulk out (2×)64 int out (2×)64 iso out (2×)ep4064 bulk out (2×)64 bulk out (2×)64 bulk out (2×)ep6064 bulk in (2×)64 int in (2×)64 iso in (2×)ep8064 bulk in (2×)64 bulk in (2×)64 bulk in (2×)Notes:4.“0” means “not implemented.”5.“2×” means “double buffered.”6.Even though these buffers are 64 bytes, they are reported as 512 for USB 2.0 compliance. The user must never transfer packets larger than 64 bytes to EP1.Table 3-7. Default High-Speed Alternate Settings [4, 5]Alternate Setting 0123ep064646464ep1out 0512 bulk [6]64 int 64 int ep1in 0512 bulk [6]64 int64 intep20512 bulk out (2×)512 int out (2×)512 iso out (2×)ep40512 bulk out (2×)512 bulk out (2×)512 bulk out (2×)ep60512 bulk in (2×)512 int in (2×)512 iso in (2×)ep80512 bulk in (2×)512 bulk in (2×)512 bulk in (2×)3.13External FIFO Interface3.13.1ArchitectureThe FX2LP slave FIFO architecture has eight 512-byte blocks in the endpoint RAM that directly serve as FIFO memories, and are controlled by FIFO control signals (such as IFCLK, SLCS#, SLRD, SLWR, SLOE, PKTEND, and flags).In operation, some of the eight RAM blocks fill or empty from the SIE, while the others are connected to the I/O transfer logic. The transfer logic takes two forms, the GPIF for internally generated control signals, or the slave FIFO interface for externally controlled transfers.3.13.2Master/Slave Control SignalsThe FX2LP endpoint FIFOS are implemented as eight physi-cally distinct 256x16 RAM blocks. The 8051/SIE can switch any of the RAM blocks between two domains, the USB (SIE) domain and the 8051-I/O Unit domain. This switching is done virtually instantaneously, giving essentially zero transfer time between “USB FIFOS” and “Slave FIFOS.” Since they are physically the same memory, no bytes are actually transferred between buffers.At any given time, some RAM blocks are filling/emptying with USB data under SIE control, while other RAM blocks are available to the 8051 and/or the I/O control unit. The RAM blocks operate as single-port in the USB domain, and dual-port in the 8051-I/O domain. The blocks can be configured as single, double, triple, or quad buffered as previ-ously shown.The I/O control unit implements either an internal-master (M for master) or external-master (S for Slave) interface.In Master (M) mode, the GPIF internally controls FIFOADR[1..0] to select a FIFO. The RDY pins (two in the 56-pin package, six in the 100-pin and 128-pin packages) can be used as flag inputs from an external FIFO or other logic if desired. The GPIF can be run from either an internally derived clock or externally supplied clock (IFCLK), at a rate that transfers data up to 96 Megabytes/s (48-MHz IFCLK with 16-bit interface).In Slave (S) mode, the FX2LP accepts either an internally derived clock or externally supplied clock (IFCLK, max. frequency 48 MHz) and SLCS#, SLRD, SLWR, SLOE, PKTEND signals from external logic. When using an external IFCLK, the external clock must be present before switching to the external clock with the IFCLKSRC bit. Each endpoint can individually be selected for byte or word operation by an internal configuration bit, and a Slave FIFO Output Enable signal SLOE enables data of the selected width. External logic must insure that the output enable signal is inactive when writing data to a slave FIFO. The slave interface can also operate asynchronously, where the SLRD and SLWR signals act directly as strobes, rather than a clock qualifier as in synchronous mode. The signals SLRD, SLWR, SLOE and PKTEND are gated by the signal SLCS#.3.13.3GPIF and FIFO Clock RatesAn 8051 register bit selects one of two frequencies for the internally supplied interface clock: 30 MHz and 48 MHz. Alter-natively, an externally supplied clock of 5 MHz–48 MHz feeding the IFCLK pin can be used as the interface clock. IFCLK can be configured to function as an output clock when the GPIF and FIFOs are internally clocked. An output enable bit in the IFCONFIG register turns this clock output off, if desired. Another bit within the IFCONFIG register will invert the IFCLK signal whether internally or externally sourced. 3.14GPIFThe GPIF is a flexible 8- or 16-bit parallel interface driven by a user-programmable finite state machine. It allows the CY7C68013A/15A to perform local bus mastering, and can implement a wide variety of protocols such as ATA interface, printer parallel port, and Utopia.The GPIF has six programmable control outputs (CTL), nine address outputs (GPIFADRx), and six general-purpose ready inputs (RDY). The data bus width can be 8 or 16 bits. Each GPIF vector defines the state of the control outputs, and deter-mines what state a ready input (or multiple inputs) must be before proceeding. The GPIF vector can be programmed to advance a FIFO to the next data value, advance an address, etc. A sequence of the GPIF vectors make up a single waveform that will be executed to perform the desired data move between the FX2LP and the external device.3.14.1Six Control OUT SignalsThe 100- and 128-pin packages bring out all six Control Output pins (CTL0-CTL5). The 8051 programs the GPIF unit to define the CTL waveforms. The 56-pin package brings out three of these signals, CTL0–CTL2. CTLx waveform edges can be programmed to make transitions as fast as once per clock (20.8 ns using a 48-MHz clock).3.14.2Six Ready IN SignalsThe 100- and 128-pin packages bring out all six Ready inputs (RDY0–RDY5). The 8051 programs the GPIF unit to test the RDY pins for GPIF branching. The 56-pin package brings out two of these signals, RDY0–1.3.14.3Nine GPIF Address OUT SignalsNine GPIF address lines are available in the 100- and 128-pin packages, GPIFADR[8..0]. The GPIF address lines allow indexing through up to a 512-byte block of RAM. If more address lines are needed, I/O port pins can be used.3.14.4Long Transfer ModeIn master mode, the 8051 appropriately sets GPIF transaction count registers (GPIFTCB3, GPIFTCB2, GPIFTCB1, or GPIFTCB0) for unattended transfers of up to 232 transactions. The GPIF automatically throttles data flow to prevent under or overflow until the full number of requested transactions complete. The GPIF decrements the value in these registers to represent the current status of the transaction.。

AN001(1)6803角度方案

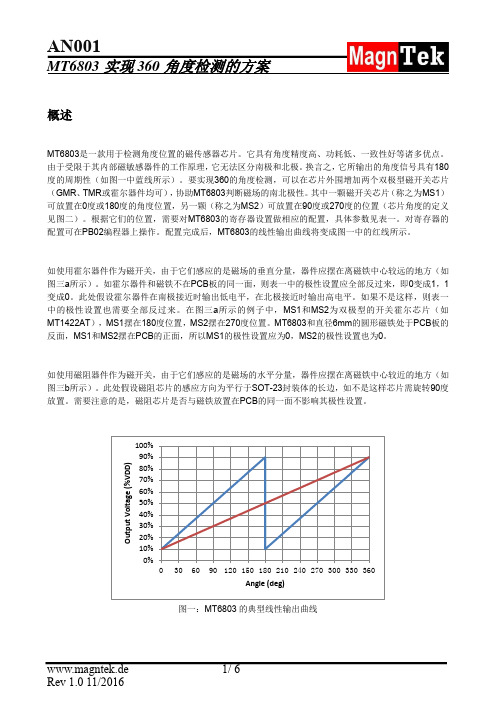

概述MT6803是一款用于检测角度位置的磁传感器芯片。

它具有角度精度高、功耗低、一致性好等诸多优点。

由于受限于其内部磁敏感器件的工作原理,它无法区分南极和北极。

换言之,它所输出的角度信号具有180度的周期性(如图一中蓝线所示)。

要实现360的角度检测,可以在芯片外围增加两个双极型磁开关芯片(GMR、TMR或霍尔器件均可),协助MT6803判断磁场的南北极性。

其中一颗磁开关芯片(称之为MS1)可放置在0度或180度的角度位置,另一颗(称之为MS2)可放置在90度或270度的位置(芯片角度的定义见图二)。

根据它们的位置,需要对MT6803的寄存器设置做相应的配置,具体参数见表一。

对寄存器的配置可在PB02编程器上操作。

配置完成后,MT6803的线性输出曲线将变成图一中的红线所示。

如使用霍尔器件作为磁开关,由于它们感应的是磁场的垂直分量,器件应摆在离磁铁中心较远的地方(如图三a所示)。

如霍尔器件和磁铁不在PCB板的同一面,则表一中的极性设置应全部反过来,即0变成1,1变成0。

此处假设霍尔器件在南极接近时输出低电平,在北极接近时输出高电平。

如果不是这样,则表一中的极性设置也需要全部反过来。

在图三a所示的例子中,MS1和MS2为双极型的开关霍尔芯片(如MT1422AT),MS1摆在180度位置,MS2摆在270度位置。

MT6803和直径6mm的圆形磁铁处于PCB板的反面,MS1和MS2摆在PCB的正面,所以MS1的极性设置应为0,MS2的极性设置也为0。

如使用磁阻器件作为磁开关,由于它们感应的是磁场的水平分量,器件应摆在离磁铁中心较近的地方(如图三b所示)。

此处假设磁阻芯片的感应方向为平行于SOT-23封装体的长边,如不是这样芯片需旋转90度放置。

需要注意的是,磁阻芯片是否与磁铁放置在PCB的同一面不影响其极性设置。

图一:MT6803的典型线性输出曲线α图二:芯片的敏感区域标示,各个角度位置的定义表一:(a)(b)图三:一种可能的放置情况(MT6803和磁铁在PCB板的背面,磁开关芯片在PCB板的正面)(a)用霍尔器件的情况;(b)用磁阻器件的情况。

医疗器械常用词汇中英文对照

55

680707

Ⅱ类

胸腔心血管外科用吸引器 thoracic cavity cardiovascular surgical aspirator

56 6808

腹部外科手术器械 abdominal surgical operation instruments

57

680802

Ⅰ类

腹部外科用剪 abdominal surgical scissors

2

680101

Ⅱ类

医用缝合针(不带线) medical suture needle (without thread)

3

680102

Ⅰ类

基础外科用刀 basic surgical knife

4

680103

Ⅰ类

基础外科用剪 basic surgical scissors

5

680104

Ⅰ类

基础外科用钳 basic surgical clamp

医疗器械产品分类目 Medical Equipment Classific

监管类

序 号 Ser ial NO.

分类 编码 Class ifica tion Code

别 Superv ision

& Admini strati

on

Level

名称 Name

1 6801

基础外科手术器械 basic surgical operation instruments

83

681202

Ⅰ类

妇产科用剪 obsteric and gynecologic scissors

84

681203

Ⅰ类

妇产科用钳 obsteric and gynecologic forceps

中文汉字电报码对照表

中文汉字电报码对照表(二) H-Q哈0761 骸7546 孩1326海3189 氦8640 亥0075 害1364 骇7480 酣6799 憨2003 邯6725韩7281 含0698 涵3211 寒1383 函0428 喊0815 罕4988 翰5060撼2338 捍2194 旱2487 憾2013 悍1880 焊3549 汗3063 汉3352夯1137 杭2635 航5300 壕1091 嚎0866 豪6275 毫3032 郝6787好1170 耗5088 号5714 浩3185 呵0725 喝0824 菏3235 核2702禾4421 和0735 何0149 合0678 盒4139 貉6288 阂7039 河3109涸3212 赫6378 褐5964 鹤7729 贺6320 嘿0884 黑7815 痕4024很1771 狠3703 恨1868 哼0774 亨0077 横2897 衡5899 恒1854轰6575 哄0758 烘3530 虹5725 鸿7703 洪3163 宏1347 弘1738红4767 喉0814 侯0186 猴3729 吼0709 厚0624 候0230 后0683呼0729 乎0039 忽1824 瑚3840 壶1106 葫5519 胡5170 蝴5814狐3698 糊4739 湖3275 弧1721 虎5706 唬0801 护6233 互0062沪3337 户2073 花5363 哗0873 华5478 猾3736 滑3323 画3937画3973 划0439 化0553 话6114 槐2849 徊1773 怀2037 淮3232坏0975 欢2970 环3883 桓2719 还6703 缓4883 换2255 患1891唤0822 痪4050 豢6273 焕3562 涣3251 宦1360 幻1634 荒5435慌1967 黄7806 磺4337 蝗5794 簧4679 皇4106 凰0420 惶1929煌3552 晃2515 幌1610 恍1857 谎6192 灰3500 挥2264 辉6540徽1798 恢1863 蛔5784 回0932 毁3014 悔1882 慧1979 卉0583惠1920 晦2526 贿6325 秽4486 会2585 烩2476 汇0565 讳6172诲6140 绘4940 荤5526 昏2495 婚1241 魂3268 浑7609 混3236豁6255 活3172 伙0129 火3499 获3752 或2057 惑1910 霍7202货6303 祸4393 击2345 圾0969 基1015 机2623 畸3982 稽4472积4480 箕4614 肌5133 饥7382 迹6619 激3423 讥6217 鸡7741姬1213 绩4921 缉4874 吉0679 极2817 棘2765 辑6549 籍4694集7162 及0644 急1838 疾4014 汲0378 汲3078 即0613 嫉1271级4878 级4787 挤2357 几0415 脊5182 己1569 蓟5636 技2111冀0370 季1323 伎0125 祭4385 剂0495 悸1900 济3444 寄1376寂1374 计6060 记6068 既2478 忌1803 际7139 妓1178 继4949纪4764 嘉0857 枷2666 夹1140 佳0163 家1367 加0502 荚5453颊7335 贾6328 甲3946 钾6905 假0250 稼4471 价0116 架2665驾7468 嫁1268 歼3005 监4148 坚1017 尖1423 笺4608 间7035煎3553 兼0369 肩5144 艰5329 奸1169 缄4873 茧4942 检2914柬2687 碱4354 碱7769 碱8969 拣2245 简4675 俭0313 剪0477减8096 荐5433 槛2920 鉴7003 践6432 贱6345 见6015 键6943箭4628 件0115 健0256 舰5324 剑0494 饯7415 渐3362 溅3457涧3386 建1696 僵0304 姜1302 姜1203 将1412 浆3364 江3068疆3984 蒋5592 桨2862 奖1162 讲6199 匠0561 酱6830 降7100蕉5604 椒2786 礁4339 焦3542 胶5231 交0074 郊6738 浇3398骄7524 娇1293 嚼0920 搅2383 铰6890 矫4255 侥0299 脚5183狡3701 角6037 饺7398 缴4945 绞4819 剿0485 剿8464 教2403酵6806 轿6569 较6525 叫0663 窖4512 揭2263 接2234 皆4105秸4447 街5894 阶7132 截2066 劫0506 节4634 桔2720 杰0267杰2638 捷2212 睫4208 竭4550 洁3381 结4814 解6043 姐1195戒2054 藉5659 芥5354 界3954 借0234 介0094 疥4003 诫6135届1447 巾1577 筋4585 斤2443 金6855 今0093 津3160 襟5992襟5995 紧4868 锦6930 仅0284 谨6310 谨6210 进6651 靳7246晋2516 禁4391 近6602 烬3612 浸3190 尽4147 劲0513 荆5427兢0352 茎5449 睛4200 晶2533 鲸7650 京0079 惊7528 精4737粳4734 经4842 井0064 警6224 警6226 景2529 颈7338 静7234境1064 敬2417 镜6975 径1777 痉3997 靖7231 竟4552 竞4544净0403 炯3518 窘4515 揪2262 究4496 纠4763 玖3773 韭7295久0036 灸3502 九9909 九9709 九9809 九0046 酒6794 厩1673救2405 旧5283 臼5273 舅5279 咎0736 就1432 疚3998 鞠7263拘2153 狙3700 疽4013 居1446 驹7467 菊5468 局1444 咀0731矩4251 举5282 沮3107 聚5112 拒2147 据2207 巨1565 具0367距6415 踞6436 锯6920 俱0215 句0658 惧2040 炬3515 剧0489捐2196 鹃7710 娟1227 倦0239 眷4187 卷0608 绢4831 撅2313攫2384 抉2115 掘2228 倔8056 爵3635 觉6030 决0414 决6076绝4815 均0971 菌5497 钧6874 军6511 君0689 峻1498 俊0193竣4546 浚3182 郡6746 骏7486 喀0807 咖0739 卡0595 咯0748开7030 揩2261 楷2818 凯0418 慨1980 刊0436 堪1030 勘0522坎0974 砍4266 看4170 康1660 慷1988 糠4749 扛2095 抗2123亢0073 炕3510 考5072 拷2166 烤3628 靠7237 坷0985 苛5381柯2688 棵2644 磕4326 颗7341 科4430 壳8199 咳0750 可0668渴3265 克0344 刻0466 客1356 课6143 肯5146 啃8186 垦1083恳2017 坑0977 吭0699 空4500 恐1858 孔1313 控2235 抠2305口0656 扣2099 寇1379 枯2661 哭0770 窟4516 苦5388 酷6807库1655 裤5974 夸1139 垮1006 挎2175 跨6421 胯5169 块1040筷4599 侩0312 快1816 宽1401 款2949 匡0562 筐4590 狂3693框2713 矿4349 眶4186 旷2568 况0400 亏5719 盔4140 岿8354窥4529 葵5525 奎1145 魁7608 傀0264 馈7432 愧1951 溃3391坤0981 昆2492 捆2190 困0938 括2161 扩2368 廓1674 阔7059垃0998 拉2139 喇0812 蜡5779 腊5198 辣6584 啦0784 莱5490来0171 赖6351 蓝5663 婪1245 栏2936 拦2374 篮4691 阑7061兰5695 澜3482 谰9301 揽2385 览6031 懒2036 缆4968 烂3620滥3448 琅3809 榔2826 狼3708 廊1671 郎6745 朗2597 浪3186捞2318 劳0525 牢3666 老5071 佬0097 姥1209 酪6803 烙3529涝3399 勒0519 乐2867 雷7191 镭7012 蕾5628 磊4320 累4797儡8079 垒1093 擂2341 肋5132 类7352 泪3223 棱2789 楞2807冷0397 厘0622 梨2746 犁3680 黎7812 篱4713 狸3706 离7180离4418 漓3347 理3810 李2621 里6849 鲤7642 礼4409 莉5461荔5408 吏0684 栗2698 丽7787 厉0632 励0536 砾4351 历2980利0448 傈0269 例0173 俐0196 痢4031 立4539 粒4721 沥3468隶7152 力0500 璃3863 哩0769 哩5070 俩0224 联5114 莲5571连6647 镰6991 廉1670 怜1995 涟3353 帘1588 敛2425 脸5245链6969 恋2043 炼3550 练4886 粮9037 凉0404 凉3213 梁2733粱4731 良5328 两0357 辆6538 量6852 晾8512 亮0081 谅6156撩2316 聊5108 僚0297 疗4070 燎3598 寥1394 辽6697 潦3388了0055 撂2297 镣9507 廖1675 料2436 列0441 裂5933 烈3525劣0503 猎3756 琳3829 林2651 磷4340 霖7207 临5259 邻6775鳞7673 淋3218 凛0412 赁6324 吝0690 拎2146 玲3781 菱5480零7190 龄7881 铃6875 伶0134 羚5024 凌0407 灵7227 陵7117岭1545 领7325 另0659 令0109 溜3296 琉3812 榴2839 硫4288馏5130 留3966 刘0491 瘤4058 流3177 柳2692 六9706 六0362六9906 六9806 龙7893 聋5122 咙0918 笼4705 窿9002 隆7127垄1096 拢2379 陇7150 楼2869 娄1236 搂2299 篓4664 漏3345陋7097 芦5684 卢4151 颅7361 庐1687 炉3619 掳2342 卤7767虏5712 鲁7627 麓7785 碌4294 露7216 路6424 赂6323 鹿7773潞3406 禄4389 录6922 陆7120 戮2068 驴7533 吕0712 铝6986侣0188 旅2464 履1462 屡1459 缕4917 虑1982 氯3048 律1774率3764 滤3459 绿4845 峦1551 挛2381 孪1334 滦3497 卵0607乱0052 掠2230 略3970 抡2241 轮6544 伦0243 仑0178 沦3229纶4858 论6158 萝5700 螺5828 罗5012 逻6709 锣7017 箩4712骡7512 裸4387 裸5953 落5507 洛3157 骆7482 络4820 妈1265麻4034 麻7802 玛3854 码4316 蚂5818 马7456 骂5006 嘛0859吗0834 埋1003 买6314 麦7796 卖6344 迈6701 脉9115 瞒4221馒7429 蛮5875 满3341 蔓5585 曼2581 慢1976 漫3355 谩6211芒5345 茫5413 盲4159 氓3047 忙1811 莽5462 猫3728 茅5403锚6931 毛3029 矛4243 铆9450 卯0602 茂5399 冒0379 帽1604貌6290 贸6319 么8010 玫3780 枚2653 梅2734 酶5326 霉7199煤3561 没3093 眉4168 媒1252 镁9485 每3020 美5019 昧2505寐1382 妹1188 媚1253 门7591 门7024 闷1899 们0226 萌5492蒙5536 檬2916 盟4145 锰7021 猛3718 梦1125 孟1322 眯4183醚5721 靡7238 糜4745 迷6617 谜6193 弥1736 米4717 秘4434觅6017 泌3125 蜜5778 密1378 幂0389 棉2758 棉7258 眠4177绵4875 冕0380 免0346 勉0517 娩1231 缅4884 面7240 苗5379描2249 瞄4178 藐5662 秒4432 渺3267 庙1680 妙1181 蔑5583灭3319 民3046 抿2129 皿4129 敏2404 悯2006 闽7044 明2494螟5820 鸣7686 铭6900 名0682 命0730 谬6208 摸2307 摹2308蘑5704 模2875 膜5229 磨4333 摩2302 魔7621 抹2130 末2608莫5459 墨1075 默7817 沫3106 漠3351 寞1389 陌7099 谋6180牟3664 某2673 拇2136 牡3665 亩3965 姆1191 母3018 墓1045暮2550 幕1612 募0927 慕1970 木2606 目4158 睦4207 牧3668穆4476 拿2169 哪0763 呐0704 钠6871 那6719 娜1226 纳4780氖6036 乃0035 奶1168 耐5082 奈1143 南0589 男3948 难7181囊0926 挠2321 脑5207 恼1925 闹9527 闹7593 淖8681 呢0716馁7407 内0355 嫩1282 能5174 妮1200 霓7206 倪0242 泥3136尼1441 拟2362 你0132 匿0574 腻5232 逆6627 溺3312 蔫5576拈2138 年1628 碾4317 撵2365 捻2214 念1819 娘1224 酿6840鸟7680 尿1443 捏2250 聂5119 孽5642 啮0909 镊7015 镊7105镍6996 涅3206 您1849 柠2899 狞3761 狞3461 凝0413 宁1337拧2349 泞3438 牛3662 扭2100 钮6873 纽4781 脓5240 浓3426农3593 农6593 弄1702 奴1167 努0505 怒1829 女1166 暖2541虐5707 疟4061 挪2180 懦2032 糯4754 诺6179 欧2962 鸥7743殴3016 藕5665 呕0868 偶0260 沤3371 爬3632 帕1584 怕1830琶3831 拍2143 排2226 牌3654 徘1780 湃3269 派3175 攀2372潘3382 盘4149 磐4323 盼4162 畔3961 判0445 叛0651 乓8004庞1690 旁2460 耪6590 胖5160 抛2141 咆0733 刨0442 炮3517袍5916 跑6410 泡3133 胚5162 培1014 裴5952 赔6341 陪7111配6792 佩0160 沛3099 喷0899 盆4133 砰4280 抨2125 烹3534澎3403 彭1756 蓬5570 棚2766 硼4296 篷4659 膨5191 朋2590鹏7720 捧2201 碰4314 坯0999 砒4268 霹7219 批2106 披2126劈0490 琵3832 毗3026 啤0802 脾5196 疲4006 皮4122 匹0572痞4028 僻0306 屁1445 譬6229 篇4638 偏0252 片3651 骗7499飘7373 漂3343 瓢3903 票4384 撇2317 瞥4224 拼2178 频7340贫6302 品0756 聘5111 乒8003 坪0988 苹5393 萍5493 平1627凭0417 瓶3910 评6097 屏1456 坡0980 泼3380 颇7324 婆1237破4275 魄7611 迫6612 粕4722 剖0472 扑2090 铺6917 仆0091莆5455 葡5515 菩5476 蒲5543 埔1033 朴2613 圃0944 普2528浦3184 谱6225 曝2566 瀑3462 期2601 欺2952 栖2722 戚2058妻1189 七9707 七9807 七9907 七0003 凄0401 漆3344 柒2675其0366 棋2759 奇1142 歧2978 畦3971 崎1505 脐5247 齐7871旗2475 祈4362 祁4359 骑7494 起6386 岂6259 乞0047 企0120启0796 契1148 砌4265 器0892 气3049 迄6597 弃2757 汽3086泣3135 讫6066 掐2225 恰1874 洽3174 牵3677 扦8422 钎7244铅6884 千0578 迁6692 签4687 仟0107 谦6197 乾0051 黔7816钱6929 钳6883 前0467 潜3383 遣6680 浅3239 谴6232 堑1058嵌1523 欠2944 歉2959 枪2847 呛0850 腔5204 羌5018 墙8255蔷5638 强1730 抢2293 橇8587 锹6942 敲2418 悄1877 桥2890瞧4225 乔0821 乔0829 侨0294 巧1564 撬2334 翘5062 峭1495俏0195 窍4534 切0434 茄5401 且0011 怯1845 窃4537 钦2953侵0187 亲6024 秦4440 琴3830 勤0530 芹5367 擒2350 禽4419寝1392 沁3084 青7230 轻6535 氢8641 倾0282 卿0615 清3237擎2348 晴2532 氰8642 情1906 顷7308 请6153 庆1987 琼8825穷4522 秋4428 丘8002 邱6726 球3808 求3061 囚0933 酋6790泅3120 趋6395 区0575 蛆5747 曲2575 躯6504 屈1448 驱7517渠3255 取0648 娶1235 龋7889 趣6393 去0637 圈0946 颧7362权2938 醛7379 泉3123 全0356 痊4019 拳2164 犬3689 券0457__________________________________________________劝0538 缺4972 炔7448 瘸4063 却0606 鹊7717 榷2854 确4292雀7158 裙5942 群5028__________________________________________________。

6803_6806_6810宣传彩页17

大型网络骨干万兆交换机--BDCOM S6803/6806/6810交换机产品概述BDCOM S6810机箱式硬件三层交换机是上海博达数据通信有限公司针对大型网络汇聚、中小型网络核心等情况推出的高性能的机箱式L2/L3/L4交换机。

BDCOM S/6810完全为自主研发产品,采用全模块化,具有高密度端口,4.8T的背板带宽,可根据用户的需求灵活配置,灵活构建弹性可扩展的网络。

BDCOM S6810交换机产品提供强大的交换和路由功能,可与博达公司各系列交换机配合,为用户提供完整的端到端解决方案,是大型网络核心骨干交换机的理想选择。

适用范围∙网络的核心∙大型网络汇聚∙高性能网络交换环境主要特性高密度、接口类型丰富的业务模块BDCOM S6810系列交换机提供高密度端口的接入能力,整机最多支持384千兆端口、64个万兆端。

交换容量,全线速交换性能BDCOM S6810万兆交换机最高具有4.8T的背板带宽,为所有的端口提供非阻塞线速转发性能。

强大的处理能力是构建可靠、稳定、高速的IP网络平台的重要保障。

BDCOM S6810交换机硬件支持多层线速交换,能够识别、处理四层以上的应用业务流,所有端口都具有单独的数据包过滤、区分不同应用流,并根据不同的流进行不同的管理和控制。

BDCOM S6800系列硬件芯片支持IPv6协议,有利于将来进行平滑的网络升级。

功能丰富的安全特性BDCOM S6800系列提供了完整的ACL支持,除通常的标准ACL以及扩展ALC,还提供基于时间的ACL,使得控制策略非常丰富和灵活。

DAP(DOS攻击防御)的功能,使网络免受ICMP、SYN、UDP等病毒扫描攻击、更加安全可靠。

支持基于用户的接入控制协议802.1x,提供比传统接入控制方式更为有效的用户端口控制能力,端口MAC地址限定功能可以对端口接入的主机数目进行限制。

丰富的QoS策略支持802.1p、WRR、RED、 DiffServ等优先级处理和调度算法,可以对不同优先级业务进行调度及良好的网络拥塞控制策略,支持基于L2/L3/L4的流分类,丰富的Qos策略是构建高质量NGN(下一代网络)的基础。

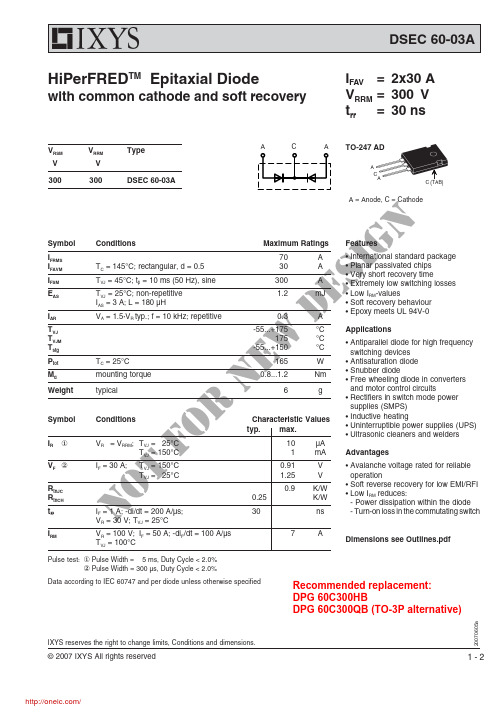

DSEC60-03A;中文规格书,Datasheet资料

Conditions

or VR = VRRM; TVJ = 25°C TVJ = 150°C

f IF = 30 A; TVJ = 150°C

TVJ = 25°C

ot IF = 1 A; -di/dt = 200 A/µs; NVR = 30 V; TVJ = 25°C

10

µA

1 mA Advantages

0.91

V

• Avalanche voltage rated for reliable

1.25

V

operation

0.25

0.9

K/W K/W

• Soft reverse recovery for low EMI/RFI • Low IRM reduces:

- Power dissipation within the diode

.+175

°C

175

°C

-55...+150

°C

w165

W

e0.8...1.2

Nm

n6

g

Applications

• Antiparallel diode for high frequency switching devices

• Antisaturation diode • Snubber diode • Free wheeling diode in converters

DSEC 60-03A

HiPerFREDTM Epitaxial Diode

with common cathode and soft recovery

IFAV = 2x30 A VRRM = 300 V trr = 30 ns

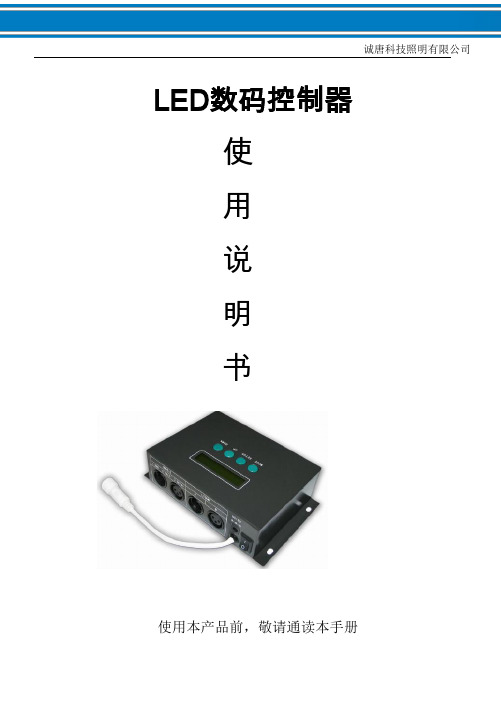

6803液晶LED数码控制器

一、 性能参数

型号 工作电压 消耗功率 控制方式 输出端口 通信接口 变化程序 控制数量 外形尺寸 包装尺寸

CL-6803 DC:9V-12V ≤1W TTL signal 2路(可扩展至8路) DMX512 30种变化程序 16D*200TQY=3200个象素/路 L190×W120×H50(mm) L280×W150×H70(mm)

诚唐科技照明有限公司

LED数码控制器

使 用 说 明 书

使用本产品前,敬请通读本手册

使用说明

感谢您选择我公司的CL-6803 液晶LED数码控制器。在拆开包装使用前, 请查实产品有没有存在运输过程所造成的损坏,如果出现损坏,请立即通知你的 供应商并不要使用产品。

售后服务

从购买产品时间起,1年时间内按操作说明正常使用出现质量问题,本公司 免费提供维修或更换服务。 由于不遵循此说明书说明和下列条款而致使产品损害的,供应商不负责由此引起 的任何问题和缺陷,即使在质保期内,由客户承担维修费用。

1.误操作造成的损坏,如没按照操作说明的误操作。 2.私自撤除、维修、修改电路、不正确连接以及私自撤换芯片造成的损坏。 3.购买后由于运输、震荡、摔地、进水造成的损坏。 4.地震、火灾、洪灾、雷击自然灾害、环境污染和不正常电压造成的损坏。 5.由于疏忽或不恰当如储存在高温和潮湿环境,离有害化学物质附近等不恰 当维护造成的损坏。 6.产品已更新换代。

由 UP,DOWN来调整(1-512),预置起始地址为1。每个控制器占用4个

DMX512地址。

1、第一路DMX512数据:控制30种状态(30为自动模式,调用本机设置的速度

和运行循环次数)。当数据小于248为控制模式,当大于248-256为调光模式。

2、 第二路DMX512数据:控制速度(DMX512模式的30自动模式下无效),调光 模式R的亮度数据数据。 3、第三路DMX512数据:控制整体亮度(5线控制线有效),调光模式G 的亮度 数据。

AO6801A;中文规格书,Datasheet资料

G1 S2 G2 Pin1

1 2 3

6 5 4

D1 S1 D2 G1 S1 G2 S2

Absolute Maximum Ratings TA=25° C unless otherwise noted Parameter Symbol Drain-Source Voltage VDS Gate-Source Voltage Continuous Drain Current Pulsed Drain Current Power Dissipation

0 0 1 2 3 4 -VGS(Volts) Figure 2: Transfer Characteristics (Note E)

2 1.8 1.6 1.4 1.2 1 0.8 0 25 50 75 100 125 150 175 VGS=-4.5V ID=-2A VGS=-10V ID=-2.3A

THIS PRODUCT HAS BEEN DESIGNED AND QUALIFIED FOR THE CONSUMER MARKET. APPLICATIONS OR USES AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS ARE NOT AUTHORIZED. AOS DOES NOT ASSUME ANY LIABILITY ARISING OUT OF SUCH APPLICATIONS OR USES OF ITS PRODUCTS. AOS RESERVES THE RIGHT TO IMPROVE PRODUCT DESIGN, FUNCTIONS AND RELIABILITY WITHOUT NOTICE.

STATIC PARAMETERS Drain-Source Breakdown Voltage BVDSS IDSS IGSS VGS(th) ID(ON) Zero Gate Voltage Drain Current Gate-Body leakage current Gate Threshold Voltage On state drain current

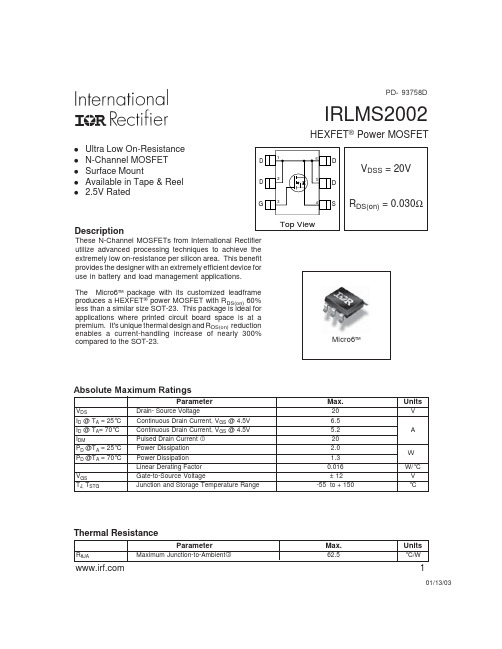

IRLMS2002中文资料

PD- 93758D

IRLMS2002

HEXFET® Power MOSFET

l l l l l

Ultra Low On-Resistance N-Channel MOSFET Surface Mount Available in Tape & Reel 2.5V Rated

10

ID = 6.5A 5.3A VDS = 10V

8

C, Capacitance (pF)

Ciss

1200

6

800

4

400

2

0 1

Coss Crss

10 100

0 0 4 8 12 16 20 24

VDS , Drain-to-Source Voltage (V)

QG , Total Gate Charge (nC)

2

元器件交易网

IRLMS2002

100

VGS 7.50V 5.00V 4.00V 3.50V 3.00V 2.50V 2.00V BOTTOM 1.50V TOP

100

I D , Drain-to-Source Current (A)

I D , Drain-to-Source Current (A)

Max.

20 6.5 5.2 20 2.0 1.3 0.016 ± 12 -55 to + 150

Units

V A W W/°C V °C

Thermal Resistance

Parameter

RθJA Maximum Junction-to-Ambient

Max.

62.5

UnSource Voltage (V)

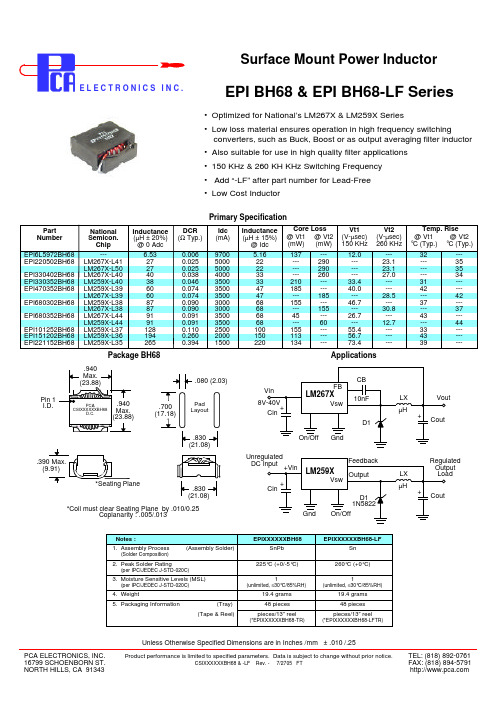

EPI680302BH68中文资料

10nF

LX µH +

Vout Cout

D1 .830 (21.08) On/Off Unregulated DC Input Gnd Feedback +Vin

.390 Max. (9.91) *Seating Plane .830 (21.08)

LM259X

Vsw

Output D1 1N5822

(per IPC/JEDEC J-STD-020C)

3. Moisture Sensitive Levels (MSL)

(per IPC/JEDEC J-STD-020C)

1

1

4. Weight 5. Packaging Information (Tray) (Tape & Reel)

19.4 grams 48 pieces pieces/13” reel

(*EPIXXXXXXBH68-TR)

19.4 grams 48 pieces pieces/13” reel

(*EPIXXXXXXBH68-LFTR)

Unless Otherwise Specified Dimensions are in Inches /mm ± .010 /.25 PCA ELECTRONICS, INC. 16799 SCHOENBORN ST. NORTH HILLS, CA 91343

Product performaБайду номын сангаасce is limited to specified parameters. Data is subject to change without prior notice.

CSIXXXXXXBH68 & -LF Rev. 7/2705 FT

5833中文资料

5833中⽂资料Designed to reduce logic supply current, chip size, and system cost, the UCN5833A/EP integrated circuits offer high-speed operation for thermal printers. These devices can also be used to drive multi-plexed LED displays or incandescent lamps within their 125 mA peak output current rating. The combination of bipolar and MOS technolo-gies gives BiMOS II smart power ICs an interface flexibility beyond the reach of standard buffers and power driver circuits.These 32-bit drivers have bipolar open-collector npn Darlington outputs, a CMOS data latch for each of the drivers, a 32-bit CMOS shift register, and CMOS control circuitry. The high-speed CMOS shift registers and latches allow operation with most microprocessor-based systems at data input rates above 3.3 MHz. Use of these drivers with TTL may require input pull-up resistors to ensure an input logic high.The UCN5833A is supplied in a 40-pin dual in-line plastic package with 0.600" (15.24 mm) row spacing. At an ambient temperature of +75°C, all outputs of the DlP-packaged device will sustain 50 mA continuously. For high-density applications, the UCN5833EP is available. This 44-lead plastic chip carrier (quad pack) is intended for surface-mounting on solder lands with 0.050" (1.27 mm) centers.CMOS serial data outputs permit cascading for applications requiring additional drive lines.FEATURESI To 3.3 MHz Data Input Rate I 30 V Minimum Output Breakdown I Darlington Current-Sink Outputs I Low-Power CMOS Logic and LatchesBiMOS II 32-BIT SERIAL-INPUT,LATCHED DRIVERAlways order by complete part number:Part Number Package UCN5833A 40-Pin DIP UCN5833EP 44-Lead PLCCData Sheet 26185.16A*58335833BiMOS II 32-BIT SERIAL-INPUT,LATCHED DRIVER115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000SERIAL DATA IN POWER STROBE OUT OUT OUT OUT OUT OUT 123456OUT7OUT 8OUT 9OUTOUT OUTOUT OUTLOGIC SUPPLY OUT OUT Dwg. No. A-13,051TYPICAL OUTPUT DRIVERSUBOUT115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000Copyright ? 1986, 1995, Allegro MicroSystems, Inc.5833BiMOS II 32-BIT SERIAL-INPUT,LATCHED DRIVERTRUTH TABLEL = Low Logic Level H = High Logic Level X = Irrelevant P = Present State R = Previous StateELECTRICAL CHARACTERISTICS at T A = +25°C, V DD = 5 V (unless otherwise noted).Limits CharacteristicSymbol Test Conditions Min.Max.Units Output Leakage Current I CEX V OUT = 30 V, T A = 70°C —10µA Collector-Emitter V CE(SAT)l OUT = 50 mA — 1.2V l OUT = 100 mA— 1.7V Input VoltageV IN(1) 3.5 5.3V V IN(0)-0.3+0.8V Input Currentl IN(1)V IN = 5.0 V — 1.0µA l IN(0)V IN = 0 V —-1.0µA Serial Output VoltageV OUT(1)I OUT = -200 µA 4.5—V V OUT(0)I OUT = 200 µA—0.3V Supply Currentl DD One output ON, l OUT = 100 mA — 1.0mA All outputs OFF—50µA Output Rise Time t r l OUT = 100 mA, 10% to 90%—500ns Output Fall Timet fl OUT = 100 mA, 90% to 10%—500nsNOTE: Positive (negative) current is defined as going into (coming out of) the specified device pin.Saturation Voltage5833BiMOS II 32-BIT SERIAL-INPUT,LATCHED DRIVER115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000TIMING CONDITIONS(V DD = 5.0 V, Logic Levels are V DD and Ground)A.Minimum Data Active Time Before Clock Pulse(Data Set-Up Time)..........................................................................75 ns B.Minimum Data Active Time After Clock Pulse(Data Hold Time).............................................................................75 ns C.Minimum Data Pulse Width ................................................................150 ns D.Minimum Clock Pulse Width...............................................................150 nsE.Minimum Time Between Clock Activation and Strobe.......................300 nsF.Minimum Strobe Pulse Width .............................................................100 nsG.Typical Time Between Strobe Activation andOutput Transition ...........................................................................500 nsDwg. No. A-12,276ASerial Data present at the input is transferred to the shift register on the logic “0” to logic “1” transition of the CLOCK input pulse. On succeeding CLOCK pulses, the registers shift data information towards the SERIAL DATA OUTPUT. The SERIAL DATA must appear at the input prior to the rising edge of the CLOCK input waveform.Information present at any register is transferred to its respective latch when the STROBE is high (serial-to-parallel conversion). The latches will continue to accept new data as long as the STROBE is held high. Applications where the latches are bypassed (STROBE tied high) will require that the OUTPUT ENABLE input be low during serial data entry.When the OUTPUT ENABLE input is low, all of the output buffers are disabled (OFF) without affecting the information stored in the latches or shift register. With the OUTPUT ENABLE input high, the outputs are controlled by the state of the latches.CLOCK DATA INSTROBE NOUTPUT ENABLEOUT5833BiMOS II 32-BIT SERIAL-INPUT,LATCHED DRIVERNOTES:1.Exact body and lead configuration at vendor’s option within limits shown.2.Lead spacing tolerance is non-cumulative.3.Lead thickness is measured at seating plane or below.UCN5833ADimensions in Inches (controlling dimensions)Dimensions in Millimeters (for reference only)123Dwg. MA-003-40 mm20421123Dwg. MA-003-40 in2045833BiMOS II 32-BIT SERIAL-INPUT,LATCHED DRIVER115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000UCN5833EPDimensions in Inches (controlling dimensions)Dimensions in Millimeters (for reference only)Dwg. MA-005-44A mm0.53340Dwg. MA-005-44A in0.021740NOTES:1.Exact body and lead configuration at vendor’s option within limits shown.2.Lead spacing tolerance is non-cumulative.5833BiMOS II 32-BITSERIAL-INPUT,LATCHED DRIVERThe products described here are manufactured under one or more U.S. patents or U.S. patents pending.Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.Allegro products are not authorized for use as critical components in life-support devices or systems without express written approval.The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsi-bility for its use; nor for any infringement of patents or other rights of third parties which may result from its use. 5833BiMOS II 32-BIT SERIAL-INPUT,LATCHED DRIVER115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000POWERINTERFACE DRIVERSFunctionOutput Ratings*Part Number ?SERIAL-INPUT LATCHED DRIVERS8-Bit (saturated drivers)-120 mA 50 V?58958-Bit 350 mA 50 V 58218-Bit 350 mA 80 V 58228-Bit 350 mA 50 V?58418-Bit 350 mA 80 V?58428-Bit (constant-current LED driver)75 mA 17 V 62758-Bit (DMOS drivers)250 mA 50 V 65958-Bit (DMOS drivers)350 mA 50 V?6A5958-Bit (DMOS drivers)100 mA 50 V 6B59510-Bit (active pull-downs)-25 mA 60 V 5810-F and 6809/1012-Bit (active pull-downs)-25 mA 60 V 5811 and 681116-Bit (constant-current LED driver)75 mA 17 V 627620-Bit (active pull-downs)-25 mA 60 V 5812-F and 681232-Bit (active pull-downs)-25 mA 60 V 5818-F and 681832-Bit100 mA 30 V 583332-Bit (saturated drivers)100 mA 40 V 5832PARALLEL-INPUT LATCHED DRIVERS4-Bit350 mA 50 V?58008-Bit -25 mA 60 V 58158-Bit350 mA 50 V?58018-Bit (DMOS drivers)100 mA 50 V 6B2738-Bit (DMOS drivers)250 mA 50 V 6273SPECIAL-PURPOSE DEVICESUnipolar Stepper Motor Translator/Driver 1.25 A 50 V?5804Addressable 8-Bit Decoder/DMOS Driver 250 mA 50 V6259Addressable 8-Bit Decoder/DMOS Driver 350 mA 50 V?6A259Addressable 8-Bit Decoder/DMOS Driver 100 mA 50 V 6B259Addressable 28-Line Decoder/Driver 450 mA30 V6817*Current is maximum specified test condition, voltage is maximum rating. See specification for sustaining voltagelimits.Negative current is defined as coming out of (sourcing) the output.Complete part number includes additional characters to indicate operating temperature range and package style. Internal transient-suppression diodes included for inductive-load protection.。

BA6803中文资料

FAbsolute maximum ratings (Ta

FBlock diagram

BA6803S

FElectrical characteristics (unless otherwise noted, Ta = 25_C)

(5) Grid and segment output timing chart. The grid and segment output timing is shown in Fig. 5. (6) Attack and release times The response characteristic for AC input signals is set by resistor R1 and capacitor C3 for ch1 and resistor R2 and capacitor C4 for ch2 (pins 2 and 4). When R1 = 47kΩ and C3 = 22µF, the attack time is about 4ms, and the release time is about 1sec. (same for ch2). Attack time : Time for the voltage on pins 2 and 4 to rise from 1V to 2.5V when the input goes from no input to 2.6Vrms, then back to no input. Release time : Time for the voltage on pins 2 and 4 to fall from 2.5V to 1V when the input goes from 2.6Vrms to no input. (7) Oscillator frequency The resistor R26 and capacitor C5 connected to pin 30 determine the oscillator frequency. The oscillator frequency (fosc) and grid output period (T) are related as follows: T (ms) = 16 / fosc (kHz)

TEL HK6803 内置和弦来电显示芯片 说明书

4.1.3 闹铃设置:按设置键选择 3,LCD 会提示 AL 1-2-3,此时按上下翻查键,或直接输入数字进入设 置,选择 1 进入第一组闹铃设置,此时屏幕显示 ALAR OFF,看到 OFF 闪动直接输入闹铃时间 即可,如要关闭闹铃用上下翻查键选择 OFF 即可。其他 2 组设定与第 1 组设定相同。按免提键 退出。第 1 组为单次闹铃,第 2、3 组为每天闹铃。闹铃过程中,按任意键可停止。

4.1.9 语音功能设定:按设置键选择 9,LCD 会提示 Uo 1-S 2-Cid,此时按上下翻查键或直接输入数 字,选择 1 进入预拨号报号选择,屏幕显示 sound on/off, 按上下翻查键选择,on 表示开启,off 表示关闭;选择 2 进入来电报号次数选择,屏幕显示 Uo cld Off/1~9 按上下翻查键选择,当前默 认值 OFF。1 为每次来电报号 1 次,9 为每次来电报号 9 次。

四:功能详解

4.0 来电制式转换及背景灯和新来电指示灯功能

第一次来码锁定来电制式,按 **# 进行 DTMF/FSK 制式转换,和弦音乐欣赏时来电将退出欣 赏状态,来电响和弦铃声时,只收当前来电。

背景灯功能:芯片上电,按任意键,来电背景灯亮 6S 新来电指示灯:如有新来电(背景灯不亮),在未翻查时新来电指示灯闪烁,亮 1S 暗 4.5S

4.2.6 贵宾存储:UP/DOWN 键翻查出所有的号码,再按 VOL/VIP 键存储该号码。

4.2.7 计算器功能:按 CAL 键进入计算器功能,可计算出 8 位内的+、-、×、÷。

4.2.8 单键存储:在挂机状态下,输入要存储的号码或按 UP/DOWN 键翻查出所要存储的号码再长按 Mx 键进行存储,屏幕显示“SAVE”表示已存入。提取时按 Mx 键提取号码,进入预拨号状态。