HY57V643220DTP-7中文资料

HYS 72V32220GU中文资料

3.3V 16M × 64/72-Bit 1 Bank SDRAM Module 3.3V 32M × 64/72-Bit 2 Bank SDRAM Module 168-Pin Unbuffered DIMM ModulesThe HYS 64(72)V16300GU and HYS 64(72)V32220GU are industry-standard 168-pin 8-byte Dual In-line Memory Modules (DIMMs) which are organized as 16M ×64, 16M ×72 in 1 bank and 32M ×64 and 32M ×72 in two banks of high-speed memory arrays designed with 128Mbit Synchronous DRAMs (SDRAMs) for non-parity and ECC applications. The DIMMs use -7.5 speed sorted 16M ×8 SDRAM devices in TSOP54 packages to meet the PC133-333 requirements and use -8 components for the standard PC100-222 applications. Decoupling capacitors are mounted on the PC board. The PC board design is in accordance with I NTEL’s PC SDRAM Rev. 1.0 Module Specification. The DIMMs have Serial Presence Detect, implemented with a serial E 2PROM using the two-pin I 2C protocol. The first 128bytes are utilized by the DIMM manufacturer and the second 128bytes are available to the end user. All INFINEON 168-pin DIMMs provide a high performance,flexible 8-byte interface in a 133.35mm long footprint, with 1.25“ (31.75mm) height.•168-Pin unbuffered 8-Byte Dual-In-Line SDRAM Modules for PC main memory applications •PC100 and PC133 versions• 1 bank 16M ×64, 16M ×72 and 2bank 32M ×64, 32M ×72 organzation •Optimized for byte-write non-parity (x64) or ECC (x72) applications •JEDEC standard Synchronous DRAMs (SDRAM)•Fully PC board layout compatible to INTEL’s Rev. 1.0 Module Specification •SDRAM Performance:•Programmed Latencies: •Single +3.3V(±0.3V) Power Supply •and Wrap Sequence(Sequential and Interleave)•Auto-Refresh (CBR) and Self-Refresh •Decoupling capacitors mounted on substrate •All inputs and outputs are LVTTL compatible •Serial Presence Detect with E 2PROM•Utilizes 16M ×8 SDRAMs in TSOPII-54 packages with 4096refresh cycles every 64ms •133.35mm ×31.75mm ×4,00mm card size with gold-contact pads-7.5-8Unit PC133PC100f CK ClockFrequency (max.)133100MHzt AC Clock Access Time5.46nsProduct Speed CL t RCDt RP-7.5PC133333-8PC100222Note:All part numbers end with a place code, designating the die revision. Consult factory forcurrent revision. Example: HYS 64V16300GU-8-C, indicates that Rev.C dies are used for SDRAM components.Ordering Information TypeCodePackageDescriptionsModule Height128MByte DIMMs HYS 64V16300GU-7.5-C PC133-333-520L-DIM-168-33133Mhz 16M ×641bank SDRAM module 1.25“HYS 72V16300GU-7.5-C PC133-333-520L-DIM-168-33133Mhz 16M ×721bank SDRAM module 1.25“HYS 64V16300GU-8-C PC100-222-620L-DIM-168-33100MHz 16M ×641bank SDRAM module 1.25“HYS 72V16300GU-8-C PC100-222-620L-DIM-168-33100MHz 16M ×721bank SDRAM module1.25“256MByte DIMMs HYS 64V32220GU-7.5-C PC133-333-520L-DIM-168-30133MHz 32M ×642bank SDRAM module 1.25“HYS 72V32220GU-7.5-C PC133-333-520L-DIM-168-30133Mhz 32M ×722bank SDRAM module 1.25“HYS 64V32220GU-8-C PC100-222-620L-DIM-168-30100MHz 32M ×642bank SDRAM module 1.25“HYS 72V32220GU-8-CPC100-222-620L-DIM-168-30100Mhz 32M ×722bank SDRAM module1.25“Pin Definitions and FunctionsA0-A11Address Inputs WE Read/Write Input V SS GroundBA0, BA1Bank Selects CKE0, CKE1Clock Enable SCL Clock for SPD DQ0 - DQ63Data Input/Output CLK0 - CLK3Clock Input SDA Serial Data Out CB0-CB7Check Bits(x72 modules only)DQMB0 - DQMB7Data Mask N.C.No Connection RAS Row Address Strobe CS0 - CS3Chip Select––CAS Column AddressStrobe VDDPower (+3.3V)––Address FormatPart Number Rows Columns Bank Select Refresh Period Interval 16M×64HYS64V16300GU121024k64ms15,6µs 16M×72HYS72V16300GU121024k64ms15,6µs 32M×64HYS64V32220GU121024k64ms15,6µs 32M×72HYS72V32220GU121024k64ms15,6µsPin ConfigurationPIN#Symbol PIN#Symbol PIN#Symbol PIN#Symbol1V SS43V SS85V SS127V SS2DQ044DU86DQ32128CKE03DQ145CS287DQ33129CS34DQ246DQMB288DQ34130DQMB65DQ347DQMB389DQ35131DQMB76V DD48DU90V DD132N.C.7DQ449V DD91DQ36133V DD8DQ550N.C.92DQ37134N.C.9DQ651N.C.93DQ38135N.C.10DQ752N.C. (CB2)94DQ39136CB611DQ853N.C. (CB3)95DQ40137CB712V SS54V SS96V SS138V SS13DQ955DQ1697DQ41139DQ4814DQ1056DQ1798DQ42140DQ4915DQ1157DQ1899DQ43141DQ5016DQ1258DQ19100DQ44142DQ51Pin Configuration (cont’d)PIN#Symbol PIN#Symbol PIN#Symbol PIN#Symbol 17DQ1359V DD101DQ45143V DD18V DD60DQ20102V DD144DQ52 19DQ1461N.C.103DQ46145N.C.20DQ1562DU104DQ47146DU21N.C. (CB0)63CKE1105N.C. (CB4)147N.C.22N.C. (CB1)64V SS106N.C. (CB5)148V SS23V SS65DQ21107V SS149DQ53 24N.C.66DQ22108N.C.150DQ54 25N.C.67DQ23109N.C.151DQ55 26V DD68V SS110V DD152V SS27WE69DQ24111CAS153DQ56 28DQMB070DQ25112DQMB4154DQ57 29DQMB171DQ26113DQMB5155DQ58 30CS072DQ27114CS1156DQ59 31DU73V DD115RAS157V DD32V SS74DQ28116V SS158DQ60 33A075DQ29117A1159DQ61 34A276DQ30118A3160DQ62 35A477DQ31119A5161DQ63 36A678V SS120A7162V SS37A879CLK2121A9163CLK3 38A1080N.C.122BA0164N.C.39BA181WP123A11165SA040V DD82SDA124V DD166SA141V DD83SCL125CLK1167SA242CLK084V DD126N.C.168V DD Note:Pin names in parentheses are for the x72 ECC versions; example: Pin 106 = (CB5).Block Diagram for 16M×64/72 SDRAM DIMM Modules (HYS64/72V16300GU)Block Diagram for 32M×64/72 SDRAM DIMM Modules (HYS64/72V32220GU)DC CharacteristicsTA=0 to 70°C; V SS=0V; V DD,V DDQ=3.3V±0.3VParameter Symbol Limit Values Unitmin.max.Input High Voltage V I H 2.0V DD+0.3V Input Low Voltage V IL–0.50.8V Output High Voltage (I OUT=–4.0mA)V OH 2.4–V Output Low Voltage (I OUT=4.0 mA)V OL–0.4VInput Leakage Current, any input(0V<V IN<3.6V, all other inputs=0V)II(L)–4040µAOutput Leakage Current(DQ is disabled, 0V<V OUT<V DD)IO(L)–4040µACapacitanceTA=0 to 70°C; V DD=3.3V±0.3V, f=1MHzParameter Symbol Limit Values Unitmax. 16M×64max.16M×72max.32M×64max.32M×72Input Capacitance(A0 to A11, BA0, BA1, RAS, CAS, WE)CI16572105144pFInput Capacitance (CS0 - CS3)C CS32403543 pF Input Capacitance (CLK0 - CLK3)C CLK38404245pF Input Capacitance (CKE0, CKE1)C CKE65726572pF Input Capacitance (DQMB0 - DQMB7)C I413132020pFInput/Output Capacitance (DQ0 - DQ63, CB0 - CB7)CIO10101717pFInput Capacitance (SCL, SA0-2)C SC8888pF Input/Output Capacitance C SD8888pFOperating Currents per SDRAM Component 1)T A =0 to 70o C, V DD =3.3V±0.3V(Recommended Operating Conditions unless otherwise noted)Parameter TestCondition Symbol-7.5-8Unit Notemax.Operating CurrenttRC=t RCMIN., t CK=t CKMIN.Outputs open, Burst Length=4, CL=3All banks operated in random access,all banks operated in ping-pong mannerto maximize gapless data access–I CC1160150mA1)Precharge Standby Currentin Power Down ModeCS=V IH (min.), CKE≤V IL(MAX)tCK=min.I CC2P 1.5 1.5mA1)Precharge Stand-by Current in Non-Power Down Mode CS=V IH (MIN.), CKE≥V IH(MIN)tCK=min.I CC2N4035mA1)No Operating CurrenttCK=min., CS=V IH(MIN), active state (max. 4banks)CKE≥V IH(MIN.)I CC3N5045mA1) CKE≤V IL(MAX.)I CC3P1010mA1)Burst Operating CurrenttCK=min.,Read command cycling–I CC410090mA1), 2)Auto-Refresh CurrenttCK=min.,Auto-Refresh command cycling–I CC5230210mA1)Self-Refresh CurrentSelf-Refresh Mode, CKE=0.2V–I CC6 1.5 1.5mA1)AC Characteristics3), 4)TA=0 to 70°C; V SS=0V; V DD=3.3V±0.3V, t T=1nsParameter Symbol Limit Values Unit Note-7.5 PC133-333-8PC100-222min.max.min.max. Clock and Access TimeClock Cycle TimeCAS Latency=3CAS Latency=2tCK7.510––1010––nsns–System FrequencyCAS Latency=3CAS Latency=2fCK––133100––100100MHzMHz–Clock Access TimeCAS Latency=3CAS Latency=2tAC––5.46––66nsns4), 5)Clock High Pulse Width t CH 2.5–3–ns6) Clock Low Pulse Width t CL 2.5–3–ns6)Setup & Hold ParametersInput Setup Time t IS 1.5–2–ns7) Input Hold Time t IH0.8–1–ns7) Power Down Mode Entry Time t SB–1–1CLK8) Power Down Mode Exit Setup Time t PDE1–1–CLK9) Mode Register Setup Time t RSC2–2–CLK Transition Time (rise and fall)t T1–1–ns–Common ParametersRAS to CAS Delay t RCD20–20–ns–Precharge Time t RP20–20–ns–Active Command Period t RAS45100k50100k ns–Cycle Time t RC67.5–70–ns–Bank-to-Bank Delay Time t RRD15–16–ns–CAS to CAS Delay Time (same bank)t CCD1–1–CLK–Refresh CycleRefresh Period (4096cycles)t REF –64–64ms Self-Refresh Exit Time t SREX1–1–CLK10)Read Cycle Data Out Hold Time t OH 3–3–ns 4)Data Out to Low Impedance t LZ 0–0–ns –Data Out to High Impedance t HZ 3738ns 11DQM Data Out Disable Latency t DQZ–2–2CLK–Write CycleData Input to Precharge (write recovery)t WR 2–2–CLK –DQM Write Mask Latencyt DQW––CLK–AC Characteristics (cont’d) 3), 4)T A =0 to 70°C; V SS =0V; V DD =3.3V ±0.3V, t T =1ns ParameterSymbolLimit ValuesUnitNote-7.5PC133-333-8PC100-222min.max.min.max.Notes1.These parameters depend on the cycle rate. These values are measured at 133MHz for -7.5modules and at 100Mhz for -8 modules. Input signals are changed once during t CK, except for Iand for standby currents when t CK=infinity. All values are shown per memory component.CC62.These parameters are measured with continuous data stream during read access and all DQtoggling. CL=3 and BL=4 assumed and the V DDQ current is excluded.3.All AC characteristics are shown on SDRAM component level.An initial pause of 100µs is required after power-up, then a Precharge All Banks command must be given followed by eight Auto-Refresh (CBR) cycles before the Mode Register Set Operation can begin.4.AC timing tests have V IL=0.4V and V IH=2.4V with the timing referenced to the 1.4V crossoverpoint. The transition time is measured between V IH and V IL. All AC measurements assume t=1ns with the AC output load circuit show. Specified t AC and t OH parameters are measured Twith a 50pF only, without any resistive termination and with a input signal of 1V/ns edge rate between 0.8V and 2.0V.5.If clock rising time is longer than 1ns, a time (t T/2–0.5)ns must be added to this parameter.6.Rated at 1.4V7.If t T is longer than 1ns, a time (t T–1)ns has to be added to this parameter.8.Anytime the Refresh Period has been exceeded, a minimum of two Auto-Refresh (CBR)commands must be given to “wake-up” the device.9.Timing is asynchronous. If setup time is not met by rising edge of the clock then the CKE signalis assumed latched on the next cycle.10.Self-Refresh Exit is a synchronous operation and begins on the second positive clock edge afterCKE returns high. Self-Refresh Exit is not complete until a time period equal to t RC is satisfied after the Self Refresh Exit command is registered.11.This is referenced to the time at which the output achieves the open circuit condition, not tooutput voltage levels.A Serial Presence Detect storage device—E2PROM—is assembled onto the module. Information about the module configuration, speed, etc. is written into the E2PROM device during moduleproduction using a Serial Presence Detect protocol (I2C synchronous 2-wire bus).SPD-Table for PC133 Modules:Byte#Description SPD EntryValueHex16Mx64 -7.516Mx72-7.532Mx64-7.532Mx72-7.50Number of SPD bytes128801T otal bytes in Serial PD256082Memory Type SDRAM043Number of Row Addresses(without BS bits)120C4Number of Column Addres-ses100A5Number of DIMM Banks 1 / 201026Module Data Width64 / 7240484048 7Module Data Width (cont’d)0008Module Interface Levels LVTTL019SDRAM Cycle Time at CL=37.5 ns7510SDRAM Access time fromClock at CL=35.4 ns5411Dimm Config none / ECC00020002 12Refresh Rate/Type Self-Refresh,15.6ms8013SDRAM w idth, P rimary x80814Error Checking SDRAM datawidthn/a / x80008000815Minimum clock delay forback-to-back random columnaddress tccd= 1 CLK0116Burst Length supported1, 2, 4 & 8 0F 17Number of SDRAM banks404 18Supported CAS Latencies CAS latency = 2& 306 19CS Latencies CS latency = 001 20WE Latencies Write latency = 00121SDRAM DIMM module attributes non buffered/nonreg.0022SDRAM Device Attributes:GeneralVcc tol +/- 10%0E23Min. Clock Cycle Time atCAS Latency = 210.0 ns A024 Max. data access time fromClock for CL=26.0 ns6025 Minimum Clock Cycle Timeat CL = 1not supported FF26Maximum Data Access Timefrom Clock at CL=1not supported FF27Minimum Row PrechargeTime20 ns1428Minimum Row Active to RowActive delay tRRD15 ns0FByte#Description SPD EntryValueHex16Mx64 -7.516Mx72-7.532Mx64-7.532Mx72-7.529Minimum RAS to CAS delaytRCD20 ns1430Minimum RAS pulse widthtRAS45 ns2D31Module Bank Density (perbank)128 MByte2032SDRAM input setup time 1.5 ns1533SDRAM input hold time0.8 ns0834SDRAM data input hold time 1.5 ns1535SDRAM data input setuptime0.8 ns0862-61Superset information (may beused in future)FF62SPD Revision Revision 1.21263Checksum for bytes 0 - 6213251426 64-125Manufacturers information XX XX XX XX 126Frequency Specification64127Support Details AF FF128+Unused storage locations FFSPD-Table for PC100 Modules:Byte#Description SPD EntryValueHex16Mx64-816Mx72-832Mx64-832Mx72-80Number of SPD bytes128801T otal bytes in Serial PD256082Memory Type SDRAM043Number of Row Addresses(without BS bits)120C4Number of Column Addres-ses100A5Number of DIMM Banks 1 / 201026Module Data Width64 / 7240484048 7Module Data Width (cont’d)0008Module Interface Levels LVTTL019SDRAM Cycle Time at CL=310.0 ns A010SDRAM Access time fromClock at CL=36.0 ns6011Dimm Config none / ECC00020002 12Refresh Rate/Type Self-Refresh,15.6ms8013SDRAM w idth, P rimary x80814Error Checking SDRAM datawidthn/a / x80008000815Minimum clock delay forback-to-back random columnaddress tccd= 1 CLK0116Burst Length supported1, 2, 4 & 8 0F 17Number of SDRAM banks404 18Supported CAS Latencies CAS latency = 2& 306 19CS Latencies CS latency = 001 20WE Latencies Write latency = 00121SDRAM DIMM module attributes non buffered/nonreg.0022SDRAM Device Attributes:GeneralVcc tol +/- 10%0E23Min. Clock Cycle Time atCAS Latency = 210.0 ns A024 Max. data access time fromClock for CL=26.0 ns6025 Minimum Clock Cycle Timeat CL = 1not supported FF26Maximum Data Access Timefrom Clock at CL=1not supported FF27Minimum Row PrechargeTime20 ns1428Minimum Row Active to RowActive delay tRRD16 ns10Byte#Description SPD EntryValueHex16Mx64-816Mx72-832Mx64-832Mx72-829Minimum RAS to CAS delaytRCD20 ns1430Minimum RAS pulse widthtRAS45 ns2D31Module Bank Density (perbank)128 MByte2032SDRAM input setup time 2 ns2033SDRAM input hold time 1 ns1034SDRAM data input hold time 2 ns2035SDRAM data input setuptime1 ns1062-61Superset information (may beused in future)FF62SPD Revision Revision 1.21263Checksum for bytes 0 - 6271837284 64-125Manufacturers information XX XX XX XX 126Frequency Specification100 MHz64127Support Details AF FF128+Unused storage locations FFPackage OutlinesSorts of PackingPackage outlines for tubes, trays etc. are contained in ourData Book “Package Information”.Dimensions in mmSorts of PackingPackage outlines for tubes, trays etc. are contained in ourData Book “Package Information”.Dimensions in mm。

奇辉电气集中器安装使用手册

QEM6601/QEM6602型集中抄表系统集中器产品说明书深圳市奇辉电气有限公司目录一、概述 (4)1、设计依据 (4)2、工作原理简介 (5)3、型号说明 (5)二、技术指标 (5)1、主控芯片 (5)2、存储部分 (5)3、上行通信 (5)4、下行通信 (6)5、级联RS485通信 (6)6、总表RS485通信 (6)7、本地通信 (6)8、时钟走时误差 (7)9、电池 (7)10、电源 (7)11、功耗(守候状态) (7)12、工作环境 (7)13、机械尺寸 (7)三、主要功能 (8)1、参数设置功能 (8)2、数据采集功能 (8)3、事件记录及采集功能 (8)4、告警功能 (8)5、级联功能 (9)6、重点用户功能 (9)7、日线损计算功能 (9)8、校时功能 (9)9、现场抄读功能 (10)10、远程控制功能 (10)11、程序升级功能 (10)四、外形及接线 (10)1、结构图 (10)2、面板 (11)3、接线端子 (11)4、安装图 (12)五、安装调试 (13)1、准备工作 (13)2、安装 (13)3、调试 (14)4、常见故障 (14)六、运输及存贮 (14)七、保证期限 (15)一、概述使用本产品前请仔细阅读各章节。

本手册主要介绍集中器的工作原理、技术指标、主要功能、安装调试、运输存贮等内容。

集中器的使用者必须是具有电气设备安装和操作经验的专业技术人员,在任何情况下,都不应该由不具备专业资历或未经培训的人员来操作。

QEM660X系列集中器是我公司开发的基于嵌入式软硬件平台的新一代集中器产品,集成度高、技术先进,支持GPRS/CDMA/SMS/PSTN/GSM/RS232等上行通信方式。

是电力系统低压用户集中抄表系统的中心设备,是连通主站和采集终端、电能表的桥梁,可实现数据自动采集、事件记录、重点用户监测、线损计算等功能。

1、设计依据本产品的设计、生产符合下列标准、规范:●广东电网公司低压电力用户集中抄表系统集中器订货及验收技术条件(试行);●广东电网公司低压电力用户集中抄表系统集中器上行通讯规约(试行);●广东电网公司RS-485接口单相电子式电能表通讯规约(试行);●广东电网公司三相多功能载波电能表485接口通讯规约(试行)。

威胜DSSD332-7M三相多功能监测仪表说明书

DSSD332-7M说明书1 技术指标业务咨询电话:0731-********2 功能介绍2.1参数测量功能本仪表具有丰富的测量功能,可测量的电网参数和指标如下:(1)各相电压值及平均电压值。

(2)各线电压值及平均线电压值。

(3)各相电流值、平均电流值以及零线电流值。

(4)总和各分相有功功率、无功功率、视在功率。

(5)各分相电压和电流的相角值。

(6)总和各分相的功率因数值。

(7)电网频率,测量范围为45~65Hz。

2.2 越限报警功能(1)仪表具备越限事件报警功能。

用户可从电压、电流、功率、功率因数和频率等参数中最多同时选择6个数据作为检测对象,对其设定高低限值和判断条件,当测量值越过设定的限值时报警。

仪表带有1路继电器输出,当报警参数配置为某继电器输出且该继电器为自动方式(非手动方式)时,越限报警信号就可通过该路继电器输出(继电器合闸)。

(2)仪表内部最多可同时设置6组越限报警参数。

各组越限报警参数的配置流程为:选择检测数据类别→设置检测数据阀值→设置判断条件→选择报警信号输出继电器。

①各类检测数据代码如下:(DL/T645代码为十进制数;Modbus-RTU代码为十六进制数)当检测数据代码为FF时表示该组越限报警功能关闭。

②检测数据阀值:检测数据是否越限的判断阀值。

不同的数据类型有不同的单位,如:电压—V;电流—A,有功—KW,无功—KV AR,视在—KV A,频率—Hz。

③判断条件:设置为0表示大于限额值报警;1表示小于限额值报警。

④报警信号输出继电器:设置为0表示报警信号无输出;1表示报警信号从继电器输出。

(3)报警参数设置举例。

将其中1组越限报警参数设定为对“A相电压”进行自动检测报警,报警阀值假定为240V,判断标准假定为“大于限额值”,信号输出口假定从继电器输出。

①使用MODBUS RTU协议配置报警参数:0110地址设置为“07”;0111地址设置为“0000”,0112地址设置为“5DC0”(根据协议先将数值“240”乘以100得到“24000”后再进行16进制转换为“00005DC0”);0113地址设置为“00”,0114地址设置为“01”。

AD5757中文手册

AD5757

产品特性

16位分辨率和单调性 用于热管理或外部PMOS模式的动态电源控制 电流输出范围:0 mA至20 mA、4 mA至20 mA或0 mA至 24 mA 总不可调整误差(TUE):±0.05%(最大值) 用户可编程失调与增益 片内诊断 片内基准电压源(±10 ppm/°C,最大值) 温度范围:−40°C至+105°C 各通道均有一个相应的CHART引脚,因此HART信号可以 耦合到AD5757的电流输出端。 该器件采用多功能三线式串行接口,能够以最高30 MHz 的时钟速率工作,并与标准SPI、QSPI™、MICROWIRE™、 DSP 和 微 控 制 器 接 口 标 准 兼 容 。 该 接 口 还 提 供 可 选 的 CRC-8分组错误校验功能,以及用于监控接口活动的看门 狗定时器。

ADI中文版数据手册是英文版数据手册的译文,敬请谅解翻译中可能存在的语言组织或翻译错误,ADI不对翻译中存在的差异或由此产生的错误负责。如需确认任何词语的准确性,请参考ADI提供 的最新英文版数据手册。

AD5757 目录

产品特性 ......................................................................................... 1 应用 .................................................................................................. 1 概述 .......................................................................

天诚通信-铜产品培训资料

目录超五类非屏蔽信息(xìnxī)模块 (5)超五类非屏蔽(píngbì)直通信息模块..................................................................................... 错误!未定义书签。

超五类屏蔽信息(xìnxī)模块 (6)超五类屏蔽直通信息(xìnxī)模块........................................................................................... 错误!未定义书签。

六类非屏蔽信息(xìnxī)模块 (7)六类屏蔽信息模块 (8)超六类非屏蔽信息模块 (9)超六类非屏蔽信息模块 (10)超六类屏蔽信息模块 (10)超五类非屏蔽免打线水晶头 .................................................................................................... 错误!未定义书签。

经典系列平口面板 . (12)雅典系列平口面板 (13)雅典系列斜口面板 (14)雅典系列有线电视面板 (15)数据语音电视三合一面板 (16)二位方形光纤开起式地脚插座 (17)三位方形信息弹起式地脚插座 (18)三位圆形信息弹起式地脚插座 (19)三位方形信息开起式地脚插座 (20)三位圆形信息开起式地脚插座 (21)五孔方形弹起式电源插座 (22)五孔圆形弹起式电源插座 (23)六孔方形弹起式电源插座 (24)六位桌面型地脚插座 (25)地插功能配件 (26)24口非屏蔽空配线架 (28)24口非屏蔽空配线架〔带防尘门〕 (29)24口超五类非屏蔽配线架 (30)24口超五类非屏蔽角型配线架................................................................................................ 错误!未定义书签。

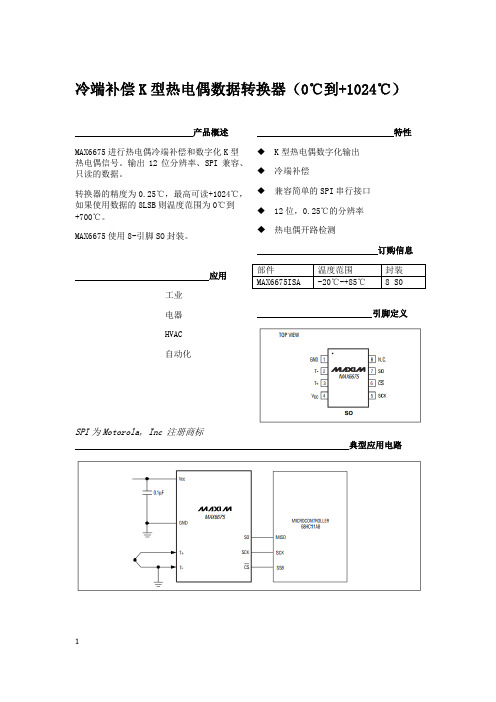

MAX6675中文数据手册

热电偶开路检测

位 D2 一般情况下为 0,在热电偶开路时 跳变为 1。为了使热电偶开路检测器能够 正常运行,T-必须接地,且接地点需尽可 能靠近 GND 引脚。

温升的考虑

在某些应用中器件自身发热会降低 MAX6675 的精度。温度误差的大小取决于 MAX6675 封装的热传导性、安装技术、和 气流的影响。使用一个大的地平面可以提 高 MAX6675 的温度测量精度。

100

ns

100 ns

100 ns

100 ns

Note 1: 所有参数都是在 TA=25℃下 100%测试。温度超过极限 (TA = TMIN to TMAX) 的参 数只从设计和特性上保证,没有产品测试。 Note 2: 从设计上保证,没有产品测试。

(没有特别指出,VCC=+3.3V,TA=+25℃) 输出码误差和环境温度

使用适当的保护套保护热电偶

仅仅在低温、温度波动小的区域使用 补偿导线

保存事件日志和热电偶阻抗的记录

噪声方面的考虑

MAX6675 的精确度易受电源耦合噪声的影 响。电源噪声的影响可以通过放置 1 个 0.1μ F 的陶瓷电容消弱,电容应靠近器 件的电源引脚。

减小拾取噪声的影响

输入放大器(A1)是一个低噪声的放大器, 它被设计为能够放大高精度的传感器输入 信号。确保热电偶和与其想接的导线远离 电子噪声源。

可以用以下措施改善热电偶系统的测量精 度:

使用尽可能粗的导线,这样的导线不 至于从测量区域分流来大量的热

如果要求使用比较细的导线在,则仅 仅在测量区使用这种线,在没有温升 的地方使用补偿导线

Yokogawa DeviceXPlorer OPC Server Ver.7 使用手册说明书

DeviceXPlorer OPC Server Ver.71.2.3.VisualizationData Analyzation Data Collection Remote monitoringConnection to Cloud (MQTT/HTTP)Expansion of OPC UA functionSupport 400+ Series!Ver.7 Special FeaturesHTTPImproved UsabilityFind moreVer.7 New FeaturesDxpSERVER ver.7 supports a general protocol MQTT/HTTP and enables to connect seamlessly with various cloud service.ProductionsiteHTTP■Operational monitoring ■Data collection ■Data AnalyzationCloudConnectable Cloud service・AWS IoT Core ・Azure IoT Hub・・Connection to Cloud (MQTT/HTTP)2.Improved UsabilityAll required functions are in one display. You can start setting all at once.The Setting can be changed duringoperation without turning off OPC Server.change1.Connect to CloudConnect with DeviceAccumulate the data◆Support Reverse Connect◆Support Historical Access◆Support Alarm&ConditionConnectOPC ServerDxpSERVER Ver.7 can notify alarm and manage status.DxpSERVER Ver.7 can acquire historical data.DxpSERVER Ver.7 does not require to open the port when connecting from OPC UA Client on the cloud.OPC ServerOPC ClientOPC ClientCloud3.Expansion of OPC UA functionOPC ClientOPC ServerRenewed edition from Ver. 6Renewal of the EditionRenewal of the License TypeList of License TypeProtection System The product will be delivered;Hardware Key Via Air Courier ,USB Key + Download link of the installation data + Documents(License Certificateetc.)Software Key Via Email ,Download link of the installation data + Documents(License Certificate etc.)Software Key(Subscription License)Protection System Need to be updated annually?How to apply the license Hardware Key ×Attach USB Key(need to attach during the operation)Software Key ×Activate the license via the InternetSoftware Key(Subscription License)✓ItemHardware KeySoftware KeySoftware Key(Subscription License )To activate the license ✓Easy Connection to Internet :✓EasyNo connection to Internet :Some process neededRisk of losing the Key Yes ✓None USB port on PC Must✓No need Updating the license✓No need Need to update annually *Initial costUsual cost✓Low costDelivered by Data (No Media delivery)We provide a subscription license to help to reduce your initial implementation costs.Maintenance service is also included during the subscription term. Subscription license must be updated annually.We deliver you a download link of the installation data when you purchase the product. If you require CD media, you need to make order for the CD media separately.*If you require CD media, please order "DxpSERVER V7 software media (model: DXPV7-MEDIA)" separately.For Ver.7, We deliver you a download link of the installation data when you purchase the product.There are 3 Line-ups for your system requirements.Choose either of Professional/Multi/Single edition.*When updating a subscription license, a license activation process is also required.To renew the subscription license, order "DxpSERVER V7 Subscription (1 year)”.Edition Professional editionfunction *Accessible devices Equivalent edition of Ver.6Professional✓All devices -Multi ×All devices Enterprise Single×1 vendor deviceAdvanced*Professional edition functions are ; MQTT (publish), HTTP Client, OPC UA Historical Access and OPC UA Alarm&Condition functions.*For information on how to activate a PC that cannot connect to the Internet, please refer to the product manual.Need to connect withthe cloud service (HTTP/MQTT)?Do you want to connect to more than one type of device?Use OPC UA Historical Accessor Alarm&Condition?MultiProfessionalNeed to Connect to data sources other than the selectable devicesin the single edition?SingleYESYES YES NOHow to select the EditionYESNONONOSTARTOur system need to be connected with the cloud...so we choose Professional edition!*OPC UA client and Modbus/TCP server functions are not available in the single edition.We provide "OPC DA/UA client" and "Modbus/TCP server" as data sources(a function to connect with devices).Version UpgradeUpgrade from (Ver.3-6)Upgrade to (Ver.7)ModelEnterprise Multi DXPV7ML-●●-VStandard or AdvancedSingleDXPV7SG-●●-V・No other version upgrade service available other than above.To upgrade the version from previous versions please refer to following list.You can select Protect Key. For further details of Protect Key, please see P4.Version UpgradeWhat device can be connected to Single Edition?When you purchase Single edition, you can select one of the models below after installation to communicate with.The Product Model does not differ depending on the device to be connected.You need to purchase Multi or Professional Edition in order to connect the device other than listed below.Selectable DeviceMitsubishi MELSEC iQ-R/Q/L/FX/QnA/A SeriesOMRON SYSMAC-NJ/CJ/CS/CP/CV/C SeriesJTEKT TOYOPUC-PC10/PC3J/PC2J SeriesYOKOGAWA FA-M3 Series HITACHI EH/H SeriesSHARP SATELLITE JW SeriesFUJI MICREX-SX/F Series Panasonic FP-X/FP7/FP2 Series YASKAWA MP Series (MEMOBUS )LSIS XGT SeriesYaskawa Robot simulator KEYENCE KV SeriesRockwell AB ControlLogix (EtherNet/IP )SIEMENS SIMATIC-S7 SeriesAZBIL (Yamatake )CPL Protocol Modbus/TCP,Modbus/RTU, Modbus/ASCII (Client )*FANUCPMC SeriesKAWASAKI Robot ControllerOPC DA2.05A/3.0 Client function *Renewed support service from Ver. 6At product purchase1 year1yearAdd (1 year)Additional maintenance(1 year)No additional maintenance Renewal of Maintenance services1 year maintenance1 YearAt product purchase1 yearMaintenance service period *2・Additional Maintenance can be purchased at the purchase of a product or at the time of update of the maintenance service period.・1 Additional maintenance can be purchased per product serial number(Additional maintenance is serviced for either 1 year or 4 years).Example: It is not available to make additional maintenance 2 year by purchasing 1 year x 2 service.You can purchase additional maintenance (1 year) again after the expiry of the additional maintenance (1 year).At renewal of maintenance service periodAdditional maintenance(4 year)No additional maintenanceAdd (1year )Add (1 year)Add (1year )Add (1 year)Add (1 year)VersionMaintenance service detailsWho is covered by the serviceVer.6andearlier ・Free version upgrade service (including major versions)・Only for licenses with maintenancesubscription and user registered products Ver.7・Free version upgrade service (including major versions)・Product inquiry support・Only for licenses with maintenancesubscription and user registered productsThe maintenance service is only provided to products which within the maintenance service period and registered User registration .The maintenance service period can be extended by purchasing Additional Maintenance separately.Free upgrade service *1This service makes your software license kept on a latest version for this period.There are no expense for upgrading software.Support service *2For products that have already been registered as users, you can receive product inquiry support during the contract period .Since we cannot accept inquiry support for products that have not been registered as a user, we recommend that you complete the procedure as soon as possible after purchasing.Additional maintenance (Update of maintenance service period)*The user will be notified when the maintenance service period is due to be renewed.The maintenance service period for the additional maintenance starts the day after the expiry date of the previous maintenance period.*1Any products can be upgraded for Minor version upgrades (version upgrades in the second digit or later digits) free ofcharge without the maintenance service.*2 We ask you to show the product serial number when you require support service. For pre-purchase support, such asproduct selection, can be provided without the maintenance service. Please note the service is not to guarantee to provide you identification of certain cause of the problem or resolve issues.The changes in the maintenance service content are as follows.Price ListProduct NameLicense TypeProtection System Model*2Price DxpSERVER V7 Professional OPC ServerPerpetual Hardware Key DXPV7PR-HW USD 2,240PerpetualSoftware Key DXPV7PR-SW USD 2,240Subscription (1 year )Software Key DXPV7PR-SS USD 1,100 / yearSubscription (1 year )(Usage in the cloud)-DXPV7PR-CL Contact us UpdateSubscription (1 year )Software Key DXPV7PR-SS-RE USD 1,100 / yearSubscription (1 year )(Usage in the cloud)-DXPV7PR-CL-RE Contact us Bulk purchase (10 pcs)Perpetual Hardware Key DXPV7PR-HW-A10USD 21,000Perpetual Software Key DXPV7PR-SW-A10USD 21,000Additional maintenance (1 year)*3--DXPV7PR-MNT1USD 430Additional maintenance (4 years)*3--DXPV7PR-MNT4USD 1,680Product NameLicense TypeProtection System Model*2Price DxpSERVER V7 Multi OPC ServerPerpetual Hardware Key DXPV7ML-HW USD 1,480Perpetual Software Key DXPV7ML-SW USD 1,480Version Up(Target :Ver.4-6 Enterprise Edition)Perpetual Hardware Key DXPV7ML-HW-V USD 740PerpetualSoftware Key DXPV7ML-SW-V USD 740Bulk purchase (10 pcs)PerpetualHardware Key DXPV7ML-HW-A10USD 12,760Perpetual Software Key DXPV7ML-SW-A10USD 12,760Additional maintenance (1 year)*3--DXPV7ML-MNT1USD 320Additional maintenance (4 years)*3--DXPV7ML-MNT4USD 1,230Product NameLicense TypeProtection System Model*2PriceDxpSERVER V7 Single OPC ServerPerpetual Hardware Key DXPV7SG-HW USD 780Perpetual Software Key DXPV7SG-SW USD 780Version Up(Target :Ver.4-6 Standard / Advanced Edition)Perpetual Hardware Key DXPV7SG-HW-V USD 390Perpetual Software Key DXPV7SG-SW-V USD 390Bulk purchase (10 pcs)Perpetual Hardware Key DXPV7SG-HW-A10USD 6,720Perpetual Software Key DXPV7SG-SW-A10USD 6,720Additional maintenance (1 year)*3--DXPV7SG-MNT1USD 160Additional maintenance (4 years)*3--DXPV7SG-MNT4USD 620Product NameLicense TypeProtection System ModelPriceDxpSERVER V7 Software Media--DXPV7-MEDIA USD 110DxpSERVER V7 license key replacement (Hardware key ⇔ Software key)--DXPV7-LICCHGUSD 220Professional EditionMulti EditionSingle EditionOthersA EditionPR :Professional ML :Multi SG :SingleB License Key /Protection System*1HW :Hardware Key (Perpetual)SW :Software key (Perpetual)SS :Software key (Subscription) CL :Software key (Subscription, For Cloud)C Maintenance /Upgrade / Bulk purchase Unspecified : Normal product RE : Update Subscription V : Version UpgradeMNT1 : Additional maintenance (1 year) MNT4 : Additional maintenance (4 years) A10 : Bulk purchase 10 pcs DDestination country *2Unspecified :Japan E :Outside of JapanModel Code definition :DXPV7A B C D---*1License type: Subscription (1 year) is only for Professional Edition.*2 Add "-E" to the end of each model for overseas markets. The display language of the software can be selected separately from the software screen.Supported languages: Japanese, English, Korean, Chinese (simplified/traditional)*3 When purchasing additional maintenance when renewing the maintenance service period, the serial number of the product is required. See page 10 for details onmaintenance services.The data can be downloaded from the website .If you need CD media, please place an order "DxpSERVER V7 software media (model: DXPV7-MEDIA)" separately.。

DPtech LSW5600系列以太网交换机安装手册v1.5

DPtech LSW5600 系列以太网交换机安装手册

2.2.4 抗干扰要求 ..................................................................................................................... 2-3 2.2.5 防雷击要求 ..................................................................................................................... 2-3 2.2.6 接地要求 ......................................................................................................................... 2-3 2.2.7 布线要求 ......................................................................................................................... 2-3 2.3 激光使用安全 .................................................................................................................... 2-3 2.4 安装工具 ............................................................................................................................ 2-4

HY57V641620F(L_S)TP_series(Rev1.0)

This document is a general product description and is subject to change without notice. Hynix does not assume any responsibility for use of circuits described. No patent licenses are implied.Rev. 1.0 / Apr. 2007164Mb Synchronous DRAM based on 1M x 4Bank x16 I/O Document Title4Bank x 1M x 16bits Synchronous DRAMRevision HistoryRevision No.History Draft Date Remark 0.1Initial Draft Jan. 2007Preliminary1.0Final VersionApr. 2007Rev. 1.0 / Apr. 20072DESCRIPTIONThe Hynix HY57V641620F(L/S)TP series is a 67,108,864bit CMOS Synchronous DRAM, ideally suited for the memory applications which require wide data I/O and high bandwidth. HY57V641620F(L/S)TP is organized as 4banks of 1,048,576x16.HY57V641620F(L/S)TP is offering fully synchronous operation referenced to a positive edge of the clock. All inputs and outputs are synchronized with the rising edge of the clock input. The data paths are internally pipelined to achieve very high bandwidth. All input and output voltage levels are compatible with LVTTL.Programmable options include the length of pipeline (Read latency of 2 or 3), the number of consecutive read or write cycles initiated by a single control command (Burst length of 1,2,4,8 or full page), and the burst count sequence(se-quential or interleave). A burst of read or write cycles in progress can be terminated by a burst terminate command or can be interrupted and replaced by a new burst read or write command on any cycle. (This pipelined design is not re-stricted by a '2N' rule)FEATURESORDERING INFORMATIONNote: 1. HY57V641620FTP Series: Normal power 2. HY57V641620FLTP Series: Low power3. HY57V641620FSTP Series: Super Low power Part Number Clock Frequency OrganizationInterfaceOperation Temp.PackageHY57V641620F(L/S)TP-5200MHz 4Banks x 1Mbits x16LVTTL0o C to 7054 Pin TSOP (Lead Free)HY57V641620F(L/S)TP-6166MHz HY57V641620F(L/S)TP-7143MHz HY57V641620F(L/S)TP-H 133MHz HY57V641620F(L/S)TP-5I 200MHz -40o C to 85HY57V641620F(L/S)TP-6I 166MHz HY57V641620F(L/S)TP-7I 143MHz HY57V641620F(L/S)TP-HI133MHz•Voltage: VDD, VDDQ 3.3V supply voltage•All device pins are compatible with LVTTL interface • 54 Pin TSOPII (Lead or Lead Free Package)•All inputs and outputs referenced to positive edge of system clock•Data mask function by UDQM, LDQM•Internal four banks operation•Auto refresh and self refresh •4096 Refresh cycles / 64ms•Programmable Burst Length and Burst Type - 1, 2, 4, 8 or full page for Sequential Burst - 1, 2, 4 or 8 for Interleave Burst•Programmable CAS Latency; 2, 3 Clocks •Burst Read Single Write operationPIN ASSIGNMENTSRev. 1.0 / Apr. 2007 3PIN DESCRIPTIONSYMBOL TYPE DESCRIPTIONCLK Clock The system clock input. All other inputs are registered to the SDRAM on the rising edge of CLKCKE Clock Enable Controls internal clock signal and when deactivated, the SDRAM will be one of the states among power down, suspend or self refreshCS Chip Select Enables or disables all inputs except CLK, CKE, UDQM and LDQMBA0, BA1Bank Address Selects bank to be activated during RAS activity Selects bank to be read/written during CAS activityA0 ~ A11Address Row Address: RA0 ~ RA11, Column Address: CA0 ~ CA7 Auto-precharge flag: A10RAS, CAS, WERow Address Strobe,Column Address Strobe,Write EnableRAS, CAS and WE define the operationRefer function truth table for detailsUDQM, LDQM Data Input/Output Mask Controls output buffers in read mode and masks input data in write modeDQ0 ~ DQ15Data Input / Output Multiplexed data input / output pinVDD / VSS Power Supply / Ground Power supply for internal circuits and input buffersVDDQ / VSSQ Data Output Power /GroundPower supply for output buffersNC No Connection No connectionRev. 1.0 / Apr. 2007 4FUNCTIONAL BLOCK DIAGRAM1Mbit x 4banks x 16 I/O Synchronous DRAMRev. 1.0 / Apr. 2007 5Rev. 1.0 / Apr. 2007 6BASIC FUNCTIONAL DESCRIPTIONMode RegisterBA1BA0A11A10A9A8A7A6A5A4A3A2A1A0OP CodeCAS LatencyBTBurst LengthOP CodeA9Write Mode0Burst Read and Burst Write1Burst Read and Single WriteBurst TypeA3Burst Type 0Sequential 1InterleaveBurst LengthA2 A1A0Burst Length A3 = 0A3=1 00011 00122 01044 01188 100Reserved Reserved 101Reserved Reserved 1 10Reserved Reserved 111Full PageReservedCAS LatencyA6A5 A4CAS Latency 00 0Reserved 0 0 1Reserved0 1 020 1 1 3 1 0 0Reserved 1 0 1Reserved 1 1 0Reserved 111ReservedRev. 1.0 / Apr. 20077ABSOLUTE MAXIMUM RATINGDC OPERATING CONDITION (T A = 0 to 70o C / -40 to 85o C )Note: 1. All voltages are referenced to V SS = 0V2. VIH(max) is acceptable 5.6V AC pulse width with <=3ns of duration.3. VIL(min) is acceptable -2.0V AC pulse width with <=3ns of duration.AC OPERATING TEST CONDITION (T A = 0 to 70o C / -40 to 85o C , V DD =3.3±0.3V, V SS =0V)Note: 1.ParameterSymbolRating UnitAmbient Temperature T A0 ~ 70(Commercial part)oC -40 ~ 85(Industrial part)oCStorage TemperatureT STG -55 ~ 125o CVoltage on Any Pin relative to VSS V IN , V OUT -1.0 ~ 4.6V Voltage on VDD supply relative to VSS V DD , V DDQ-1.0 ~ 4.6V Short Circuit Output Current I OS 50mA Power DissipationP D 1W Soldering Temperature . TimeT SOLDER260 . 10o C . SecParameterSymbol Min Typ Max Unit Note Power Supply Voltage VDD, VDDQ3.0 3.3 3.6V 1Input High Voltage VIH 2.0 3.0VDDQ + 0.3V 1, 2Input Low VoltageVIL-0.3-0.8V1, 3ParameterSymbol Value Unit NoteAC Input High/Low Level VoltageVIH / VIL 2.4 / 0.4V Input Timing Measurement Reference Level Voltage Vtrip 1.4V Input Rise/Fall TimetR / tF 1ns Output Timing Measurement Reference Level Voltage Voutref 1.4V Output Load Capacitance for Access Time MeasurementCL30pF1Rev. 1.0 / Apr. 20078CAPACITANCE (f=1MHz, V DD =3.3V)DC CHARACTERRISTICS I (T A = 0 to 70o C / -40 to 85o C )Note: 1. V IN = 0 to 3.3V, All other balls are not tested under V IN =0V 2. D OUT is disabled, V OUT =0 to 3.6ParameterPinSymbol Min Max Unit Input capacitanceCLKCI1 2.0 4.0pF A0 ~ A11, BA0, BA1, CKE, CS, RAS, CAS, WE, LDQM, UDQM CI2 2.5 5.0pF Data input / output capacitanceDQ0 ~ DQ15CI/O3.05.5pFParameterSymbol Min Max Unit Note Input Leakage Current ILI -11uA 1 Output Leakage Current ILO -11uA 2 Output High Voltage VOH 2.4-V IOH = -4mA Output Low VoltageVOL-0.4VIOL = +4mARev. 1.0 / Apr. 20079DC CHARACTERISTICS II (T A = 0 to 70o C / -40 to 85o C )Note: 1. I DD1 and I DD4 depend on output loading and cycle rates. Specified values are measured with the output open 2. Min. of tRRC (Refresh RAS cycle time) is shown at AC CHARACTERISTICS II 3. HY57V641620FTP Series: Normal Power HY57V641620FLTP Series: Low PowerHY57V641620FSTP Series: Super Low PowerParameterSymbolTest ConditionSpeed Unit Note567HOperating Current IDD1Burst length=1, One bank active tRC ≥ tRC(min), IOL=0mA 120110100100mA 1Precharge Standby Cur-rentin Power Down ModeIDD2P CKE ≤ VIL(max), tCK = 15ns 2mA IDD2PS CKE ≤ VIL(max), tCK = ∞2mAPrecharge Standby Cur-rentin Non Power Down ModeIDD2NCKE ≥ VIH(min), CS ≥ VIH(min), tCK = 15ns Input signals are changed one time during 2clks.All other pins ≥ VDD-0.2V or ≤ 0.2V 18mAIDD2NS CKE ≥ VIH(min), tCK = ∞Input signals are stable.15Active Standby Current in Power Down ModeIDD3P CKE ≤ VIL(max), tCK = 15ns 3mAIDD3PSCKE ≤ VIL(max), tCK = ∞3Active Standby Current in Non Power Down ModeIDD3N CKE ≥ VIH(min), CS ≥ VIH(min), tCK = 15ns Input signals are changed one time during 2clks.All other pins ≥ VDD-0.2V or ≤ 0.2V 40mAIDD3NSCKE ≥ VIH(min), tCK = ∞Input signals are stable.35Burst Mode Operating CurrentIDD4tCK ≥ tCK(min), IOL=0mA All banks active120110100100mA 1Auto Refresh CurrentIDD5tRC ≥ tRC(min), All banks active170160150150mA 2Self Refresh CurrentIDD6CKE ≤ 0.2VNormal1mA3Low power 400uA Super Low power300uA3, 4Rev. 1.0 / Apr. 200710AC CHARACTERISTICS I (AC operating conditions unless otherwise noted)Note: 1. Assume t R / t F (input rise and fall time) is 1ns. If t R & t F > 1ns, then [(t R +t F )/2-1]ns should be added to the parameter. 2. Access time to be measured with input signals of 1V/ns edge rate, from 0.8V to 0.2V. If t R > 1ns, then (t R /2-0.5)ns should be added to the parameter.ParameterSymbol 567H Unit NoteMin Max Min Max Min Max Min Max System Clock Cycle TimeCL = 3tCK3 5.01000 6.010007.010007.51000ns CL = 2tCK210101010ns Clock High Pulse Width tCHW 1.75- 2.0- 2.0- 2.5-ns 1Clock Low Pulse Width tCLW1.75-2.0- 2.0- 2.5-ns 1Access Time From Clock CL = 3tAC3- 4.5- 5.4- 5.4- 5.4ns 2CL = 2tAC2- 6.0- 6.0- 6.0- 6.0ns Data-out Hold Time tOH 2.0- 2.0- 2.5- 2.5-ns Data-Input Setup Time tDS 1.5- 1.5- 1.5- 1.5-ns 1Data-Input Hold Time tDH 0.8-0.8-0.8-0.8-ns 1Address Setup Time tAS 1.5- 1.5- 1.5- 1.5-ns 1Address Hold Time tAH 0.8-0.8-0.8-0.8-ns 1CKE Setup Time tCKS 1.5- 1.5- 1.5- 1.5-ns 1CKE Hold Time tCKH 0.8-0.8-0.8-0.8-ns 1Command Setup Time tCS 1.5- 1.5- 1.5- 1.5-ns 1Command Hold TimetCH0.8-0.8-0.8-0.8-ns 1CLK to Data Output in Low-Z Time tOLZ 1.0- 1.0- 1.5- 1.5-ns CLK to Data Output in High-Z TimeCL = 3tOHZ3- 4.5- 5.4- 5.4- 5.4ns CL = 2tOHZ2- 6.0- 6.0- 6.0- 6.0nsRev. 1.0 / Apr. 200711AC CHARACTERISTICS II (AC operating conditions unless otherwise noted)Note: 1. A new command can be given t RRC after self refresh exit.ParameterSymbol 567H Unit Note Min Max Min Max Min Max Min Max RAS Cycle Time OperationtRC55-60-63-63-ns RAS Cycle Time Auto Refresh tRRC55-60-63-63-ns RAS to CAS Delay tRCD 15-18-20-20-ns RAS Active Time tRAS 38.7100K 42 100K 42 100K 42120K ns RAS Precharge TimetRP 15-18-20-20-ns RAS to RAS Bank Active Delay tRRD 10-12-14-15-ns CAS to CAS DelaytCCD1-1-1-1-CLK Write Command to Data-In De-laytWTL0 -0 -0 -0 -CLK Data-in to Precharge Command tDPL 2-2-2-2-CLKData-In to Active Command tDAL tDPL + tRPDQM to Data-Out Hi-Z tDQZ 2-2-2-2-CLK DQM to Data-In Mask tDQM 0-0-0-0-CLK MRS to New Command tMRD 2-2-2-2-CLK Precharge to Data Output High-ZCL = 3tPROZ33-3-3-3-CLK CL = 2tPROZ22-2-2-2-CLK Power Down Exit Time tDPE 1-1-1-1-CLK Self Refresh Exit Time tSRE 1-1-1-1-CLK 1Refresh TimetREF-64-64-64-64msCOMMAND TRUTH TABLECommand CKEn-1CKEn CS RAS CAS WE DQM ADDR A10/AP BA Note Mode Register Set H X L L L L X OP codeNo Operation H X H X X XX X L H H HBank Active H X L L H H X RA VReadH X L H L H X CA LVRead with Autopre-chargeHWriteH X L H L L X CA LVWrite with Autopre-chargeHPrecharge All BanksH X L L H L X X H XPrecharge selectedBankL V Burst Stop H X L H H L X XDQM H X V XAuto Refresh H H L L L H X XBurst-Read-Single-WRITE H X L L L L XA9 ball High(Other balls OP code)MRSModeSelf Refresh1Entry H L L L L H XX Exit L HH X X XXL H H HPrecharge power down Entry H LH X X XXXL H H HExit L HH X X XXL H H HClock Suspend Entry H LH X X XXXL V V VExit L H X XRev. 1.0 / Apr. 200712PACKAGE INFORMATION400mil 54pin Thin Small Outline PackageRev. 1.0 / Apr. 200713。

常用开关电源芯片大全之欧阳育创编

常用开关电源芯片大全第1章DC-DC电源转换器/基准电压源1.1 DC-DC电源转换器1.低噪声电荷泵DC-DC电源转换器AAT3113/AAT31142.低功耗开关型DC-DC电源转换器ADP30003.高效3A开关稳压器AP15014.高效率无电感DC-DC电源转换器FAN56605.小功率极性反转电源转换器ICL76606.高效率DC-DC电源转换控制器IRU30377.高性能降压式DC-DC电源转换器ISL64208.单片降压式开关稳压器L49609.大功率开关稳压器L4970A10.1.5A降压式开关稳压器L497111.2A高效率单片开关稳压器L497812.1A高效率升压/降压式DC-DC电源转换器L597013.1.5A降压式DC-DC电源转换器LM157214.高效率1A降压单片开关稳压器LM1575/LM2575/LM2575HV15.3A降压单片开关稳压器LM2576/LM2576HV16.可调升压开关稳压器LM257717.3A降压开关稳压器LM259618.高效率5A开关稳压器LM267819.升压式DC-DC电源转换器LM2703/LM270420.电流模式升压式电源转换器LM273321.低噪声升压式电源转换器LM275022.小型75V降压式稳压器LM500723.低功耗升/降压式DC-DC电源转换器LT107324.升压式DC-DC电源转换器LT161525.隔离式开关稳压器LT172526.低功耗升压电荷泵LT175127.大电流高频降压式DC-DC电源转换器LT176528.大电流升压转换器LT193529.高效升压式电荷泵LT193730.高压输入降压式电源转换器LT195631.1.5A升压式电源转换器LT196132.高压升/降压式电源转换器LT343333.单片3A升压式DC-DC电源转换器LT343634.通用升压式DC-DC电源转换器LT346035.高效率低功耗升压式电源转换器LT346436.1.1A升压式DC-DC电源转换器LT346737.大电流高效率升压式DC-DC电源转换器LT378238.微型低功耗电源转换器LTC175439.1.5A单片同步降压式稳压器LTC187540.低噪声高效率降压式电荷泵LTC191141.低噪声电荷泵LTC3200/LTC3200-542.无电感的降压式DC-DC电源转换器LTC325143.双输出/低噪声/降压式电荷泵LTC325244.同步整流/升压式DC-DC电源转换器LTC340145.低功耗同步整流升压式DC-DC电源转换器LTC340246.同步整流降压式DC-DC电源转换器LTC340547.双路同步降压式DC-DC电源转换器LTC340748.高效率同步降压式DC-DC电源转换器LTC341649.微型2A升压式DC-DC电源转换器LTC342650.2A两相电流升压式DC-DC电源转换器LTC342851.单电感升/降压式DC-DC电源转换器LTC344052.大电流升/降压式DC-DC电源转换器LTC344253.1.4A同步升压式DC-DC电源转换器LTC345854.直流同步降压式DC-DC电源转换器LTC370355.双输出降压式同步DC-DC电源转换控制器LTC373656.降压式同步DC-DC电源转换控制器LTC377057.双2相DC-DC电源同步控制器LTC380258.高性能升压式DC-DC电源转换器MAX1513/MAX151459.精简型升压式DC-DC电源转换器MAX1522/MAX1523/MAX152460.高效率40V升压式DC-DC电源转换器MAX1553/MAX155461.高效率升压式LED电压调节器MAX1561/MAX159962.高效率5路输出DC-DC电源转换器MAX156563.双输出升压式DC-DC电源转换器MAX1582/MAX1582Y64.驱动白光LED的升压式DC-DC电源转换器MAX158365.高效率升压式DC-DC电源转换器MAX1642/MAX164366.2A降压式开关稳压器MAX164467.高效率升压式DC-DC电源转换器MAX1674/MAX1675/MAX167668.高效率双输出DC-DC电源转换器MAX167769.低噪声1A降压式DC-DC电源转换器MAX1684/MAX168570.高效率升压式DC-DC电源转换器MAX169871.高效率双输出降压式DC-DC电源转换器MAX171572.小体积升压式DC-DC电源转换器MAX1722/MAX1723/MAX172473.输出电流为50mA的降压式电荷泵MAX173074.升/降压式电荷泵MAX175975.高效率多路输出DC-DC电源转换器MAX180076.3A同步整流降压式稳压型MAX1830/MAX183177.双输出开关式LCD电源控制器MAX187878.电流模式升压式DC-DC电源转换器MAX189679.具有复位功能的升压式DC-DC电源转换器MAX194780.高效率PWM降压式稳压器MAX1992/MAX199381.大电流输出升压式DC-DC电源转换器MAX61882.低功耗升压或降压式DC-DC电源转换器MAX62983.PWM升压式DC-DC电源转换器MAX668/MAX66984.大电流PWM降压式开关稳压器MAX724/MAX72685.高效率升压式DC-DC电源转换器MAX756/MAX75786.高效率大电流DC-DC电源转换器MAX761/MAX76287.隔离式DC-DC电源转换器MAX8515/MAX8515A88.高性能24V升压式DC-DC电源转换器MAX872789.升/降压式DC-DC电源转换器MC33063A/MC34063A90.5A升压/降压/反向DC-DC电源转换器MC33167/MC3416791.低噪声无电感电荷泵MCP1252/MCP125392.高频脉宽调制降压稳压器MIC220393.大功率DC-DC升压电源转换器MIC229594.单片微型高压开关稳压器NCP1030/NCP103195.低功耗升压式DC-DC电源转换器NCP1400A96.高压DC-DC电源转换器NCP140397.单片微功率高频升压式DC-DC电源转换器NCP141098.同步整流PFM步进式DC-DC电源转换器NCP142199.高效率大电流开关电压调整器NCP1442/NCP1443/NCP1444/NCP1445100.新型双模式开关稳压器NCP1501101.高效率大电流输出DC-DC电源转换器NCP1550102.同步降压式DC-DC电源转换器NCP1570103.高效率升压式DC-DC电源转换器NCP5008/NCP5009 104.大电流高速稳压器RT9173/RT9173A105.高效率升压式DC-DC电源转换器RT9262/RT9262A106.升压式DC-DC电源转换器SP6644/SP6645107.低功耗升压式DC-DC电源转换器SP6691108.新型高效率DC-DC电源转换器TPS54350109.无电感降压式电荷泵TPS6050x110.高效率升压式电源转换器TPS6101x111.28V恒流白色LED驱动器TPS61042112.具有LDO输出的升压式DC-DC电源转换器TPS6112x 113.低噪声同步降压式DC-DC电源转换器TPS6200x114.三路高效率大功率DC-DC电源转换器TPS75003115.高效率DC-DC电源转换器UCC39421/UCC39422116.PWM控制升压式DC-DC电源转换器XC6371117.白光LED驱动专用DC-DC电源转换器XC9116118.500mA同步整流降压式DC-DC电源转换器XC9215/XC9216/XC9217119.稳压输出电荷泵XC9801/XC9802120.高效率升压式电源转换器ZXLB16001.2 线性/低压差稳压器121.具有可关断功能的多端稳压器BAXXX122.高压线性稳压器HIP5600123.多路输出稳压器KA7630/KA7631124.三端低压差稳压器LM2937125.可调输出低压差稳压器LM2991126.三端可调稳压器LM117/LM317127.低压降CMOS500mA线性稳压器LP38691/LP38693128.输入电压从12V到450V的可调线性稳压器LR8129.300mA非常低压降稳压器(VLDO)LTC3025130.大电流低压差线性稳压器LX8610131.200mA负输出低压差线性稳压器MAX1735132.150mA低压差线性稳压器MAX8875133.带开关控制的低压差稳压器MC33375134.带有线性调节器的稳压器MC33998135.1.0A低压差固定及可调正稳压器NCP1117136.低静态电流低压差稳压器NCP562/NCP563137.具有使能控制功能的多端稳压器PQxx138.五端可调稳压器SI-3025B/SI-3157B139.400mA低压差线性稳压器SPX2975140.五端线性稳压器STR20xx141.五端线性稳压器STR90xx142.具有复位信号输出的双路输出稳压器TDA8133143.具有复位信号输出的双路输出稳压器TDA8138/TDA8138A144.带线性稳压器的升压式电源转换器TPS6110x145.低功耗50mA低压降线性稳压器TPS760xx146.高输入电压低压差线性稳压器XC6202147.高速低压差线性稳压器XC6204148.高速低压差线性稳压器XC6209F149.双路高速低压差线性稳压器XC64011.3 基准电压源150.新型XFET基准电压源ADR290/ADR291/ADR292/ADR293151.低功耗低压差大输出电流基准电压源MAX610x152.低功耗1.2V基准电压源MAX6120153.2.5V精密基准电压源MC1403154.2.5V/4.096V基准电压源MCP1525/MCP1541155.低功耗精密低压降基准电压源REF30xx/REF31xx156.精密基准电压源TL431/KA431/TLV431A第2章AC-DC转换器及控制器1.厚膜开关电源控制器DP104C2.厚膜开关电源控制器DP308P3.DPA-Switch系列高电压功率转换控制器DPA423/DPA424/DPA425/DPA4264.电流型开关电源控制器FA13842/FA13843/FA13844/FA138455.开关电源控制器FA5310/FA53116.PWM开关电源控制器FAN75567.绿色环保的PWM开关电源控制器FAN76018.FPS型开关电源控制器FS6M07652R9.开关电源功率转换器FS6Sxx10.降压型单片AC-DC转换器HV-2405E11.新型反激准谐振变换控制器ICE1QS0112.PWM电源功率转换器KA1M088013.开关电源功率转换器KA2S0680/KA2S088014.电流型开关电源控制器KA38xx15.FPS型开关电源功率转换器KA5H0165R16.FPS型开关电源功率转换器KA5Qxx17.FPS型开关电源功率转换器KA5Sxx18.电流型高速PWM控制器L499019.具有待机功能的PWM初级控制器L599120.低功耗离线式开关电源控制器L659021.LINK SWITCH TN系列电源功率转换器LNK304/LNK305/LNK30622.LINK SWITCH系列电源功率转换器LNK500/LNK501/LNK52023.离线式开关电源控制器M51995A24.PWM电源控制器M62281P/M62281FP25.高频率电流模式PWM控制器MAX5021/MAX502226.新型PWM开关电源控制器MC4460427.电流模式开关电源控制器MC4460528.低功耗开关电源控制器MC4460829.具有PFC功能的PWM电源控制器ML482430.液晶显示器背光灯电源控制器ML487631.离线式电流模式控制器NCP120032.电流模式脉宽调制控制器NCP120533.准谐振式PWM控制器NCP120734.低成本离线式开关电源控制电路NCP121535.低待机能耗开关电源PWM控制器NCP123036.STR系列自动电压切换控制开关STR8xxxx37.大功率厚膜开关电源功率转换器STR-F665438.大功率厚膜开关电源功率转换器STR-G865639.开关电源功率转换器STR-M6511/STR-M652940.离线式开关电源功率转换器STR-S5703/STR-S5707/STR-S570841.离线式开关电源功率转换器STR-S6401/STR-S6401F/STR-S6411/STR-S6411F 442.开关电源功率转换器STR-S651343.离线式开关电源功率转换器TC33369~TC3337444.高性能PFC与PWM组合控制集成电路TDA16846/TDA1684745.新型开关电源控制器TDA1685046.“绿色”电源控制器TEA150447.第二代“绿色”电源控制器TEA150748.新型低功耗“绿色”电源控制器TEA153349.开关电源控制器TL494/KA7500/MB375950.Tiny SwitchⅠ系列功率转换器TNY253、TNY254、TNY25551.Tiny SwitchⅡ系列功率转换器TNY264P~TNY268G52.TOP Switch(Ⅱ)系列离线式功率转换器TOP209~TOP22753.TOP Switch-FX系列功率转换器TOP232/TOP233/TOP23454.TOP Switch-GX系列功率转换器TOP242~TOP25055.开关电源控制器UCX84X56.离线式开关电源功率转换器VIPer12AS/VIPer12ADIP57.新一代高度集成离线式开关电源功率转换器VIPer53第3章功率因数校正控制/节能灯电源控制器1.电子镇流器专用驱动电路BL83012.零电压开关功率因数控制器FAN48223.功率因数校正控制器FAN75274.高电压型EL背光驱动器HV8265.EL场致发光背光驱动器IMP525/IMP5606.高电压型EL背光驱动器/反相器IMP8037.电子镇流器自振荡半桥驱动器IR21568.单片荧光灯镇流器IR21579.调光电子镇流器自振荡半桥驱动器IR215910.卤素灯电子变压器智能控制电路IR216111.具有功率因数校正电路的镇流器电路IR216612.单片荧光灯镇流器IR216713.自适应电子镇流器控制器IR252014.电子镇流器专用控制器KA754115.功率因数校正控制器L656116.过渡模式功率因数校正控制器L656217.集成背景光控制器MAX8709/MAX8709A18.功率因数校正控制器MC33262/MC3426219.固定频率电流模式功率因数校正控制器NCP165320.EL场致发光灯高压驱动器SP440321.功率因数校正控制器TDA4862/TDA486322.有源功率因数校正控制器UC385423.高频自振荡节能灯驱动器电路VK05CFL24.大功率高频自振荡节能灯驱动器电路VK06TL第4章充电控制器1.多功能锂电池线性充电控制器AAT36802.可编程快速电池充电控制器BQ20003.可进行充电速率补偿的锂电池充电管理器BQ20574.锂电池充电管理电路BQ2400x5.单片锂电池线性充电控制器BQ2401xB接口单节锂电池充电控制器BQ2402x7.2A同步开关模式锂电池充电控制器BQ241008.集成PWM开关控制器的快速充电管理器BQ29549.具有电池电量计量功能的充电控制器DS277010.锂电池充电控制器FAN7563/FAN756411.2A线性锂/锂聚合物电池充电控制器ISL629212.锂电池充电控制器LA5621M/LA5621V13.1.5A通用充电控制器LT157114.2A恒流/恒压电池充电控制器LT176915.线性锂电池充电控制器LTC173216.带热调节功能的1A线性锂电池充电控制器LTC173317.线性锂电池充电控制器LTC173418.新型开关电源充电控制器LTC198019.开关模式锂电池充电控制器LTC400220.4A锂电池充电器LTC400621.多用途恒压/恒流充电控制器LTC400822.4.2V锂离子/锂聚合物电池充电控制器LTC405223.可由USB端口供电的锂电池充电控制器LTC405324.小型150mA锂电池充电控制器LTC405425.线性锂电池充电控制器LTC405826.单节锂电池线性充电控制器LTC405927.独立线性锂电池充电控制器LTC406128.镍镉/镍氢电池充电控制器M62256FP29.大电流锂/镍镉/镍氢电池充电控制器MAX150130.锂电池线性充电控制器MAX150731.双输入单节锂电池充电控制器MAX1551/MAX155532.单节锂电池充电控制器MAX167933.小体积锂电池充电控制器MAX1736B接口单节锂电池充电控制器MAX181135.多节锂电池充电控制器MAX187336.双路输入锂电池充电控制器MAX187437.单节锂电池线性充电控制器MAX189838.低成本/多种电池充电控制器MAX190839.开关模式单节锂电池充电控制器MAX1925/MAX192640.快速镍镉/镍氢充电控制器MAX2003A/MAX200341.可编程快速充电控制器MAX712/MAX71342.开关式锂电池充电控制器MAX74543.多功能低成本充电控制器MAX846A44.具有温度调节功能的单节锂电池充电控制器MAX8600/MAX860145.锂电池充电控制器MCP73826/MCP73827/MCP7382846.高精度恒压/恒流充电器控制器MCP73841/MCP73842/MCP73843/MCP73844 647.锂电池充电控制器MCP73861/MCP7386248.单节锂电池充电控制器MIC7905049.单节锂电池充电控制器NCP180050.高精度线性锂电池充电控制器VM7205。

PQ3220

4.32

5.02

7.62

30.12

0.8

寸實

2

33.23

34.13

21.36

4.25

5.03

7.63

30.13

0.8

檢測

驗數

3

33.25

34.10

21.36

4.30

5.02

7.60

30.12

0.8

據

4

33.20

34.15

21.36

4.35

5.03

7.60

30.10

0.8

5

33.20

34.10

21.35

4.30

5.02

7.63

30.18

0.8

結果

OK

OK

OK

OK

OK

OK

OK

OK

項目

A.可焊性

HI-POT(P-S)

HI-POT(P-C S-C)

HI-POT (P-P)

L(1-4)

測試條件

255±5℃ 2±0.5S

AC 3.6KV

AC 1.5KV AC 1.2KV

1KHZ 0.3V

60HZ 5mA 3S 60HZ 5mA 3S 60HZ 5mA 3S

S1 7,8,9

P2 5--6 0.20*2 4T

P1 2--4 0.30*2 13T 0.025*7*66 1T

S1 10,11,12--7,8,9 0.40*3 5T 0.025*7*60 1T

P1 1--2 0.30*2 14T

BOBBIN WALL

0.025*9.5 3T 0.025*9.5 3T 0.025*9.5 3T 0.025*9.5 3T 0.025*9.5 3T 0.025*9.5 3T

亿芯存储器选型手册2010

低速低功耗SRAM 高速SRAM● DRAMSDRAM DDR-ⅠS DRAM DDR-Ⅱ SDRAMMobile SDRAM Mobile DDR-ⅠS DRAM● FLASHNOR FLASH NAND FLASH● EEPROMI2C总线系列 Microwire总线系列 SPI总线系列1 2亿芯伟业来扬包装数量表托盘和管装 Tray and Tube卷带包装 Tape and Reel3 4亿芯伟业力晶半导体股份有限公司—华人地区最大的内存晶圆厂Powerchip Semiconductor Corp.力晶半导体股份有限公司于1994年12月创立于台湾新竹科学园区,业务范围涵盖DRAM 制造、NAND FLASH 闪存制造和晶圆代工三大类别。

目前为全球领先之全方位内存公司,不仅拥有最先进制程技术,更具备世界级水准之产品良率及品质。

自1996年第一座8英寸晶圆厂投入生产,力晶持续投入巨资,扩大生产规模。

2002年第一座12英寸晶圆厂正式量产,2005年第二座12英寸晶圆厂投入生产,2006年力晶花费53亿新台币购入旺宏半导体晶圆三厂,2007年与日本尔必达合资设立的瑞晶电子第一座12英寸晶圆厂启用,2008年开始动工兴建第四、五座12英寸晶圆厂。

一连串购厂、建厂的作为,展现出力晶半导体积极投资、拓展全球市场的决心与行动力。

5 6亿芯伟业产品简介:串行E 2PROM 是可在线电擦除和电写入的存储器,具有体积小、接口简单、数据保存可靠、可在线改写、功耗低等特点,而且为低电压写入,在单片机系统中应用十分普遍。

Aplus 公司的串行E 2PROM 兼容工业上最受欢迎的三种总线:I 2C 总线、Microwire 总线及SPI 总线。

Aplus 公司的产品提供1~256K 的高密度存储,以及1.8V~5.5V 的宽电压操作范围。

产品特性:● 支持标准和快速I 2C 协议、兼容SPI/Microwire 总线 ● 宽工作电压:1.8~5.5V ● 工业级温度范围● 对全部存储器进行硬件写保护 ● 可编程/擦除100万次 ● 数据保存期100年NOR FLASH78亿芯伟业低压差电压稳压器LDO电荷泵白光LED驱动器升压型白光LED驱动器降压型DC/DC转换器锂电池充电电路智能电源开关9 10亿芯伟业时钟电路低速低功耗S R A M 代换表11 12亿芯伟业高速S R A M 代换表DRAM产品代换表13 14亿芯伟业音频放大器的分类音频放大器的目的是以要求的音量和功率水平在发声输出元件上重新产生真实、高效和低失真的输入音频信号。

HYS72D64020GR-7-B资料

2.5V 184-pin Registered DDR-I SDRAM Modules 256MB,512MB &1GByte Modules PC1600&PC2100Preliminary Datasheet revision 0.91DescriptionThe HYS 72Dxx0x0GR are industry standard 184-pin 8-byte Dual in-line Memory Modules (DIMMs)organized as 32M ×72(256MB),64M ×72(512MB)and 128M ×72(1GB).The memory array is designed with Double Data Rate Synchronous DRAMs for ECC applications.All control and address signals are re-driven on the DIMM using register devices and a PLL for the clock distribution.This reduces capacitive loading to the system bus,but adds one cycle to the SDRAM timing.A variety of decoupling capacitors are mounted on the PC board.The DIMMs feature serial presence detect based on a serial E 2PROM device using the 2-pin I 2C protocol.The first 128bytes are programmed with configuration data and the second 128bytes are available to the customer.•184-pin Registered 8-Byte Dual-In-Line DDR-I SDRAM Module for PC and Server main memory applications •One bank 32M ×72,64M x 72,and two bank 64M x 72and 128M ×72organization •JEDEC standard Double Data RateSynchronous DRAMs (DDR-I SDRAM)with a single +2.5V (±0.2V)power supply •Built with 256Mbit DDR-I SDRAMs in 66-Lead TSOPII package •Programmable Latency,Burst Length,and Wrap Sequence (Sequential &Interleave)•Auto Refresh (CBR)and Self Refresh •All inputs and outputs SSTL_2compatible •Re-drive for all input signals using register and PLL devices.•Serial Presence Detect with E 2PROM •Jedec standard MO-206form factor:133.35mm (nom.)×43.18mm (nom.)×4.00mm (max.)(6,80mm max.with stacked components)•Jedec standard reference layout:Raw Cards A,B and C •Gold plated contacts•Performance:-7-8UnitComponent Speed Grade DDR266A DDR200Module Speed GradePC2100PC1600f CK Clock Frequency (max.)@CL =2.5143125MHz f CKClock Frequency (max.)@CL =2133100MHzOrdering InformationType Compliance Code Description SDRAMTechnologyPC2100(CL=2):HYS72D32000GR-7-B PC2100R-20330-A1one bank256MB Reg.DIMM256MBit(x8) HYS72D64000GR-7-B PC2100R-20330-B1one bank512MB Reg.DIMM256Mbit(x4) HYS72D64020GR-7-B PC2100R-20330-A1two banks512MB Reg.DIMM256MBit(x8) HYS72D128020GR-7-B PC2100R-20330-C1two banks1GByte Reg.DIMM256MBit(x4)(stacked withsoldering process) HYS72D128021GR-7-B PC2100R-20330-C1two banks1GByte Reg.DIMM256MBit(x4)(stacked withlaser weldingprocess)PC1600(CL=2):HYS72D32000GR-8-B PC1600R-20220-A1one bank256MB Reg.DIMM256MBit(x8) HYS72D64000GR-8-B PC1600R-20220-B1one bank512MB Reg.DIMM256Mbit(x4) HYS72D64020GR-8-B PC1600R-20220-A1two banks512MB Reg.DIMM256MBit(x8) HYS72D128020GR-8-B PC1600R-20220-C1two banks1GByte Reg.DIMM256MBit(x4)(stacked withsoldering process) HYS72D128021GR-8-B PC1600R-20220-C1two banks1GByte Reg.DIMM256MBit(x4)(stacked withlaser weldingprocess)Note:All part numbers end with a place code(not shown),designating the silicon-die revision.Reference information available on request.Example:HYS72D32000GR-8-B,indicating Rev.B die are used for SDRAM componentsThe Compliance Code is printed on the module labels and describes the speed sort fe.“PC2100R”,the latencies(f.e.“20330”means CAS latency=2,trcd latency=3and trp latency=3)and the Raw Card used for this module.Pin Definitions and FunctionsA0-A11,A12Address Inputs(A12for256Mb&512Mb based modules)V DD Power(+2.5V)BA0,BA1Bank Selects VSSGroundD Q0-D Q63Data Input/Output VDD QI/O Driver power supplyCB0-CB7Check Bits(x72organization only)VDDIDVDD Indentification flagRAS Row Address Strobe VDDSPDEEPROM power supplyCAS Column Address Strobe VREFI/O reference supply WE Read/Write Input SCL Serial bus clockCKE0,CKE1Clock Enable SDA Serial bus data lineD Q S0-D Q S8SDRAM low data strobes SA0-SA2slave address select CK0,CK0Differential Clock Input NC no connectDM0-DM8D Q S9-D Q S17SDRAM low data mask/high data strobesDU don’t useCS0-CS1Chip Selects RESET Reset pin(forces registerinputs low)*)*)for detailed description of the Power Up and Power Management on DDR Registered DIMMs see the Application Note at the end of this datasheetAddress FormatDensity Organization MemoryBanks SDRAMs#ofSDRAMs#of row/bank/columns bitsRefresh Period Interval256MB32M x72132M x8913/2/108k64ms7.8µs 512MB64M×72164M×41813/2/118k64ms7.8µs 512MB64M x72232M x81813/2/108k64ms7.8µs 1GB128M×72264M×43613/2/118k64ms7.8µsPin ConfigurationBlock Diagram:One Bank32Mb x72DDR-I SDRAM DIMM Module HYS72D32000GR using x8organized SDRAMs on Raw Card Version ABlock Diagram:Two Bank64Mb x72DDR-I SDRAM DIMM Modules HYS72D64020GR Using x8Organized SDRAMs on Raw Card Version ABlock Diagram:One Bank64Mb x72DDR-I SDRAM DIMM Modules HYS72D64000GR using x4Organized SDRAMs on Raw Card Version BBlock Diagram:Two Bank128Mb x72DDR-I SDRAM DIMM Modules HYS72D128020GR using x4Organized SDRAMs on Raw Card Version CAbsolute Maximum RatingsParameter Symbol Limit Values Unitmin.max.Input/Output voltage relative to VSSV IN,V OUT–0.5 3.6VPower supply voltage on VDD /VDD Qto VSSV DD,V DD Q–0.5 3.6VStorage temperature range TSTG-55+150o CPower dissipation(per SDRAM component)PD–1WData out current(short circuit)IOS–50mA Permanent device damage may occur if“Absolute Maximum Ratings”are exceeded.Functional operation should be restricted to recommended operation conditions.Exposure to higher than recommended voltage for extended periods of time affect device reliabilitySupply Voltage LevelsParameter Symbol Limit Values Unit Notesmin.nom.max.Device Supply Voltage VDD2.3 2.5 2.7V-Output Supply Voltage VDD Q2.3 2.5 2.7V1)Input Reference Voltage VREF 0.49x VDD Q0.5x VDD Q0.51x VDD QV2)Termination Voltage VTTV REF–0.04V REF V REF+0.04V3)EEPROM supply voltage VDDSPD2.3 2.53.6V1Under all conditions,VDD Q must be less than or equal to VDD2Peak to peak AC noise on VREF may not exceed±2%VREF(DC).V REF is also expected to track noise variations in V DD Q.3VTT of the transmitting device must track VREFof the receiving device.DC Operating Conditions(SSTL_2Inputs)(V DD Q=2.5V,T A=70°C,Voltage Referenced to V SS)Parameter Symbol Limit Values Unit Notesmin.max.DC Input Logic High VIH(DC)V REF+0.15V DD Q+0.3V1)DC Input Logic Low VIL(DC)–0.30VREF–0.15V–Input Leakage Current IIL–55µA1)Output Leakage Current IOL–55µA2)1)The relationship between the VDD Q of the driving device and the VREFof the receiving device is whatdetermines noise margins.However,in the case of VIH(max)(input overdrive),it is the VDD Qof the receivingdevice that is referenced.In the case where a device is implemented such that it supports SSTL_2inputs buthas no SSTL_2outputs(such as a translator),and therefore no VDD Q supply voltage connection,inputs musttolerate input overdrive to3.0V(High corner VDD Q +300mV).2)For any pin under test input of0V≤VIN≤V DD Q+0.3V.Values are shown per DDR-SDRAM component.Operating,Standby and Refresh Currents(PC1600)Operating,Standby and Refresh Currents(PC2100)Electrical Characteristics&AC Timing for DDR-I components (for reference only)≤ 70 °C; V DD Q=2.5V± 0.2V;V DD=2.5V± 0.2V)(0°C≤ TAElectrical Characteristics&AC Timing for DDR-I components (for reference only)≤ 70 °C; V DD Q=2.5V± 0.2V;V DD=2.5V± 0.2V)(0°C≤ TAPackage Outlines Raw Card A(one memory bank)Package Outlines Raw Card A(two memory banks)Package Outlines Raw Card BPackage Outlines Raw Card CAPPLICATION NOTE:Power Up and Power Management on DDR Registered DIMMs(according to JEDEC ballot JC-42.5Item1173)184-pin Double Data Rate(DDR)Registered DIMMs include two new features to facilitate controlled power-up and to minimize power consumption during low power mode.One feature is externally controlled via a system-generated RESET signal;the second is based on module detection of the input clocks.These enhancements permit the modules to power up with SDRAM outputs in a High-Z state(eliminating risk of high current dissipa-tions and/or dotted I/Os),and result in the powering-down of module support devices(registers and Phase-Locked Loop)when the memory is in Self-Refresh mode.The new RESET pin controls power dissipation on the module’s registers and ensures that CKE and other SDRAM inputs are maintained at a valid‘low’level during power-up and self refresh.When RESET is at a low level,all the register outputs are forced to a low level,and all differential register input receivers are powered down,resulting in very low register power consumption.The pin,located on DIMM tab#10,is driven from the system as an asynchronous signal according to the attached ing this function also permits the system and DIMM clocks to be stopped during memory Self Refresh operation,while ensuring that the SDRAMs stay in Self Refresh mode.The function for RESET is as follows:As described in the table above,a low on the input ensures that the Clock Enable(CKE)signal(s)are maintained low at the SDRAM pins(CKE being one of the'Q'signals at the register output).Holding CKE low maintains a high impedance state on the SDRAM D Q,D Q S and DM outputs—where they will remain until acti-vated by a valid‘read’cycle.CKE low also maintains SDRAMs in Self Refresh mode when applicable.The DDR PLL devices automatically detect clock activity above20MHz.When an input clock frequency of20MHz or greater is detected,the PLL begins operation and initiates clock frequency lock(the minimum operat-ing frequency at which all specifications will be met is95MHz).If the clock input frequency drops below20MHz (actual detect frequency will vary by vendor),the PLL VCO(Voltage Controlled Oscillator)is stopped,outputs aremade High-Z,and the differential inputs are powered down—resulting in a total PLL current consumption of less e of this low power PLL function makes the use of the PLL RESET(or G pin)unnecessary,and it is tied inactive on the DIMM.This application note describes the required and optional system sequences associated with the DDR Regis-tered DIMM''function.It is important to note that all references to CKE refer to both CKE0and CKE1for a2-bank DIMM.Because applies to all DIMM register devices,it is therefore not possible to uniquely control CKE to one physical DIMM bank through the use of the RESET pin.Power-Up Sequence with RESET—Required1.The system sets RESET at a valid low level.This is the preferred default state during power-up.This input condition forces all register outputs to a low state independent of the condition on the register inputs(data and clock),ensuring that CKE is at a stable low-level at the DDR SDRAMs.2.The power supplies should be initialized according to the JEDEC-approved initialization sequence for DDR SDRAMs.3.Stabilization of Clocks to the SDRAMThe system must drive clocks to the application frequency(PLL operation is not assured until the input clock reaches20MHz).Stability of clocks at the SDRAMs will be affected by all applicable system clock devices, and time must be allotted to permit all clock devices to settle.Once a stable clock is received at the DIMM PLL,the required PLL stabilization time(assuming power to the DIMM is stable)is100microseconds.Whena stable clock is present at the SDRAM input(driven from the PLL),the DDR SDRAM requires200µsec priorto SDRAM operation.4.The system applies valid logic levels to the data inputs of the register(address and controls at the DIMM con-nector).CKE must be maintained low and all other inputs should be driven to a known state.In general these com-mands can be determined by the system designer.One option is to apply an SDRAM‘NOP’command(with CKE low),as this is the first command defined by the JEDEC initialization sequence(ideally this would be a ‘NOP Deselect’command).A second option is to apply low levels on all of the register inputs to be consistent with the state of the register outputs.5.The system switches RESET to a logic‘high’level.The SDRAM is now functional and prepared to receive commands.Since the RESET signal is asynchronous, setting the RESET timing in relation to a specific clock edge is not required(during this period,register inputs must remain stable).6.The system must maintain stable register inputs until normal register operation is attained.The registers have an activation time that allows their clock receivers,data input receivers,and output drivers sufficient time to be turned on and become stable.During this time the system must maintain the valid logic levels described in step5.It is also a functional requirement that the registers maintain a low state at the CKE outputs to guarantee that the DDR SDRAMs continue to receive a low level on CKE.Register activation time (t(ACT)),from asynchronous switching of RESET from low to high until the registers are stable and ready to accept an input signal,is specified in the register and DIMM do-umentation.7.The system can begin the JEDEC-defined DDR SDRAM power-up sequence(according to the JEDEC-pproved initialization sequence).Self Refresh Entry(RESET low,clocks powered off)—OptionalSelf Refresh can be used to retain data in DDR SDRAM DIMMs even if the rest of the system is powered down and the clocks are off.This mode allows the DDR SDRAMs on the DIMM to retain data without external clocking. Self Refresh mode is an ideal time to utilize the RESET pin,as this can reduce register power consumption low deactivates register CK and CK,data input receivers,and data output drivers).1.The system applies Self Refresh entry command.(CKE→Low,CS→Low,RAS → Low,CAS→Low,WE→High)Note:The commands reach the DDR SDRAM one clock later due to the additional register pipelining on a Registered DIMM.After this command is issued to the SDRAM,all of the address and control and clock input conditions to the SDRAM are Don’t Cares—with the exception of CKE.2.The system sets RESET at a valid low level.This input condition forces all register outputs to a low state,independent of the condition on the registerm inputs(data and clock),and ensures that CKE,and all other control and address signals,are a stable low-level at the DDR SDRAMs.Since the RESET signal is asynchronous,setting the RESET timing in relation toa specific clock edge is not required.3.The system turns off clock inputs to the DIMM.(Optional)a.In order to reduce DIMM PLL current,the clock inputs to the DIMM are turned off,resulting in High-Z clockinputs to both the SDRAMs and the registers.This must be done after the RESET deactivate time of the reg-ister(t(INACT)).The deactivate time defines the time in which the clocks and the control and address sig-nals must maintain valid levels after RESET low has been applied and is specified in the register and DIMM documentation.b.The system may release DIMM address and control inputs to High-Z.This can be done after the RESET deactivate time of the register.The deactivate time defines the time in which the clocks and the control and the address signals must maintain valid levels after RESET low has been applied.It is highly recommended that CKE continue to remain low during this operation.4.The DIMM is in lowest power Self Refresh mode.Self Refresh Exit(RESET low,clocks powered off)—Optional1.Stabilization of Clocks to the SDRAM.The system must drive clocks to the application frequency(PLL operation is not assured until the input clock reaches~20MHz).Stability of clocks at the SDRAMs will be affected by all applicable system clock devices, and time must be allotted to permit all clock devices to settle.Once a stable clock is received at the DIMM PLL,the required PLL stabilization time(assuming power to the DIMM is stable)is100microseconds.2.The system applies valid logic levels to the data inputs of the register(address and controls at the DIMM con-nector).CKE must be maintained low and all other inputs should be driven to a known state.In general these com-mands can be determined by the system designer.One option is to apply an SDRAM‘NOP’command(with CKE low),as this is the first command defined by the JEDEC Self Refresh Exit sequence(ideally this would be a‘NOP Deselect’command).A second option is to apply low levels on all of the register inputs,to be con-sistent with the state of the register outputs.3.The system switches to a logic‘high’level.The SDRAM is now functional and prepared to receive commands.Since the RESET signal is asynchronous, timing relationship to a specific clock edge is not required(during this period,register inputs must remain stable).4.The system must maintain stable register inputs until normal register operation is attained.The registers have an activation time that allows the clock receivers,input receivers,and output drivers suffi-cient time to be turned on and become stable.During this time the system must maintain the valid logic levels described in Step2.It is also a functional requirement that the registers maintain a low state at the CKE out-puts to guarantee that the DDR SDRAMs continue to receive a low level on CKE.Register activation time(t (ACT)),from asynchronous switching of RESET from low to high until the registers are stable and ready to accept an input signal,is specified in the register and DIMM do-umentation.5.System can begin the JEDEC-defined DDR SDRAM Self Refresh Exit Procedure.Self Refresh Entry(RESET low,clocks running)—OptionalAlthough keeping the clocks running increases power consumption from the on-DIMM PLL during self refresh, this is an alternate operating mode for these DIMMs.1.System enters Self Refresh entry command.(CKE→Low,CS→Low,RAS→Low,CAS→Low,WE→High)Note:The commands reach the DDR SDRAM one clock later due to the additional register pipelining on a Registered DIMM.After this command is issued to the SDRAM,all of the address and control and clock input conditions to the SDRAM are Don’t Cares—with the exception of CKE.2.The system sets RESET at a valid low level.This input condition forces all register outputs to a low state,independent of the condition on the data and clock register inputs,and ensures that CKE is a stable low-level at the DDR SDRAMs.3.The system may release DIMM address and control inputs to High-Z.This can be done after the RESET deactivate time of the register(t(INACT)).The deactivate time describes the time in which the clocks and the control and the address signals must maintain valid levels afterlow has been applied.It is highly recommended that CKE continue to remain low during the operation.4.The DIMM is in a low power,Self Refresh mode.Self Refresh Exit(RESET low,clocks running)—Optional1.The system applies valid logic levels to the data inputs of the register(address and controls at the DIMM con-nector).CKE must be maintained low and all other inputs should be driven to a known state.In general these com-mands can be determined by the system designer.One option is to apply an SDRAM‘NOP’command(with CKE low),as this is the first command defined by the Self Refresh Exit sequence(ideally this would be a ‘NOP Deselect’command).A second option is to apply low levels on all of the register inputs to be consistent with the state of the register outputs.2.The system switches to a logic'high'level.The SDRAM is now functional and prepared to receive commands.Since the signal is asynchronous, it does not need to be tied to a particular clock edge(during this period,register inputs must continue to remain stable).3.The system must maintain stable register inputs until normal register operation is attained.The registers have an activation time that allows the clock receivers,input receivers,and output drivers suffi-cient time to be turned on and become stable.During this time the system must maintain the valid logic levels described in Step1.It is also a functional requirement that the registers maintain a low state at the CKE out-puts in order to guarantee that the DDR SDRAMs continue to receive a low level on CKE.This activation time,from asynchronous switching of from low to high,until the registers are stable and ready to accept an input signal,is t(ACT)as specified in the register and DIMM documentation.4.The system can begin JEDEC defined DDR SDRAM Self Refresh Exit Procedure.Self Refresh Entry/Exit(RESET high,clocks running)—OptionalAs this sequence does not involve the use of the RESET function,the JEDEC standard SDRAM specification explains in detail the method for entering and exiting Self Refresh for this case.Self Refresh Entry(RESET high,clocks powered off)—Not PermissibleIn order to maintain a valid low level on the register output,it is required that either the clocks be running and the system drive a low level on CKE,or the clocks are powered off and RESET is asserted low according to thesequence defined in this application not e.In the case where remains high and the clocks are powered off,the PLL drives a High-Z clock input into the register clock input.Without the low level on RESET an unknown DIMM state will result.。

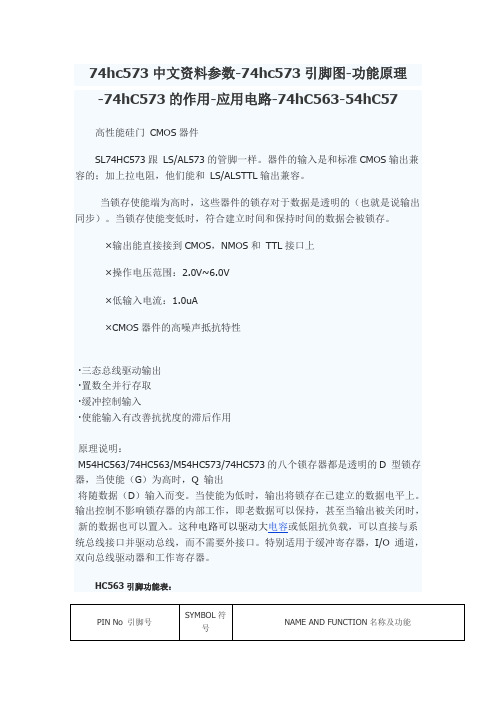

74hc573完整中文资料

74hc573中文资料参数-74hc573引脚图-功能原理-74hC573的作用-应用电路-74hC563-54hC57高性能硅门CMOS器件SL74HC573跟LS/AL573的管脚一样。

器件的输入是和标准CMOS输出兼容的;加上拉电阻,他们能和LS/ALSTTL输出兼容。

当锁存使能端为高时,这些器件的锁存对于数据是透明的(也就是说输出同步)。

当锁存使能变低时,符合建立时间和保持时间的数据会被锁存。

×输出能直接接到CMOS,NMOS和TTL接口上×操作电压范围:2.0V~6.0V×低输入电流:1.0uA×CMOS器件的高噪声抵抗特性·三态总线驱动输出·置数全并行存取·缓冲控制输入·使能输入有改善抗扰度的滞后作用原理说明:M54HC563/74HC563/M54HC573/74HC573的八个锁存器都是透明的D 型锁存器,当使能(G)为高时,Q 输出将随数据(D)输入而变。

当使能为低时,输出将锁存在已建立的数据电平上。

输出控制不影响锁存器的内部工作,即老数据可以保持,甚至当输出被关闭时,新的数据也可以置入。

这种电路可以驱动大电容或低阻抗负载,可以直接与系统总线接口并驱动总线,而不需要外接口。

特别适用于缓冲寄存器,I/O 通道,双向总线驱动器和工作寄存器。

HC563引脚功能表:HC573引脚功能表:图1 HC573引脚图图2 HC573 国际电工委员会逻辑符号图3 HC563引脚图图4 HC563 国际电工委员会逻辑符号图5 HC563 逻辑图图6 HC573 逻辑图图7 输入输出等效电路真值表:ABSOLUTE MAXIMUM RATINGS绝对最大额定值:Top Operating Temperature: M54HC Series M74HC Series 操作温度:M54HC系列M74HC系列-55 to +125 -40 to +85℃tr,tf Input Rise and Fall Time输入上升和下降时间VCC =2V0 to 1000ns VCC=4.5V0 to 500VCC =6V0 to 400VOHHigh Level Output Voltage输出高电平电压2.0 VI = VIH or VILIO=-20 μA1.92.0-1.9 -1.9 -V4.54.44.54.44.4---6.05.96.05.95.9-4.5IO=-6.0mA4.184.314.134.10-6.0IO=-7.8 mA5.685.85.635.60-VOLLow Level Output Voltage输出低电平电压2.0 VI = VIH or VILIO=20μA-0.0 0.1 -0.1-0.1V4.5-0.00.1 0.10.16.0-0.00.10.10.14.5IO=6.0mA-0.170.260.330.406.0IO=7.8mA-0.180.260.330.40IIInput Leakage Current输入漏电流6.0VI =VCC or GND--±0.1-±1±1μA IOZState Output Off State Current关断状态3态输出电流6.0VI =VIH or VIL VO =VCC or GND--±0.5-±5.0-±10μAICCQuiescent Supply Current静态电源电流6.0VI =VCC or GND--4-40-80μA应用电路图:点击图片查看大图图8。

太阳微系统Sun Netra CP3220刀片服务器产品说明书