SM20MT24C中文资料

SM20中文资料

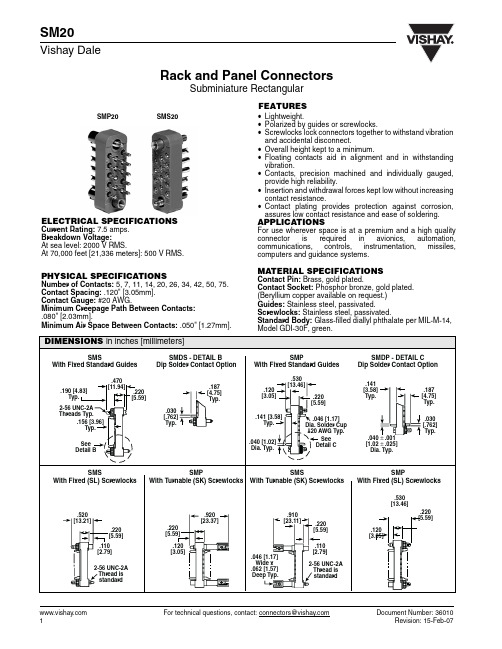

Rack and Panel ConnectorsSubminiature Rectangular For technical questions, contact: connectors@Document Number: 36010SM20Vishay DaleFEATURES•Lightweight.•Polarized by guides or screwlocks.•Screwlocks lock connectors together to withstand vibration and accidental disconnect.•Overall height kept to a minimum.•Floating contacts aid in alignment and in withstanding vibration.•Contacts, precision machined and individually gauged,provide high reliability.•Insertion and withdrawal forces kept low without increasing contact resistance.•Contact plating provides protection against corrosion,assures low contact resistance and ease of soldering.SMP20SMS20ELECTRICAL SPECIFICATIONSCurrent Rating: 7.5 amps.Breakdown Voltage:At sea level: 2000 V RMS.At 70,000 feet [21,336 meters]: 500 V RMS.PHYSICAL SPECIFICATIONSNumber of Contacts: 5, 7, 11, 14, 20, 26, 34, 42, 50, 75.Contact Spacing: .120" [3.05mm].Contact Gauge: #20 AWG.Minimum Creepage Path Between Contacts:.080" [2.03mm].Minimum Air Space Between Contacts: .050" [1.27mm].APPLICATIONSFor use wherever space is at a premium and a high quality connector is required in avionics, automation,communications, controls, instrumentation, missiles,computers and guidance systems.MATERIAL SPECIFICATIONSContact Pin: Brass, gold plated.Contact Socket: Phosphor bronze, gold plated.(Beryllium copper available on request.)Guides: Stainless steel, passivated.Screwlocks: Stainless steel, passivated.Standard Body: Glass-filled diallyl phthalate per MIL-M-14,Model GDI-30F, green.SM20Vishay DaleDocument Number: 36010For technical questions, contact: connectors@ For technical questions, contact: connectors@Document Number: 36010SM20Vishay DaleVishay DaleDocument Number: 36010For technical questions, contact: connectors@ Disclaimer Legal Disclaimer NoticeVishayAll product specifications and data are subject to change without notice.Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, “Vishay”), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.Vishay disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay’s terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay.The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay for any damages arising or resulting from such use or sale. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.Product names and markings noted herein may be trademarks of their respective owners.元器件交易网。

M24C32,M24C64--存储芯片手册免费下载

64Kbit and 32Kbit Serial I²C Bus EEPROM

FEATURES SUMMARY

■ Two-Wire I2C Serial Interface Supports 400kHz Protocol

■ Single Supply Voltage: – 4.5 to 5.5V for M24Cxx – 2.5 to 5.5V for M24Cxx-W – 1.8 to 5.5V for M24Cxx-R

Table 1. Product List

Reference

Part Number

M24C64

M24C64

M24C64-W

M24C64-R

M24C32

M24C32

M24C32-W

M24C32-R

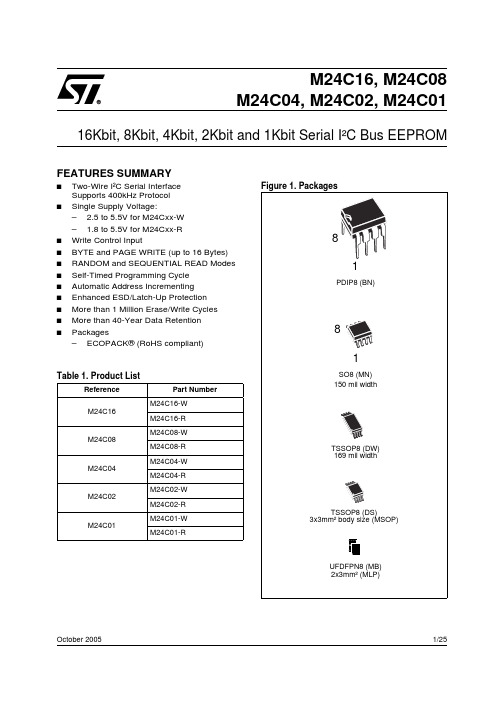

Figure 1. Packages

8 1

PDIP8 (BN)

8 1

SO8 (MN) 150 mil width

MEMORY ORGANIZATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Figure 6. Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

TSSOP8 (DW) 169 mil width

UFDFPN8 (MB) 2x3mm² (MLP)

24c02中文资料

24c02中文资料1. 简介24c02是Microchip公司推出的一种串行电子可擦写可编程读写存储器,属于EEPROM(Electrically Erasable Programmable Read-Only Memory)系列。

它采用2-wire串行总线(I2C)接口,具有体积小、功耗低、可靠性高等特点。

本文档将详细介绍24c02的硬件特性、接口规范、存储容量和使用方法。

2. 硬件特性24c02的主要硬件特性如下:•存储容量:24c02有256个字节,每个字节有8位,总计拥有2Kb的存储空间。

•工作电源:24c02需要使用3.3V到5V的供电电压,支持广泛的电源电压范围。

•通信接口:24c02使用I2C串行总线进行通信,具有两根信号线:串行数据线(SDA)和串行时钟线(SCL)。

•封装类型:24c02有多种封装类型可供选择,如DIP(双列直插式封装)、SOP(小型轻负载封装)等。

3. 接口规范24c02采用I2C串行总线接口,其接口规范如下:•数据传输方式:24c02支持字节读写操作和页写操作。

字节读写操作是指每次读写一个字节的数据;页写操作是指每次可以写入8个连续字节的数据。

•起始信号和停止信号:在I2C总线上进行通信时,需要发送起始信号(Start)和停止信号(Stop)以标识数据传输的开始和结束。

•从器件地址:24c02有多个从器件地址可供选择,通过设置硬件地址引脚,可以实现多个24c02器件的级联。

4. 存储容量24c02的存储容量为2Kb,相当于256个字节。

每个字节有8位,可存储0x00到0xFF的数据。

这些存储空间可以被分为多个页,每页包含8个字节。

5. 使用方法以下是24c02的基本使用方法,供参考:•初始化:将24c02与主控芯片(如单片机)连接,并提供正常的供电电源。

同时,设置24c02的硬件地址引脚,确保能正确寻址。

•写入数据:选择要写入数据的存储地址,发送起始信号和器件地址,然后发送数据字节。

24c02中文官方资料手册pdf

w 址输入脚 A0 A1 A2 可悬空或连接到 Vss 如果只有一个 24WC01 被总线寻址 这三个地址输入

脚 A0 A1 A2 必须连接到 Vss

当使用 24WC04 时最多可连接 4 个器件 该器件仅使用 A1 A2 地址管脚 A0 管脚未用 可以连

符号

参数

最小

典型

最大 单位

测试条件

ICC 电源电流

3

mA

FSCL=100KHz

ISB ILI ILO VIL VIH VOL1 VOL2

备用电流(Vcc=5.0V) 输入漏电流 输出漏电流 输入低电压 输入高电压 输出低电压 输出低电压

1 Vcc 0.7

0

A

10

A

10

A

Vcc 0.3 V

Vcc+0.5 V

s

tHD: DAT

数据输入保持时间

0

0

ns

tSUl: DAT

数据输入建立时间

50

50

ns

tR

SDA 及 SCL 上升时间

1

0.3

s

tF

SDA 及 SCL 下降时间

300

300

ns

tSU: STO

停止信号建立时间

4

0.6

s

tDH

数据输出保持时间

100

100

ns4Biblioteka 海纳电子资讯网: www.fpga-arm.com

上电时序

符号

参数

最大

单位

tPUR

上电到读操作

1

SM24A 调节器说明书

SM24ADamper actuator for adjusting dampers intechnical building installations• Air damper size up to approx. 4 m²• Torque motor 20 Nm• Nominal voltage AC/DC 24 V• Control Open/close, 3-pointTechnical dataElectrical data Nominal voltage AC/DC 24 VNominal voltage frequency50/60 HzNominal voltage range AC 19.2...28.8 V / DC 19.2...28.8 VPower consumption in operation 2 WPower consumption in rest position0.2 WPower consumption for wire sizing 4 VAConnection supply / control Cable 1 m, 3x 0.75 mm²Parallel operation Yes (note the performance data)Functional data Torque motor20 NmDirection of motion motor selectable with switch 0 (ccw rotation) / 1 (cwrotation)Manual override with push-button, can be lockedAngle of rotation Max. 95°Angle of rotation note can be limited on both sides with adjustablemechanical end stopsRunning time motor150 s / 90°Sound power level, motor45 dB(A)Mechanical interface Universal shaft clamp reversible 10...20 mmPosition indication Mechanical, pluggableSafety data Protection class IEC/EN III, Safety Extra-Low Voltage (SELV)Power source UL Class 2 SupplyDegree of protection IEC/EN IP54Degree of protection NEMA/UL NEMA 2Enclosure UL Enclosure Type 2EMC CE according to 2014/30/EUCertification IEC/EN IEC/EN 60730-1 and IEC/EN 60730-2-14UL Approval cULus according to UL60730-1A, UL60730-2-14and CAN/CSA E60730-1The UL marking on the actuator depends onthe production site, the device is UL-compliantin any caseHygiene test According to VDI 6022 Part 1 / SWKI VA104-01, cleanable and disinfectable, lowemissionType of action Type 1Rated impulse voltage supply / control0.8 kVPollution degree3Safety dataAmbient humidity Max. 95% RH, non-condensing Ambient temperature -30...50°C [-22...122°F]Storage temperature -40...80°C [-40...176°F]Servicingmaintenance-free WeightWeight 0.94 kg•••••••Safety notesThis device has been designed for use in stationary heating, ventilation and air-conditioning systems and must not be used outside the specified field of application, especially in aircraft or in any other airborne means of transport.Outdoor application: only possible in case that no (sea) water, snow, ice, insolation or aggressive gases interfere directly with the device and that it is ensured that the ambient conditions remain within the thresholds according to the data sheet at any time.Only authorised specialists may carry out installation. All applicable legal or institutional installation regulations must be complied with during installation.The device may only be opened at the manufacturer's site. It does not contain any parts that can be replaced or repaired by the user.Cables must not be removed from the device.To calculate the torque required, the specifications supplied by the damper manufacturers concerning the cross-section and the design, as well as the installation situation and the ventilation conditions must be observed.The device contains electrical and electronic components and must not be disposed of as household refuse. All locally valid regulations and requirements must be observed.Product featuresSimple direct mountingSimple direct mounting on the damper shaft with a universal shaft clamp, supplied with an anti-rotation device to prevent the actuator from rotating.Manual overrideManual override with push-button possible (the gear train is disengaged for as long as the button is pressed or remains locked).Adjustable angle of rotation Adjustable angle of rotation with mechanical end stops.High functional reliabilityThe actuator is overload protected, requires no limit switches and automatically stops when the end stop is reached.AccessoriesElectrical accessoriesDescriptionType Auxiliary switch 1x SPDT add-on S1A Auxiliary switch 2x SPDT add-onS2A Feedback potentiometer 140 Ω add-on P140A Feedback potentiometer 1 kΩ add-on P1000A Feedback potentiometer 10 kΩ add-onP10000A Mechanical accessoriesDescriptionType Actuator arm for standard shaft clamp (reversible)AH-20Shaft extension 240 mm ø20 mm for damper shaft ø12...21 mm CrNi AV12-25-I Shaft extension 240 mm ø20 mm for damper shaft ø8...22.7 mm AV8-25Ball joint suitable for damper crank arm KH8KG8Ball joint suitable for damper crank arm KH8 / KH10KG10A Damper crank arm Slot width 8.2 mm, clamping range ø10...18 mm KH8Shaft clamp one-sided, clamping range ø8...26 mm, Multipack 20 pcs.K-ENSA Shaft clamp one-sided, clamping range ø12...26 mm, for CrNi shaft (INOX), Multipack 20 pcs.K-ENSA-IDescription Type Shaft clamp reversible, clamping range ø10...20 mm K-SAAnti-rotation mechanism 180 mm, Multipack 20 pcs.Z-ARS180Anti-rotation mechanism 230 mm, Multipack 20 pcs.Z-ARS230 Form fit insert 10x10 mm, Multipack 20 pcs.ZF10-NSAForm fit insert 12x12 mm, Multipack 20 pcs.ZF12-NSAForm fit insert 15x15 mm, Multipack 20 pcs.ZF15-NSA Form fit insert 16x16 mm, Multipack 20 pcs.ZF16-NSA Mounting kit for linkage operation for flat installation ZG-SMA Position indicator, Multipack 20 pcs.Z-PI Baseplate extension for SM..A to SM../AM../SMD24R Z-SMAWire colours:1 = black2 = red3 = whiteElectrical installationSupply from isolating transformer.Parallel connection of other actuators possible. Observe the performance data.Wiring diagramsAC/DC 24 V, open/closeAC/DC 24 V, 3-point DimensionsSpindle lengthMin. 48Min. 20Clamping rangeWhen using a round shaft made of CrNi(INOX): ø12...20 mm。

SM20MT24C-LF-T13中文资料

SM20MT05CthruSM20MT24CST ANDARD CAP ACIT ANCE TVS ARRA YOnly One Name Means ProTek’Tion™APPLICA TIONS✔ Parallel Port✔ RS-232, RS-422 & RS-423 Data Lines ✔ Industrial & Instrumentation Equipment ✔ Board Level Interface Protection ✔ I/O Port ProtectionIEC COMPA TIBILITY (EN61000-4)✔ 61000-4-2 (ESD): Air - 15kV, Contact - 8kV ✔ 61000-4-4 (EFT): 40A - 5/50ns✔ 61000-4-5 (Surge): 24A, 8/20µs - Level 2(Line-Gnd) & Level 3(Line-Line)FEA TURES✔ 1500 Watts Peak Pulse Power per Line (tp=8/20µs)✔ ESD Protection > 40 kilovolts✔ Protection for 8 or 9 Bidirectional Data Lines ✔ Externally Low Clamping Voltage✔ Available in 4 Voltage Types Ranging From 5V to 24V ✔ Bidirectional Configuration ✔ Monolithic Design✔ RoHS Compliant in Lead-Free VersionsMECHANICAL CHARACTERISTICS✔ Molded JEDEC SO-20WB (Wide Body) Package ✔ Weight 0.5 grams (Approximate)✔ Available in Tin-Lead or Lead-Free Pure-Tin Plating(Annealed)✔ Solder Reflow Temperature:Tin-Lead - Sn/Pb, 85/15: 240-245°C Pure-Tin - Sn, 100: 260-270°C✔ Flammability rating UL 94V-0✔ 24mm Tape and Reel Per EIA Standard 481✔ Marking: Logo, Part Number, Date Code & Pin One Defined By Dot on Top of PackageSO-20WB(Wide Body)05079PIN CONFIGURA TIONSIN 1IN 2IN 3IN 4IN 5GND IN 6IN 7IN 8I N 9OUT 1OUT 2OUT 3OUT 4OUT5GND OUT 6OUT 7OUT 8OUT 9GND IN 1IN 2IN 3IN 4IN 5IN 6IN 7IN 8GND GND OUT 1OUT 2OUT 3OUT4OUT 5OUT 6OUT 7OUT 8GNDEQUAL T O 8 BIDIRECTIONAL T VS DEVICESEQUAL T O 9 BIDIRECTIONAL T VS DEVICESSM20MT05CthruSM20MT24CDEVICE CHARACTERISTICSMAXIMUM RATINGS @ 25°C Unless Otherwise SpecifiedOperating T emperature SYMBOL VALUE -55°C to 150°C°C°C -55°C to 150°C UNITS T J T STGPARAMETERStorage T emperaturePeak Pulse Power (t p = 8/20µs) - See Figure 1P PP 1500Watts ELECTRICAL CHARACTERISTICS PER LINE @ 25°C Unless Otherwise SpecifiedPART NUMBER (See Note 1)RATED ST AND-OFF VOLTAGEV WM VOLTSMINIMUM BREAKDOWN VOLTAGE@ 1mA V (BR)VOLTS MAXIMUM CLAMPING VOLTAGE (See Fig. 2)@ I PP = 10AV C VOLTSSM20MT05C SM20MT08C SM20MT15C SM20MT24C 5.08.015.024.0 6.510.018.025.09.513.023.031.011.017.026.036.0MAXIMUM LEAKAGE CURRENT@V WMI D µA MAXIMUM CAPACITANCE@V WM , 1 MHzC pF501044700360250140Note 1: These devices are bidirectional only. Electrical characteristics apply in both directions. The monolithic TVS array is based on 10 unidirec-tional P/N junctions with a common cathode and can be configured to offer 8 to 9 bidirectional lines of protection. The inputs are symmetrical and can be reversed for specific application layout requirements.MAXIMUM CLAMPING VOLTAGE (See Fig. 2)@ I PP = 25AV C VOLTSSM20MT05CthruSM20MT24CGRAPHST L - Lead Temperature - °C20406080100% O f R a t e d P o w e rFIGURE 3POWER DERATING CURVE0 5 10 15 20 25 30t - Time - µs20406080100120I P P - P e a k P u l s e C u r r e n t - %o f I P PFIGURE 20.1 1 10 100 1,000 10,000t d - Pulse Duration - µs1001,00010,000100,000P P P - P e a k P u l s e P o w e r - W a t t sFIGURE 1PEAK PULSE POWER VS PULSE TIMESM20MT05CthruSM20MT24CCOPYRIGHT © ProTek Devices 2005SPECIFICATIONS: ProTek reserves the right to change the electrical and or mechanical characteristics described herein without notice (except JEDEC).DESIGN CHANGES: ProTek reserves the right to discontinue product lines without notice, and that the final judgement concerning selection and specifications is the buyer’s and that in furnishing engineering and technical assistance, ProTek assumes no responsibility with respect to the selection or specifications of such products.P ACKAGE OUTLINE & DIMENSIONSProTek Devices2929 South Fair Lane, Tempe, AZ 85282Tel: 602-431-8101 Fax: 602-431-2288E-Mail: sales@ Web Site: 。

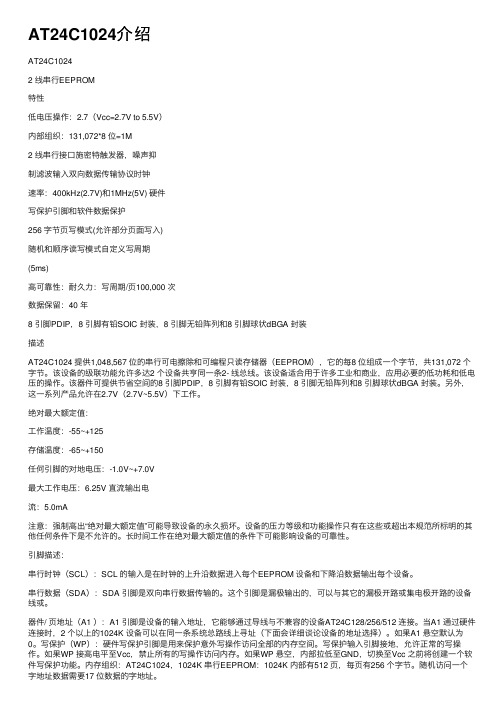

AT24C1024介绍

AT24C1024介绍AT24C10242 线串⾏EEPROM特性低电压操作:2.7(Vcc=2.7V to 5.5V)内部组织:131,072*8 位=1M2 线串⾏接⼝施密特触发器,噪声抑制滤波输⼊双向数据传输协议时钟速率:400kHz(2.7V)和1MHz(5V) 硬件写保护引脚和软件数据保护256 字节页写模式(允许部分页⾯写⼊)随机和顺序读写模式⾃定义写周期(5ms)⾼可靠性:耐久⼒:写周期/页100,000 次数据保留:40 年8 引脚PDIP,8 引脚有铅SOIC 封装,8 引脚⽆铅阵列和8 引脚球状dBGA 封装描述AT24C1024 提供1,048,567 位的串⾏可电擦除和可编程只读存储器(EEPROM),它的每8 位组成⼀个字节,共131,072 个字节。

该设备的级联功能允许多达2 个设备共亨同⼀条2- 线总线。

该设备适合⽤于许多⼯业和商业,应⽤必要的低功耗和低电压的操作。

该器件可提供节省空间的8 引脚PDIP,8 引脚有铅SOIC 封装,8 引脚⽆铅阵列和8 引脚球状dBGA 封装。

另外,这⼀系列产品允许在2.7V(2.7V~5.5V)下⼯作。

绝对最⼤额定值:⼯作温度:-55~+125存储温度:-65~+150任何引脚的对地电压:-1.0V~+7.0V最⼤⼯作电压:6.25V 直流输出电流:5.0mA注意:强制⾼出“绝对最⼤额定值”可能导致设备的永久损坏。

设备的压⼒等级和功能操作只有在这些或超出本规范所标明的其他任何条件下是不允许的。

长时间⼯作在绝对最⼤额定值的条件下可能影响设备的可靠性。

引脚描述:串⾏时钟(SCL):SCL 的输⼊是在时钟的上升沿数据进⼊每个EEPROM 设备和下降沿数据输出每个设备。

串⾏数据(SDA):SDA 引脚是双向串⾏数据传输的。

这个引脚是漏极输出的,可以与其它的漏极开路或集电极开路的设备线或。

器件/ 页地址(A1 ):A1 引脚是设备的输⼊地址,它能够通过导线与不兼容的设备AT24C128/256/512 连接。

24C02B中文资料

FEATURES•Single supply with 5.0V operation •Low power CMOS technology - 1 mA active current typical-10 µ A standby current typical at 5.0V - 5 µ A standby current typical at 5.0V•Organized as a single block of 128 bytes (128 x 8) or 256 bytes (256 x 8)•2-wire serial interface bus, I 2 C compatible •100 kHz compatibility•Self-timed write cycle (including auto-erase)•Page-write buffer for up to 8 bytes• 2 ms typical write cycle time for page-write •Hardware write protect for entire memory •Can be operated as a serial ROM •ESD protection > 3,000V•1,000,000 ERASE/WRITE cycles guaranteed Data retention > 200 years •8 pin DIP or SOIC package•Available for extended temperature ranges DESCRIPTIONThe Microchip T echnology Inc. 24C01B and 24C02B are 1K bit and 2K bit Electrically Erasable PROMs. The devices are organized as a single block of 128 x 8 bit or 256 x 8 bit memory with a 2-wire serial interface. The 24C01B and 24C02B also have page-write capability for up to 8 bytes of data. The 24C01B and 24C02B are available in the standard 8-pin DIP and an 8-pin surface mount SOIC package.These devices are for extended temperature applications only. It is recommended that all other applications use Microchip’s 24LC01B/02B.-Automotive (E):-40˚C to +125˚C2元器件交易网24C01B/02B1.0ELECTRICAL CHARACTERISTICS1.1Maximum Ratings*V CC ...................................................................................7.0V All inputs and outputs w.r.t. V SS ................-0.6V to V CC +1.0V Storage temperature.....................................-65˚C to +150˚C Ambient temp. with power applied.................-65˚C to +125˚C Soldering temperature of leads (10 seconds).............+300˚C ESD protection on all pins............................................. ≥ 4 kV*Notice: Stresses above those listed under “Maximum ratings”may cause permanent damage to the device. This is a stress rat-ing only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.TABLE 1-1:PIN FUNCTION TABLEName FunctionV SS SDA SCL WP V CC NCGroundSerial Address/Data I/O Serial ClockWrite Protect Input +5.0V Power Supply No Internal ConnectionTABLE 1-1:DC CHARACTERISTICSAll parameters apply across the speci-fied operating ranges unless otherwise noted.VCC = +4.5V to 5.5VAutomotive (E):Tamb = -40 ° C to 125 ° C ParameterSymbol Min.Max.Units ConditionsWP , SCL and SDA pins:High level input voltageV IH .7 V CCV Low level input voltageV IL .3 V CC V Hysteresis of Schmidt trigger inputs V HYS .05 V CC —V (Note)Low level output voltage V OL .40V I OL = 3.0 mA, V CC = 2.5V Input leakage current ILI -1010 µ A V IN = .1V to 5.5V Output leakage currentILO -1010 µ mA V OUT = .1V to 5.5VPin capacitance (all inputs/outputs)C IN , C OUT —10pF V CC = 5.0V (Note 1)Tamb = 25˚C, F CLK = 1 MHz Operating current I CC Write —3mA V CC = 5.5V , SCL = 100 kHzI CC Read —1mA Standby current ICCS—30 µ A V CC = 3.0V , SDA = SCL = VCC 100 µ AV CC = 5.5V , SDA = SCL = VCC Note:This parameter is periodically sampled and not 100% tested.元器件交易网24C01B/02BTABLE 1-2:AC CHARACTERISTICSAll Parameters apply across thespecified operating ranges unless otherwise notedVcc = 4.5V to 5.5V Automotive (E):Tamb = -40˚C to +125˚C,ParameterSymbol Min.Max.Units RemarksClock frequency F CLK —100kHz Clock high time T HIGH 4000—ns Clock low time T LOW 4700—ns SDA and SCL rise time T R —1000ns (Note 1)SDA and SCL fall time T F —300ns (Note 1)ST ART condition hold time T HD : STA 4000—ns After this period the first clock pulse is generatedST ART condition setup time T SU : STA 4700—ns Only relevant for repeated ST ART condition Data input hold time T HD : DAT 0—ns (Note 2)Data input setup time T SU : DAT 250—ns STOP condition setup time T SU : STO 4000—ns Output valid from clock T AA —3500ns (Note 2)Bus free timeT BUF 4700—ns Time the bus must be free before a new transmission can start Output fall time from V IH minimum to V IL maximum T OF —250ns (Note 1), CB ≤ 100 pF Input filter spike suppression (SDA and SCL pins)T SP —50ns (Note 3)Write cycle time T WR —10ms Byte or Page modeEndurance—1M—cycles25 ° C, Vcc = 5.0V , Block Mode (Note 4)Note 1:Not 100% tested. CB = total capacitance of one bus line in pF .2:As a transmitter, the device must provide an internal minimum delay time to bridge the undefined region(minimum 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.3:The combined T SP and VHYSspecifications are due to Schmitt trigger inputs which provide improved noisespike suppression. This eliminates the need for a TI specification for standard operation.4:This parameter is not tested but guaranteed by characterization. For endurance estimates in a specificapplication, please consult the T otal Endurance Model which can be obtained on our BBS or website.元器件交易网24C01B/02B2.0FUNCTIONAL DESCRIPTION The 24C01B/02B supports a bi-directional two wire bus and data transmission protocol. A device that sends data onto the bus is defined as transmitter, and a device receiving data as receiver. The bus has to be controlled by a master device which generates the serial clock (SCL), controls the bus access, and gener-ates the ST ART and STOP conditions, while the 24C01B/02B works as slave. Both master and slave can operate as transmitter or receiver but the master device determines which mode is activated.3.0BUS CHARACTERISTICSThe following bus protocol has been defined:•Data transfer may be initiated only when the busis not busy.•During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is HIGH will be interpreted as a ST ART or STOP condition. Accordingly, the following bus conditions have been defined (Figure 3-1).3.1Bus Not Busy (A)Both data and clock lines remain HIGH.3.2Start Data Transfer (B)A HIGH to LOW transition of the SDA line while the clock (SCL) is HIGH determines a ST ART condition. All commands must be preceded by a ST ART condi-tion.3.3Stop Data Transfer (C)A LOW to HIGH transition of the SDA line while the clock (SCL) is HIGH determines a STOP condition. All operations must be ended with a STOP condition.3.4Data Valid (D)The state of the data line represents valid data when, after a ST ART condition, the data line is stable for the duration of the HIGH period of the clock signal.The data on the line must be changed during the LOW period of the clock signal. There is one clock pulse per bit of data.Each data transfer is initiated with a ST ART condition and terminated with a STOP condition. The number of the data bytes transferred between the ST ART and STOP conditions is determined by the master device and is theoretically unlimited, although only the last six-teen will be stored when doing a write operation. When an overwrite does occur it will replace data in a first in first out fashion.3.5AcknowledgeEach receiving device, when addressed, is obliged to generate an acknowledge after the reception of each byte. The master device must generate an extra clock pulse which is associated with this acknowledge bit. The device that acknowledges has to pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse. Of course, setup and hold times must be taken into account. A master must signal an end of data to the slave by not generating an acknowledge bit on the last byte that has been clocked out of the slave. In this case, the slave must leave the data line HIGH to enable the master to generate the STOP condition.元器件交易网24C01B/02B3.6Device AddressAfter generating a ST ART condition, the bus master transmits the slave address consisting of a 4-bit device code (1010) for the 24C01B/02B, followed by three don't care bits.The eighth bit of slave address determines if the master device wants to read or write to the 24C01B/02B (Figure 3-2).The 24C01B/02B monitors the bus for its correspond-ing slave address all the time. It generates an acknowl-edge bit if the slave address was true and it is not in a programming mode.4.0WRITE OPERATION4.1Byte WriteFollowing the start signal from the master, the device code (4 bits), the don't care bits (3 bits), and the R/W bit which is a logic low is placed onto the bus by the master transmitter. This indicates to the addressed slave receiver that a byte with a word address will follow after it has generated an acknowledge bit during the ninth clock cycle. Therefore the next byte transmitted by the master is the word address and will be written into the address pointer of the 24C01B/02B. After receiving another acknowledge signal from the 24C01B/02B the master device will transmit the data word to be written into the addressed memory location.The 24C01B/02B acknowledges again and the master generates a stop condition. This initiates the internal write cycle, and during this time the 24C01B/02B will not generate acknowledge signals (Figure 4-1).4.2Page WriteThe write control byte, word address and the first data byte are transmitted to the 24C01B/02B in the same way as in a byte write. But instead of generating a stop condition the master transmits up to eight data bytes to the 24C01B/02B which are temporarily stored in the on-chip page buffer and will be written into the memoryafter the master has transmitted a stop condition. After the receipt of each word, the three lower order address pointer bits are internally incremented by one. The higher order five bits of the word address remains con-stant. If the master should transmit more than eight words prior to generating the stop condition, the address counter will roll over and the previously received data will be overwritten. As with the byte write operation, once the stop condition is received an inter-nal write cycle will begin (Figure 4-2).元器件交易网24C01B/02B5.0ACKNOWLEDGE POLLINGSince the device will not acknowledge during a write cycle, this can be used to determine when the cycle is complete (this feature can be used to maximize bus throughput). Once the stop condition for a write com-mand has been issued from the master, the device ini-tiates the internally timed write cycle. ACK polling can be initiated immediately. This involves the master send-ing a start condition followed by the control byte for a write command (R/W = 0). If the device is still busy with the write cycle, then no ACK will be returned. If the cycle is complete, then the device will return the ACK and the master can then proceed with the next read or write command. See Figure 5-1 for flow diagram. FIGURE 5-1:ACKNOWLEDGE POLLING6.0WRITE PROTECTIONThe 24C01B/02B can be used as a serial ROM when the WP pin is connected to V CC. Programming will be inhibited and the entire memory will be write-protected.7.0READ OPERATIONRead operations are initiated in the same way as write operations with the exception that the R/W bit of the slave address is set to one. There are three basic types of read operations: current address read, random read, and sequential read.7.1Current Address ReadThe 24C01B/02B contains an address counter that maintains the address of the last word accessed, inter-nally incremented by one. Therefore, if the previous access (either a read or write operation) was to address n, the next current address read operation would access data from address n + 1. Upon receipt of the slave address with R/W bit set to one, the 24C01B/ 02B issues an acknowledge and transmits the eight bit data word. The master will not acknowledge the trans-fer but does generate a stop condition and the 24C01B/ 02B discontinues transmission (Figure 7-1).7.2Random ReadRandom read operations allow the master to access any memory location in a random manner. T o perform this type of read operation, first the word address must be set. This is done by sending the word address to the 24C01B/02B as part of a write operation. After the word address is sent, the master generates a start condition following the acknowledge. This terminates the write operation, but not before the internal address pointer is set. Then the master issues the control byte again but with the R/W bit set to a one. The 24C01B/02B will then issue an acknowledge and transmits the eight bit data word. The master will not acknowledge the transfer but does generate a stop condition and the 24C01B/02B discontinues transmission (Figure 7-2).7.3Sequential ReadSequential reads are initiated in the same way as a ran-dom read except that after the 24C01B/02B transmits the first data byte, the master issues an acknowledge as opposed to a stop condition in a random read. This directs the 24C01B/02B to transmit the next sequen-tially addressed 8-bit word (Figure 7-3).To provide sequential reads the 24C01B/02B contains an internal address pointer which is incremented by one at the completion of each operation. This address pointer allows the entire memory contents to be serially read during one operation.7.4Noise ProtectionThe 24C01B/02B employs a V CC threshold detector cir-cuit which disables the internal erase/write logic if the V CC is below 1.5 volts at nominal conditions.The SCL and SDA inputs have Schmitt trigger and filter circuits which suppress noise spikes to assure proper device operation even on a noisy bus.元器件交易网24C01B/02B8.0PIN DESCRIPTIONS8.1Serial DataThis is a bi-directional pin used to transfer addresses and data into and data out of the device. It is an open drain terminal, therefore the SDA bus requires a pull-up resistor to V CC (typically 10 KΩ for 100 kHz).For normal data transfer SDA is allowed to change only during SCL low. Changes during SCL high are reserved for indicating the ST ART and STOP condi-tions.8.2SCL Serial ClockThis input is used to synchronize the data transfer from and to the device.8.3WPThis pin must be connected to either V SS or V CC.If tied to V SS, normal memory operation is enabled (read/write the entire memory).If tied to V CC, WRITE operations are inhibited. The entire memory will be write-protected. Read operations are not affected.This feature allows the user to use the 24C01B/02B as a serial ROM when WP is enabled (tied to V CC).元器件交易网元器件交易网24C01B/02B Array NOTES:元器件交易网24C01B/02B Array NOTES:元器件交易网24C01B/02B Array NOTES:24C01B/02BT o order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.Data SheetsProducts supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recom-mended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:1.Y our local Microchip sales office.2.The Microchip Corporate Literature Center U.S. FAX: (602) 786-7277.3.The Microchip’s Bulletin Board, via your local CompuServe number (CompuServe membership NOT required).Please specify which device, revision of silicon and Data Sheet (include Literature #) you are using.元器件交易网元器件交易网MAll rights reserved. © 1997, Microchip T echnology Incorporated, USA. 12/97 Printed on recycled paper.。

英特吉小系统(SM20)简介

英特吉配置编辑器 英特吉配置编辑器通常安装在笔记本电脑中,并且由施威

(ICE)

特克的工程师在安装和维护时使用。笔记本电脑可通过

SM20 前面板后的 RS232 口与 IMPS 进行连接。

管理模块 (SM20)

管理模块 SM20 监视着 IMPS 的各种功能,并且控制整流 器和 LVD 的操作。所有独立模块都受监视,即任一影响 系统参数的模块故障,SM20 都会产生告警。SM20 可接 收来自电流、电压、温度等传感器输出的模拟信号。SM20 有 8 个继电器输出触点,也用于外部告警电路。

低压脱离 (LVD)

低压脱离保护是为了防止交流停电时间过长时导致电池过 放电而影响电池寿命。用一组电子开关来控制电池的通和 断,当电池电压低于预先设定的电压时,电子开关断开; 当电压上升到预先设定的电压时,电子开关重新闭合。在 操作过程中 LVD 接收来自监控器 SM20 的控制信号。

整流器

整流器的功能是将交流输入电压转化直流输出电压,然后 给电池和负载供电。整流器的交流输入来自用户的交流输 出,MS500 就是从 ACD 上接入的。 每个整流器的直流 输出均连接到直配模块上。SM20 通过多芯控制线控制每 个整流器。整流器告警及其状态通过前面板的发光二极管 显示。

负载

DCD

负A只C适D用和于

MOVs MS500)

交流输出

路

MOV 告警

背

板

进线故障告警

电池温度 房间温度 7 路数字输入

键盘和 显示

RS 232

8 路外部告警 (数字量输出)

输入 输入 输入

接口 延时

SM20

告警 告警 告警 告警 告警

LV电D池控电制流 负载电流

AT24C1024B 1024K EEPROM 产品说明书

Features•Low-voltage Operation–1.8V(V CC=1.8V to3.6V)–2.5V(V CC=2.5V to5.5V)•Internally Organized131,072x8•Two-wire Serial Interface•Schmitt Triggers,Filtered Inputs for Noise Suppression•Bidirectional Data Transfer Protocol•400kHz(1.8V)and1MHz(5V,2.5V)Clock Rate•Write Protect Pin for Hardware and Software Data Protection•256-byte Page Write Mode(Partial Page Writes Allowed)•Random and Sequential Read Modes•Self-timed Write Cycle(5ms Typical)•High Reliability–Endurance:1,000,000Write Cycles/Page–Data Retention:40Years•8-lead PDIP,8-lead JEDEC SOIC,8-lead EIAJ SOIC,8-lead TSSOP,8-lead Ultra Thin Small Array(SAP),and8-ball dBGA2Packages•Die Sales:Wafer Form,Tape and Reel and Bumped DieDescriptionThe AT24C1024B provides1,048,576bits of serial electrically erasable and program-mable read only memory(EEPROM)organized as131,072words of8bits each.The device’s cascadable feature allows up to four devices to share a common two-wire bus.The device is optimized for use in many industrial and commercial applications where low-power and low-voltage operation are essential.The devices are available in space-saving8-lead PDIP,8-lead JEDEC SOIC,8-lead EIAJ SOIC,8-lead TSSOP, 8-ball dBGA2and8-lead Ultra Thin SAP packages.In addition,the entire family is available in1.8V(1.8V to3.6V)and2.5V(2.5V to5.5V)versions.8-lead PDIP12348765NCA1A2GNDVCCWPSCLSDA8-lead TSSOP12348765VCCWPSCLSDANCA1A2GND8-lead SOIC12348765NCA1A2GNDVCCWPSCLSDA8-lead Ultra-Thin SAPBottom ViewVCCWPSCLSDANCA1A2GND123487658-lead dBGA2Bottom ViewVCCWPSCLSDANCA1A2GND1234876525194F–SEEPR–1/08AT24C1024B1.Absolute Maximum Ratings**NOTICE:Stresses beyond those listed under “Absolute Maximum Ratings”may cause permanent dam-age to the device.This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied.Exposure to absolute maximum rating conditions for extended periods may affect device reliability.35194F–SEEPR–1/08AT24C1024BFigure 1-1.Block Diagram2.Pin DescriptionSERIAL CLOCK (SCL):The SCL input is used to positive edge clock data into each EEPROM device and negative edge clock data out of each device.SERIAL DATA (SDA):The SDA pin is bi-directional for serial data transfer.This pin is open-drain driven and may be wire-ORed with any number of other open-drain or open-collector devices.DEVICE/ADDRESSES (A1/A2):The A1,A2pin is a device address input that can be hardwired or left not connected for hardware compatibility with other AT24Cxx devices.When the A1,A2pins are hardwired,as many as four 1024K devices may be addressed on a single bus system (device addressing is discussed in detail under the Device Addressing section).If the A1/A2pins are left floating,the A1/A2pin will be internally pulled down to GND if the capacitive coupling to the circuit board V CC plane is <3pF.If coupling is >3pF,Atmel recommends connecting the A1/A2pin to GND.WRITE PROTECT (WP):The write protect input,when connected to GND,allows normal write operations.When WP is connected high to V CC ,all write operations to the memory are inhibited.If the pin is left floating,the WP pin will be internally pulled down to GND if the capacitive cou-pling to the circuit board V CC plane is <3pF.If coupling is >3pF,Atmel recommends connecting the pin to GND.Switching WP to V CC prior to a write operation creates a software write-protectfunction.VCC GND WP SCL SDAA 2A 1A 045194F–SEEPR–1/08AT24C1024B3.Memory OrganizationAT24C1024B,1024K SERIAL EEPROM:The 1024K is internally organized as 512pages of 256bytes each.Random word addressing requires a 17-bit data word address.IL IH Table 3-1.Pin Capacitance (1)Table 3-2.DC CharacteristicsTable 3-3.AC Characteristics (Industrial Temperature)Applicable over recommended operating range from T AI =-40︒C to +85︒C,V CC =+1.8V to +3.6V,CL =100pF (unless oth-55194F–SEEPR–1/08AT24C1024B2.AC measurement conditions:R L (connects to V CC ):1.3k Ω(2.5V,5V),10k Ω(1.8V)Input pulse voltages:0.3V CC to 0.7V CC Input rise and fall times:≤50nsInput and output timing reference voltages:0.5V CC4.Device OperationCLOCK and DATA TRANSITIONS:The SDA pin is normally pulled high with an external device.Data on the SDA pin may change only during SCL low time periods (see Figure 4-4on page 7).Data changes during SCL high periods will indicate a start or stop condition as defined below.START CONDITION:A high-to-low transition of SDA with SCL high is a start condition which must precede any other command (see Figure 4-5on page 8).Table 3-3.AC Characteristics (Industrial Temperature)Applicable over recommended operating range from T AI =-40︒C to +85︒C,V CC =+1.8V to +3.6V,CL =100pF (unless oth-65194F–SEEPR–1/08AT24C1024BSTOP CONDITION:A low-to-high transition of SDA with SCL high is a stop condition.After a read sequence,the Stop command will place the EEPROM in a standby power mode (see Fig-ure 4-5on page 8).ACKNOWLEDGE:All addresses and data words are serially transmitted to and from the EEPROM in 8-bit words.The EEPROM sends a zero during the ninth clock cycle to acknowl-edge that it has received each word.STANDBY MODE:The AT24C1024B features a low-power standby mode which is enabled:a)upon power-up and b)after the receipt of the stop bit and the completion of any internal operations.SOFTWARE RESET:After an interruption in protocol,power loss or system reset,any 2-wire part can be protocol reset by following these steps:(a)Create a start bit condition,(b)clock 9cycles,(c)create another start bit followed by stop bit condition as shown below.The device is ready for next communication after above steps have been completed.Figure 4-1.Software ResetFigure 4-2.Bus Timing (SCL:Serial Clock,SDA:Serial Data I/O ®)SCLSDASCLSDA INSDA OUT75194F–SEEPR–1/08AT24C1024BFigure 4-3.Write Cycle Timing (SCL:Serial Clock,SDA:Serial Data I/O)Note:1.The write cycle time t WR is the time from a valid stop condition of a write sequence to the end of the internal clear/write cycle.Figure 4-4.DataValiditySTOP CONDITIONSTART CONDITIONSCLSDASDASCLDAT A STABLEDAT A STABLEDAT A CHANGE85194F–SEEPR–1/08AT24C1024BFigure 4-5.Start and Stop DefinitionFigure 4-6.Output Acknowledge5.Device AddressingThe 1024K EEPROM requires an 8-bit device address word following a start condition to enable the chip for a read or write operation (see Figure 7-1on page 11).The device address word con-sists of a mandatory one,zero sequence for the first four most significant bits as shown.This is common to all two-wire EEPROM devices.The 1024K uses the two device address bit,A1,A2,to allow up to four devices on the same bus.These A1,A2bits must compare to the corresponding hardwired input pins.The A1,A2pin uses an internal proprietary circuit that biases it to a logic low condition if the pin is allowed to float.The seventh bit (P 0)of the device address is a memory page address bit.This memory page address bit is the most significant bit of the data word address that follows.The eighth bit of the device address is the read/write operation select bit.A read operation is initiated if this bit is high and a write operation is initiated if this bit is low.Upon a compare of the device address,the EEPROM will output a zero.If a compare is not made,the device will return to astandby state.SDASCLSTART STOPSCLDAT A INDAT A OUTSTART ACKNOWLEDGE98195194F–SEEPR–1/08AT24C1024BDATA SECURITY:The AT24C1024B has a hardware data protection scheme that allows the user to write-protect the entire memory when the WP pin is at V CC .6.Write OperationsBYTE WRITE:To select a data word in the 1024K memory requires a 17-bit word address.The word address field consists of the P 0bit of the device address,then the most significant word address followed by the least significant word address (see Figure 7-2on page 11)A write operation requires the P 0bit and two 8-bit data word addresses following the device address word and acknowledgment.Upon receipt of this address,the EEPROM will again respond with a zero and then clock in the first 8-bit data word.Following receipt of the 8-bit data word,the EEPROM will output a zero.The addressing device,such as a microcontroller,then must terminate the write sequence with a stop condition.At this time the EEPROM enters an internally timed write cycle,T WR ,to the nonvolatile memory.All inputs are disabled during this write cycle and the EEPROM will not respond until the write is complete (see Figure 7-2on page 11).PAGE WRITE:The 1024K EEPROM is capable of 256-byte page writes.A page write is initiated the same way as a byte write,but the microcontroller does not send a stop condition after the first data word is clocked in.Instead,after the EEPROM acknowledges receipt of the first data word,the microcontroller can transmit up to 255more data words.The EEPROM will respond with a zero after each data word received.The microcontroller must ter-minate the page write sequence with a stop condition (see Figure 7-3on page 11).The data word address lower 8bits are internally incremented following the receipt of each data word.The higher data word address bits are not incremented,retaining the memory page row location.When the word address,internally generated,reaches the page boundary,the follow-ing byte is placed at the beginning of the same page.If more than 256data words are transmitted to the EEPROM,the data word address will “roll over”and previous data will be overwritten.The address “rollover”during write is from the last byte of the current page to the first byte of the same page.ACKNOWLEDGE POLLING:Once the internally timed write cycle has started and the EEPROM inputs are disabled,acknowledge polling can be initiated.This involves sending a start condition followed by the device address word.The read/write bit is representative of the operation desired.Only if the internal write cycle has completed will the EEPROM respond with a zero,allowing the read or write sequence to continue.7.Read OperationsRead operations are initiated the same way as write operations with the exception that the read/write select bit in the device address word is set to one.There are three read operations:current address read,random address read and sequential read.CURRENT ADDRESS READ:The internal data word address counter maintains the last address accessed during the last read or write operation,incremented by one.This address stays valid between operations as long as the chip power is maintained.The address “rollover”during read is from the last byte of the last memory page,to the first byte of the first page.105194F–SEEPR–1/08AT24C1024BOnce the device address with the read/write select bit set to one is clocked in and acknowledged by the EEPROM,the current address data word is serially clocked out.The microcontroller does not respond with an input zero but does generate a following stop condition (see Figure 7-4on page 11).RANDOM READ:A random read requires a “dummy”byte write sequence to load in the data word address.Once the device address word and data word address are clocked in and acknowledged by the EEPROM,the microcontroller must generate another start condition.The microcontroller now initiates a current address read by sending a device address with the read/write select bit high.The EEPROM acknowledges the device address and serially clocks out the data word.The microcontroller does not respond with a zero but does generate a follow-ing stop condition (see Figure 7-5on page 12).SEQUENTIAL READ:Sequential reads are initiated by either a current address read or a ran-dom address read.After the microcontroller receives a data word,it responds with an acknowledge.As long as the EEPROM receives an acknowledge,it will continue to increment the data word address and serially clock out sequential data words.When the memory address limit is reached,the data word address will “roll over”and the sequential read will continue.The sequential read operation is terminated when the microcontroller does not respond with a zero,but does generate a following stop condition (see Figure 7-6on page 12).115194F–SEEPR–1/08AT24C1024BFigure 7-1.Device AddressFigure 7-2.Byte WriteFigure 7-3.Page WriteFigure 7-4.Current AddressReadSIGNIFICANTMOSTSIGNIFICANTLEAST125194F–SEEPR–1/08AT24C1024BFigure 7-5.Random ReadFigure 7-6.Sequential Read135194F–SEEPR–1/08AT24C1024BNotes: 1.“-B”denotes bulk2.“-T”denotes tape and reel.SOIC =4K per reel.TSSOP and dBGA2=5K per reel.SAP =3K per reel.EIAJ =2K per reel.3.Available in tape and reel and wafer form;order as SL788for inkless wafer form.Bumped die available upon request.Pleasecontact Serial Interface Marketing.Ordering Information145194F–SEEPR–1/08AT24C1024B8.Part marking scheme8.18-SOIC(1.8V)8.28-SOIC(2.5V)TOP MARKSeal YearY = SEAL YEARWW = SEAL WEEK | Seal Week6: 2006 0: 2010 02 = Week 2 | | |7: 2007 1: 2011 04 = Week 4 |---|---|---|---|---|---|---|---| 8: 2008 2: 2012 :: : :::: : A T M L H Y W W 9: 2009 3: 2013:: : :::: :: |---|---|---|---|---|---|---|---| 50 = Week 50 2 G B 152 = Week 52|---|---|---|---|---|---|---|---| * Lot NumberLot Number to Use ALL Characters in Marking |---|---|---|---|---|---|---|---| |BOTTOM MARKPin 1 Indicator (Dot)No Bottom MarkTOP MARKSeal YearY = SEAL YEARWW = SEAL WEEK | Seal Week6: 2006 0: 2010 02 = Week 2 | | |7: 2007 1: 2011 04 = Week 4 |---|---|---|---|---|---|---|---| 8: 2008 2: 2012 :: : :::: : A T M L H Y W W 9: 2009 3: 2013:: : :::: :: |---|---|---|---|---|---|---|---| 50 = Week 50 2 G B 252 = Week 52|---|---|---|---|---|---|---|---| * Lot NumberLot Number to Use ALL Characters in Marking |---|---|---|---|---|---|---|---| |BOTTOM MARKPin 1 Indicator (Dot)No Bottom Mark155194F–SEEPR–1/08AT24C1024B8.38-TSSOP(1.8V)8.48-TSSOP(2.5V)TOP MARKPin 1 Indicator (Dot)Y = SEAL YEAR WW = SEAL WEEK |6: 2006 0: 2010 02 = Week 2 |---|---|---|---| 7: 2007 1: 2011 04 = Week 4 * H Y W W 8: 2008 2: 2012 :: : :::: : |---|---|---|---|---| 9: 2009 3: 2013:: : :::: :: 2 G B 1 50 = Week 50 |---|---|---|---|---| 52 = Week 52BOTTOM MARK|---|---|---|---|---|---|---| P H|---|---|---|---|---|---|---| A A A A A A A |---|---|---|---|---|---|---| <- Pin 1 IndicatorTOP MARKPin 1 Indicator (Dot)Y = SEAL YEAR WW = SEAL WEEK |6: 2006 0: 2010 02 = Week 2 |---|---|---|---| 7: 2007 1: 2011 04 = Week 4 * H Y W W 8: 2008 2: 2012 :: : :::: : |---|---|---|---|---| 9: 2009 3: 2013:: : :::: :: 2 G B 2 50 = Week 50 |---|---|---|---|---| 52 = Week 52BOTTOM MARK|---|---|---|---|---|---|---| P H|---|---|---|---|---|---|---| A A A A A A A |---|---|---|---|---|---|---| <- Pin 1 Indicator165194F–SEEPR–1/08AT24C1024B8.58-PDIP(1.8V)8.68-PDIP(2.5V)8.78-Ultra Thin SAP (1.8V)TOP MARKSeal YearY = SEAL YEARWW = SEAL WEEK | Seal Week6: 2006 0: 2010 02 = Week 2 | | |7: 2007 1: 2011 04 = Week 4 |---|---|---|---|---|---|---|---| 8: 2008 2: 2012 :: : :::: : A T M L U Y W W 9: 2009 3: 2013:: : :::: :: |---|---|---|---|---|---|---|---| 50 = Week 50 2 G B 152 = Week 52|---|---|---|---|---|---|---|---| * Lot NumberLot Number to Use ALL Characters in Marking |---|---|---|---|---|---|---|---| |BOTTOM MARKPin 1 Indicator (Dot)No Bottom MarkTOP MARKSeal YearY = SEAL YEARWW = SEAL WEEK | Seal Week6: 2006 0: 2010 02 = Week 2 | | |7: 2007 1: 2011 04 = Week 4 |---|---|---|---|---|---|---|---| 8: 2008 2: 2012 :: : :::: : A T M L U Y W W 9: 2009 3: 2013:: : :::: :: |---|---|---|---|---|---|---|---| 50 = Week 50 2 G B 252 = Week 52|---|---|---|---|---|---|---|---| * Lot NumberLot Number to Use ALL Characters in Marking |---|---|---|---|---|---|---|---| |BOTTOM MARKPin 1 Indicator (Dot)No Bottom MarkTOP MARKSeal Year| Seal Week Y = SEAL YEARWW = SEAL WEEK | | |6: 2006 0: 2010 02 = Week 2 |---|---|---|---|---|---|---|---| 7: 2007 1: 2011 04 = Week 4 A T M L H Y W W 8: 2008 2: 2012 :: : :::: : |---|---|---|---|---|---|---|---| 9: 2009 3: 2013:: : :::: :: 2 G B 150 = Week 50 |---|---|---|---|---|---|---|---| 52 = Week 52Lot Number|---|---|---|---|---|---|---|---| * |Pin 1 Indicator (Dot)175194F–SEEPR–1/08AT24C1024B8.88-Ultra Thin SAP (2.5V)8.9dBGA2TOP MARKSeal Year| Seal Week Y = SEAL YEARWW = SEAL WEEK | | |6: 2006 0: 2010 02 = Week 2 |---|---|---|---|---|---|---|---| 7: 2007 1: 2011 04 = Week 4 A T M L H Y W W 8: 2008 2: 2012 :: : :::: : |---|---|---|---|---|---|---|---| 9: 2009 3: 2013:: : :::: :: 2 G B 250 = Week 50 |---|---|---|---|---|---|---|---| 52 = Week 52Lot Number|---|---|---|---|---|---|---|---| * |Pin 1 Indicator (Dot)TOP MARKLINE 1-------> 2GBU LINE 2-------> PYMTC|<-- Pin 1 This CornerP = COUNTRY OF ORIGINY = ONE DIGIT YEAR CODE 4: 2004 7: 20075: 2005 8: 20086: 2006 9: 2009M = SEAL MONTH (USE ALPHA DESIGNATOR A-L) A = JANUARY B = FEBRUARY " " """"""" J = OCTOBER K = NOVEMBER L = DECEMBERTC = TRACE CODE (ATMEL LOT NUMBERS TO CORRESPONDWITH ATK TRACE CODE LOG BOOK)185194F–SEEPR–1/08AT24C1024B9.Packaging Information 8P3–PDIP195194F–SEEPR–1/08AT24C1024B8S1-JEDEC SOIC205194F–SEEPR–1/08AT24C1024B8S2–EIAJ SOICAT24C1024B 8A2-TSSOP2122AT24C1024B8U4-1-dBGA2AT24C1024B 8Y7–SAP2324AT24C1024B10.Revision HistoryHeadquarters InternationalAtmel Corporation 2325Orchard Parkway San Jose,CA95131 USATel:1(408)441-0311 Fax:1(408)487-2600Atmel AsiaRoom1219Chinachem Golden Plaza77Mody Road TsimshatsuiEast KowloonHong KongTel:(852)2721-9778Fax:(852)2722-1369Atmel EuropeLe Krebs8,Rue Jean-Pierre TimbaudBP30978054Saint-Quentin-en-Yvelines CedexFranceTel:(33)1-30-60-70-00Fax:(33)1-30-60-71-11Atmel Japan9F,Tonetsu Shinkawa Bldg.1-24-8ShinkawaChuo-ku,Tokyo104-0033JapanTel:(81)3-3523-3551Fax:(81)3-3523-7581Product ContactWeb SiteTechnical Support******************Sales Contact/contactsLiterature Requests/literatureDisclaimer:The information in this document is provided in connection with Atmel products.No license,express or implied,by estoppel or otherwise,to any intellectual property right is granted by this document or in connection with the sale of Atmel products.EXCEPT AS SET FORTH IN ATMEL’S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL’S WEB SITE,ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS,IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING,BUT NOT LIMITED TO,THE IMPLIED WARRANTY OF MERCHANTABILITY,FITNESS FOR A PARTICULAR PURPOSE,OR NON-INFRINGEMENT.IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT,INDIRECT,CONSEQUENTIAL,PUNITIVE,SPECIAL OR INCIDEN-TAL DAMAGES(INCLUDING,WITHOUT LIMITATION,DAMAGES FOR LOSS OF PROFITS,BUSINESS INTERRUPTION,OR LOSS OF INFORMATION)ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT,EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice.Atmel does not make any commitment to update the information contained herein.Unless specifically provided otherwise,Atmel products are not suitable for,and shall not be used in,automotive applications.Atmel’s products are not intended,authorized,or warranted for use as components in applications intended to support or sustain life.©2008Atmel Corporation.All rights reserved.Atmel®,logo and combinations thereof,are registered trademarks or trademarks of Atmel Cor-poration or its subsidiaries.Other terms and product names may be trademarks of others.。

24C64中文资料_数据手册_参数

5.3 Read Identification Page (M24C64-D only) . . . . . . . . . . . . . . . . . . . . . . . 21 5.4 Read the lock status (M24C64-D only) . . . . . . . . . . . . . . . . . . . . . . . . . . 22

5.1.2 Page Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

5.1.3 Write Identification Page (M24C64-D only) . . . . . . . . . . . . . . . . . . . . . . 18

5.1 Write operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

5.1.1 Byte Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

24c02中文资料

24C02中文资料1. 介绍24C02是一种串行电子可擦除可编程只读存储器(EEPROM),由美国Microchip Technology公司生产。

它具有2K位存储容量,可用于存储数据。

24C02具有低功耗、高可靠性和可编程性等特点,因此在许多电子设备中得到广泛应用。

2. 24C02的功能特点•存储容量:24C02具有2K位的存储容量,相当于256个字节,每个字节包含8位二进制数据。

•串行接口:24C02采用串行接口进行数据的读写操作,使得它能够与各种微处理器和其他外围设备进行通信。

•可擦除、可编程:24C02采用电子擦除可编程技术,可以对存储的数据进行擦除和编程的操作。

•低功耗:24C02在工作状态下的功耗非常低,使得它适合应用于移动设备和电池供电的设备。

•高可靠性:24C02采用了自动页写技术,具有高可靠性和稳定性,适用于各种工业和消费类电子产品。

3. 24C02的引脚图和功能说明24C02具有8个引脚,每个引脚的功能如下:•VCC:供电引脚,将其连接到供电电源即可。

•GND:地引脚,连接到系统的地线。

•SDA:串行数据输入/输出引脚,与微处理器或其他设备进行数据传输。

•SCL:串行时钟引脚,用于同步传输数据。

•WC:写控制引脚,用于控制写入和擦除操作。

•A0、A1、A2:地址选择引脚,用于选择设备的地址,使得多个设备可以同时使用。

4. 24C02的工作原理24C02采用了I2C总线协议进行数据通信,它的工作原理如下:•开始信号:主设备发出一个开始信号,通知24C02开始进行工作。

•地址传输:主设备发送一个设备地址和操作位(读或写)到24C02。

•对应设备响应:24C02将自己的设备地址进行识别,并发出一个应答信号。

•数据传输:主设备发送要读取或写入的数据到24C02。

•应答信号:24C02接收到数据后,会发出应答信号。

•停止信号:传输完成后,主设备发送一个停止信号,通知24C02本次操作结束。

SMDJ24中文资料

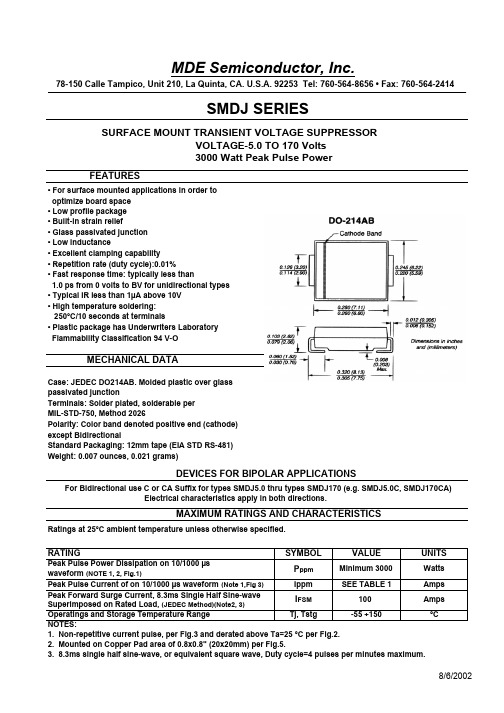

MDE Semiconductor, Inc.78-150 Calle Tampico, Unit 210, La Quinta, CA. U.S.A. 92253 Tel: 760-564-8656 • Fax: 760-564-2414SMDJ SERIESSURFACE MOUNT TRANSIENT VOLTAGE SUPPRESSORVOLTAGE-5.0 TO 170 Volts3000 Watt Peak Pulse PowerFEATURES• For surface mounted applications in order to optimize board space • Low profile package • Built-in strain relief• Glass passivated junction • Low inductance• Excellent clamping capability• Repetition rate (duty cycle):0.01%• Fast response time: typically less than1.0 ps from 0 volts to BV for unidirectional types • Typical IR less than 1µA above 10V • High temperature soldering: 250°C/10 seconds at terminals• Plastic package has Underwriters Laboratory Flammability Classification 94 V-OMECHANICAL DATACase: JEDEC DO214AB. Molded plastic over glass passivated junctionTerminals: Solder plated, solderable per MIL-STD-750, Method 2026Polarity: Color band denoted positive end (cathode)except BidirectionalStandard Packaging: 12mm tape (EIA STD RS-481)Weight: 0.007 ounces, 0.021 grams)DEVICES FOR BIPOLAR APPLICATIONSFor Bidirectional use C or CA Suffix for types SMDJ5.0 thru types SMDJ170 (e.g. SMDJ5.0C, SMDJ170CA)Electrical characteristics apply in both directions.MAXIMUM RATINGS AND CHARACTERISTICSRatings at 25°C ambient temperature unless otherwise specified.RATING SYMBOL VALUEUNITSPeak Pulse Power Dissipation on 10/1000 µswaveform (NOTE 1, 2, Fig.1)Ippm SEE TABLE 1Amps Superimposed on Rated Load, (JEDEC Method)(Note2, 3)Operatings and Storage Temperature Range Tj, Tstg -55 +150°C NOTES:1. Non-repetitive current pulse, per Fig.3 and derated above Ta=25 °C per Fig.2.2. Mounted on Copper Pad area of 0.8x0.8" (20x20mm) per Fig.5.3. 8.3ms single half sine-wave, or equivalent square wave, Duty cycle=4 pulses per minutes maximum.P ppmMinimum 3000Watts Peak Pulse Current of on 10/1000 µs waveform (Note 1,Fig 3)I FSM100Amps Peak Forward Surge Current, 8.3ms Single Half Sine-waveMDE Semiconductor, Inc.MDE Semiconductor, Inc.78-150 Calle Tampico, Unit 210, La Quinta, CA., USA 92253 Tel: 760-564-8656 • Fax: 760-564-2414 3000 Watt Surface Mount TVSUNI- DIRECTIONALPARTNUMBERDEVICEMARKINGCODEUNI-POLARDEVICEMARKINGCODE BI-POLARREVERSESTANDOFFVOLTAGEVRWM (V)BREAKDOWNVOLTAGEVBR (V)MIN. @ ITBREAKDOWNVOLTAGEVBR (V)MAX. @ ITTESTCURRENT(It)mAMAXIMUMCLAMPINGVOLTAGE@Ipp Vc (V)PEAKPULSECURRENTIpp (A)REVERSELEAKAGE@ VRWMIR (µA)SMDJ5.0RDD DDD 5.00 6.407.30109.6312.5800 SMDJ5.0A RDE DDE 5.00 6.407.00109.2326.1800 SMDJ6.0RDF DDF 6.00 6.678.151011.4263.2800 SMDJ6.0A RDG DDG 6.00 6.677.371010.3291.3800 SMDJ6.5RDH DDH 6.507.228.821012.3243.9500 SMDJ6.5A RDK DDK 6.507.227.981011.2267.9500 SMDJ7.0PDL DDL7.007.789.511013.3225.6200 SMDJ7.0A PDM DDM7.007.788.601012.0250.0200 SMDJ7.5PDN DDN7.508.3310.20114.3209.8100 SMDJ7.5A PDP DDP7.508.339.21112.9232.6100 SMDJ8.0PDQ DDQ8.008.8910.90115.0200.050 SMDJ8.0A PDR DDR8.008.899.83113.6220.650 SMDJ8.5PDS DDS8.509.4411.50115.9188.720 SMDJ8.5A PDT DDT8.509.4410.40114.4208.320 SMDJ9.0PDU DDU9.0010.0012.20116.9177.510 SMDJ9.0A PDV DDV9.0010.0011.10115.4194.810 SMDJ10PDW DDW10.0011.1013.60118.8159.65 SMDJ10A PDX DDX10.0011.1012.30117.0176.55 SMDJ11PDY DDY11.0012.2014.90120.1149.35 SMDJ11A PDZ DDZ11.0012.2013.50118.2164.85 SMDJ12PED DED12.0013.3016.30122.0136.45 SMDJ12A PEE DEE12.0013.3014.70119.9150.85 SMDJ13PEF DEF13.0014.4017.60123.8126.15 SMDJ13A PEG DEG13.0014.4015.90121.5139.55 SMDJ14PEH DEH14.0015.6019.10125.8116.35 SMDJ14A PEK DEK14.0015.6017.20123.2129.35 SMDJ15PEL DEL15.0016.7020.40126.9111.55 SMDJ15A PEM DEM15.0016.7018.50124.4123.05 SMDJ16PEN DEN16.0017.8021.80128.8104.25 SMDJ16A PEP DEP16.0017.8019.70126.0115.45 SMDJ17PEQ DEQ17.0018.9023.10130.598.45 SMDJ17A PER DER17.0018.9020.90127.6108.75 SMDJ18PES DES18.0020.0024.40132.293.25 SMDJ18A PET DET18.0020.0022.10129.2102.75 SMDJ20PEU DEU20.0022.2027.10135.883.85 SMDJ20A PEV DEV20.0022.2024.50132.492.65 SMDJ22PEW DEW22.0024.4029.80139.476.15 SMDJ22A PEX DEX22.0024.4026.90135.584.55 SMDJ24PEY DEY24.0026.7032.60143.069.85 SMDJ24A PEZ DEZ24.0026.7029.50138.977.15 SMDJ26PFD DFD26.0028.9035.30146.664.45 SMDJ26A PFE DFE26.0028.9031.90142.171.35 SMDJ28PFF DFF28.0031.1038.00150.159.55 SMDJ28A PFG DFG28.0031.1034.40145.466.15 SMDJ30PFH DFH30.0033.3040.70153.556.15 SMDJ30A PFK DFK30.0033.3036.80148.462.05 SMDJ33PFL DFL33.0036.7044.90159.050.85 SMDJ33A PFM DFM33.0036.7040.60153.356.35MDE Semiconductor, Inc.78-150 Calle Tampico, Unit 210, La Quinta, CA., USA 92253 Tel: 760-564-8656 • Fax: 760-564-2414 3000 Watt Surface Mount TVSUNI- DIRECTIONALPARTNUMBERDEVICEMARKINGCODEUNI-POLARDEVICEMARKINGCODE BI-POLARREVERSESTANDOFFVOLTAGEVRWM (V)BREAKDOWNVOLTAGEVBR (V)MIN. @ ITBREAKDOWNVOLTAGEVBR (V)MAX. @ ITTESTCURRENT(It)mAMAXIMUMCLAMPINGVOLTAGE@Ipp Vc (V)PEAKPULSECURRENTIpp (A)REVERSELEAKAGE@ VRWMIR (µA)SMDJ36PFN DFN36.0040.0048.90164.346.75 SMDJ36A PFP DFP36.0040.0044.20158.151.65 SMDJ40PFQ DFQ40.0044.4054.30171.442.05 SMDJ40A PFR DFR40.0044.4049.10164.546.55 SMDJ43PFS DFR43.0047.8058.40176.739.15 SMDJ43A PFT DFT43.0047.8052.80169.443.25 SMDJ45PFU DFU45.0050.0061.10180.337.45 SMDJ45A PFV DFV45.0050.0055.30172.741.35 SMDJ48PFW DFW48.0053.3065.20185.535.15 SMDJ48A PFX DFX48.0053.3058.90177.438.85 SMDJ51PFY DFY51.0056.7069.30191.132.95 SMDJ51A PFZ DFZ51.0056.7062.70182.436.45 SMDJ54A PGD DGD54.0060.0073.30196.331.25 SMDJ54A PGE DGE54.0060.0066.30187.134.45 SMDJ58PGF DGF58.0064.4078.701103.029.15 SMDJ58A PGG DGG58.0064.4071.20193.632.15 SMDJ60PGH DGH60.0066.7081.501107.028.05 SMDJ60A PGK DGK60.0066.7073.70196.831.05 SMDJ64PGL DGL64.0071.1086.901114.026.35 SMDJ64A PGM DGM64.0071.1078.601103.029.15 SMDJ70PGN DGN70.0077.8095.101125.024.05 SMDJ70A PGP DGP70.0077.8086.001113.026.55 SMDJ75PGQ DGQ75.0083.30102.001134.022.45 SMDJ75A PGR DGR75.0083.3092.101121.024.85 SMDJ78PGS DGS78.0086.70106.001139.021.65 SMDJ78A PGT DGT78.0086.7095.801126.023.85 SMDJ85PGU DGU85.0094.40115.001151.019.95 SMDJ85A PGV DGV85.0094.40104.001137.021.95 SMDJ90PGW DGW90.00100.00122.001160.018.85 SMDJ90A PGX DGX90.00100.00111.001146.020.55 SMDJ100PGY DGY100.00111.00136.001179.016.85 SMDJ100A PGZ DGZ100.00111.00123.001162.018.55 SMDJ110PHD DHD110.00122.00149.001196.015.35 SMDJ110A PHE DHE110.00122.00135.001177.016.95 SMDJ120PHF DHF120.00133.00163.001214.014.05 SMDJ120A PHG DHG120.00133.00147.001193.015.55 SMDJ130PHH DHH130.00144.00176.001230.013.05 SMDJ130A PHK DHK130.00144.00159.001209.014.45 SMDJ150PHL DHL150.00167.00204.001268.011.25 SMDJ150A PHM DHM150.00167.00185.001243.012.35 SMDJ160PHN DHN160.00178.00218.001287.010.55 SMDJ160A PHP DHP160.00178.00197.001259.011.65 SMDJ170PHQ DHQ170.00189.00231.001304.09.95 SMDJ170A PHR DHR170.00189.00209.001275.010.95 For Bidirectional type having Vrwm of 10volts and less, the IR limit is double.。

24c02中文资料 (2)

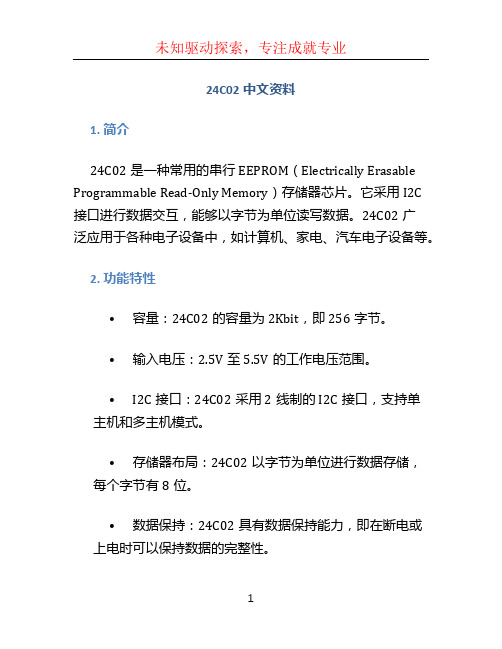

24C02中文资料1. 简介24C02是一种常用的串行EEPROM(Electrically Erasable Programmable Read-Only Memory)存储器芯片。

它采用I2C 接口进行数据交互,能够以字节为单位读写数据。

24C02广泛应用于各种电子设备中,如计算机、家电、汽车电子设备等。

2. 功能特性•容量:24C02的容量为2Kbit,即256字节。

•输入电压:2.5V至5.5V的工作电压范围。

•I2C接口:24C02采用2线制的I2C接口,支持单主机和多主机模式。

•存储器布局:24C02以字节为单位进行数据存储,每个字节有8位。

•数据保持:24C02具有数据保持能力,即在断电或上电时可以保持数据的完整性。

•写保护功能:24C02提供可编程的写保护功能,可以通过设置相应的寄存器位来保护存储器中的数据免受非授权操作。

3. 存储器结构24C02的存储器由256个字节组成,每个字节有8位数据。

存储器分为多个页面,每个页面包含16个字节。

可以通过I2C接口访问这些页面和字节,实现数据的读写操作。

4. 数据读写4.1 读操作要读取24C02中的数据,首先需发送起始条件,并将器件地址(通常为0xA0)和读命令发送到器件。

然后,按照字节的顺序读取数据。

读取操作的流程如下:1.发送起始条件。

2.发送器件地址和读命令。

3.等待器件确认。

4.读取数据。

5.发送停止条件。

4.2 写操作要向24C02写入数据,也需要发送起始条件,并将器件地址和写命令发送到器件。

然后,写入要存储的数据,并发送停止条件。

写入操作的流程如下:1.发送起始条件。

2.发送器件地址和写命令。

3.等待器件确认。

4.写入数据。

5.发送停止条件。

5. 写保护功能24C02提供了可编程的写保护功能,以保护存储器中的数据免受非授权操作。

通过设置存储器的相应寄存器位,可以开启或关闭写保护功能。

具体的设置方法可以参考24C02的数据手册。

M24C04-W1BN6T中文资料