LDS-C5202RI, 规格书,Datasheet 资料

富士通 PRiMERGY BX920 s2 双插槽服务器板数据表说明书

Datasheet Fujitsu PRiMERGY BX920 s2 Dual-sockEt sERvER BlaDEDatasheetFujitsu PRiMERGY BX920 s2 Dual-sockEt sERvER BlaDEunivERsal Dual-sockEl sERvER BlaDE with hiGh coMPutinG anD i/o PERFoRMancE in asMall FoRM FactoRthe PRiMERGY BX Blade servers are the ideal choice for data center solutions of today and tomorrow.our blade servers provide maximum performance and maximum redundancy, but with only minimumspace requirements, low power consumption and a reduction in the time and effort required for cabling.the PRiMERGY BX system family is designed to share components between chassis in order to reactquickly and easily to changing business requirements. storage and server blades can be added withoutany extra effort, as would be needed when cabling or adding management software. You can use thesame applications, rely on the same server and storage components and establish connections to thesame networks. The PRIMERGY BX Blade Servers are flexible and have complete control via a centraladministration instance that is redundant in design; they minimize administrative time and effort, freeingyou of time-consuming administration tasks. our build-to-order process ensures that only completelyinstalled and previously tested solutions are supplied, which have been precisely adapted to individualrequirements and which will grow with future business requirements.PRIMeRGY BX920 s2the PRiMERGY BX920 s2 server Blade uses the cPus of the intel® Xeon® processor 5500 and 5600series and thus the latest and most powerful members of the Xeon® family. utilizing the QuickPatharchitecture and special on-chip memory controllers, the cPus of the intel® Xeon® processor 5600 serieseasily exceed the capacities of the previous generation. the BX920 s2 server blade can host two ofthese processors, with up to two hard drives, 144 GB of DDR3 memory as well as two dual-channel intel82575 Gigabit Ethernet controllers. the protection against data loss can be increased via the Ras function(now available) called channel sparing of the main memory modules in conjunction with cPus from theintel® Xeon® processor 5600 series. the BX920 s2 is ideal for virtualization using hypervisors such asvMware® EsXi, Microsoft hyper-v™, or citrix Xenserver™. in addition, the PRiMERGY BX920 s2 bladesare equipped with the state-of-the-art integrated Remote Management controller (iRMc s2) and - withits wide range of processor, disk and memory options, it provides it managers with the performance andscalability they need for all their data center applications. the optimal and secure support of i/o-intensiveapplications, such as terminal servers is ensured by the optional use of a RaiD controller with write-backcache and BBu.FeatuRes anD BeneFItstechnIcal DetaIlsMaInBoaRDMainboard type D 3030chipset intel® 5500Processor quantity and type 1 - 2 x intel® Xeon® processor 5500 series / intel® Xeon® processor 5600 seriesPRocessoR intel® Xeon® processor E5503(2c/2t, 2.00 Ghz, slc: 4 x 256 kB, tlc: 4 MB, turbo: no, 4.8 Gt/s, Mem bus: 800 Mhz, 80 w)intel® Xeon® processor E5506(4c/4t, 2.13 Ghz, slc: 4 x 256 kB, tlc: 4 MB, turbo: no, 4.8 Gt/s, Mem bus: 800 Mhz, 80 w)intel® Xeon® processor E5507(4c/4t, 2.26 Ghz, slc: 4 x 256 kB, tlc: 4 MB, turbo: no, 4.8 Gt/s, Mem bus: 800 Mhz, 80 w)intel® Xeon® processor E5620(4c/8t, 2.40 Ghz, slc: 4 x 256 kB, tlc: 12 MB, turbo: 1/1/2/2, 5.86 Gt/s, Mem bus: 1066 Mhz, 80 w)intel® Xeon® processor E5630(4c/8t, 2.53 Ghz, slc: 4 x 256 kB, tlc: 12 MB, turbo: 1/1/2/2, 5.86 Gt/s, Mem bus: 1066 Mhz, 80 w)intel® Xeon® processor E5640(4c/8t, 2.66 Ghz, slc: 4 x 256 kB, tlc: 12 MB, turbo: 1/1/2/2, 5.86 Gt/s, Mem bus: 1066 Mhz, 80 w)intel® Xeon® processor l5609(4c/4t, 1.86 Ghz, slc: 4 x 256 kB, tlc: 4 MB, turbo: no, 4.8 Gt/s, Mem bus: 800 Mhz, 40 w)intel® Xeon® processor l5630(4c/8t, 2.13 Ghz, slc: 4 x 256 kB, tlc: 12 MB, turbo: 1/1/2/2, 5.86 Gt/s, Mem bus: 1066 Mhz, 40 w)intel® Xeon® processor l5640(6c/12t, 2.26 Ghz, slc: 4 x 256 kB, tlc: 12 MB, turbo: 2/2/3/3/4/4, 6.4 Gt/s, Mem bus: 1333 Mhz, 60 w)intel® Xeon® processor X5650(6c/12t, 2.66 Ghz, slc: 4 x 256 kB, tlc: 12 MB, turbo: 2/2/2/2/3/3, 6.4 Gt/s, Mem bus: 1333 Mhz, 95 w)intel® Xeon® processor X5660(6c/12t, 2.80 Ghz, slc: 4 x 256 kB, tlc: 12 MB, turbo: 2/2/2/2/3/3, 6.4 Gt/s, Mem bus: 1333 Mhz, 95 w)intel® Xeon® processor X5667(4c/8t, 3.06 Ghz, slc: 4 x 256 kB, tlc: 12 MB, turbo: 2/2/3/3, 6.4 Gt/s, Mem bus: 1333 Mhz, 95 w)intel® Xeon® processor X5670(6c/12t, 2.93 Ghz, slc: 4 x 256 kB, tlc: 12 MB, turbo: 2/2/2/2/3/3, 6.4 Gt/s, Mem bus: 1333 Mhz, 95 w) Memory slots9 (6 slots on cPu 1, 3 slots on cPu 2)Memory slot type DiMM (DDR3)Memory capacity (min. - max.) 2 GB - 144 GBMemory protection advanced EccMemory scrubbingsDDc (chipkill™)Memory Mirroring supporthot-spare memory supportMeMoRY MoDules InDePenDent MoDe 2 GB (1 module(s) 2 GB) DDR3, registered, Ecc, 1333 Mhz, Pc3-10600, DiMM2 GB (1 module(s) 2 GB) DDR3, unbuffered, Ecc, 1333 Mhz, Pc3-10600, DiMM 2 GB (1 module(s) 2 GB) DDR3 lv, unbuffered, Ecc, 1333 Mhz, Pc3-10600, DiMM4 GB (1 module(s) 4 GB) DDR3, registered, Ecc, 1333 Mhz, Pc3-10600, DiMM4 GB (1 module(s) 4 GB) DDR3 lv, registered, Ecc, 1333 Mhz, Pc3-10600, DiMM 8 GB (1 module(s) 8 GB) DDR3, registered, Ecc, 1333 Mhz, Pc3-10600, DiMM8 GB (1 module(s) 8 GB) DDR3 lv, registered, Ecc, 1333 Mhz, Pc3-10600, DiMM 16 GB (1 module(s) 16 GB) DDR3, registered, Ecc, 1066 Mhz, Pc3-8500, DiMMMeMoRY MoDules MIRRoReD MoDe 4 GB (2 module(s) 2 GB) DDR3, registered, Ecc, 1333 Mhz, Pc3-10600, DiMM8 GB (2 module(s) 4 GB) DDR3, registered, Ecc, 1333 Mhz, Pc3-10600, DiMM8 GB (2 module(s) 4 GB) DDR3 lv, registered, Ecc, 1333 Mhz, Pc3-10600, DiMM16 GB (2 module(s) 8 GB) DDR3, registered, Ecc, 1333 Mhz, Pc3-10600, DiMM16 GB (2 module(s) 8 GB) DDR3 lv, registered, Ecc, 1333 Mhz, Pc3-10600, DiMM32 GB (2 module(s) 16 GB) DDR3, registered, Ecc, 1066 Mhz, Pc3-8500, DiMMMeMoRY MoDules sPaRe oR PeR-FoRMance MoDe 6 GB (3 module(s) 2 GB) DDR3, registered, Ecc, 1333 Mhz, Pc3-10600, DiMM12 GB (3 module(s) 4 GB) DDR3, registered, Ecc, 1333 Mhz, Pc3-10600, DiMM 12 GB (3 module(s) 4 GB) DDR3 lv, registered, Ecc, 1333 Mhz, Pc3-10600, DiMM 24 GB (3 module(s) 8 GB) DDR3, registered, Ecc, 1333 Mhz, Pc3-10600, DiMM 24 GB (3 module(s) 16 GB) DDR3 lv, registered, Ecc, 1333 Mhz, Pc3-10600, DiMM 48 GB (3 module(s) 16 GB) DDR3, registered, Ecc, 1066 Mhz, Pc3-8500, DiMMInteRFacesusB ports 4 x usB at the front via special cableGraphics (15-pin) 1 x vGa at the front via special cableserial connection 1 x Rs232 (9-pin) at the front via special cablelan / ethernet (RJ-45) 4 x Gbit Ethernet via Midplane to Ethernet connection Bladeservice lan (RJ45)Service LAN traffic can be switched to shared onboard Gbit LAN portI/o contRolleR on BoaRDRaID controller integrated sas RaiD 0/1 for hDD´slan controller 2 x intel® 82575, 4 x 10/100/1000 Mbit/s Ethernet,Remote Management controller integrated Remote Management controller (iRMc s2, 32 MB attached memory incl. graphics controller) trusted Platform Module (tPM)Infineon / 1.2 (option)slotsPcI-express 2.0 x8 2 x BX900 Mezzanine Mezzanine cardDRIVe BaYshard disk bays2oPeRatInG Paneloperating buttons on/off switchiD buttonstatus leDs Power (amber / green)system status (amber)lan connection (green)Identification (blue)css (yellow)BIosBIos features local and remote update via serverview update Manageronline update tools for main windows and linux versionssMBios v2.6Remote PXE boot supportRemote iscsi boot supportsuPPoRteD oPeRatInG sYsteMssupported operating systems Microsoft® windows server® 2008 R2Microsoft® windows server® 2008Microsoft® windows server® 2003 R2novell susE linux Enterprise serverRed hat Enterprise linuxcitrix® Xenserver™vMware infrastructurenote: support of other linux derivatives on demandoperating system release link /software/dl.aspx?id=a9e600b9-e4cb-4f48-aa41-632f69058421seRVeR ManaGeMentstandard PDa Prefailure Detection and anaylsisasR&R automatic server Recovery and Restartserverview suite:sv installation Managersv operation Managersv RaiD Managersv update Managementsv Power Managementsv agentsserverview Remote Management (iRMc s2)iRMc s2 advanced PackOnline update packages for BIOS, firmware drivers and ServerView Agentsserverview integration solutions for Microsoft sMs, MoM, scoM, sccM and altirisDeployment solution serverview Deployment Manager (fully functional 30-day trial version)option serverview vioM - virtual io Managerserverview integration for tivoli tEc®, tivoli netview, hP nnM and hP operations Managerserver Management notes Regarding operating system dependencies and product details for serverview suite software products see dedicatedproduct datasheets.DIMensIons / WeIGhtDimensions (W x D x h)45 x 500 x 210 mmWeight 5.75 kgWeight notes Actual weight may vary depending on configurationenVIRonMentaltemperature note in accordance with the corresponding PRiMERGY BX900 system unitcoMPlIanceGermany Gseurope cE class a *Global cBRohs (Restriction of hazardous substances)wEEE (waste electrical and electronical equipment)compliance notes in combination with corresponding PRiMERGY BX system unitthere is general compliance with the safety requirements of all European countries and north america. national approvalsrequired in order to satisfy statutory regulations or for other reasons can be applied for on request.compliance link https:///sites/certificates/default.aspxcoMPonentshaRD DIsk DRIVes ssD sata, 3 Gb/s, 64 GB, hot-plug, 2.5-inch, enterprisessD sata, 3 Gb/s, 32 GB, hot-plug, 2.5-inch, enterprisehDD sata, 3 Gb/s, 500 GB, 7200 rpm, hot-plug, 2.5-inch, business criticalhDD sata, 3 Gb/s, 320 GB, 5400 rpm, hot-plug, 2.5-inch, economichDD sata, 3 Gb/s, 160 GB, 7200 rpm, hot-plug, 2.5-inch, business criticalhDD sata, 3 Gb/s, 160 GB, 5400 rpm, hot-plug, 2.5-inch, economichDD sas, 6 Gb/s, 300 GB, 10000 rpm, hot-plug, 2.5-inch, enterprisehDD sas, 6 Gb/s, 146 GB, 15000 rpm, hot-plug, 2.5-inch, enterprisehDD sas, 6 Gb/s, 146 GB, 10000 rpm, hot-plug, 2.5-inch, enterprisehDD sas, 6 Gb/s, 73 GB, 15000 rpm, hot-plug, 2.5-inch, enterprisehard disk notes one Gigabyte equals one billion bytes, when referring to hard disk drive capacity.MezzanIne caRDs Fibre channel Mezzanine card 2 x 8 Gb Emulex (Mc-Fc82E), Pcie x4Ethernet Mezzanine card 4 ports int. x 1 Gb Fujitsu (), Pcie x4InfiniBand Mezzanine Card 2 x 40 Gb Mellanox (), PCIe x8Ethernet Mezzanine card 2 x 10 Gb, Pcie Gen2 x8WaRRantYstandard Warranty 3 yearsservice level (depending on country) MaIntenance anD suPPoRt seRVIces - the PeRFect eXtensIon Recommended service7x24, onsite Response time: 4h spare Parts availability 5 yearsservice Weblink /supportservicecontactFujitsu liMitEDMies-van-der-Rohe-straße 8 80807 München Germanywebsite: 2010-05-03 cE-Enproject for reducing burdens on the environment.using our global know-how, we aim to resolveissues of environmental energy efficiencythrough it.Please find further information at http://www./global/about/environment/delivery subject to availability. any liability thatthe data and illustrations are complete, actualor correct is excluded. Designations may betrademarks and/or copyrights of the respectivemanufacturer, the use of which by third partiesfor their own purposes may infringe the rights ofsuch owner。

人民电器 RDCPS系列控制与保护开关电器 产品说明书

313RDCPS 系列控制与保护开关电器RDCPS 系列控制与保护开关电器,主要用于交流50Hz ( 60Hz )、额定工作电压至400V 、主体额定电流自1A 至125A 、智能控制器可调工作电流自0.4A 至125A 、控制电机功率自0.05KW 至55KW 的电力系统中接通、承载和分断正常条件下(包括规定的过载条件)的电流或电压,也能够接通、承载一定时间和分断规定的非正常条件下(如短路、欠压等)的电流或电压。

□ 周围空气温度:上限值不超过+40℃;下限值不低于-5℃;日平均值不超过+35℃;当周围 空气温度超出以上范围,用户可与我公司协商。

□ 海拔:安装地点的海拔高度不超过2000米。

□ 大气条件:大气相对湿度在周围空气温度+40℃时不超过50%;在较低温度下可以有较高的 相对湿度。

月平均最低温度为+25℃时,该月的平均最大相对湿度为90%,由于温度变化发 生在产品上的凝露必须采取措施。

□ 污染等级:3级□ 安装类别:III 类(690V 系统)、IV (380V 系统)类□ 控制电源电压应在(85%~110%) Us 的波动范围内正常工作条件产品概述选型指南主电路的参数主电路主要由于主体和智能脱扣器构成,这两部分是构成可以应用的RDCPS 产品的最少配置。

主体额定电流in 、约定发热电流Ith 、额定绝缘电压Ui 、额定频率、额定工作电压Ue 以及可选的智能控制器的额定工作电流Ie 范围或控制功率范围见表1、表2。

主要技术数据表1主电路的基本参数314注:□ 瞬时保护参数li 不可调,其值整定在16le电机用产品其短延时保护整定参数ls 可调范围为6lr~12lr □ □ 配电用产品其短延时保护整定参数Is 可调范围为3lr~6lr □ 以上功率范围参考Y 系列三相异步电动机的技术参数 □如有特殊要求时请生产厂家联系表2 主电路的主要参数315RDCPS 系列控制与保护开关电器RDCPS保护特性曲线1.0l r 1最小1.2l r 1最小1.0l r 1最大1.2l r 1最大6l r 1(l r 2最小)12l r 1(l r 2最16l r 1±1520l r 1±20I c s I(A)RDCPS电动机保护时间-电流特性0.1s 0.01s 0.001s1.05l r 1最小1.30l r 1最小1.05l r 1最大1.30l r 1最大3l r 1(l r 2最小)6l r 1(l r 2最大)16l r 1±1520l n ±20%I c sI(A)RDCPS 配电保护时间-电流特性用于电动机控制(使用类别:AC-42、AC-43、AC-44)的动作特性316智能脱扣器主要技术参数□ 起动延时在RDCPS 起动时间内,只对缺相、断相、过压、欠压、欠流、短路、漏电及三相不平衡进行保护,以避免RDCPS 启动大电流和过电流的保护;整定时间为 ( 1~99 ) 秒内之间选择;□ 过压及欠压保护只对辅助电源电压进行保护,以确保线圈与智能控制器正常工作;过压保护:当辅助电源电压超过设定值时(出厂整定在120%Us ),动作时间≤10秒;欠压保护:当辅助电源电压低于设定值时(出厂整定在85%Us ),动作时间≤10秒;□ 反时限过载长延时保护用户根据负载电流I 设定智能脱扣器的额定工作电流Ie ,使负载电流I 在80~100%Ie 之间,动作时间应根据负载特性设定,过流倍数与动作时间特性见表四,反时限过载长延时保护特性曲线出厂设定在F1表3 RDCPS反时限过载长延时保护动作特性用于配电线路负载(使用类别:AC-40、AC-41)的动作特性□ 欠流保护欠流保护:是根据最小电流与额定电流的比值来判断是否启动欠流保护(出厂设定在0),可以对不能空载的电机进行保护;也可以避免用户未根据负载电流I 设定RDCPS 智能脱扣器的工作电流Ie ,从而导致电机不在RDCPS 的保护范围内。

红色贴片式发光二极管XL-2012SURC产品说明书

产品承认书产品名称:0805-T0.8红色贴片式发光二极管产品型号:XL-2012SURC客户名称:客户料号:承认日期:深圳市成兴光电子科技有限公司制定审核核准客户承认栏确认审核核准一、产品描述:●外观尺寸(L/W/H): 2.0x1.25x0.8mm●颜色:高亮度红色●胶体:透明胶体●EIA规范标准包装●环保产品,符合ROHS要求●适用于自动贴片机●适用于回流焊制程二、外形尺寸及建议焊盘尺寸:C athode A nodeG reen m ark建议焊盘尺寸备注:1.单位:毫米(mm)2.公差:如无特别标注则为±0.10mm三、建议焊接温度曲线:有铅制程无铅制程四、最大绝对额定值(Ta=25℃):参数符号最大额定值单位消耗功率Pd55mW最大脉冲电流(1/10占空比,0.1ms脉宽)I FP100mA正向直流工作电流I F25mA 反向电压V R5V 工作环境温度Topr-30°C~+85°C存储环境温度Tstg-40°C~+90°C焊接条件Tsol 回流焊:260°C,10s 手动焊:300°C,3s五、光电参数(Ta=25℃):参数符号最小值代表值最大值单位测试条件光强IV 38---75mcd IF=5mA 半光强视角2θ1/2---120---deg IF=5mA 主波长λD 617---623nm IF=5mA 正向电压VF 1.85--- 2.1V IF=5mA 反向电流IR------1uAVR=5V亮度分档:代码最小值最大值单位测试条件M33845mcdIF=5mAM44560M56075电压分档:代码最小值最大值单位测试条件V1 1.85 1.9V IF=5mAV2 1.9 1.95V3 1.95 2.0V4 2.0 2.05V52.052.1波长分档:代码最小值最大值单位测试条件R1617619nmIF=5mAR2619621R3621623六、光电参数代表值特征曲线:φ60七、标签标识:CAT :光强(mcd )HUE :波长(nm )REF :电压(V )误差范围a.Luminous Intensity:±15%b.HUE:±1nmc.Forward Voltage:±0.1V八、包装载带与圆盘尺寸:φ13.0AU ser Feed D irectionAA-A剖面图备注:1.单位:毫米(mm)2.公差:如无特别标注则为±0.15mm九、圆盘及载带卷出方向及空穴规格:尾端至少160mm盖带和空壳载带的组合开始端装有零件部分至少160mm盖带和至少160mm独立盖带或空壳载带的组合盖带与空壳载带的组合十、内包装及外包装:内标签圆盘干燥剂防潮防静电袋5cartons/box外标签抽真空、热封10bags/carton十一、信赖性实验:测试项目测试条件测试次数参考标准失效判定标准失效LED数量(PCS)防潮等级1.回流焊最高温度=260℃,10秒,2次回流焊;2.回流焊之前存储条件:30℃,相对湿度=70%,168H;-JEITAED-4701300301﹟10/22焊接信赖性(无铅回流焊)回流焊最高温度=245±5℃,5秒(无铅回流焊)-JEITAED-4701303303A﹟20/22冷热循环-40℃30分钟~25℃5分钟~100℃30分钟~25℃5分钟300个循环JESD22-A104﹟10/22冷热冲击-35℃15分钟转换时间3分钟85℃15分钟300个循环JESD22-A106﹟10/22高温存储Ta=100℃1000小时JESD22-A103﹟10/22低温存储Ta=-40℃1000小时JESD22-A119﹟10/22常温老化Ta=25℃IF=20mA1000小时JESD22-A108﹟10/22(2)失效标准标准﹟项目测试条件失效标准﹟1正向电压(V F)I F=20mA>U.S.L*1.1光强(IV)I F=20mA<L.S.L*0.7反向电流(I R)V R=5V>U.S.L*2.0﹟2焊接可靠性/锡膏覆盖焊盘比例小于95%★U.S.L:规格上限L.S.L:规格下限十二、使用注意事项:◆使用:1.过高的温度会影响LED的亮度以及其他性能,所以为使LED有较好的性能表现,应将LED远离热源。

IP5206 datasheet v1.0

3 简介

IP5206 是一款集成升压转换器、 锂电池充电管 理、电池电量指示的多功能电源管理 SOC,为移动 电源提供完整的电源解决方案。 IP5206 的高集成度与丰富功能, 使其在应用时 仅需极少的外围器件, 并有效减小整体方案的尺寸, 降低 BOM 成本。 IP5206 只需一个电感实现降压与升压功能。 DC-DC 转换器工作在 600KHz, 可以支持低成本电 感和电容。 IP5206 的同步升压系统提供最大 2A 输出电流, 转换效率高至 95%。空载时,自动进入休眠状态, 静态电流降至 50uA。 IP5206 采用开关充电技术,提供最大 1.5A 电 流,充电效率高至 96%。内置 IC 温度和输入电压 智能调节充电电流。 IP5206 内置 14bit ADC, 精确测量电池电压和 电流. 支持 3/4/5 颗 LED 电量显示和照明功能。 IP5206 采用 ESOP16L 封装。

图 2 IP5206 引脚图

IP5206

VBAT KEY GND L4 VREG L3 L2 GND L1 16 15 14 13 12 11 10 9

引脚 序号

1 2 3、4 5、6 7 8 9 10 11 12 13 14 15 16 17

描述 名称

CSIN GND LX VOUT VIN LIGHT L1 L2 L3 VREG L4 GND KEY VBAT GND Current sense input GROUND DCDC switch node,connect inductor DCDC 5v OUTPUT pin Charger 5V input pin LED lighting driver Battery indicator pin1 Battery indicator pin2 Battery indicator pin3 Regulator output pin Battery indicator pin4 GROUND Key input pin Battery voltage sense pin EPAD,should be connected to GND

EUCHIPS EUCP50XY-1WxxxxC-0MWWZ LED 恒流调光驱动器 产品说明书

SHANGHAI EUCHIPS INDUSTRIAL CO.,LTDEUCP50XY-1WxxxxC-0MWWZProduct FeaturesLED 恒流调光驱动器概述EUCP50XY-1WxxxxC-0MWWZ 系列是恒流模式输出的LED 驱动器,抗浪涌等级高,防护等级为IP67,适用于户外。

用户可根据调光方式和市场需求选择相应的型号,并可通过NFC 编程器修改输出电流。

电源电压: 100-277VAC 或 141-391VDC 10kV 浪涌等级- 60℃低温启动(可选择) 100,000小时的寿命@ Tc=75C 5 年保修 @ Tc<=80C Airset TM NFC 编程电流输出精度+/-2% (可编程模型) 0-10V/PWM/DALI 可调光 (取决于型号) 调灭后待机功耗0.5W(取决于型号)电源控制器与风扇的辅助电源为12V 300mA (取决于型号) 输入过压保护(可选择)UL Class P , Class 2,ENEC/CB/CCC,SELV 认证 安全依据EN 61347-1, 61347-2-3,61347-2-13, 62384 应用 :LED 灯带、景观灯、工矿灯、路灯、泛光灯上海欧切斯实业有限公司型号清单 技术参数上海欧切斯实业有限公司注: 除非特别注明,所有的测试结果均在220VAC ,25℃室温下测得。

* 可选择标记项目,获取详细功能请联系销售人员调光安规/电磁兼容调调光光曲曲线线a. 带调灭功能默认值)b. 无调灭功能(联系销售获取此功能调光接线图(End of Life: Maximum Failure Rate=10%)使用寿命 vs. 外壳温度功率因数vs.负载THD vs.负载EUCP50NN(FR)-1WxxxxC-0MWWUUnspecified tolerance :±1AC INPUT(UL SJTW 3×18AWG)DC OUTPUT(UL SJTW 2×18AWG)BLACK(ACL)WHITE(ACN)GREEN(GND)RED(V+)BLUE(V-)效率 vs.负载 (1050mA)尺寸 (mm)EUCP50AR(AN)-1WxxxxC-0MWWUUnspecified tolerance :±1AC INPUT(UL SJTW 3×18AWG)DC OUTPUT(UL SJTW 2×18AWG)DIMMING WIRE(UL SJTW 2×18AWG)BLACK(ACL)WHITE(ACN)GREEN(GND)PURPLE(Vdim+)GRAY(Vdim-)RED(V+)BLUE(V-)EUCP50ER-1WxxxxC-0MWWUUnspecified tolerance :±1AC INPUT(UL SJTW 3×18AWG)DC OUTPUT(UL SJTW 2×18AWG)DIMMING WIRE(UL SJTW 3×18AWG)BLACK(ACL)WHITE(ACN)GREEN(GND)BLACK&WHITE(Vaux/+12V)PURPLE(Vdim+)GRAY(Vdim-)RED(V+)BLUE(V-)EUCP50DR-1WxxxxC-0MWWUUnspecified tolerance :±1AC INPUT(UL SJTW 3×18AWG)DC OUTPUT(UL SJTW 2×18AWG)DIMMING WIRE(UL 2464 4×22AWG)BLACK(ACL)WHITE(ACN)GREEN(GND)RED(V+)BLUE(V-)PINK(DALI 2)BLACK&WHITE(Vaux+)GRAY(Vaux-)BLUE&WHITE(DALI 1)EUCP50NN(FR)-1WxxxxC-0MWWSUnspecified tolerance :±1AC INPUT(VDE H05RN-F 3×1.0mm2)DC OUTPUT(VDE H05RN-F 2×1.0mm2)BROWN(ACL)BLUE(ACN)YELLOW&GREEN (GND)BROWN(V+)BLUE(V-)EUCP50AR(AN)-1WxxxxC-0MWWSUnspecified tolerance :±1AC INPUT(VDE H05RN-F 3×1.0mm2)DC OUTPUT(VDE H05RN-F 2×1.0mm2)DIMMING WIRE(H05RN-F 2×0.75mm2)BROWN(ACL)BLUE(ACN)YELLOW&GREEN (GND)PURPLE(Vdim+)GRAY(Vdim-)BROWN(V+)BLUE(V-)EUCP50ER-1WxxxxC-0MWWSUnspecified tolerance :±1AC INPUT(VDE H05RN-F 3×1.0mm2)DC OUTPUT(VDE H05RN-F 2×1.0mm2)DIMMING WIRE(H05RN-F 3×0.75mm2)BROWN(ACL)BLUE(ACN)YELLOW&GREEN (GND)BLACK&WHITE(Vaux/+12V)PURPLE(Vdim+)GRAY(Vdim-)BROWN(V+)BLUE(V-)EUCP50DR-1WxxxxC-0MWWSUnspecified tolerance :±1AC INPUT(VDE H05RN-F 3×1.0mm2)DC OUTPUT(VDE H05RN-F 2×1.0mm2)DIMMING WIRE(H05RN-F 4×0.5mm2)BROWN(ACL)BLUE(ACN)YELLOW&GREEN (GND)BROWN(V+)BLUE(V-)PINK(DALI 2)BLACK&WHITE(Vaux+)GRAY(Vaux-)BLUE&WHITE(DALI 1)。

AD2S1205WSTZ;AD2S1205YSTZ;ADW71205WSTZ-RL;ADW71205WSTZ;ADW71205YSTZ;中文规格书,Datasheet资料

12-Bit RDCwith Reference OscillatorAD2S1205 Rev. AInformation furnished by Analog Devices is believed to be accurate and reliable. However, noresponsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners. One Technology Way, P.O. Box 9106, Norwood, M A 02062-9106, U.S.A. Tel: 781.329.4700 Fax: 781.461.3113 ©2007–2010 Analog Devices, Inc. All rights reserved.FEATURESComplete monolithic resolver-to-digital converter (RDC) Parallel and serial 12-bit data portsSystem fault detection±11 arc minutes of accuracyInput signal range: 3.15 V p-p ± 27%Absolute position and velocity outputs1250 rps maximum tracking rate, 12-bit resolution Incremental encoder emulation (1024 pulses/rev) Programmable sinusoidal oscillator on boardSingle-supply operation (5.00 V ± 5%)−40°C to +125°C temperature rating44-lead LQFP4 kV ESD protectionQualified for automotive applications APPLICATIONSAutomotive motion sensing and controlHybrid-electric vehiclesElectric power steeringIntegrated starter generator/alternatorIndustrial motor controlProcess control FUNCTIONAL BLOCK DIAGRAMFigure 1.GENERAL DESCRIPTIONThe AD2S1205 is a complete 12-bit resolution tracking resolver-to-digital converter that contains an on-board programmable sinusoidal oscillator providing sine wave excitation for resolvers.The converter accepts 3.15 V p-p ± 27% input signals on the Sin and Cos inputs. A Type II tracking loop is employed to track the inputs and convert the input Sin and Cos information into a digital representation of the input angle and velocity. The maximum tracking rate is a function of the external clock frequency. The performance of the AD2S105 is specified across a frequency range of 8.192 MHz ± 25%, allowing a maximum tracking rate of 1250 rps. PRODUCT HIGHLIGHTS1.Ratiometric Tracking Conversion. The Type II trackingloop provides continuous output position data withoutconversion delay. It also provides noise immunity andtolerance of harmonic distortion on the reference andinput signals.2.System Fault Detection. A fault detection circuit can senseloss of resolver signals, out-of-range input signals, inputsignal mismatch, or loss of position tracking.3.Input Signal Range. The Sin and Cos inputs can acceptdifferential input voltages of 3.15 V p-p ± 27%.4.Programmable Excitation Frequency. Excitation frequencyis easily programmable to 10 kHz, 12 kHz, 15 kHz, or 20 kHz by using the frequency select pins (the FS1 and FS2 pins).5.Triple Format Position Data. Absolute 12-bit angular positiondata is accessed via either a 12-bit parallel port or a 3-wire serial interface. Incremental encoder emulation is in standard A-quad-B format with direction output available.6.Digital Velocity Output. 12-bit signed digital velocity accessedvia either a 12-bit parallel port or a 3-wire serial interface.AD2S1205Rev. A | Page 2 of 20TABLE OF CONTENTSFeatures .............................................................................................. 1 Applications ....................................................................................... 1 Functional Block Diagram .............................................................. 1 General Description ......................................................................... 1 Product Highlights ........................................................................... 1 Revision History ............................................................................... 2 Specifications ..................................................................................... 3 Absolute Maximum Ratings ............................................................ 5 ESD Caution .................................................................................. 5 Pin Configuration and Function Descriptions ............................. 6 Resolver Format Signals ................................................................... 8 Theory of Operation ........................................................................ 9 Fault Detection Circuit ................................................................ 9 Monitor Signal .............................................................................. 9 Loss of Signal Detection .............................................................. 9 Signal Degradation Detection .................................................. 10 Loss of Position Tracking Detection ........................................ 10 Responding to a Fault Condition ............................................. 10 False Null Condition .................................................................. 10 On-Board Programmable Sinusoidal Oscillator .................... 11 Synthetic Reference Generation ............................................... 11 Charge-Pump Output ................................................................ 11 Connecting the Converter ........................................................ 11 Clock Requirements ................................................................... 12 Absolute Position and Velocity Output ................................... 12 Parallel Interface ......................................................................... 12 Serial Interface ............................................................................ 14 Incremental Encoder Outputs .................................................. 16 Supply Sequencing and Reset ................................................... 16 Circuit Dynamics ........................................................................... 17 Loop Response Model ............................................................... 17 Sources of Error .......................................................................... 18 Connecting to the DSP .............................................................. 19 Outline Dimensions ....................................................................... 20 Ordering Guide .......................................................................... 20 Automotive Products .. (20)REVISION HISTORY5/10—Rev. 0 to Rev. AChanges to Features Section............................................................ 1 Changes to Input Bias Current Parameter and InputImpedance Parameter ...................................................................... 3 Changes to Table 2 ............................................................................ 5 Changes to Loss of Signal Detection Section ................................ 9 Changes to Connecting the Converter Section and Figure 5 ... 11 Change to t 6 Max Value in Table 6 ............................................... 13 Changes to t 9 and t 10 Max Values Table 7 .................................... 15 Changes to Ordering Guide .......................................................... 20 Added Automotive Products Section .......................................... 20 1/07—Revision 0: Initial VersionAD2S1205SPECIFICATIONSAV DD = DV DD = 5.0 V ± 5% at −40°C to +125°C, CLKIN = 8.192 MHz ± 25%, unless otherwise noted.Rev. A | Page 3 of 20AD2S12051 The voltages for Sin, SinLO, Cos, and CosLO relative to AGND must be between 0.2 V and AV DD.Rev. A | Page 4 of 20AD2S1205Rev. A | Page 5 of 20ABSOLUTE MAXIMUM RATINGSTable 2.Parameter RatingSupply Voltage (V DD ) −0.3 V to +7.0 VSupply Voltage (AV DD ) −0.3 V to +7.0 VInput Voltage −0.3 V to V DD + 0.3 VOutput Voltage Swing −0.3 V to V DD + 0.3 VInput Current to Any Pin Except Supplies 1 ±10 mAOperating Temperature Range (Ambient) −40°C to +125°C Storage Temperature Range −65°C to +150°C1Transient currents of up to 100 mA do not cause latch-up.Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stressrating only; functional operation of the device at these or anyother conditions above those indicated in the operationalsection of this specification is not implied. Exposure to absolutemaximum rating conditions for extended periods may affectdevice reliability. ESD CAUTIONAD2S1205Rev. A | Page 6 of 2006339-002PIN CONFIGURATION AND FUNCTION DESCRIPTIONSR E F O U T44R E F B Y P43C o s L O40S i n L O38A G N D42A G N D36A V D D39E X C35E X C34C o s41S i n37DV DD 1RD 2CS 3SAMPLE4RDVEL 5SOE 6DB11/SO 7DB10/SCLK8DB99DB810DB71133FS232FS131LOT 30DOS 29AD2S1205TOP VIEW (Not to Scale)DIR 28NM 27B 26A 25CPO 24DGND23DB 612D B 513D B 414D B 315D G N D16D V D D17D B 218D B 119D B 020X T A L O U T21C L K I N22Figure 2. Pin ConfigurationAD2S1205Rev. A | Page 7 of 20AD2S1205Rev. A | Page 8 of 20RESOLVER FORMAT SIGNALS06339-003V b = V s × Sin(ωt) × Sin(θ)(A) CLASSICAL RESOLVERs × Sin(ωt) × Cos(θ)V b = V s × Sin(ωt) × Sin(θ)(B)VARIABLE RELUCTANCE RESOLVERs × Sin(ωt) × Cos(θ)Figure 3. Classical Resolver vs. Variable Reluctance ResolverA classical resolver is a rotating transformer that typically has a primary winding on the rotor and two secondary windings on the stator. A variable reluctance resolver, on the other hand, has the primary and secondary windings on the stator and no windings on the rotor, as shown in Figure 3; however, the saliency in this rotor design provides the sinusoidal variation in the secondary coupling with the angular position. For both designs, the resolver output voltages (S3 − S1, S2 − S4) are as follows:Sinθt Sin E S1S30×ω=−)( (1)Cosθt Sin E S4S20×ω=−)(where:θ is the shaft angle.Sin(ωt) is the rotor excitation frequency. E 0 is the rotor excitation amplitude.The stator windings are displaced mechanically by 90° (see Figure 3). The primary winding is excited with an ac reference. The amplitude of subsequent coupling onto the secondary windings is a function of the position of the rotor (shaft) relative to the stator. The resolver therefore produces two output voltages (S3 − S1, S2 − S4), modulated by the sine and cosine of the shaft angle. Resolver format signals refer to the signals derived from the output of a resolver, as shown in Equation 1. Figure 4 illustrates the output format. 06339-0040°R2 – R4(REFERENCE)90°180°θ270°360°Figure 4. Electrical Resolver RepresentationAD2S1205Rev. A | Page 9 of 20THEORY OF OPERATIONThe AD2S1205’s operation is based on a Type II tracking closed-loop principle. The digitally implemented tracking loop continually tracks the position and velocity of the resolver without the need for external convert and wait states. As the resolver moves through a position equivalent to the least significant bit weighting, the tracking loop output is updated by 1 LSB.The converter tracks the shaft angle (θ) by producing an output angle (ϕ) that is fed back and compared with the input angle (θ); the difference between the two angles is the error, which is driven towards 0 when the converter is correctly tracking the input angle. T o measure the error, S3 − S1 is multiplied by Cosϕ and S2 − S4 is multiplied by Sinϕ to giveS4 S2for )(S1S3for )(00−×−×SinφCosθωt Sin E CosφSinθωt Sin E (2)The difference is taken, giving)()(0SinφCosθCos Sinθωt Sin E −φ× (3)This signal is demodulated using the internally generated synthetic reference, yielding)(0φ−φSin CosθCos SinθE (4)Equation 4 is equivalent to E 0Sin (θ − ϕ), which is approximately equal to E 0(θ − ϕ) for small values of θ − ϕ, where θ − ϕ is the angular error. The value E 0(θ − ϕ) is the difference between the angular error of the rotor and the digital angle output of the converter. A phase-sensitive demodulator, some integrators, and a compen-sation filter form a closed-loop system that seeks to null the error signal. If this is accomplished, ϕ equals the resolver angle, θ, within the rated accuracy of the converter. A Type II tracking loop is used so that constant velocity inputs can be tracked without inherent error.For more information about the operation of the converter, see the Circuit Dynamics section.FAULT DETECTION CIRCUITThe AD2S1205 fault detection circuit can sense loss of resolver signals, out-of-range input signals, input signal mismatch, or loss of position tracking; however, the position indicated by the AD2S1205 may differ significantly from the actual shaft position of the resolver.MONITOR SIGNALThe AD2S1205 generates a monitor signal by comparing the angle in the position register to the incoming Sin and Cos signals from the resolver. The monitor signal is created in a similar fashion to the error signal (described in the Theory of Operation section). The incoming Sinθ and Cosθ signals are multiplied by the Sin and Cos of the output angle, respectively, and then these values are added together:)()(CosφCosθA2SinφSinθA1Monitor ××+××= (5)where:A1 is the amplitude of the incoming Sin signal (A1 × Sinθ). A2 is the amplitude of the incoming Cos signal (A2 × Cosθ).θ is the resolver angle.ϕ is the angle stored in the position register.Note that Equation 5 is shown after demodulation with thecarrier signal Sin(ωt) removed. Also note that for a matchedinput signal (that is, a no fault condition), A1 is equal to A2.When A1 is equal to A2 and the converter is tracking (therefore, θ is equal to ϕ), the monitor signal output has aconstant magnitude of A1 (Monitor = A1 × (Sin 2θ + Cos 2θ) = A1), which is independent of the shaft angle. When A1 does notequal A2, the monitor signal magnitude alternates between A1 and A2 at twice the rate of the shaft rotation. The monitor signal is used to detect degradation or loss of input signals. LOSS OF SIGNAL DETECTIONLoss of signal (LOS) is detected when either resolver input (Sin or Cos) falls below the specified LOS Sin/Cos threshold. The AD2S1205 detects this by comparing the monitor signal to a fixed minimum value. Without the use of external circuitry, the AD2S1205 can detect the loss of up to three of the four connections from the resolver. The addition of two external 68 kΩ resistors, as outlined in Figure 5, ensures that the loss of all 4 connections, that is, complete removal of the resolver, may also be detected. LOS is indicated by both DOS and LOT latching as logic low outputs. The DOS and LOT pins are reset to the no fault state by a rising edge of SAMPLE . The LOS condition has priority over both the DOS and LOT conditions, as shown in . LOS is indicated within 57° of the angular output error (worst case).Table 4AD2S1205Rev. A | Page 10 of 20SIGNAL DEGRADATION DETECTIONDegradation of signal (DOS) is detected when either resolver input (Sin or Cos) exceeds the specified DOS Sin/Cos threshold. The AD2S1205 detects this by comparing the monitor signal to a fixed maximum value. In addition, DOS is detected when the amplitudes of the Sin and Cos input signals are mismatched by more than the specified DOS Sin/Cos mismatch. This is identified because the AD2S1205 continuously stores the minimum and maximum magnitude of the monitor signal in internal registers and calculates the difference between these values. DOS is indicated by a logic low on the DOS pin and is not latched when the input signals exceed the maximum input level. When DOS is indicated due to mismatched signals, the output is latched low until a rising edge of SAMPLE resets the stored minimum and maximum values. The DOS condition has priority over the LOT condition, as shown in . DOS is indicated within 33° of the angular output error (worst case).Table 4LOSS OF POSITION TRACKING DETECTIONLoss of tracking (LOT) is detected when • The internal error signal of the AD2S1205 exceeds 5°. • The input signal exceeds the maximum tracking rate. •The internal position (at the position integrator) differs from the external position (at the position register) by more than 5°.LOT is indicated by a logic low on the LOT pin and is not latched. LOT has a 4° hysteresis and is not cleared until the internal error signal or internal/external position mismatch is less than 1°. When the maximum tracking rate is exceeded, LOT is cleared only if the velocity is less than the maximum tracking rate and the internal/external position mismatch is less than 1°. LOT can be indicated for step changes in position (such as after a RESET signal is applied to the AD2S1205), or for accelerations of >~65,000 rps 2. It is also useful as a built-in test to indicate that the tracking converter is functioningproperly. The LOT condition has lower priority than both the DOS and LOS conditions, as shown in . The LOT and DOS conditions cannot be indicated at the same time. Table 4Table 4. Fault Detection DecodingConditionDOS Pin LOT Pin Order of Priority Loss of Signal (LOS)0 0 1 Degradation of Signal (DOS) 0 1 2 Loss of Tracking (LOT) 1 0 3 No Fault1 1RESPONDING TO A FAULT CONDITIONIf a fault condition (LOS, DOS, or LOT) is indicated by the AD2S1205, the output data is presumed to be invalid. Even if a RESET or SAMPLE pulse releases the fault condition and is not immediately followed by another fault, the output data may be corrupted. As discussed previously, there are some fault conditions with inherent latency. If the device fault is cleared, there may be some latency in the resolver’s mechanical position before the fault condition is reindicated.When a fault is indicated, all output pins still provide data, although the data may or may not be valid. The fault condition does not force the parallel, serial, or encoder outputs to a known state. Response to specific fault conditions is a system-level requirement. The fault outputs of the AD2S1205 indicate that the device has sensed a potential problem with either the internal or external signals of the AD2S1205. It is the responsibility of the system designer to implement the appropriate fault-handling schemes within the control hardware and/or algorithm of a given appli-cation based on the indicated fault(s) and the velocity or position data provided by the AD2S1205.FALSE NULL CONDITIONResolver-to-digital converters that employ Type II tracking loops based on the previously stated error equation (see Equation 4 in the Theory of Operation section) can suffer from a condition known as a false null. This condition is caused by a metastable solution to the error equation when θ − ϕ = 180°. The AD2S1205 is not susceptible to this condition because its hysteresis is implemented external to the tracking loop. As a result of the loop architecture chosen for the AD2S1205, the internal error signal constantly has some movement (1 LSB per clock cycle); therefore, in a metastable state, the converter moves to anunstable condition within one clock cycle. This causes the tracking loop to respond to the false null condition as if it were a 180° step change in input position (the response time is the same, as specified in the Dynamic Performance section of Table 1). Therefore, it is impossible to enter the metastable condition after the start-up sequence if the resolver signals are valid.分销商库存信息:ANALOG-DEVICESAD2S1205WSTZ AD2S1205YSTZ ADW71205WSTZ-RL ADW71205WSTZ ADW71205YSTZ EVAL-AD2S1205SDZ。

FGA25N120FTD;中文规格书,Datasheet资料

@ TC = 25oC @ TC = 100oC

Diode continuous Forward current Maximum Power Dissipation Maximum Power Dissipation Operating Junction Temperature

@ TC = 100oC @ TC = 25oC @ TC = 100oC

Symbol

Parameter

Test Conditions

VFM

Diode Forward Voltage

IF = 25A

TC = 25oC TC = 125oC

trr

Diode Reverse Recovery Time

TC = 25oC TC = 125oC

Irr

Diode Reverse Recovery Time

©2009 Fairchild Semiconductor Corporation

1

FGA25N120FTD Rev. A1

G

E

Ratings

1200 ± 25 50 25 75 25 313 125 -55 to +150 -55 to +150 300

Units

V V A A A A W W oC oC

Applications

• Induction heating and Microvewave oven • Soft switching applications

February 2009

tm

General Description

Using advanced field stop trench technology, Fairchild’s 1200V trench IGBTs offer superior conduction and switching performances, and easy parallel operation with exceptional avalanche ruggedness. This device is designed for soft switching applications.

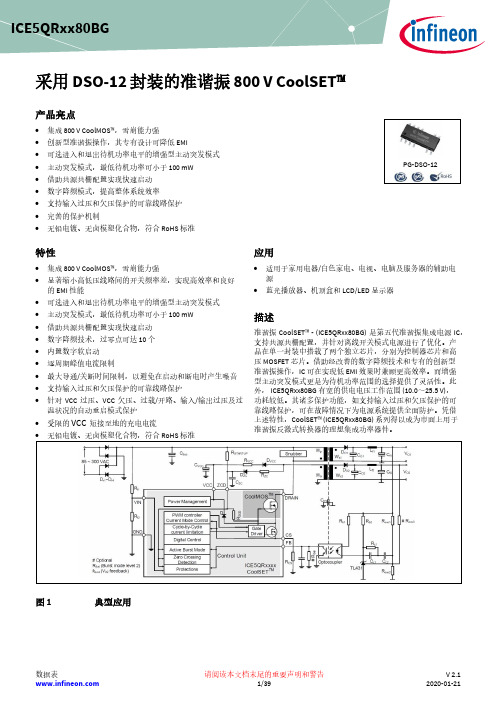

英飞凌 ICE5QRxx80BG 第五代准谐振集成电源IC 数据表

采用 DSO-12 封装的准谐振 800 V CoolSET ™产品亮点• 集成 800 V CoolMOS ™,雪崩能力强 • 创新型准谐振操作,其专有设计可降低 EMI• 可选进入和退出待机功率电平的增强型主动突发模式 • 主动突发模式,最低待机功率可小于 100 mW • 借助共源共栅配置实现快速启动 • 数字降频模式,提高整体系统效率 • 支持输入过压和欠压保护的可靠线路保护 • 完善的保护机制•无铅电镀、无卤模塑化合物,符合 RoHS 标准特性• 集成 800 V CoolMOS ™,雪崩能力强• 显著缩小高低压线路间的开关频率差,实现高效率和良好的 EMI 性能• 可选进入和退出待机功率电平的增强型主动突发模式 • 主动突发模式,最低待机功率可小于 100 mW • 借助共源共栅配置实现快速启动 • 数字降频技术,过零点可达 10 个 • 内置数字软启动 • 逐周期峰值电流限制• 最大导通/关断时间限制,以避免在启动和断电时产生噪音 • 支持输入过压和欠压保护的可靠线路保护•针对 VCC 过压、VCC 欠压、过载/开路、输入/输出过压及过温状况的自动重启模式保护• 受限的 VCC 短接至地的充电电流• 无铅电镀、无卤模塑化合物,符合 RoHS 标准应用• 适用于家用电器/白色家电、电视、电脑及服务器的辅助电源• 蓝光播放器、机顶盒和 LCD/LED 显示器描述准谐振 CoolSET ™ - (ICE5QRxx80BG) 是第五代准谐振集成电源 IC ,支持共源共栅配置,并针对离线开关模式电源进行了优化。

产品在单一封装中搭载了两个独立芯片,分别为控制器芯片和高压 MOSFET 芯片。

借助经改善的数字降频技术和专有的创新型准谐振操作,IC 可在实现低 EMI 效果时兼顾更高效率。

而增强型主动突发模式更是为待机功率范围的选择提供了灵活性。

此外, ICE5QRxx80BG 有宽的供电电压工作范围 (10.0~25.5 V), 功耗较低。

CR5229规格书-中文版,欢迎观看,下载。。。

启达科技(成都)有限公司

典型应用

启达科技(成都)有限公司 V1.3

成都启臣微电子有限公司 2/8

CR5229

功能框图

绿色节能电流模反激 PWM 功率开关

极限参数

符号 VDD VDDG VDrain IVDD VFB VSense

ESD

TL

TSTG TJ

参数

工作电压

功率输出电路的电源电压

高压MOSFET漏端电压(关闭状态)

备用开关电源 ADSL等无线路由器开关电源

概述

CR5229 是内置高压功率 MOSFET 的电 流模反激 PWM 控制芯片,适用于 18W 以内 的离线式反激开关电源,具有高性能、低待机 功耗、低成本的优点。

为了保证芯片正常工作,CR5229 针对各 种故障设计了一系列完善的具有自动恢复功 能的保护措施,包括软启动、过温保护(OTP)、

成都启臣微电子有限公司

V1.3

6/8

CR5229

绿色节能电流模反激 PWM 功率开关

为了滤除 MOSFET 导通瞬间 SENSE 端所产生 的瞬时大电压,防止错误的 SENCE 峰值电流 检测。在前沿消隐时间内,功率 MOSFET 始 终保持关断。这样就可以节省一个外部的 RC 网络。

内部斜波补偿

斜波补偿电路在 SENSE 端检测电压信号 上叠加了一个三角波信号。这极大的改善了系 统工作在 CCM 模式的闭环稳定性,防止次谐 波振荡,减小输出纹波电压。

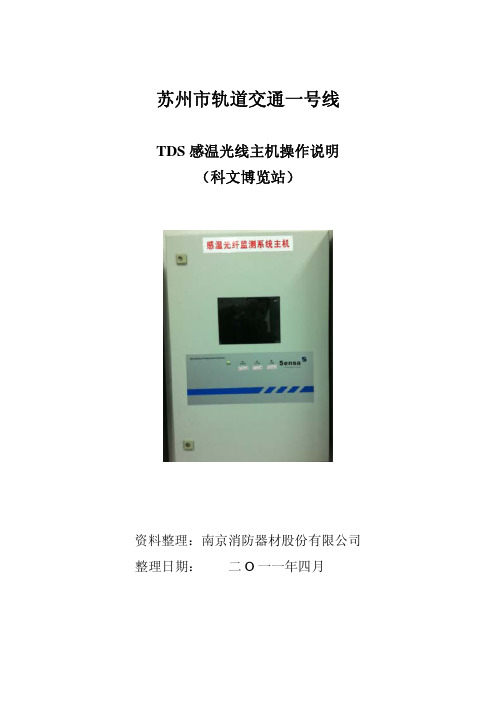

感温光纤主机DTS用户手册

3.2 多台主机联网

每一台主机都有一个唯一的固定IP地址。通过网络集线器或网络交换机,可 以实现多台主机与一台计算机的网络连接,如图7所示。

图7 多台DTS联网拓扑结构 当有多台主机与计算机连接时,所有主机的数据都根据上位计算机的指令要 求上传给计算机,用户在软件主界面选择需要显示的主机及其感温光纤。

图2

图3 此时,通过 DTS 处理器可读出光纤内部信息,最终在计算机上显示相应温 度数据。 后向散射光谱 在后向散射光谱中,有多个波长光谱,如下图所示。下面就对这些光谱作分 析。

5

图 4 后向散射光谱 【瑞利散射】

瑞利散射,散射光谱中的最强部分,对温度的敏感性弱,所以不适用于温度 感应。 【布里渊散射】

在后向散射的频率光谱中拉曼散射和瑞利散射以及布里渊散射的距离足够 大,因此拉曼散射光可通过一个滤波器与其他散射光分离,并可用雪崩光电二极 管检测器(APD)进行检测。其所分出的两个波段中,波长较长的波段 (Stokes), 温度感应特性弱,但是,波长较短的波段(Anti-Stokes),具有很强的的温度敏 感性。 【Stokes 和 Anti-Stokes】

产品包装 建议将产品原始包装妥善保管,当设备退回厂家进行维护时,可减少由于运

输造成设备损坏的可能性。

激光器安全注意 DTS 被认定为一流的激光产品,在通常的操作条件下,应根据用户文档使

用。

2

激光器规格 激光器类型 脉冲宽度 脉冲重复频率 最大脉冲能量

脉冲式 <50 ns <12 kHz 15 nJ

4.1.1 DTS 壁挂式的安装.......................................................................................................... 11 4.1.2 传感光缆的安装 ............................................................................................................ 12 4.2 系统调试 ............................................................................................................................... 14 4.2.1 配置文件设置 ................................................................................................................ 15 4.2.2 软件的操作步骤 ............................................................................................................. 23 第五章 维护和保养 ........................................................................................................................ 25 第六章 注意事项 ............................................................................................................................ 27

Pm25LD512C datasheet v0.7

Pm25LD512CChingis Technology Corp.1DRAFT Date: June , 2011, Rev: 0.7FEATURES• Single Power Supply Operation - Low voltage range: 2.7 V - 3.6 V• Memory Organization- Pm25LD512C: 64K x 8 (512Kbit)• Cost Effective Sector/Block Architecture - 512Kb : Uniform 4KByte sectors / two uniform32KByte blocks• Low standby current 1uA (Typ)• Serial Peripheral Interface (SPI) Compatible - Supports single- or dual-output - Supports SPI Modes 0 and 3- Maximum 33 MHz clock rate for normal read - Maximum 100 MHz clock rate for fast read• Page Program (up to 256 Bytes) Operation - Typical 2 ms per page program• Sector, Block or Chip Erase Operation - Maximum 15ms sector, block or chip erase• Low Power Consumption- Typical 10 mA active read current - Typical 15 mA program/erase current• Hardware Write Protection- Protect and unprotect the device from write operation by Write Protect (WP#) Pin• Software Write Protection- The Block Protect (BP2, BP1, BP0) bits allow partial or entire memory to be configured as read-only• High Product Endurance- Guaranteed 200,000 program/erase cycles per single sector- Minimum 20 years data retention• Industrial Standard Pin-out and Package - 8-pin 150mil SOIC - 8-pin TSSOP - 8-contact WSON- Lead-free (Pb-free), halogen-free package • Security function- Build in Safe Guard function and sector unlock function to make the flash Robust (Appendix1&2)GENERAL DESCRIPTIONThe Pm25LD512C are 512Kbit Serial Peripheral Interface (SPI) Flash memories, providing single- or dual-output. The devices are designed to support a 33 MHz clock rate in normal read mode, and 100 MHz in fast read, the fastest in the industry. The devices use a single low voltage power supply, wide operating voltage ranging from 2.7 Volt to 3.6 Volt, to perform read, erase and program operations. The devices can be programmed in standard EPROM programmers.The Pm25LD512C are accessed through a 4-wire SPI Interface consisting of Serial Data Input/Output (SlO), Serial Data Output (SO), Serial Clock (SCK), and Chip Enable (CE#) pins. They comply with all recognized command codes and operations. The dual-output fast read operation provides and effective serial data rate of 200MHz.The devices support page program mode, where 1 to 256 bytes data can be programmed into the memory in one program operation. These devices are divided into uniform 4 KByte sectors or uniform 32 KByte blocks.The Pm25LD512C are manufactured on pFLASH™’s advanced non-volatile technology. The devices are offered in 8-pin SOIC 150mil, 8-contact WSON and 8-pin TSSOP. The devices operate at wide temperatures between -40°C to +105°C.512Kbit Single Operating Voltage Serial Flash Memory With 100 MHz Dual-Output SPI Bus Interface Output SPI Bus InterfacePm25LD512CChingis Technology Corp.2Date: April, 2011, Rev: 0.6PRODUCT ORDERING INFORMATIONPacking Type R = Tape & Reel Blank = TubeEnvironmental AttributeE = Lead-free (Pb-free) and Halogen- free packageTemperature RangeC = Commercial Grade (-40°C to +105°C)Package TypeS = 8-pin SOIC 150mil (8S) K = 8-contact WSON (8K) D = 8-pin TSSOP (8D)pFlash Device Number Pm25LD512CPart Number Operating Frequency (MHz) PackageTemperature RangePm25LD512C-SCE 1008S150mil SOICPm25LD512C-KCE 1008K WSON (Back Side Metal) Pm25LD512C-DCE1008D TSSOPCommercial Grade (-40o C to +105o C)Pm25LD512CChingis Technology Corp.3Date: April, 2011, Rev: 0.6CONNECTION DIAGRAMSHOLD#SCK SISO GNDWP#CE#PIN DESCRIPTIONSSYMBOL TYPE DESCRIPTIONCE#INPUT Chip Enable: CE# low activates the devices internal circuitries for device operation. CE# high deselects the devices and switches intostandby mode to reduce the power consumption. When a device is not selected, data will not be accepted via the serial input pin (Sl), and the serial output pin (SO) will remain in a high impedance state.SCK INPUT Serial Data ClockSIO INPUT/OUTPUT Serial Data Input/Output SO OUTPUTSerial Data Output GND Ground Vcc Device Power Supply WP#INPUT Write Protect: A hardware program/erase protection for all or part of amemory array. When the WP# pin is low, memory array write-protection depends on the setting of BP2, BP1 and BP0 bits in the Status Register. When the WP# is high, the devices are not write-protected.HOLD#INPUT Hold: Pause serial communication by the master device without resettingthe serial sequence.CE# SOHOLD#SCKSIOSIOVcc 8-Pin SOIC8-Contact WSON8-Pin TSSOPPm25LD512CChingis Technology Corp.4Date: April, 2011, Rev: 0.6BLOCK DIAGRAMSIOPm25LD512CChingis Technology Corp.5Date: April, 2011, Rev: 0.6SPI MODES DESCRIPTIONMultiple Pm25LD512C devices can be connected on the SPI serial bus and controlled by a SPI Master, i.e. microcontroller, as shown in Figure 1. The devices support either of two SPI modes:Mode 0 (0, 0) Mode 3 (1, 1)The difference between these two modes is the clock polarity when the SPI master is in Stand-by mode: the serial clock remains at “0” (SCK = 0) for Mode 0 and the clock remains at “1” (SCK = 1) for Mode 3. Please refer to Figure 2. For both modes, the input data is latched on the rising edge of Serial Clock (SCK), and the output data is available from the falling edge of SCK.Figure 1. Connection Diagram among SPI Master and SPI Slaves (Memory Devices)Figure 2. SPI Modes SupportedMSbMSbSCKSCKSOSIOInput mode Mode 0 (0, 0) Mode 3 (1, 1)Pm25LD512CChingis Technology Corp.6Date: April, 2011, Rev: 0.6SYSTEM CONFIGURATIONThe Pm25LD512C devices are designed to interface directly with the synchronous Serial Peripheral Interface (SPI) of the Motorola MC68HCxx series of microcontrollers or any SPI interface-equipped system controllers. The devices have two superset features that can be enabled through specific software instructions and the Configuration Register:Table 1. Block/Sector Addresses of Pm25LD512CMemory Density Block No. Block Size (KBytes) Sector No. SectorSize (KBytes)Address RangeSector 0 4 000000h - 000FFFh Sector 1 4 001000h - 001FFFh: : :Block 0 32 Sector 7 4 007000h - 007FFFh Sector 8 4 008000h - 008FFFh Sector 17 4 009000h - 009FFFh : : :512KbitBlock 1 32Sector 15 4 00F000h - 00FFFFhPm25LD512CChingis Technology Corp.7Date: April, 2011, Rev: 0.6REGISTERS (CONTINUED)STATUS REGISTERRefer to Tables 5 and 6 for Status Register Format and Status Register Bit Definitions.The BP0, BP1, BP2, and SRWD are non-volatile memory cells that can be written by a Write Status Register (WRSR) instruction. The default value of the BP2, BP1, BP0 were set to “0” and SRWD bits was set to “0” at factory. Once a “0” or “1”is written, it will not be changed by device power-up or power-down, and can only be altered by the next WRSR instruction. The Status Register can be read by the Read StatusRegister (RDSR). Refer to Table 10 for Instruction Set.The function of Status Register bits are described as follows:WIP bit : The Write In Progress (WIP) bit is read-only, and can be used to detect the progress or completion of a program or erase operation. When the WIP bit is “0”, the device is ready for a write status register, program or erase operation. When the WIP bit is “1”, the device is busy.WEL bit : The Write Enable Latch (WEL) bit indicates the status of the internal write enable latch. When the WEL is “0”, the write enable latch is disabled, and all write operations, including write status register, page program, sector erase, block and chip erase operations are inhibited. When the WEL bit is “1”, write operations are allowed. The WEL bit is set by a Write Enable (WREN) instruction. Each write register, program and erase instruction must be preceded by a WREN instruction. The WEL bit can be reset by a WriteDisable (WRDI) instruction. It will automatically be the reset after the completion of a write instruction.BP2, BP1, BP0 bits : The Block Protection (BP2, BP1, BP0) bits are used to define the portion of the memory area to be protected. Refer to Tables 7, 8 and 9 for the Block Write Protection bit settings. When a defined combination of BP2, BP1 and BP0 bits are set, the corresponding memory area is protected. Any program or erase operation to that area will be inhibited. Note: a Chip Erase (CHIP_ER) instruction is executedsuccessfully only if all the Block Protection Bits are set as “0”s.SRWD bit : The Status Register Write Disable (SRWD) bit operates in conjunction with the Write Protection (WP#) signal to provide a Hardware Protection Mode. When the SRWD is set to “0”, the Status Register is not write-protected. When the SRWD is set to “1” and the WP# is pulled low (V IL ), the volatile bits of Status Register (SRWD, BP2, BP1, BP0) become read-only, and a WRSR instruction will be ignored. If the SRWD is set to “1” and WP# is pulled high (V IH ), the Status Register can be changed by a WRSR instruction.Table 5. Status Register FormatBit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 SRWD1ReservedBP2BP1 BP0 WEL WIP Default (flash bit) 0 0Pm25LD512CChingis Technology Corp.8Date: April, 2011, Rev: 0.6REGISTERS (CONTINUED)Table 6. Status Register Bit Definition BitNameDefinitionRead- /Write Non-Volatile bit Bit 0 WIP Write In Progress Bit:"0" indicates the device is ready"1" indicates a write cycle is in progress and the device is busy R No Bit 1 WEL Write Enable Latch:"0" indicates the device is not write enabled (default)"1" indicates the device is write enabledR/W No Bit 2 BP0 Bit 3 BP1 Bit 4 BP2 Block Protection Bit: (See Table 7 and Table 8 for details) "0" indicates the specific blocks are not write-protected (default) "1" indicates the specific blocks are write-protected R/W Yes Bits 5 - 6 N/A Reserved: Always "0"sN/A Bit 7 SRWD Status Register Write Disable: (See Table 9 for details)"0" indicates the Status Register is not write-protected (default)"1" indicates the Status Register is write-protectedR/WYesTable 8. Block Write Protect Bits for Pm25LD512CStatus Register Bits Protected Memory AreaBP2 BP1 BP0 512Kbit Not used 0 0 None Not used 0 1 None Not used 1 0 NoneNot used 11All blocks: 000000h - 00FFFFhPm25LD512CChingis Technology Corp.9Date: April, 2011, Rev: 0.6REGISTERS (CONTINUED)PROTECTION MODEThe Pm25LD512C have two types of write-protection mechanisms: hardware and software. These are used to prevent irrelevant operation in a possibly noisy environment and protect the data integrity.HARDWARE WRITE-PROTECTIONThe devices provide two hardware write-protection features:a. When inputting a program, erase or write status register instruction, the number of clock pulse ischecked to determine whether it is a multiple of eight before the executing. Any incomplete instruction command sequence will be ignored.b. The Write Protection (WP#) pin provides ahardware write protection method for BP2, BP1, BP0 and SRWD in the Status Register. Refer to the STATUS REGISTER description.c. Write inhibit is 2.1V, all write sequence will beignored when Vcc drop to 2.1V and lowerSOFTWARE WRITE PROTECTIONThe Pm25LD512C also provides two software write protection features:a. Before the execution of any program, erase or write status register instruction, the Write Enable Latch (WEL) bit must be enabled by executing a Write Enable (WREN) instruction. If the WEL bit is not enabled first, the program, erase or write register instruction will be ignored.b. The Block Protection (BP2, BP1, BP0) bits allow part or the whole memory area to be write-protected. Table 9. Hardware Write Protection on Status RegisterSRWD WP#Status Register 0Low Writable 1 Low Protected 0 High Writable 1HighWritablePm25LD512CChingis Technology Corp.10Date: April, 2011, Rev: 0.6DEVICE OPERATIONThe Pm25LD512C utilize an 8-bit instruction register. Refer to Table 10 Instruction Set for details of theInstructions and Instruction Codes. All instructions,addresses, and data are shifted in with the mostsignificant bit (MSB) first on Serial Data Input (SI). The input data on SI is latched on the rising edge of Serial Clock (SCK) after Chip Enable (CE#) is driven low (V IL ). Every instruction sequence starts with a one-byte instruction code and is followed by address bytes, databytes, or both address bytes and data bytes, depending on the type of instruction. CE# must be driven high (V IH ) after the last bit of the instruction sequence has been shifted in.The timing for each instruction is illustrated in the following operational descriptions.Table 10. Instruction SetInstruction NameHexCodeOperationCommand Cycle Maximum FrequencyRDIDABh Read Manufacturer and Product ID4 Bytes 100 MHz JEDEC ID READ 9Fh Read Manufacturer and Product ID by JEDEC ID Command1 Byte 100 MHz RDMDID 90h Read Manufacturer and Device ID 4 Bytes 100 MHz WREN 06h Write Enable 1 Byte 100 MHz WRDI 04h Write Disable1 Byte 100 MHz RDSR 05h Read Status Register 1 Byte 100 MHz WRSR 01h Write Status Register2 Bytes 100 MHz READ03h Read Data Bytes from Memory at Normal Read Mode 4 Bytes 33 MHz FAST_READ 0Bh Read Data Bytes from Memory at Fast Read Mode 5 Bytes 100 MHz FRDO3Bh Fast Read Dual Output5 Bytes 100 MHz PAGE_ PROG 02h Page Program Data Bytes Into Memory 4 Bytes + 256B 100 MHz SECTOR_ER D7h/20h Sector Erase 4 Bytes 100 MHz BLOCK_ER D8h Block Erase 4 Bytes 100 MHz CHIP_ERC7h/60hChip Erase1 Byte100 MHzHOLD OPERATIONHOLD# is used in conjunction with CE# to select the Pm25LD512C. When the devices are selected and a serial sequence is underway, HOLD# can be used to pause the serial communication with the master device without resetting the serial sequence.To pause, HOLD# is brought low while the SCK signal is low. To resume serial communication, HOLD# is brought high while the SCK signal is low (SCK may still toggle during HOLD). Inputs to Sl will be ignored while SO is in the high impedance state.Pm25LD512CChingis Technology Corp.11Date: April, 2011, Rev: 0.6DEVICE OPERATION (CONTINUED)RDID COMMAND (READ PRODUCT IDENTIFICATION) OPERATIONThe Read Product Identification (RDID) instruction is for reading out the old style of 8-bit Electronic Signature, whose values are shown as table of ID Definitions. This is not same as RDID or JEDEC ID instruction. It’s not recommended to use for newdesign. For new design, please use RDID or JEDEC ID instruction.The RDES instruction code is followed by three dummy bytes, each bit being latched-in on SI during the rising edge of SCK. Then the Device ID is shifted out on SO with the MSB first, each bit been shifted out during the falling edge of SCK. The RDES instruction is ended byCE# goes high. The Device ID outputs repeatedly if continuously send the additional clock cycles on SCK while CE# is at low.Table 11. Product IdentificationProduct Identification Data First Byte 9DhManufacturer ID Second Byte7Fh Device ID: Device ID 1 Device ID 2Pm25LD512C 05h 20hFigure 3. Read Product Identification SequenceSCKCE#SI SOPm25LD512CChingis Technology Corp.12Date: April, 2011, Rev: 0.6DEVICE OPERATION (CONTINUED)JEDEC ID READ COMMAND (READ PRODUCT IDENTIFICATION BY JEDEC ID) OPERATIONThe JEDEC ID READ instruction allows the user to read the manufacturer and product ID of devices. Refer to Table 11 Product Identification for pFlash Manufacturer ID and Device ID. After the JEDEC ID READ command is input, the second Manufacturer ID (7Fh) is shifted out on SO with the MSB first, followed by the first Manufacturer ID (9Dh) and the Device ID (20h), each bit shifted out during the falling edge of SCK. If CE# stays low after the last bit of the Device ID is shifted out, the Manufacturer ID and Device ID will loop until CE# is pulled high.Figure 4. Read Product Identification by JEDEC ID READ SequenceSCKCE#SISOPm25LD512CChingis Technology Corp.13Date: April, 2011, Rev: 0.6DEVICE OPERATION (CONTINUED)RDMDID COMMAND (READ DEVICE MANUFACTURER AND DEVICE ID) OPERATIONThe RDMDID instruction allows the user to read the manufacturer and product ID of devices. Refer to Table 11 Product Identification for pFlash Manufacturer ID and Device ID. The RDMDID command is input, followed by a 24-bit address pointing to an ID table. The table contains the first Manufacturer ID (9Dh) andthe Device ID (20h), and is shifted out on SO with the MSB first, each bit shifted out during the falling edge of SCK. If CE# stays low after the last bit of the Device ID is shifted out, the Manufacturer ID and Device ID will loop until CE# is pulled high.Figure 5. Read Product Identification by RDMDID READ SequencePm25LD512CChingis Technology Corp. 14 Date: April, 2011, Rev: 0.6Pm25LD512CChingis Technology Corp.15Date: April, 2011, Rev: 0.6DEVICE OPERATION (CONTINUED)WRITE ENABLE OPERATIONThe Write Enable (WREN) instruction is used to set the Write Enable Latch (WEL) bit. The WEL bit of the Pm25LD512C is reset to the write –protected state after power-up. The WEL bit must be write enabled before any write operation, including sector, block erase, chip erase, page program and write status register operations. The WEL bit will be reset to the write-protect state automatically upon completion of a write operation. The WREN instruction is required before any above operation is executed.Figure 6. Write Enable SequenceWRDI COMMAND (WRITE DISABLE) OPERATIONThe Write Disable (WRDI) instruction resets the WEL bit and disables all write instructions. The WRDI instruction is not required after the execution of a write instruction, since the WEL bit is automatically reset.Figure 7. Write Disable SequenceSIOSIOPm25LD512CChingis Technology Corp.Date: April, 2011, Rev: 0.6DEVICE OPERATION (CONTINUED)RDSR COMMAND (READ STATUS REGISTER) OPERATIONThe Read Status Register (RDSR) instruction provides access to the Status Register. During the execution of a program, erase or write status register operation, all other instructions will be ignored except the RDSR instruction, which can be used to check the progress or completion of an operation by reading the WIP bit of Status Register.Figure 8. Read Status Register SequenceWRSR COMMAND (WRITE STATUS REGISTER) OPERATIONThe Write Status Register (WRSR) instruction allows the user to enable or disable the block protection and status register write protection features by writing “0”s or “1” s into the volatile BP2, BP1, BP0 and SRWD bits.Figure 9. Write Status Register SequenceDEVICE OPERATION (CONTINUED)SIOSIOPm25LD512CChingis Technology Corp.17Date: April, 2011, Rev: 0.6READ COMMAND (READ DATA) OPERATIONThe Read Data (READ) instruction is used to read memory data of a Pm25LD512C under normal mode running up to 33 MHz.The READ instruction code is transmitted via the Sl line, followed by three address bytes (A23 - A0) of the first memory location to be read. A total of 24 address bits are shifted in, but only A MS (most significantaddress) - A0 are decoded. The remaining bits (A23 – A MS ) are ignored. The first byte addressed can be at any memory location. Upon completion, any data on the Sl will be ignored. Refer to Table 12 for the related Address Key.The first byte data (D7 - D0) addressed is then shifted out on the SO line, MSb first. A single byte of data, or up to the whole memory array, can be read out in one READ instruction. The address is automaticallyincremented after each byte of data is shifted out. The read operation can be terminated at any time by driving CE# high (V IH ) after the data comes out. When the highest address of the devices is reached, the address counter will roll over to the 000000h address, allowing the entire memory to be read in one continuous READ instruction.Table 12. Address KeyAddress Pm25LD512CA N (A MS – A 0) A15 - A0 Don't Care BitsA23 – A16Figure 12. Read Data SequenceSIOPm25LD512CChingis Technology Corp.18Date: April, 2011, Rev: 0.6DEVICE OPERATION (CONTINUED)FAST_READ COMMAND (FAST READ DATA) OPERATIONThe FAST_READ instruction is used to read memory data at up to a 100 MHz clock. The FAST_READ instruction code is followed by three address bytes (A23 - A0) and a dummy byte (8 clocks), transmitted via the SI line, with each bit latched-in during the rising edge of SCK. Then the first data byte addressed is shifted out on the SO line, with each bit shifted out at a maximum frequency f CT , during the falling edge of SCK. The first byte addressed can be at any memory location. The address is automatically incremented after each byte of data is shifted out. When the highest address is reached, the address counter will roll over to the 000000h address, allowing the entire memory to be read with a single FAST_READ instruction. The FAST_READ instruction is terminated by driving CE# high (V IH ).Figure 13. Fast Read Data SequenceSIOSIOPm25LD512CChingis Technology Corp.19Date: April, 2011, Rev: 0.6DEVICE OPERATION (CONTINUED)FRDO COMMAND (FAST READ DUAL OUTPUT) OPERATIONThe FRDO instruction is used to read memory data on two output pins each at up to a 100 MHz clock. The FRDO instruction code is followed by threeaddress bytes (A23 - A0) and a dummy byte (8 clocks), transmitted via the SI line, with each bit latched-in during the rising edge of SCK. Then the first data byte addressed is shifted out on the SO and SIO lines, with each pair of bits shifted out at a maximum frequency f CT , during the falling edge of SCK. The first bit (MSb) is output on SO, while simultaneously the second bit is output on SIO.The first byte addressed can be at any memory location. The address is automatically incremented after each byte of data is shifted out. When the highest address is reached, the address counter will roll over to the 000000h address, allowing the entire memory to be read with a single FRDO instruction. FRDO instruction is terminated by driving CE# high (V IH).Figure 14. Fast Read Dual-Output Sequence123456789101128293031...INSTRUCTION = 0011 1011b (23)22213213 - BYTE ADDRESSCE#SCKSIOSO HIGH IMPEDANCE3233343536373839404142434445464748765432107654321076CE#SCKSIOSOHIGH IMPEDANCEDATA OUT 1DATA OUT 2Pm25LD512CChingis Technology Corp.20Date: April, 2011, Rev: 0.6DEVICE OPERATION (CONTINUED)PAGE_PROG COMMAND (PAGE PROGRAM) OPERATIONThe Page Program (PAGE_PROG) instruction allows up to 256 bytes data to be programmed into memory in a single operation. The destination of the memory to be programmed must be outside the protected memoryarea set by the Block Protection (BP2, BP1, BP0) bits. A PAGE_PROG instruction which attempts to program into a page that is write-protected will be ignored.Before the execution of PAGE_PROG instruction, the Write Enable Latch (WEL) must be enabled through a Write Enable (WREN) instruction.The PAGE_PROG instruction code, three addressbytes and program data (1 to 256 bytes) are input via the Sl line. Program operation will start immediately after the CE# is brought high, otherwise thePAGE_PROG instruction will not be executed. Theinternal control logic automatically handles the programming voltages and timing. During a program operation, all instructions will be ignored except the RDSR instruction. The progress or completion of theprogram operation can be determined by reading the WIP bit in Status Register via a RDSR instruction. If the WIP bit is “1”, the program operation is still in progress. If WIP bit is “0”, the program operation hascompleted.If more than 256 bytes data are sent to a device, theaddress counter rolls over within the same page, the previously latched data are discarded, and the last 256 bytes data are kept to be programmed into the page. The starting byte can be anywhere within the page.When the end of the page is reached, the address will wrap around to the beginning of the same page. If the data to be programmed are less than a full page, the data of all other bytes on the same page will remainunchanged. Note: A program operation can alter “1”s into “0”s, but an erase operation is required to change “0”s back to “1”s. A byte cannot be reprogrammed without firsterasing the whole sector or block.Figure 15. Page Program SequenceSIOPm25LD512CChingis Technology Corp.21Date: April, 2011, Rev: 0.6DEVICE OPERATION (CONTINUED)ERASE OPERATIONThe memory array of the Pm25LD512C is organized into uniform 4 KByte sectors or 32KByte uniform blocks (a block consists of sixteen adjacent sectors).Before a byte can be reprogrammed, the sector or block that contains the byte must be erased (erasing sets bits to “1”). In order to erase the devices, there are three erase instructions available: Sector Erase(SECTOR_ER), Block Erase (BLOCK_ER) and Chip Erase (CHIP_ER). A sector erase operation allows any individual sector to be erased without affecting the data in other sectors. A block erase operation erases any individual block. A chip erase operation erases the whole memory array of a device. A sector erase, block erase or chip erase operation can be executed prior to any programming operation.SECTOR_ER COMMAND (SECTOR ERASE) OPERATIONA SECTOR_ER instruction erases a 4 KByte sector Before the execution of a SECTOR_ER instruction, the Write Enable Latch (WEL) must be set via a Write Enable (WREN) instruction. The WEL bit is reset automatically after the completion of sector an erase operation.A SECTOR_ER instruction is entered, after CE# ispulled low to select the device and stays low during the entire instruction sequence The SECTOR_ERinstruction code, and three address bytes are input via SI. Erase operation will start immediately after CE# is pulled high. The internal control logic automatically handles the erase voltage and timing. Refer to Figure 14 for Sector Erase Sequence.During an erase operation, all instruction will be ignored except the Read Status Register (RDSR) instruction. The progress or completion of the eraseoperation can be determined by reading the WIP bit in the Status Register using a RDSR instruction. If the WIP bit is “1”, the erase operation is still in progress. If the WIP bit is “0”, the erase operation has been completed.BLOCK_ER COMMAND (BLOCK ERASE) OPERATIONA Block Erase (BLOCK_ER) instruction erases a 32 KByte block of the Pm25LD512C. Before the execution of a BLOCK_ER instruction, the Write Enable Latch (WEL) must be set via a Write Enable (WREN)instruction. The WEL is reset automatically after the completion of a block erase operation.The BLOCK_ER instruction code and three address bytes are input via SI. Erase operation will startimmediately after the CE# is pulled high, otherwise the BLOCK_ER instruction will not be executed. The internal control logic automatically handles the erase voltage and timing. Refer to Figure 15 for Block Erase Sequence.CHIP_ER COMMAND (CHIP ERASE) OPERATIONA Chip Erase (CHIP_ER) instruction erases the entire memory array of a Pm25LD512C. Before the execution of CHIP_ER instruction, the Write Enable Latch (WEL) must be set via a Write Enable (WREN) instruction. The WEL is reset automatically after completion of a chip erase operation.The CHIP_ER instruction code is input via the SI. Erase operation will start immediately after CE# ispulled high, otherwise the CHIP_ER instruction will not be executed. The internal control logic automatically handles the erase voltage and timing. Refer to Figure 16 for Chip Erase Sequence.。

STM8L052C6T6;中文规格书,Datasheet资料