OX2551A中文资料

东芝2051-2551维修手册Weiss故障排除手册

感谢您购买东芝多功能彩色数码复印机。本手册描述如何解决使用设备时发生的问题。请把本手册放在触手可及的地方, 并用它来配置一个能最佳使用 e-STUDIO 功能的环境。 公司拥有手册的最终解释权。手册中的不当之处在所难免,敬请谅解。手册中的相关图片请以实际安装后的图片为准。

前言 1

2 前言

目录

第一章

第二章 第三章

前言 ............................................................................................................................................ 1

指出操作设备时您应注意的信息。

此外,本手册也使用以下标记,描述了便于操作本设备的有用信息:

ᦤ冫

描述了有利于设备操作的便捷信息。 表示页面所描述的内容与您当前所做的有关。根据需要,参见这些页面。

选购件

关于可用的选购件,请参阅随机的 《快速开始手册》中的 “选购件”。

屏幕

y 根据设备的使用环境,例如:选购件的安装状态,本手册中的屏幕可能会与实际情况不同。 y 本手册中的屏幕以使用 A/B 型纸张为例。如果使用 LT 型纸张时,则按键的显示或顺序可能会与您的设备不同。

清除卡纸 ................................................................................................................................... 14 确定卡纸位置 ....................................................................................................................... 14 清除卡纸 .............................................................................................................................. 15 自动双面输稿器(下部)中的卡纸 ........................................................................................ 16 自动双面输稿器(上部)中的卡纸 ........................................................................................ 17 纸盒供纸区域中的卡纸 ........................................................................................................ 18 大容量供纸器中的卡纸 ........................................................................................................ 19 供纸工作台中的卡纸 ............................................................................................................ 19 第一纸盒中的卡纸................................................................................................................ 20 第二到第四纸盒中的卡纸 ..................................................................................................... 20 大容量供纸器纸盒中的卡纸 ................................................................................................. 21 旁路供纸托盘中的卡纸 ........................................................................................................ 22 自动双面单元中的卡纸 ........................................................................................................ 23 纸张输送通路中的卡纸 ........................................................................................................ 24 定影单元中的卡纸................................................................................................................ 25 作业分类托盘和交错分页托盘中的卡纸 ............................................................................... 27 中继桥单元中的卡纸 ............................................................................................................ 28 内置式整理器和打孔单元中的卡纸....................................................................................... 28 脊缝式装订整理器和打孔单元中的卡纸 ............................................................................... 31 脊缝式装订整理器的脊缝式装订单元中的卡纸..................................................................... 33 清除由错误的纸张尺寸设置引起的卡纸 ............................................................................... 34

OX2150A-LX中文资料

OCXO SERIES 5100"FEATURESMiniature OCXO in modified CO-15 packageLow current cnsumptionFrequencies up to 155.520 MHz"ELECTRICAL PERFORMANCEPARAMETER OCXO SERIES 5000AT CUT CRYSTAL SC CUT CRYSTAL Supply voltage, nom. 5V ±5% (3.3V Optional)Power dissipation steady state 1.5 Watt Max.Heat up power 3 Watt MaxHeat up time. 3 min MaxFrequency range 1 To 155.520 MHz StandardFrequency Adjustment ±10PPM Min (0 to 5V) ±0.7PPM Min (0 to 5V)±0.05 PPM ±0.1 PPM±0.25 PPM ±0.01 PPM ±0.02 PPM ±0.03 PPMFreq. stability vs. temperatureLX: 0°C to 60°CFZ: -30°C to 70°CD3: -40°C to 85°(Standard, contact factory for different temp ranges and stabilities) Freq. stability vs. supplychanges±0.015 PPM Max for ±5% Change ±0.010 PPM Max for ±5% Change Freq. stability vs. load changes ±0.01 PPM Max for ±5% Change ±0.005 PPM Max for ±5% ChangeLong term stability (Aging) ±4 PPM Max for 10 Years±0.005 PPM/Day Max. ±1 PPM Max for 10 Years ±0.002 PPM/Day Max.Output HCMOS/TTL/Sine 0 to +7dBm (Low voltage CMOS Available)Harmonics -30dBc(SineOutput) Spurious -75dBc(SineOutput) Duty cycle 40/60% to 60/40%(HCMOS)Rise / fall time 10nS Max. (HCMOS,10%~90%Vout, 90%~10%Vout)Short term Stability 1 E-10 /Sec 5 E-11 /SecPhase Noise Offset Phase Noise10Hz -90 dBc/Hz100Hz -125 dBc/Hz1000Hz -135 dBc/Hz10000Hz -150 dBc/Hz Offset Phase Noise 10Hz -110 dBc/Hz 100Hz -125 dBc/Hz 1000Hz -140 dBc/Hz 10000Hz -150 dBc/Hz" HOW TO ORDER (PART NUMBER)Prefix Output Type Cut Type Series Revision Temperature Range Stability Frequency OX2:HCMOS 4:LVCMOS 6:SINE0:AT (No Vcontrol ) 1: SC (No Vcontrol ) 4: AT (Elect Vcontrol) 5: SC (Elect Vcontrol)50:5000AFirst letter Lowest Temperature,Second letter Highest Temperature:From A=-55°C to Z=+70°C, Then: 1=+75°C, 2=+80°C, 3=+85°C… in 5°C steps Example: LZ: +0°C to +70°C LX: +0°C to +60°C FZ: -30°C to +70°C D3: -40°C to +85°CValue x 10E-2 in PPMExample 28= 0.28PP M 10= 0.1PPMIn MHZ。

2-PXA255开发系统

和工业控制计算机相比,嵌入式微处理器具有体积小、重量轻 、成本低、可靠性高的优点。目前主要的嵌入式处理器类型有 Am186/88、386EX、SC-400、Power PC、68000、MIPS、ARM/ StrongARM系列等

(4)嵌入式片上系统(System On Chip)

• • • • SoC 就是System on Chip ,SoC嵌入式系统微处理器就是一种 电路系统。 一般说来, SoC称为系统级芯片,也有称片上系统,意指它是一个产 品,是一个有专用目标的集成电路,其中包含完整系统并有嵌入软 件的全部内容。 国内外学术界一般倾向将SoC定义为将微处理器、模拟IP核、数 字IP核和存储器(或片外存储控制接口)集成在单一芯片上,它通常 是客户定制的,或是面向特定用途的标准产品。 它结合了许多功能区块,将功能做在一个芯片上,像是ARM RISC、MIPS RISC、DSP或是其他的微处理器核心,加上通信 的接口单元,像是万用串行端口(USB)、TCP/IP通信单元、 GPRS通信接口、GSM通信接口、IEEE1394、蓝牙模块接口等 等,这些单元以往都是依照各单元的功能做成一个个独立的处理 芯片。

高 速 缓 存 控 制 器

数据

CACHE 主存

CPU

地址 数据

系统连接的枢纽:总线和总线桥

CPU 低速设备

高速总线

桥

低速总线

存储器

高速设备

数据

高速设备

存储器系统

RAM:随机存取存储器(Random Access Memory )

SRAM:静态随机存储器(static RAM)

DRAM:动态随机存储器(Dynamic RAM) ROM:只读存储器(Read Only Memory )

NPort W2150A W2250A 系列无线串行设备服务器说明文档说明书

NPort W2150A/W2250A系列1和2埠RS-232/422/485IEEE802.11a/b/g無線串列設備伺服器特色與優點•可將任何串列裝置連接至IEEE802.11a/b/g網路•透過內建乙太網路或WLAN執行Web-based設定•強化的區域網路、串列和電力突波保護•利用HTTPS和SSH強化遠端設定•透過WEP、WPA和WPA2保護存取資料的安全性•快速漫遊,可在存取點之間快速自動切換•具備離線埠緩衝和串列資料記錄功能•雙電源輸入(1螺旋式電源接頭、1端子台)認證簡介NPort®W2150A和W2250A是將串列和乙太網路裝置(例如PLC、儀表和感測器)連接到無線LAN的理想選擇。

您的通訊軟體將能夠透過無線LAN隨處存取串列裝置。

此外,無線裝置伺服器需要較少纜線,相當適合不便佈線的應用。

在基礎架構模式或Ad-Hoc模式中,NPort®W2150A和NPort®W2250A可以連接辦公室和工廠的Wi-Fi網路,以便使用者在多個AP(存取點)之間移動或漫遊,並且對於經常在不同的地點之間移動的裝置提供絕佳的解決方案。

規格Ethernet Interface10/100BaseT(X)Ports(RJ45connector)1Magnetic Isolation Protection 1.5kV(built-in)Standards IEEE802.3for10BaseTIEEE802.3u for100BaseT(X)Ethernet Software FeaturesConfiguration Options Web Console(HTTP/HTTPS),Windows UtilityManagement DHCP Option82,HTTP,IPv4,SMTP,SNMPv1/v2c/v3,Syslog,Telnet,Web Console Windows Real COM Drivers Windows95/98/ME/NT/2000,Windows XP/2003/Vista/2008/7/8/8.1/10(x86/x64),Windows2008R2/2012/2012R2/2016/2019(x64),Windows Embedded CE5.0/6.0,Windows XP EmbeddedLinux Real TTY Drivers Kernel versions:2.4.x,2.6.x,3.x,4.x,and5.xFixed TTY Drivers SCO UNIX,SCO OpenServer,UnixWare7,QNX4.25,QNX6,Solaris10,FreeBSD,AIX5.x,HP-UX11i,Mac OS XAndroid API Android3.1.x and laterMIB Device Settings MIB,RFC1213,RFC1317Security HTTPS/SSL,User Authentication Management:local database,RADIUS,SecureProtocols:HTTPS(TLSv1.2),SSH,SNMPv3,Cryptography:HMAC,SHA-1,SHA-256,SHA-384,RSA-1024,AES-128,AES-256Time Management NTP Client,SNTP ClientWLAN InterfaceWLAN Standards802.11a/b/g/nReceiver Sensitivity for802.11a(measured at5.680 GHz)Typ.-91@6Mbps Typ.-74@54MbpsReceiver Sensitivity for802.11b(measured at2.437 GHz)Typ.-92dBm@1Mbps Typ.-84dBm@11MbpsReceiver Sensitivity for802.11g(measured at2.437 GHz)Typ.-91dBm@6Mbps Typ.-73dBm@54MbpsReceiver Sensitivity for802.11n(2.4GHz;measured at2.437GHz)Typ.-89dBm@6.5Mbps(20MHz) Typ.-71dBm@72.2Mbps(20MHz)Receiver Sensitivity for802.11n(5GHz;measured at 5.680GHz)Typ.-89dBm@6.5Mbps(20MHz) Typ.-71dBm@72.2Mbps(20MHz) Typ.-85dBm@13.5Mbps(40MHz) Typ.-67dBm@150Mbps(40MHz)Modulation Type DSSSOFDMTransmission Distance Up to100meters(in open areas) Transmission Rate802.11a/g:54Mbps802.11b:11Mbps802.11n:6.5to150Mbps Transmitter Power for802.11b16±1.5dBm@1Mbps16±1.5dBm@11Mbps Transmitter Power for802.11g16±1.5dBm@6Mbps14±1.5dBm@54Mbps Transmitter Power for802.11a15±1.5dBm@6Mbps14±1.5dBm@54Mbps Transmitter Power for802.11n(2.4GHz)16dBm@1.5Mbps(6.5MHz)12dBm@1.5Mbps(72.2MHz) Transmitter Power for802.11n(5GHz)15dBm@1.5Mbps(6.5MHz)12dBm@1.5Mbps(150MHz) Frequency Band for CN(20MHz operating channels) 2.412to2.472GHz(13channels)5.180to5.240GHz(4channels)5.260to5.320GHz(4channels)15.745to5.825GHz(5channels) Frequency Band for EU(20MHz operating channels) 2.412to2.472GHz(13channels)5.180to5.240GHz(4channels)5.260to5.320GHz(4channels)15.500to5.700GHz(11channels)1 Frequency Band for JP(20MHz operating channels) 2.412to2.484GHz(14channels)5.180to5.240GHz(4channels)5.260to5.320GHz(4channels)15.500to5.700GHz(11channels)1 Frequency Band for US(20MHz operating channels) 2.412to2.462GHz(11channels)5.180to5.240GHz(4channels)5.260to5.320GHz(4channels)25.500to5.700GHz(11channels)25.745to5.825GHz(5channels)Wireless Security WEP encryption(64-bit and128-bit)WPA/WPA2-Enterprise(IEEE802.1X/RADIUS,TKIP,AES)WPA/WPA2-PersonalWLAN Modes Ad-hoc Mode,Infrastructure modeSerial InterfaceConnector DB9maleNo.of Ports NPort W2150A/W2150A-T:1NPort W2250A/W2250A-T:2Serial Standards RS-232,RS-422,RS-485Operation Modes Real COM mode,TCP Server mode,TCP Client mode,UDP mode,RFC2217mode,PairConnection mode,Ethernet Modem mode,DisabledBaudrate50bps to921.6kbpsData Bits5,6,7,8Stop Bits1,1.5,2Parity None,Even,Odd,Space,MarkFlow Control None,RTS/CTS,XON/XOFFRS-485Data Direction Control ADDC®(automatic data direction control)Pull High/Low Resistor for RS-4851kilo-ohm,150kilo-ohmsTerminator for RS-485120ohmsSurge1kVPhysical CharacteristicsHousing MetalInstallation Desktop,DIN-rail mounting(with optional kit),Wall mountingDimensions(with ears,without antenna)77x111x26mm(3.03x4.37x1.02in)Dimensions(without ears or antenna)100x111x26mm(3.94x4.37x1.02in)Weight NPort W2150A/W2150A-T:547g(1.21lb)NPort W2250A/W2250A-T:557g(1.23lb)Antenna Length109.79mm(4.32in)Environmental LimitsOperating Temperature Standard Models:0to55°C(32to131°F)Wide Temp.Models:-40to75°C(-40to167°F)Storage Temperature(package included)-40to75°C(-40to167°F)Ambient Relative Humidity5to95%(non-condensing)Power ParametersInput Current NPort W2150A/W2150A-T:179mA@12VDCNPort W2250A/W2250A-T:200mA@12VDCInput Voltage12to48VDCStandards and CertificationsEMC EN55032/24EMI CISPR32,FCC Part15B Class AEMS IEC61000-4-2ESD:Contact:4kV;Air:8kVIEC61000-4-3RS:80MHz to1GHz:3V/mIEC61000-4-4EFT:Power:2kV;Signal:2kVIEC61000-4-5Surge:Power:2kV;Signal:1kVIEC61000-4-6CS:150kHz to80MHz:3V/m;Signal:3V/mIEC61000-4-8PFMFIEC61000-4-11Radio Frequency CE(ETSI EN301893,ETSI EN300328,ETSI EN301489-17,ETSI EN301489-1),ARIBRCR STD-33,ARIB STD-66ReliabilityAlert Tools RTC(real-time clock)Automatic Reboot Trigger Built-in WDTMTBFTime NPort W2150A/W2150A-T:383,187hrsNPort W2250A/W2250A-T:363,327hrsStandards Telcordia(Bellcore)Standard TR/SRWarrantyWarranty Period5yearsDetails See /tw/warrantyPackage ContentsDevice1x NPort W2150A/W2250A Series device serverPower Supply1x power adapter,suitable for your region(standard temp.models only)Antenna1x2.4/5GHz antennaDocumentation1x quick installation guide1x warranty card尺寸訂購資訊Model Name No.of serial portsWLAN Channels Input Current Operating Temp.Power Adapter inBox Notes NPort W2150A-CN 1China bands 179mA @12VDC 0to 55°C Yes (CN plug)—NPort W2150A-EU 1Europe bands 179mA @12VDC 0to 55°C Yes (EU/UK/AUplug)—NPort W2150A-EU/KC 1Europe bands 179mA @12VDC 0to 55°C Yes (EU plug)KC certificateNPort W2150A-JP 1Japan bands 179mA @12VDC 0to 55°C Yes (JP plug)—NPort W2150A-US 1US bands 179mA @12VDC 0to 55°C Yes (US plug)—NPort W2150A-T-CN 1China bands 179mA @12VDC -40to 75°C No —NPort W2150A-T-EU 1Europe bands 179mA @12VDC -40to 75°C No —NPort W2150A-T-JP 1Japan bands 179mA @12VDC -40to 75°C No —NPort W2150A-T-US 1US bands 179mA @12VDC -40to 75°C No —NPort W2250A-CN 2China bands 200mA @12VDC 0to 55°C Yes (CN plug)—NPort W2250A-EU 2Europe bands 200mA @12VDC 0to 55°C Yes (EU/UK/AUplug)—NPort W2250A-EU/KC 2Europe bands 200mA @12VDC 0to 55°C Yes (EU plug)KC certificateNPort W2250A-JP 2Japan bands 200mA @12VDC 0to 55°C Yes (JP plug)—NPort W2250A-US 2US bands 200mA @12VDC 0to 55°C Yes (US plug)—NPort W2250A-T-CN 2China bands 200mA @12VDC -40to 75°C No —NPort W2250A-T-EU 2Europe bands 200mA @12VDC -40to 75°C No —NPort W2250A-T-JP 2Japan bands 200mA @12VDC -40to 75°C No —NPort W2250A-T-US2US bands200mA @12VDC-40to 75°CNo—配件(選購)AntennasANT-WDB-ARM-02 2.4/5GHz,omni-directional rubber duck antenna,2dBi,RP-SMA(male)CablesCBL-F9M9-150DB9female to DB9male serial cable,1.5mCBL-F9M9-20DB9female to DB9male serial cable,20cmConnectorsADP-RJ458P-DB9F DB9female to RJ45connectorMini DB9F-to-TB DB9female to terminal block connectorDIN-Rail Mounting KitsDK35A DIN-rail mounting kit,35mmPower AdaptersPWR-12050-WPAU-S1Locking barrel plug,12VDC,0.5A,100-240VAC,Australia(AU)plug,0to40°C operating temperature PWR-12050-WPCN-S1Locking barrel plug,12VDC,0.5A,100to240VAC,China(CN)plug,0to40°C operating temperature PWR-12050-WPEU-S1Locking barrel plug,12VDC,0.5A,100-240VAC,Continental Europe(EU)plug,0to40°C operatingtemperaturePWR-12050-WPUK-S1Locking barrel plug,12VDC,0.5A,100-240VAC,United Kingdom(UK)plug,0to40°C operatingtemperaturePWR-12050-WPUSJP-S1Locking barrel plug,12VDC,0.5A,100-240VAC,United States/Japan(US/JP)plug,0to40°C operatingtemperaturePWR-12150-AU-SA-T Locking barrel plug,12VDC,1.5A,100-240VAC,Australia(AU)plug,-40to75°C operating temperatureApplicable Models:NPort W2150A-TNPort W2250A-TPWR-12150-CN-SA-T Wide-temperature(-40to75°C)locking barrel plug,12VDC,1.5A,100to240VAC,China(CN)plugApplicable Models:NPort W2150A-TNPort W2250A-TPWR-12150-EU-SA-T Locking barrel plug,12VDC,1.5A,100-240VAC,Continental Europe(EU)plug,-40to75°C operatingtemperatureApplicable Models:NPort W2150A-TNPort W2250A-TPWR-12150-UK-SA-T Locking barrel plug,12VDC,1.5A,100-240VAC,United Kingdom(UK)plug,-40to75°C operatingtemperatureApplicable Models:NPort W2150A-TNPort W2250A-TPWR-12150-USJP-SA-T Locking barrel plug,12VDC1.5A,100-240VAC,United States/Japan(US/JP)plug,-40to75°Coperating temperatureApplicable Models:NPort W2150A-TNPort W2250A-TPower CordsCBL-PJ21NOPEN-BK-30Locking barrel plug to bare-wire cable©Moxa Inc.版權所有.2021年1月25日更新。

25AA256_07中文资料

• Block Write Protection:

- Protect none, 1/4, 1/2 or all of array

• Built-In Write Protection:

- Power-on/off data protection circuitry

- Write enable latch

-0.3

— 0.3 VCC V

-0.3

— 0.2 VCC V

D004 VOL D005 VOL

Low-level output voltage

—

—

0.4

V

—

—

0.2

V

D006 VOH

High-level output

VCC -0.5 —

—

V

voltage

D007 ILI

Input leakage current —

VCC = 5.5V; FCLK = 10.0 MHz; SO = Open VCC = 2.5V; FCLK = 5.0 MHz; SO = Open VCC = 5.5V VCC = 2.5V CS = VCC = 5.5V, Inputs tied to VCC or VSS, 125°C CS = VCC = 5.5V, Inputs tied to VCC or VSS, 85°C

DS21822F-page 2

© 2007 Microchip Technology Inc.

元器件交易网

25AA256/25LC256

TABLE 1-2: AC CHARACTERISTICS

AC CHARACTERISTICS

Industrial (I): TA = -40°C to +85°C Automotive (E): TA = -40°C to +125°C

OXuPCI954_DS

External—Free ReleaseOxford Semiconductor, Inc.1900 McCarthy Boulevard, Suite 210 © Oxford Semiconductor, Inc. 2007F EATURES• Four 16C950 High performance UART channels • 8-bit Pass-through Local Bus (PCI Bridge )• IEEE1284 Compliant SPP/EPP/ECP parallel port (with external transceiver)• Efficient 32-bit, 33 MHz, multi-function target-only PCIcontroller, fully compliant to PCI Local Bus Specification 3.0 and PCI Power Management Specification 1.1 • Software compatible with OXmPCI954• UARTs fully software compatible with 16C550-type devices • UART operation up to 60 MHz via external clock source. Up to 20 MHz with the crystal oscillator• Baud rates up to 60 Mbps in external 1x clock mode and 15 Mbps in asynchronous mode• 128-byte deep FIFO per transmitter and receiver • Flexible clock prescaler, from 1 to 31.875• Automated in-band flow control using programmable Xon/Xoff in both directions•Automated out-of-band flow control using CTS#/RTS# and/or DSR#/DTR#• Programmable RS485 turnaround delay• Arbitrary trigger levels for receiver and transmitter FIFO interrupts and automatic in-band and out-of-band flow control• Infra-red (IrDA) receiver and transmitter operation • 9-bit data framing, as well as 5, 6, 7, and 8 bits • Detection of bad data in the receiver FIFO• Global Interrupt Status and readable FIFO levels to facilitate implementation of efficient device drivers.• Local registers to provide status/control of device functions • 11 multi-purpose I/O pins, which can be configured as input interrupt pins or ‘wake-up’• Auto-detection of a wide range of optional MICROWIRE TM compatible EEPROMs, to re-configure device parameters • Function access , to pre-configure each function prior to handover to generic device drivers • Operation via I/O or memory mapping• 3.3 V or 5 V operation (PCI Universal Voltage)• Extended operating temperature range: -40° C to 85° C •176-pin LQFP packageD ESCRIPTIONThe OXuPCI954 is a single chip solution for PCI-based serial and parallel expansion add-in cards. It is a dual function PCI device, where function 0 offers four ultra-high performance OX16C950 UARTs, and function 1 is configurable either as an 8-bit local bus or a bi-directional parallel port.Each UART channel in the OXuPCI954 is the fastest available PC-compatible UART, offering data rates up to 15 Mbps and 128-byte deep transmitter and receiver FIFOs. The deep FIFOs reduce CPU overhead and allow utilization of higher data rates. Each UART channel is software compatible with the widely used industry-standard 16C550 devices (and compatibles), as well as the OX16C95x family of high performance UARTs. In addition to increased performance and FIFO size, the UARTs also provide the full set of OX16C95x enhanced features including automated in-band flow control, readable FIFO levels, etc.To enhance device driver efficiency and reduce interrupt latency, internal UARTs have multi-port features such as shadowed FIFO fill levels, a global interrupt source register and Good-Data Status, readable in four adjacent DWORD registers visible to logical functions in I/O space and memory space.Expansion of serial ports beyond four channels is possible using the 8-bit pass-through Local Bus function. This provides a general address/data bus and interrupt capability to a discrete UART part, such as the Oxford SemiconductorOX16C954. Other controllers could be used to provide capabilities beyond additional UART ports. The addressable space provided by the Local Bus can be increased up to 256 bytes, and divided into four chip-select regions. This flexible expansion scheme caters for cards with up to 20 serial ports using external 16C950, 16C954 or compatible devices, or composite applications such as combined serial and parallel port expansion cards. Serial port cards with up to 20 ports (or with 4 serial ports and a parallel port) can be designed without redefining any device or timing parameters.The parallel port is an IEEE 1284 compliant SPP/EPP/ECP parallel port that fully supports the existing Centronics interface. The parallel port can be enabled in place of the local bus. A n external bus transceiver is required for 5V parallel port operation if device is 3.3V sourced.For full flexibility, all the default configuration register values can be overwritten using an optional M ICROWIRE compatibleserial EEPROM. This EEPROM can also be used to provide function access to pre-configure devices on the local bus/parallel port, prior to any PCI configuration accesses and before control is handed to (generic) device drivers.The OXuPCI954 can be used to replace the OXmPCI954 in a PCI application where quad UARTs and a local bus/parallel port functionality are required.OXuPCI954 DATA SHEETIntegrated High Performance Quad UARTs,8-bit Local Bus/Parallel Port,3.3 V and 5 V (Universal Voltage) PCI Interface .Improvements of the OXuPCI954 over Discrete SolutionsHigher degree of integrationThe OXuPCI954 device offers four internal 16C950 high-performance UARTs and an 8-bit local bus or abi-directional parallel port.Multi-function deviceThe OXuPCI954 is a multi-function device to enable users to load individual device drivers for the internal serial ports, drivers for the peripheral devices connected to the local bus or drivers for the internal parallel port.Quad Internal OX16C950 UARTsThe OXuPCI954 device contains four ultra-high performance UARTs, which can increase driver efficiency by using features such as the 128-byte deep transmitter and receiver FIFOs, flexible clock options, automatic flow control, programmable interrupt and flow control trigger levels and readable FIFO levels. Data rates are up to 60 Mbps.Improved access timingAccess to the internal UARTs require zero or one PCI wait state. A PCI read transaction from an internal UART can complete within five PCI clock cycles and a write transaction to an internal UART can complete within four PCI clock cycles. Reduces interrupt latencyThe OXuPCI954 device offers shadowed FIFO levels and Interrupt status registers on the internal UARTs and the MIO pins. This reduces the device driver interrupt latency. Power managementThe OXuPCI954 device complies with the PCI Power Management Specification 1.1 and the Microsoft Communications Device-class Power Management Specification 2.0 (2000). Both functions offer the extended capabilities for Power Management. This achieves significant power savings by enabling device drivers to power down the PCI functions. For function 0, this is through switching off the channel clock, in power state D3. Wake-up (PME# generation) can be requested by either functions. For function 0, this is via the RI# inputs of the UARTs in the power-state D3 or any modem line and SIN inputs of the UARTs in power-state D2. For function 1, this is via the MIO[2] input.Optional EEPROMThe OXuPCI954 device can be reconfigured from an external EEPROM to the end-user’s requirements. However, this is not required in many applications as the default values are sufficient for typical applications. An overrun detection mechanism built into the EEPROM controller prevents the PCI system from ‘hanging’ due to an incorrectly programmed EEPROM.R EVISION H ISTORYRevision Modification May 2007 First publication.Sep 2007 Feature revision, including removal of D3coldT ABLE OF C ONTENTS1OXuPCI954 Device Modes (6)2Block Diagram (7)3Pin Information—176-Pin LQFP (8)3.1Mode ‘0’ Quad UARTs + 8-bit Local Bus (8)3.1.1Mode ‘1’ : Quad UARTs + Parallel Port (9)3.2Pin Descriptions (10)4Configuration and Operation (16)5PCI Target Controller (17)5.1Operation (17)5.2Configuration Space (17)5.2.1PCI Configuration Space Register Map (18)5.3Accessing Logical Functions (20)5.3.1PCI Access to Internal UARTs (21)5.3.2PCI Access to 8-bit Local Bus (22)5.3.3PCI Access to Parallel Port (22)5.4Accessing Local Configuration Registers (23)5.4.1Local Configuration and Control Register ‘LCC’ (Offset 0x00) (23)5.4.2Multi-purpose I/O Configuration Register ‘MIC’ (Offset 0x04) (24)5.4.3Local Bus Timing Parameter Register 1 ‘LT1’ (Offset 0x08) (26)5.4.4Local Bus Timing Parameter Register 2 ‘LT2’ (Offset 0x0C) (27)5.4.5UART Receiver FIFO Levels ‘URL’ (Offset 0x10) (28)5.4.6UART Transmitter FIFO Levels ‘UTL’ (Offset 0x14) (29)5.4.7UART Interrupt Source Register ‘UIS’ (Offset 0x18) (29)5.4.8Global Interrupt Status and Control Register ‘GIS’ (Offset 0x1C) (30)5.5PCI Interrupts (31)5.6Power Management (32)5.6.1Power Management of Function 0 (32)5.6.2Power Management of Function 1 (33)5.6.3Universal Voltage (34)5.7Unique Bar Option – for Function 0 (35)6Internal OX16C950 UARTs (36)6.1Operation – Mode Selection (36)6.1.1450 Mode (36)6.1.2550 Mode (36)6.1.3Extended 550 Mode (36)6.1.4750 Mode (36)6.1.5650 Mode (36)6.1.6950 Mode (37)6.2Register Description Tables (38)6.3UART Reset Configuration (41)6.3.1Hardware Reset (41)6.3.2Software Reset (41)6.4Transmitter and Receiver FIFOs (42)6.4.1FIFO Control Register ‘FCR’ (42)6.5Line Control and Status (43)6.5.1False Start Bit Detection (43)6.5.2Line Control Register ‘LCR’ (43)6.5.3Line Status Register ‘LSR’ (44)6.6Interrupts and Sleep Mode (45)6.6.1Interrupt Enable Register ‘IER’ (45)6.6.2Interrupt Status Register ‘ISR’ (46)6.6.3Interrupt Description (46)6.6.4Sleep Mode (47)6.7Modem Interface (47)6.7.1Modem Control Register ‘MCR’ (47)6.7.2Modem Status Register ‘MSR’ (48)6.8Other Standard Registers (48)6.8.1Divisor Latch Registers ‘DLL and DLM’ (48)6.8.2Scratch Pad Register ‘SPR’ (48)6.9Automatic Flow Control (49)6.9.1Enhanced Features Register ‘EFR’ (49)6.9.2Special Character Detection (50)6.9.3Automatic In-band Flow Control (50)6.9.4Automatic Out-of-band Flow Control (50)6.10Baud Rate Generation (51)6.10.1General Operation (51)6.10.2Clock Prescaler Register ‘CPR’ (51)6.10.3Times Clock Register ‘TCR’ (51)6.10.4External 1x Clock Mode (53)6.10.5Crystal Oscillator Circuit (53)6.11Additional Features (54)6.11.1Additional Status Register ‘ASR’ (54)6.11.2FIFO Fill Levels ‘TFL and RFL’ (54)6.11.3Additional Control Register ‘ACR’ (54)6.11.4Transmitter Trigger Level ‘TTL’ (55)6.11.5Receiver Interrupt. Trigger Level ‘RTL’ (55)6.11.6Flow Control Levels ‘FCL’ and ‘FCH’ (56)6.11.7Device Identification Registers (56)6.11.8Clock Select Register ‘CKS’ (56)6.11.9Nine-bit Mode Register ‘NMR’ (57)6.11.10Modem Disable Mask ‘MDM’ (57)6.11.11Readable FCR ‘RFC’ (58)6.11.12Good-data Status Register ‘GDS’ (58)6.11.13Port Index Register ‘PIX’ (58)6.11.14Clock Alteration Register ‘CKA’ (58)6.11.15RS485 Delay Enable ‘RS485_DLYEN’ (58)6.11.16RS485 Delay Count ‘RS485_DLYCNT’ (59)7Local bus (60)7.1Overview (60)7.2Operation (60)7.3Configuration and Programming (61)8Bidirectional Parallel Port (62)8.1Operation and Mode Selection (62)8.1.1SPP Mode (62)8.1.2PS2 Mode (62)8.1.3EPP Mode (62)8.1.4ECP Mode (62)8.2Parallel Port Interrupt (63)8.3Register Description (63)8.3.1Parallel Port Data Register ‘PDR’ (64)8.3.2ECP FIFO Address / RLE (64)8.3.3Device Status Register ‘DSR’ (64)8.3.4Device Control Register ‘DCR’ (64)8.3.5EPP Address register ‘EPPA’ (65)8.3.6EPP Data Registers ‘EPPD1-4’ (65)8.3.7ECP Data FIFO (65)8.3.8Test FIFO (65)8.3.9Configuration A Register (65)8.3.10Configuration B Register (65)8.3.11Extended Control Register ‘ECR’ (65)9Serial EEPROM (66)9.1Specification (66)9.1.1Zone 0: Header (67)9.1.2Zone 1: Local Configuration Registers (68)9.1.3Zone 2: Identification Registers (69)9.1.4Zone 3: PCI Configuration Registers (69)9.1.5Zone 4: Power Management DATA (and DATA_SCALE Zone) (70)9.1.6Zone 5: Function Access (70)10Operating Conditions (72)10.1DC Electrical Characteristics (72)11AC Electrical Characteristics (76)11.1PCI Bus Timings (76)11.2Local Bus (77)11.3Serial Ports (79)12Timing Waveforms (80)13Package Information (95)13.1176-Pin LQFP (95)14Ordering Information (96)1OX U PCI954D EVICE M ODESThe OXuPCI954 supports two modes of operation. These modes are summarized in the following table.Device Mode Mode Pin Selection Functionality0 MODE = 0 Function 0 : Quad UARTs Function 1 : 8-bit local bus1 MODE = 1 Function 0 : Quad UARTs Function 1 : Parallel Port* The OXuPCI954 is not pin-compatible with the OX16PCI954 or the OXmPCI954, but is the same in all other aspects.2B LOCK D IAGRAMFIFOSELMODEAD[31:0]C/BE[3:0]#PCI_CLKFRAME#DEVSEL#IRDY#TRDY#STOP#PARPERR#IDSELRST#INTA#PME#XTLIXTLOUART_Clk_Out Local_Bus ClkEE_DIEE_CSEE_CKEE_DOSOUT[3:0]SIN[3:0]RTS[3:0]DTR[3:0]CTS[3:0]DSR[3:0]DCD[3:0]RI[3:0]MIO[10:0]PD[7:0]ACK#PEBUSYSLCTERR#SLIN#INIT#AFD#STB#LBA[7:0]LBD[7:0]LBCS[3:0]LBWR#LBRD#LBRSTDATA_DIR OXuPCI954 Block DiagramOSCDIS XTLSEL3P IN I NFORMATION—176-P IN LQFP 3.1Mode ‘0’ Quad UARTs + 8-bit Local Bus7 NC. Do not connect these pins:23, 40, 41, 136, 137, 138, 1393.1.1Mode ‘1’ : Quad UARTs + Parallel Port15 NC. Do not connect these pins:23, 40, 41, 74, 112, 113, 114, 115, 116, 117, 124, 136, 137, 138, 1393.2Pin DescriptionsFor the actual pinouts of the OXuPCI954 device (for the various modes), refer to the Section 3, Pin Information. The I/O direction key table is on page 15.PCI Interface – All ModesPin Dir1Name Description149, 150, 151, 154, 155,157, 158, 160, 164, 165,167, 168, 169, 170, 171,174, 13, 14, 15, 17, 18, 20,24, 25, 27, 28, 31, 32, 33,34, 35, 39P_I/O AD[31:0] Multiplexed PCI Address/Data bus161, 175, 12, 26 P_I C/BE[3:0]# PCI Command/Byte enable146 P_I CLK PCI system clock (33MHz)176 P_IFRAME#CycleFrame5 P_ODEVSEL#DeviceSelect1 P_IIRDY#Initiatorready2 P_OTRDY#Targetready6 P_O STOP# Target Stop request10 P_I/OPAR Parity8 P_OSERR#Systemerror7 P_I/OPERR#Parityerror163 P_I IDSEL Initialization device select144 P_I RST# PCI system reset142 P_ODINTA# PCIinterrupt147 P_OD PME# Power management eventSerial Port Pins – All ModesPin Dir1Name Description50 I FIFOSEL FIFO select. For backward compatibility with 16C550,16C650 and 16C750 devices the UARTs’ FIFO depth is 16when FIFOSEL is low. The FIFO size is increased to 128when FIFOSEL is high. The unlatched state of this pin isreadable by software. The FIFO size may also be set to 128by setting FCR[5] when LCR[7] is set, or by putting thedevice into Enhanced mode.82, 81, 63, 62 O(h)SOUT[3:0]IrDA_Out[3:0] These four pins are present in all modes but they can serve one of two functions, as follows:UART serial data outputs.UART IrDA data output when MCR[6] of the corresponding channel is set in Enhanced mode.91, 73, 72, 55I(h) I(h) SIN[3:0]IrDA_In[3:0]These four pins are present in all modes but they can serveone of two functions, as follows:UART serial data inputs.UART IrDA data input when IrDA mode is enabled (seeabove).Serial Port Pins – All ModesPin Dir1Name Description89, 76, 71, 57 I(h) DCD[3:0]# Active-low modem data-carrier-detect input 84, 79, 65, 60O(h) O(h) O(h) DTR[3:0]#485_En[3:0]Tx_Clk_Out[3:0]These four pins are present in all modes but they can serveone of three functions, as follows:Active-low modem data-terminal-ready output. If automatedDTR# flow control is enabled, the DTR# pin is asserted anddeasserted if the receiver FIFO reaches or falls below theprogrammed thresholds, respectively.In RS485 half-duplex mode, the DTR# pin may beprogrammed to reflect the state of the transmitter empty bitto automatically control the direction of the RS485transceiver buffer (see register ACR[4:3]).Transmitter 1x clock (baud rate generator output). Forisochronous applications, the 1x (or Nx) transmitter clockmay be asserted on the DTR# pins (see register CKS[5:4]).83, 80, 64, 61 O(h) RTS[3:0]# Active-low modem request-to-send output. If automatedRTS# flow control is enabled, the RTS# pin is deassertedand reasserted whenever the receiver FIFO reaches or fallsbelow the programmed thresholds, respectively.85, 78, 67, 59 I(h) CTS[3:0]# Active-low modem clear-to-send input. If automated CTS#flow control is enabled, upon deassertion of the CTS# pin,the transmitter will complete the current character and enterthe idle mode until the CTS# pin is reasserted. Note: any in-band flow control characters are transmitted regardless ofthe state of the CTS# pin.86, 77, 66, 58I(h) I(h) DSR[3:0]#Rx_Clk_In[3:0]These four pins are present in all modes but they can serveone of two functions, as follows:Active-low modem data-set-ready input. If automated DSR#flow control is enabled, upon deassertion of the DSR# pin,the transmitter will complete the current character and enterthe idle mode until the DSR# pin is reasserted. Note: any in-band flow control characters are transmitted regardless ofthe state of the DSR# pin.External receiver clock for isochronous applications. TheRx_Clk_In is selected when CKS[1:0] = ‘01’.90, 75, 70, 56 I(h)I(h) RI[3:0]#Tx_Clk_In[3:0]Active-low modem Ring-Indicator inputExternal transmitter clock. This clock can be used by thetransmitter (and indirectly by the receiver) when CKS[6]=’1’.Clock Interface Pins – All ModesPin Dir 1 Name Description49 I/OXTLOCrystal oscillator output when OSCDIS = ‘0’.External clock source input when OSCDIS = ‘1’48 I XTLI Crystal oscillator input when OSCDIS = ‘0’, up to 20MHz.N/C when OSCDIS = ‘1’45 I OSCDIS Oscillator disable.When 0, the internal crystal oscillator is enabled and a crystal needs to be attached to XTLI/XTLO.XTLSEL must be set according to the crystal frequency that is used (up to 20Mhz).When 1, the internal crystal oscillator is disabled and an external oscillator source (up to 60MHz) can be input to XTLO. XTLI is N/C and XTLSEL must be 0130 I XTLSEL Defines the frequency of the crystal attached to XTLI/XTLO(when OSCDIS = ‘0’)0 = 1 MHz – 12 MHz 1 = 12 MHz – 20 MHz8-bit Local Bus – Mode 0Pin Dir 1 Name Description 111O UART_CLK_Out Buffered crystal output. This clock can drive external UARTsconnected to the local bus. Can be enabled / disabled by software.123 O(h) LBRST Local bus active-high reset. 124 O LBRST# Local bus active-low reset. 104 O LBDOUT Local bus data out enable. This pin can be used by externaltransceivers; it is high when LBD[7:0] are in output mode and low when they are in input mode.74 O LBCLK Buffered PCI clock. Can be enabled / disabled by software. 114, 115, 116, 117 O(h) O(h) LBCS[3:0]# LBDS[3:0]# Local bus active-low Chip-Select (Intel mode).Local bus active-low Data-Strobe (Motorola mode).112 O O LBWR# LBRDWR# Local bus active-low write-strobe (Intel mode).Local bus Read-not-Write control (Motorola mode).113 O Z LBRD# Hi-Z Local bus active-low read-strobe (Intel mode).Permanent high impedance (Motorola mode).105, 106, 108, 109 118, 119, 120, 122 O(h) LBA[7:0] Local bus address signals. 96, 97, 98, 99 100, 101, 102, 103I/O(h) LBD[7:0] Local bus data signals.Parallel Port – Mode 1Pin Dir 1 NameDescription123 I(h) I(h) ACK#INTR#Acknowledge (SPP mode). ACK# is asserted (low) by the peripheral to indicate that a successful data transfer has taken place.Identical function to ACK# (EPP mode).122 I(h) PEPaper Empty. Activated by printer when it runs out of paper. 120 I(h) I(h) BUSYWAIT#Busy (SPP mode). BUSY is asserted (high) by the peripheral when it is not ready to accept data.Wait (EPP mode). Handshake signal for interlocked IEEE 1284 compliant EPP cycles.109 OD(h) O(h) SLIN#ADDRSTB#Select (SPP mode). Asserted by host to select the peripheral.Address strobe (EPP mode) provides address read and write strobe.119 I(h) SLCT Peripheral selected. Asserted by peripheral when selected. 118 I(h) ERR#Error. Held low by the peripheral during an error condition. 108 OD(h) O(h) INIT#INIT#Initialize (SPP mode). Commands the peripheral to initialize.Initialize (EPP mode). Identical function to SPP mode. 106 OD(h) O(h) AFD#DATASTB# Auto Feed (SPP mode, open-drain).Data strobe (EPP mode) provides data read and write strobe.105 OD(h) O(h) STB#WRITE#Strobe (SPP mode). Used by peripheral to latch data currently available on PD[7:0].Write (EPP mode). Indicates a write cycle when low and a read cycle when high . 96, 97, 98, 99, 100, 101, 102, 103I/O(h) PD[7:0] Parallel data bus.104OPDOUTParallel port data out enable. This pin should be used by external transceivers for 5 V signaling; it is high when PD[7:0] are in output mode and low when they are in input mode.Multi-purpose and External Interrupt Pins – All ModesPin Dir1Name DescriptionMODE0 1135 --135I/O(h)OMIO0NCMulti-purpose I/O 0. Can drive high or low, or assert a PCIinterrupt.Output Driving ‘0’. Can be left as a No-connect.134 134 134134I/O(h)MIO1NCMulti-purpose I/O 1. Can drive high or low, or assert a PCIinterrupt (as long as LCC[6:5] = “00”).Output Driving ‘0’ (when LCC[6:5] ≠ ‘00’)Can be left as a No-Connect.133 133 133133I/O(h)IMIO2PME_InMulti-purpose I/O 2. When LCC[7] = 0, this pin can drive highor low, or assert a PCI interrupt.Input power management event. When LCC[7] is set thisinput pin can assert a function 1 PME#.93, 94, 95, 125, 126, 127, 128, 132 I/O(h) MIO[10:3] Multi-purpose I/O pins. Can drive high or low, or assert a PCIinterrupt.EEPROM Pins – All ModesPin Dir1Name Description53 OEE_CKEEPROMclock.52 O EE_CS EEPROM active-high Chip Select.54 IU(h) EE_DI EEPROM data in, with internal pull-up.When the serial EEPROM is connected, this pin should bepulled up using a 1-10k resistor. When the EEPROM is notused the internal pull-up is sufficient.Pin to be connected to the external EEPROM’s EE_DO pin(if used).51 O EE_DO EEPROM data out.Pin to be connected to the external EEPROM’s EE_DI pin(if used).Table 1: Pin DescriptionsI/O Direction Key P_I PCI input 3.3 V Only P_O PCI output / PCITristates 3.3 V Only P_I/O PCI bi-directional 3.3 V Only P_OD PCI open drain 3.3 V OnlyI Input LVTTL level I(h) Input LVTTL level, 5 V tolerant IU(h) Input with internal pull-up LVTTL level, 5 V tolerant I/O(h) Bi-Directional LVTTL level, 5 V tolerantO Output Standard Output O(h) Output 5 V tolerant (High Voltage BI-Direct in output mode) OD Open drain Standard Open-drain Output OD(h) Open drain 5 V tolerant (High Voltage BI-Direct in open-drain mode) NC No connectG Ground V VoltageMiscellaneous PinsPin Dir 1 NameDescription44 IMODEMode selector Pin0 : Function 0 : Quad UART. Function 1 : 8-bit local bus.1 : Function 0 : Quad UART. Function 1 : Parallel port.Power and GroundPinType Name Description19, 42, 47, 69, 88, 107, 131, 148VVDDPower Supply (3.3 V)11, 22, 36, 140, 156, 162, 173 V VIOPCI I/O Universal VoltageDefines the (clamping) voltage of the PCI I/O Buffers.To be connected to the VIO pin of the PCI connector. 3, 4, 9, 16, 21, 29, 30, 37, 38, 43, 46, 68, 87, 92, 110, 121, 129, 141, 143, 145, 152, 153, 159, 166, 172G GNDPower Supply Ground (0 V)4C ONFIGURATION AND O PERATIONThe OXuPCI954 is a multi-function, target-only PCI device, compliant with the PCI Local Bus Specification, Revision 3.0 and the PCI Power Management Specification, Revision 1.1.The OXuPCI954 affords maximum configuration flexibility by treating the internal UARTs, the local bus and the parallel port as separate logical functions. Each function has its own configuration space and is therefore recognized and configured by the PCI BIOS separately. The functions used are configured by the Mode Selection Pin as shown in Section 1 OXuPCI954 Device Modes.The OXuPCI954 is configured by system start-up software during the bootstrap process that follows bus reset. The system scans the bus and reads the vendor and device identification codes from any devices it finds. It then loads device-driver software according to this information and configures the I/O, memory and interrupt resources. Device drivers can then access the functions at the assigned addresses in the usual fashion, with the improved data throughput provided by PCI.Each function operates as though it was a separate device. However there are a set of Local Configuration Registers that can be used to enable signals and interrupts, configure timings, and improve the efficiency of multi-port drivers. This architecture enables separate drivers to be installed for each function. Generic port drivers can be hooked to use the functions individually, or more efficient multi-port drivers can hook both functions, accessing the Local Configuration Registers from either.All registers default after reset to suitable values for typical applications such a 4/8 port serial, or combo 4-port serial/1-port parallel add-in cards. However, all identification, control and timing registers can be redefined using an optional serial EEPROM.5PCI T ARGET C ONTROLLER5.1OperationThe OXuPCI954 responds to the following PCI transactions:-•Configuration access: The OXuPCI954 responds to type 0 configuration reads and writes if the IDSELsignal is asserted and the bus address is selecting theconfiguration registers for function 0 or 1. The devicewill respond to the configuration transaction by asserting DEVSEL#. Data transfer then follows. Anyother configuration transaction will be ignored by theOXuPCI954.•I/O reads/writes: The address is compared with the addresses reserved in the I/O Base Address Registers(BARs). If the address falls within one of the assignedranges, the device will respond to the I/O transactionby asserting DEVSEL#. Data transfer follows thisaddress phase. For the UARTs and 8-bit local buscontroller, only byte accesses are possible. For I/Oaccesses to these regions, the controller comparesAD[1:0] with the byte-enable signals as defined in thePCI specification. The access is always completed;however if the correct BE signal is not present thetransaction will have no effect.•Memory reads/writes: These are treated in the same way as I/O transactions, except that the memoryranges are used. Memory access to single-byte regions is always expanded to DWORDs in theOXuPCI954. In other words, OXuPCI954 reserves aDWORD per byte in single-byte regions. The deviceallows the user to define the active byte lane usingLCC[4:3] so that in Big-Endian systems the hardwarecan swap the byte lane automatically. For Memorymapped access in single-byte regions, the OXuPCI954 compares the asserted byte-enable withthe selected byte-lane in LCC[4:3] and completes theoperation if a match occurs, otherwise the access willcomplete normally on the PCI bus, but it will have noeffect on either the internal UARTs or the local buscontroller.•All other cycles (64-bit, special cycles, reserved encoding etc.) are ignored.The OXuPCI954 will complete all transactions as disconnect-with-data, i.e. the device will assert the STOP# signal alongside TRDY#, to ensure that the Bus Master does not continue with a burst access. The exception to this is Retry, which will be signaled in response to any access while the OXuPCI954 is reading from the serial EEPROM.The OXuPCI954 performs medium-speed address decoding as defined by the PCI specification. It asserts the DEVSEL# bus signal two clocks after FRAME# is first sampled low on all bus transaction frames which address the chip. The internal UARTs are accessed with zero wait states inserted. Fast back-to-back transactions are supported by the OXuPCI954 as a target, so a bus master can perform faster sequences of write transactions to the UARTs or local bus when an inter-frame turn-around cycle is not required.The device supports any combination of byte-enables to the PCI Configuration Registers and the Local Configuration Registers. If a byte-enable is not asserted, that byte is unaffected by a write operation and undefined data is returned upon a read.The OXuPCI954 performs parity generation and checking on all PCI bus transactions as defined by the standard. Note this is entirely unrelated to serial data parity which is handled within the UART functional modules themselves. If a parity error occurs during the PCI bus address phase, the device will report the error in the standard way by asserting the SERR# bus signal. However if that address/command combination is decoded as a valid access, it will still complete the transaction as though the parity check was correct.The OXuPCI954 does not support any kind of caching or data buffering in addition to that already provided within the UARTs by the transmit and receive data FIFOs. In general, registers in the UARTs and on the local bus can not be pre-fetched because there may be side-effects on read.5.2Configuration SpaceThe OXuPCI954 is a dual-function device, where each logical function has its own configuration space. All required fields in the standard header are implemented, plus the Power Management Extended Capability register set. The format of the configuration space is shown in the following tables.In general, writes to any registers that are not implemented are ignored, and all reads from unimplemented registers return 0.。

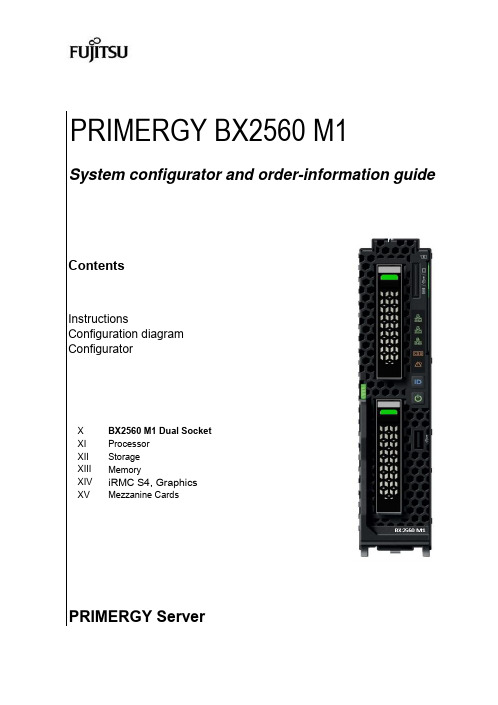

PRIMERGY BX2560 M1 系统配置器和订单信息指南说明书

PRIMERGY BX2560 M1System configurator and order-information guide ContentsInstructionsConfiguration diagramConfigurator10X BX2560 M1 Dual Socket11XI Processor12XII Storage13XIII Memory14XIV iRMC S4, Graphics15XV Mezzanine Cards16PRIMERGY ServerSystem configurator and order-information guidePRIMERGY BX2560 M1 Status: 2016-04-01 InstructionsThis document contains basic product and configuration information that will enable you to configure your system viaSystem-Architect.Only the tool "System-Arcitect" will ensure a fast and proper configuration of your PRIMERGY server or your complete PRIMERGY Rack system.Please pay attention to the naming conventions: BX2560 M1Dual Server Blade M1You can configure your individual PRIMERGY server in order to adjust your specific requirements.The System configurator is divided into several chapters that are identical to the current price list and PC-/ System-Architect. Please follow the lines. If there is a junction, you can choose which way or component you would like to take. Go throughthe configurator by following the lines from the top to the bottom.In one chapter you can only select as many components (here 3x) as the arrow indicates.3xPlease note that there are information symbols which indicate necessary information.For further information see:/products/standard_servers/index.html(internet)https:///com/order-supply/configurators/primergy_config/Pages/Currentconfigurators.aspx(extranet)Prices and availability see price list and PC-/ System-ArchitectSubject to change and errors exceptedSystem configurator and order-information guidePRIMERGY BX2560 M1 Status: 2016-04-01Configuration diagram Dual Server Blade BX2560 M1Key:Included in basic unit OptionThe population order for the DIMMs: for each CPU, the DIMM row 1 (DIMMS 1A 1B 1C 1D) (DIMMS1E 1F 1G 1H) first,then row 2 (DIMMs 2A 2B 2C 2D) (DIMMs 2E 2F 2G 2H)Section XII Storage / RAID Functionality on Server BladeOne UFM can be installed independent from the disk drivesRemark: UFM is part of the VMWare Embedded solution (26361-F2341-E433)Configuration Hint - Second CPU needed for PCIe x4 Gen3 SSD/HDD OptionThe PCIe HDD/SSD Option is only supported if the second CPU is installedPlease refer the following configuration matrix for your desired confuration.S26361-F3823-E410S26361-F3823-E400S26361-F4008-E100S26361-F4008-E101PRAID EM400i PRAID CM400i PCH connection Kit PCIe x4 Gen3PY SAS 12G RAID HDD Module PY SAS 12G RAID HDD Module supports up to 2 HDD/SSDw/ 1 GB Cache w/o Cache connected to onboard PCHMegaRAID MegaRAIDRAID level 0/1/1E/10/5/50/6/60RAID level 0/1/10Hint: 2nd CPU is mandatorySAS 12 Gb/sec SAS 12 Gb/sec for this Optionincl. PRAID EM400i Riser incl. PRAID EM400i Riser for this Optionpluggable on the main board pluggable on the main boardPCIe Gen3 interface PCIe Gen3 interface SATA interface PCIe x4 Gen3 interface4x SAS links to midplane2x SAS links to internal HDD's2x PCIe x4 Gen3 links2x SAS links to internal HDD's2x SATA links to int. HDD's to internal HDD'smax. 1x per Server Blade max. 1x per Server Blade max. 1x per Server Blade max. 1x per Server BladeS26361-F3823-E10PRAID EM400i FBUPY FBU03 ModuleFlash Backup Unitincl. FBU holder SATA HDD / SSD PCIe-SSD / HDDS26361-F3823-E30PRAID EM400i MezzPY SAS Expander Mezzanine Cardconnection to SAS CBincl. SAS cableS26361-F3823-E20S26361-F3823-E20PRAID EM400i BP PRAID EM400i BPPY SAS 12G HDD Backplane PY SAS 12G HDD Backplane2 internal SAS links 2 internal SAS linksto PY SAS 12G RAID HDD Modul to PY SAS 12G RAID HDD ModulGSystem configurator and order-information guide PRIMERGY BX2560 M1 Status: 2016-04-01Memory Configuration PRIMERGY BX2560 M1Each CPU offers 8 Slots for DDR4 Memory Modules organised in 2 Banks and 4 Channels.If you need more than 8 Slots you have to configure the 2nd CPU.Depending on the amount of memory configured you can decide between 4 basic modes of operation (see explanation below).There are 2 different kinds of DDR4 Memory Modules available: RDIMM and LRDIMM Mix of RDIMM and LRDIMM is not allowed.ModeConfigurationApplication SDDC (chipkill) support any no yes detect multi-bit errors Independant Channel Mode 1, 2 or 3 Modules per Bank yes yes offers max. flexibility, upgradeability, capacity Mirrored Channel Mode *) 4 identical Modules / Bank noyes offers maximum security Performance Mode 4 identical Modules / Bank yes yes offers maximum performance and capacity Rank Sparing Mode *)min. 2 Ranks / Channel no yes balances security and capacity *) For the delivery ex works the system will be prepared with dedicated BIOS setting.CapacityConfiguration RDIMM LRDIMM NotesMin. Memory per CPU 1 Module / CPU with one CPU Max. Memory per CPU 8/12 Modules / CPU with one CPUMax. Memory per System16/24 Modules / System512GB 1024GBif second CPU is configuredMemory-Speed:Max. DDR4 memory speed depends on the memory configuration on one memory channel and the speed of the CPU The memory channel with the lowest speed defines the speed of all CPU channels in the system1R - Single Rank4R - Quad Rank 2R - Dual Rank 8R - Eight Rank1DPC = 1 DIMM per Channel 2DPC = 2 DIMM per Channel Configuration hints:- The memory sockets on the systemboard offer a color coding:Bank I black sockets Bank II blue sockets- A so called Bank consits of 1 memory module on every Channel available on one CPU (examples see below)Bank I on CPU 1/2up to 4 memory modules connected to Channel A - H on the 1st/2nd CPU Bank II on CPU 1/2up to 4 memory modules connected to Channel A - E on the 1st/2nd CPU - See below and next page for a detailed descriptions of the memory configuration supported.1x32GB 8x32GB 8x64GB RDIMMRDIMM LRDIMM x8x41x8GBrequiredrequired if 2nd CPU is configured Bank Ioptional, same type in Bank per CPU Bank IIoptional, any type--------not usedIndependent Channel Mode allows all channels to be populated in any orderCan run with differently rated DIMMs and use the settings of the slowest DIMM installed in the system2. Mirrored Channel Moderequiredrequired if 2nd CPU is configuredBank I optional, same type in Bank per CPUBank II Mirrored Channel Mode requires identical modules on channel A,B, C, D (1st CPU) or channel E, F, G and H (2nd CPU)50% of the capacity is used for the mirror => the available memory for applications is only half of the installed memory If this mode is used, a multiple of 4 identical modules has to be ordered.3. Performance Channel Moderequiredrequired if 2nd CPU is configured Bank I optional, same type in Bank per CPU Bank II optional, any typePerformance Channel Mode requires identical modules on all channels of each Bank per CPU.If this mode is used, a multiple of 4 identical modules has to be ordered.C h a n n e l AC h a n n e l BC h a n n e l CC h a n n e l DC h a n n e l EC h a n n e l FC h a n n e l EC h a n n e l Fh a n n e l HC h a n n e l AC h a n n e l BC h a n n e l CC h a n n e l Dh a n n e l Eh a n n e l FC h a n n e l GC h a n n e l HC h a n n e l GC h a n n e l Ha n n e l Aa n n e l Ba n n e l Ca n n e l Dh a n n e l Grequiredrequired if 2nd CPU is configured Bank Ioptional, same type in Channel per CPU Bank IIoptional, any typeBank Irequired(black)required if 2nd CPU is configured Bank II (blue)optional, same type in Channel per CPU optional, any typeBank I required(black)required if 2nd CPU is configured optional, same type in Channel per CPUBank II (blue)optional, any typeRank Sparing Mode requires identical modules (same capacity and technology) within the same channel.The available memory for applications will vary depending on configuration. Please refer to the spreadsheet above "Effective Memory capacity with active Rank Sparing Mode". Population rule for Rank sparing mode is to achieve max.available memory, e.g. 8 DIMMs will be spread across two channels, each with 4DPCC h a n n e l GC h a n n e l H4-Rank Memory modules (LRDIMM)C h a n n e l AC h a n n e l BC h a n n e l CC h a n n e l FC h a n n e l GC h a n n e l HC h a n n e l FC h a n n e l GC h a n n e l HC h a n n e l AC h a n n e l BC h a n n e l CC h a n n e l FC h a n n e l EC h a n n e l D2-Rank Memory modules (RDIMM)C h a n n e l AC h a n n e l BC h a n n e l CC h a n n e l DC h a n n e l EC h a n n e l EC h a n n e l D1-Rank Memory modules (RDIMM)System configurator and order-information guidePRIMERGY BX2560 M1 Status: 2016-04-01 Change Report。

IBM ThinkPad各种错误代码

IBM ThinkPad各种错误代码-深度解析在大家平时工作,生活中使用IBM 的笔记本电脑经常会出现各种各样的故障提示代码,有的时候其实只是小问题,只要知道代码其所代表的含意,解决问题就是件非常轻松的事情了.0175:Bad CRC1, stop POST task(CRC1 错误,停止POST 任务)0176:System Security - The system has been tampered with.(系统安全性- 系统受到了干扰.)0177:Bad SVP data, stop POST task.(SVP 数据错误,停止POST 任务.)0182:Bad CRC2.Enter BIOS Setup and load Setup defaults.(CRC2 错误.请进入BIOS Setup 并装入Setup 缺省值.)0185:Bad startup sequence settings. Enter BIOS Setup and load Setup defaults.(启动顺序设置错误.请进入BIOS Setup 并装入Setup 缺省值.)0187:EAIA data access error(EAIA 数据访问错误)0188:Invalid RFID Serialization Information Area.(无效的RFID 序列化信息区域.)0189:Invalid RFID configuration information area(无效的RFID 配置信息区域)0190:Critical low-battery error(电池电量严重不足错误)0191:Sytem Security - Invalid remote change requested.(系统安全性- 请求了无效的远程更改.)0192:System Security - IBM Embedded Security hardware tamper detected.(系统安全性- 检测到IBM Embedded Security 硬件干扰.)0199:System Security - IBM Security password retry count exceeded.(系统安全性- 超出IBM 安全性密码重试次数.)01C8:More than one modem devices are found. Remove one of them. Press to continue.(找到多个调制解调器设备.请卸下其中之一.按键继续.)01C9:More than one Ethernet devices are found. Remove one of them. Press to continue.(找到多个以太网设备.请卸下其中之一.按键继续.)0200:Hard disk error(硬盘错误)021x:Keyboard error(键盘错误)0230:Shadow RAM error(影子RAM 错误)0231:System RAM error(系统RAM 错误)0232:Extended RAM error(扩展RAM 错误)0250:System battery error(系统电池错误)0251:System CMOS checksum bad(系统CMOS 校验和错误)0260:System timer error(系统定时器错误)0270:Real time clock error(实时时钟错误)0271:Date and time error(日期和时间错误)0280:Previous boot incomplete(先前的引导未完成)02D0:System cache error(系统高速缓存错误)02F4:EISA CMOS not writable(EISA CMOS 不可写)02F5:DMA test failed(DMA 测试失败)02F6:Software NMI failed(软件NMI 失败)02F7:Fail-safe timer NMI failed(故障安全定时器NMI 失败)1802:Unauthorized network card is plugged in - Power off and remove the miniPCI network card.(插入了未授权的网卡- 关闭电源,然后卸下小型P 网卡).1803:Unauthorized daughter card is plugged in - Power off and remove the daughter card.(插入了未授权的子卡-关闭电源,然后卸下子卡.)1810:Hard disk partition layout error(硬盘分区布局错误)The power-on password prompt(出现开机密码提示)The hard disk password prompt(出现硬盘密码提示)Hibernation error(休眠错误)Operating system not found.(未找到操作系统.)Fan error(风扇错误)EMM386 Not Installed--Unable to Set Page Frame Base Address.(未安装EMM386 - 无法设置页帧基地址.)CardBus Configuration Error--Device Disabled.(CardBus 配置错误- 设备禁用.)Thermal sensing error(热检测错误)Authentication of system services failed. Press to resume.(系统服务认证失败.按恢复.)消息:0175:Bad CRC1, stop POST task(CRC1 错误,停止POST 任务)解决方案:EEPROM 校验和不正确(块#6).将计算机送去维修.消息:0176:System Security - The System has been tampered with.(系统安全性- 系统受到了干扰.)解决方案:如果您卸下了安全芯片并将其重新安装,或安装了一个新的安全芯片,则显示此消息.要清除该错误,请进入BIOS Setup Utility.如果这样不能解决问题,请将计算机送去维修.消息:0177:Bad SVP data, stop POST task.(SVP 数据错误,停止POST 任务.)解决方案:EEPROM 中的超级用户密码的校验和不正确.应该更换系统板. 将计算机送去维修.消息:0182:Bad CRC2.Enter BIOS Setup and load Setup defaults.(CRC2 错误.进入BIOS Setup 并装入Setup 缺省值.)解决方案:EEPROM 中的CRC2 设置的校验和不正确.请转至BIOS Setup Utility.按F9,然后按Enter 键来装入缺省设置.按F10,然后按Enter 键来重新启动系统.消息:0185:Bad startup sequence settings.Enter BIOS Setup and load Setup defaults.(启动顺序设置错误.进入BIOS Setup 并装入Setup 缺省值.)解决方案:EEPROM 中的启动顺序设置不正确.请转至BIOS Setup Utility.按F9,然后按Enter 键来装入缺省设置.按F10,然后按Enter 键来重新启动系统.消息:0187:EAIA data access error(EAIA 数据访问错误)解决方案:访问EEPROM 失败.将计算机送去维修.消息:0188:Invalid RFID Serialization Information Area.(无效的RFID 序列化信息区域.)解决方案:EEPROM 校验和不正确(块# 0 和1).应更换系统板,并且需要重新安装计算机序列号.将计算机送去维修.消息:0189:Invalid RFID configuration information area(无效的RFID 配置信息区域)解决方案:EEPROM 校验和不正确(块# 4 和5).应该更换系统板,并且需要重新安装UUID.将计算机送去维修.消息:0190:Critical low-battery error(电池电量严重不足错误)解决方案:由于电池电量过低,计算机关闭.将交流电源适配器连接到计算机并给电池充电,也可用充足电的电池替换此电池.消息:0191:System Security - Invalid remote change requested.(系统安全性- 请求了无效的远程更改.)解决方案:系统配置更改出现故障.请确认此操作并重试.要清除该错误,请进入BIOS Setup Utility.消息:0192:System Security - IBM Embedded Security hardware tamper detected.(系统安全性- 检测到IBM Embedded Security 硬件干扰.)解决方案:用另一芯片更换了安全芯片.将计算机送去维修.消息:0199:System Security - IBM Security password retry count exceeded.(系统安全性- 超出IBM 安全性密码重试次数.)解决方案:如果您输入错误的超级用户密码超过三次,则显示此消息.请确认超级用户密码并重试.要清除该错误,请进入BIOS Setup Utility.消息:01C8:More than one modem devices are found. Remove one of them. Press to continue.(找到多个调制解调器设备.请卸下其中之一.按继续.)解决方案:卸下调制解调器小型PCI 卡.否则,按Esc 忽略警告消息.如果这样不能解决问题,请将计算机送去维修.消息:01C9:More than one Ethernet devices are found. Remove one of them. Press to continue.(找到多个以太网设备.请卸下其中之一.按继续.)解决方案:您的ThinkPad 计算机具有内置的以太网功能部件,您不能通过安装以太网设备来添加另外一个这样的功能部件.如果显示此错误消息,请卸下您安装的以太网设备.否则,按Esc 忽略警告消息.如果这样不能解决问题,请将计算机送去维修.消息:0200:Hard disk error(硬盘错误)解决方案:硬盘不工作.确保硬盘驱动器连接牢固.运行BIOS Setup Utility;然后确保未在Startup 菜单中禁用该硬盘驱动器.消息:021x:Keyboard error(键盘错误)解决方案:确保键盘或外接键盘(如果有)上没有放置任何物体.关闭计算机,然后关闭所有连接设备的电源.首先打开计算机,然后打开所有连接设备的电源.如果仍看到相同的错误代码,请执行以下操作:如果连接了外接键盘,请执行以下操作:关闭计算机,断开外接键盘的连接;然后打开计算机.确保内置键盘工作正常.如果内置键盘工作正常,请将外接键盘送去维修.确保外接键盘连接到了正确的接口.使用PC-Doctor 测试计算机.如果计算机在测试过程中停止,应将计算机送去维修.0210:F1<—>3A; F2<—>3C; F3<—>3D; F4<—>3E; F5<—>3F; F6<—>40; F7<—>41; F8<—>42; F9<—>43; F10<—>44; F11<—>45; F12<—>46; Q<—>10; W<—>11; E<—>12; R<—>13; T<—>14; Y<—>15; U<—>16; I<—>17; O<—>18; P<—>19; A<—>1E; S<—>1F; D<—>20; F<—>21; G<—>22; H<—>23; J<—>24; K<—>25; L:26; ;<—>27 ; <—>28; Z<—>2C; X<—>2D; C<—>2E; V<—>2F; B<—>30; N<—>31; M<—>32 <<—>33; ><—>34; ?<—>35; Space<—>39; Capslock<—>3A; Enter<—>1C; left shift<—>2A; left ctrl<—>1D; left alt<—>38Stuck key : 0C ——主板故障原文地址:/bbs/dispbbs.asp?boardid=36&Id=217消息:0230:Shadow RAM error(影子RAM 错误)解决方案:影子RAM 失败.使用PC-Doctor 测试计算机内存.如果恰好在打开计算机之前添加了内存条,请重新安装它.然后使用PC-Doctor 测试内存.消息:0231:System RAM error(系统RAM 错误)解决方案:系统RAM 失败.使用PC-Doctor 测试计算机内存.如果恰好在打开计算机之前添加了内存条,请重新安装它.然后使用PC-Doctor 测试内存.消息:0232:Extended RAM error(扩展RAM 错误)解决方案:扩展RAM 失败.使用PC-Doctor 测试计算机内存.如果恰好在打开计算机电源之前增加了内存,应重新安装它.然后使用PC-Doctor 测试内存.消息:0250:System battery error(系统电池错误)解决方案:当计算机关闭时用来保存配置信息(例如日期和时间)的备份电池被耗尽.更换电池,并运行BIOS Setup Utility 以验证配置.如果仍有问题,应将计算机送去维修.消息:0251:System CMOS checksum bad(系统CMOS 校验和错误)解决方案:系统CMOS 可能已被应用程序毁坏.计算机使用缺省设置.运行BIOS Setup Utility 以重新配置设置.如果仍看到相同的错误代码,应将计算机送去维修.消息:0260:System timer error(系统定时器错误)解决方案:将计算机送去维修.消息:0270:Real time clock error(实时时钟错误)解决方案:将计算机送去维修.消息:0271:Date and time error(日期和时间错误)解决方案:计算机中既没有设置日期也没有设置时间.使用BIOS Setup Utility 设置日期和时间.消息:0280:Previous boot incomplete(先前的引导未完成)解决方案:计算机先前无法完成引导过程.关闭计算机;然后再打开,以启动BIOS Setup Utility.验证配置,然后通过选择Restart 项下的Exit Saving Changes 选项或按F10 重新启动计算机.如果仍看到相同的错误代码,应将计算机送去维修.消息:02D0:System cache error(系统高速缓存错误)解决方案:高速缓存禁用.将计算机送去维修.消息:02F4:EISA CMOS not writable(EISA CMOS 不可写)解决方案:将计算机送去维修.消息:02F5:DMA test failed(DMA 测试失败)解决方案:将计算机送去维修.消息:02F6:Software NMI failed(软件NMI 失败)解决方案:将计算机送去维修.消息:02F7:Fail-safe timer NMI failed(故障安全定时器NMI 失败)解决方案:将计算机送去维修.消息:1802:Unauthorized network card is plugged in - Power off and remove the miniPCI network card.(插入了未经认证的网卡- 关闭电源,然后卸下小型PCI 网卡.)解决方案:此计算机上不支持小型PCI 网卡.请卸下它.消息:1803:Unauthorized daughter card is plugged in - Power off and remove the daughter card.(插入了未授权的子卡-关闭电源并卸下子卡.)解决方案:子卡在本计算机上不受支持.将其卸下.消息:1810:Hard disk partition layout error(硬盘分区布局错误)解决方案:在识别硬盘上分区布局的过程中出现的问题停止了计算机启动.IBM Predesktop Area 已经被删除或硬盘包含毁坏的数据.要尝试重新启动计算机,请完成以下操作之一:如果IBM Predesktop Area 已被删除按F1 打开IBM BIOS Setup Utility.选择Security --> IBM Predesktop Area --> Access IBM Predesktop Area.将该项设置为Disabled.保存并退出.如果以上操作失败按Enter 键.单击RECOVER TO FACTORY CONTENTS 并按照屏幕上的指示信息操作.注:这将永久擦除硬盘上的所有内容,然后恢复IBM 预安装的软件.按F1 打开IBM BIOS Setup Utility 或按Enter 键启动IBM Predesktop Area.如果计算机仍然无法启动,则请致电IBM HelpCenter(R).消息:The power-on password prompt(出现开机密码提示)解决方案:设置了开机密码或超级用户密码.输入密码并按Enter 键即可使用计算机(请参考使用密码).如果不接受开机密码,可能是设置了超级用户密码.输入超级用户密码并按Enter 键.如果仍看到相同的错误消息,应将计算机送去维修.消息:The hard disk password prompt(出现硬盘密码提示)解决方案:设置了硬盘密码.输入密码并按Enter 键即可使用计算机(请参考硬盘密码).如果仍看到相同的错误消息,应将计算机送去维修.消息:Hibernation error(休眠错误)解决方案:在计算机进入休眠方式和结束该方式之间的时间内,系统配置发生了变化,计算机无法恢复正常运行.将系统配置恢复到计算机进入休眠方式之前的状态.如果改变了内存大小,应重新创建休眠文件.消息:Operating system not found.(未找到操作系统.)解决方案:请验证以下内容:正确地安装了硬盘驱动器.软盘驱动器中有可启动软盘如果仍看见相同的错误消息,请使用BIOS Setup Utility 检查引导顺序.消息:Fan error(风扇错误)解决方案:散热风扇出现故障.将计算机送去维修.消息:EMM386 Not Installed--Unable to Set Page Frame Base Address.(未安装EMM386 - 无法设置页帧基地址)解决方案:编辑C:\CONFIG.SYS 并将此行device=C:\WINDOWS\EMM386.EXE RAM更改为device=C:\WINDOWS\EMM386.EXE NOEMS然后保存此文件.消息:CardBus Configuration Error--Device Disabled(CardBus 配置错误- 设备禁用)解决方案:转至IBM BIOS Setup Utility.按F9,然后按Enter 键装入缺省设置.按F10,然后按Enter 键重新启动系统.消息:Thermal sensing error(热检测错误)解决方案:热传感器未正确工作.将计算机送去维修.消息:Authentication of system services failed. Press to resume.(系统服务认证失败.按恢复.)解决方案:HDD 中的IBM Predesktop Area 毁坏.要使用IBM Predesktop Area,获取一张恢复CD,并使用它来恢复IBM Predesktop Area.。

ATMEGA2561V资料