S82078中文资料

ISO 2768-1-1989中文版

2768-1初版1989-11-15常规公差——第一部分:无单独公差标示的线尺度、角度公差参考号ISO2768-1:1989(E) ISO 2768-1:1989(E)前言ISO(国际标准化组织)是世界范围内国家标准实体(ISO成员)的联合体。

通常由ISO技术委员会制定国际标准。

但是,只要对该组织建立的某个主题感兴趣,任何成员都可以在这方面充当委员会的代表。

所有与ISO关联的国际组织,政府以及非政府机构,都参加此项工作。

ISO在电工标准事务上,与国际电工委员会紧密一致。

由技术委员会起草的国际标准草稿,在ISO将其作为国际标准正式文件之前,需要分发给各成员实体进行核准。

标准的核准需要经过ISO的程序进行,即需要所有成员的75%赞成才可获得通过。

ISO2768-2由技术委员会ISO/TC 3(误差与配合)制定。

ISO2678-1初版与ISO2678-1:1989一起取代了ISO2768:1973。

题为常规公差的ISO2768包括以下部分:第一部分:无单独公差标示的线尺度、角度公差第二部分:无单独公差标示的部件几何公差ISO2768中附录A与B仅供参考。

简介所有部件部分的零部件都有自己的尺寸和几何形状。

如果尺寸或几何特性(形状,方向与位置)出现偏差,超出了该部分要求的最低值,则破坏了该部分的功能。

图纸上的公差规定应当完整,以确保控制零部件的尺寸与几何因素,也就是,不应该留给车间或检验部人员来判断。

使用尺寸与几何常规公差,减轻了满足该必要条件的任务。

国际标准 ISO2768-1:1989(E)常规公差——第一部分:无单独公差标示的线尺度、角度公差1 应用范围ISO2768的这部分意在简化图纸标示,规范常规线尺度、角度公差,从而使图纸上所有零部件不再出现单独不同的公差。

此处分四类进行公差规定。

注1:对常规线尺度、角度公差规定的方案,将在附件A中阐述。

该部分主要适用于金属材料切除后生产的或由金属板加工的零部件。

S108T02;S108T02F;S208T02;中文规格书,Datasheet资料

S108T02 Series S208T02 Series■ FeaturesI T (rms)≤8A, Zero Cross type Low profile SIP 4pin Triac output SSR1. Output current, I T (rms)≤8.0A2. Zero crossing functionary (V OX : MAX. 35V)3. Slim 4 pin low profile SIP package4. High repetitive peak off-state voltage (V DRM : 600V, S208T02 Series ) (V DRM : 400V, S108T02 Series )5. High isolation voltage between input and output (V iso (rms) : 3.0kV)6. Lead-free terminal components are also available (see Model Line-up section in this datasheet)7. Screw hole for heat sink■ DescriptionS108T02 Series and S208T02 Series Solid State Relays (SSR) are an integration of an infrared emitting diode (IRED), a Phototriac Detector and a main output Triac. These devices are ideally suited for controlling high voltage AC loads with solid state reliability while providing 3.0kV isolation (V iso (rms)) from input to out-put.Notice The content of data sheet is subject to change without prior notice.In the absence of confirmation by device specification sheets, SHARP takes no responsibility for any defects that may occur in equipment using any SHARP ■ Agency approvals/Compliance1. Isolated interface between high voltage AC devices and lower voltage DC control circuitry.2. Switching motors, fans, heaters, solenoids, and valves.3. Power control in applications such as lighting and temperature control equipment.■ Applications1. Package resin : UL flammability grade (94V-0)∗Non-zero cross type is also available. (S108T01 Series/S208T01 Series)∗ : Do not allow external connection.( ) : Typical dimensions■ Internal Connection Diagram+)−)■ Outline Dimensions(Unit : mm)Date code (2 digit)Rank markThere is no rank mark indicator and currently there are no rank offered for this device.A.D.199019911992199319941995199619971998199920002001MarkABCDEFHJKLMN Mark P R S T U V W X A B C Mark 123456789O N DMonth January February March April May June July August September October November December A.D 20022003200420052006200720082009201020112012······2nd digitMonth of production 1st digitYear of productionCountry of originJapanrepeats in a 20 year cycle■ Electro-optical CharacteristicsParameter Symbol Unit InputOutput (T a =25˚C)Forward voltageReverse currentRepetitive peak OFF-state currentON-state voltageHolding currentCritical rate of rise of OFF-state voltageCritical rate of rise of OFF-state voltage at commutaion Minimum trigger currentZero cross voltageIsolation resistanceTurn-on time Turn-off timeThermal resistanceV F I R I DRM V T (rms)I H dV/dt (dV/dt)c I FT V OX R ISO t ont off R th (j-c)R th (j-a)I F =20mA V R =3V V D =V DRM I T (rms)=2A, Resistance load, I F =20mA −V D =2/3•V DRM T j =125˚C , V D =2/3•V DRM , dI T /dt =−4.0A/msV D =6V, R L =30ΩI F =8mA DC500V, 40 to 60%RH V D (rms)=100V, AC50Hz, I F =20mAI T (rms)=2A, Resistance load V D (rms)=200V, AC50Hz, I F =20mA I T (rms)=2A, Resistance load V D (rms)=100V, AC50Hz, I F =20mAI T (rms)=2A, Resistance loadV D (rms)=200V, AC50Hz, I F =20mAI T (rms)=2A, Resistance loadBetween junction and case Between junction and ambience Conditions MIN.TYP.MAX.Transfer charac-teristics S108T02S208T02S108T02S208T02−−−−−305−−1010−−−−−−1.2−−−−−−−−−−−−−4.5401.41001001.550−−835−10101010−−V µA µA V mA V/µs V/µs mA V Ωmsms˚C /W ■ Absolute Maximum RatingsParameter Symbol Rating UnitInputOutput(T a =25˚C)Forward current Reverse voltage RMS ON-state current Peak one cycle surge current Repetitive peak OFF-state voltage Non-Repetitive peak OFF-state voltage Critical rate of rise of ON-state current Operating frequency Isolation voltage Operating temperature Storage temperature Soldering temperature *2*1I FV R I T (rms)I surge V DRMV DSMdI T /dt fV iso (rms)T opr T stg T solmA V A A VVA/µs Hz kV ˚C ˚C ˚C*3*3*45068804006004006005045 to 653.0−25 to +100−30 to +125260*1 40 to 60%RH, AC for 1minute, f =60Hz *2 For 10s*3 Refer to Fig.1, Fig.2*4 f =60Hz sine wave, T j =25˚C startS108T02S208T02S108T02S208T02Soldering areaShipping PackageModel No.Sleeve 25pcs/sleeve S108T02F S208T02FI FT [mA](V D =6V, R L =30Ω)MAX.8400MAX.8600V DRM [V]Please contact a local SHARP sales representative to see the actual status of the production.■ Model Line-up (1) (Lead-free terminal components)■ Model Line-up (2) (Lead solder plating components)Shipping PackageModel No.Sleeve 25pcs/sleeve S108T02S208T02I FT [mA](V D =6V, R L =30Ω)MAX.8400MAX.8600V DRM [V]F o r w a r d c u r r e n t I F (m A )Ambient temperature T a (˚C)060−2502550751001255040302010Fig.1 Forward Current vs. AmbientTemperatureFig.2 RMS ON-state Current vs.Ambient TemperatureF o r w a r d c u r r e n t I F (m A )Forward voltage V F (mA)1010.1100Fig.4 Forward Current vs. Forward VoltageFig.3 RMS ON-state Current vs.Case TemperatureR M S O N -s t a t e c u r r e n t I T (r m s )(A )Case temperature T C (°C)010−25255075100125987654321R M S O N -s t a t e c u r r e n t I T (r m s )(A )Ambient temperature T a (˚C)0987654321−25100755025125(1)(2)(3)(4)(5)(1)With infinite heat sink(2)With heat sink (200×200×2mm Al plate)(3)With heat sink (100×100×2mm Al plate)(4)With heat sink (50×50×2mm Al plate)(5)Without heat sink(N ote)In natural cooling condition, please locate Al platevertically, spread the thermal conductive silicone grease on the touch surface of the device and tighten up the device in the center of Al plate at the torque of 0.4N•m.Fig.8-b Repetitive Peak OFF-state Current vs.Ambient Temperature (S208T02)Fig.8-a Repetitive Peak OFF-state Current vs.Ambient Temperature (S108T02)R e p e t i t i v e p e a k O F F -s t a t e c u r r e n t I D R M (A )Ambient temperature T a (˚C)10−910−310−410−510−610−710−8R e p e t i t i v e p e a k O F F -s t a t e c u r r e n t I D R M (A )Ambient temperature T a (˚C)10−910−310−410−510−610−710−8Remarks : Please be aware that all data in the graph are just for reference.Fig.5 Surge Current vs. Power-on CycleFig.6 Minimum Trigger Current vs.Ambient TemperatureFig.7 Maximum ON-state Power Dissipationvs. RMS ON-state CurrentM i n i m u m t r i g g e r c u r r e n t I F T (m A )Ambient temperature T a (°C)0108642S u r g e c u r r e n t I s u r g e (A )Power-on cycle (Times)10080604020120M a x i m u m O N -s t a t e p o w e r d i s s i p a t i o n (W )RMS ON-state current I T (rms)(A)010864297531■ Design ConsiderationsIn order for the SSR to turn off, the triggering current (l F ) must be 0.1mA or less.When the input current (I F ) is below 0.1mA, the output Triac will be in the open circuit mode. However, if the voltage across the Triac, V D , increases faster than rated dV/dt, the Triac may turn on. To avoid this situation, please incorporate a snubber circuit. Due to the many different types of load that can be driven, we can merely recommend some circuit vales to start with : Cs=0.022µF and Rs=47Ω. The operation of the SSR and snubber circuit should be tested and if unintentional switching occurs, please adjust the snubber circuit component values accordingly.When making the transition from On to Off state, a snubber circuit should be used ensure that sudden drops in current are not accompanied by large instantaneous changes in voltage across the Triac.This fast change in voltage is brought about by the phase difference between current and voltage. Primarily, this is experienced in driving loads which are inductive such as motors and solenoids. Following the procedure outlined above should provide sufficient results. For over voltage protection, a Varistor may be used.Any snubber or Varistor used for the above mentioned scenarios should be located as close to the main out-put triac as possible.Particular attention needs to be paid when utilizing SSRs that incorporate zero crossing circuitry.If the phase difference between the voltage and the current at the output pins is large enough, zero crossing type SSRs cannot be used. The result, if zero crossing SSRs are used under this condition, is that the SSR may not turn on and off irregardless of the input current. In this case, only a non zero cross type SSR should be used in combination with the above mentioned snubber circuit selection process.The load current should be within the bounds of derating curve. (Refer to Fig.2) Also, please use the optional heat sink when necessary.In case the optional heat sink is used and the isolation voltage between the device and the optional heat sink is needed, please locate the insulation sheet between the device and the heat sink.When the optional heat sink is equipped, please set up the M3 screw-fastening torque at 0.3 to 0.5N•m.In order to dissipate the heat generated from the inside of device effectively, please follow the below sugges-tions.● Design guide● Recommended Operating ConditionsParameterS108T02S208T02Symbol Unit InputOutputInput signal current at ON state Input signal current at OFF state Load supply voltage Load supply currentFrequencyOperating temperatureI F (ON)I F (OFF)V OUT (rms)I OUT (rms)f T oprmA mA V mA Hz ˚C−−−Locate snubber circuit between output terminals(Cs =0.022µF, Rs =47Ω)−−Conditions(∗) See Fig.2 about derating curve (I T (rms) vs. ambient temperature).16080800.147−20240.1120240I T (rms)×80%(∗)6380MIN.MAX.✩ For additional design assistance, please review our corresponding Optoelectronic Application Notes.● Standard CircuitV +V S108T02● DegradationIn general, the emission of the IRED used in SSR will degrade over time.In the case where long term operation and / or constant extreme temperature fluctuations will be applied to the devices, please allow for a worst case scenario of 50% degradation over 5years.Therefore in order to maintain proper operation, a design implementing these SSRs should provide at least twice the minimum required triggering current from initial operation.(a) Make sure there are no warps or bumps on the heat sink, insulation sheet and device surface.(b) Make sure there are no metal dusts or burrs attached onto the heat sink, insulation sheet and device sur-face.(c) Make sure silicone grease is evenly spread out on the heat sink, insulation sheet and device surface.Silicone grease to be used is as follows;1) There is no aged deterioration within the operating temperature ranges.2) Base oil of grease is hardly separated and is hardly permeated in the device.3) Even if base oil is separated and permeated in the device, it should not degrade the function of a device. Recommended grease : G-746 (Shin-Etsu Chemical Co., Ltd.): G-747 (Shin-Etsu Chemical Co., Ltd.): SC102 (Dow Corning Toray Silicone Co., Ltd.) In case the optional heat sink is screwed up, please solder after screwed.In case of the lead frame bending, please keep the following minimum distance and avoid any mechanical stress between the base of terminals and the molding resin.Some of AC electromagnetic counters or solenoids have built-in rectifier such as the diode.In this case, please use the device carefully since the load current waveform becomes similar with rectangu-lar waveform and this results may not make a device turn off.■ Manufacturing Guidelines● Soldering MethodFlow Soldering (No solder bathing)Flow soldering should be completed below 260˚C and within 10s.Preheating is within the bounds of 100 to 150˚C and 30 to 80s.Please solder within one time.Other noticesPlease test the soldering method in actual condition and make sure the soldering works fine, since the impact on the junction between the device and PCB varies depending on the tooling and soldering conditions.分销商库存信息:SHARP-MICROELECTRONICSS108T02S108T02F S208T02。

JTMP04090XXXXS中文资料

TOSHIBA CMOS Digital Integrated Circuit Silicon Monolithic

TMP04090FXXXX(ES),JTMP04090XXXXS(ES)

CMOS 4-bit LL Microcontroller (OTP built-in) (LL: Low power consumption & voltage operation microcontroller)

Note 1: Pin specifications differ between the OTP versions corresponding to TMP04CH00FXXX and TMP04CH01FXXX. Example: COM9/S60, COM9 OTP version corresponding OTP version corresponding to TMP04CH00FXXX to TMP04CH01FXXX Note 2: Chip size differs from that of the mask ROM version.

LCD Controller

Interrupt Controller

Quadrupler

V3 V2 V1 C1 C2 VXT VSS VDD

V1 Timer/Counter (8 bit/16 bit)

Voltage Reglater

IN1 to IN4 IO01 to IO04 IO11 to IO14 IO21 to IO24

Parameter

Input/output pins

Note:

For product names, see page 14.

S88 手机说明书

大部分的电子设备几乎都有适当的屏障,保护其不受 RF 能量干扰。但是 没有适当保护装置或故障的一些电子设备,就可能会受到 RF 能量的影 响。

心律调节器

卫生工业制造协会 (Health Industry Manufactures Association) 建议在手 机和心律调节器之间的最小距离是六英吋 (6")。这是为了避免对心律调 节器的潜在干扰。这些建议与无线技术研究会的独立研究以及建议是相 符合的。 装有心律调节器的人请注意:

安全事项 iii

由于标志不清楚,因此人们常常身处充满易燃气体的环境内而不自知, 包括加油站、船舱底层、石油或化学容器周围,使用液化汽 ( 如丙烷或丁 烷 ) 的汽车以及含有化学物质或分子,火药微尘、金属粉末的空气等等。

车上的安全气囊

安全气囊膨胀时会产生强大的力量。切勿将物品 ( 包括车载设备 ) 或者手 持式无线设备放到安全气囊上方的区域内。不正确地安装车载无线设 备,会导致安全气囊膨胀,造成严重的伤害。

注意事项

BenQ-Siemens S88 手机 3.6V, 900/1800/1900 MHz GSM 900: 2W, DCS 1800: 1W, PCS 1900:1W 请将电池拆下后参考手机背面标签 请将电池拆下后参考手机背面标签 中国江苏 符合 GSM 手机标准 请参考使用手册内容 请参考使用手册 , 并咨询零售经销商或致电客服专线 4008-885656 明基电通信息技术有限公司 请参考使用手册的 “安全事项”及 “常见问题与解决 办法”

安全事项

以下这些数据,关系到本款手机的使用效率和安全,请您务必仔 细阅读:

RF 能量对人体的影响

• 减少电磁波影响,请妥善使用。 • SAR 标准值 1.60 W/KG,送检产品 SAR 实测最大值为:GSM900: 0.829

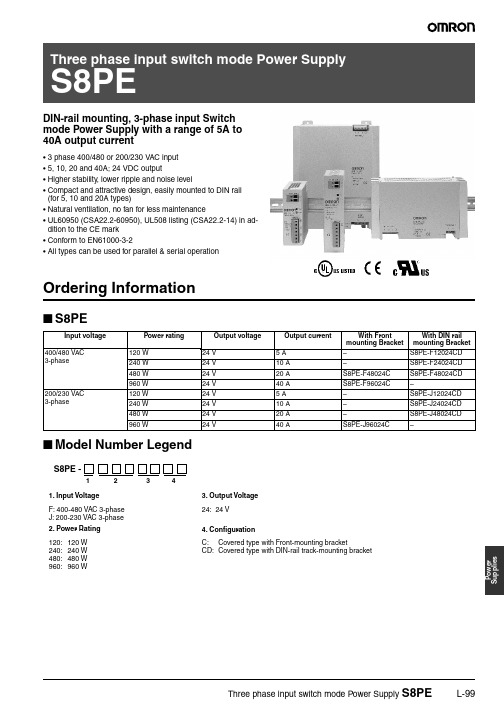

S8PE中文资料

40 A – –

91% 5.0 A

– – 0.89 – – 1.4 mA 75 A

0.1 s 5 ms

– – 13 ms

4.75 kg

L-100 Three phase input switch mode Power Supply S8PE

Protection

5A 85% 84%

–

0.5 A

0.58 0.52

– 0.4 mA 0.5 mA

– 30 A

1.7 s

– 21 ms Leabharlann 5 ms–Others

Parallel operation Serial operation Indicator Heat radiation Ambient temperature (Note 2) Storage temperature Ambient humidity Dielectric strength

2. Power Rating

120: 120 W 240: 240 W 480: 480 W 960: 960 W

3. Output Voltage 24: 24 V

4. Configuration C: Covered type with Front-mounting bracket CD: Covered type with DIN-rail track-mounting bracket

Ordering Information

I S8PE

Input voltage

Power rating

Output voltage

400/480 VAC 3-phase

Ashford e-Spinner Super Jumbo ESPSJ08082019V2 2 说明

INSTRUCTIONSe-Spinner Super JumboESPSJ08082019V22AssemblyYarn GuideOrifice Reducer Bushes 3. Squeeze and slide the stainless-steel yarn guides onto opposite sides of the flyer arms.NOTE: when spinning at higher RPM it may be necessary tosqueeze and rotate whichever yarn guide isn’t being used to achieve perfect balance.4. Apply a drop of oil to the flyer spindle and slide the bobbin on.1. Locate the two Orifice Reducer Bushes into the holes in top of the base.2. Locate the threading hook into the tapered hole in the front. This will only be required when using the Orifice Reducer Bushes.35. Locate the drive band onto the MIDDLE groove in the bobbinControls4Changing the bobbin- Turn the motor off using the ON/OFF switch or foot switch.- Remove the drive band from the motor pulley.- Slide the bobbin off the flyer spindle.- Apply a drop of oil to the spindle and fit anotherbobbin. Locate the drive band onto the MIDDLE groove in the bobbin whorl. Do not use the large groove as this will stretch the drive band.- Apply a drop of oil to the front of the flyer shaft. Position it under the leather brake band and into the front and rear flyer bearings.Orifice Reducer Bushes- Use the large Orifice Reducer Bush to reduce the orifice from 27mm (1⅛”) to 15mm (⅝”) for spinning medium yarns.- Use the small Orifice Reducer Bush to reduce the orifice to 9mm (⅜”) for spinning fine yarns.- Orifice Reducer Bushes help prevent the yarn vibrating. By drafting the yarn at about a 45-degree angle to the orifice the vibration will almost be eliminated.- When not in use store the bushes in the holes in top of the base.- Apply Vaseline to the o-ring to make them easier to Because the e-Spinner Super Jumbo is bobbin lead the yarn needs to be strong enough to turn the flyer. Thus, it requires very little tension on the leather brake band. At full speed the flyer rotates at approx. 500 RPM.1. Tie a piece of medium to thick wool yarn called a leader, approx. 1.5m (5 feet) long to the bobbin. Thread it through the flyer yarn guides with the black inserts on the left-hand side of the flyer and out through the orifice.SpinningAccessories - Available from your local Ashford Dealer.1. Thread the leader through the flyer yarn guide with the black inserts and out through the orifice. Locate 2 bobbins of spun yarn onto the pins of the optional Lazy Kate and tie the two strands of yarn to the leader.2. Check the SPIN/PLY switch is on PLY (up) and the SPEED control is on SLOW. Switch the ON/OFF switch to ON. Gradually turn the SPEED control clockwise until the flyer starts to turn slowly.PlyingMore InformationThe Wheel MagazineAshford’s annual fibrecraft magazine. Spinning, weaving, felting, dyeing and knitting projects, patterns and articles from around the world. To receive the premium version delivered to you, subscribe at:/subscribeHow-to videos on You TubeWatch our how-to videos on You Tube./user/AshfordHandicraftsFacebookJoin us on facebook./ashford.wheels.looms3. Allow the leader and your spun yarn to start feeding in. Use the least amount of leather brake band tension possible. Kate – do we need to say something about keep the yarn under tension in your hand when plying the two yarns together?For further plying information refer to “The Ashford book of Hand Spinning” by Jo Reeve, a 116-page book full of ideas and inspiration for spinners.12V cigarette cordso you can spin away from home in your car, caravan, RV, boat or using a battery pack.BobbinsAshford Country Spinner2 bobbins.Lazy KateHolds 2 Country Spinner2 bobbins.Padded Carry BagStore your e-Spinner Super Jumbo in the convenient padded carry bag. The power pack, foot switch and oil bottle will fit in the handy pockets.。

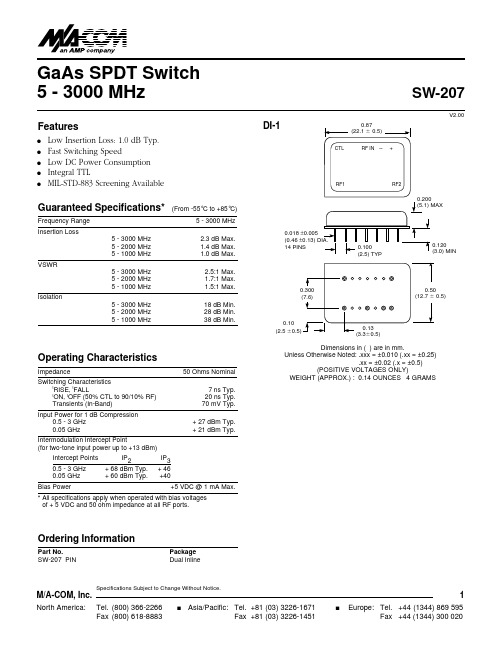

SW-207中文资料

Europe: Tel. +44 (1344) 869 595 Fax +44 (1344) 300 020

Specifications Subject to Change Without Notice.

M/A-COM, Inc.

North America: Tel. (800) 366-2266 Fax (800) 618-8883

s

1

Asia/Pacific: Tel. +81 (03) 3226-1671 Fax +81 (03) 3226-1451

(From -55°C to +85°C) 5 - 3000 MHz 5 - 3000 MHz 5 - 2000 MHz 5 - 1000 MHz 2.3 dB Max. 1.4 dB Max. 1.0 dB Max. 2.5:1 Max. 1.7:1 Max. 1.5:1 Max. 18 dB Min. 28 dB Min. 38 dB Min.

元器件交易网

GaAs SPDT Switch 5 - 3000 MHz

Features

q q q q q

SW-207

V2.00

DI-1

CTL

0.87 (22.1 0.5)

RF IN

Low Insertion Loss: 1.0 dB Typ. Fast Switching Speed Low DC Power Consumption Integral TTL MIL-STD-883 Screening Available

Schematic

Truth Table

Specifications Subject to Change Without Notice.

X5043S8-2.7中文资料

4K X5043/X5045512 x 8 BitCPU Supervisor with 4K SPI EEPROMFEATURES•Selectable time out watchdog timer•Low V CC detection and reset assertion—Five standard reset threshold voltages—Re-program low V CC reset threshold voltage using special programming sequence.—Reset signal valid to V CC = 1V•Long battery life with low power consumption —<50µA max standby current, watchdog on —<10µA max standby current, watchdog off —<2mA max active current during read• 2.7V to 5.5V and 4.5V to 5.5V power supply versions•4Kbits of EEPROM–1M write cycle endurance •Save critical data with Block Lock™ memory —Protect 1/4, 1/2, all or none of EEPROM array •Built-in inadvertent write protection—Write enable latch—Write protect pin• 3.3MHz clock rate•Minimize programming time—16-byte page write mode—Self-timed write cycle—5ms write cycle time (typical)•SPI modes (0,0 & 1,1)•Available packages—8-lead MSOP, 8-lead SOIC, 8-pin PDIP—14-lead TSSOP DESCRIPTIONThese devices combine four popular functions, Power-on Reset Control, Watchdog Timer, Supply Voltage Supervision, and Block Lock Protect Serial EEPROM Memory in one package. This combination lowers system cost, reduces board space requirements, and increases reliability.Applying power to the device activates the power on reset circuit which holds RESET/RESET active for a period of time. This allows the power supply and oscil-lator to stabilize before the processor executes code. The Watchdog Timer provides an independent protec-tion mechanism for microcontrollers. When the micro-controller fails to restart a timer within a selectable time out interval, the device activates the RESET/ RESET signal. The user selects the interval from three preset values. Once selected, the interval does not change, even after cycling the power.The device’s low V CC detection circuitry protects the user’s system from low voltage conditions, resetting the system when V CC falls below the minimum V CC trip point. RESET/RESET is asserted until V CC returns to proper operating level and stabilizes. Five industry standard V TRIP thresholds are available, however, Xicor’s unique circuits allow the threshold to be repro-grammed to meet custom requirements or to fine-tune the threshold for applications requiring higher precision.BLOCK DIAGRAMSISOSCK CS/WDIV CC RESET/RESETWPX5043 = RESETX5045 = RESET 元器件交易网X5043/X5045The memory portion of the device is a CMOS Serial EEPROM array with Xicor’s block lock protection. The array is internally organized as x 8. The device features a Serial Peripheral Interface (SPI) and software proto-col allowing operation on a simple four-wire bus.The device utilizes Xicor’s proprietary Direct Write™cell, providing a minimum endurance of 1,000,000 cycles and a minimum data retention of 100 years.PIN CONFIGURATIONPIN DESCRIPTIONSSerial Output (SO)SO is a push/pull serial data output pin. During a read cycle, data is shifted out on this pin. Data is clocked out by the falling edge of the serial clock.Serial Input (SI)SI is the serial data input pin. All opcodes, byte addresses, and data to be written to the memory are input on this pin. Data is latched by the rising edge of the serial clock.Serial Clock (SCK)The Serial Clock controls the serial bus timing for data input and output. Opcodes, addresses, or data present on the SI pin is latched on the rising edge of the clock input, while data on the SO pin changes after the fall-ing edge of the clock input.Chip Select (CS)When CS is high, the X5043/45 is deselected and the SO output pin is at high impedance and, unless an internal write operation is underway, the X5043/45 will be in the standby power mode. CS low enables the X5043/45, placing it in the active power mode. It should be noted that after power-up, a high to low transition on CS is required prior to the start of any operation.Write Protect (WP)When WP is low, nonvolatile writes to the X5043/45 are disabled, but the part otherwise functions normally. When WP is held high, all functions, including non vol-atile writes operate normally. WP going low while CS is still low will interrupt a write to the X5043/45. If the internal write cycle has already been initiated, WP going low will have no affect on a write.Reset (RESET, RESET)X5043/45, RESET/RESET is an active low/HIGH, open drain output which goes active whenever V CC falls below the minimum V CC sense level. It will remain active until V CC rises above the minimum V CC sense level for 200ms. RESET/RESET also goes active if the Watchdog timer is enabled and CS remains either high or low longer than the Watchdog time out period. A fall-ing edge of CS will reset the watchdog timer.PIN NAMESSymbol DescriptionCS Chip Select InputSO Serial OutputSI Serial InputSCK Serial Clock InputWP Write Protect InputV SS GroundV CC Supply VoltageRESET/RESET Reset Output 元器件交易网X5043/X5045PRINCIPLES OF OPERATIONPower On ResetApplication of power to the X5043/X5045 activates a Power On Reset Circuit. This circuit pulls the RESET/ RESET pin active. RESET/RESET prevents the sys-tem microprocessor from starting to operate with insuf-ficient voltage or prior to stabilization of the oscillator. When V CC exceeds the device V TRIP value for 200ms (nominal) the circuit releases RESET/RESET, allowing the processor to begin executing code.Low Voltage MonitoringDuring operation, the X5043/X5045 monitors the V CC level and asserts RESET/RESET if supply voltage falls below a preset minimum V TRIP. The RESET/RESET signal prevents the microprocessor from operating in a power fail or brownout condition. The RESET/RESET signal remains active until the voltage drops below 1V. It also remains active until V CC returns and exceeds V TRIP for 200ms.Watchdog TimerThe Watchdog Timer circuit monitors the microproces-sor activity by monitoring the WDI input. The micropro-cessor must toggle the CS/WDI pin periodically to prevent an active RESET/RESET signal. The CS/WDI pin must be toggled from HIGH to LOW prior to the expiration of the watchdog time out period. The state of two nonvolatile control bits in the Status Register determines the watchdog timer period. The micropro-cessor can change these watchdog bits. With no microprocessor action, the watchdog timer control bits remain unchanged, even during total power failure.V CC Threshold Reset ProcedureThe X5043/X5045 is shipped with a standard V CC threshold (V TRIP) voltage. This value will not change over normal operating and storage conditions. How-ever, in applications where the standard V TRIP is not exactly right, or if higher precision is needed in the V TRIP value, the X5043/X5045 threshold may be adjusted. The procedure is described below, and uses the application of a high voltage control signal.Setting the V TRIP VoltageThis procedure is used to set the V TRIP to a higher volt-age value. For example, if the current V TRIP is 4.4V and the new V TRIP is 4.6V, this procedure will directly make the change. If the new setting is to be lower than the current setting, then it is necessary to reset the trip point before setting the new value.T o set the new V TRIP voltage, apply the desired V TRIP threshold voltage to the V CC pin and tie the WP pin to the programming voltage V P. Then send a WREN com-mand, followed by a write of Data 00h to address 01h. CS going HIGH on the write operation initiates the V TRIP programming sequence. Bring WP LOW to com-plete the operation.Note: This operation also writes 00h to array address 01h.Figure 1. Set V TRIP Level Sequence (V CC = desired V TRIP value.)元器件交易网X5043/X5045Resetting the V TRIP VoltageThis procedure is used to set the V TRIP to a “native”voltage level. For example, if the current V TRIP is 4.4V and the new V TRIP must be 4.0V, then the V TRIP must be reset. When V TRIP is reset, the new V TRIP is some-thing less than 1.7V. This procedure must be used to set the voltage to a lower value.T o reset the V TRIP voltage, apply at least 3V to the V CC pin and tie the WP pin to the programming voltage V P. Then send a WREN command, followed by a write of Data 00h to address 03h. CS going HIGH on the write operation initiates the V TRIP programming sequence. Bring WP LOW to complete the operation.Note: This operation also writes 00h to array address 03h.Figure 2. Reset V TRIP Level Sequence (V CC > 3V. WP = 15–18V)Figure 3. Sample V TRIP Reset Circuit元器件交易网X5043/X5045Figure 4. V TRIP Programming SequenceSPI Serial MemoryThe memory portion of the device is a CMOS Serial EEPROM array with Xicor’s block lock protection. The array is internally organized as x8 bits. The device fea-tures a Serial Peripheral Interface (SPI) and software protocol allowing operation on a simple four-wire bus. The device utilizes Xicor’s proprietary Direct Write ™ cell, providing a minimum endurance of 1,000,000cycles and a minimum data retention of 100 years.The device is designed to interface directly with the synchronous Serial Peripheral Interface (SPI) of many popular microcontroller families.The device contains an 8-bit instruction register that controls the operation of the device. The instruction code is written to the device via the SI input. There are two write operations that requires only the instruction byte. There are two read operations that use the instruction byte to initiate the output of data. The remainder of the operations require an instruction byte,an 8-bit address, then data bytes. All instruction,address and data bits are clocked by the SCK input. All instructions (T able 1), addresses and data are trans-ferred MSB first.Clock and Data TimingData input on the SI line is latched on the first rising edge of SCK after CS goes LOW. Data is output on the SO line by the falling edge of SCK. SCK is static,allowing the user to stop the clock and then start it again to resume operations where left off. CS must be LOW during the entire operation.Table 1. Instruction Set Note:*Instructions are shown MSB in leftmost position. Instructions are transferred MSB first.Instruction NameInstruction Format*OperationWREN 0000 0110Set the Write Enable Latch (Enable Write Operations)WRDI 0000 0100Reset the Write Enable Latch (Disable Write Operations)RSDR 0000 0101Read Status RegisterWRSR 0000 0001Write Status Register (Watchdog and Block Lock)READ 0000 A 8011Read Data from Memory Array Beginning at Selected Address WRITE0000 A 8010Write Data to Memory Array Beginning at Selected Address (1 to 16 bytes)元器件交易网Write Enable LatchThe device contains a Write Enable Latch. This latch must be SET before a Write Operation is initiated. The WREN instruction will set the latch and the WRDI instruction will reset the latch (Figure 3). This latch is automatically reset upon a power-up condition and after the completion of a valid byte, page, or status register write cycle. The latch is also reset if WP is brought LOW.When issuing a WREN, WRDI or RDSR commands, it is not necessary to send a byte address or data.Figure 5. Write Enable/Disable Latch SequenceStatus RegisterThe Status Register contains four nonvolatile control bits and two volatile status bits. The control bits set the operation of the watchdog timer and the memory block lock protection. The Status Register is formatted as shown in “Status Register”.Status Register: (Default = 30H)The Write-In-Progress (WIP) bit is a volatile, read only bit and indicates whether the device is busy with an internal nonvolatile write operation. The WIP bit is read using the RDSR instruction. When set to a “1”, a non-volatile write operation is in progress. When set to a “0”, no write is in progress.The Write Enable Latch (WEL) bit indicates the status of the “write enable” latch. When WEL = 1, the latch is set and when WEL = 0 the latch is reset. The WEL bit is a volatile, read only bit. The WREN instruction sets the WEL bit and the WRDS instruction resets the WEL bit.The block lock bits, BL0 and BL1, set the level of block lock protection. These nonvolatile bits are programmed using the WRSR instruction and allow the user to pro-tect one quarter, one half, all or none of the EEPROM array. Any portion of the array that is block lock pro-tected can be read but not written. It will remain pro-tected until the BL bits are altered to disable block lock protection of that portion of memory.The Watchdog Timer bits, WD0 and WD1, select the Watchdog Time-out Period. These nonvolatile bits are programmed with the WRSR instruction.Read Status RegisterT o read the Status Register, pull CS low to select the device, then send the 8-bit RDSR instruction. Then the contents of the Status Register are shifted out on the SO line, clocked by CLK. Refer to the Read Status Register Sequence (Figure 6). The Status Register may be read at any time, even during a Write Cycle. Write Status RegisterPrior to any attempt to write data into the status regis-ter, the “Write Enable” Latch (WEL) must be set by issuing the WREN instruction (Figure 5). First pull CS LOW, then clock the WREN instruction into the device and pull CS HIGH. Then bring CS LOW again and enter the WRSR instruction followed by 8 bits of data.These 8 bits of data correspond to the contents of the status register. The operation ends with CS going HIGH. If CS does not go HIGH between WREN and WRSR, the WRSR instruction is ignored.7654321WD1WD0BL1BL0WELWIP1234567CSSI SCKHigh ImpedanceSOStatus Reg Bits Array Addresses ProtectedBL1BL0X5043/X504500None 01$180–$1FF 10$100–$1FF 11$000–$1FFStatus Register Bits Watchdog Time Out(Typical)WD1WD000 1.4 seconds 01600 milliseconds 10200 milliseconds 11disabled (factory default)Table 2. Device Protect Matrix Figure 6. Read Status Register SequenceFigure 7. Write Status Register SequenceWREN CMD (WEL)Device Pin (WP)Memory BlockStatus Register Protected AreaUnprotected Area(BL0, BL1, WD0, WD1)0x Protected Protected Protected x 0Protected Protected Protected 11ProtectedWritableWritableRead Memory ArrayWhen reading from the EEPROM memory array, CS is first pulled low to select the device. The 8-bit READ instruction is transmitted to the device, followed by the 8-bit address. Bit 3 of the READ instruction selects the upper or lower half of the device. After the READ opcode and address are sent, the data stored in the memory at the selected address is shifted out on the SO line. The data stored in memory at the nextaddress can be read sequentially by continuing to pro-vide clock pulses. The address is automatically incre-mented to the next higher address after each byte of data is shifted out. When the highest address is reached, the address counter rolls over to address $000 allowing the read cycle to be continued indefi-nitely. The read operation is terminated by taking CS high. Refer to the Read EEPROM Array Sequence (Figure 8).Figure 8. Read EEPROM Array SequenceWrite Memory ArrayPrior to any attempt to write data into the memory array, the “Write Enable” Latch (WEL) must be set by issuing the WREN instruction (Figure 5). First pull CS LOW, then clock the WREN instruction into the device and pull CS HIGH. Then bring CS LOW again and enter the WRITE instruction followed by the 8-bit address and then the data to be written. Bit 3 of the WRITE instruction contains address bit A8, which selects the upper or lower half of the array. If CS does not go HIGH between WREN and WRITE, the WRITE instruction is ignored.The WRITE operation requires at least 16 clocks. CS must go low and remain low for the duration of the operation. The host may continue to write up to 16 bytes of data. The only restriction is that the 16 bytes must reside within the same page. A page address begins with address [x xxxx 0000] and ends with [x xxxx 1111]. If the byte address reaches the last byte on the page and the clock continues, the counter will roll back to the first address of the page and overwrite any data that has been previously written.For the write operation (byte or page write) to be com-pleted, CS must be brought HIGH after bit 0 of the last complete data byte to be written is clocked in. If it is brought HIGH at any other time, the write operation will not be completed (Figure 9).While the write is in progress following a status register or memory array write sequence, the Status Register may be read to check the WIP bit. WIP is HIGH while the nonvolatile write is in progress.Figure 9. Write Memory SequenceOPERATIONAL NOTESThe device powers-up in the following state:–The device is in the low power standby state.–A HIGH to LOW transition on CS is required to enter an active state and receive an instruction.–SO pin is high impedance.–The Write Enable Latch is reset.–The Flag Bit is reset.–Reset Signal is active for t PURST.Data ProtectionThe following circuitry has been included to prevent inadvertent writes:–A WREN instruction must be issued to set the Write Enable Latch.–CS must come HIGH at the proper clock count in order to start a nonvolatile write cycle.–Block Protect bits provide additional level of write protection for the memory array.–The WP pin LOW blocks nonvolatile write operations.ABSOLUTE MAXIMUM RATINGST emperature under bias....................–65°C to +135°C Storage temperature ........................–65°C to +150°C Voltage on any pin withrespect to V SS ......................................–1.0V to +7V D.C. output current...............................................5mA Lead temperature (soldering, 10 seconds).........300°CCOMMENTStresses above those listed under “Absolute Maximum Ratings” may cause permanent damage to the device.This is a stress rating only; functional operation of the device (at these or any other conditions above those listed in the operational sections of this specification) is not implied. Exposure to absolute maximum rating con-ditions for extended periods may affect device reliability.RECOMMENDED OPERATING CONDITIONS TemperatureMin.Max.Commercial 0°C 70°C Industrial–40°C+85°COptionSupply Voltage Limits-2.7, -2.7A 2.7V to 5.5V Blank, -4.5A4.5V to5.5VD.C. OPERATING CHARACTERISTICS (Over the recommended operating conditions unless otherwise specified.)CAPACITANCE T A = +25°C, f = 1MHz, V CC = 5V Notes:(1)V IL min. and V IH max. are for reference only and are not tested.(2)This parameter is periodically sampled and not 100% tested.(3)SCK frequency measured from V CC x 0.1/V CC x 0.9SymbolParameterLimitsUnitTest Conditions/CommentsMin.Typ.(2)Max.I CC1V CC Write Current (Active)3mA SCK = 3.3MHz (3); SO, RESET, RESET = OpenI CC2V CC Read Current (Active)2mA SCK = 3.3MHz (3); SI = V SS , RESET, RESET = OpenI SB1V CC Standby Current WDT = OFF10µA CS = V CC , SCK, SI = V SS , V CC = 5.5VI SB2V CC Standby Current WDT = ON50µA CS = V CC , SCK, SI = V SS , V CC = 5.5VI LI Input Leakage Current 0.110µA SCK, SI, WP = V SS to V CC I LO Output Leakage Current 0.110µA SO, RESET, RESET = V SS to V CC V IL (1)Input LOW Voltage –0.5V CC x 0.3V SCK, SI, WP, CS V IH (1)Input HIGH Voltage V CC x 0.7V CC + 0.5V SCK, SI, WP, CSV OL Output LOW Voltage (SO)0.4V I OL = 2mA @ V CC = 2.7V I OL = 0.5mA @ V CC = 1.8V V OH1Output HIGH Voltage (SO)V CC – 0.8 V V CC > 3.3V, I OH = –1.0mA V OH2Output HIGH Voltage (SO)V CC – 0.4V 2V < V CC ≤ 3.3V, I OH = –0.4mA V OH3Output HIGH Voltage (SO)V CC – 0.2V V CC ≤ 2V, I OH = –0.25mA V OLRSOutput LOW Voltage (RESET, RESET)0.4VI OL = 1mASymbolTestMax.UnitConditionsC OUT (2)Output Capacitance (SO, RESET, RESET)8pF V OUT = 0V C IN (2)Input Capacitance (SCK, SI, CS, WP)6pFV IN = 0VEquivalent A.C. Load Circuit at 5V V CC A.C. Test ConditionsInput pulse levels V CC x 0.1 to V CC x 0.9Input rise and fall times10nsInput and output timing level V CC x0.5A.C. CHARACTERISTICS (Over recommended operating conditions, unless otherwise specified)Data Input TimingData Output TimingNotes:(3)This parameter is periodically sampled and not 100% tested.(4)t WC is the time from the rising edge of CS after a valid write sequence has been sent to the end of the self-timed internal nonvolatilewrite cycle.Symbol Parameter2.7V–5.5VUnitMin.Max.f SCK Clock Frequency0 3.3MHzt CYC Cycle Time300ns t LEAD CS Lead Time150ns t LAG CS Lag Time150ns t WH Clock HIGH Time130ns t WL Clock LOW Time130ns t SU Data Setup Time30ns t H Data Hold Time30ns t RI(3)Input Rise Time2µs t FI(3)Input Fall Time2µs t CS CS Deselect Time100ns t WC(4)Write Cycle Time10msSymbol Parameter2.7–5.5VUnitMin.Max.f SCK Clock Frequency0 3.3MHzt DIS Output Disable Time150ns t V Output Valid from Clock Low120ns t HO Output Hold Time0ns t RO(3)Output Rise Time50ns t FO(3)Output Fall Time50nsSerial Output TimingSerial Input TimingSYMBOL TABLEPower-Up and Power-Down TimingRESET Output TimingV TRIP Programming Timing DiagramV TRIP Programming ParametersParameter Description Min Max Unit t VPS V TRIP Program Enable Voltage Setup time1µs t VPH V TRIP Program Enable Voltage Hold time1µs t PCS V TRIP Programming CS inactive time1µs t TSU V TRIP Setup time1µs t THD V TRIP Hold (stable) time10ms t WC V TRIP Write Cycle Time10ms t VPO V TRIP Program Enable Voltage Off time (Between successive adjustments)0µs t RP V TRIP Program Recovery Period (Between successive adjustments)10ms V P Programming Voltage1518V V TRAN V TRIP Programmed Voltage Range 1.7 5.0V V ta1Initial V TRIP Program Voltage accuracy (V CC applied–V TRIP) (Programmedat 25°C.)-0.1+0.4VV ta2Subsequent V TRIP Program Voltage accuracy [(V CC applied–V ta1)–V TRIP.Programmed at 25°C.)-25+25mVV tr V TRIP Program Voltage repeatability (Successive program operations.Programmed at 25°C.)-25+25mV V tv V TRIP Program variation after programming (0–75°C). (Programmed at 25°C.)-25+25mV V TRIP programming parameters are periodically sampled and are not 100% tested.PACKAGING INFORMATION8-Lead Miniature Small Outline Gull Wing Package Type M0.007 (0.18)0.005 (0.13)NOTE:1.ALL DIMENSIONS IN INCHES AND (MILLIMETERS)PACKAGING INFORMATIONNOTE:1.ALL DIMENSIONS IN INCHES (IN PARENTHESES IN MILLIMETERS)2.PACKAGE DIMENSIONS EXCLUDE MOLDING FLASH8-Lead Plastic Dual In-Line Package Type PMax.PACKAGING INFORMATION8-Lead Plastic Small Outline Gull Wing Package Type SNOTE: ALL DIMENSIONS IN INCHES (IN PARENTHESES IN MILLIMETERS)PACKAGING INFORMATIONNOTE: ALL DIMENSIONS IN INCHES (IN PARENTHESES IN MILLIMETERS)14-Lead Plastic, TSSOP, Package Type V0° - 8°Ordering InformationV CC Range V TRIPRange PackageOperatingTemperature RangePart Number RESET(Active LOW)Part Number RESET(Active HIGH)4.5-5.5V 4.5-4.758-Pin PDIP-40°C–85°C X5043PI-4.5A X5045PI-4.5A8L SOIC-40°C–85°C X5043S8I-4.5A X5045S8I-4.5A8L MSOP-40°C–85°C X5043M8I-4.5A X5045M8I-4.5A14L TSSOP-40°C–85°C X5043V14I-4.5A X5045V14I-4.5A4.25-4.58-Pin PDIP-40°C–85°C X5043PI X5045PI8L SOIC0°C–70°C X5043S8X5045S8-40°C–85°C X5043S8I X5045S8I8L MSOP-40°C–85°C X5043M8I X5045M8I14L TSSOP-40°C–85°C X5043V14I X5045V14I 2.7-5.5V 2.85-3.08L PDIP-40°C–85°C X5043PI-2.7A X5045PI-2.7A8L SOIC-40°C–85°C X5043S8I-2.7A X5045S8I-2.7A8L MSOP-40°C–85°C X5043M8I-2.7A X5045M8I-2.7A14L TSSOP-40°C–85°C X5043V14I-2.7A X5045V14I-2.7A2.55-2.78-Pin PDIP-40°C–85°C X5043PI-2.7X5045PI-2.78L SOIC0°C–70°C X5043S8-2.7X5045S8-2.7-40°C–85°C X5043S8I-2.7X5045S8I-2.78L MSOP-40°C–85°C X5043M8I-2.7X5045M8I-2.714L TSSOP-40°C–85°C X5043V14I-2.7X5045V14I-2.7©Xicor, Inc. 2001 Patents PendingLIMITED WARRANTY Devices sold by Xicor, Inc. are covered by the warranty and patent indemnification provisions appearing in its T erms of Sale only. Xicor, Inc. makes no warranty,express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described devices from patent infringement.Xicor, Inc. makes no warranty of merchantability or fitness for any purpose. Xicor, Inc. reserves the right to discontinue production and change specifications and prices at any time and without notice.Xicor, Inc. assumes no responsibility for the use of any circuitry other than circuitry embodied in a Xicor, Inc. product. No other circuits, patents, or licenses are implied.COPYRIGHTS AND TRADEMARKSXicor, Inc., the Xicor logo, E 2POT, XDCP, XBGA, AUTOSTORE, Direct Write cell, Concurrent Read-Write, PASS, MPS, PushPOT, Block Lock, IdentiPROM,E 2KEY, X24C16, SecureFlash, and SerialFlash are all trademarks or registered trademarks of Xicor, Inc. All other brand and product names mentioned herein are used for identification purposes only, and are trademarks or registered trademarks of their respective holders. U.S. PATENTSXicor products are covered by one or more of the following U.S. Patents: 4,326,134; 4,393,481; 4,404,475; 4,450,402; 4,486,769; 4,488,060; 4,520,461; 4,533,846;4,599,706; 4,617,652; 4,668,932; 4,752,912; 4,829,482; 4,874,967; 4,883,976; 4,980,859; 5,012,132; 5,003,197; 5,023,694; 5,084,667; 5,153,880; 5,153,691;5,161,137; 5,219,774; 5,270,927; 5,324,676; 5,434,396; 5,544,103; 5,587,573; 5,835,409; 5,977,585. Foreign patents and additional patents pending.LIFE RELATED POLICYIn situations where semiconductor component failure may endanger life, system designers using this product should design the system with appropriate error detection and correction, redundancy and back-up features to prevent such an occurrence.Xicor’s products are not authorized for use in critical components in life support devices or systems.1.Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure toperform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the lifesupport device or system, or to affect its safety or effectiveness.Part Mark Information Blank = 8-Lead SOIC P= 8 Pin Plastic DIPBlank = No suffix, 0°C to +70°C I = No Suffix; –40°C to +85°C A = -4,5A; 0°C to +70°C,IA = -4.5A; –40°C to +85°C F = -2.7; 0°C to +70°C G = -2.7; –40°C to +85°C FA = -2.7A; 0°C to +70°C GA = -2.7A; –40°C to +85°CXX5043/45XAEP/AEY = No Suffix; –40°C to +85°C AEN/AEW = -4.5A; –40°C to +85°C AET/AFC = -2.7; –40°C to +85°C AER/AFA = -2.7A; –40°C to +85°CX5043/X5045YWW XXXPDIP/SOIC MSOP V = 14 Lead TSSOPBlank = 5V ±10%, 0°C to +70°C, V TRIP = 4.25-4.5AL = 5V±10%, 0°C to +70°C, V TRIP = 4.5-4.75I = 5V ±10%, –40°C to +85°C, V TRIP = 4.25-4.5AM = 5V ±10%, –40°C to +85°C, V TRIP = 4.5-4.75F = 2.7V to 5.5V , 0°C to +70°C, V TRIP = 2.55-2.7AN = 2.7V to 5.5V , 0°C to +70°C, V TRIP = 2.85-3.0G = 2.7V to 5.5V , –40°C to +85°C, V TRIP = 2.55-2.7AP = 2.7V to 5.5V , –40°C to +85°C, V TRIP = 2.85-3.0WX5043/45XTSSOP。

s88_精品文档

s88IntroductionThe s88 documentation provides an overview and detailed information about s88, its features, and how to use it effectively. This document is divided into several sections to provide a structured and comprehensive understanding of s88.Table of Contents1.What is s88?2.Key Features3.Getting Startedage5.Best Practices6.TroubleshootingWhat is s88?s88 is a software framework designed to streamline and simplify the development of software applications. It provides a set of tools, libraries, and best practices that enable developers to build robust and scalable applications quickly. s88 helps developers focus on business logic rather than dealing with low-level implementation details.Key Features•Easy to use: s88 offers a simple and intuitive interface that allows developers to quickly get started with their application development.•Scalable: s88 is designed to handle applications of any size, from small projects to large-scale enterprise applications.•Modular architecture: s88 promotes a modular architecture that allows developers to easily extend and customize the functionality of theirapplications.•Integration: s88 provides seamless integration with other popular frameworks and libraries, making it easy to incorporate existing solutions into your application.•Performance: s88 is optimized for performance, ensuring that your application runs efficiently and delivers a smooth user experience.Getting StartedTo get started with s88, follow these steps:1.Install s88: Use the package manager of your choice to install thelatest version of s88. For example, if you are using npm, run npm install s88.2.Set up your development environment: Configure your developmentenvironment to work with s88. This may involve setting up dependencies,configuring build tools, etc.3.Create a new project: Create a new directory for your project andinitialize it with s88 using the command s88 init.4.Start building: Use the features and tools provided by s88 to startbuilding your application.Usages88 can be used in a wide range of scenarios, including:•Web development: Use s88 to build web applications, RESTful APIs, or server-side rendered applications.•Mobile app development: s88 provides support for building mobile applications using popular frameworks such as React Native.•Microservices: Build scalable and loosely coupled microservices using s88’s modular architecture and integration features.Best PracticesTo make the most out of s88, consider the following best practices:e s88’s modular architecture to break your application into smaller,reusable components.2.Follow industry best practices for code organization, such asseparating concerns and keeping your codebase clean and maintainable.3.Leverage the integration capabilities of s88 to incorporate other tools,libraries, and frameworks into your application.4.Regularly update to the latest version of s88 to benefit from bug fixes,performance improvements, and new features.5.Familiarize yourself with the s88 documentation and communityresources to get the most out of the framework.TroubleshootingIf you encounter any issues or have questions while using s88, consider the following troubleshooting steps:1.Check the s88 documentation and resources for answers to commonquestions and known issues.2.Search the s88 community forums and online developer communitiesfor similar issues and solutions.3.If the issue persists, consider opening a bug report or asking for helpin the s88 community channels.ConclusionIn conclusion, s88 provides a powerful framework for developing robust and scalable applications. With its easy-to-use interface, modular architecture, and seamless integration capabilities, s88 empowers developers to focus on building innovative solutions rather than getting stuck in implementation details. Start exploring s88 today and unlock its full potential for your next project.。

ISO-2768-1-1989中文版

国际标准 ISO2768-1初版1989-11-15常规公差——第一部分:无单独公差标示的线尺度、角度公差参考号ISO2768-1:1989(E)ISO 2768-1:1989(E)前言ISO(国际标准化组织)是世界范围内国家标准实体(ISO成员)的联合体。

通常由ISO技术委员会制定国际标准。

但是,只要对该组织建立的某个主题感兴趣,任何成员都可以在这方面充当委员会的代表。

所有与ISO关联的国际组织,政府以及非政府机构,都参加此项工作。

ISO 在电工标准事务上,与国际电工委员会紧密一致。

由技术委员会起草的国际标准草稿,在ISO将其作为国际标准正式文件之前,需要分发给各成员实体进行核准。

标准的核准需要经过ISO的程序进行,即需要所有成员的75%赞成才可获得通过。

ISO2768-2由技术委员会ISO/TC 3(误差与配合)制定。

ISO2678-1初版与ISO2678-1:1989一起取代了ISO2768:1973。

题为常规公差的ISO2768包括以下部分:第一部分:无单独公差标示的线尺度、角度公差第二部分:无单独公差标示的部件几何公差ISO2768中附录A与B仅供参考。

简介所有部件部分的零部件都有自己的尺寸和几何形状。

如果尺寸或几何特性(形状,方向与位置)出现偏差,超出了该部分要求的最低值,则破坏了该部分的功能。

图纸上的公差规定应当完整,以确保控制零部件的尺寸与几何因素,也就是,不应该留给车间或检验部人员来判断。

使用尺寸与几何常规公差,减轻了满足该必要条件的任务。

国际标准 ISO2768-1:1989(E)常规公差——第一部分:无单独公差标示的线尺度、角度公差1 应用范围ISO2768的这部分意在简化图纸标示,规范常规线尺度、角度公差,从而使图纸上所有零部件不再出现单独不同的公差。

此处分四类进行公差规定。

注1:对常规线尺度、角度公差规定的方案,将在附件A中阐述。

该部分主要适用于金属材料切除后生产的或由金属板加工的零部件。

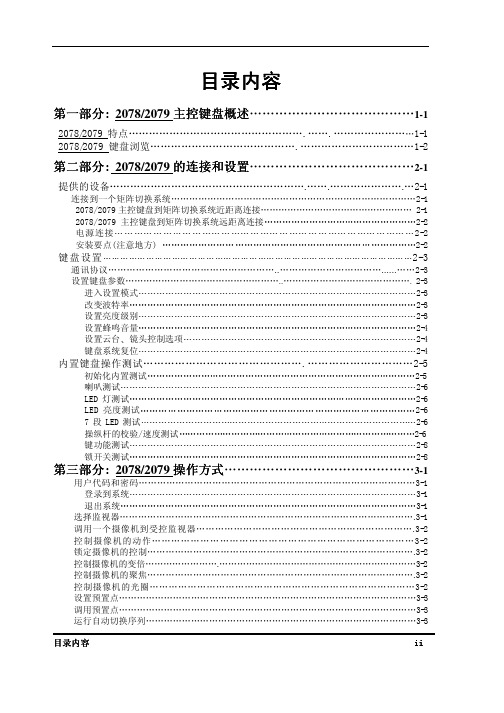

2078 2079全兼容中文版说明书

设防监视器……………………………………………………………………………………….4-2 撤防监视器……………………………………………………………………………………….4-2

提供的设备………………………………………………….…….………………….…2-1

连接到一个矩阵切换系统………………………………………………………………………2-1

2078/2079 主控键盘到矩阵切换系统近距离连接…………………………………………… 2-1

2078/2079 主控键盘到矩阵切换系统远距离连接

控制键可控制变倍,聚焦,和光圈调节 ! 队列功能—可对摄像机自动切换队列进行编程 运行 和控制 ! 同步队列功能—允许编程和同时调多个摄像机场景到一组监视器上显示 ! 报警功能—可对监视器进行报警设防 撤防和确认 ! 云台预置功能—允许编程和调用摄像机预置点 ! 可选择的波特率—1200,2400,4800,9600,19200,38400bps(出厂设置为 1200) ! 可选择的 LED 亮度—允许八个不同的亮度等级 ! 可选择的蜂鸣音量—允许八个不同的音量等级 ! 自动聚焦/自动调节光圈能力—支持智能球的自动聚焦和自动光圈功能 ! 摄像机锁定—防止其他用户去操作其它用户正在控制的摄像机

在菜单模式下用 2078/2079………………………………………………………4-3

附录 A:规范…………………………………………………………A-1

附录 B:故障释疑……………………………………………………B-1

附录 C:典型系统连接………………………………………………C-1

X25168S8-2.7资料

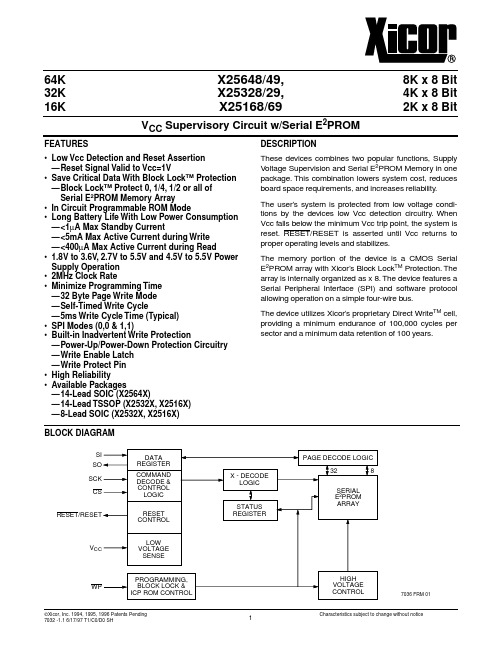

64K 32K 16KX25648/49,X25328/29,X25168/698K x 8 Bit4K x 8 Bit2K x 8 Bit V CC Supervisory Circuit w/Serial E2PROMFEATURES•Low Vcc Detection and Reset Assertion—Reset Signal Valid to Vcc=1V•Save Critical Data With Block Lock TM Protection —Block Lock TM Protect 0, 1/4, 1/2 or all of Serial E2PROM Memory Array•In Circuit Programmable ROM Mode•Long Battery Life With Low Power Consumption —<1µA Max Standby Current—<5mA Max Active Current during Write—<400µA Max Active Current during Read• 1.8V to 3.6V, 2.7V to 5.5V and 4.5V to 5.5V Power Supply Operation•2MHz Clock Rate•Minimize Programming Time—32 Byte Page Write Mode—Self-Timed Write Cycle—5ms Write Cycle Time (Typical)•SPI Modes (0,0 & 1,1)•Built-in Inadvertent Write Protection—Power-Up/Power-Down Protection Circuitry —Write Enable Latch—Write Protect Pin•High Reliability•Available Packages—14-Lead SOIC (X2564X)—14-Lead TSSOP (X2532X, X2516X)—8-Lead SOIC (X2532X, X2516X)DESCRIPTIONThese devices combines two popular functions, Supply Voltage Supervision and Serial E2PROM Memory in one package. This combination lowers system cost, reduces board space requirements, and increases reliability.The user’s system is protected from low voltage condi-tions by the devices low Vcc detection circuitry. When Vcc falls below the minimum Vcc trip point, the system is reset. RESET/RESET is asserted until Vcc returns to proper operating levels and stabilizes.The memory portion of the device is a CMOS Serial E2PROM array with Xicor’s Block Lock TM Protection. The array is internally organized as x 8. The device features a Serial Peripheral Interface (SPI) and software protocol allowing operation on a simple four-wire bus.The device utilizes Xicor’s proprietary Direct Write TM cell, providing a minimum endurance of 100,000 cycles per sector and a minimum data retention of 100 years.BLOCK DIAGRAMRESET/RESET7036 FRM 01元器件交易网X25648/49, X25328/29, X25168/69PIN DESCRIPTIONSSerial Output (SO)SO is a push/pull serial data output pin. During a read cycle, data is shifted out on this pin. Data is clocked out by the falling edge of the serial clock.Serial Input (SI)SI is a serial data input pin. All opcodes, byte addresses, and data to be written to the memory are input on this pin. Data is latched by the rising edge of the serial clock. Serial Clock (SCK)The Serial Clock controls the serial bus timing for data input and output. Opcodes, addresses, or data present on the SI pin are latched on the rising edge of the clock input, while data on the SO pin change after the falling edge of the clock input.Chip Select (CS)When CS is HIGH, the device is deselected and the SO output pin is at high impedance and unless a nonvolatile write cycle is underway, the device will be in the standby power mode. CS LOW enables the device, placing it in the active power mode. It should be noted that after power-up, a HIGH to LOW transition on CS is required prior to the start of any operation.Write Protect (WP)When WP is low and the nonvolatile bit WPEN is “1”, nonvolatile writes to the device Status Register are disabled, but the part otherwise functions normally. When WP is held high, all functions, including nonvolatile writes to the Status Register operate normally. If an internal Status Register Write Cycle has already been initiated, WP going low while WPEN is a “1” will have no effect on this write. Subsequent write attempts to the Status Register under these conditions will be disabled.The WP pin function is blocked when the WPEN bit in the Status Register is “0”. This allows the user to install the device in a system with WP pin grounded and still be able to program the Status Register. The WP pin functions will be enabled when the WPEN bit is set to a “1”.Reset (RESET/RESET)RESET/RESET is an active LOW/HIGH, open drain out-put which goes active whenever Vcc falls below the mini-mum Vcc sense level. It will remain active until Vcc rises above the minimum Vcc sense level for 200ms. PIN CONFIGURATIONPIN NAMES7036 FRM T01 Symbol DescriptionCS Chip Select InputSO Serial OutputSI Serial InputSCK Serial Clock InputWP Program Protect InputV SS GroundV CC Supply VoltageRESET/RESET Reset Output元器件交易网X25648/49, X25328/29, X25168/69PRINCIPLES OF OPERATIONThe device is designed to interface directly with the syn-chronous Serial Peripheral Interface (SPI) of many popu-lar microcontroller families.The device monitors V CC and asserts RESET/RESEToutput if the supply voltage falls below a preset minimum V trip. The device contains an 8-bit instruction register. It is accessed via the SI input, with data being clocked in on the rising edge of SCK. CS must be LOW during the entire operation.All instructions (T able 1), addresses and data are trans-ferred MSB first. Data input on the SI line is latched on the first rising edge of SCK after CS goes LOW. Data is out-put on the SO line by the falling edge of SCK. SCK is static, allowing the user to stop the clock and then start it again to resume operations where left off.Write Enable LatchThe device contains a Write Enable Latch. This latch must be SET before a Write Operation is initiated. The WREN instruction will set the latch and the WRDI instruction will reset the latch (Figure 3). This latch is automatically reset upon a power-up condition and after the completion of a valid Write Cycle.Status RegisterThe RDSR instruction provides access to the Status Reg-ister. The Status Register may be read at any time, even during a Write Cycle. The Status Register is formatted as follows:The Write-In-Progress (WIP) bit is a volatile, read only bit and indicates whether the device is busy with an internal nonvolatile write operation. The WIP bit is read using the RDSR instruction. When set to a “1”, a nonvolatile write operation is in progress. When set to a “0”, no write is in progress.The Write Enable Latch (WEL) bit indicates the Status of the Write Enable Latch. When WEL=1, the latch is set HIGH and when WEL=0 the latch is reset LOW. The WEL bit is a volatile, read only bit. It can be set by the WREN instruction and can be reset by the WRDS instruction.The Block Lock bits, BL0 and BL1, set the level of Block Lock TM Protection. These nonvolatile bits are pro-grammed using the WRSR instruction and allow the user to protect one quarter, one half, all or none of the E 2 PROM array . Any portion of the array that is Block Lock Protected can be read but not written. It will remain pro-tected until the BL bits are altered to disable Block Lock Protection of that portion of memory. 7036 FRM T03Bits 4 and 5 of the Status Register will be read as “1’s”and must be written as “1’s” on all Status Register writes.7654321WPEN FLB11BL1BL0WELWIP7036 FRM T02Status Register Bits Array Addresses Protected BL1BL0X2564XX2532XX2516X00NoneNoneNone01$1800–$1FFF $0C00–$0FFF $0600–$07FF 10$1000–$1FFF $0800–$0FFF $0400–$07FF 11$0000–$1FFF $0000–$0FFF $0000–$07FFTable 1. Instruction Set *Instructions are shown MSB in leftmost position. Instructions are transferred MSB first.7036 FRM T04Instruction NameInstruction Format*OperationWREN 0000 0110Set the Write Enable Latch (Enable Write Operations)SFLB 0000 0000Set Flag BitWRDI/RFLB 0000 0100Reset the Write Enable Latch/Reset Flag Bit RSDR 0000 0101Read Status RegisterWRSR 0000 0001Write Status Register (BlockLock,WPEN & Flag Bits)READ 0000 0011Read Data from Memory Array Beginning at Selected Address WRITE0000 0010Write Data to Memory Array Beginning at Selected Address元器件交易网X25648/49, X25328/29, X25168/69The read only FLAG bit shows the status of a volatile latchthat can be set and reset by the system using the SFLB and RFLB instructions. The Flag bit is automatically reset upon power up.The nonvolatile WPEN bit is programmed using the WRSR instruction. This bit works in conjunction with the WP pin to provide Programmable Hardware Write Protec-tion (T able 2). When WP is LOW and the WPEN bit is pro-grammed HIGH, all Status Register Write Operations are disabled.In Circuit Programmable ROM ModeThis mechanism protects the Block Lock and Watchdog bits from inadvertant corruption. It may be used to per-form an In Circuit Programmable ROM function by hard-wiring the WP pin to ground, writing and Block Locking the desired portion of the array to be ROM, and then pro-gramming the WPEN bit HIGH.Read SequenceWhen reading from the E 2 PROM memory array, CS is first pulled low to select the device. The 8-bit READ instruction is transmitted to the device, followed by the 16-bit address. After the READ opcode and address are sent, the data stored in the memory at the selected address is shifted out on the SO line. The data stored in memory at the next address can be read sequentially by continuing to provide clock pulses. The address is auto-matically incremented to the next higher address after each byte of data is shifted out. When the highest address is reached, the address counter rolls over to address $0000 allowing the read cycle to be continued indefinitely.The read operation is terminated by taking CS high. Refer to the Read E 2 PROM Array Sequence (Figure 1).T o read the Status Register, the CS line is first pulled low to select the device followed by the 8-bit RDSR instruc-tion. After the RDSR opcode is sent, the contents of the Status Register are shifted out on the SO line. Refer to the Read Status Register Sequence (Figure 2).Write SequencePrior to any attempt to write data into the device, the “Write Enable” Latch (WEL) must first be set by issuing the WREN instruction (Figure 3). CS is first taken LOW,then the WREN instruction is clocked into the device.After all eight bits of the instruction are transmitted, CS must then be taken HIGH. If the user continues the Write Operation without taking CS HIGH after issuing the WREN instruction, the Write Operation will be ignored.T o write data to the E 2 PROM memory array, the user then issues the WRITE instruction followed by the 16 bit address and then the data to be written. Any unused bits are specified to be “0’s”. The WRITE operation minimally takes 32 clocks. CS must go low and remain low for the duration of the operation. If the address counter reaches the end of a page and the clock continues, the counter will roll back to the first address of the page and overwrite any data that may have been previously written.For the Page Write Operation (byte or page write) to be completed, CS can only be brought HIGH after bit 0 of the last data byte to be written is clocked in. If it is brought HIGH at any other time, the write operation will not be completed (Figure 4).T o write to the Status Register, the WRSR instruction is followed by the data to be written (Figure 5). Data bits 0and 1 must be “0”. Data bits 4 and 5 must be “1”.Table 2. 7036 FRM T06STATUS REGISTER STATUS REGISTER DEVICE PIN BLOCK BLOCK STATUS REGISTER WELWPENWP#PROTECTED BLOCKUNPROTECTEDBLOCKWPEN, BL0, BL1 BITS0X X Protected Protected Protected 110Protected Writable Protected 10X Protected Writable Writable 1X1ProtectedWritableWritable元器件交易网X25648/49, X25328/29, X25168/69While the write is in progress following a Status Register or E 2 PROM Sequence, the Status Register may be read to check the WIP bit. During this time the WIP bit will be high.RESET/RESET OperationThe RESET (X25XX3) output is designed to go LOW whenever V CC has dropped below the minimum trip point,V trip .The RESET (X25XX5) output is designed to go HIGH whenever V CC has dropped below the minimum trip point,V trip.The RESET/RESET output is an open drain output and requires a pull up resistor.Operational NotesThe device powers-up in the following state:•The device is in the low power standby state.• A HIGH to LOW transition on CS is required to enter an active state and receive an instruction.•SO pin is high impedance.•The Write Enable Latch is reset.•The Flag Bit is reset.•Reset Signal is active for t PURST .Data ProtectionThe following circuitry has been included to prevent inad-vertent writes:• A WREN instruction must be issued to set the Write Enable Latch.•CS must come HIGH at the proper clock count in order to start a nonvolatile write cycle.Figure 1. Read E 2PROM Array Sequence元器件交易网元器件交易网X25648/49, X25328/29, X25168/69Figure 2. Read Status Register SequenceFigure 3. Write Enable Latch SequenceCS01234567SCKSIHIGH IMPEDANCESO7036 FRM05元器件交易网X25648/49, X25328/29, X25168/69Figure 4. Write SequenceFigure 5. Status Register Write SequenceSymbol TableX25648/49, X25328/29, X25168/69D.C. OPERATING CHARACTERISTICS (Over the recommended operating conditions unless otherwise specified.)7036 FRM T09POWER-UP TIMING 7036 FRM T10CAPACITANCE T A = +25 ° C, f = 1MHz, V CC = 5V. Notes:(1) V IL min. and V IH max. are for reference only and are not tested. 7036 FRM T11(2) This parameter is periodically sampled and not 100% tested.Symbol ParameterLimitsUnits Test ConditionsMin.Typ.Max. I CC1 V CC Write Current (Active)5mA SCK = V CC x 0.1/V CC x 0.9 @ 2MHz, SO = OpenI CC2 V CC Read Current (Active)0.4mA SCK = V CC x 0.1/V CC x 0.9 @ 2MHz, SO = OpenI SB1 V CC Standby Current WDT=OFF 1 µ A CS = V CC , V IN = V SS or V CC , V CC= 5.5V I SB2V CC Standby Current WDT=ON 50µA CS = V CC , V IN = V SS or V CC , V CC = 5.5V I SB3V CC Standby Current WDT=ON 20µA CS = V CC , V IN = V SS or V CC , V CC =3.6V I LI Input Leakage Current 0.110µA V IN = V SS to V CC I LO Output Leakage Current 0.110µA V OUT = V SS to V CCV IL (1)Input LOW Voltage –0.5V CC x0.3V V IH (1)Input HIGH Voltage V CC x0.7V CC +0.5V V OL1Output LOW Voltage 0.4V V CC > 3.3V, I OL = 2.1mA V OL2Output LOW Voltage 0.4V 2V < V CC ≤ 3.3V, I OL = 1mA V OL3Output LOW Voltage 0.4V V CC ≤ 2V, I OL = 0.5mA V OH1Output HIGH Voltage V CC –0.8 V V CC > 3.3V, I OH = –1.0mA V OH2Output HIGH Voltage V CC –0.4V 2V < V CC ≤ 3.3V, I OH = –0.4mA V OH3Output HIGH Voltage V CC –0.2V V CC ≤ 2V, I OH = –0.25mA V OLRSReset Output LOW Voltage0.4VI OL = 1mASymbolParameterMin.Max.Unitst PUR (2)Power-up to Read Operation 1ms t PUW (2)Power-up to Write Operation5msSymbolTestMax.UnitsConditionsC OUT (2)Output Capacitance (SO, RESET, RESET)8pF V OUT = 0V C IN (2)Input Capacitance (SCK, SI, CS, WP)6pFV IN = 0VABSOLUTE MAXIMUM RATINGS*T emperature under Bias ........................–65°C to +135°C Storage T emperature .............................–65°C to +150°C Voltage on any Pin with Respect to V SS .......–1.0V to +7V D.C. Output Current....................................................5mA Lead T emperature (Soldering, 10 seconds)............300°C RECOMMENDED OPERATING CONDITIONS7036 FRM T07*COMMENTStresses above those listed under “Absolute Maximum Ratings” may cause permanent damage to the device.This is a stress rating only and the functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.7036 FRM T08TempMin.Max.Commercial 0°C 70°C Industrial–40°C+85°CSupply Voltage LimitsX25XXX –1.8 1.8V-3.6V X25XXX –2.7 2.7V to 5.5V X25XXX4.5V-5.5V元器件交易网A.C. CHARACTERISTICS (Over recommended operating conditions, unless otherwise specified)Data Input Timing7036 FRM T13Symbol Parameter Voltage RangeMin.Max.Unitsf SCK Clock Frequency 2.7V–5.5V 1.8V–3.6V 021MHz t CYC Cycle Time 2.7V–5.5V 1.8V–3.6V 5001000ns t LEAD CS Lead Time 2.7V–5.5V 1.8V–3.6V 250500ns t LAG CS Lag Time 2.7V–5.5V 1.8V–3.6V 250500ns tWH Clock HIGH Time 2.7V–5.5V 1.8V–3.6V 200400ns t WL Clock LOW Time 2.7V–5.5V 1.8V–3.6V 200400ns t SU Data Setup Time 2.7V–5.5V 1.8V–3.6V 50ns t H Data Hold Time 2.7V–5.5V 1.8V–3.6V 50nst RI (3)Input Rise Time 2.7V–5.5V 1.8V–3.6V 100ns t FI (3)Input Fall Time 2.7V–5.5V 1.8V–3.6V 100ns t CS CS Deselect Time 2.7V–5.5V 1.8V–3.6V 500ns t WC (4)Write Cycle Time2.7V–5.5V 1.8V–3.6V10msEQUIVALENT A.C. LOAD CIRCUIT AT 5V V CCA.C. TEST CONDITIONS 7036 FRM T12Input Pulse Levels V CC x 0.1 to V CC x 0.9Input Rise and Fall Times 10ns Input and Output Timing LevelV CC x0.5Data Output Timing7036 FRM T14Notes:(3) This parameter is periodically sampled and not 100% tested.(4) t WC is the time from the rising edge of CS after a valid write sequence has been sent to the end of the self-timed internal nonvolatile write cycle.Symbol ParameterPart NumberMin.Max.Unitsf SCK Clock Frequency 2.7V–5.5V 1.8V–3.6V 021MHz t DIS Output Disable Time 2.7V–5.5V 1.8V–3.6V 250ns t V Output Valid from Clock Low 2.7V–5.5V 1.8V–3.6V 200400ns t HO Output Hold Time 2.7V–5.5V 1.8V–3.6V 0nst RO (3)Output Rise Time 2.7V–5.5V 1.8V–3.6V 100ns t FO (3)Output Fall Time2.7V–5.5V 1.8V–3.6V100nsSerial Output TimingSerial Input TimingPower-Up and Power-Down TimingRESET Output Timing 7036 FRM T15Notes:(5) This parameter is periodically sampled and not 100% tested.Symbol ParameterMin.Typ.Max.UnitsV TRIP Reset Trip Point Voltage, 5V Device Reset Trip Point Voltage, 2.7V Device Reset Trip Point Voltage, 1.8V Device 4.252.551.7 4.52.71.8V V V t PURST Power-up Reset Timeout 100200280ms t RPD (5)V CC Detect to Reset/Output 500ns t F (5)V CC Fall Time 0.1ns t R (5)V CC Rise Time 0.1ns V RVALIDReset Valid V CC1VPACKAGING INFORMATION0.014 (0.35)0.020 (0.51)(4X) 714-LEAD PLASTIC SMALL OUTLINE GULL WING P ACKAGE TYPE SNOTE: ALL DIMENSIONS IN INCHES (IN PARENTHESES IN MILLIMETERS)0.0075 (0.19)0.010 (0.25)0.014 (0.35)0.019 (0.49)(4X) 70.0075 (0.19)0.010 (0.25)8-LEAD PLASTIC SMALL OUTLINE GULL WING P ACKAGE TYPE SNOTE:ALL DIMENSIONS IN INCHES (IN P ARENTHESES IN MILLIMETERS)NOTE:ALL DIMENSIONS IN INCHES (IN P ARENTHESES IN MILLIMETERS)14-LEAD PLASTIC, TSSOP, P ACKAGE TYPE V0° – 8Gage PlaneSeating PlaneDetail A (20X)ORDERING INFORMATIONPart Mark Convention DeviceLIMITED WARRANTYDevices sold by Xicor, Inc. are covered by the warranty and patent indemnification provisions appearing in its Terms of Sale only. Xicor, Inc.makes no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. Xicor, Inc. makes no warranty of merchantability or fitness for any purpose. Xicor, Inc. reserves the right to discontinue production and change specifications and prices at any time and without notice.Xicor, Inc. assumes no responsibility for the use of any circuitry other than circuitry embodied in a Xicor, Inc. product. No other circuits, patents,licenses are implied.U.S. PATENTSXicor products are covered by one or more of the following U.S. Patents: 4,263,664; 4,274,012; 4,300,212; 4,314,265; 4,326,134; 4,393,481;4,404,475; 4,450,402; 4,486,769; 4,488,060; 4,520,461; 4,533,846; 4,599,706; 4,617,652; 4,668,932; 4,752,912; 4,829, 482; 4,874, 967;4,883, 976. Foreign patents and additional patents pending.LIFE RELATED POLICYIn situations where semiconductor component failure may endanger life, system designers using this product should design the system with appropriate error detection and correction, redundancy and back-up features to prevent such an occurence.Xicor’s products are not authorized for use in critical components in life support devices or systems.1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.V CC LimitsBlank = 5V ±10%2.7 = 2.7V to 5.5V 1.8 = 1.8V to 3.6VTemperature RangeBlank = Commercial = 0°C to +70°C I = Industrial = –40°C to +85°C PackageS14 = 14-Lead SOIC S8 = 8-Lead SOIC V14 = 14-Lead TSSOPBlank = 14-Lead SOICBlank = 5V ±10%, 0°C to +70°C I = 5V ±10%, –40°C to +85°C F = 2.7V to 5.5V , 0°C to +70°C G = 2.7V to 5.5V , –40°C to +85°C AG = 1.8V to 3.6V , 0°C to +70°C X25648/49P T -VX25648/49X XX25328/29X25168/69Blank = 8-Lead SOIC V = 14 Lead TSSOPBlank = 5V ±10%, 0°C to +70°C I = 5V ±10%, –40°C to +85°C F = 2.7V to 5.5V , 0°C to +70°C G = 2.7V to 5.5V , –40°C to +85°C AG = 1.8V to 3.6V , 0°C to +70°C X25328/29X XX25168/69。

102278-6资料

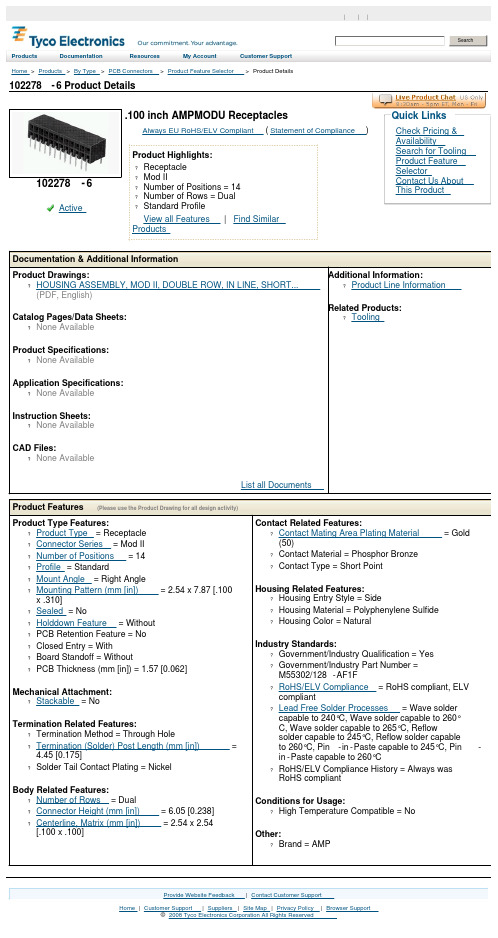

102278-6 Product DetailsHome | Customer Support | Suppliers | Site Map | Privacy Policy | Browser Support© 2008 Tyco Electronics Corporation All Rights Reserved SearchProducts Documentation Resources My Account Customer Support Home > Products > By Type > PCB Connectors > Product Feature Selector > Product Details102278-6Active .100 inch AMPMODU ReceptaclesAlways EU RoHS/ELV Compliant (Statement of Compliance)Product Highlights:?Receptacle?Mod II?Number of Positions = 14?Number of Rows = Dual?Standard ProfileView all Features | Find SimilarProductsCheck Pricing &AvailabilitySearch for ToolingProduct FeatureSelectorContact Us AboutThis ProductQuick LinksDocumentation & Additional InformationProduct Drawings:?HOUSING ASSEMBLY, MOD II, DOUBLE ROW, IN LINE, SHORT...(PDF, English)Catalog Pages/Data Sheets:?None AvailableProduct Specifications:?None AvailableApplication Specifications:?None AvailableInstruction Sheets:?None AvailableCAD Files:?None AvailableList all Documents Additional Information:?Product Line InformationRelated Products:?ToolingProduct Features (Please use the Product Drawing for all design activity)Product Type Features:?Product Type = Receptacle?Connector Series = Mod II?Number of Positions = 14?Profile = Standard?Mount Angle = Right Angle?Mounting Pattern (mm [in]) = 2.54 x 7.87 [.100x .310]?Sealed = No?Holddown Feature = Without?PCB Retention Feature = No?Closed Entry = With?Board Standoff = Without?PCB Thickness (mm [in]) = 1.57 [0.062] Mechanical Attachment:?Stackable = NoTermination Related Features:?Termination Method = Through Hole?Termination (Solder) Post Length (mm [in]) =4.45 [0.175]?Solder Tail Contact Plating = NickelBody Related Features:?Number of Rows = Dual?Connector Height (mm [in]) = 6.05 [0.238]?Centerline, Matrix (mm [in]) = 2.54 x 2.54[.100 x .100] Contact Related Features:?Contact Mating Area Plating Material = Gold(50)?Contact Material = Phosphor Bronze?Contact Type = Short PointHousing Related Features:?Housing Entry Style = Side?Housing Material = Polyphenylene Sulfide?Housing Color = NaturalIndustry Standards:?Government/Industry Qualification = Yes?Government/Industry Part Number =M55302/128-AF1F?RoHS/ELV Compliance = RoHS compliant, ELVcompliant?Lead Free Solder Processes = Wave soldercapable to 240°C, Wave solder capable to 260°C, Wave solder capable to 265°C, Reflowsolder capable to 245°C, Reflow solder capableto 260°C, Pin-in-Paste capable to 245°C, Pin-in-Paste capable to 260°C?RoHS/ELV Compliance History = Always wasRoHS compliantConditions for Usage:?High Temperature Compatible = NoOther:?Brand = AMPProvide Website Feedback | Contact Customer Support。

1952678资料

Extract from the onlinecatalogMCDNV 1,5/19-G1-3,5 RNP14THROrder No.: 1952678The figure shows a 10-position version of the producthttp://eshop.phoenixcontact.de/phoenix/treeViewClick.do?UID=1952678Headers with engagement nose, 3.5 mm pitch, pin length 14, plug-in direction vertical to the PCBhttp://Please note that the data givenhere has been taken from theonline catalog. For comprehensiveinformation and data, please referto the user documentation. TheGeneral Terms and Conditions ofUse apply to Internet downloads. Technical dataDimensions / positionsLength16 mmHeight13.3 mmPitch 3.5 mmDimension a63 mmNumber of positions19Pin dimensions0,8 x 0,8 mm Pin spacing 3.5 mmHole diameter 1.4 mmTechnical dataInsulating material group IIIaRated surge voltage (III/3) 2.5 kVRated surge voltage (III/2) 2.5 kVRated surge voltage (II/2) 2.5 kVRated voltage (III/2)200 VRated voltage (II/2)250 V Connection in acc. with standard EN-VDE Nominal current I N8 ANominal voltage U N160 V Maximum load current8 A (per position) Insulating material LCP Inflammability class acc. to UL 94V0Certificates / ApprovalsApproval logoCULNominal voltage U N150 VNominal current I N8 AULNominal voltage U N150 VNominal current I N8 A Certification CUL, ULAccessoriesItem Designation DescriptionMarking0805030SK 3,5/2,8:SO Marker card, special printing, self-adhesive, labeled acc. tocustomer requirements, 14 identical marker strips per card, max.25-position labeling per strip, color: White0804109SK 3,81/2,8:FORTL.ZAHLEN Marker card, printed horizontally, self-adhesive, 10-section markerstrip, 14 identical decades marked 1-10, 11-20 etc. up to 91-(99)100, sufficient for 140 terminal blocksPlug/Adapter1734634CP-MSTB Coding profile, is inserted into the slot on the plug or invertedheader, red insulating materialDrawingsDrilling diagram*) ≤ 8-pos. = 1.3 / > 8-pos. = 1.4Dimensioned drawingAddressPHOENIX CONTACT GmbH & Co. KGFlachsmarktstr. 832825 Blomberg,GermanyPhone +49 5235 3 00Fax +49 5235 3 41200http://www.phoenixcontact.de© 2008 Phoenix ContactTechnical modifications reserved;。

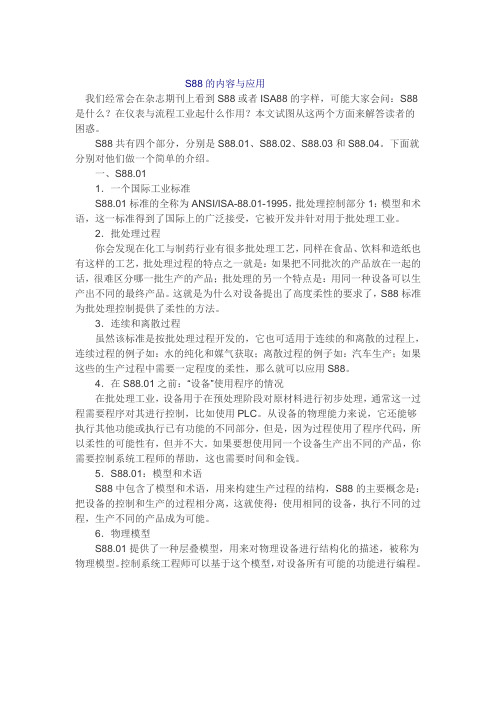

S88的内容与应用

S88的内容与应用我们经常会在杂志期刊上看到S88或者ISA88的字样,可能大家会问:S88是什么?在仪表与流程工业起什么作用?本文试图从这两个方面来解答读者的困惑。

S88共有四个部分,分别是S88.01、S88.02、S88.03和S88.04。

下面就分别对他们做一个简单的介绍。

一、S88.011.一个国际工业标准S88.01标准的全称为ANSI/ISA-88.01-1995,批处理控制部分1:模型和术语,这一标准得到了国际上的广泛接受,它被开发并针对用于批处理工业。

2.批处理过程你会发现在化工与制药行业有很多批处理工艺,同样在食品、饮料和造纸也有这样的工艺,批处理过程的特点之一就是:如果把不同批次的产品放在一起的话,很难区分哪一批生产的产品;批处理的另一个特点是:用同一种设备可以生产出不同的最终产品。

这就是为什么对设备提出了高度柔性的要求了,S88标准为批处理控制提供了柔性的方法。

3.连续和离散过程虽然该标准是按批处理过程开发的,它也可适用于连续的和离散的过程上,连续过程的例子如:水的纯化和媒气获取;离散过程的例子如:汽车生产;如果这些的生产过程中需要一定程度的柔性,那么就可以应用S88。

4.在S88.01之前:“设备”使用程序的情况在批处理工业,设备用于在预处理阶段对原材料进行初步处理,通常这一过程需要程序对其进行控制,比如使用PLC。

从设备的物理能力来说,它还能够执行其他功能或执行已有功能的不同部分,但是,因为过程使用了程序代码,所以柔性的可能性有,但并不大。

如果要想使用同一个设备生产出不同的产品,你需要控制系统工程师的帮助,这也需要时间和金钱。

5.S88.01:模型和术语S88中包含了模型和术语,用来构建生产过程的结构,S88的主要概念是:把设备的控制和生产的过程相分离,这就使得:使用相同的设备,执行不同的过程,生产不同的产品成为可能。

6.物理模型S88.01提供了一种层叠模型,用来对物理设备进行结构化的描述,被称为物理模型。

ISO276811989中文版

国际标准ISO2768-1第一版1989-11-15常规公差——第一部份:无单独公差标示的线尺度、角度公差参考号ISO2768-1:1989(E)ISO 2768-1:1989(E)前言ISO(国际标准化组织)是世界范围内国家标准实体(ISO成员)的联合体。

通常由ISO技术委员会制定国际标准。

可是,只要对该组织成立的某个主题感爱好,任何成员都能够在这方面充当委员会的代表。

所有与ISO关联的国际组织,政府和非政府机构,都参加此项工作。

ISO在电工标准事务上,与国际电工委员会紧密一致。

由技术委员会起草的国际标准草稿,在ISO将其作为国际标准正式文件之前,需要分发给各成员实体进行核准。

标准的核准需要通过ISO的程序进行,即需要所有成员的75%同意才可取得通过。

ISO2768-2由技术委员会ISO/TC 3(误差与配合)制定。

ISO2678-1第一版与ISO2678-1:1989一路取代了ISO2768:1973。

题为常规公差的ISO2768包括以下部份:第一部份:无单独公差标示的线尺度、角度公差第二部份:无单独公差标示的部件几何公差ISO2768中附录A与B仅供参考。

简介所有部件部份的零部件都有自己的尺寸和几何形状。

假设是尺寸或几何特性(形状,方向与位置)显现误差,超出了该部份要求的最低值,那么破坏了该部份的功能。

图纸上的公差规定应当完整,以确保操纵零部件的尺寸与几何因素,也确实是,不该该留给车间或查验部人员来判定。

利用尺寸与几何常规公差,减轻了知足该必要条件的任务。

国际标准ISO2768-1:1989(E)常规公差——第一部份:无单独公差标示的线尺度、角度公差1 应用范围ISO2768的这部份意在简化图纸标示,标准常规线尺度、角度公差,从而使图纸上所有零部件再也不显现单独不同的公差。

此处分四类进行公差规定。

注1:对常规线尺度、角度公差规定的方案,将在附件A中论述。

该部份要紧适用于金属材料切除后生产的或由金属板加工的零部件。

ISO-2768-1-1989中文版

ISO-2768-1-1989中文版国际标准 ISO2768-1初版1989-11-15常规公差——第一部分:无单独公差标示的线尺度、角度公差参考号ISO2768-1:1989(E)ISO 2768-1:1989(E)前言ISO(国际标准化组织)是世界范围内国家标准实体(ISO成员)的联合体。

通常由ISO技术委员会制定国际标准。

但是,只要对该组织建立的某个主题感兴趣,任何成员都可以在这方面充当委员会的代表。

所有与ISO关联的国际组织,政府以及非政府机构,都参加此项工作。

ISO在电工标准事务上,与国际电工委员会紧密一致。

由技术委员会起草的国际标准草稿,在ISO将其作为国际标准正式文件之前,需要分发给各成员实体进行核准。

标准的核准需要经过ISO的程序进行,即需要所有成员的75%赞成才可获得通过。

ISO2768-2由技术委员会ISO/TC 3(误差与配合)制定。

ISO2678-1初版与ISO2678-1:1989一起取代了ISO2768:1973。

题为常规公差的ISO2768包括以下部分:第一部分:无单独公差标示的线尺度、角度公差第二部分:无单独公差标示的部件几何公差ISO2768中附录A与B仅供参考。

国际标准 ISO2768-1:1989(E)常规公差——第一部分:无单独公差标示的线尺度、角度公差1 应用范围ISO2768的这部分意在简化图纸标示,规范常规线尺度、角度公差,从而使图纸上所有零部件不再出现单独不同的公差。

此处分四类进行公差规定。

注1:对常规线尺度、角度公差规定的方案,将在附件A中阐述。

该部分主要适用于金属材料切除后生产的或由金属板加工的零部件。

注2. 这些公差可以实用于金属以外的其他材料。

3. 与之平衡的国际标准已经存在或正在生成,例如,见铸件ISO8062①。

ISO2768仅用于以下尺度,它们没有单独公差说明。

a)线性尺度(例如破碎边缘的外部尺寸、内部尺寸、步长、直径、半径、距离、外半径以及斜面高度等)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。