D. Maximum CMRR The

大连交通大学coa考试题1

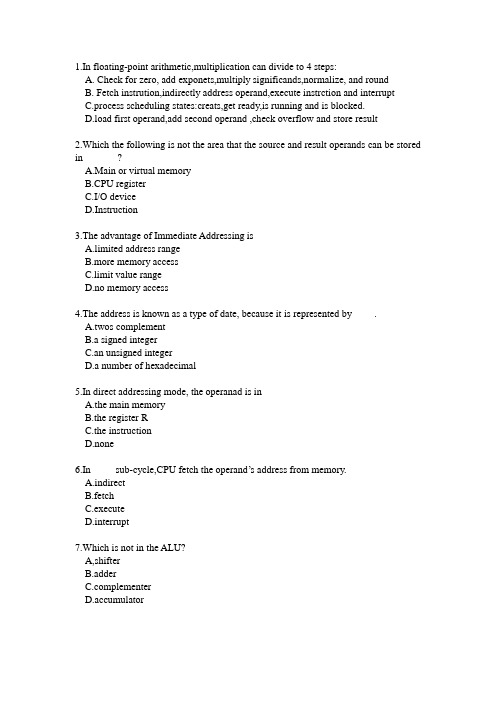

1.In floating-point arithmetic,multiplication can divide to 4 steps:A. Check for zero, add exponets,multiply significands,normalize, and roundB. Fetch instrution,indirectly address operand,execute instrction and interruptC.process scheduling states:creats,get ready,is running and is blocked.D.load first operand,add second operand ,check overflow and store result2.Which the following is not the area that the source and result operands can be stored in_______?A.Main or virtual memoryB.CPU registerC.I/O deviceD.Instruction3.The advantage of Immediate Addressing is _______A.limited address rangeB.more memory accessC.limit value rangeD.no memory access4.The address is known as a type of date, because it is represented by ____.A.twos complementB.a signed integerC.an unsigned integerD.a number of hexadecimal5.In direct addressing mode, the operanad is in ____A.the main memoryB.the register RC.the instructionD.none6.In ____ sub-cycle,CPU fetch the operand’s address from memory.A.indirectB.fetchC.executeD.interrupt7.Which is not in the ALU? _____A,shifterB.adderplementerD.accumulator8.Instruction pipeline can improve______A.processing speed of programB.accessing speed of memoryC.accessing speed of I?OD.accessing speed of RAID9.The protocol “mesi” is alse called _______.A.write back policyB.write -update protocolC.write -invalidate protocolD.write through policy10.MESI protocol can solve the ______.A.problem of cache coherenceB.problem of memory write bottle-nekmunication problem of person-computerD.volatile problem of DRAM11.At the end of fetch cycle,IR holds______.A.instructionB.operandC.address of operandD.address of instruction12.There are three kinds of BUS,Which does not belong to themA.address busB.system busC.data busD.control bus13.Cache’s write-back policy means write operation to main memory_____.A.as well as to cacheB.only when the relative cache is replacedC.when the difference between cache and main mimory is foundD.only when using direct mapping14.A four-way set associative chache has 63k words,main memory has 256M words and divided 32M blocks.line size is _____words.A.4B.8C.16D.3215.In the following description,which is NOT right6?________.A.SRAM is faster than DRAMB.DRAM needs periodic charg refreshing circuitC.DRAM is slower than FlashD.ROM does not require power supplied continuously16.Which RAID level make use of parallel access technique?______.A.RAID0B.RAID2C.RAID4D.RAID617.RAID stored _____information that enable the recovery of data lost due to a disk failure.A.parityer dataC.OSD.interrupt18.The signals of interrupt request and acknowledgement exchange between CPU and requesting I?O module. The rason of CPU’s acknowledgement is ______.A.to let the I?O module remove request signalB.to let CPU get the vector from data busC.both A&BD.other aims19.In DMA,the DMA module takes over the operations of data transferring from CPU,it means_______.A.the DMA module can fetch and execute instructions like CPU doesB.the DMA module can control the bus to transfer data to or from meory using stealing cycle techniqueC.the DMA module and CPU work together(co-operate)to transfer data into or from memoryD.the DMA module get ready,it issues interrupt request signal to CPU for getting interrupt service20.In twos complement,two positive intergers add,when does overflow occur?A.There is a carryB.Sign bit of result is 1C.There is a carry,and sign bit of result is 0D.Can’t determine21.The 8-bits twos complement -128 is 10000000,its 16-bits twos complement is ___A.1000 0000 1000 0000B.0000 0000 1000 0000C.1111 1111 1000 0000D.1000 0000 0000 000022.The address of the top of stack is stored in ____ registerA.PCB. ACC.SPD.BP23.The REGISTER ADDRESSING is very fast,but it has_______.A.very less value rangeB.very less address spaceC.more memory accessD.very complex address’ calculating24.In instrucion,the number of addressed is 2,One address doubles as____A.a result and the address of next instructionB.an operand and a resultC.an operand and the address of next instructionD.two closed operands25.A branch instruction performed by CPU is to updatae ______.A.MBR to contain the instructionB.Program counter to contain the address of next instructionC.MAR to contain the address of current instructionD.IR to contain the instruction that just fetched from memory26.In register indirect addressing,the effective address of operand is stored in ____.A.registerB.main memoryC.instructionD.PC27.The Memory Address Register of CPU connects to ______BUSA.systemB.addressC.dataD.control28.The Accumulator is a(n)______register in 8086A.general purposeB. DataC.addressD.control29.Which is the worst instruction to limit instruction pipeline?A.ADD AX,XB.MOV AX,[X]C.RETURND.ISZ X30.In MESI protocol,the line in the cache is the same as that in main memory and is not present in other cache,which state is the line in______.A.ModifiedB.exclusiveC.sharedD.invalid31.Which of the following attributes associated with architectureA.Control signalsB.interfacesC.Instruction setD.memory technology32.Which of the following statement is not correct?A.N bits binary address coding can be 2N storage word to identify a wordB.N bits unsigned binary number can represent a value in the range between 0 to 2N-1C.The length of address is 32 bits ,so addressing range is 4GD.8086 has 20 bite address bus giving 220-1 address spaceputer memory is organized into a hierarchy .At the top level are the_____.A.registers B cache C.main memory D.external memory34.On address mapping of cache ,the data in any block of main memory can be mapped to ______of cache ,it is direct mapping.A.any lineB.fixed lineC.fixed set any lineD.A and B35.Which is the nonvolatile and permanent storge semiconductor memory?___A.SRAMB.CD-ROMC.FLASHD.DRAM36.In hamming code ,if syndrome contains one & only one 1,it means____.A.the old correct bit is errorB.the data is errorC.more than one errorD.nor error37.In _____,two copies of each stripe on separate disks,read from either and write to both.A.RAID 1B.RAID2C.RAID 3D.RAID438.When aprocessor access to the disk physical block ,it must know that the physical blocks on the disk location of three parameters:________.A.side,head and trackB.side ,sector and cylinderC.cylinder,sector and trackD.side,sector and platter39.There are three types of the Input Output Techniques,Which one is not belong them?______.A.Interrupt-driven I/OB.programmed I/O \C.direct I/O accessD.DMA40.In DMA,when does DMA module issue interrupt request signal to CPU?A.before DMA module transfers a block dataB.after DMA module finishes a block data transferC.before DMA module seizes to use busD.after DMA module ends to size bus1 2 3 4 5 6 7 8 9 10D D D C A A D A C A11 12 13 14 15 16 17 18 19 20A B B B C B A C B B21 22 23 24 25 26 27 28 29 30C C B B B B B AD B31 32 33 34 35 36 37 38 39 40C D A B C A A B C BII Answer the following questions1)Interrupt Processing,The CPU save information of current program to stack forresuming it.What is the important information?2) In MESI protocol , READ MISS, initiating in invalid and snooping in modified,fill in the following table.initiating snoopingState in beginning invalid ModifyactionState in end3)In Displacement Addressing,EA=A+(R),what is the R register holds? In RelativeAddressing,what is the R register?1)PC, PSW (4分)2)initiating SnoopingBegin invalid ModifiedAction Read data from ……Write to memoryEnd shared shared(4分)3)base or displacement, PC (4分)得分15III A four-way set associative main memory has 256M words,cache has 4M words and block size is 32-words. Please answer the following questions:1)Show the format of main memory addresses2)Which set of cache is memory location FCB5C6AH mapped to?What is the tag?3)Which words of main memory may be mapped to cache set 6E8A and tag value is B5H?1)-2分- Line size=Block size=32words=25words =>Word# =5bits(2)-3分- Number of sets=4M/32 lines/ 4lines/set =215sets =>Set# =15bits(3)-2分-Memory size=256Mwords=228words => Length of RA =28bits =>Tag=28-5-15=8 bitsTag 8 itb Set# 15 bit Word# 5 bit-1分-2) (3分)FCB5C6AH=1111 1100 1011 0101 1100 011 0 1010 is mapping to set# 5AE3, tag#FC3) (4分)B5 6E8A1011 0101 110 1 110 1 000 1 010 0 00001011 0101 110 1 110 1 000 1 010 1 1111words of main memory: B5 DD140~ B5 DD15IV According to the instruction of the following,Answer the questions. 1) Show all the micro-operations for the following instruction: BSA X -Branch and save addressAddress of instruction following BSA is saved in X Execution continues from X+12) Which addressing mode is included in this instruction? Please draw the figure of its addressing mode3) According to the initial value of the following figure ,at the end of Execute cycle,what is the value of PC,MBU,MAR and IR holdⅣAnswer:2) (4分) PC:2012MAR:2012(应该是2011) MBR:1124 IR:BSA 20113) (4分)Direct Addressing1) (10分)Fetch cycle t1: (PC) -> MAR t2: (MAR) ---> Memory read ---> Memory t3: Memory ---> MBR t4: (MBR) -> IR (PC) +1 -> PC Execute cycle t1: Ad(MBR) ->MAR t2: (PC) ->MBR t3: (MAR)-> Memory (MBR) ->Memory write ->Memory t4: (MAR)+1 ->PCFor the 8-bit data 0011 1001,Using the Hamming algorithm,the check bits stored with it.Suppose when the word is read from memory,the check bit are calculated to be 1101.1)What is the data word that was read from memory?2)Write the correct Hamming code(1) (2分)2k-1≥m+k =>k=4-bit(2) (4分)Set up a tableBit Position PositionnumberCheckbitDatabit12 1100 D8011 1011 D7010 1010 D6 19 1001 D5 18 1000 C87 0111 D4 16 0110 D305 0101 D204 0100 C43 0011 D1 12 0010 C21 0001 C1(3)(4分)Calculates old check bits:C1(1,2,4,5,7)=1⊕0⊕1⊕1⊕0=1C2(1,3,4,6,7)=1⊕0⊕1⊕1⊕0=1C4(2,3,4,8) =0⊕0⊕1⊕0 =1C8(5,6,7,8) =1⊕1⊕0⊕0 = 0old check bits:C8C4C2C1=0111 (4)(2分)Syndrome word: 0111⊕1101=1010 =>D6 is wrong, so the data from memory is 00011001.2) (3分)0011 0 100 1 1 11。

程式性直流电压负载 Chroma 63200系列说明书

ProgrammableChroma's 63200 series of programmable electronicloads are designed for a wide variety of dc powerconversion products including; DC power sources,battery chargers, server power supplies, dc-dcconverters, batteries and many others. Thehigh power rating, parallel and synchronizationcapabilities, and the ability to provide up to 2.7times of rated power for short duty cycle loadingmake 63200 series especially well-suited for highpower applications such as switch-mode rectifiersand for discharging batteries packs and fuel cells.The 63200 series offers 12 different models withpower ranges from 2600 watts to 15600 watts,currents from 50A to 1000A and operatingvoltages from 0 to 1000V. By paralleling modulesvery large systems can be assembled existing93.6kW. Four operating modes provide differentload simulation methods designed for variousapplications. The CC/CR modes are designedto test constant voltage power supplies andconverters. CV mode simulates the battery fortesting battery chargers and current sources, andCP mode is ideal for battery testing by simulatingreal discharge profiles.The 63200 series can sink rated current downto 1VDC even under the highest specified risetime. This unique feature guarantees the bestloading performance for low voltage/high currentapplications. With it's unique external waveformsimulation and Master / Slave control capability,the 63200 series electronic loads allow users toparallel and synchronize more than one loadtogether using an internal or external loadingcontrol signal. This feature provides unlimited loadsimulation and increased power.The 63200 series also provides necessar ymeasurement func tions and shor t circuitsimulations that extend the test capability for themost demanding engineering and automated testapplications.With front LCD displays and rotary knob, the 63200loads offer versatile bench top operation. Users arealso able to control the loads remotely via GPIB orRS-232 interface or with a USB adapter. Complexwaveforms can also be created by driving theloads from an analog programming source (i.e.function generator).Chroma 63200 loads incorporate built-in fanspeed controls to minimize audio noise. The self-diagnosis routines, built-in protection against OC,OP, OT, and an alarm indicating OV reverse polarityto ensure safe operation and reliability. PROGRAMMABLE DC ELECTRONIC LOADMODEL 63200 SERIESRS-232GPIBChroma's 63200 series electronic loads provide constant current, constant resistance, constant voltage and constant power modes.The CC and CR mode load simulation is helpful to test whether the output voltage of the UUT remains stable, or regulated under different load conditions. For battery chargers, CV mode can change the output voltage to test if the battery charger is providing the correct charging current corresponding to the battery voltage. If the UUT is a battery, the electronic load is able to simulate the behavior of the device that uses the battery. For many battery discharge applications, power consumption patterns need to be analyzed. The constant power, or CP mode, is ideal for these applications.For low voltage/high current applications, the 63200 series is available with a low voltage mode, which provides ultra-low voltage operation and in many cases can compensate for large voltage loss in the input wiring.The 63200 series loads use a current closed loop design connecting all power MOSFET devices in parallel, to insure high accuracy load control with minimal drift (less than 0.15% of the current setting). The MOSFET technology keeps the input impedance to a minimum and enables the load to draw very high current even at very low voltages. For example, the model 63209 is capable of drawing 1,000A at only 1V input.Model 63209(15600W) Input CharacteristicsThe Chroma 63200 series loads have a built-in 15-bit precision A/D converter that can achieve 0.05%+0.05% F.S., 0.1%+0.1% F.S. and 0.3%+0.3% F.S. accuracy for voltage, current, and power measurements respectively. These measurements can be displayed simultaneously on three big LED readouts for convenience. In addition to standard measurements, the 63200 series also provides voltage and current monitor outputs, which are useful when the user needs to monitor the voltage and current waveform via a scope.Arbitrary Waveform Generatorexternal loadinG waveform SimulationmaSter / Slave parallel controlThe 63200 series electronic loads can be controlled by an external analog control signal, which is generated by any kind of signal or an arbitrary waveform generator. This makes it capable of simulating any loading waveform observed in the field within the load specifications.When higher power is required, it is common to parallel two electronic loads together to draw higher current. The 63200 series high power loads have a smart Master/Slave control mode. When the loads are set to Master/Slave mode, users can program the loading (CC mode only) on the master unit. The loading current values of the slave unit(s) will be calculated and downloaded by the master unit automatically. In short, unlike traditional designs, users now have the option of operating several loads in Master/Slave mode as a single load unit.Modern electronic devices operate at very high speeds; therefore, it is important for an electronic load to perform well during the transient and dynamic testing. To satisfy these testing applications, the 63200 loads offer outstanding high speed, programmable dynamic load simulation and control capabilities. The figure below shows the programmable parameters of the 63200 load modules. The programmable slew rate makes the simulation of transient load changes demanded by the requirement of real life application possible. The internal waveform generator of the 63200 is capable of producing a maximum slew rate of 25A/µs (63208), and dynamic cycling up to 20kHz. Its dedicated remote load sense and control circuitry guarantee theminimum waveform distortion during continuous load changes.Chroma's 63200 Series DC Loads provide a unique surge load simulation capability which allows users to overdrive the loads up to 2.7 times their rated power for short periods. This feature is ideal when the average power required by the UUT is low compared to short-term peak power demands. Plasma Display Panel (PDP) testing is one typical applications, others include battery 3C discharge, breaker & fuse over rating (300% to 1000%) tests, car engine startup simulation and DC motor startup simulation.The amount of surge loading available using the 63200 loads is related to initial loading conditions. Figures 1 and 2 show the relationship of the initial state (Load_Low under Dynamic mode) and the maximum acceptable overdrive power. Under this operation, the load will display an Over Power Protection Alarm (OPP) and will disable the load current if the user violates the maximum surge load capability showed in the figures.Note 1 :The Initial state under Static Mode should last at least 1 second.Note 2 :This surge load capability will be regulated by the temperature de-rating characteristics. (Refer to Note 1 in Specifications)Note 3 :Examples below assume the use of the Model 63201 load with a continuous rating of 2600W/300A/1-80VDC Note 4 :Model 63211/63212 does not support this feature.Example 1: STATIC LOADINGThe Model 63201 can be overdriven to approximately 5200W (200% of its rated continuous power rating) for 6.0 ms when the starting power is 650W (25% of its rated power). This is represented by DOT on the blue curve in Figure 1.Example 2: DYNAMIC LOADINGThe Model 63201 is capable of a zero - to- 6500W (250%) pulse at a duty cycle of 5%. This is represented by the DOT on the purple curve in Figure 2.Chroma's 63200 series electronic loads can also simulate a short circuit condition. The load can short a DC power source or any power supply that has abuilt in current limit function and measure its short circuit current so that users can verify if the UUT current limit is functional.The 63200 loads include a unique timing and measurement function. This allows for precision time settings and measurements in the range of 1s to 99,999s. This feature also allows users to set a final cutoff voltage and timeout value for battery discharge testing and similar applications. For example, the figure to the right shows that the 63200's internal timer can be initiated automatically when starting load on. The timer will stop counting until the cutoff voltage value is reached, or timeout occurs.Electronic & Electrical Devices TestingAlmost all modern electronic equipment have a built in power supply. Therefore, a DC electronic load is an important instrument for these devices during the R/D and Q/A phases. For example, A/D, D/D and D/A stages are normally integrated within a UPS. The Chroma 63200 electronic loads are helpful in testing the internal A/D and D/D boards of UPS devices.Battery TestingFor most applications, power consumption patterns are based on constant power. Therefore, the CP mode of the 63200 series electronic load is ideal to use as a discharge load for battery testing.System integrationChroma 63200 series electronic loads provide GPIB, RS-232 and RS-485 PC controllable interfaces. These features combined with the external waveformsimulation and voltage / current monitoring capability make Chroma 63200 series ideal for automatic system integration.Power Supply TestingPower supplies play a critical role in electrical and electronic devices. They have diversified into several different configurations for various applications. For example, AC/AC power supplies are used for UPS and AVR, AC/DC power supplies are used for server power supplies, and DC/AC power supplies areused for inverters that transfer battery power to AC for home appliances. Lastly, DC/DC converters are widely used in battery powered devices such ascellular phones and laptop computers. With four different load modes, Chroma 63200 series electronic loads are capable of testing many different DC output power supplies either directly or via a rectifier. They can also be used to test AC output power supplies.Server Power SupplyUPS/AVRRectifier1. Power Switch2. LED Display: Voltage read back3. LED Display: Current/ ohm read back4. LED Display: Power read back5. LCD Display: For setting and editing6. Rotary knob: To adjust the loading and parameter setting7. Numeric key: For data setting8. Function key: To select load mode, control mode, and define the reading specification9. System key:For system config and data store, recall 10. Load terminal11. Voltage sense terminal 12. RS-485 connector 13. GPIB connector 14. RS-232C connector15. Voltage monitor output:Analog output which indicates the voltage waveform 16. Current monitor output: Analog output which indicates the current waveform 17. External V reference:External programming voltage inputModel: 63203, 63204panel deScriptionThe 63200 series can be operated from the front panel or controlled by softpanel software. The user friendly software includes all the functions of 63200 series, and is easy to understand and operate. The 63200 series can be configured with either GPIB or RS-232 interfaces as an option for remote control and automated testing applications.Sequence TestBattery Discharge Test Dynamic Test Main Operation Menu OCP Test1002003004005006007008009001000110010020030040050060070080090010001020304050607080901001101201301401501600123456789101100.10.20.30.40.50.60.70.80.9 1.0 1.1102030405060708090100V-I Curve :Model 63201/ 63203/ 63205/ 63206/ 63207/ 63208/ 63209Low Voltage Operating :Model 63201/ 63203/ 63205/ 63206/ 63207/ 63208/ 63209Low Voltage Operating :Model 63202/ 63204/ 63210/ 63211/ 63212V-I Curve :Model 63202/ 63204/ 63210/ 63211/ 63212 Voltage(V)Voltage(V)Current(A)Current(A)Current (A)Current (A)Voltage (V)Voltage (V) Note: All specifications are measured at load input terminals. (Ambient temperature of +25)Model 63208 / 63209 / 63210Model 63211 / 63212Model 63203 / 63204Model 63201 / 63202Model 63205Model 63206 / 63207NOTE*1 : The power rating specifications at ambient temperature=25˚C and see the diagram below for power derating. NOTE*2 : If the operating voltage exceeds the rated voltage for 1.1 times, it would cause permanent damage to the device. NOTE*3 : S (siemens) is the SI unit of conductance, equal to one reciprocal ohm.NOTE*4 : The Vin must be greater than min. operating voltage of each model.NOTE*5 : Setting error will be 1% for R<0.005 at CRL range.NOTE*6 : The Vin must be greater than 7V of each model.NOTE*7 : Power F.S. = Vrange x Irange F.S.63200-E-201408-1000Worldwide Distribution andService NetworkJAPANCHROMA JAPAN CORP .472 Nippa-cho, Kouhoku-ku, Yokohama-shi, Kanagawa,223-0057 JapanTel: +81-45-542-1118Fax: +81-45-542-1080http://www.chroma.co.jp E-mail:******************U.S.A.CHROMA SYSTEMS SOLUTIONS, INC.19772 Pauling, Foothill Ranch, CA 92610Tel: +1-949-600-6400Fax: +1-949-600-6401 E-mail:*******************Developed and Manufactured by :HEADQUARTERS CHROMA ATE INC.66 Hwaya 1st Rd., KueishanHwaya Technology Park,Taoyuan County 33383,Taiwan Tel: +886-3-327-9999Fax: +886-3-327-8898 E-mail:******************EUROPECHROMA ATE EUROPE B.V.Morsestraat 32, 6716 AH Ede,The Netherlands Tel: +31-318-648282Fax: +31-318-648288 E-mail:******************CHINA CHROMA ELECTRONICS(SHENZHEN) CO., LTD.8F, No.4, Nanyou Tian An Industrial Estate, Shenzhen, China PC: 518052Tel: +86-755-2664-4598Fax: +86-755-2641-9620A632001A632004A63200663201 : DC Electronic Load 80V/300A/2.6kW 63202 : DC Electronic Load 600V/50A/2.6kW 63203 : DC Electronic Load 80V/600A/5.2kW 63204 : DC Electronic Load 600V/100A/5.2kW 63205 : DC Electronic Load 80V/180A/6.5kW 63206 : DC Electronic Load 80V/600A/10.4kW 63207 : DC Electronic Load 80V/300A/10.4kW 63208 : DC Electronic Load 80V/600A/15.6kW 63209 : DC Electronic Load 80V/1000A/15.6kW 63210 : DC Electronic Load 600V/150A/14.5kW 63211 : DC Electronic Load 1000V/150A/15.6kW 63212 : DC Electronic Load 1000V/150A/10kW A632001 : Remote ControllerA632002 : Load Cable 38mm/242A/200cmx2A632003 : Load Cable 80mm/390A/200cmx2A632004 : Sync. Link Box for 6330A & 63200 series A632005 : Softpanel for 63200 seriesA632006 :NI USB-6211 Bus-Powered Multifunction DAQnumber of parallel load unitS and ratinGorderinG information。

2N5566中文资料

Unit

V mA pA nA pA nA W V

mS mS mS

pF nV⁄ √Hz dB

mV mV/ _C

dB NCBD

8-2

Document Number: 70254 S-04031—Rev. D, 04-Jun-01

元器件交易网

2N5564/5565/5566

元器件交易网

2N5564/5565/5566

Vishay Siliconix

Matched N-Channel JFET Pairs

PRODUCT SUMMARY

Part Number

2N5564 2N5565 2N5566

VGS(off) (V)

–0.5 to –3 –0.5 to –3 –0.5 to –3

76

Notes a. Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

b. Pulse test: PW v300 ms duty cycle v3%. c. This parameter not registered with JEDEC.

160

0 –10

rDS(on) – Drain-Source On-Resistance ( W )

120 VGS(off) = –2 V

80

40

gfs – Forward Transconductance (mS)

0 –55 –35 –15 5

APPLICATIONS

D Wideband Differential Amps D High-Speed,

MAX44242 低输入偏置电流、低噪声操作放大器 (OP 放大器) 评估套件说明书

General DescriptionThe MAX44242 evaluation kit (EV kit) provides a prov-en design to evaluate the MAX44242 low-input biascurrent, low-noise operational amplifier (op amp) in an8-pin µMAX ® package. The EV kit circuit is preconfig-ured as noninverting amplifiers, but can be adapted toother topologies by changing a few components. Thecomponent pads accommodate 0805 packages, makingthem easy to solder and replace. The EV kit comes with aMAX44242AUA+ installed.Features and Benefits●Accommodates Multiple Op-Amp Configurations●Rail-to-Rail Outputs●Accommodates Easy-to-Use 0805 Components● 2.7V to 20V Single Supply or ±1.35V to Q 10V DualSupplies●Proven PCB Layout●Fully Assembled and TestedQuick StartRequired Equipment●MAX44242 EV kit●+5V, 10mA DC power supply (PS1)●Two precision voltage sources●Two digital multimeters (DMMs)Procedure The EV kit is fully assembled and tested. Follow the steps below to verify board operation:1) Verify that the jumpers are in their default position, as shown in Table 1.2) Connect the positive terminal of the +5V supply to VDD and the negative terminal to GND and VSS.3) Connect the positive terminal of the precision voltage source to INAP . Connect the negative terminal of the precision voltage source to GND.4) Connect INAM to GND.5) Connect the positive terminal of the second precision voltage source to the INBP pad. Connect the nega-tive terminal of the precision voltage source to GND.6) Connect INBM to GND.7) Connect the DMMs to monitor the voltages on OUTA and OUTB. With the 10kΩ feedback resistors and 1kΩ series resistors, the gain of each noninverting amplifier is +11.8) Turn on the +5V power supply.9) Apply 100mV from the precision voltage sources. Observe the output at OUTA and OUTB on the DMMs. Both should read approximately +1.1V.10) Apply 400mV from the precision voltage sources. Both OUTA and OUTB should read approximately +4.4V.19-6917; Rev 0; 2/14Ordering Information appears at end of data sheet.μMAX is a registered trademark of Maxim Integrated Products, Inc.Detailed Description of HardwareThe MAX44242 EV kit provides a proven layout for theMAX44242 low input bias current, low-noise dual op amp.The IC is a single-supply dual op amp whose primaryapplication is operating in the noninverting configuration;however, the IC can operate with a dual supply as long asthe voltage across the VDD and GND pins of the IC do notexceed the absolute maximum ratings. When operatingwith a single supply, short VSS to GND.Op-Amp Configurations The IC is a single-supply dual op amp ideal for differential sensing, noninverting amplification, buffering, and filter-ing. A few common configurations are shown in the next few sections.The following sections explain how to configure one of the device’s op amps (op-amp A). To configure the device’s second op amp (op-amp B), the same equations can be used after modifying the component reference designa-tors. For op-amp B, the equations should be modified by adding 10 to the number portion of the reference designa-tors (e.g., for the noninverting configuration, equation R1 becomes R11 and R5 becomes R15).Noninverting ConfigurationThe EV kit comes preconfigured as a noninvertingamplifier. The gain is set by the ratio of R5 and R1. TheEV kit comes preconfigured for a gain of +11. The outputvoltage for the noninverting configuration is given by the equation below:OUTA INAP R5V 1V R1 =+ *Default position.JUMPERSHUNT POSITION DESCRIPTION JU1Installed*Connects INAM to R1. Also shorts capacitor C5.OpenConnects INAM to R1 through capacitor C5. When AC-coupling is desired, remove the shunt and install capacitor C5. JU2Installed*Connects INAP to JU3 position 1. Also shorts capacitor C6. OpenConnects INAP to JU3 position 1 through capacitor C6. When AC-coupling is desired, remove the shunt and install capacitor C6. JU31-2*Connects INAP to JU2 and C6 through R2 and R82-3Connects INAP to GND through R2 and R8JU4Installed*Connects OUTA to OUTA OpenConnects OUTA to OUTA through capacitor C10. When AC-coupling is desired, remove the shunt and install capacitor C10. JU5Installed*Connects INBM to R11. Also shorts capacitor C15. OpenConnects INBM to R11 through capacitor C15. When AC-coupling is desired, remove the shunt and install capacitor C15. JU6Installed*Connects INBP to JU6 position 1. Also shorts capacitor C16. OpenConnects INBP to JU6 position 1 through capacitor C16. When AC-coupling is desired, remove the shunt and install capacitor C16. JU71-2*Connects INBP to JU7 and C16 through R12 and R182-3Connects INBP to GND through R12 and R18JU8Installed*Connects OUTB to OUTB Open Connects OUTB to OUTB through capacitor C20. When AC-coupling is desired, remove the shunt and install capacitor C20.R1–R3, and R5 with appropriate resistors. WhenR1 = R2 and R3 = R5, the CMRR of the differential ampli-fier is determined by the matching of the resistor ratiosR1/R2 and R3/R5.OUTA INAP INAM V GAIN (V V )=−where:R5R3GAIN R1R2==Sallen-Key Filter ConfigurationThe Sallen-Key filter topology is ideal for filtering sensorsignals with a second-order filter and acting as a buffer.Schematic complexity is reduced by combining the filterand buffer operations. The EV kit can be configured ina Sallen-Key topology by replacing and populating afew components. The Sallen-Key topology is typicallyconfigured as a unity-gain buffer, which can be done byreplacing R1 and R5 with 0Ω resistors and short JU2. Thenoninverting signal is applied to the INAP test point withJU2 short and short pins 1-2 on JU3 or do the same on theINBP pad similarly. The filter component pads are R2–R4,and R8, where some have to be populated with resistorsand others with capacitors.Lowpass Sallen-Key FilterTo configure the Sallen-Key as a lowpass filter, populatethe R2 and R8 pads with resistors, and populate the R3and R4 pads with capacitors. The corner frequency and Qare then given by:C R3R2R8f Q ==the R3 and R4 pads with resistors and populate the R2 and R8 pads with capacitors. The corner frequency and Qare then given by:C R4R2R8f Q ==Transimpedance Application To configure op-amp U1-A as a transimpedance amplifier (TIA), replace R1 with a 0Ω resistor and install a shunt on jumper JU1 and shunt on pins 2-3 on jumper JU3. The output voltage of the TIA is the input current multiplied by the feedback resistor:OUT IN BIAS OS V (I I )R4V =+×+where R4 is installed as a 10kΩ resistor, I IN is defined as the input current source applied at the INAM pad, I BIAS is the input bias current, and V OS is the input offset voltage of the op amp. Use capacitor C8 (and C7, if applicable) to stabilize the op amp by rolling off high-frequency gain due to a large cable capacitance. Similarly, we can configure op-amp U1-B for transimpedance application.Capacitive Loads Some applications require driving large capacitive loads. To improve the stability of the amplifier, replace R6 (R16 for U1-B) with a suitable resistor value to improve ampli-fier phase margin. The R6/C9 (R16/C19 for U1-B) filter can also be used as an anti-alias filter, or to limit amplifier output noise by reducing its output bandwidth.DESIGNATION QTY DESCRIPTIONC1, C320.1µF ±10%, 25V X7R ceramic capacitors (0805)C2, C424.7µF ±10%, 25V X5R ceramic capacitors (0805)C5–C10, C15–C200Not installed, ceramic capacitors(0805)GND2Black test points INAM, INAP,INBM, INBP,OUTA, OUTB,VDD, VSS8Red test pointsJU1, JU2,JU4–JU6, JU862-pin headers JU3, JU723-pin headers DESIGNATION QTY DESCRIPTION R1, R2,R11, R1241kΩ ±1% resistors (0805)R3, R4, R7,R13, R14, R170Not installed, resistors (0805) R5, R15210kΩ ±1% resistors (0805)R6, R8,R16, R1840Ω ±5% resistors (0805) TP1, TP20Not installed, miniature test points U11Dual low-power, rail-to-rail I/O opamp (8 µMAX)Maxim MAX44242AUA+—8Shunts—1PCB: MAX44242 EVKITFigure 1. MAX44242 EV Kit SchematicFigure 3. MAX44242 EV Kit PCB Layout—Component SideComponent SideFigure 4. MAX44242 EV Kit PCB Layout—Solder SidePART TYPE MAX44242EVKIT#EV Kit #Denotes ROHS compliant.Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time.REVISIONNUMBERREVISION DATE DESCRIPTION PAGES CHANGED 02/14Initial release —For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated’s website at .。

分析器设备-AMP03精确差分放大器手册说明书

REV.FInformation furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.Tel: 781/329-4700 Fax: 781/326-8703© 2003 Analog Devices, Inc. All rights reserved.aAMP03Precision, Unity-Gain Differential AmplifierFEATURESHigh CMRR: 100 dB TypLow Nonlinearity: 0.001% Max Low Distortion: 0.001% Typ Wide Bandwidth: 3MHz Typ Fast Slew Rate: 9.5V/s Typ Fast Settling (0.01%): 1s Typ Low CostAPPLICATIONSSumming AmplifiersInstrumentation Amplifiers Balanced Line Receivers Current-Voltage Conversion Absolute Value Amplifier4to 20mA Current TransmitterPrecision Voltage Reference ApplicationsLower Cost and Higher Speed Version of INA105GENERAL DESCRIPTIONThe AMP03 is a monolithic unity-gain, high speed differential amplifier. Incorporating a matched thin film resistor network,the AMP03 features stable operation over temperature without requiring expensive external matched components. The AMP03is a basic analog building block for differential amplifier and instrumentation applications.The differential amplifier topology of the AMP03 both amplifies the difference between two signals and provides extremely high rejection of the common-mode input voltage. By providing common-mode rejection (CMR) of 100 dB typical, the AMP03solves common problems encountered in instrumentation design.As an example, the AMP03 is ideal for performing either addi-tion or subtraction of two signals without using expensive externally matched precision resistors. The large common-mode rejection is made possible by matching the internal resistors to better than 0.002% and maintaining a thermally symmetric layout. Additionally, due to high CMR over frequency, the AMP03 is an ideal general amplifier for buffering signals in a noisy environment into data acquisition systems.The AMP03 is a higher speed alternative to the INA105.Featuring slew rates of 9.5 V/µs and a bandwidth of 3 MHz, the AMP03 offers superior performance to the INA105 for high speed current sources, absolute value amplifiers, and summing amplifiers.FUNCTIONAL BLOCK DIAGRAMSENSE +V CC OUTPUT –V EEREFERENCEPIN CONNECTIONS8-Lead PDIP (P Suffix)NC = NO CONNECT–IN +IN V–8-Lead SOIC (S Suffix)NC = NO CONNECTSENSEOUTPUT V+NCHeader (J Suffix)–IN 2V–NC = NO CONNECTAMP03* Product Page Quick Links Last Content Update: 11/01/2016Comparable PartsView a parametric search of comparable partsDocumentationApplication Notes•AN-244: A User's Guide to I.C. Instrumentation Amplifiers •AN-245: Instrumentation Amplifiers Solve Unusual Design Problems•AN-348: Avoiding Passive-Component Pitfalls•AN-589: Ways to Optimize the Performance of aDifference Amplifier•AN-671: Reducing RFI Rectification Errors in In-AmpCircuitsData Sheet•AMP03: Military Data Sheet•AMP03: Precision, Unity-Gain Differential Amplifier Data SheetTechnical Books• A Designer's Guide to Instrumentation Amplifiers, 3rdEdition, 2006Reference MaterialsTechnical Articles•Auto-Zero Amplifiers•High-performance Adder Uses Instrumentation Amplifiers •Input Filter Prevents Instrumentation-amp RF-Rectification Errors•The AD8221 - Setting a New Industry Standard forInstrumentation AmplifiersDesign Resources•AMP03 Material Declaration•PCN-PDN Information•Quality And Reliability•Symbols and FootprintsDiscussionsView all AMP03 EngineerZone DiscussionsSample and BuyVisit the product page to see pricing optionsTechnical SupportSubmit a technical question or find your regional support number* This page was dynamically generated by Analog Devices, Inc. and inserted into this data sheet. Note: Dynamic changes to the content on this page does not constitute a change to the revision number of the product data sheet. This content may be frequently modified.–2–REV. FAMP03–SPECIFICATIONSELECTRICAL CHARACTERISTICS AMP03F AMP03B AMP03GParameter Symbol Conditions Min Typ Max MinTyp Max Min Typ Max UnitOffset Voltage V OSV CM = 0 V–400+10+400–700+20+700–750+25+750µVGain ErrorNo Load, V IN = ±10 V,R S = 0 Ω0.000040.0080.000040.0080.0010.008%Input Voltage RangeIVR (Note 1)±20±20±20VCommon-Mode Rejection CMR V CM = ±10 V8510080958095dB Power Supply Rejection Ratio PSRR V S = ±6 V to ±18 V 0.6100.6100.710µV/V Output SwingV O R L = 2 k Ω±12±13.7±12±13.7±12±13.7VShort-Circuit Current Limit I SC Output Shorted to Ground +45/–15+45/–15+45/–15mASmall-Signal Bandwidth (–3 dB)BW R L = 2 k Ω333MHz Slew RateSR R L = 2 k Ω69.569.569.5V/µs Capacitive Load Drive Capability C L No Oscillation 300300300pF Supply CurrentI SYNo Load2.53.5 2.53.5 2.53.5mANOTES 1Input voltage range guaranteed by CMR test.Specifications subject to change without notice.ELECTRICAL CHARACTERISTICS AMP03BParameterSymbol ConditionsMin TypMax Unit Offset Voltage V OS V CM = 0 V–1500+150+1500µV Gain ErrorNo Load, V IN = ±10 V, R S = 0 Ω0.00140.02%Input Voltage RangeIVR ±20V Common-Mode Rejection CMR V CM = ±10 V 7595dB Power Supply Rejection RatioPSRR V S = ±6 V to ±18 V 0.720µV/V Output Swing V O R L = 2 k Ω±12±13.7V Slew RateSR R L = 2 k Ω9.5V/µs Supply CurrentI SYNo Load3.04.0mASpecifications subject to change without notice.ELECTRICAL CHARACTERISTICS AMP03F AMP03G ParameterSymbol ConditionsMin Typ Max Min Typ Max UnitOffset Voltage V OS V CM = 0 V–1000+100+1000–2000+200+2000µV Gain ErrorNo Load, V IN = ±10 V, R S = 0 Ω0.00080.0150.0020.02%Input Voltage RangeIVR ±20±20V Common-Mode Rejection CMR V CM = ±10 V 80957590dB Power Supply Rejection RatioPSRR V S = ±6 V to ±18 V 0.7151.015µV/V Output Swing V O R L = 2 k Ω±12±13.7±12±13.7V Slew RateSR R L = 2 k Ω9.59.5V/µs Supply CurrentI SYNo Load2.64.02.64.0mASpecifications subject to change without notice.(@ V S= ؎15 V, T A= +25؇C, unless otherwise noted.)(@ V S= ؎15 V, –55؇C ≤ T A≤ +125؇C for B Grade)(@ V S= ؎15 V, –40؇C ≤ T A≤ +85؇C for F and G Grades)–3–REV. F AMP03(@ V = ؎15 V, T = 25؇C, unless otherwise noted.)*CAUTIONESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000V readily accumulate on the human body and test equipment and can discharge without detection.Although the AMP03 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.DIE SIZE 0.076 inch ؋ 0.076 inch, 5,776 sq. mmAMP03–Typical Performance Characteristics–4–REV. FTPC 1.Small Signal TransientResponse TPC rge Signal Transient ResponseI N P U T O F F S E T V O L T A G E (V )1000800–8000–200–400–600600200400TEMPERATURE (؇C)TPC 7.Input Offset Voltage vs. TemperatureFREQUENCY (Hz)C O M M O N -M ODE R E J E C T I O N (d B )TPC mon-Mode Rejection vs. Frequency FREQUENCY (Hz)P O W E R S U P P L Y R E J E C T I O N (d B )01101M1001k 10k 100k 904030201080705060TPC 5.Power Supply Rejection vs.Frequency FREQUENCY (Hz)C L O S ED -L O O P G A I N (d B )50401001k10M10k 100k 1M 1003020 TPC 8.Closed-Loop Gain vs. FrequencyFREQUENCY (Hz)T HD +N (%)0.10.0100.00010.001TPC 3.Total Harmonic Distortion vs. FrequencyFREQUENCY (Hz)D I M (%)TPC 6.Dynamic Intermodulation Distortion vs. FrequencyFREQUENCY (Hz)O U T P U T I M P E D A N C E (⍀)1081001k1M10k 100k 642TPC 9.Closed-Loop Output Impedance vs. FrequencyAMP03–5–REV. F TEMPERATURE (؇C)G A I N E R R O R (%)0.0030.0020.000–0.001–0.002–0.003TPC 10.Gain Error vs. Temperature SUPPLY VOLTAGE (V)S U P P L Y C U R R EN T (m A )4213TPC 13.Supply Current vs. Supply VoltageFREQUENCY (Hz)120100080604020H z )V O L T A G E N O I S E D E N S I T Y (n / TPC 16.Voltage Noise Density vs.Frequency+10V 0V –10VNOTE: EXTERNAL AMPLIFIER GAIN = 1000;THEREFORE, VERTICAL SCALE = 10V/DIV.TPC 19.Voltage Noise from 0kHz to 10 kHzTEMPERATURE (؇C)S L E W R A T E (V /s )136121098711TPC 11.Slew Rate vs. TemperatureOUTPUT SOURCE CURRENT (mA)17.56361218243015.012.510.05.02.57.5M A X I M U M O U T P U T V O L T A G E (V )TPC 14.Maximum Output Voltage vs. Output Current (Source)0.1 TO 10Hz PEAK-TO-PEAK NOISETPC 17.Low Frequency Voltage NoiseTEMPERATURE (؇C)S U P P L Y CU R R E N T (m A )65324 TPC 12.Supply Current vs. TemperatureOUTPUT SINK CURRENT (mA)–17.5–2–12–4–6–8–10–15.0–12.5–10.0–5.0–2.5–7.5M A X I M U M O U T P U T V O L T A G E (V)TPC 15.Maximum Output Voltagevs. Output Current (Sink)NOTE: EXTERNAL AMPLIFIER GAIN = 1000;THEREFORE, VERTICAL SCALE = 10V/DIV.TPC 18.Voltage Noise from 0kHz to 1kHzAMP03–6–REV. FGROUND REFERENCE 1GROUND REFERENCE 2= –V SIGNALFigure 1.AMP03 Serves to Reject Common-Mode Volt- ages in Instrumentation Systems. Common-Mode Volt- ages Occur Due to Ground Current Returns. V SIGNAL and E CM Must Be within the Common-Mode Range of AMP03.APPLICATIONS INFORMATIONThe AMP03 represents a versatile analog building block. In order to capitalize on the fast settling time, high slew rate, and high CMR, proper decoupling and grounding techniques must be employed. Figure 1 illustrates the use of 0.1µF decoupling capacitors and proper ground connections.MAINTAINING COMMON-MODE REJECTIONIn order to achieve the full common-mode rejection capability of the AMP03, the source impedance must be carefully con-trolled. Slight imbalances of the source resistance will result in a degradation of dc CMR—even a 5Ω imbalance will degrade CMR by 20dB. Also, the matching of the reactive source impedance must be matched in order to preserve the CMRR over frequency.APPLICATION CIRCUITS+IN E 2–IN E E 0 = E 2 – E 1Figure 2.Precision Difference Amplifier. Rejects Common-Mode Signal = (E 1 + E 2)/2 by 100dBE 0 = –E 1Figure 3.Precision Unity-Gain Inverting Amplifier–10V OUTFigure 4.؎10 V Precision Voltage Reference–5V OUT+5V OUTFigure 5.؎5 V Precision Voltage ReferenceE 0 = E 1 + E 2Figure 6.Precision Summing AmplifierR2R1E 0 = (R2/R1+1)E 1= E 22Figure 7.Precision Summing Amplifier with GainAMP03–7–REV. F System Design Suggested Op Amp RequirementFor A1 and A2Source Impedance Low, Need Low OP27, OP37Voltage Noise PerformanceOP227 (Dual Matched)OP270 (Dual)OP271OP470OP471Source Impedance HighOP80(R S ≥ 15 k Ω). Need Low Current OP41 NoiseOP43OP249OP97Require Ultrahigh Input ImpedanceOP80OP97OP41OP43Need Wider Bandwidth and High OP42SpeedOP43OP249E E Figure 8.Differential Input Voltage-to-Current Converter for Low I OUT . OP80EJ maintains 250 fA max input current,allowing I O to be less than 1pA.–IN E +IN E E 0 OUTPUTE 0 = (1 + 2R2/R1) (E 2 – E 1)Figure 9.Suitable Instrumentation Amplifier Requirements Can Be Addressed by Using an Input Stage Consisting of A1,A2, R1, and R2. The following matrix suggests a suitable amplifier.AMP03–8–REV. FOUTLINE DIMENSIONSC 00249–0–12/03(F )Revision HistoryLocationPage12/03—Data Sheet changed from REV. E to REV. F.Changes to ELECTRICAL CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2Changes to ORDERING GUIDE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3Updated OUTLINE DIMENSIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .78-Lead Plastic Dual In-Line Package [PDIP][P Suffix](N-8)Dimensions shown in inches and (millimeters)CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FORREFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGNCOMPLIANT TO JEDEC STANDARDS MO-095AA8-Lead Small Outline Package [SOIC][S Suffix](R-8)Dimensions shown in millimeters and (inches)45؇PLANECONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGNCOMPLIANT TO JEDEC STANDARDS MS-012AA8-Lead Metal Can [TO-99][J Suffix](H-08B)Dimensions shown in inches and (millimeters)CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETERS DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FORREFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGNCOMPLIANT TO JEDEC STANDARDS MO-002AK。

Meggitt MPC4 机器人保护卡型号M版特色说明书

Information contained in this document may be subject to Export Control Regulations of the European Union, USA or other countries. Each recipient of this document is responsible for ensuring that transfer or use of any information contained in this document complies with all relevant Export ControlRegulations. ECN N/A.MPC4Machinery protection card Type MPC4FEATURES»From the Vibro-Meter ® product line»Continuously online machinery protection card »Real-time measurement and monitoring using state-of-the-art DSP techniques» 4 dynamic signal inputs and 2 tachometer (speed) inputs, all individually programmable »Programmable broad-band and narrow-band filters»Simultaneous amplitude and phase monitoring in order tracking mode»Programmable Alert, Danger and OK set points »Adaptive Alert and Danger levels»Front panel BNC connectors for easy analysis of raw signals»7 front panel LEDs show status and alarms »Integrated power supply for many Vibro-Meter front-ends, including ICP accelerometers and proximity systems»Live insertion and removal of cards»Available in ‘standard’, ‘separate circuits’ and‘safety’ (SIL) versions‘Standard’MPC4‘Safety’MPC4Machinery protection card MPC4DESCRIPTIONMPC4 cardThe MPC4 machinery protection card is the central element in the VM600 series machinery protection system (MPS), from Meggitt Sensing Systems’Vibro-Meter® product line. This very versatile card is capable of measuring and monitoring up to four dynamic signal inputs and up to two speed inputs simultaneously.The dynamic signal inputs are fully programmable and can accept signals representing acceleration, velocity and displacement (proximity), among others. On-board multi-channel processing allows measurement of various physical parameters, including relative and absolute vibration, S max, eccentricity, thrust position, absolute and differential housing expansion, displacement and dynamic pressure.Digital processing includes digital filtering, integration or differentiation (if required), rectification (RMS, mean value, true peak or true peak-to-peak), order tracking (amplitude and phase) and measurement of the transducer-target gap.The speed (tachometer) inputs accept signals from a variety of speed sensors, including systems based on proximity probes, magnetic pulse pick-up sensors or providing TTL signals. Fractional tacho ratios are also supported.The calibration may be expressed in metric or imperial units. Alert and Danger set points are fully programmable, as are alarm time delay, hysteresis and latching. The Alert and Danger levels can be adapted as a function of the speed or any external information.A digital output is available internally (on the corresponding IOC4T card) for each alarm level. These alarm signals may be routed on a bus within the VM600 rack to drive relays on optional relay cards (such as the IRC4 and RLC16).The processed dynamic (vibration) signals and speed signals are available at the rear of the rack (on the front panel of the IOC4T) as analog output signals. Voltage-based (0to10V) and current-based(4to20mA) signals are provided.The MPC4 performs a self-test and diagnostic routine on power-up. In addition, the card’s built-in“OK System” continuously monitors the level of signals provided by the sensors and indicates any problem due to a broken transmission line, faulty transducer or conditioner.An LED indicator on the MPC4 front panel indicates whether a processing or hardware error has occurred. Six additional LEDs (one per input channel) indicate whether the OK System has detected a fault and whether an alarm has occurred on the channel.The MPC4 card is available in three versions: a‘standard’ version, a ‘separate circuits’ version and a ‘safety’ (SIL) version, all of which function as a card pair using an IOC4T input/o utput card.‘Standard’ and ‘safety’ (SIL) versions of the MPC4 Both the ‘standard’ version and the ‘safety’ (SIL) version of the MPC4 card are certified to IEC61508 and ISO13849.The ‘standard’ MPC4 card is the original version, intended for safety systems using a VM600 rack with a limited range of cards, that is, ‘standard’ MPC4/ IOC4T card pairs and RLC16 relay cards. It has a VME-compatible slave interface and is fully software configurable via RS-232 (on the front panel of the card) or VME.The ‘safety’ MPC4 card, also known as the MPC4 SIL, was developed to permit a wider range of installation options. Specifically, VM600 racks that also contain condition monitoring cards (such as the CMC16 and XMx16) and relay cards (such as the IRC4 and RLC16). To safety certify these configurations, it was necessary to ensure that the ‘safety’ MPC4 is isolated from the other cards in a VM600 rack, so that there is no possibility of its configuration being inadvertently modified. Therefore, the ‘safety’ (SIL) version of the MPC4 does not include a VME-compatible slave interface, nor does it provide all of the signal processing capabilities of the ‘standard’ MPC4 card (see Specifications –‘standard’ and ‘separate circuits’ MPC4 cards only on page6).Segregation of MPS and CMSThe VM600 rack, machinery protection cards, condition monitoring cards and associated software are designed for compliance with the machinery protection system (MPS) and condition monitoring system (CMS) “segregation” requirements of the API670 standard, which ensures that the functionality of the MPS does not depend on and is notMachinery protection cardMPC4 DESCRIPTION (continued)compromised in any way by the operation of the CMS.So although machinery protection cards and condition monitoring cards can easily share sensor signals from measurement chains, MPC4/IOC4T card pairs do not share any communication buses with XMx16/XIO16T condition monitoring card pairs in a VM600 rack, and MPC4/IOC4T card pairs are configured and operated using the VM600 MPSx software (while XMx16/XIO16T card pairs are configured and operated using the VibroSight® software).Applications informationThe MPC4 cards are highly suitable for machinery protection in a wide range of industrial applications. For further information on the use of MPC4 cards, refer to the VM600 Functional Safety Manual MAVM600-FS/E. For specific applications, contact your nearest Meggitt Sensing Systems representative.SPECIFICATIONS – ALL MPC4 CARDSDynamic signal inputsNumber of inputs:4 per MPC4 cardDC range:0 to +20 V or 0 to −20 VAC range:±10 V (maximum)Common mode voltage range:−50 to +50 VCMRR:>60 dB at 50 HzCrosstalk:−72 dBInput impedance:200 kΩCurrent input range•DC signals:0 to 25 mA•AC signals:±8 mA (maximum)Analog AC frequency band(without integration):0.1 Hz to 10 kHzAnalog AC frequency band(with integration):2.5 Hz to 10 kHzAnalog frequency band for throughput toother cards and buffered AC outputs:DC to 60 kHz (−3 dB)Current measuring resistor:324.5ΩProcessing optionsBroad-bandFiltering options:High-pass, low-pass or band-passLP/H P ratio in pass band:500 (maximum)Ripple:±0.3 dBSlope:6 to 60 dB/o ctave (software configurable) Attenuation outside pass band:>50 dBAmplitude accuracy:±1% of full-scaleLinearity error:<±1%Equivalent input noise(without integration):<200 µV RMSMachinery protection card ArrayMPC4SPECIFICATIONS – ALL MPC4 CARDS(continued)Narrow-band (tracking)The ‘standard’ and ‘separate circuits’ versions of the MPC4 card support narrow-band tracking (see Specifications – ‘standard’ and ‘separate circuits’ MPC4 cards only on page6).The ‘safety’ MPC4 card does not support narrow-band tracking.Relative shaft vibrationFrequency band•Vibration:0.1 Hz to 10 kHz•Gap/p osition:DC to 1 HzAmplitude accuracy•Vibration:±1.2% of full-scale•Gap/p osition:±1% of full-scale•Linearity error:<±1%Initial gap/o ffset compensation:AvailableBuffered (raw) dynamic signal outputsThese signals are available on the MPC4 card’s BNC outputs and the IOC4T card’s raw outputs.Frequency range:DC to 10 kHz (−0.1 dB or 1%).DC to 60 kHz (−3 dB).Admissible load on output:>50 kΩAmplitude error:<2%Phase error:<5° (DC to 10 kHz)Transfer ratio•Voltage input:1 V/V•Current input:0.3245 V/m ASpeed/p hase reference inputs and outputsThe ‘standard’ and ‘separate circuits’ versions of the MPC4 card support speed/p hase reference inputs and outputs (see Specifications – ‘standard’ and ‘separate circuits’ MPC4 cards only on page6).The ‘safety’ MPC4 card does not support speed/p hase reference inputs and outputs.Alarm programmingLevel detectors•Vibration systems:Over-level switching (A+, D+) and under-level switching (A−, D−)•Accelerometer systems:Over-level switching (A+, D+)•Speed channel:2 Alert levels (A−, A+)Alarm scanning interval:100 ms (maximum)Alarm level value:User-programmable within rangeHysteresis:User-programmable within rangeLatching:User-programmable within rangeAlarm delay time:User-programmable within rangeAlarm outputs:Individual alarms and common alarms (open-collector transistor) Adaptation criteria (for adaptive:Speed or digital inputmonitoring)Logical combinations:AND, OR, majority voting logicNumber of logical combinations:8 basic functions and 4 advanced functionsMachinery protection cardMPC4 SPECIFICATIONS – ALL MPC4 CARDS(continued)OK systemRange:−20 to +20 VOperating principle•Powered sensors:DC voltage monitoring (open circuit and short circuit line check)•Unpowered sensors:Open circuit line check onlyTransducer power supplyVoltage power supply:+27.2 V ±5% in the range 0 to 25 mA.−27.2 V ±5% in the range 0 to 25 mA.+15.0 V ±5% in the range 0 to 25 mA.Current power supply: 6.16 mA ±5% in the range 1 to 23 VOver-current protection (on-board):11.0 A on +5 V linePower supply to MPC4 cardSupply voltage:5 V DC ±5% and ±12 V DCConsumption from +5 V DC supply:12.5 W, plus an additional 1 W per sensor usedConsumption from ±12 V DC supply:2.5 W (maximum)CommunicationsVME bus:D16 / A24 slave mode.The ‘standard’ and ‘separate circuits’ versions of the MPC4 card includea VME bus. The ‘safety’ MPC4 card does not include a VME bus.RS-232 port:Configuration port, proprietary protocolBus to IOC4T card:IP (Industry Pack)Notes: The ‘standard’ and ‘separate circuits’ versions of the MPC4 card are fully software configurable viaRS-232 or VME. The ‘safety’ MPC4 card is fully software configurable via RS-232 only.EnvironmentalOperating•Temperature:−25 to +65°C (−13 to +149°F)•Humidity:0 to 90% non-condensingStorage•Temperature:−40 to +85°C (−40 to +185°F)•Humidity:0 to 95% non-condensingPhysicalHeight:6U (262 mm, 10.3 in)Width:20 mm (0.8 in)Depth:187 mm (7.4 in)Weight:0.40 kg (0.88 lb)Machinery protection cardMPC4SPECIFICATIONS – ‘STANDARD’ AND ‘SEPARATE CIRCUITS’ MPC4 CARDS ONLYProcessing optionsNarrow-band (tracking)Constant Q filter:Q = 28Frequency range:0.15Hz to 10kHzMax. frequency ratio in selected band:f upper / f lower = 25Rate of change of speed:450 Hz/s ec. (in band 25 to 500 Hz)Order extraction:1/3X, 1/2X, 1X, 2X, 3X, 4XPhase error:<±6° maximum.<±1° typical (with order = 1X).Amplitude accuracy:±1.2%Linearity error:<±1%Speed/p hase reference inputsNumber of inputs:2 per MPC4 cardTriggering method:Crossing of thresholds on rising/f alling edge of signalTriggering thresholds:Rising = 2/3 of peak-peak value, falling = 1/3 of peak-peak valueTacho range:0.016Hz to 50kHz on input.0.016Hz to 1092Hz (1 to 65535RPM) after division by the“wheel teeth number”.Speed resolution:0.001 Hz (internal)Input voltage range:0.4 to 500 Vpp in the range 0.3 Hz to 10 kHz.2.0 to 500 Vpp in the range 10 kHz to 50 kHz.Minimum input voltage for reliable detection•Square-wave input signal:0.8 Vpp (0.016 Hz to 10 kHz).2.0 Vpp (10 kHz to 50 kHz).•Sinusoidal input signal:10 Vpp (0.016 Hz to 1 Hz).2.0 Vpp (1 Hz to 10 Hz).0.8 Vpp (10 Hz to 10 kHz).2.0 Vpp (10 kHz to 50 kHz).Range of DC component:−20 to +20 VFor speed/phase reference input channels, it can be more difficult to achieve the minimum input voltage required when current is selected as the signal transmission mode. Therefore, the 200Ω current-to-voltage conversionresistor used by the MPC4 card for current-modulated input signals should be used in any system designcalculations in order to ensure reliable detection.Speed/p hase reference outputsBNC outputs:TTL compatibleOutputs to IOC4T and:TTL compatibleTacho Bus (VM600 rack)Speed resolution:1 RPM (external)Machinery protection cardMPC4Headquartered in the UK, Meggitt PLC is a global engineering group specializing in extreme environment components and smart sub-systems for aerospace, defence and energy markets.Meggitt Sensing Systems is the operating division of Meggitt specializing in sensing and monitoring systems, which has operated through its antecedents since 1927 under the names of ECET, Endevco, Ferroperm Piezoceramics, Lodge Ignition, Sensorex, Vibro-Meter and Wilcoxon Research. Today, these operations areintegrated under one strategic business unit called Meggitt Sensing Systems, headquartered in Switzerland and providing complete systems, using these renowned brands, from a single supply base.The Meggitt Sensing Systems facility in Fribourg, Switzerland was formerly known as Vibro-Meter SA, but is now Meggitt SA. This site produces a wide range of vibration and dynamic pressure sensors capable of operation in extreme environments, leading-edge microwave sensors, electronics monitoring systems and innovative software for aerospace and land-based turbo-machinery.All statements, technical information, drawings, performance rates and descriptions in this document, whilst stated in good faith, are issued for the sole purpose of giving an approximate indication of the products described in them, and are not binding on Meggitt SA unless expressly agreed in writing. Before acquiring this product, you must evaluate it and determine if it is suitable for your intended application. Unless otherwise expressly agreed in writing with Meggitt SA, you assume all risks and liability associated with its use. Any recommendations and advice given without charge, whilst given in good faith, are not binding on Meggitt SA.Meggitt Sensing Systems takes no responsibility for any statements related to the product which are not contained in a current Meggitt Sensing Systems publication, nor for any statements contained in extracts, summaries, translations or any other documents not authored by Meggitt Sensing Systems. We reserve the right to alter any part of this publication without prior notice.In this publication, a dot (.) is used as the decimal separator and thousands are separated by thin spaces. Example: 12 345.678 90.Sales officesYour local agent Head officeMeggitt Sensing Systems has offices in more than 30 countries. For a complete list, please visit our website.Meggitt SARoute de Moncor 4PO Box 1616CH - 1701 FribourgSwitzerland Tel: +41 26 407 11 11Fax: +41 26 407 13 01ABCDISO 9001FS584089ORDERING INFORMATION To order please specify Type DesignationOrdering number MPC4Machinery protection card: ‘Standard’ version200-510-SSS-1Hh ‘Separate circuits’ version, in accordance with CEI / I EC 60255-5200-510-SSS-2Hh ‘Safety’ (SIL) version, safety certified in accordance with IEC 61508 and ISO 13849200-510-SSS-3HhNote: “SSS” represents the firmware (embedded software) version and “Hh” the hardware version. “H” increments are for major modifications that can affect product interchangeability. “h” increments are for minor modifications that have no effect on interchangeability.。

12-bit Low-power fully differential switched capacitor noncalibrating successive approximation ADC

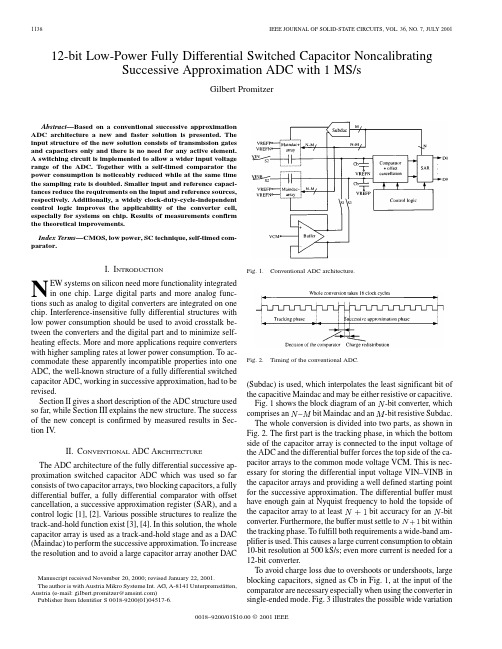

12-bit Low-Power Fully Differential Switched Capacitor Noncalibrating Successive Approximation ADC with1MS/sGilbert PromitzerAbstract—Based on a conventional successive approximation ADC architecture a new and faster solution is presented.The input structure of the new solution consists of transmission gates and capacitors only and there is no need for any active element.A switching circuit is implemented to allow a wider input voltage range of the ADC.Together with a self-timed comparator the power consumption is noticeably reduced while at the same time the sampling rate is doubled.Smaller input and reference capaci-tances reduce the requirements on the input and reference sources, respectively.Additionally,a widely clock-duty-cycle-independent control logic improves the applicability of the converter cell, especially for systems on chip.Results of measurements confirm the theoretical improvements.Index Terms—CMOS,low power,SC technique,self-timed com-parator.I.I NTRODUCTIONN EW systems on silicon need more functionality integrated in one rge digital parts and more analog func-tions such as analog to digital converters are integrated on one chip.Interference-insensitive fully differential structures with low power consumption should be used to avoid crosstalk be-tween the converters and the digital part and to minimize self-heating effects.More and more applications require converters with higher sampling rates at lower power consumption.To ac-commodate these apparently incompatible properties into one ADC,the well-known structure of a fully differential switched capacitor ADC,working in successive approximation,had to be revised.Section II gives a short description of the ADC structure used so far,while Section III explains the new structure.The success of the new concept is confirmed by measured results in Sec-tion IV.II.C ONVENTIONAL ADC A RCHITECTUREThe ADC architecture of the fully differential successive ap-proximation switched capacitor ADC which was used so far consists of two capacitor arrays,two blocking capacitors,a fully differential buffer,a fully differential comparator with offset cancellation,a successive approximation register(SAR),and a control logic[1],[2].Various possible structures to realize the track-and-hold function exist[3],[4].In this solution,the whole capacitor array is used as a track-and-hold stage and as a DAC (Maindac)to perform the successive approximation.To increase the resolution and to avoid a large capacitor array another DACManuscript received November20,2000;revised January22,2001.The author is with Austria Mikro Systeme Int.AG,A-8141Unterpremstätten, Austria(e-mail:gilbert.promitzer@)Publisher Item Identifier S0018-9200(01)04517-6.Fig.1.Conventional ADCarchitecture.Fig.2.Timing of the conventional ADC.(Subdac)is used,which interpolates the least significant bit of the capacitive Maindac and may be either resistive or capacitive. Fig.1shows the block diagram ofan–bit Maindac andanFig.3.Input voltages of the comparator.of the critical output signals of the two Maindacs,which is re-duced by the large blocking capacitors.These additional capac-itors increase the input and reference capacitance of the ADC. For a12-bit converter,the input and reference capacitance is four times larger than that for a10-bit converter.In most appli-cations,an on-chip buffer is used to provide the input signal to the ADC,but with such a large input capacitance,it is very hard to achieve more than250kHz with12-bit accuracy in an inte-grated system.During the tracking phase,the offset cancellation is per-formed.In this phase,the common-mode input voltage of the comparator depends on the voltage VCM,which is derived from the reference voltage.During the successive approxima-tion phase the common mode input voltage of the comparator depends on the common mode voltage of the input signal. So the operating point of the comparator during the offset cancellation is different to that at a critical decision.This difference can be up to one quarter of the supply voltage and might cause a gain error or INL error due to an insufficient common-mode rejection ratio(CMRR)of the comparator. Fig.3illustrates the variation of the operating point for two different input voltages in single ended mode.In both casesthe Fig.4.New ADCarchitecture.Fig.5.Timing of the new ADC architecture.input VINB is connected to the VCM voltage.In Fig.3,the conversion of the maximum negative voltage difference at the input,which corresponds to the digital output code0,is shown on the top whereas the maximum positive voltage difference, which is converted to the digital output code1023,is shown on the bottom.Another problem is the reduction of the input voltage swing at the comparator input due to the voltage divider built by the blocking capacitors.The swing is reduced to one quarter of the supply voltage,which decreases the signal to noise ratio of the whole converter.The second part of the conversion is the successive approx-imation phase,whichtakesFig.6.Input voltages of the comparator.During the tracking phase,the sample switch S1and the input switches S2are on.Both capacitor arrays are charged to (VIN–VINB)/2,even in single-ended mode.In Fig.6,the input voltagesofthecomparatorareshownforthesamesetupasinFig.3. During the whole conversion,no overshoots or undershoots are possible,even without the blocking capacitors.This elimi-nates the need for blocking capacitors and increases the input voltage swing of the comparator to half of the supply,which increases the signal to noise ratio of the whole converter by2. Because of the series connection of the two capacitor arrays and the nonexisting blocking capacitors,it was possible to improve the resolution from10to12bit without rising the capacitive load.This makes the implementation of an on-chip input buffer easier and allows higher frequencies for the input signal.An additional advantage is a more simplified implementation of a power-down option,because the only active component re-maining has enough time to perform the power up.B.Enhanced Range of the Input VoltageFor decoupling the comparator stage from the input voltage during the tracking phase,some additional switches are inserted, as shown in Fig.7and described in[6].Fig.7.Decoupling of the comparatorstage.Fig.8.Self-timedcomparator.Fig.9.Timing of self-timed comparator.In the tracking phase,the switches S4are off and the switches S1and S5are on,while in the successive approximation phase, switches S4are on and switches S1and S5are off.During the tracking phase,the voltage VCM is applied to the comparator stage.The voltage VCM has to be(VREFPFig.10.Measured staticcharacteristics.Fig.11.Measured dynamic characteristics.large capacitors are necessary to obtain enough linearity while the resistance arises from the on resistance of the transmission gates.The whole comparator stage consists of a fast open-loop gain stage with offset cancellation,a fast clocked comparator,and some additional logic in the SAR as well as in the control logic (see Fig.8).When the control signal LATCH of the comparator is low,its output signals CP and CN are set to low and its positive feedback is open.With the rising clock edge,the LATCH signal is set to high,which triggers the comparator and has the effect that one of the output signals CP or CN changes to high,depending on the input voltage difference.When the high signal is detected the LATCH signal is reset to low,the bits for the DACs are set and a new charge redistribution is started.The next rising clock edge begins this procedure anew.This increases the critical time for the charge redistribution to nearly one whole clock cycle,independent from the clock duty cycle.TABLE I K EY FEATURES The second clock edge is only used to abort a decision of the comparator if its input signal difference is too small to decide within a few nanoseconds.The successive approximation algo-rithm ensures that the error of a wrong decision caused by an aborted decision is always only a fraction of an LSB.This usage of the second clock edge reduces the freedom of the clock duty cycle to the range between about 25%and 75%.This self-timed solution does the time partitioning itself.When the comparator has to detect a very small voltage differ-ence,the time for the charge redistribution is longer,because the previous one was an easy and fast decision.The subsequent charge redistribution needs less time,because an uncritical decision always follows.This correlation and the timing of the comparator are shown in Fig.9.The combination of all those improvements makes it possible to increase the sampling rate and to reduce the power consump-tion at the same time.IV .I MPLEMENTATION AND M EASURED R ESULTSThe conventional 10-bit converter which was described in Section II was designed in the0.6-m process as well,to compare thenew architecture with the old one.Both converters are noncali-brating ADCs with poly1-poly2capacitor arrays.To achieve the required linearity a special common centroid layout technique was used to build a 12-bit accurate capacitor array [7],[8].The greatest advantage of the new architecture is to have a higher sampling rate and lower power consumption at the same time,as shown in Table I.The sampling rate is increased by the factor 2,the power consumption is decreased by the factor 1.5.This results in an overall improvement by the factor 3.Further-more the resolution is increased from 10to 12bit and the input and reference capacitances are almost the same for the 10-bit and the 12-bit ADC which is comparable with an effective re-duction of about the factor 4.The area of the new 12-bit cell is about the same as that for the old 10-bit cell.Altogether this is an effective size reduction of about one third,mainly because the buffer as well as the blocking capacitors were removed.In Table II,typical parameters of the conventional 10-bit and the new 12-bit converter are listed.The measurements were done at the maximum conversion rate with a supply voltage ofTABLE IIM EASURED R ESULTS AT 5.0-V SUPPLYFig.12.Chip photograph.5V and a dynamic input rangeofV ,temperatureC,worst-case process).The resolution was improved from 10-bit to 12-bit while the area remained roughly the same.Furthermore,the applicability of the converter in an integrated system was facilitated noticeably because of the re-duction of the input and reference capacitance.A CKNOWLEDGMENTThe author would like to thank G.Schatzberger,W.Meus-burger,and C.Trattler for useful discussions.R EFERENCES[1]K.S.Tan et al.,“Error correction techniques for high-performancedifferential A/D converters,”IEEE J.Solid-State Circuits,vol.25,pp.1318–1327,Dec.1990.[2]J.L.McCreary et al.,“All-MOS charge redistribution analog-to-dig-ital conversion techniques—Part I,”IEEE J.Solid-State Circuits,vol.SC-10,pp.371–379,Dec.1975.[3] C.A.Leme and J.E.Franca,“An overview and novel solutions for high-resolution self-calibrating analogue-digital converters,”presented at the Int.Symp.Signals,Systems and Electronics,Erlangen,1989.[4]R.Van De Plassche,Integrated Analog-to-Digital and Digital-to-AnalogConverters,The Netherlands:Kluwer,1994.[5]“Differentieller analog-digitalwandler,”Austria Mikro Systeme Int.AG,Österreichisches Gebrauchsmuster Nr.3853,Aug.2000.[6]R.R.Hester et al.,“Fully differential ADC with rail-to-railcommon-mode range and nonlinear capacitor compensation,”IEEE J.Solid-State Circuits,vol.25,no.1,pp.173–183,Feb.1990. [7]T.Brandtner,“Device-Generator für Kapazitätsarrays,”,Institut fürElektronik L1415,1997.[8]P.O’Leary,Practical Aspects of Mixed Analogue and Digital Design,Austria Mikro Systeme International AG,1991.。

2N5564中文资料

76

Notes a. Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

b. Pulse test: PW v300 ms duty cycle v3%. c. This parameter not registered with JEDEC.

APPLICATIONS

D Wideband Differential Amps D High-Speed,

Temp-Compensated, Single-Ended Input Amps D High-Speed Comparators D Impedance Converters D Matched Switches

IG = –1 mA, VDS = 0 V

VDS = 15 V, ID = 1 nA

VDS = 15 V, VGS = 0 V VGS = –20 V, VDS = 0 V

TA = 150_C VDG = 15 V, ID = 2 mA

TA = 125_C VGS = 0 V, ID = 1 mA VDG = 15 V, ID = 2 mA IG = 2 mA , VDS = 0 V

The hermetically-sealed TO-71 package is available with full military processing (see Military Information).

For similar products see the low-noise U/SST401 series, and the low-leakage 2N5196/5197/5198/5199 data sheets.

LT1990 微电流精密差分放大器说明书