基于NiosⅡ处理器的多功能计数器系统设计

基于Nios Ⅱ嵌入式软核多处理器系统研究

基于Nios Ⅱ嵌入式软核多处理器系统研究通过对硬件互斥核,程序存储器分区,重叠地址空间,启动地址和异常地址的分析,提出了多处理器系统共享片上存储器、FLASH存储器和外设资源的解决方法,为Nios Ⅱ嵌入式多处理器系统的设计提供了有效的方法和途径。

0 引言基于SoPC 技术开发的嵌入式Nios Ⅱ软核多处理器系统具有可自主设计,重构性好,软硬件裁剪容易,系统扩充升级方便,能兼顾性能、体积、功耗、成本、可靠性等方面的要求。

研发嵌入式Nios Ⅱ软核多处理器系统,是提高嵌入式系统性价比和实用性一种有效途径。

1 片上Nios Ⅱ嵌入式软核多处理器系统嵌入式系统的核心是RISC 处理器,具有代表性的RISC软核处理器是Nios Ⅱ处理器。

软核处理器是指用编程的方法生成的处理器。

是一种将硬件逻辑、智能算法、硬件描述语言和编程有机的结合出来,设计处理器硬件电路的新技术。

片上Nios Ⅱ嵌入式多处理器系统优势在于设计者可根据的实际的需要,自主选择Nios Ⅱ处理器的类型和数目并进行设置,对存储器和外围设备进行优化配置,最大限度提高片内资源和系统资源的利用率。

1.1 Nios Ⅱ处理器由Nios Ⅱ软核处理器构建的系统,对系统软硬件容易进行裁剪,并可集成在一个FPGA 芯片上,构建系统和实时评估非常迅速、方便,可大大地缩短设计周期,降低设计风险。

1.2 多处理器系统类型按共享资源分为非共享资源多处理器系统和共享资源多处理器系统两种。

非共享资源多个处理器系统中的多个Nios Ⅱ处理器完全是独立的,不共享系统资源,处理器相互之间无干扰,系统结构不太复杂。

共享资源多处理器系统在共享资源的情况下,要确保多个Nios Ⅱ处理器安全、可靠的工作,它对提高每个处理器的性能、减小体积,降低成本和功耗有利,但系统软件的设计较为复杂。

win7 64位/win7/64/按处理器拓扑结构分为2 种,一种是非层次结构,处理器与系统组件的连接容易;另一种是层次结构,它可根据实际需要来确定Nios Ⅱ处理器的数目,优化系统的内部结构,有效利用FPGA芯片的资源。

基于NiosII的智能多接口片上系统设计

基于NiosII的智能多接口片上系统设计

摘要:设计了一种基于NiosII处理器的片上系统(SoC),集成了Nios II处理器IP、PCI接口IP、网络接口IP以及基于Wishbone总线的串行接口IP核、CAN接口IP核等。

系统具有可重配置、可扩展、灵活、兼容性高、功耗低等优点,适合于片上系统开发与应用。

本设计使用Verilog HDL硬件描述语言在QuartusII环境下进行IP软核设计、综合、布局布线,在Model Sim下完成功能、时序仿真,在SoPC下完成系统的定制与集成,在NiosII IDE环境下完成片上系统软件程序的开发,最后在FPGA器件上实现了智能多接口功能的片上系统。

随着超大规模片上系统需求的日益增多,基于传统IC芯片的微电子应用系统设计技术正在转向基于知识产权IP(Intellectual Property)核的片上系统技术发展[1]。

因此,基于资源IP核的复用设计方式已开始逐渐成为国内外微电子系统设计的一项支撑技术。

从应用功能角度划分IP核有三大类:微处理器IP核(如8位8051核、32位NiosII、Microblaze核等)、各种接口IP核(如SDRAM控制器、PCI总线接口、CAN总线接口、串行总线接口IP核等)和专用算法IP核(图形编解码H.264、加密核等)。

使用IP核复用技术,将IP集成到FPGA芯片上,可缩小PCB板体积,降低功耗;还可以根据需要进行功能的升级、扩充和裁减。

本文以Altera公司的NiosII为主处理器并集成PCI接口、串行接口、CAN接口、网络接口设计为例,说明片上系统的设计方法。

基于Nios Ⅱ的多生理参数处理系统的设计

基于Nios Ⅱ的多生理参数处理系统的设计

王丽花;唐晓英;刘伟峰

【期刊名称】《电子技术应用》

【年(卷),期】2008(34)4

【摘要】以NiosⅡ软核处理器为核心的多生理参数系统数据处理平台的搭建,在FPGA中嵌入32位Nios Ⅱ软核系统,用以控制信号的采集、处理、存储与显示等功能.NiosⅡ系统设计以NiosⅡ软核为核心,将全部的接口电路集成在同一片FPGA 上,结构简单,易于修改,具有很高的性价比.

【总页数】3页(P10-12)

【作者】王丽花;唐晓英;刘伟峰

【作者单位】北京理工大学,生命科学与技术学院生物医学工程系,100081;北京理工大学,生命科学与技术学院生物医学工程系,100081;北京理工大学,生命科学与技术学院生物医学工程系,100081

【正文语种】中文

【中图分类】TP3

【相关文献】

1.一种面向多维生理参数的前端嵌入式数据处理系统的设计 [J], 项方康;吕勇;姚容;周正驰;巫溢滨

2.消防员生理参数采集与处理系统设计 [J], 梁梦杰;魏剑鹏;李驰原

3.消防员生理参数采集与处理系统设计 [J], 梁梦杰;魏剑鹏;李驰原

4.一种基于N ios Ⅱ软核的嵌入式图像采集处理系统设计 [J], 龚向东;刘春平;黄虹

宾;曾振兴

5.基于niosII的测控中频处理系统设计 [J], 张天平;郝建华;许斌;丁丹

因版权原因,仅展示原文概要,查看原文内容请购买。

基于NiosII的SOPC多处理器系统设计方法

altera_avalon_mutex _lock( ) altera_avalon_mutex _unlock ( ) altera_avalon_mutex _is_mine( ) altera_avalon_mutex _firs t_lock( )

4 NiosII 多处理器系统设计实例

下面将利用 SO PC Builder 建立一 个基于 标准模板 的 3 处理器、共 享 片 上 存储 器 的 N iosII系 统, 之 后在 N iosII

paper@ m esnet . com . cn( 投稿专用)

19 2007 年第 3 期 M icrocontrollers & Em bedded Syst ems

3. 2 启动地址

在多处理器系统中, 每个处理器必须从自己的存 储区 域启动。为了从同一个非易 失性存 储器中 的不 同区域 启 动多处理器, 简单地设置每个处理器的复位地址为所 期望 的启动地址。在启动地址之 间要留 出足够 的空 间存放 启

动代码。 NiosII Flash Programmer 能 够将 多个 处理 器 的启 动

在多处理器系统中, 多个处理器可能使用同一个程 序 存储器, 每个 处理器 的程序 必须 存放在 不同 的位 置。Ni osII 和 SOPC Builder 提供一个简单的存储器分区模式, 允 许多个处理器在同一存储器的不同区域运行各自的 软件。 分区模式使 用处 理 器的 异 常地 址, 可以 在 S OPC Builder 中进行设置。NiosII IDE 负责 根据 异常 地址 计算 出不 同 代码段链接的位置。如 果 2 个 不同 的处理 器被 链接到 同 一存储器, 那么每个处理器的异常地址用来决定处理器 软 件存放的基地址, 其末地址由下一个异常地址或者存储 器 的末地址决定。对于每个处理器, 软件有 5 个主要的代 码 段需要被链接到存储器中的固定地址, 分别是:

基于NiosⅡ的SOPC系统设计与研究的开题报告

基于NiosⅡ的SOPC系统设计与研究的开题报告一、选题背景及意义SOPC(System-on-a-Programmable-Chip,可编程芯片系统)是一种新的系统设计方法,其核心是将CPU、DSP、FPGA等各种数字电路系统的设计集成到一个单一的可编程处理器芯片中,这种设计方法在数字电路领域中具有非常广泛的应用前景和研究价值。

而在这种系统设计方法中,Nios Ⅱ是基于可编程逻辑设备的嵌入式处理器,具有易于设计与控制、可裁剪性强、资源占用小等优点,广泛应用于SOPC系统的设计与实现之中。

因此,本次选题旨在通过对于Nios Ⅱ的SOPC系统设计与研究进行深入探索,探究其在实际应用中的优势与不足之处,为其进一步的优化和完善提供参考依据。

二、研究方法及流程1、资料收集:在本研究中,需要深入了解Nios Ⅱ处理器的内部结构与工作原理、SOPC系统的设计与构建过程、各种数字电路模块的实现方法等相关资料,并进行整理和分析。

2、系统设计:在收集和分析相关资料的基础上,进行简化的Nios Ⅱ处理器设计和SOPC系统架构设计,并利用Quartus II工具进行系统实现和验证。

3、系统测试:完成系统的实现之后,进行系统测试,包括硬件实验和软件编程测试两个方面。

4、分析评估:分析实验数据,评估Nios Ⅱ的SOPC系统在实际应用中的性能优劣,提出系统的改进和优化方案。

三、预期结果及意义1、在实验设计过程中,通过对Nios Ⅱ的SOPC系统架构设计与实现,可以深刻理解可编程处理器芯片中各种数字电路模块的工作原理与相互联接关系,彻底掌握SOPC系统的设计与构建方法。

2、通过实验测试和数据分析,可以全面评估Nios Ⅱ的SOPC系统在实际应用中的性能优劣,研究其应用前景和推广价值,并针对其不足之处提出系统的改进和优化方案,提高系统的性能水平和可靠性。

3、研究成果可为相关技术研究和应用推广提供科学依据和参考借鉴,促进数字电路领域技术的创新和发展。

基于NIOS Ⅱ的多功能数字频率计的设计

基于NIOS Ⅱ的多功能数字频率计的设计

曹作宝;包晓敏;彭霄

【期刊名称】《工业控制计算机》

【年(卷),期】2009(022)010

【摘要】介绍了一种基于可编程片上系统(System On Programmable Chip,以下简称SOPC)技术的多功能数字频率计的实现方案.通过在FPGA芯片中植入NIOS Ⅱ软核作为系统的控制核心,并利用FPGA中的可编程逻辑资源构成该嵌入式系统的外围数字控制电路,借助于Avalon总线,实现高速FIFO,触发控制电路,LCD显示控制电路,频率周期测量模块等.可测量方波、正弦波、三角波等不同波形的频率、周期和脉宽,且可测范围达0.1Hz-100MHz.

【总页数】2页(P74-75)

【作者】曹作宝;包晓敏;彭霄

【作者单位】浙江理工大学信息电子学院,浙江,杭州,310018;浙江理工大学信息电子学院,浙江,杭州,310018;浙江理工大学信息电子学院,浙江,杭州,310018

【正文语种】中文

【中图分类】TP3

【相关文献】

1.基于FPGA的多功能数字频率计的设计与实现 [J], 张楠楠;陈龙;郭恒哲;李大宇

2.基于EDA技术的多功能数字频率计设计 [J], 龚泰龙

3.基于可编程逻辑器件的多功能数字频率计的设计 [J], 包佳佳

4.基于NiosⅡ的多功能数码相框设计 [J], 刘胜辉;王燕飞

5.基于Nios Ⅱ处理器的多功能计数器系统设计 [J], 邹宇;王承

因版权原因,仅展示原文概要,查看原文内容请购买。

40基于NiosⅡ的双核处理器的设计与实现

随着 电子技术 与计算机技 术 的快速发展 ,产 品的新功 能和新特 性 、业 界新标 准 、市 场供求 、用户 对低功 耗甚至 零 功 耗 的 不断 追 求 , 以及产 品成 本 等越 来 越 多 因素 的影 响,使 的市场 上的各种 应用产 品 ,从基础 设备到单 纯 的消 费 电子对 嵌入 式产 品的设计有 了更 高的要求 ,这些 变化 使 研 发人 员开发 更加完 善复杂 的软件 ,在高端 产 品使 用大量 的F G , 同时也将 设计者引 向A I/ O 与非传统硬件模 型一 PA SCSC

中 国西 部科 技 2 0 年1 月 ( 08 1 上旬 ) 7 第3 期总 第1 6 第O 卷 1 5 期

基于No Ⅱ的双核处理器的设计与实现 i s

吕生峰 张 光 健

( 安 建 筑 科 技 大 学 信 控 学 院 , 陕 西 西 安 7 0 5 西 1 5) 0

摘

要 :N s lr公 司开 发的嵌 入 式软 核 处理 器 ,本 文介 绍 了Atr N0J 理 器及 基 于N01 多核 处理 器的工 作原 _】 t a oI e 是A l a .l e s 处 _I s的

( )独立多核处理器 之间是完全独立 的,各处理器不 1 参 与 其他 处 理器 的运 算 。也 可 以说它 们 是 一个 分 开 的系

统 。这种 形式 的双核系 统是… 种非常 简单 的双核系 统 ,只

是 在芯片 系统 中多添加 一个处 理器 ,所 能提 高的系 统性能

有 限。如图i( )。 a

l 多内核简介 多 内核是指在 一个 芯片பைடு நூலகம்内集 成两个 或 多个完整 的计算

~

机 内核 。半导体 工 艺技 术 的飞速 进步 和体 系结构 的不断 发 展 推动处 理器 向多核方 向 的发 展 。微 处理器 的速度 以及单 片 集成度 已经 到 了非 常高 的程 度 ,仅提 高单 核芯片 的速度 会产生过 多热 量且无法 带来相 应的 性能改 善,多核通 过在

基于NiosⅡ的SOPC多处理器系统设计方法

2 2 硬 件 互 斥核 。

Nol处理 器 允 许 使用 其 硬 件 互 斥 核 部 件 对 共 享 资 源 i I s

进 行 保 护处 理 。这 个 硬 件 互斥 核 不 是 一 个 NisI 理 器 内 ol处

部 的 部件 , 是一 个 称 为 Mue 而 t x的 S P ul r 件 。 O CB i e 组 d 互 斥核 也可 看 作 一种 共 享 资 源 , 供 一 个 原子 的“ 试 提 测 和置位” 作 , 操 处理 器 测 试 Mue 否 可 行 。如 果 可 行 , t x是 就 在 某 个操 作 中 获 取 它 。 当 处 理 器 结 束 与 Mue 相 关 的 共 tx 享 资 源 使用 时 , 放 该 Mue ; 时 , 一 个 处 理 器 可 能 获 释 tx 此 另

、 , n … nr莹g田 商~ 。 t - - 、 rJ . '

连接 , 在 于 多个 处 理 器 的 软件 设 计 , 它 们 正 常 操 作 , 而 使 相

互 之 间 不 产 生 冲 突 。NisI 处 理器 系统 分 为 2类 : 类 ol 多 一 是 共 享 资 源 的 多处 理 器 系统 ; 一 类 处 理 器 相 互 独 立 , 另 之 间不 进 行 信 息 交 换 。

本 文 将 对 基 于 NisI的 S C 多处 理 器 系 统 的 实 现 ol 0P 原 理 、 计 流 程 和 方 法进 行 详 细 的讨 论 。 设

数据错误 , 少使应用程序出错 , 至使系统崩溃 。 至 甚 共 享存 储 器 的 处 理器 需 要 一个 机 制 来 通 知其 他 处 理 器 何 时 正在 使 用 共享 资源 , 以便 不 受 其 他 处理 器 的干 扰 。

2 1 共 享 存储 器 .

基于NiosⅡ的片上多核处理器系统设计

对独 立工作 , 用于控 制外 围输 出接 口电平 变化 , 在F P G A平 台上验 证 了多核 处 理 器协 同工作原 理 , 较为 系 统地 掌握 了片上 多核 系统 结构设计 的关键技 术 , 为下一步设计 多核处理 器 系统芯片打下 了坚实基础 。

关 键词 :多核 ;同构 ;片上 通信 ; N i o s I I ; F P G A

第3 2卷第 1 期 2 0 1 4年 3月

誊

嚣

V o 1 . 3 2 No . 1

Ma r . 2 01 4

J I cHENGDI ANLU T ONGXU N

基于 N i o s 1 1 的片 上 多核 处 理 器 系统设 计

徐叔喜 王 少轩 余 向阳 张 瑾

口处理模块进行 图像处理, 整个 系统 由图像数据 存储结构模块 、 多核控制模块、 中值滤波处理模

块、 L C D显 示控 制 模 块 组成 , F P G A 中的 N i o s l I 处

理器 , 实现了输人 、 输 出、 边缘采样 、 中断控制功

能, 用 以控 制 系统 的启 动 、 算法处理、 L C D显示 与 关 闭 等 。多核 系统结 构框 图如 图 1 所示 。

P r o c e s s o r , C M P ) , 或 单 芯 片 多 处 理 器 。多 核 处 理 器 是将 多个 完 全 功 能 的核 心集 成 在 同一 个 芯 片 内, 整个 芯 片作 为一个 统一 的结 构对外 提供 服务 。 其 性 能优 势 主要 有 以下 几 点 : ( 1 ) 通 过集 成 多个 单 线 程处理 核心 或者集 成 多个 同时 多线程 处理 核 心, 使 得整个 处 理器 可 同时 执行 的线 程 数 或任 务

niosii课程设计

niosii课程设计一、教学目标本课程旨在通过NIOS II软核处理器的教学,让学生掌握嵌入式系统的基本概念、软硬件协同设计的方法,以及基于NIOS II处理器的设计和实现。

具体目标如下:1.理解嵌入式系统的基本概念、特点和应用。

2.掌握NIOS II处理器的基本结构、工作原理和指令系统。

3.熟悉软硬件协同设计的基本方法,包括硬件描述语言(HDL)和软件编程。

4.能够使用NIOS II处理器进行简单的嵌入式系统设计和实现。

5.能够独立完成NIOS II处理器的硬件设计和软件编程。

6.能够对NIOS II处理器的设计进行优化和调试。

情感态度价值观目标:1.培养学生的创新意识和团队协作精神。

2.增强学生对嵌入式系统领域的兴趣和热情。

3.培养学生对我国嵌入式产业发展的关注和支持。

二、教学内容本课程的教学内容主要包括以下几个部分:1.嵌入式系统概述:嵌入式系统的定义、特点、应用和发展趋势。

2.NIOS II处理器:基本结构、工作原理、指令系统、寄存器文件和数据通路。

3.软硬件协同设计:硬件描述语言(HDL)的基本概念和应用,软件编程基础。

4.NIOS II处理器设计:硬件设计和软件编程,设计优化和调试方法。

5.案例分析:分析实际应用中的嵌入式系统设计,了解行业动态和发展趋势。

三、教学方法本课程采用多种教学方法,以激发学生的学习兴趣和主动性:1.讲授法:讲解基本概念、原理和方法,确保学生掌握基础知识。

2.案例分析法:分析实际应用案例,让学生了解嵌入式系统的实际应用和发展趋势。

3.讨论法:学生进行小组讨论,培养学生的团队协作能力和创新意识。

4.实验法:动手实践,让学生亲自设计并实现NIOS II处理器 based的嵌入式系统。

四、教学资源为了支持本课程的教学,我们将准备以下教学资源:1.教材:《NIOS II嵌入式系统设计与实践》。

2.参考书:提供相关领域的经典教材和论文,以便学生深入研究。

3.多媒体资料:制作课件、视频等教学资料,以便学生更好地理解和掌握知识。

基于NIOSⅡ技术的系统设计与实现(LED流水灯显示)

基于NIOSⅡ技术的系统设计与实现(LED流水灯显示)基于NIOS?技术的系统设计与实现- 流水灯LED显示基于 NIOS?技术的系统设计与实现- 流水灯LED显示内容提要:随着电子技术的不断发展,电子产品向体积越来越小、设计时间越来越短、集成度越来越精密、产品周期越来越短、成本越来越低、功能越来越强大等方向发展。

使用NIOS?处理器的用户可以根据他们的需要调嵌入式系统的特性、性能以及成本,快速使得产品推向市场,扩展产品的生命周期,并且避免处理器的更新换代。

本论文结合EDA技术、C语言、NIOS?技术、计算机技术等多种技术实现基于Nios?的系统设计。

并用LED流水灯显示来检验我设计的NIOS?技术的系统功能。

同时也为其他相关项目的设计提供了参考。

关键词:EDA技术 SOPC技术 NIOS?处理器嵌入式技术 LED显示NIOS ? technology-based systems design andimplementation of- LED light water showAbstract:With the continuous development of electronic technology, electronic products to the size is getting smaller and smaller, shorter and shorter design time, more and more sophisticated integration, product life cycle is becoming shorter and shorter, more and more low-cost, more and more powerful features, such as Direction. The use of NIOS ? processorusers based on their need to transfer the characteristics of embedded systems, performance and cost of making products to market quickly, expand the?product's life cycle and to avoid the replacement of the processor.This thesis EDA combination of technology, C language, NIOS ? technology, computer technology and other technology-based Nios ? system design. And theLED light water show designed to test my NIOS ? technology system.At the sametime as other related projects designed to provide a referenceKey words: EDA Technology SOPC technology NIOS ? processor technologyembedded LED display目录一、前言………………………………………………………………………………… 二、总体方案…………………………………………………………………………… (一) 方案比较………………………………………………………………………(二) 方案论证与选择…………………………………………………………… 三、所用技术和器件的介绍…………………………………………………………… (一)基本器件的介绍………………………………………………………………… 1、EDA的介绍…………………………………………………………………………………………………………………………………………… 2、CPLD和FPGA的介绍3、Quartus?的介绍……………………………………………………………………(二)特殊器件介绍……………………………………………………………………1、SOPC Builder开发工具介绍……………………………………………………… 2、NIOS?的使用说明………………………………………………………………… 3、Cyclone EP1C12Q240C8开发板的介绍…………………………………………… 四、系统设计…………………………………………………………………………… (一)、硬件设计………………………………………………………………………1.新建工程……………………………………………………………………………2.用SOPC Builder 定制Nios?处理器及其外设……………………………………3.在Quartus ?工程中添加上述nios?系统………………………………………4.添加其他元件模块…………………………………………………………………5.定义管脚……………………………………………………………………………6.编译工程……………………………………………………………………………7.下载编辑代码到FPGA………………………………………………………………(二)、软件设计……………………………………………………………………… 1.设计该工程软件…………………………………………………………………… 2.编译设置…………………………………………………………………………… 3.编译………………………………………………………………………………… 五、系统调试…………………………………………………………………………1.调试…………………………………………………………………………………2.编译并下载到实验板上面………………………………………………………… 六、系统功能、指标参数……………………………………………………………… 七、总结与体会…………………………………………………………………………?八、辞谢………………………………………………………………………………… 附录…………………………………………………………………………………… 参考文献………………………………………………………………………………基于NIOS ?技术的系统设计与实现一、前言(绪论)随着微电子技术的发展,促使集成电路向高速、高集成度、低工耗的系统集成方向发展,SOPC(System On a Programmable Chip、片上可编程系统)是现代电子技术和电子系统设计的汇聚点和发展方向。

基于Nios_的双核处理器的设计与实现

随着电子技术与计算机技术的快速发展,产品的新功能和新特性、业界新标准、市场供求、用户对低功耗甚至零功耗的不断追求,以及产品成本等越来越多因素的影响,使的市场上的各种应用产品,从基础设备到单纯的消费电子对嵌入式产品的设计有了更高的要求,这些变化使研发人员开发更加完善复杂的软件,在高端产品使用大量的FPGA,同时也将设计者引向ASIC/SOC与非传统硬件模型---多核设计。

多内核是指在一个芯片内集成两个或多个完整的计算机内核。

半导体工艺技术的飞速进步和体系结构的不断发展推动处理器向多核方向的发展。

微处理器的速度以及单片集成度已经到了非常高的程度,仅提高单核芯片的速度会产生过多热量且无法带来相应的性能改善,多核通过在一个芯片上集成多个简单的处理器核,充分利用这些晶体管资源,发挥其最大的能效。

NiosII多核系统分为两种:独立多核与资源共享多核。

(1)独立多核处理器之间是完全独立的,各处理器不参与其他处理器的运算。

也可以说它们是一个分开的系统。

这种形式的双核系统是一种非常简单的双核系统,只是在芯片系统中多添加一个处理器,所能提高的系统性能有限。

如图1(a)。

(2)资源共享多核系统中资源能被一个以上处理器访问,根据共享资源可以分为存储器共享和外设共享。

因为非存储器共享目前有相当的难度,尤其是外设的中断问题,没有有效的方法保证哪个处理器优先做出中断并进入中断服务程序,也很难决定哪个处理器来接收外设数据。

目前NiosII还不支持外设资源共享。

在资源共享的多核系统中,存储器是最常见的共享资源。

如图1(b)。

1多内核简介基于Nios II的双核处理器的设计与实现摘要:NiosII是Altera公司开发的嵌入式软核处理器,本文介绍了AlteraNiosII处理器及基于NiosII的多核处理器的工作原理,应用SOPCBuilder工具建立双核处理器系统,以及使用NiosIIIDE为系统中每个处理器建立和调试软件工程。

基于Nios Ⅱ的SOPC系统设计

能囤 l

建立项层图

l

用S OPCBule建 i r d 立 Nis 理 器及 o处

所需外设接口

段. 借助 于 以计 算 机 为平 台的 E A工具 进行 _。 D 2 j

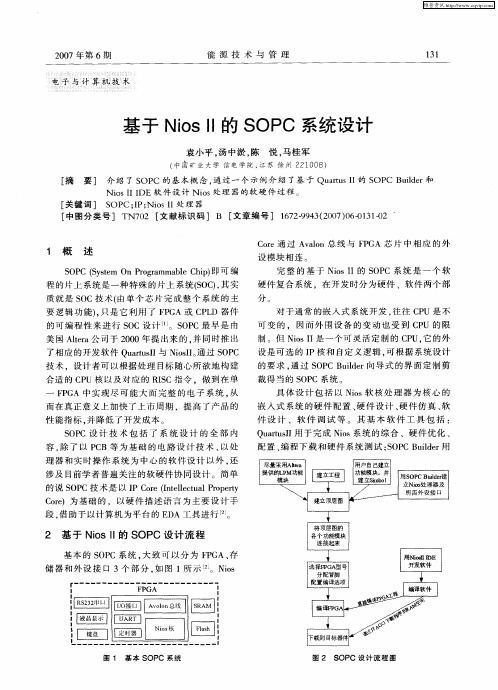

2 基 于 No l S C 设 计 流 程 is l的 0P

基本的 S P O C系统 , 致 可 以分 为 F G 存 大 P A、

1 概

述

S P S s m O rga a l C i1 O C fyt nP ormm be hp 即可 编 e

程 的片上 系统 是 一种 特殊 的片 上系 统(o )其 实 s c,

质就 是 S C技术 f O 由单 个 芯 片 完成 整 个 系统 的 主 要 逻辑 功 能1只 是 它利 用 了 F G , P A或 C L P D器 件 的可编 程 性来 进 行 S C设 计 n。S P O ] O C最早 是 由 美 国 At a 司 于 2 0 lr 公 e 0 0年 提 出来 的 , 同时推 出 并

于设计 工程 Байду номын сангаас件 ,建立 N o 核 。具 体流 程 如 图 2 is

所 示 [。 3 ]

21 硬 件 设 计 .

根 据 系统 要实 现 的功 能 . 定 No 处 理器 和 确 is

外 围器件 , : 如 显示 屏 、 钮 、 按 蜂鸣器 、 储器等 。 存 接

下 来 ,在 S P ule 中 建 立 系 统 要 添 加 的模 O CB i r d 块 , 括 : i I3 bt P 定 时 器 、 键 P O、 包 No I 2 i C U、 s 按 I L D PO、 部 R C I 外 AM 总 线 ( ao Avl n三 态 桥 ) 外 部 、

基于NIOSII软核处理器的研究与设计

提 供构 建管 理工 具, 使用 G u 译器 作为其 支撑 技术 。 ISI D N编 N OI E I

还 可 以运行和 调试 嵌入 式程序 ,设 计入 员可 以将精 力放在 N O I IS I

开发包 的 F G 开 发板或 者 I S 。此 外 ,N O I D 具 有 F A H PA S上 I S II E LS

No I系列 软核 处理器 是 A tr i sI le a的第 二代 FG PA嵌 入式 处 理器 ,其 性能超 过 20 MP ,在 A tr PA中实现非 常理 想 。 0D IS le aFG

A tr l e a的 S r t x S r t xG 、 t a i I和 C c o e系 列 F G t a i 、 t a i X S r t xI y ln PA

开发 。软件 开发 需要 N o l D i s I I E的支 持 。 图 1 基于 N O I 的 S F 软 件开 发流程 。N O I D 是 IS I OC I S IIE具有 编码 生成环 境 以及 可选 的 R O 和 T P I 集 成库 。N O I D TS C/ P I S II E还

全面 支持 N o I处 理器 , 以后推 出的 F G isI PA器 件也将 支持 N o is

工I 。

使用 N o I 件开 发工具 能够 为 N o I 统构建 软件 , i sI 软 is I 系 即一键式 自动 生成适 用于 系统硬 件 的专用 CC + / +运行 环境 。N o is I 集 成开发环 境 ( D )提供 了许 多软件 模板 ,简化 了项 目设置 。 I IE 此外 ,No l开发套 件包 括两 个第 三方 实时操 作系 统 ( TS is I RO )

Nios_多处理器系统方案设计

技术创新中文核心期刊《微计算机信息》(嵌入式与SOC)2007年第23卷第7-2期360元/年邮局订阅号:82-946《现场总线技术应用200例》片上系统SOCNiosII多处理器系统方案设计ThedesignofmultiprocessorbaseonNiosII(1.解放军信息工程大学;2新疆大学)王卫源1戴紫彬1钱育蓉2WANGWEIYUANDAIZIBINQIANYURONG摘要:NiosII是Altera公司利用其SOPC技术开发出第二代软核处理器,它提供了多处理器的支持,但在多处理器的支持上,却存在一定的问题,本文针对这一问题,提出基于NIOS平台的多处理器设计方案。

关键词:SOPC;SMP;NIOSII中图分类号:TP332文献标识码:AAbstract:AdvancesinsystemonaprogrammablechiptechnologieshaveledtoVendorprovidesoftcoreprocessors.However,itisachallengetoimplementSymmetricMultiprocessoronaProgrammableChipsystemsusingsuchprocessors.Thispaperpresentsanim-plementationofatightly-coupled,cache-coherentsymmetricmultiprocessingdesignusingaNiosIIsoftcoreprocessor.Keyword:SOPC,SMP,NIOSII文章编号:1008-0570(2007)07-2-0096-021引言NiosII系列软核处理器是Altera公司的第二代FPGA(可编程门阵列)嵌入式处理器,主要利用了SOPC(Systemonapro-grammablechip)技术,通过将包括32位高性能处理器在内的多种应用模块嵌入到一个通用的FPGA/CPLD(复杂的可编程逻辑控制器件)内,实现一个完全可重置的嵌入式系统。

nios2课程设计

nios2课程设计一、课程目标知识目标:1. 理解Nios II处理器的核心概念和原理,掌握其基本架构和运作机制。

2. 学习并掌握基于Nios II处理器的嵌入式系统设计流程和方法。

3. 掌握Nios II处理器的编程技术,包括汇编语言和C语言的编程。

技能目标:1. 能够运用Nios II处理器设计简单的嵌入式系统,进行硬件描述和软件编程。

2. 能够运用Nios II处理器的开发工具进行系统仿真、调试和优化。

3. 能够分析并解决基于Nios II处理器的嵌入式系统问题,提高实际工程应用能力。

情感态度价值观目标:1. 培养学生对嵌入式系统设计和开发的兴趣,激发创新意识和探索精神。

2. 培养学生良好的团队合作精神和沟通能力,提高解决实际问题的自信心。

3. 增强学生对我国嵌入式产业发展的认识,树立为国家和民族科技事业做贡献的价值观。

课程性质分析:本课程为电子信息类专业课程,以实践性为主,注重培养学生的动手能力和实际应用能力。

学生特点分析:学生具备一定的电子技术和编程基础,对嵌入式系统有一定了解,但Nios II处理器相关知识掌握较少。

教学要求:结合学生特点,采用理论与实践相结合的教学方法,以项目驱动为导向,使学生在实践中掌握Nios II处理器的相关知识,提高嵌入式系统设计和开发能力。

通过课程学习,实现上述课程目标,为后续相关课程和实际工作打下坚实基础。

二、教学内容1. Nios II处理器概述:介绍Nios II处理器的背景、特点和应用领域,使学生对其有一个全面的了解。

教材章节:第一章2. Nios II处理器架构:讲解Nios II处理器的硬件架构、指令集和存储器结构等内容。

教材章节:第二章3. 嵌入式系统设计流程:介绍基于Nios II处理器的嵌入式系统设计流程,包括硬件描述、软件编程、系统集成和调试等。

教材章节:第三章4. Nios II处理器编程技术:学习Nios II处理器的编程方法,包括汇编语言和C语言的编程技巧。

基于Nios II软核的多核处理器系统的设计与实现

源,提供“测试和设置”操作。

当处理器测试到Mutex核可用时,就会在一个具体操作中暂时占有Mutex核,之后当处理器完成对存储器的读写操许所有其他函数访问Mutex核。

Altera_avalon_mutex_trylock()

Altera_avalon_mutex_is_mine()

功能:判断CPU是否拥有Mutex

图1 双Nios II软核处理器系统体系结构图2 基于Mutex核的双核系统通信流程图 图3 SDRAM地址空间分配图图4 双Nios II软核处理器系统的配置

是我们所编写的软件程序。

在获得相关共享资源前,软件总是询问并获得Mutex 核。

2.2 软件设计

本设计中,两个处理器的软件程图5 验证程序在双核系统的运行结果理器来说,有五个主要的代码段需要映射到存储器的固定地址中:.text ,存放实际执行的代码;.r o d a t a ,存放实际执行代码中所使用的常量;.rwdata ,存放读写变量和指针;。

基于Nios Ⅱ处理器的多功能计数器系统设计

基于Nios Ⅱ处理器的多功能计数器系统设计

邹宇;王承

【期刊名称】《制造业自动化》

【年(卷),期】2011(33)15

【摘要】系统以FPGA为核心,通过对正弦信号进行滤波、放大整形后得到标准的方波,由FPGA对其频率、周期及相位差进行测量.频率、周期测量采用等精度测量法,其具有精度高的特点;.相位差测量采用鉴相器分辨出相位差后测量其高电平所占比例测量.摒弃传统的FPGA+单片机方案,利用SOPC Builder在FPGA上构建Nios Ⅱ处理器对测量的数据进行数据处理及显示,实现了频率、周期、相位差测量的片上系统(SOPC),提高了系统的稳定性、降低了布线难度.

【总页数】4页(P146-149)

【作者】邹宇;王承

【作者单位】武汉理工大学信息工程学院,武汉430070;武汉理工大学信息工程学院,武汉430070

【正文语种】中文

【中图分类】TP274

【相关文献】

1.一种基于NIOS Ⅱ处理器的频谱分析系统设计 [J], 黄成华;付涛

2.基于NiosⅡ的片上多核处理器系统设计 [J], 徐叔喜;王少轩;余向阳;张瑾;

3.基于OPENCORE及NiosⅡ处理器的片上系统设计 [J], 孙杰;孙波;张兴堂

4.基于NiosⅡ双核处理器的数字水印系统设计 [J], 郝世博;许江淳;郝君坦

5.基于Nios Ⅱ软核处理器的运动目标跟踪系统设计 [J], 王峰;张福欣;李转令;夏涛因版权原因,仅展示原文概要,查看原文内容请购买。

基于NiosⅡ的SOPC多处理器系统设计方法

基于NiosⅡ的SOPC多处理器系统设计方法

李兰英;李霄燕

【期刊名称】《单片机与嵌入式系统应用》

【年(卷),期】2007(000)003

【摘要】详细地阐述基于NiosⅡ和FPGA的多处理器系统的实现机制,讨论利用硬件互斥核实现多处理器资源共享的方法,并给出硬件设计的具体步骤以及软件设计、调试方法和关键技术;利用Altera公司提供的QuartusⅡ、SOPC Builder和NiosⅡ IDE等开发工具,通过一个3处理器系统设计实例,验证了设计方法的正确性,实现了3处理器对存储器资源的共享.

【总页数】4页(P18-21)

【作者】李兰英;李霄燕

【作者单位】哈尔滨理工大学;哈尔滨工业大学

【正文语种】中文

【中图分类】TP3

【相关文献】

1.基于Nios Ⅱ的片上可编程系统(SOPC)实现的直流电机的PWM调速系统 [J], 朱科星;郁建平

2.基于NiosⅡ片上可编程系统(SOPC)实现的雷达监控系统 [J], 谢东辉;齐伟民

3.基于SoPC和NIOSⅡ的SD卡文件系统的设计 [J], 陈侠;李开航

4.基于SOPC/Nios Ⅱ的心音信号特征提取与记录系统 [J], 周克良;刘彬彬;聂磊

5.基于FPGA的NiosⅡ多处理器SOPC系统设计研究 [J], 杨航;潘传红

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

作者简介:邹宇 ( 9 9~),男,湖北荆州人 ,本科 ,研究方 向为通信 工程 。 18 [4 1 第3 卷 1 6 3 第8 期 21- ( ) 0 1 8上

参l

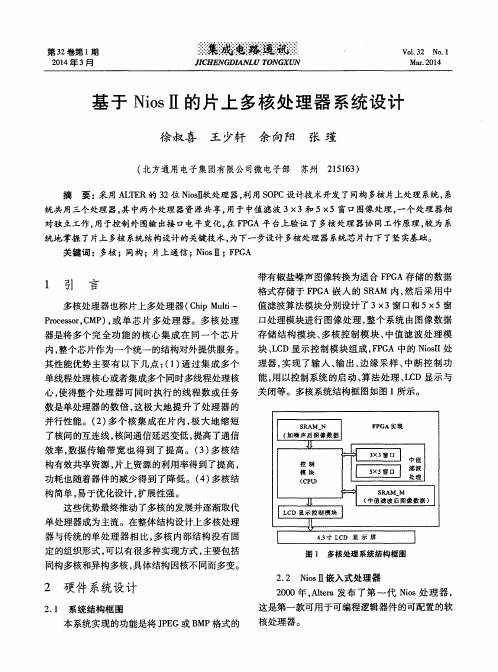

能 。具 体 的系统 框 图如 图 1 示 。 所

待 测 正 弦 波 信 号 经 信 号 放 大 模 块 放 大 后 ,得 到 幅 值 合 适 的 正 弦 波 波 形 ,进 入 调 理 整 形 电路 处 理 ,

的 意 义 ,多 功 能 计 数 器 的设 计 与 制 作 ,涉 及 到 单 片 机 技 术 、信 息 存 储 技 术 、人 机 界 面 技 术 等 多 方

0 引言

计 数 器 作 为 一种 测 量 工 具 在 仪 器 仪 表 、通 信 和 电路 控 制 中有 着 广 泛 的应 用 。 随着 通 信 电子 技

术 的 飞 速 发 展 .计 数 器 的 应 用 领 域 得 到 了 不 断

量 ,通 过在F G P A内部 搭建 鉴 相 器再 利 用脉 冲 计数 的 方 法 来 实现 , 相对 于数 字 鉴相 技 术 实现 相位 测 量 方 法 而 言 ,既提 高 了 测 量 精 度 , 整 体 来 说 又 相

面 理 论 知 识 和 实 际 制 作 技 术 ,本 文 介 绍 了一 种 基

由迟 滞 电压 比较 器 整 形 处 理 得 到 标 准 的方 波 ,再 送 入F GA内部 ,Nis I 理 系统 控 制频 率 测 量及 P o 处 I 相 位差 测量 模块 对 信号 进 行测量 。Nis I o 系统 获取 I 频 率 测量 及 相位 差 测量 模 块 的 测量 数 据 后进 行 数

、 l 似 I I 造 8

基于NisI o 处理器 的多功能计数器系统设计 I

Ni s I ocess - o I pr orbased sy t s em des gn m ulif i t—uncton count i er

邹 宇 ,王 承

ZOU Yu W ANG e g . Ch n

据处 理 ,将 处 理 得 到 的 数 据 送  ̄ L D1 0 显 示 , J IC 6 2

于NisI 理 器 多功 能计 数 器 。系统 以F GA为 核 o I 处 P

心 ,通 过 对 正 弦 信 号 进 行 滤 波 和 放 大 ,得 到 幅 值

合 适 的 正 弦 波 ,然 后 利 用 迟 滞 电压 比较 器 对 正 弦

期 及 两 路 同 周 期 信 号 的 相 位 差 在 工 程 上 有 着 重 要

1 多功能计数器系统结构组成分析

多 功 能 计 数 器 整 体 系统 结构 由 待 测 信 号 放 大 模 块 、信 号 整 形 模 块 、F GA模 块 、L P CD显 示 模 块 构成 。其 中F GA模 块 中 内嵌 了Nis 理 系统 、 P o处 F GA频 率 测 量 模 块 以 及F G P P A相 位差 测量 模 块 。

对降 低 了布线 难 度 。

扩 展 .功 能 也 进 一 步得 到 了加 强 。近 年 来 , 多功 能 计 数 器正 在 向数 字 化 的 领域 过 渡 ,其 优 点 在 于 硬 件 简 单 、适 应性 强 而且 极 大地 提 高 了 测 量 的 精 度 、 测 量 的范 围 与 测 量 的 内容 , 总体 性 能 明 显 优 于 一 般 的 模 拟 式 测 量 。测 量 一 个 信 号 的 频 率 、 周

信 号 整 形 ,得 到 标 准 的 方 波 ,再 由F GA对 其 频 P 率 、 周期 及相 位差 进行 测量 。Nis I o 处理 器可 以根 I 据 用 户 的需 要 来 调 整 嵌 入 式 系统 的 特性 、性 能 以 及 成 本 ,快 速 使 得 产 品推 向市 场 , 扩 展 产 品 的生

度。

关键词 :F A;频率测量 ;相位 差测 量 ;S P PG OO 中图分类号 :T 2 4 P 7 文献标识码 :B 文章编号 :10 -0 3 ( 0 ) ( 一0 6 0 9 1 4 21 8 上) 1 — 3 0 1 4

D i1 .9 9 J i n 10 - 14 2 1 .(E .4 o : 3 6/ . s .0 9 0 .0 1 8 ) 4 0 s 3

( 武汉理工大学 信息 工程 学院 ,武汉 4 0 7 ) 3 0 0

摘

要 :系 统以F G 为核心 ,通过对正弦信号进行滤波 、放大整形 后得到标准 的方波 ,由F G 对其 PA P A 频率 、周 期及相位 差进行测 量。频 率 、周期 测量采用 等精度测 量法 ,其具有精度 高的特点 ; 相位差测量采 用鉴相器分 辨出相位差后测 量其高 电平 所占 比例测量 。摒弃传统 的F G + P A 单片 机方案 ,利用S P ud r P A O C B ie在F G 上构建No l 器对测量的数据进 行数据处理及显示 , l is【 处理 实现 了频率 、周期、相位差测量 的片上系统 ( O C ,提高了系统的稳定性 、降低了布线难 SP )

F G 相位 PA 理 系

阵列F G P A实现高速信号的高精度测量 ,能够很好 的解 决单片机受本身时钟频率和指令运算周期的 限 制造 成 的 测 频 速 度 慢 的 问 题 。对 于 相 位 差 的 测

收稿日期:2 1- 4 5 0 1 0 -1

差 模 测量 块

统

图 1 多 功 能 计 数 器 整 体 系 统 结 构 框 图

完 成 多功 能计 数 器 的频 率 、 周期 、相 位 差 测量 功

F GA频率 P 测 量模块

2 0

∽

命 周期 ,并 且 避 免 处 理 器 的 更 新换 代 。对 于频 率 和 周期 的 测 量 系统 采 用 了 高 速现 场 可 编程 逻 辑 门

FG P A系统 处 目