74SSTUB32868ZRHR;中文规格书,Datasheet资料

SBR3U30P1-7;中文规格书,Datasheet资料

3.0A SBR SUPER BARRIER RECTIFIERPowerDI®123Features• Ultra Low Forward Voltage Drop• Superior Reverse Avalanche Capability• Patented Interlocking Clip Design for High Surge Current Capacity• Patented Super Barrier Rectifier Technology• Soft, Fast Switching Capability• 150ºC Operating Junction Temperature• ±16KV ESD Protection (HBM, 3B)• ±25KV ESD Protection (IEC61000-4-2 Level 4, Air Discharge) • Lead Free Finish, RoHS Compliant (Note 1)• “Green” Molding Compound (No Br, Sb)• Qualified to AEC-Q101 Standards for High Reliability Mechanical Data• Case: PowerDI®123• Case Material: Molded Plastic, “Green” Molding Compound.UL Flammability Classification Rating 94V-0• Moisture Sensitivity: Level 1 per J-STD-020D• Polarity Indicator: Cathode Band• Terminals: Matte Tin Finish annealed over Copper leadframe.Solderable per MIL-STD-202, Method 208• Marking Information: See Page 4• Ordering Information: See Page 4• Weight: 0.018 grams (approximate)Top ViewMaximum Ratings@T A = 25°C unless otherwise specifiedSingle phase, half wave, 60Hz, resistive or inductive load.For capacitance load, derate current by 20%.Characteristic Symbol Value UnitPeak Repetitive Reverse Voltage Working Peak Reverse Voltage DC Blocking Voltage V RRMV RWMV RM30 VRMS Reverse Voltage V R(RMS)21 V Average Rectified Output Current (See Figure 1) I O 3.0 A Non-Repetitive Peak Forward Surge Current 8.3msSingle Half Sine-Wave Superimposed on Rated Load I FSM75 A Non-Repetitive Avalanche Energy(T J = 25°C, I AS = 5A, L = 8.5 mH)E AS105 mJ Repetitive Peak Avalanche Energy(1µs, 25°C) P ARM1100 W Thermal CharacteristicsCharacteristic Symbol Value UnitMaximum Thermal ResistanceThermal Resistance Junction to Soldering (Note 2) Thermal Resistance Junction to Ambient (Note 3) Thermal Resistance Junction to Ambient (Note 4) RθJSRθJARθJA5178123ºC/WOperating and Storage Temperature Range (Note 5) T J, T STG-65 to +150 ºC Notes: 1. RoHS revision 13.2.2003. High temperature solder exemption applied, see EU Directive Annex Note 7.2. Theoretical RθJS calculated from the top center of the die straight down to the PCB cathode tab solder junction.3. FR-4 PCB, 2 oz. Copper, minimum recommended pad layout per /datasheets/ap02001.pdf.4. Polymide PCB, 2 oz. Copper, minimum recommended pad layout per /datasheets/ap02001.pdfSBR and PowerDI are registered trademark of Diodes Incorporated.BR and PowerDI are registered trademark of Diodes Incorporated.Electrical Characteristics @T A = 25°C unless otherwise specifiedCharacteristicSymbol MinTypMaxUnitTest Condition Reverse Breakdown Voltage (Note 5)V (BR)R30 - - V I R = 400µAForward Voltage DropV F- 0.280.31 0.39 0.20 0.23 0.35 0.32 0.35 0.43 0.23 0.26 0.38 VI F = 0.5A, T J = 25ºC I F = 1.0A, T J = 25ºC I F = 3.0A, T J = 25ºC I F = 0.5A, T J = 125ºC I F = 1.0A, T J = 125ºC I F = 3.0A, T J = 125ºC Leakage Current (Note 5) I R -70 150 6 12150 400 15 20µA µA mA mAV R = 5V, T J = 25ºC V R = 30V, T J = 25ºC V R = 5V, T J = 125ºC V R = 30V, T J = 125ºCNotes:5. Short duration pulse test used to minimize self-heating effect.Fig. 1 Forward Power DissipationI , AVERAGE FORWARD CURRENT (A)F(AV)P , P O W E R D I S S I P A T I O N (W )DFig. 2 Typical Forward Characteristics V , INSTANTANEOUS FORWARD VOLTAGE (V)F I , I N S T A N T A N E O U S F O R W A R D C U R R E N T (m A )FFig. 3 Typical Reverse Characteristics V , INSTANTANEOUS REVERSE VOLTAGE (V)R I , I N S T A N T A N E O U S R E V E R S E C U R R E N T (m A )RFig. 4 Total Capacitance vs. Reverse Voltage 1V , DC REVERSE VOLTAGE (V)R C , T O T A L C A P A C I T A N C E (p F )TSBR and PowerDI are registered trademark of Diodes Incorporated.I , A V E R A G E F O R W A R D C U R R E N T (A )F (A V )T , AMBIENT TEMPERATURE (°C)Fig. 5 Forward Current Derating CurveA70120110100T , D E R A T E D A M B I E N T T E M P E R A T U R E (°C )A V , DC REVERSE VOLTAGE (V)Fig. 6 Operating Temperature DeratingRT , JUNCTION TEMPERATURE (C)J °P , A V A L A N C H E P E A K P U L S E P O W E R D E R A T I N G I N P E R C E N T A G E (%)A R M Fig. 7 Pulse Derating Curve0.0010.010.11101001,000P , M A X I M U M A V A L A N C H E P O W E R (W )A R M Fig. 8 Maximum Avalanche Power CurveT , PULSE DURATION (uS)PSSBR and PowerDI are registered trademark of Diodes Incorporated. Ordering Information (Note 6)Part Number CasePackaging SBR3U30P1-7 PowerDI ®1233000/Tape & ReelNotes: 6. For packaging details, go to our website at /datasheets/ap02007.pdf.Marking Information3U3 = Product Type Marking CodeYM = Date Code MarkingY = Year (ex: T = 2006)M = Month (ex: 9 = September)3U3Y MDate Code KeyYear 2006 2007 2008 2009 2010 2011 2012 2013 2014 2015 Code T U V W X Y Z A B CMonth Jan Feb Mar AprMay Jun Jul Aug Sep Oct Nov DecCode 1 2 3 4 5 6 7 8 9 O NDPackage Outline DimensionsPowerDI ®123 Dim Min Max Typ A 3.50 3.90 3.70 B 2.60 3.00 2.80 C 1.63 1.93 1.78 D 0.93 1.000.98 E 0.85 1.25 1.00 H 0.150.250.20 L 0.550.750.65 L1 1.80 2.20 2.00 L2 0.95 1.25 1.10 All Dimensions in mmSuggested Pad LayoutX1GX2Y2Y1DimensionsValue (in mm)G 1.0 X1 2.2 X2 0.9 Y1 1.4 Y2 1.4IMPORTANT NOTICEDiodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to any product herein. Diodes Incorporated does not assume any liability arising out of the application or use of any product described herein; neither does it convey any license under its patent rights, nor the rights of others. The user of products in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on our website, harmless against all damages.LIFE SUPPORTDiodes Incorporated products are not authorized for use as critical components in life support devices or systems without the expressed written approval of the President of Diodes Incorporated.分销商库存信息: DIODESSBR3U30P1-7。

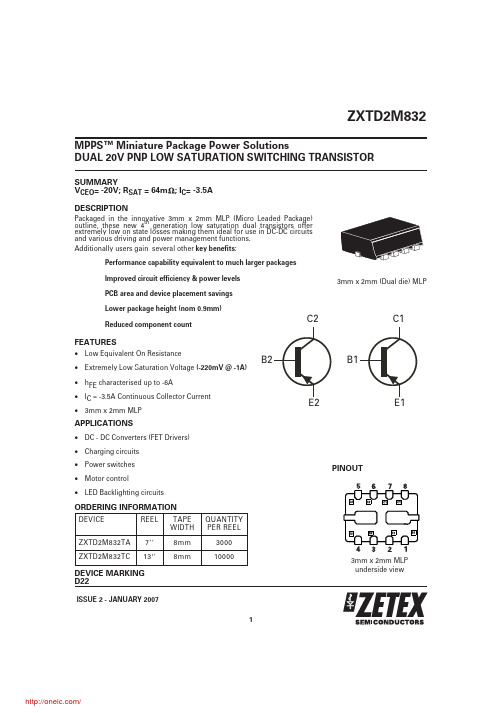

ZXTD2M832TA;中文规格书,Datasheet资料

SUMMARYV CEO = -20V;R SAT = 64m ;I C = -3.5A DESCRIPTIONPackaged in the innovative 3mm x 2mm MLP (Micro Leaded Package)outline,these new 4th generation low saturation dual transistors offer extremely low on state losses making them ideal for use in DC-DC circuits and various driving and power management functions.Additionally users gain several other key benefits :Performance capability equivalent to much larger packages Improved circuit efficiency & power levels PCB area and device placement savings Lower package height (nom 0.9mm)Reduced component countFEATURES•Low Equivalent On Resistance•Extremely Low Saturation Voltage (-220mV @ -1A)•h FE characterised up to -6A•I C = -3.5A Continuous Collector Current •3mm x 2mm MLPAPPLICATIONS•DC - DC Converters (FET Drivers)•Charging circuits •Power switches •Motor control•LED Backlighting circuitsDEVICE MARKING D22ZXTD2M832ISSUE 2 - JANUARY 20071MPPS™ Miniature Package Power SolutionsDUAL 20V PNP LOW SATURATION SWITCHING TRANSISTORDEVICE REEL TAPE WIDTH QUANTITY PER REELZXTD2M832TA 78mm 3000ZXTD2M832TC138mm10000ORDERING INFORMATION3mm x 2mm (Dual die)MLP3mm x 2mm MLP underside viewPINOUTZXTD2M832ISSUE 2 - JANUARY 20072PARAMETERSYMBOL VALUE UNIT Junction to Ambient (a)(f)R θJA 83.3°C/W Junction to Ambient (b)(f)R θJA 51°C/W Junction to Ambient (c)(f)R θJA 125°C/W Junction to Ambient (d)(f)R θJA 111°C/W Junction to Ambient (d)(g)R θJA 73.5°C/W Junction to Ambient (e)(g)R θJA41.7°C/WTHERMAL RESISTANCENotes(a) For a dual device surface mounted on 8 sq cm single sided 2oz copper on FR4 PCB, in still air conditions with all exposed pads attached . The copper area is split down the centre line into two separate areas with one half connected to each half of the dual device.(b) Measured at t<5 secs for a dual device surface mounted on 8 sq cm single sided 2oz copper on FR4 PCB, in still air conditions with all exposed pads attached.The copper area is split down the centre line into two separate areas with one half connected to each half of the dual device.(c) For a dual device surface mounted on 8 sq cm single sided 2oz copper on FR4 PCB, in still air conditions with minimal lead connections only.(d) For a dual device surface mounted on 10 sq cm single sided 1oz copper on FR4 PCB, in still air conditions with all exposed pads attached attached . The copper area is split down the centre line into two separate areas with one half connected to each half of the dual device.(e) For a dual device surface mounted on 85 sq cm single sided 2oz copper on FR4 PCB, in still air conditions with all exposed pads attached attached . The copper area is split down the centre line into two separate areas with one half connected to each half of the dual device.(f) For a dual device with one active die.(g) For dual device with 2 active die running at equal power.(h) Repetitive rating - pulse width limited by max junction temperature. Refer to Transient Thermal Impedance graph.(i) The minimum copper dimensions required for mounting are no smaller than the exposed metal pads on the base of the device as shown in the package dimensions data. The thermal resistance for a dual device mounted on 1.5mm thick FR4 board using minimum copper 1 oz weight, 1mm wide tracks and one half of the device active is Rth = 250°C/W giving a power rating of Ptot = 500mW.PARAMETERSYMBOL LIMIT UNIT Collector-Base Voltage V CBO -25V Collector-Emitter Voltage V CEO -20V Emitter-Base Voltage V EBO -7.5V Peak Pulse CurrentI CM -6A Continuous Collector Current (a)(f)I C -3.5A Base CurrentI B -1000mA Power Dissipation at TA=25°C (a)(f)Linear Derating FactorP D 1.512W mW/°C Power Dissipation at TA=25°C (b)(f)Linear Derating FactorP D 2.4519.6W mW/°C Power Dissipation at TA=25°C (c)(f)Linear Derating FactorP D 18W mW/°C Power Dissipation at TA=25°C (d)(f)Linear Derating FactorP D 1.139W mW/°C Power Dissipation at TA=25°C (d)(g)Linear Derating FactorP D 1.713.6W mW/°C Power Dissipation at TA=25°C (e)(g)Linear Derating FactorP D 324W mW/°C Operating and Storage Temperature RangeT j :T stg-55 to +150°CABSOLUTE MAXIMUM RATINGS.ZXTD2M832ISSUE 2 - JANUARY 20073TYPICAL CHARACTERISTICSZXTD2M832ISSUE 2 - JANUARY 20074PARAMETERSYMBOL MIN.TYP.MAX.UNIT CONDITIONS.Collector-Base Breakdown VoltageV (BR)CBO -25-35V I C =-100A Collector-Emitter Breakdown VoltageV (BR)CEO -20-25V I C =-10mA*Emitter-Base Breakdown Voltage V (BR)EBO -7.58.5V I E =-100A Collector Cut-Off Current I CBO -25nA V CB =-20V Emitter Cut-Off CurrentI EBO -25nA V EB =-6V Collector Emitter Cut-Off Current I CES -25nA V CES =-16VCollector-Emitter Saturation VoltageV CE(sat)-19-170-190-240-225-30-220-250-350-300mV mV mV mV mV I C =-0.1A,I B =-10mA*I C =-1A,I B =-20mA*I C =-1.5A,I B =-50mA*I C =-2.5A,I B =-150mA*I C =-3.5A,I B =-350mA*Base-Emitter Saturation Voltage V BE(sat)-1.01-1.075VI C =-3.5A,I B =350mA*Base-Emitter Turn-On Voltage V BE(on)-0.87-0.95VI C =-3.5A,V CE =-2V*Static Forward Current Transfer Ratioh FE3003001501547545023030I C =-10mA,V CE =-2V*I C =-0.1A,V CE =-2V*I C =-2A,V CE =-2V*I C =-6A,V CE =-2V*Transition Frequency f T 150180MHz I C =-50mA,V CE =-10V f=100MHzOutput Capacitance C obo 2130pF V CB =10V,f=1MHz Turn-On Time t (on)40ns V CC =-10V,I C =1A I B1=I B2=20mATurn-Off Timet (off)670nsELECTRICAL CHARACTERISTICS (at T amb = 25°C unless otherwise stated).*Measured under pulsed conditions. Pulse width=300µs. Duty cycle ≤2%ISSUE 2 - JANUARY 20075ZXTD2M832ISSUE 2 - JANUARY 20076EuropeZetex GmbH Balan-straße 59D-81541 München GermanyTelefon: (49) 89 45 49 49 0Fax: (49) 89 45 49 49 49europe.sales@AmericasZetex Inc700 Veterans Memorial Hwy Hauppauge, NY11788USATelephone: (631) 360 2222Fax: (631) 360 8222usa.sales@Asia PacificZetex (Asia) Ltd3701-04Metroplaza, Tower 1Hing Fong Road Kwai Fong Hong KongTelephone: (852) 26100 611Fax: (852) 24250 494asia.sales@Corporate Headquarters Zetex Semiconductors plc Zetex Technology Park ChaddertonOldham, OL9 9LL United KingdomTel: (44) 161 622 4444Fax: (44) 161 622 4446hq@These offices are supported by agents and distributors in major countries world-wide.This publication is issued to provide outline information only which (unless agreed by the Company in writing)may not be used,applied or reproduced for any purpose or form part of any order or contract or be regarded as a representation relating to the products or services concerned.The Company reserves the right to alter without notice the specification,design,price or conditions of supply of any product or service.For the latest product information,log on to©ZetexSemiconductors plc 2007CONTROLLING DIMENSIONS IN MILLIMETRES APPROX. CONVERTED DIMENSIONS IN INCHESDIM MILLIMETRESINCHES DIM MILLIMETRES INCHES MIN.MAX.MIN.MAX.MIN.MAX.MIN.MAX.A 0.80 1.000.0310.039e 0.65REF 0.0256BSC A10.000.050.000.002E 2.00BSC 0.0787BSC A20.650.750.02550.0295E20.430.630.0170.0249A30.150.250.0060.0098E40.160.360.0060.014b 0.240.340.0090.013L 0.200.450.00780.0157b10.170.300.00660.0118L20.1250.000.005D 3.00BSC 0.118BSC r 0.075BSC0.0029BSCD20.82 1.020.0320.040⍜0Њ12Њ0Њ12ЊD31.011.210.03970.0476MLP832 PACKAGE DIMENSIONS分销商库存信息: DIODESZXTD2M832TA。

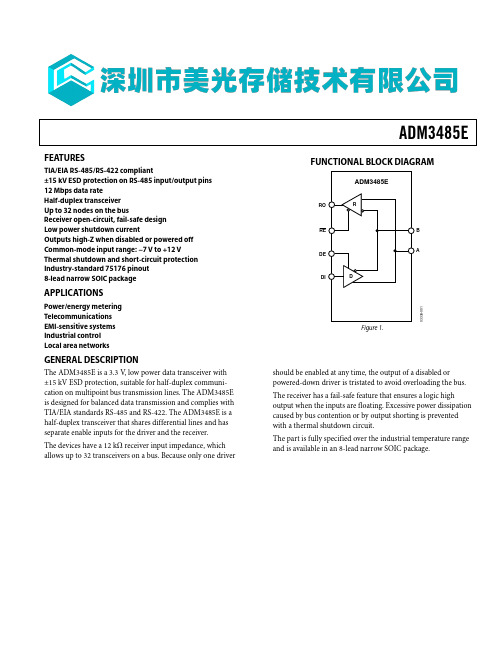

瑞盟科技 MS3485 数据手册说明书

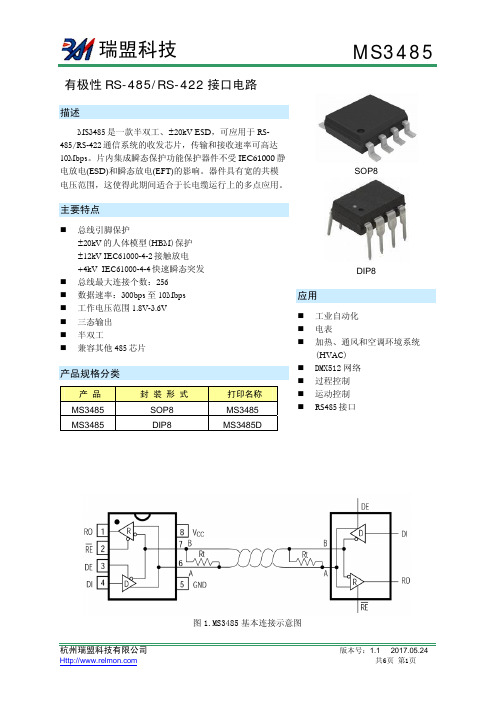

有极性RS-485/RS-422接口电路SOP8DIP8描述MS3485是一款半双工、±20kV ESD ,可应用于RS-485/RS-422通信系统的收发芯片,传输和接收速率可高达10Mbps 。

片内集成瞬态保护功能保护器件不受IEC61000静电放电(ESD)和瞬态放电(EFT)的影响。

器件具有宽的共模电压范围,这使得此期间适合于长电缆运行上的多点应用。

主要特点⏹ 总线引脚保护±20kV 的人体模型(HBM )保护±12kV IEC61000-4-2接触放电 +4kV IEC61000-4-4快速瞬态突发 ⏹ 总线最大连接个数:256 ⏹ 数据速率:300bps 至10Mbps ⏹ 工作电压范围1.8V-3.6V ⏹ 三态输出 ⏹ 半双工⏹ 兼容其他485芯片产品规格分类产 品 封 装 形 式 打印名称 MS3485 SOP8 MS3485 MS3485DIP8MS3485D应用⏹ 工业自动化 ⏹ 电表⏹ 加热、通风和空调环境系统(HVAC ) ⏹ DMX512网络 ⏹ 过程控制⏹ 运动控制 ⏹ RS485接口图1.MS3485基本连接示意图管脚说明引 脚 序 号名 称功 能 描 述1 RO接收输出端 2 RE接收使能端,低电平有效,RE 为高时,接收输出端为高阻 3 DE 发送使能端,高电平有效,DE 为低时,发送输出为高阻。

4 DI 发送输入端 5 GND 地 6 A 总线端口A 7 B 总线端口B 8VCC电源极限参数参 数 符 号 参 数 范 围 单位供电电压 V CC -0.5~+5 V 控制输入电压 V DE 、V RE -0.5~+5V 发送输入电压 V DI,IN -0.5~+5 V 发送输出电压 V A,OUT 、V B,OUT-0.5~+5 V 接收输入电压 V A,IN 、V B,IN -7~+12V 接收输出电压 V RO -0.5~+5 V 470(SOP8封装) 连续功率谱(T A =70℃)P C 725(DIP8封装) mW 工作温度范围 T WORK -40~+85 ℃ 存储温度范围 T STORE -60~+160 ℃ 焊锡温度(5秒) T SOLDERING+300℃直流特性VCC = 3.3V ,TA=+25℃,除非特别说明参 数 符 号 测 试 条 件最小值典型值 最大值 单位无负载2.8 2.9 发送差分输出 V ODR L =50Ω 1.35V互补输出状态输出 差分电压幅度变化 ΔV OD R L =50Ω 0.2 V 驱动输出共模电压 V OCR L =50Ω1.65 3 V 互补输出状态共模 输出电压幅度变化ΔV OC R L =50Ω 0.2 V输入高电平 V IH DE ,RE ,DI 2.0 V输入低电平V ILDE ,RE ,DI 0.8 V 逻辑端口输入电流 I IN,LOGIC DE ,RE ,DI ±2 uA V IN =3.3V 40 90总线端口输入电流 I IN,BUSDE=0V ,V CC =3.3VV IN =0V60 100 uA接收差分阈值电压 V TH -7V ≤V CM ≤12V -0.2 0.2 V 接收输入迟滞 ΔV TH V CM =0V 25 mV 接收输出高电平 V OH I OUT =-1.5mA ,V ID =200mV VCC-0.4V接收输出低电平 V OL I OUT =-1.5mA ,V ID =200mV 0.4 V 接收三态(高阻) 输出电流 I OSRV CC =3.3V ,0V ≤V OUT ≤V CC±1 uA 接收输入阻抗 R IN -7V ≤V CM ≤12V 100 k Ω 电源电流 I CC 无负载,RE=DE=DI=0V or V CC 0.2 mA V OUT = -7V 133 发送输出短路电流 I OSDV OUT = 12V80mA 接收输出短路电流 I OSR 0V ≤V RO ≤V CC98 mA A 、B 管脚ESD 保护 V ESD Human Body Model±20 kV开关特性VCC = 3.3V ,TA=+25℃,除非特别说明参 数 符 号 测 试 条 件 最小值典型值 最大值 单位 t PLH 7 22 35 发送传输延时 t PHL R L =27Ω,C LA =C LB =15pF 7 22 35ns发送传输失真 t PDS R L =27Ω,C LA =C LB =15pF 8 ns 发送使能开启延时输出为高 t PZH R L =110Ω,C LA =C LB =15pF 45 90 ns 发送使能开启延时输出为低 t PZL R L =110Ω,C LA =C LB =15pF 45 90 ns 发送使能关闭延时输出为高 t PHZ R L =110Ω,C LA =C LB =15pF 40 80 ns 发送使能关闭延时输出为低 t PLZ R L =110Ω,C LA =C LB =15pF 40 80 ns t PLH 25 65 90 接收传输延时 t PHL C L =15pF25 75 120ns接收传输失真 t PDS C L =15pF ,| t PLH –t PHL | 10 ns 接收使能开启延时输出为高 t PZH C L =15pF 25 50 ns 接收使能开启延时输出为低 t PZL C L =15pF 25 50 ns 接收使能关闭延时输出为高 t PHZ C L =15pF 25 45 ns 接收使能关闭延时输出为低 t PLZC L =15pF25 45 ns 最高数据速率 f MAX10 Mbps封装外形图尺寸(英寸)最大0.0690.0100.061DIP8尺寸(毫米) 尺寸(英寸) 符号最小 最大 最小 最大A 3.710 4.310 0.146 0.170A1 0.510 0.020A2 3.200 3.600 0.126 0.142B 0.380 0.570 0.015 0.022B1 1.524(BSC) 0.060(BSC)C 0.204 0.360 0.008 0.014D 9.000 9.400 0.354 0.370E 6.200 6.600 0.244 0.260E1 7.320 7.920 0.288 0.312e 2.540(BSC) 0.100(BSC)L 3.000 3.600 0.118 0.142 E2 8.400 9.000 0.331 0.354。

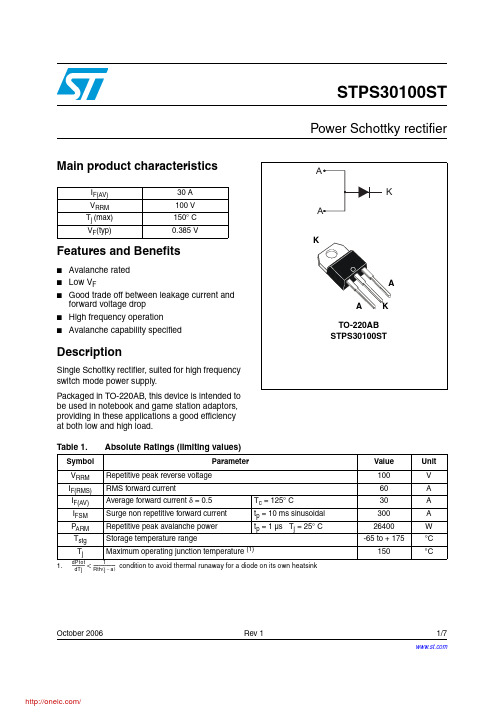

STPS30100ST;中文规格书,Datasheet资料

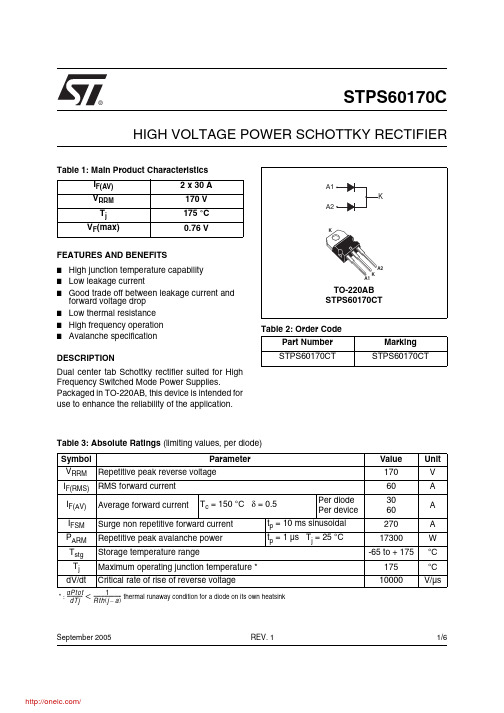

October 2006 Rev 11/7STPS30100STPower Schottky rectifierMain product characteristicsFeatures and Benefits■Avalanche rated ■Low V F■Good trade off between leakage current and forward voltage drop ■High frequency operation ■Avalanche capability specifiedDescriptionSingle Schottky rectifier, suited for high frequency switch mode power supply.Packaged in TO-220AB, this device is intended to be used in notebook and game station adaptors, providing in these applications a good efficiency at both low and high load.I F(AV)30 A V RRM 100 V T j (max)150° C V F (typ)0.385 VTable 1.Absolute Ratings (limiting values)Symbol ParameterValue Unit V RRM Repetitive peak reverse voltage 100V I F(RMS)RMS forward current60A I F(AV)Average forward current δ = 0.5T c = 125° C 30A I FSM Surge non repetitive forward current t p = 10 ms sinusoidal 300A P ARM Repetitive peak avalanche power t p = 1 µs T j = 25° C26400W T stg Storage temperature range-65 to + 175°C T jMaximum operating junction temperature (1)1. condition to avoid thermal runaway for a diode on its own heatsink150°CdPtot dTj---------------1Rth j a –()-------------------------<Characteristics STPS30100ST2/71 CharacteristicsTo evaluate the conduction losses use the following equation:P = 0.475 x I F(AV) + 0.006 x I F 2(RMS)Table 2.Thermal resistanceSymbol ParameterValue Unit R th(j-c)Junction to case1°C/WTable 3.Static electrical characteristics (per diode)SymbolParameterTest Conditions Min.Typ.Max.Unit I R (1)1.Pulse test: t p = 5 ms, δ < 2%Reverse leakage currentT j = 25° CV R = V RRM175µA T j = 125° C 2050mA T j = 25° C V R = 70 V 60µA T j = 125° C 1020mAV F (2)2.Pulse test: t p = 380 µs, δ < 2%Forward voltage dropT j = 25° C I F = 5 A0.475VT j = 125° C 0.385T j = 25° C I F = 10 A0.555T j = 125° C 0.475T j = 25° C I F = 15 A 0.6200.660T j = 125° C 0.5250.565T j = 25° C I F = 30 A0.7400.800T j = 125° C0.6050.655STPS30100STCharacteristics3/7Figure 1.Conduction losses versus average Figure 2.Average forward current versusTδ=t /Tp tTδ=t p /Tt Figure 3.Normalized avalanche power derating versus pulse durationFigure 4.Normalized avalanche power derating versus junction Figure 5.Non repetitive surge peak forward current versus overload duration Figure 6.Relative variation of thermalimpedance junction to case versusCharacteristicsSTPS30100ST4/7Figure 7.Reverse leakage current versusreverse voltage applied (typicalFigure 8.Junction capacitance versus reverse voltage applied (typical Figure 9.Forward voltage drop versusFigure 10.Forward voltage drop versusSTPS30100ST Package Information5/72 Package InformationEpoxy meets UL94,V0In order to meet environmental requirements, ST offers these devices in ECOP ACK®packages. These packages have a lead-free second level interconnect. The category of second level interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label. ECOP ACK is an ST trademark. ECOP ACK specifications are available at: .Ordering Information STPS30100ST6/73 Ordering Information4 Revision HistoryOrdering type Marking Package Weight Base qtyDelivery modeSTPS30100STSTPS30100STTO-220AB2.23 g50TubeDate RevisionChanges24-Oct-20061First issueSTPS30100STPlease Read Carefully:Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.All ST products are sold pursuant to ST’s terms and conditions of sale.Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.UNLESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER’S OWN RISK.Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.ST and the ST logo are trademarks or registered trademarks of ST in various countries.Information in this document supersedes and replaces all information previously supplied.The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.© 2006 STMicroelectronics - All rights reservedSTMicroelectronics group of companiesAustralia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America7/7分销商库存信息: STMSTPS30100ST。

杨泽阳州杨杰电子科技有限公司S-S348电阻说明书

Mechanical Data ● Package: DO-214AA (SMB)

Molding compound meets UL 94 V-0 flammability

rating, RoHS-compliant, halogen-free

● Terminals: Tin plated leads, solderable per

Ta =25℃

5.0

rated DC blocking voltage per diode IRRM μA

@ VRM=VRRM

Ta =125℃

125

S-S348 Rev. 2.1, 07-Mar-15

1/5 Yangzhou Yangjie Electronic Technology Co., Ltd.

Device marking code

GS2A

GS2B

Repetitive peak reverse voltage

VRRM V

50

100

Average rectified output current @60Hz sine wave, resistance load, TL (Fig.1)

Surge(non-repetitive)forward current @ 60Hz half-sine wave,1 cycle, Ta=25℃

Peak Forward Surge Current(A)

30

20

10

150

01

1000

10

100

Number of Cycles

FIG4:Typical Reverse Characteristics

100

1.0

Schurter PG07连接器芯片块文件说明书

1Strip Block for Snap-in Mounting with up to 6 IEC Appliance Outlets F4751 with 2 ganged outlets in white4751 with 4 ganged outlets in grey4751 with 6 ganged outlets in blackSee below:Approvals and CompliancesF70° CDescription- Panel mount- Snap-in version from front side- Strip block from 2 up to 6 outlets type F - Bus bar for L/N/PE- Solder pin or quick connect terminals 6.3 x 0.8 or 4.8 x 0.8 mmUnique Selling Proposition- Compact design- Prewired blocks with 2, 4 or 6 outlets - Cord retention for cordsets with V-Lock - Color coding in black, grey or whiteCharacteristics- Compact solution for intelligent PDU applications- Suitable for use in equipment according to IEC/UL 60950Other versions on request- Other panel thicknesses: S = 1.0 - 3.0 mm - Other terminals on request - Individual live contactWeblinkspdf data sheet , html data sheet , General Product Information ,Distributor-Stock-Check , Accessories , Detailed request for product , Landing PageThe integration of light pipes in the appliance outlet provides status indication in smart PDUs. See PDU Landing Page for more information. Power Distribution UnitsT echnical DataRatings IEC10 A / 250 VAC; 50 Hz Ratings UL/CSA 15 A / 250 VAC; 60 Hz Dielectric Strength> 2.5 kVAC between L-N > 3 kVAC between L/N-PE (1 min/50 Hz)Allowable Operation Tempe-rature-25 °C to 70 °CIP-Protection from front side IP20 acc. to IEC 60529Insulation cover Suitable for appliances with protection class I acc. to IEC 61140TerminalSolder pin or quick connect terminals 6.3 x 0.8 or 4.8 x 0.8 mm Panel Thickness S Snap-in 1.5 mmMaterial: HousingPA6, black / grey / white, UL 94V-0appliance inlet/-outletF acc. to IEC 60320-3UL 60320-1 CSA C22.2 no. 60320-1 (for cold conditions) pin-temperature 70 °C, 10 A, Protection Class IApprovals and CompliancesDetailed information on product approvals, code requirements, usage instructions and detailed test conditions can be looked up in Details about ApprovalsSCHURTER products are designed for use in industrial environments. They have approvals from independent testing bodies according to national and international standards. Products with specific characteristics and requirements such as required in the automotive sector according to IATF 16949, medical technology according to ISO 13485 or in the aerospace industry can be offered exclusively with customer-specific, individual agree-ments by SCHURTER.ApprovalsThe approval mark is used by the testing authorities to certify compliance with the safety requirements placed on electronic products. Approval Reference T ype: 4751Approval LogoCertificates Certification Body Description VDE Approvals VDE Certificate Number: UL Approvals ULUL File Number: CCC ApprovalsCCCCCC Certificate Number:Product standardsProduct standards that are referencedOrganization Design StandardDescriptionDesigned according to IEC 60320-1Appliance couplers for household and similar general purposesDesigned according to IEC 60320-3Appliance couplers for household and similar general purposesDesigned according to UL 60320-1Standard for Attachment Plugs and ReceptaclesDesigned according to CSA C22.2 no. 60320-1General Use Receptacles, Attachment Plugs, and Similar Wiring Devices Application standardsApplication standards where the product can be usedOrganization Design StandardDescriptionDesigned for applications acc.IEC/UL 60950IEC 60950-1 includes the basic requirements for the safety of informationtechnology equipment.CompliancesThe product complies with following Guide LinesIdentification Details InitiatorDescriptionRoHS SCHURTER AG Directive RoHS 2011/65/EU, Amendment (EU) 2015/836China RoHS SCHURTER AG The law SJ / T 11363-2006 (China RoHS) has been in force since 1 March2007. It is similar to the EU directive RoHS.REACH SCHURTER AG On 1 June 2007, Regulation (EC) No 1907/2006 on the Registration,Evaluation, Authorization and Restriction of Chemicals 1 (abbreviated as"REACH") entered into force.Dimensions [mm]+.123+0.10 0 N o .All VariantsMating Inlets/PlugsCategory / DescriptionPlug Overview complete4732, Mounting: Power Cord, Plug: IEC E, Cable47324735, Mounting: Power Cord, Plug: IEC E, Cable47359009, Mounting: Plug: IEC E, Screw clamps90094733, Mounting: Power Cord, Plug: IEC E, Cable47334736, Mounting: Power Cord, Plug: IEC E, Cable4736Plug further types to 4751...The specifications, descriptions and illustrations indicated in this document are based on currentinformation. All content is subject to modifications and amendments. Information furnished is believed2.3.2194。

TSOP34838;中文规格书,Datasheet资料

IR Receiver Modules for Remote Control SystemsMECHANICAL DATAPinning for TSOP348.., TSOP344..:1 = OUT, 2 = GND, 3 = V SPinning for TSOP322.., TSOP324..:1 = OUT, 2 = V S , 3 = GNDFEATURES•Very low supply current•Photo detector and preamplifier in one package •Internal filter for PCM frequency •Improved shielding against EMI •Supply voltage: 2.5 V to 5.5 V•Improved immunity against ambient light •Insensitive to supply voltage ripple and noise•Material categorization: For definitions of compliance please see /doc?99912DESCRIPTIONThese products are miniaturized receivers for infrared remote control systems. A PIN diode and a preamplifier are assembled on a lead frame, the epoxy package acts as an IR filter.The demodulated output signal can be directly decoded by a microprocessor. The TSOP348.., TSOP322.. are compatible with all common IR remote control data formats. The TSOP324.., TSOP344.. are optimized to suppress almost all spurious pulses from energy saving fluorescent lamps but will also suppress some data signals.This component has not been qualified according to automotive specifications.BLOCK DIAGRAMAPPLICATION CIRCUITPARTS TABLECARRIER FREQUENCY STANDARD APPLICATIONS(AGC2)VERY NOISY ENVIRONMENTS(AGC4)PINNING1 = OUT,2 = GND,3 = V S1 = OUT,2 = V S ,3 = GND1 = OUT,2 = GND,3 = V S1 = OUT,2 = V S ,3 = GND30 kHz TSOP34830TSOP32230TSOP34430TSOP3243033 kHz TSOP34833TSOP32233TSOP34433TSOP3243336 kHz TSOP34836TSOP32236TSOP34436TSOP3243638 kHz TSOP34838TSOP32238TSOP34438TSOP3243840 kHz TSOP34840TSOP32240TSOP34440TSOP3244056 kHzTSOP34856TSOP32256TSOP34456TSOP32456Note•Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect the device reliability.TYPICAL CHARACTERISTICS (T amb = 25 °C, unless otherwise specified)Fig. 1 - Output Active Low Fig. 2 - Pulse Length and Sensitivity in Dark AmbientABSOLUTE MAXIMUM RATINGSPARAMETER TEST CONDITIONSYMBOLVALUE UNIT Supply voltage V S - 0.3 to + 6V Supply current I S 3mA Output voltage V O - 0.3 to (V S + 0.3)V Output current I O 5mA Junction temperature T j 100°C Storage temperature range T stg - 25 to + 85°C Operating temperature range T amb- 25 to + 85°C Power consumption T amb ≤ 85 °C P tot 10mW Soldering temperaturet ≤ 10 s, 1 mm from caseT sd260°CELECTRICAL AND OPTICAL CHARACTERISTICS (T amb = 25 °C, unless otherwise specified)PARAMETER TEST CONDITION SYMBOLMIN.TYP.MAX.UNIT Supply current E v = 0, V S = 3.3 V I SD 0.270.350.45mA E v = 40 klx, sunlightI SH 0.45mA Supply voltage V S 2.55.5V Transmission distance E v = 0, test signal see fig. 1,IR diode TSAL6200,I F = 250 mA d 45m Output voltage low I OSL = 0.5 mA, E e = 0.7 mW/m 2,test signal see fig. 1V OSL 100mV Minimum irradiance Pulse width tolerance:t pi - 5/f 0 < t po < t pi + 6/f 0,test signal see fig. 1E e min.0.10.25mW/m 2Maximum irradiance t pi - 5/f 0 < t po < t pi + 6/f 0,test signal see fig. 1E e max.30W/m 2DirectivityAngle of half transmissiondistanceϕ1/2± 45degE eV O V VFig. 3 - Output Function Fig. 4 - Output Pulse Diagram Fig. 5 - Frequency Dependence of Responsivity Fig. 6 - Sensitivity in Bright AmbientFig. 7 - Sensitivity vs. Supply Voltage DisturbancesFig. 8 - Sensitivity vs. Electric Field DisturbancesEV O V V OL0.00.20.40.60.81.01.20.70.9 1.1 1.3f/f 0 - Relative Frequency16925E /E - R e l. R e s p o n s i v i t y e m i n.eFig. 9 - Max. Envelope Duty Cycle vs. Burst Length Fig. 10 - Sensitivity vs. Ambient TemperatureFig. 11 - Relative Spectral Sensitivity vs. WavelengthFig. 12 - Horizontal DirectivityFig. 13 - Sensitivity vs. Supply VoltageSUITABLE DATA FORMATThese products are designed to suppress spurious output pulses due to noise or disturbance signals. Data and disturbance signals can be distinguished by the devices according to carrier frequency, burst length and envelope duty cycle. The data signal should be close to the band-pass center frequency (e.g. 38 kH z) and fulfill the conditions in the table below.When a data signal is applied to the IR receiver in the presence of a disturbance signal, the sensitivity of the receiver is reduced to insure that no spurious pulses are present at the output. Some examples of disturbance signals which are suppressed are:•DC light (e.g. from tungsten bulb or sunlight)•Continuous signals at any frequency•Strongly or weakly modulated noise from fluorescent lamps with electronic ballasts (see figure 14 or figure 15)Fig. 14 - IR Signal from Fluorescent Lampwith Low ModulationFig. 15 - IR Signal from Fluorescent Lampwith High ModulationNote•For data formats with short bursts please see the datasheet for TSOP323.., TSOP325.., TSOP343.., TSOP345..0101520Time (ms)16920I R S i g n a l50101520Time (ms)16921I R S i g n a l5TSOP322.., TSOP348..TSOP324.., TSOP344..Minimum burst length10 cycles/burst 10 cycles/burst After each burst of lengtha minimum gap time is required of10 to 70 cycles ≥ 10 cycles 10 to 35 cycles ≥ 10 cycles For bursts greater thana minimum gap time in the data stream is needed of 70 cycles > 4 x burst length35 cycles> 10 x burst lengthMaximum number of continuous short bursts/second 18001500Recommended for NEC code yes yes Recommended for RC5/RC6 code yes yes Recommended for Sony codeyes no Recommended for Thomson 56 kHz codeyes yes Recommended for Mitsubishi code (38 kHz, preburst 8 ms, 16 bit)yes no Recommended for Sharp codeyesyesSuppression of interference from fluorescent lampsMost common disturbance signals are suppressedEven extreme disturbance signals are suppressedPACKAGE DIMENSIONS in millimetersLegal Disclaimer Notice VishayDisclaimerALL PRODU CT, PRODU CT SPECIFICATIONS AND DATA ARE SU BJECT TO CHANGE WITHOU T NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively,“Vishay”), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.Statements regarding the suitability of products for certain types of applications are based on Vishay’s knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer’s responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and/or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer’s technical experts. Product specifications do not expand or otherwise modify Vishay’s terms and conditions of purchase, including but not limited to the warranty expressed therein.Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk and agree to fully indemnify and hold Vishay and its distributors harmless from and against any and all claims, liabilities, expenses and damages arising or resulting in connection with such use or sale, including attorneys fees, even if such claim alleges that Vishay or its distributor was negligent regarding the design or manufacture of the part. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.Material Category PolicyVishay Intertechnology, Inc. hereb y certifies that all its products that are identified as RoHS-Compliant fulfill the definitions and restrictions defined under Directive 2011/65/EU of The European Parliament and of the Council of June 8, 2011 on the restriction of the use of certain hazardous substances in electrical and electronic equipment (EEE) - recast, unless otherwise specified as non-compliant.Please note that some Vishay documentation may still make reference to RoHS Directive 2002/95/EC. We confirm that all the products identified as being compliant to Directive 2002/95/EC conform to Directive 2011/65/EU.分销商库存信息: VISHAYTSOP34838。

SP000074866中文资料

Vbb(on)

VON(CL) RDS(ON)

5.5 .. 24 V 39 V 12 mΩ 7A 27 A 50 A 6 µA

IL(nom) IL(ISO) IL6(SC)

Ibb(OFF)

Basic Features

• • • • • Very low standby current Current controlled input pin Improved electromagnetic compatibility (EMC) Fast demagnetization of inductive loads Stable behavior at under-voltage

Type BTS 6142D

Data Sheet

PO74G38072A中文资料

FEATURES:DESCRIPTION:. Patented technology. Max input frequency > 1GHz. Operating frequency up to 1GHz with 2pf load . Operating frequency up to 700MHz with 5pf load . Operating frequency up to 400MHz with 15pf load . Operating frequency up to 200MHz with 50pf load . Very low output pin to pin skew < 20ps . VCC = 1.65V to 3.6V. Propagation delay < 1.3ns max with 15pf load . Low input capacitance: 3pf typical . 1:2 fanout. Available in 8 pin SOIC packagePotato Semiconductor’s PO74G38072A is designed for world top performance using submicron CMOS technology to achieve 1GHz TTL output frequency with less than 20ps output pin to pin skew.PO74G38072A is a 3.3V CMOS 1 input to 2 outputs Buffered driver to achieve 1GHz output frequency. Typical applications are clock and signal distribution.Inputs can be driven from either 3.3V or 5V devices. This feature allows the use of these devices astranslators in a mixed 3.3V/5V system environment.Pin Configuration Logic Block DiagramPin DescriptionPin Name Description t u p n IN IOutputsOx02/13/0711GHz TTL/CMOS Potato ChipMaximum RatingsDC Electrical CharacteristicsSymbolDescriptionTest ConditionsMin Typ Max UnitV OH Output High voltage Vcc=3V Vin=V IH or V IL , I OH = -12mA 2.4 3 - V V OL Output Low voltage Vcc=3V Vin=V IH or V IL , I OH =12mA - 0.3 0.5 V V IH Input High voltage Guaranteed Logic HIGH Level (Input Pin) 2 - Vcc V V IL Input Low voltage Guaranteed Logic LOW Level (Input Pin)-0.5 - 0.8 V I IH Input High current Vcc = 3.6V and Vin = 5.5V - - 1 uA I IL Input Low current Vcc = 3.6V and Vin = 0V - --1uA V IKClamp diode voltageVcc = Min. And I IN = -18mA--0.7 -1.2VNotes:1.For conditions shown as Max. or Min., use appropriate value specified under Electrical Characteristics for the applicable device type.2.Typical values are at Vcc =3.3V, 25 °C ambient.3.This parameter is guaranteed but not tested.4.Not more than one output should be shorted at one time. Duration of the test should not exceed one second.5.VoH = Vcc – 0.6V at rated currentDescription Max Unit Storage Temperature -65 to 150 °C Operation Temperature -40 to 85 °C Operation Voltage -0.5 to +4.6 V Input Voltage -0.5 to +5.5 V Output Voltage-0.5 to Vcc+0.5VNote:stresses greater than listed under Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability specification is not implied.02/13/0721GHz TTL/CMOS Potato ChipPower Supply CharacteristicsSymbolDescriptionTest Conditions (1)Min Typ Max UnitIcc Q Quiescent Power Supply Current Vcc=Max, Vin=Vcc or GND - 0.1 30 uA !IccPower Supply Current per Input HighVcc=Max, Vin= Vcc-0.6V-50300uANotes:1.For conditions shown as Max. or Min., use appropriate value specified under Electrical Characteristics for the applicable device type.2.Typical values are at Vcc =3.3V, 25°C ambient. 3.This parameter is guaranteed but not tested.4.Not more than one output should be shorted at one time. Duration of the test should not exceed one second.5.VoH = Vcc – 0.6V at rated currentCapacitanceParameters (1)DescriptionTest ConditionsTyp Max UnitCin Input Capacitance Vin = 0V 3 4 pFCoutOutput CapacitanceVout = 0V-6pFNotes:1This parameter is determined by device characterization but not production tested.Switching Characteristicst i n U x a M)1( s n o i t i d n o C t s e Tn o i t p i r c s e Dl o b m y S t PLH Propagation Delay A to Bn CL = 15pF 1.3 ns t PHL Propagation Delay A to Bn CL = 15pF 1.3 ns tr/tf Rise/Fall Time0.8V – 2.0V0.8 ns tsk(o)Output Pin to Pin Skew (Same Package) CL = 15pF, 125MHz 20ps tsk(pp) Output Skew (Different Package) CL = 15pF, 125MHz0.25 nsfmax F p 05 = L C y c n e u q e r F t u p n I 200 MHz fmax F p 51= L C y c n e u q e r F t u p n I 400 MHz fmax F p 5 = L C y c n e u q e r F t u p n I 700 MHz fmaxF p 2 = L Cy c n e u q e r F t u p n I 1000MHzNotes:1.See test circuits and waveforms.2.tpLH, tpHL, tsk(p), and tsk(o) are production tested. All other parameters guaranteed but not production tested.3.Airflow of 1m/s is recommended for frequencies above 133MHz31GHz TTL/CMOS Potato ChipTest Circuit41GHz TTL/CMOS Potato ChipTest Waveforms02/13/0751GHz TTL/CMOS Potato ChipPackaging Mechanical Drawing: 8 pin SOIC02/13/07Ordering Information。

PSMN7R0-100ES,127;中文规格书,Datasheet资料

PSMN7R0-100ESN-channel 100V 6.8 mΩ standard level MOSFET in I2PAK.Rev. 03 — 23 February 2010Product data sheet 1.Product profile1.1General descriptionStandard level N-channel MOSFET in I2PAK package qualified to 175C. This product isdesigned and qualified for use in a wide range of industrial, communications and domesticequipment.1.2Features and benefitsHigh efficiency due to low switchingand conduction lossesSuitable for standard level gate drive1.3ApplicationsDC-to-DC converters Load switching Motor controlServer power supplies1.4Quick reference dataTable 1.Quick referenceSymbol Parameter Conditions Min Typ Max Unit V DS drain-source voltage T j≥25°C; T j≤175°C--100VI D drain current T mb=25°C; V GS=10V;see Figure 1[1]--100AP tot total powerdissipationT mb=25°C; see Figure 2--269W T j junction temperature-55-175°C Avalanche ruggednessE DS(AL)S non-repetitivedrain-sourceavalanche energy V GS=10V; T j(init)=25°C;I D=100A; V sup≤100V;unclamped; R GS=50Ω--315mJDynamic characteristicsQ GD gate-drain charge V GS=10V; I D=25A;V DS=50V; see Figure 15and 14-36-nCQ G(tot)total gate charge V GS=10V; I D=25A;V DS=50V; see Figure 14and 15-125-nC[1]Continuous current is limited by package2.Pinning information3.Ordering informationStatic characteristics R DSondrain-sourceon-state resistanceV GS =10V; I D =15A; T j =100°C; see Figure 12--12m ΩV GS =10V; I D =15A; T j =25°C; see Figure 13- 5.46.8m ΩTable 1.Quick referenceSymbol Parameter ConditionsMinTyp Max Unit Table 2.Pinning information Pin Symbol Description Simplified outline Graphic symbol1G gate SOT226 (I2PAK)2D drain 3S sourcembDmounting base; connected to drain321mbTable 3.Ordering informationType numberPackage NameDescriptionVersion PSMN7R0-100ES I2PAKplastic single-ended package (I2PAK); TO-262SOT2264.Limiting values[1]Continuous current is limited by packageTable 4.Limiting values In accordance with the Absolute Maximum Rating System (IEC 60134).Symbol ParameterConditionsMin Max Unit V DS drain-source voltage T j ≥25°C; T j ≤175°C-100V V DGR drain-gate voltage T j ≤175°C; T j ≥25°C; R GS =20k Ω-100V V GS gate-source voltage -2020V I D drain current V GS =10V; T mb =100°C; see Figure 1-85A V GS =10V; T mb =25°C; see Figure 1[1]-100A I DM peak drain current t p ≤10µs; pulsed; T mb =25°C; see Figure 3-475A P tot total power dissipation T mb =25°C; see Figure 2-269W T stg storage temperature -55175°C T j junction temperature -55175°C T sld(M)peak soldering temperature -260°C Source-drain diodeI S source current T mb =25°C;[1]-100A I SM peak source currentt p ≤10µs; pulsed; T mb =25°C-475A Avalanche ruggednessE DS(AL)Snon-repetitive drain-source avalanche energy V GS =10V; T j(init)=25°C; I D =100A; V sup ≤100V; unclamped; R GS =50Ω-315mJ5.Thermal characteristicsTable 5.Thermal characteristics Symbol ParameterConditions Min Typ Max Unit R th(j-mb)thermal resistance from junction to mounting basesee Figure 4-0.30.56K/W R th(j-a)thermal resistance from junction to ambientvertical in free air-60-K/W6.CharacteristicsTable 6.CharacteristicsSymbol Parameter Conditions Min Typ Max Unit Static characteristicsV(BR)DSS drain-sourcebreakdown voltage I D=0.25mA;V GS=0V; T j=-55°C90--V I D=0.25mA;V GS=0V; T j=25°C100--VV GS(th)gate-source thresholdvoltage I D=1mA; V DS = V GS; T j=175°C; see Figure 101--V I D=1mA; V DS = V GS; T j=25°C;see Figure 11and 10234V I D=1mA; V DS = V GS; T j=-55°C;see Figure 10-- 4.8VI DSS drain leakage current V DS=100V; V GS=0V;T j=125°C--150µAV DS=100V; V GS=0V;T j=25°C-0.084µA I GSS gate leakage current V GS=20V; V DS=0V; T j=25°C-10100nAV GS=-20V;V DS=0V; T j=25°C-10100nAR DSon drain-source on-stateresistance V GS=10V; I D=15A; T j=100°C; see Figure 12--12mΩV GS=10V; I D=15A; T j=175°C; see Figure 12-1519mΩV GS=10V; I D=15A; T j=25°C;see Figure 13- 5.4 6.8mΩR G internal gate resistance(AC)f=1MHz-0.74-ΩDynamic characteristicsQ G(tot)total gate charge I D=25A;V DS=50V;V GS=10V;see Figure 14and 15-125-nCI D=0A;V DS=0V; V GS=10V-100-nC Q GS gate-source charge I D=25A;V DS=50V;V GS=10V;see Figure 15and 14-28-nCQ GS(th)pre-thresholdgate-source chargeI D=25A; V DS=50V;V GS=10V;see Figure 15-19.4-nCQ GS(th-pl)post-thresholdgate-source charge-9-nCQ GD gate-drain charge I D=25A;V DS=50V;V GS=10V;see Figure 15and 14-36-nCV GS(pl)gate-source plateauvoltageV DS=50V;see Figure 15 and 14- 4.3-VC iss input capacitance V DS=50V;V GS=0V; f=1MHz; T j=25°C;see Figure 16-6686-pFC oss output capacitance-438-pF C rss reverse transfercapacitance-272-pFt d(on)turn-on delay time V DS=50V;R L=2Ω; V GS=10V;R G(ext)=4.7Ω; T j=25°C -34.6-nst r rise time-45.6-ns t d(off)turn-off delay time-103.9-ns t f fall time-49.5-nsSource-drain diodeV SD source-drain voltage I S =25A;V GS =0V; T j =25°C; see Figure 17-0.8 1.2V t rr reverse recovery time I S =25A;dI S /dt =100A/µs; V GS =0V; V DS =50V-64-ns Q rrecovered charge-167-nCTable 6.Characteristics …continued Symbol ParameterConditionsMin Typ Max Unit分销商库存信息: NXPPSMN7R0-100ES,127。

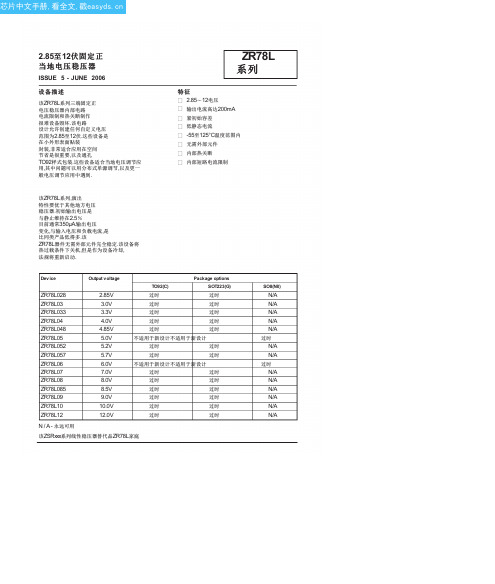

ZR78L033中文资料(Zetex Semiconductors)中文数据手册「EasyDatasheet - 矽搜」

第五系数

O

IO=5.0mA

ZR78L12TEST条件(除非另有说明): T已

符号参数

条件

V

输出电压

V

线路调整

IO= 1 200mA的

Vin=14 to 20V IO= 1为100mA

V =14 to 20V

V

负载调节

l

静态电流

I = 1 200mA的 IO= 1为100mA

l

静态电流变化I

V

输出噪声电压

Package options

TO92(C) 过时

SOT223(G) 过时

过时

过时

过时

过时

过时

过时

过时

过时

不适用于新设计不适用于新设计

过时

过时

过时

过时

不适用于新设计不适用于新设计

过时

过时

过时

过时

过时 过时

过时 过时

过时

过时

过时

过时

N / A - 永远可用 该ZSRxxx系列线性稳压器替代品ZR78L家庭

V

需要输入电压

防护持调控

Vin= 7.85至18V f=120Hz

V /∆T 平均温度

第五系数

O

IO=5.0mA

=Tj = -55至125°C

j=25°C, I O=100mA, V 在=8V MIN. TYP. MAX. UNITS

3.9

4.0

4.1

V

3.84

4.16 V

3.84

4.16 V

10

40

9.75 10

10.25 V

9.6

10.4 V

9.6

CS5532-BSZR;CS5534-BSZR;CDB5532U;中文规格书,Datasheet资料

Copyright © Cirrus Logic, Inc. 2008CS5532/34-BS24-bit ∆Σ ADCs with Ultra-low-noise PGIAFeaturesChopper-stabilized PGIA (ProgrammableGain Instrumentation Amplifier, 1x to 64x)– 6 nV/√Hz @ 0.1 Hz (No 1/f noise) at 64x –1200pA Input Current with Gains >1 Delta-sigma Analog-to-digital Converter –Linearity Error: 0.0007% FS–Noise-free Resolution: Up to 23 bits Two- or Four-channel Differential MUX Scalable Input Span via Calibration –±5 mV to differential ±2.5VScalable V REF Input: Up to Analog Supply Simple Three-wire Serial Interface –SPI™ and Microwire™ Compatible –Schmitt Trigger on Serial Clock (SCLK) R/W Calibration Registers Per Channel Selectable Word Rates: 6.25 to 3,840 Sps Selectable 50 or 60 Hz RejectionPower Supply Configurations–VA+ = +5 V; VA- = 0 V; VD+ = +3 V to +5 V–VA+ = +2.5 V; VA- = -2.5 V; VD+ = +3 V to +5 V –VA+ = +3 V; VA- = -3 V; VD+ = +3 VGeneral DescriptionThe CS5532/34 are highly integrated ∆Σ Analog-to-Digi-tal Converters (ADCs) which use charge-balance techniques to achieve 24-bit performance. The ADCs are optimized for measuring low-level unipolar or bipolar signals in weigh scale, process control, scientific, and medical applications.To accommodate these applications, the ADCs come as either two-channel (CS5532) or four-channel (CS5534)devices and include a very low-noise, chopper-stabilized instrumentation amplifier (6 nV/√Hz @ 0.1 Hz) with se-lectable gains of 1×, 2×, 4×, 8×, 16×, 32×, and 64×.These ADCs also include a fourth-order ∆Σ modulator followed by a digital filter which provides twenty selectable output word rates of 6.25, 7.5, 12.5, 15, 25, 30, 50, 60, 100,120, 200, 240, 400, 480, 800, 960, 1600, 1920, 3200, and 3840 Sps (MCLK =4.9152MHz).To ease communication between the ADCs and a micro-controller, the converters include a simple three-wire se-rial interface which is SPI™ and Microwire™ compatible with a Schmitt-trigger input on the serial clock (SCLK).High dynamic range, programmable output rates, and flexible power supply options makes these ADCs ideal solutions for weigh scale and process control applications.ORDERING INFORMATIONSee page 47VA+C1C2VREF+VREF-VD+DIFFERENTIAL 4TH ORDER ∆ΣMODULATORPGIA 1,2,4,8,16PROGRAMMABLE SINC FIR FILTERMUX(CS5534SHOWN)AIN1+AIN1-AIN2+AIN2-AIN3+AIN3-AIN4+AIN4-SERIAL INTERFACELATCHCLOCK GENERATORCALIBRATION SRAM/CONTROLLOGICDGNDCSSDI SDO SCLKOSC2OSC1A1A0/GUARD VA-32,64OCT ‘08TABLE OF CONTENTS1.CHARACTERISTICS AND SPECIFICATIONS (4)ANALOG CHARACTERISTICS (4)TYPICAL RMS NOISE (NV) (7)TYPICAL NOISE-FREE RESOLUTION(BITS) (7)5 V DIGITAL CHARACTERISTICS (8)3 V DIGITAL CHARACTERISTICS (8)DYNAMIC CHARACTERISTICS (9)ABSOLUTE MAXIMUM RATINGS (9)SWITCHING CHARACTERISTICS (10)2.GENERAL DESCRIPTION (12)2.1.Analog Input (12)2.1.1. Analog Input Span (13)2.1.2. Multiplexed Settling Limitations (13)2.1.3. Voltage Noise Density Performance (13)2.1.4. No Offset DAC (14)2.2.Overview of ADC Register Structure and Operating Modes (14)2.2.1. System Initialization (15)2.2.2. Serial Port Interface (22)2.2.3. Reading/Writing On-Chip Registers (23)2.3.Configuration Register (23)2.3.1. Power Consumption (23)2.3.2. System Reset Sequence (23)2.3.3. Input Short (24)2.3.4. Guard Signal (24)2.3.5. Voltage Reference Select (24)2.3.6. Output Latch Pins (24)2.3.7. Offset and Gain Select (25)2.3.8. Filter Rate Select (25)2.4.Setting up the CSRs for a Measurement (27)2.5.Calibration (30)2.5.1. Calibration Registers (30)2.5.2. Performing Calibrations (31)2.5.3. Self Calibration (31)2.5.4. System Calibration (32)2.5.5. Calibration Tips (32)2.5.6. Limitations in Calibration Range (33)2.6.Performing Conversions (33)2.6.1. Single Conversion Mode (33)2.6.2. Continuous Conversion Mode (34)2.6.3. Examples of Using CSRs to Perform Conversions and Calibrations (35)ing Multiple ADCs Synchronously (36)2.8.Conversion Output Coding (36)2.9.Digital Filter (38)2.10.Clock Generator (39)2.11.Power Supply Arrangements (39)2.12.Getting Started (43)2.13.PCB Layout (43)3.PIN DESCRIPTIONS (44)4.SPECIFICATION DEFINITIONS (46)5.ORDERING INFORMATION (47)6.ENVIRONMENTAL, MANUFACTURING, & HANDLING INFORMATION (47)7.PACKAGE DRAWINGS (48)LIST OF FIGURESFigure 1. SDI Write Timing (Not to Scale) (11)Figure 2. SDO Read Timing (Not to Scale) (11)Figure 3. Multiplexer Configuration (12)Figure 4. Input models for AIN+ and AIN- pins (13)Figure 5. Measured Voltage Noise Density (13)Figure 6. CS5532/34 Register Diagram (14)Figure 7. Command and Data Word Timing (22)Figure 8. Guard Signal Shielding Scheme (24)Figure 9. Input Reference Model when VRS = 1 (25)Figure 10. Input Reference Model when VRS = 0 (25)Figure 11. Self Calibration of Offset (32)Figure 12. Self Calibration of Gain (32)Figure 13. System Calibration of Offset (32)Figure 14. System Calibration of Gain (32)Figure 15. Synchronizing Multiple ADCs (36)Figure 16. Digital Filter Response (WR = 60 Sps) (38)Figure 18. 120 Sps Filter Phase Plot to 120 Hz (38)Figure 17. 120 Sps Filter Magnitude Plot to 120 Hz (38)Figure 19. Z-Transforms of Digital Filters (38)Figure 20. On-chip Oscillator Model (39)Figure 21. CS5532 Configured with a Single +5 V Supply (40)Figure 22. CS5532 Configured with ±2.5 V Analog Supplies (41)Figure 23. CS5532 Configured with ±3 V Analog Supplies (41)Figure 24. CS5532 Configured for Thermocouple Measurement (42)Figure 25. Bridge with Series Resistors (42)LIST OF TABLESTable 1. Conversion Timing – Single Mode (34)Table 2. Conversion Timing – Continuous Mode (35)Table 3. Command Byte Pointer (35)Table 4. Output Coding for 24-bit CS5532 and CS5534 (37)1. CHARACTERISTICS AND SPECIFICATIONSANALOG CHARACTERISTICS(VA+, VD+ = 5 V ±5%; VREF+ = 5 V; VA-, VREF-, DGND = 0 V; MCLK = 4.9152 MHz; OWR (Output Word Rate) = 60 Sps; Bipolar Mode; Gain = 32)(See Notes 1 and 2.)Notes: 1.Applies after system calibration at any temperature within -40 °C ~ +85 °C.2.Specifications guaranteed by design, characterization, and/or test. LSB is 24 bits.3. This specification applies to the device only and does not include any effects by external parasiticthermocouples. The PGIA contributes 5 nV of offset drift, and the modulator contributes 640/G nV of offset drift, where G is the amplifier gain setting.4.Drift over specified temperature range after calibration at power-up at 25 °C.ParameterMin Typ Max Unit Accuracy Linearity Error -±0.0007±0.0015%FS No Missing Codes 24--Bits Bipolar Offset -±16±32LSB 24Unipolar Offset-±32±64LSB 24Offset Drift(Notes 3 and 4)-640/G +5-nV/°C Bipolar Full-scale Error -±8±31ppm Unipolar Full-scale Error -±16±62ppm Full-scale Drift(Note 4)-2-ppm/°CANALOG CHARACTERISTICS (Continued)(See Notes 1 and 2.)Notes: 5.The voltage on the analog inputs is amplified by the PGIA, and becomes V CM ± Gain*(AIN+ - AIN-)/2 atthe differential outputs of the amplifier. In addition to the input common mode + signal requirements for the analog input pins, the differential outputs of the amplifier must remain between (VA- + 0.1 V) and (VA+ - 0.1 V) to avoid saturation of the output stage.6.See the section of the data sheet which discusses input models.7.Input current on AIN+ or AIN- (with Gain =1), or VREF+ or VREF- may increase to 250nA if operatedwithin 50mV of VA+ or VA-. This is due to the rough charge buffer being saturated under these conditions.ParameterMin TypMaxUnitAnalog InputCommon Mode + Signal on AIN+ or AIN-Bipolar/Unipolar ModeGain = 1 Gain = 2, 4, 8, 16, 32, 64(Note 5)VA-VA- + 0.7--VA+VA+ - 1.7V V CVF Current on AIN+ or AIN-Gain = 1 (Note 6, 7)Gain = 2, 4, 8, 16, 32, 64--501200--nA pA Input Current Noise Gain = 1 Gain = 2, 4, 8, 16, 32, 64--2001--pA/√Hz pA/√Hz Input Leakage for Mux when Off (at 25 °C)-10-pA Off-channel Mux Isolation -120-dB Open Circuit Detect Current 100300-nA Common Mode Rejection dc, Gain = 1dc, Gain = 6450, 60 Hz ---90130120---dB dB dB Input Capacitance -60-pF Guard Drive Output -20-µA Voltage Reference Input Range (VREF+) - (VREF-)1 2.5(VA+)-(VA-)V CVF Current (Note 6, 7)-50-nA Common Mode Rejection dc 50, 60 Hz --120120--dB dB Input Capacitance 11-22pF System Calibration Specifications Full-scale Calibration Range Bipolar/Unipolar Mode 3-110%FS Offset Calibration Range Bipolar Mode -100-100%FS Offset Calibration Range Unipolar Mode -90-90%FSANALOG CHARACTERISTICS (Continued)(See Notes 1 and 2.)8.All outputs unloaded. All input CMOS levels.9.Power is specified when the instrumentation amplifier (Gain ≥ 2) is on. Analog supply current is reducedby approximately 1/2 when the instrumentation amplifier is off (Gain = 1).10.Tested with 100 mV change on VA+ or VA-.ParameterMinTypMaxUnitPower SuppliesDC Power Supply Currents (Normal Mode)I A+, I A-I D+- - 130.5151mA mA Power ConsumptionNormal Mode (Notes 8 and 9)Standby Sleep---70450080--mW mW µW Power Supply Rejection (Note 10)dc Positive Supplies dc Negative Supply--115115--dB dBTYPICAL RMS NOISE (nV)(See notes 11, 12, 13 and 14)Notes:11.The -B devices provide the best noise specifications.12.Wideband noise aliased into the baseband. Referred to the input. Typical values shown for 25 °C.13.For Peak-to-Peak Noise multiply by 6.6 for all ranges and output rates.14.Word rates and -3dB points with FRS = 0. When FRS = 1, word rates and -3dB points scale by 5/6.TYPICAL NOISE-FREE RESOLUTION(BITS)(See Notes 15 and 16)15.Noise-free resolution listed is for bipolar operation, and is calculated as LOG((Input Span)/(6.6xRMSNoise))/LOG(2) rounded to the nearest bit. For unipolar operation, the input span is 1/2 as large, so one bit is lost. The input span is calculated in the analog input span section of the data sheet. The noise-free resolution table is computed with a value of 1.0 in the gain register. Values other than 1.0 will scale the noise, and change the noise-free resolution accordingly.16.“Noise-free resolution” is not the same as “effective resolution”. Effective resolution is based on theRMS noise value, while noise-free resolution is based on a peak-to-peak noise value specified as 6.6 times the RMS noise value. Effective resolution is calculated as LOG((Input Span)/(RMS Noise))/LOG(2).Specifications are subject to change without notice.Output Word Rate (Sps)-3 dB Filter Frequency (Hz)Instrumentation Amplifier Gain x64x32x16x8x4x2x17.5 1.948.59101526509915 3.88121315213770139307.751718213052991966015.524252942731402771203134364259103198392240628013626051410202050409048012211319436973014502900581096023015927452310302060411082301,920390260470912181036207230145003,84078013602690538010800215004300086000Output Word Rate (Sps)-3 dB Filter Frequency (Hz)Instrumentation Amplifier Gainx64x32x16x8x4x2x17.5 1.942021222323232315 3.8820212222222222307.75192021222222226015.5192021212121211203118192021212121240621717181818181848012217171717171717960230161617171717171,920390161616161616163,840780131313131313135 V DIGITAL CHARACTERISTICS(VA+, VD+ = 5 V ±5%; VA-, DGND = 0 V; See Notes 2 and 17.)3 V DIGITAL CHARACTERISTICS(T A = 25 °C; VA+ = 5V ±5%; VD+ = 3.0V±10%; VA-, DGND = 0V; See Notes 2 and 17.)17.All measurements performed under static conditions.ParameterSymbol Min Typ Max Unit High-level Input Voltage All Pins Except SCLKSCLK V IH 0.6 VD+(VD+) - 0.45--VD+VD+V Low-level Input Voltage All Pins Except SCLKSCLK V IL 0.00.0-0.80.6V High-level Output Voltage A0 and A1, I out = -1.0 mASDO, I out = -5.0 mA V OH (VA+) - 1.0(VD+) - 1.0--V Low-level Output Voltage A0 and A1, I out = 1.0 mASDO, I out = 5.0 mAV OL --(VA-) + 0.40.4V Input Leakage Current I in -±1±10µA SDO Tri-State Leakage Current I OZ --±10µA Digital Output Pin CapacitanceC out-9-pFParameterSymbol Min Typ Max Unit High-level Input Voltage All Pins Except SCLKSCLK V IH 0.6 VD+(VD+) - 0.45-VD+VD+V Low-level Input Voltage All Pins Except SCLKSCLK V IL 0.00.0-0.80.6V High-level Output Voltage A0 and A1, I out = -1.0 mASDO, I out = -5.0 mA V OH (VA+) - 1.0(VD+) - 1.0--V Low-level Output Voltage A0 and A1, I out = 1.0 mASDO, I out = 5.0 mAV OL --(VA-) + 0.40.4V Input Leakage Current I in -±1±10µA SDO Tri-State Leakage Current I OZ --±10µA Digital Output Pin CapacitanceC out-9-pFDYNAMIC CHARACTERISTICS18.The ADCs use a Sinc 5 filter for the 3200 Sps and 3840 Sps output word rate (OWR) and a Sinc 5 filterfollowed by a Sinc 3 filter for the other OWRs. OWR sinc5 refers to the 3200 Sps (FRS = 1) or 3840 Sps (FRS = 0) word rate associated with the Sinc 5 filter.19.The single conversion mode only outputs fully settled conversions. See Table 1 for more details aboutsingle conversion mode timing. OWR SC is used here to designate the different conversion time associated with single conversions.20.The continuous conversion mode outputs every conversion. This means that the filter’s settling timewith a full scale step input in the continuous conversion mode is dictated by the OWR.ABSOLUTE MAXIMUM RATINGS(DGND = 0 V; See Note 21.)Notes:21.All voltages with respect to ground.22.VA+ and VA- must satisfy {(VA+) - (VA-)} ≤ +6.6 V.23.VD+ and VA- must satisfy {(VD+) - (VA-)} ≤ +7.5 V.24.Applies to all pins including continuous overvoltage conditions at the analog input (AIN) pins.25.Transient current of up to 100 mA will not cause SCR latch-up. Maximum input current for a power supply pin is ±50 mA.26.Total power dissipation, including all input currents and output currents.WARNING:Operation at or beyond these limits may result in permanent damage to the device.Normal operation is not guaranteed at these extremes.ParameterSymbol Ratio Unit Modulator Sampling Ratef s MCLK/16Sps Filter Settling Time to 1/2 LSB (Full Scale Step Input)Single Conversion mode (Notes 18, 19, and 20)Continuous Conversion mode, OWR < 3200 Sps Continuous Conversion mode, OWR ≥ 3200 Spst s t s t s1/OWR SC5/OWR sinc5 + 3/OWR5/OWRs s sParameterSymbol Min Typ Max Unit DC Power Supplies(Notes 22 and 23)Positive Digital Positive Analog Negative Analog VD+VA+VA--0.3-0.3+0.3---+6.0+6.0-3.75V V V Input Current, Any Pin Except Supplies (Notes 24 and 25)I IN --±10mA Output Current I OUT--±25mA Power Dissipation (Note 26)PDN --500mW Analog Input Voltage VREF pins AIN PinsV INR V INA (VA-) -0.3(VA-) -0.3--(VA+) + 0.3(VA+) + 0.3V V Digital Input VoltageV IND -0.3-(VD+) + 0.3V Ambient Operating Temperature T A -40-85°C Storage Temperature T stg-65-150°CSWITCHING CHARACTERISTICS(VA+ = 2.5 V or 5 V ±5%; VA- = -2.5V±5% or 0 V; VD+ = 3.0 V ±10% or 5 V ±5%;DGND = 0 V; Levels: Logic 0 = 0 V, Logic 1 = VD+; C L = 50 pF; See Figures 1 and 2.)Notes:27.Device parameters are specified with a 4.9152 MHz clock.28.Specified using 10% and 90% points on waveform of interest. Output loaded with 50pF.29.Oscillator start-up time varies with crystal parameters. This specification does not apply when using anexternal clock source.ParameterSymbol Min Typ MaxUnitMaster Clock Frequency (Note 27)External Clock or Crystal OscillatorMCLK1 4.91525MHz Master Clock Duty Cycle 40-60%Rise Times(Note 28)Any Digital Input Except SCLKSCLKAny Digital Output t rise-----50 1.0100-µs µs ns Fall Times(Note 28)Any Digital Input Except SCLKSCLKAny Digital Output t fall-----50 1.0100-µs µs ns Start-upOscillator Start-up Time XTAL = 4.9152 MHz(Note 29)t ost-20-ms Serial Port Timing Serial Clock Frequency SCLK 0-2MHz Serial Clock Pulse Width High Pulse Width Lowt 1t 2250250----ns nsSDI Write TimingCS Enable to Valid Latch Clock t 350--ns Data Set-up Time prior to SCLK rising t 450--ns Data Hold Time After SCLK Rising t 5100--ns SCLK Falling Prior to CS Disable t 6100--nsSDO Read Timing CS to Data Validt 7--150ns SCLK Falling to New Data Bit t 8--150ns CS Rising to SDO Hi-Zt 9--150ns分销商库存信息:CIRRUS-LOGICCS5532-BSZR CS5534-BSZR CDB5532U。

SSTUP32866ECG,518;中文规格书,Datasheet资料

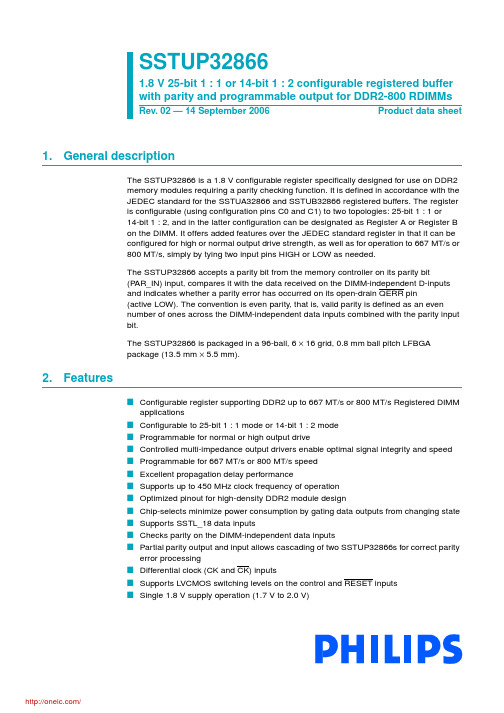

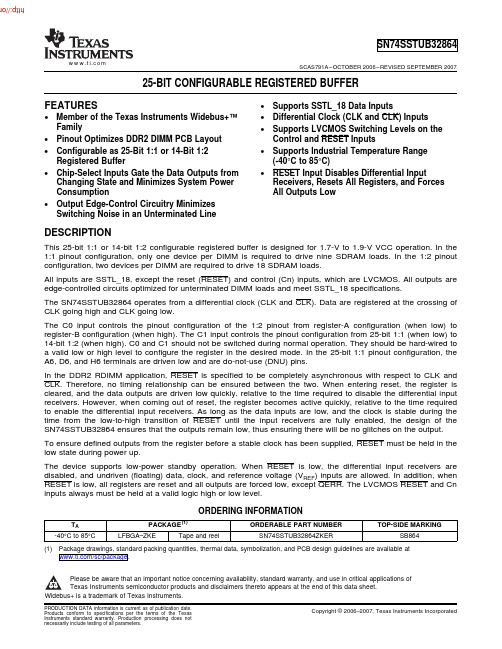

SSTUP328661.8 V 25-bit 1 : 1 or 14-bit 1 : 2 configurable registered bufferwith parity and programmable output for DDR2-800 RDIMMsRev. 02 — 14 September 2006Product data sheet1.General descriptionThe SSTUP32866 is a 1.8V configurable register specifically designed for use on DDR2memory modules requiring a parity checking function.It is defined in accordance with theJEDEC standard for the SSTUA32866 and SSTUB32866 registered buffers. The registeris configurable (using configuration pins C0 and C1) to two topologies: 25-bit 1:1 or14-bit 1:2, and in the latter configuration can be designated as Register A or Register Bon the DIMM. It offers added features over the JEDEC standard register in that it can beconfigured for high or normal output drive strength,as well as for operation to667MT/s or800MT/s, simply by tying two input pins HIGH or LOW as needed.The SSTUP32866 accepts a parity bit from the memory controller on its parity bit(PAR_IN) input, compares it with the data received on the DIMM-independent D-inputsand indicates whether a parity error has occurred on its open-drain QERR pin(active LOW). The convention is even parity, that is, valid parity is defined as an evennumber of ones across the DIMM-independent data inputs combined with the parity inputbit.The SSTUP32866 is packaged in a 96-ball, 6×16 grid, 0.8mm ball pitch LFBGApackage (13.5mm×5.5mm).2.FeaturesI Configurable register supporting DDR2up to667MT/s or800MT/s Registered DIMMapplicationsI Configurable to 25-bit 1:1 mode or 14-bit 1:2 modeI Programmable for normal or high output driveI Controlled multi-impedance output drivers enable optimal signal integrity and speedI Programmable for 667MT/s or 800MT/s speedI Excellent propagation delay performanceI Supports up to 450MHz clock frequency of operationI Optimized pinout for high-density DDR2 module designI Chip-selects minimize power consumption by gating data outputs from changing stateI Supports SSTL_18 data inputsI Checks parity on the DIMM-independent data inputsI Partial parity output and input allows cascading of two SSTUP32866s for correct parityerror processingI Differential clock (CK and CK) inputsI Supports LVCMOS switching levels on the control and RESET inputsI Single 1.8V supply operation (1.7V to 2.0V)I Available in 96-ball, 13.5mm ×5.5mm, 0.8mm ball pitch LFBGA package3.ApplicationsI 667MT/s to 800MT/s DDR2 registered DIMMs desiring parity checking functionality4.Ordering information4.1Ordering optionsTable 1.Ordering informationType numberSolder processPackage NameDescriptionVersionSSTUP32866EC/G Pb-free (SnAgCu solder ball compound)LFBGA96plastic low profile fine-pitch ball grid array package;96 balls; body 13.5×5.5× 1.05mm SOT536-1SSTUP32866EC/SPb-free (SnAgCu solder ball compound)LFBGA96plastic low profile fine-pitch ball grid array package;96 balls; body 13.5×5.5×1.05mmSOT536-1Table 2.Ordering optionsType number Temperature range SSTUP32866EC/G T amb = 0°C to +70°C SSTUP32866EC/ST amb = 0°C to +85°C5.Functional diagram(1)Disabled in 1:1 configuration.Fig 1.Functional diagram of SSTUP32866;1:2Register A configuration with C0=0andC1=1 (positive logic)002aab8691D R1D R 1D RQCKEA QCKEB (1)QODTA QODTB (1)QCSA QCSB (1)C1C1C1CSRDCSDODTDCKED2011D RQ2A Q2B (1)C1to 10 other channels (D3, D5, D6, D8 to D14)CK VREF CK RESETSSTUP32866Fig 2.Parity logic diagram for 1:2 Register A configuration (positive logic); C0=0, C1=1002aaa650D R Q2A, Q3A,Q5A, Q6A,Q8A to Q14A Q2B, Q3B,Q5B, Q6B,Q8B to Q14BCLK P AR_IND2, D3, D5, D6,D8 to D14CK CKRESETLPS0(internal node)CE VREFPARITY CHECKC11D RCLK D R CLK CED RCLK 10C0RCLK D RCLK LPS1(internal node)12-BIT COUNTER QERRPPOD2, D3, D5, D6,D8 to D14D2, D3, D5, D6,D8 to D1411111111116.Pinning information6.1PinningFig 3.Pin configuration for LFBGA96Fig 4.Ball mapping, 1:1 register (C0=0, C1=0)002aab870SSTUP32866EC/G SSTUP32866EC/STransparent top viewTR P N M L J G K H F E D C B A 246135ball A1index areaDCKE PPO VREF V DD QCKE DNU 123456D2D15GND GND Q2Q15A B D3D16V DD V DD Q3Q16C DODT GND GND QODT DNU D D5D17V DD V DD Q5Q17E D6D18GND GND Q6Q18F PAR_IN RESET V DD V DD C1C0G CK DCS GND GND QCS DNU H CK CSR V DD V DD SELAB SELDR J D8D19GND GND Q8Q19K D9D20V DD V DD Q9Q20L D10D21GND GND Q10Q21M D11D22V DD V DD Q11Q22N D12D23GND GND Q12Q23P D13D24V DD V DD Q13Q24R D14D25VREFV DDQ14Q25T002aab871QERRFig 5.Ball mapping, 1:2 Register A (C0=0, C1=1)Fig 6.Ball mapping, 1:2 Register B (C0=1, C1=1)DCKE PPO VREF V DD QCKEA QCKEB 123456D2DNU GND GND Q2A Q2B A B D3DNU V DD V DD Q3A Q3B C DODT QERR GND GND QODTA QODTB D D5n.c.V DD V DD Q5A Q5B E D6n.c.GND GND Q6A Q6B F PAR_IN RESET V DD V DD C1C0G CK DCS GND GND QCSA H CK CSR V DD V DD SELAB SELDR J D8DNU GND GND Q8A Q8B K D9DNU V DD V DD Q9A Q9B L D10DNU GND GND Q10A Q10B M D11DNU V DD V DD Q11A Q11B N D12DNU GND GND Q12A Q12B P D13DNU V DD V DD Q13A Q13B R D14DNUVREFV DDQ14AQ14BT002aab872QCSB D1PPO VREF V DD Q1A Q1B 123456D2DNU GND GND Q2A Q2B A B D3DNU V DD V DD Q3A Q3B C D4GND GND Q4A Q4B D D5DNU V DD V DD Q5A Q5B E D6DNU GND GND Q6A Q6B F PAR_IN RESET V DD V DD C1C0G CK DCS GND GND QCSA H CK CSR V DD V DD SELAB SELDR J D8DNU GND GND Q8A Q8B K D9DNU V DD V DD Q9A Q9B L D10DNU GND GND Q10A Q10B M DODT DNU V DD V DD QODTA QODTB N D12DNU GND GND Q12A Q12B P D13DNU V DD V DD Q13A Q13B R DCKEDNUVREFV DDQCKEAQCKEBT002aab873QCSB QERR6.2Pin descriptionTable 3.Pin descriptionSymbol Pin Type DescriptionGND B3, B4, D3, D4,F3, F4, H3, H4,K3, K4, M3, M4,P3, P4ground input groundV DD A4, C3, C4, E3,E4, G3, G4, J3,J4, L3, L4, N3,N4, R3, R4, T41.8V nominal power supply voltageVREF A3, T30.9V nominal input reference voltageCK H1differential input positive master clock inputCK J1differential input negative master clock inputC0G6LVCMOS inputs Configuration control inputs; Register Aor Register B and 1:1mode or1:2mode select.C1G5SELDR J6LVCMOS input Selects output drive strength: HIGH fornormal drive,LOW for high drive.This pinwill default HIGH if left open-circuit(built-in weak pull-up resistor).SELAB J5LVCMOS input Selects speed grade: HIGH forDDR2-667,LOW for DDR2-800.This pinwill default HIGH if left open-circuit(built-in weak pull-up resistor).RESET G2LVCMOS input Asynchronous reset input (active LOW).Resets registers and disables VREF dataand clock.CSR J2SSTL_18 input Chip select inputs(active LOW).DisablesD1to D25[1]outputs switching when bothinputs are HIGH.DCS H2D1to D25[2]SSTL_18 input Data input. Clocked in on the crossing ofthe rising edge of CK and the falling edgeof CK.DODT[2]SSTL_18 input The outputs of this register bit will not besuspended by the DCS and CSR control.DCKE[2]SSTL_18 input The outputs of this register bit will not besuspended by the DCS and CSR control.P AR_IN G1SSTL_18 input Parity input.Arrives one clock cycle afterthe corresponding data input.Q1to Q25,Q2A to Q14A, Q1B to Q14B [2] 1.8V CMOSoutputsData outputs that are suspended by theDCS and CSR control[3].PPO A2 1.8V CMOSoutput Partial parity out. Indicates odd parity of inputs D1to D25[1].QCS,QCSA, QCSB [2] 1.8V CMOSoutputData output that will not be suspended bythe DCS and CSR control.QODT, QODT A, QODTB [2] 1.8V CMOSoutputData output that will not be suspended bythe DCS and CSR control.[1]Data inputs =D2, D3, D5, D6, D8to D25 when C0=0 and C1=0.Data inputs =D2, D3, D5, D6, D8to D14 when C0=0 and C1=1.Data inputs =D1to D6, D8to D10, D12, D13 when C0=1 and C1=1.[2]Depends on configuration. See Figure 4,Figure 5, and Figure 6 for ball number.[3]Data outputs =Q2, Q3, Q5, Q6, Q8to Q25 when C0=0 and C1=0.Data outputs =Q2, Q3, Q5, Q6, Q8to Q14 when C0=0 and C1=1.Data outputs =Q1to Q6, Q8to Q10, Q12, Q13 when C0=1 and C1=1.7.Functional descriptionThe SSTUP32866is a 25-bit 1:1or 14-bit 1:2configurable registered buffer with parity,designed for 1.7V to 2.0V V DD operation. Additionally, the SSTUP32866 can be programmed to deliver either normal or high output drive, and either 600MT/s or 800MT/s speeds.Two programming pins, SELAB and SELDR, allow the user to respectively select speed and drive strength options by tying these pins either LOW or HIGH on the DIMM.The truth table for these options is shown in Table 6.All clock and data inputs are compatible with the JEDEC standard for SSTL_18. The control and reset (RESET) inputs are LVCMOS. All data outputs are 1.8V CMOS drivers that have been optimized to drive the DDR2 DIMM load, and meet SSTL_18specifications. The error (QERR) output is 1.8V open-drain driver.The SSTUP32866 operates from a differential clock (CK and CK). Data are registered at the crossing of CK going HIGH, and CK going LOW.The C0 input controls the pinout configuration for the 1:2 pinout from A configuration (when LOW) to B configuration (when HIGH). The C1 input controls the pinout configuration from 25-bit 1:1 (when LOW) to 14-bit 1:2 (when HIGH).The SSTUP32866 accepts a parity bit from the memory controller on its parity bit(PAR_IN) input, compares it with the data received on the DIMM-independent D-inputs and indicates whether a parity error has occurred on its open-drain QERR pin(active LOW). The convention is even parity, that is, valid parity is defined as an even number of ones across the DIMM-independent data inputs combined with the parity input bit.When used as a single device, the C0 and C1 inputs are tied LOW. In this configuration,parity is checked on the P AR_IN input which arrives one cycle after the input data to which it applies.The Partial-Parity-Out (PPO)and QERR signals are produced three cycles after the corresponding data inputs.QCKE, QCKEA,QCKEB [2]1.8V CMOS output Data output that will not be suspended by the DCS and CSR control.QERRD2open-drain output Output error bit (active LOW).Generated one clock cycle after the corresponding data outputDNU[2]-Do not use. Inputs are instandby-equivalent mode and outputs are driven LOW.Table 3.Pin description …continuedSymbolPinType DescriptionWhen used in pairs, the C0 input of the first register is tied LOW and the C0 input of the second register is tied HIGH. The C1 input of both registers are tied HIGH. Parity, which arrives one cycle after the data input to which it applies,is checked on the P AR_IN input of the first device. The PPO and QERR signals are produced on the second device three clock cycles after the corresponding data inputs. The PPO output of the first register is cascaded to the P AR_IN of the second register. The QERR output of the first register is left floating and the valid error information is latched on the QERR output of the second register.If an error occurs and the QERR output is driven LOW,it stays latched LOW for two clock cycles or until RESET is driven LOW.The DIMM-dependent signals(DCKE,DCS,DODT, and CSR) are not included in the parity check computation.The device supports low-power standby operation. When RESET is LOW, the differential input receivers are disabled, and undriven (floating) data, clock and reference voltage (VREF) inputs are allowed. In addition, when RESET is LOW all registers are reset, and all outputs are forced LOW. The LVCMOS RESET input must always be held at a valid logic HIGH or LOW level.The device also supports low-power active operation by monitoring both system chip select(DCS and CSR)inputs and will gate the Qn and PPO outputs from changing states when both DCS and CSR inputs are HIGH. If either DCS or CSR input is LOW, the Qn and PPO outputs will function normally. The RESET input has priority over the DCS and CSR control and when driven LOW will force the Qn and PPO outputs LOW, and the QERR output HIGH.If the DCS control functionality is not desired,then the CSR input can be hard-wired to ground,in which case,the setup time requirement for DCS would be the same as for the other Dn data inputs. T o control the low-power mode with DCS only, then the CSR input should be pulled up to V DD through a pull-up resistor.To ensure defined outputs from the register before a stable clock has been supplied, RESET must be held in the LOW state during power-up.In the DDR2RDIMM application,RESET is specified to be completely asynchronous with respect to CK and CK. Therefore, no timing relationship can be guaranteed between the two. When entering reset, the register will be cleared and the Qn outputs will be driven LOW quickly,relative to the time to disable the differential input receivers.However,when coming out of reset, the register will become active quickly, relative to the time to enable the differential input receivers.As long as the data inputs are LOW,and the clock is stable during the time from the LOW-to-HIGH transition of RESET until the input receivers are fully enabled, the design of the SSTUP32866 must ensure that the outputs will remain LOW, thus ensuring no glitches on the output.7.1Function table[1]Q 0 is the previous state of the associated output.[1]PPO 0 is the previous state of output PPO;QERR 0 is the previous state of output QERR.[2]Data inputs =D2, D3, D5, D6, D8to D25 when C0=0 and C1=0.Data inputs =D2, D3, D5, D6, D8to D14 when C0=0 and C1=1.Data inputs =D1to D6, D8to D10, D12, D13 when C0=1 and C1=1.[3]P AR_IN arrives one clock cycle (C0=0), or two clock cycles (C0=1), after the data to which it applies.[4]This condition assumes QERR is HIGH at the crossing of CK going HIGH and CK going LOW.If QERR is LOW,it stays latched LOW for two clock cycles or until RESET is driven LOW.Table 4.Function table (each flip-flop)L =LOW voltage level; H = HIGH voltage level; X =don’t care;↑=LOW-to-HIGH transition;↓=HIGH-to-LOW transition.InputsOutputs [1]RESET DCS CSR CK CK Dn,DODTn,DCKEnQn QCS QODT,QCKE H L L ↑↓L L L L H L L ↑↓H H L H H L L L or H L or H X Q 0Q 0Q 0H L H ↑↓L L L L H L H ↑↓H H L H H L H L or H L or H X Q 0Q 0Q 0H H L ↑↓L L H L H H L ↑↓H H H H H H L L or H L or H X Q 0Q 0Q 0H H H ↑↓L Q 0H L H H H ↑↓H Q 0H H H H H L or H L or H X Q 0Q 0Q 0LX or floatingX or floatingX or floatingX or floatingX or floatingLLLTable 5.Parity and standby function tableL =LOW voltage level; H = HIGH voltage level; X =don’t care;↑=LOW-to-HIGH transition;↓=HIGH-to-LOW transition.InputsOutputs [1]RESET DCS CSR CK CK ∑of inputs =H (D1to D25)PAR_IN [2]PPO [3]QERR [4]H L X ↑↓even L L H H L X ↑↓odd L H L H L X ↑↓even H H L H L X ↑↓odd H L H H H L ↑↓even L L H H H L ↑↓odd L H L H H L ↑↓even H H L H H L ↑↓odd H L H H H H ↑↓X X PPO 0QERR 0H XXL or HL or HX X PPO 0QERR 0LX or floating X or floating X or floating X or floatingX or floatingX or floatingLH分销商库存信息: NXPSSTUP32866EC/G,518。

74270036;中文规格书,Datasheet资料