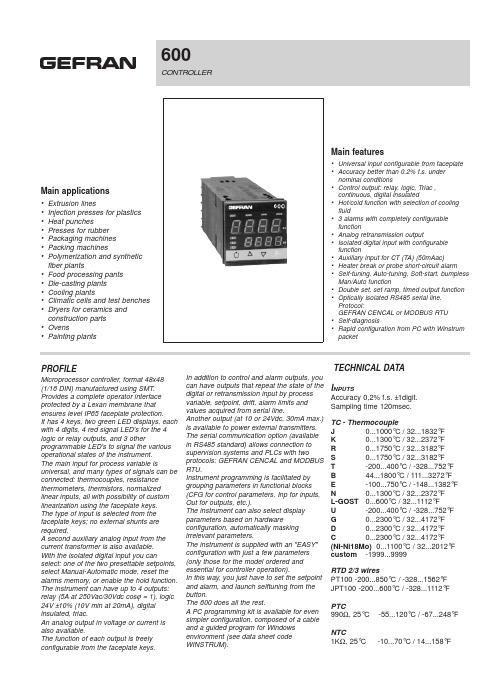

660_thumb

第三章第二节thumb2指令集及汇编格式资料

用户文件与库文件通过stm32f10x_lib.h建立关系,该文件中 定义了所有外设头文件的头文件,用于声明头文件,因此需 要include在用户的文件中

而文件stm32f10x_conf.h则指定具体的参数,用户可以对此 文件进行修改

外设的操作步骤

PPP代表任意外设 1. 在主应用文件中,声明一个结构

程序入口,而是作为主堆栈的标志 可以在设置中修改,但一般不做修改 9 .code16和code32 作为16位指令和32位指令开始的标志 等同于THUMB和ARM

10 END

END指示符告诉编译器已经到了源程序结尾。

语法格式:

END 使用说明:

每一个汇编源程序都包含END指示符,以告诉本源程 序的结束。

}

IAR的固件库

由ST公司开发,包括驱动程序和应用函数的 函数库

版本:3.4 优点:

入手快 便于开发,节约时间

缺点:

结构复杂繁琐 原理不够清晰

PPP:某一外设名称

说明

每一个外设都有一个对应的源文件: stm32f10x_ppp.c和一个对应的头文件: stm32f10x_ppp.h

硬件资源分配:

PC6----PC9分别连到4个LED,定义为 LED1~4

跑马灯实验

控制过程

点亮LED

相应管脚输出高电平 即相应管脚置1

管脚如何控制?

特殊寄e:GPIO控制

GPIO寄存器结构

GPIO寄存器结构,GPIO_TypeDef和AFIO_TypeDef,在文件

Example:GPIO控制

一、什么是GPIO?

GPIO,英文全称为General-Purpose IO ports,也就是通 用IO口。嵌入式系统中常常有数量众多,但是结构却比较 简单的外部设备/电路,对这些设备/电路有的需要CPU为 之提供控制手段,有的则需要被CPU用作输入信号。而且, 许多这样的设备/电路只要求一位,即只要有开/关两种状 态就够了,比如灯亮与灭。对这些设备/电路的控制,使 用传统的串行口或并行口都不合适。所以在微控制器芯片 上一般都会提供一个“通用可编程IO接口”,即GPIO。

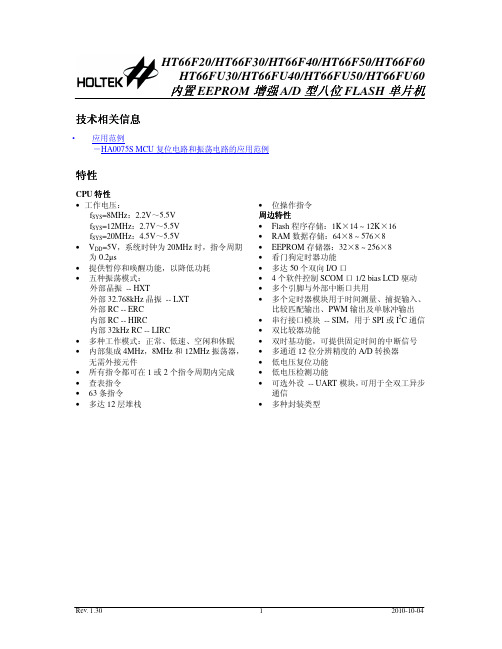

66164;66166;66167;66168;66169;中文规格书,Datasheet资料

COMMON POINT GROUND

Per ANSI/ESD S6.1, Grounding section 4.1.1 “Every element to be grounded at an ESD protected station shall be connected to the same common point ground.” ESD Handbook ESD TR20.20 section 5.1.3 Basic Grounding Requirements “The first step in ensuring that everything in an EPA is at the same electrical potential is to ground all conductive components of the work area (worksurfaces, people, equipment, etc.) to the same electrical ground point. This point is called the common point ground. The next step in completing the ground circuit is to connect the common point ground to the equipment ground (third wire, green).”

General Grounding Guidelines

1. ANSI/ESD S20.20 requires that all conductors in an ESD protected area, including personnel, must be grounded. 2. The ESD ground must be tied directly to and at the same potential as the building or “green wire” equipment ground. 3. Per ANSI/ESD S20.20, the ESD control program can in no way replace or supercede any requirements for personnel safety. Ground fault circuit interrupters (GFCI) and other safety protection should be considered wherever personnel might come into contact with electrical sources. 4. All electrical outlets should be verified for proper wiring configuration, resistance or impedance and GFCI function when the mat is installed and periodically thereafter.

x86 Assembly Language Reference Manual

x86Assembly Language ReferenceManual Sun Microsystems,Inc.4150Network CircleSanta Clara,CA95054U.S.A.Part No:817–5477–10January2005Copyright2005Sun Microsystems,Inc.4150Network Circle,Santa Clara,CA95054U.S.A.All rights reserved.This product or document is protected by copyright and distributed under licenses restricting its use,copying,distribution,and decompilation.No part of this product or document may be reproduced in any form by any means without prior written authorization of Sun and its licensors,if any. Third-party software,including font technology,is copyrighted and licensed from Sun suppliers.Parts of the product may be derived from Berkeley BSD systems,licensed from the University of California.UNIX is a registered trademark in the U.S. and other countries,exclusively licensed through X/Open Company,Ltd.Sun,Sun Microsystems,the Sun logo,,AnswerBook,AnswerBook2,and Solaris are trademarks or registered trademarks of Sun Microsystems,Inc.in the U.S.and other countries.The OPEN LOOK and Sun™Graphical User Interface was developed by Sun Microsystems,Inc.for its users and licensees.Sun acknowledges the pioneering efforts of Xerox in researching and developing the concept of visual or graphical user interfaces for the computer industry.Sun holds a non-exclusive license from Xerox to the Xerox Graphical User Interface,which license also covers Sun’s licensees who implement OPEN LOOK GUIs and otherwise comply with Sun’s written license agreements.ernment Rights–Commercial ernment users are subject to the Sun Microsystems,Inc.standard license agreement and applicable provisions of the FAR and its supplements.DOCUMENTATION IS PROVIDED“AS IS”AND ALL EXPRESS OR IMPLIED CONDITIONS,REPRESENTATIONS AND WARRANTIES, INCLUDING ANY IMPLIED WARRANTY OF MERCHANTABILITY,FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT,ARE DISCLAIMED,EXCEPT TO THE EXTENT THAT SUCH DISCLAIMERS ARE HELD TO BE LEGALLY INVALID.Copyright2005Sun Microsystems,Inc.4150Network Circle,Santa Clara,CA95054U.S.A.Tous droits réservés.Ce produit ou document est protégépar un copyright et distribuéavec des licences qui en restreignent l’utilisation,la copie,la distribution,et ladécompilation.Aucune partie de ce produit ou document ne peutêtre reproduite sous aucune forme,par quelque moyen que ce soit,sansl’autorisation préalable etécrite de Sun et de ses bailleurs de licence,s’il y en a.Le logiciel détenu par des tiers,et qui comprend la technologie relative aux polices de caractères,est protégépar un copyright et licenciépar des fournisseurs de Sun.Des parties de ce produit pourrontêtre dérivées du système Berkeley BSD licenciés par l’Universitéde Californie.UNIX est une marque déposée aux Etats-Unis et dans d’autres pays et licenciée exclusivement par X/Open Company,Ltd.Sun,Sun Microsystems,le logo Sun,,AnswerBook,AnswerBook2,et Solaris sont des marques de fabrique ou des marques déposées,de Sun Microsystems,Inc.aux Etats-Unis et dans d’autres pays.L’interface d’utilisation graphique OPEN LOOK et Sun™aétédéveloppée par Sun Microsystems,Inc.pour ses utilisateurs et licenciés.Sun reconnaît les efforts de pionniers de Xerox pour la recherche et le développement du concept des interfaces d’utilisation visuelle ou graphique pour l’industrie de l’informatique.Sun détient une licence non exclusive de Xerox sur l’interface d’utilisation graphique Xerox,cette licence couvrantégalement les licenciés de Sun qui mettent en place l’interface d’utilisation graphique OPEN LOOK et qui en outre se conforment aux licencesécrites de Sun. CETTE PUBLICATION EST FOURNIE“EN L’ETAT”ET AUCUNE GARANTIE,EXPRESSE OU IMPLICITE,N’EST ACCORDEE,Y COMPRIS DES GARANTIES CONCERNANT LA VALEUR MARCHANDE,L’APTITUDE DE LA PUBLICATION A REPONDRE A UNE UTILISATION PARTICULIERE,OU LE FAIT QU’ELLE NE SOIT PAS CONTREFAISANTE DE PRODUIT DE TIERS.CE DENI DE GARANTIE NES’APPLIQUERAIT PAS,DANS LA MESURE OU IL SERAIT TENU JURIDIQUEMENT NUL ET NON AVENU.040910@9495ContentsPreface71Overview of the Solaris x86Assembler11Assembler Overview11Syntax Differences Between x86Assemblers12Assembler Command Line122Solaris x86Assembly Language Syntax13Lexical Conventions13Statements13Tokens15Instructions,Operands,and Addressing17Instructions17Operands18Assembler Directives203Instruction Set Mapping25Instruction Overview25General-Purpose Instructions26Data Transfer Instructions26Binary Arithmetic Instructions30Decimal Arithmetic Instructions31Logical Instructions32Shift and Rotate Instructions32Bit and Byte Instructions333Control Transfer Instructions35String Instructions38I/O Instructions39Flag Control(EFLAG)Instructions40Segment Register Instructions41Miscellaneous Instructions41Floating-Point Instructions42Data Transfer Instructions(Floating Point)42Basic Arithmetic Instructions(Floating-Point)43Comparison Instructions(Floating-Point)45Transcendental Instructions(Floating-Point)46Load Constants(Floating-Point)Instructions47Control Instructions(Floating-Point)47SIMD State Management Instructions49MMX Instructions49Data Transfer Instructions(MMX)50Conversion Instructions(MMX)50Packed Arithmetic Instructions(MMX)51Comparison Instructions(MMX)52Logical Instructions(MMX)53Shift and Rotate Instructions(MMX)53State Management Instructions(MMX)54SSE Instructions54SIMD Single-Precision Floating-Point Instructions(SSE)55MXCSR State Management Instructions(SSE)6164–Bit SIMD Integer Instructions(SSE)61Miscellaneous Instructions(SSE)62SSE2Instructions63SSE2Packed and Scalar Double-Precision Floating-Point Instructions63SSE2Packed Single-Precision Floating-Point Instructions70SSE2128–Bit SIMD Integer Instructions70SSE2Miscellaneous Instructions72Operating System Support Instructions7364–Bit AMD Opteron Considerations75Index774x86Assembly Language Reference Manual•January2005TablesTABLE3–1Data Transfer Instructions26TABLE3–2Binary Arithmetic Instructions30TABLE3–3Decimal Arithmetic Instructions32TABLE3–4Logical Instructions32TABLE3–5Shift and Rotate Instructions33TABLE3–6Bit and Byte Instructions34TABLE3–7Control Transfer Instructions36TABLE3–8String Instructions38TABLE3–9I/O Instructions40TABLE3–10Flag Control Instructions40TABLE3–11Segment Register Instructions41TABLE3–12Miscellaneous Instructions42TABLE3–13Data Transfer Instructions(Floating-Point)42TABLE3–14Basic Arithmetic Instructions(Floating-Point)44TABLE3–15Comparison Instructions(Floating-Point)45TABLE3–16Transcendental Instructions(Floating-Point)46TABLE3–17Load Constants Instructions(Floating-Point)47TABLE3–18Control Instructions(Floating-Point)47TABLE3–19SIMD State Management Instructions49TABLE3–20Data Transfer Instructions(MMX)50TABLE3–21Conversion Instructions(MMX)50TABLE3–22Packed Arithmetic Instructions(MMX)51TABLE3–23Comparison Instructions(MMX)52TABLE3–24Logical Instructions(MMX)53TABLE3–25Shift and Rotate Instructions(MMX)53TABLE3–26State Management Instructions(MMX)54TABLE3–27Data Transfer Instructions(SSE)555TABLE3–28Packed Arithmetic Instructions(SSE)56TABLE3–29Comparison Instructions(SSE)58TABLE3–30Logical Instructions(SSE)59TABLE3–31Shuffle and Unpack Instructions(SSE)59TABLE3–32Conversion Instructions(SSE)60TABLE3–33MXCSR State Management Instructions(SSE)61TABLE3–3464–Bit SIMD Integer Instructions(SSE)61TABLE3–35Miscellaneous Instructions(SSE)62TABLE3–36SSE2Data Movement Instructions64TABLE3–37SSE2Packed Arithmetic Instructions65TABLE3–38SSE2Logical Instructions66TABLE3–39SSE2Compare Instructions67TABLE3–40SSE2Shuffle and Unpack Instructions67TABLE3–41SSE2Conversion Instructions68TABLE3–42SSE2Packed Single-Precision Floating-Point Instructions70TABLE3–43SSE2128–Bit SIMD Integer Instructions71TABLE3–44SSE2Miscellaneous Instructions72TABLE3–45Operating System Support Instructions736x86Assembly Language Reference Manual•January2005PrefaceThe x86Assembly Language Reference Manual documents the syntax of the Solaris™x86 assembly language.This manual is provided to help experienced programmers understand the assembly language output of Solaris compilers.This manual is neither an introductory book about assembly language programming nor a reference manual for the x86architecture.Note–In this document the term“x86”refers to64-bit and32-bit systems manufactured using processors compatible with the AMD64or Intel Xeon/Pentium product families.For supported systems,see the Solaris10Hardware Compatibility List.Who Should Use This BookThis manual is intended for experienced x86assembly language programmers who are familiar with the x86architecture.Before You Read This BookYou should have a thorough knowledge of assembly language programming in general and be familiar with the x86architecture in specific.You should be familiar with the ELF objectfile format.This manual assumes that you have the following documentation available for reference:I IA-32Intel Architecture Software Developer’s Manual(Intel Corporation,2004).Volume1:Basic Architecture.Volume2:Instruction Set Reference A-M.Volume3: Instruction Set Reference N-Z.Volume4:System Programming Guide.7I AMD64Architecture Programmer’s Manual(Advanced Micro Devices,2003).Volume1:Application Programming.Volume2:System Programming.Volume3:General-Purpose and System Instructions.Volume4:128-Bit Media Instructions.Volume5:64-Bit Media and x87Floating-Point Instructions.I Linker and Libraries GuideI Sun Studio9:C User’s GuideI Sun Studio9:Fortran User’s Guide and Fortran Programming GuideI Man pages for the as(1),ld(1),and dis(1)utilities.How This Book Is OrganizedChapter1provides an overview of the x86functionality supported by the Solaris x86assembler.Chapter2documents the syntax of the Solaris x86assembly language.Chapter3maps Solaris x86assembly language instruction mnemonics to the nativex86instruction set.Accessing Sun Documentation OnlineThe SM Web site enables you to access Sun technical documentationonline.You can browse the archive or search for a specific book title orsubject.The URL is .Ordering Sun DocumentationSun Microsystems offers select product documentation in print.For a list ofdocuments and how to order them,see“Buy printed documentation”at.8x86Assembly Language Reference Manual•January2005Typographic ConventionsThe following table describes the typographic changes that are used in this book. TABLE P–1Typographic ConventionsTypeface or Symbol Meaning ExampleAaBbCc123The names of commands,files,anddirectories,and onscreen computeroutput Edit your.loginfile.Use ls-a to list allfiles. machine_name%you have mail.AaBbCc123What you type,contrasted with onscreencomputer output machine_name%su Password:AaBbCc123Command-line placeholder:replace witha real name or value The command to remove afile is rmfilename.AaBbCc123Book titles,new terms,and terms to beemphasized Read Chapter6in the User’s Guide.Perform a patch analysis.Do not save thefile.[Note that some emphasized items appear bold online.]Shell Prompts in Command ExamplesThe following table shows the default system prompt and superuser prompt for theC shell,Bourne shell,and Korn shell.TABLE P–2Shell PromptsShell PromptC shell prompt machine_name%C shell superuser prompt machine_name#Bourne shell and Korn shell prompt$9TABLE P–2Shell Prompts(Continued)Shell PromptBourne shell and Korn shell superuser prompt#10x86Assembly Language Reference Manual•January2005CHAPTER1Overview of the Solaris x86AssemblerThis chapter provides a brief overview of the Solaris x86assembler as.This chapterdiscusses the following topics:I“Assembler Overview”on page11I“Syntax Differences Between x86Assemblers”on page12I“Assembler Command Line”on page12Assembler OverviewThe Solaris x86assembler as translates Solaris x86assembly language into Executableand Linking Format(ELF)relocatable objectfiles that can be linked with other objectfiles to create an executablefile or a shared objectfile.(See Chapter7,“Object FileFormat,”in Linker and Libraries Guide,for a complete discussion of ELF objectfileformat.)The assembler supports macro processing by the C preprocessor(cpp)or them4macro processor.The assembler supports the instruction sets of the followingCPUs:Intel8086/8088processorsIntel286processorIntel386processorIntel486processorIntel Pentium processorIntel Pentium Pro processorIntel Pentium II processorPentium II Xeon processorIntel Celeron processorIntel Pentium III processorPentium III Xeon processorAdvanced Micro Devices Athlon processor11Advanced Micro Devices Opteron processorSyntax Differences Between x86AssemblersThere is no standard assembly language for the x86architecture.Vendorimplementations of assemblers for the x86architecture instruction sets differ in syntaxand functionality.The syntax of the Solaris x86assembler is compatible with thesyntax of the assembler distributed with earlier releases of the UNIX operating system(this syntax is sometimes termed“AT&T syntax”).Developers familiar with otherassemblers derived from the original UNIX assemblers,such as the Free SoftwareFoundation’s gas,willfind the syntax of the Solaris x86assembler verystraightforward.However,the syntax of x86assemblers distributed by Intel and Microsoft(sometimestermed“Intel syntax”)differs significantly from the syntax of the Solaris x86assembler.These differences are most pronounced in the handling of instructionoperands:I The Solaris and Intel assemblers use the opposite order for source and destinationoperands.I The Solaris assembler specifies the size of memory operands by adding a suffix tothe instruction mnemonic,while the Intel assembler prefixes the memoryoperands.I The Solaris assembler prefixes immediate operands with a dollar sign($)(ASCII0x24),while the Intel assembler does not delimit immediate operands.See Chapter2for additional differences between x86assemblers.Assembler Command LineDuring the translation of higher-level languages such as C and Fortran,the compilersmight invoke as using the alias fbe(“Fortran back end”).You can invoke theassembler manually from the shell command line with either name,as or fbe.See theas(1)man page for the definitive discussion of command syntax and command lineoptions.12x86Assembly Language Reference Manual•January2005CHAPTER2Solaris x86Assembly Language SyntaxThis chapter documents the syntax of the Solaris x86assembly language.I“Lexical Conventions”on page13I“Instructions,Operands,and Addressing”on page17I“Assembler Directives”on page20Lexical ConventionsThis section discusses the lexical conventions of the Solaris x86assembly language.StatementsAn x86assembly language program consists of one or morefiles containing statements.A statement consists of tokens separated by whitespace and terminated by either anewline character(ASCII0x0A)or a semicolon(;)(ASCII0x3B).Whitespace consists ofspaces(ASCII0x20),tabs(ASCII0x09),and formfeeds(ASCII0x0B)that are notcontained in a string or comment.More than one statement can be placed on a singleinput line provided that each statement is terminated by a semicolon.A statement canconsist of a comment.Empty statements,consisting only of whitespace,are allowed.CommentsA comment can be appended to a statement.The comment consists of the slashcharacter(/)(ASCII0x2F)followed by the text of the comment.The comment isterminated by the newline that terminates the statement.13LabelsA label can be placed at the beginning of a statement.During assembly,the label isassigned the current value of the active location counter and serves as an instructionoperand.There are two types of lables:symbolic and numeric.Symbolic LabelsA symbolic label consists of an identifier(or symbol)followed by a colon(:)(ASCII0x3A).Symbolic labels must be defined only once.Symbolic labels have global scopeand appear in the objectfile’s symbol table.Symbolic labels with identifiers beginning with a period(.)(ASCII0x2E)areconsidered to have local scope and are not included in the objectfile’s symbol table.Numeric LabelsA numeric label consists of a single digit in the range zero(0)through nine(9)followedby a colon(:).Numeric labels are used only for local reference and are not included inthe objectfile’s symbol table.Numeric labels have limited scope and can be redefinedrepeatedly.When a numeric label is used as a reference(as an instruction operand,for example),the suffixes b(“backward”)or f(“forward”)should be added to the numeric label.Fornumeric label N,the reference N b refers to the nearest label N defined before thereference,and the reference N f refers to the nearest label N defined after the reference.The following example illustrates the use of numeric labels:1:/define numeric label"1"one:/define symbolic label"one"/...assembler code...jmp1f/jump to first numeric label"1"defined/after this instruction/(this reference is equivalent to label"two")jmp1b/jump to last numeric label"1"defined/before this instruction/(this reference is equivalent to label"one")1:/redefine label"1"two:/define symbolic label"two"jmp1b/jump to last numeric label"1"defined/before this instruction/(this reference is equivalent to label"two")14x86Assembly Language Reference Manual•January2005TokensThere arefive classes of tokens:I Identifiers(symbols)I KeywordsI Numerical constantsI String ConstantsI OperatorsIdentifiersAn identifier is an arbitrarily-long sequence of letters and digits.Thefirst character must be a letter;the underscore(_)(ASCII0x5F)and the period(.)(ASCII0x2E)are considered to be letters.Case is significant:uppercase and lowercase letters are different.KeywordsKeywords such as x86instruction mnemonics(“opcodes”)and assembler directives are reserved for the assembler and should not be used as identifiers.See Chapter3for a list of the Solaris x86mnemonics.See“Assembler Directives”on page20for the list of as assembler directives.Numerical ConstantsNumbers in the x86architecture can be integers orfloating point.Integers can be signed or unsigned,with signed integers represented in two’s complement representation. Floating-point numbers can be:single-precisionfloating-point;double-precisionfloating-point;and double-extended precisionfloating-point.Integer ConstantsIntegers can be expressed in several bases:I Decimal.Decimal integers begin with a non-zero digit followed by zero or moredecimal digits(0–9).I Binary.Binary integers begin with“0b”or“0B”followed by zero or more binarydigits(0,1).I Octal.Octal integers begin with zero(0)followed by zero or more octal digits(0–7).I Hexadecimal.Hexadecimal integers begin with“0x”or“0X”followed by one ormore hexadecimal digits(0–9,A–F).Hexadecimal digits can be either uppercase or lowercase.Chapter2•Solaris x86Assembly Language Syntax15Floating Point ConstantsFloating point constants have the following format:I Sign(optional)–either plus(+)or minus(–)I Integer(optional)–zero or more decimal digits(0–9)I Fraction(optional)–decimal point(.)followed by zero or more decimal digitsI Exponent(optional)–the letter“e”or“E”,followed by an optional sign(plus orminus),followed by one or more decimal digits(0–9)A validfloating point constant must have either an integer part or a fractional part.String ConstantsA string constant consists of a sequence of characters enclosed in double quotes(")(ASCII0x22).To include a double-quote character("),single-quote character(’),orbackslash character(\)within a string,precede the character with a backslash(\)(ASCII0x5C).A character can be expressed in a string as its ASCII value in octalpreceded by a backslash(for example,the letter“J”could be expressed as“\112”).Theassembler accepts the following escape sequences in strings:Escape Sequence Character Name ASCII Value(hex)\n newline0A\r carriage return0D\b backspace08\t horizontal tab09\f form feed0C\v vertical tab0BOperatorsThe assembler supports the following operators for use in expressions.Operators haveno assigned precedence.Expressions can be grouped in square brackets([])toestablish precedence.+Addition-Subtraction\*Multiplication\/Division&Bitwise logical AND16x86Assembly Language Reference Manual•January2005|Bitwise logical OR>>Shift right<<Shift left\%Remainder!Bitwise logical AND NOT^Bitwise logical XORNote–The asterisk(*),slash(/),and percent sign(%)characters are overloaded.When used as operators in an expression,these characters must be preceded by the backslash character(\).Instructions,Operands,and Addressing Instructions are operations performed by the CPU.Operands are entities operated upon by the instruction.Addresses are the locations in memory of specified data.InstructionsAn instruction is a statement that is executed at runtime.An x86instruction statement can consist of four parts:I Label(optional)I Instruction(required)I Operands(instruction specific)I Comment(optional)See“Statements”on page13for the description of labels and comments.The terms instruction and mnemonic are used interchangeably in this document to refer to the names of x86instructions.Although the term opcode is sometimes used as a synonym for instruction,this document reserves the term opcode for the hexadecimal representation of the instruction value.Chapter2•Solaris x86Assembly Language Syntax17For most instructions,the Solaris x86assembler mnemonics are the same as the Intelor AMD mnemonics.However,the Solaris x86mnemonics might appear to bedifferent because the Solaris mnemonics are suffixed with a one-character modifier thatspecifies the size of the instruction operands.That is,the Solaris assembler derives itsoperand type information from the instruction name and the suffix.If a mnemonic isspecified with no type suffix,the operand type defaults to long.Possible operandtypes and their instruction suffixes are:b Byte(8–bit)w Word(16–bit)l Long(32–bit)(default)q Quadword(64–bit)The assembler recognizes the following suffixes for x87floating-point instructions:[no suffix]Instruction operands are registers onlyl(“long”)Instruction operands are64–bits(“short”)Instruction operands are32–bitSee Chapter3for a mapping between Solaris x86assembly language mnemonics andthe equivalent Intel or AMD mnemonics.OperandsAn x86instruction can have zero to three operands.Operands are separated bycommas(,)(ASCII0x2C).For instructions with two operands,thefirst(lefthand)operand is the source operand,and the second(righthand)operand is the destinationoperand(that is,source→destination).Note–The Intel assembler uses the opposite order(destination←source)for operands.Operands can be immediate(that is,constant expressions that evaluate to an inlinevalue),register(a value in the processor number registers),or memory(a value stored inmemory).An indirect operand contains the address of the actual operand value.Indirect operands are specified by prefixing the operand with an asterisk(*)(ASCII0x2A).Only jump and call instructions can use indirect operands.I Immediate operands are prefixed with a dollar sign($)(ASCII0x24)I Register names are prefixed with a percent sign(%)(ASCII0x25)18x86Assembly Language Reference Manual•January2005I Memory operands are specified either by the name of a variable or by a register thatcontains the address of a variable.A variable name implies the address of avariable and instructs the computer to reference the contents of memory at that address.Memory references have the following syntax:segment:offset(base,index,scale).I Segment is any of the x86architecture segment registers.Segment is optional:ifspecified,it must be separated from offset by a colon(:).If segment is omitted,the value of%ds(the default segment register)is assumed.I Offset is the displacement from segment of the desired memory value.Offset isoptional.I Base and index can be any of the general32–bit number registers.I Scale is a factor by which index is to be multipled before being added to base tospecify the address of the operand.Scale can have the value of1,2,4,or8.Ifscale is not specified,the default value is1.Some examples of memory addresses are:movl var,%eaxMove the contents of memory location var into number register%eax.movl%cs:var,%eaxMove the contents of memory location var in the code segment(register%cs)into number register%eax.movl$var,%eaxMove the address of var into number register%eax.movl array_base(%esi),%eaxAdd the address of memory location array_base to the contents of numberregister%esi to determine an address in memory.Move the contents of thisaddress into number register%eax.movl(%ebx,%esi,4),%eaxMultiply the contents of number register%esi by4and add the result to thecontents of number register%ebx to produce a memory reference.Move thecontents of this memory location into number register%eax.movl struct_base(%ebx,%esi,4),%eaxMultiply the contents of number register%esi by4,add the result to thecontents of number register%ebx,and add the result to the address ofstruct_base to produce an address.Move the contents of this address intonumber register%eax.Chapter2•Solaris x86Assembly Language Syntax19Assembler DirectivesDirectives are commands that are part of the assembler syntax but are not related to thex86processor instruction set.All assembler directives begin with a period(.)(ASCII0x2E)..align integer,padThe.align directive causes the next data generated to be aligned modulo integerbytes.Integer must be a positive integer expression and must be a power of2.Ifspecified,pad is an integer bye value used for padding.The default value of pad forthe text section is0x90(nop);for other sections,the default value of pad is zero(0)..ascii"string"The.ascii directive places the characters in string into the object module at thecurrent location but does not terminate the string with a null byte(\0).String mustbe enclosed in double quotes(")(ASCII0x22).The.ascii directive is not valid forthe.bss section..bcd integerThe.bcd directive generates a packed decimal(80-bit)value into the currentsection.The.bcd directive is not valid for the.bss section..bssThe.bss directive changes the current section to.bss..bss symbol,integerDefine symbol in the.bss section and add integer bytes to the value of the locationcounter for.bss.When issued with arguments,the.bss directive does notchange the current section to.bss.Integer must be positive..byte byte1,byte2,...,byteNThe.byte directive generates initialized bytes into the current section.The.bytedirective is not valid for the.bss section.Each byte must be an8-bit value..2byte expression1,expression2,...,expressionNRefer to the description of the.value directive..4byte expression1,expression2,...,expressionNRefer to the description of the.long directive..8byte expression1,expression2,...,expressionNRefer to the description of the.quad directive..comm name,size,alignmentm directive allocates storage in the data section.The storage is referencedby the identifier name.Size is measured in bytes and must be a positive integer.Name cannot be predefined.Alignment is optional.If alignment is specified,theaddress of name is aligned to a multiple of alignment..dataThe.data directive changes the current section to.data.20x86Assembly Language Reference Manual•January2005。

aurora_64b66b_protocol_spec_sp011

aurora_64b66b_protocol_spec_sp011Aurora 64B/66B Protocol SpecificationSP011 (v1.2) July 23, 2010Xilinx is disclosing to you this Specification (hereinafter "the Specification") for use in the development of designs in connection with semiconductor devices. Xilinx expressly disclaims any liability arising out of your use of the Specification. Xilinx does not convey any license under its patents, copyrights, or any rights of others in connection with the Specification. Y ou are responsible for obtaining any rights you may require for your use or implementation of the Specification. Xilinx reserves the right to make changes, at any time, to the Specification without notice and at the sole discretion of Xilinx. Xilinx assumes no obligation to correct any errors contained in the Specification or to advise you of any corrections or updates. Xilinx expressly disclaims any liability in connection with technical support or assistance that may be provided to you in connection with the Specification.THE SPECIFICA TION IS DISCLOSED TO YOU "AS-IS" WITH NO WARRANTY OF ANY KIND. YOU BEAR THE ENTIRE RISK AS TO ITS IMPLEMENTA TION AND USE. YOU ACKNOWLEDGE AND AGREE THA T YOU HAVE NOT RELIED ON ANY ORAL OR WRITTEN INFORMATION OR ADVICE, WHETHER GIVEN BY XILINX, ITS EMPLOYEES OR CONTRACTORS. XILINX MAKES NO OTHER WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STA TUTORY, REGARDING THE SPECIFICATION, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A P ARTICULAR PURPOSE, OR NONINFRINGEMENT OF THIRD-PARTY RIGHTS.IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES, INCLUDING ANY LOSS OF DA TA OR LOST PROFITS, ARISING FROM OR RELATING TO YOUR USE OF THE SPECIFICA TION, EVEN IF YOU HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.2008, 2010 Xilinx, Inc. All rights reserved.XILINX, the Xilinx logo, the Brand Window, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.Revision HistoryThe following table shows the revision history for this document.Date Version Revision03/31/08 1.0Initial Xilinx release.09/19/08 1.1Minor typographical edits. Changed block codes to blocks. Removed Not Ready blocks from Simplex in Table4-1, page36. Clarified simplex Aurora channel bonding inSection4.2.2“Channel Bonding,” page36. Added Appendix1, “References.”07/23/10 1.2Updated Section1.2“Scope” and Section8.1“Overview.”Deleted Sections 8.4 Transmitter Specifications, 8.5 Receiver Specifications, and 8.6Receiver Eye Diagrams.Table of ContentsSchedule of Figures. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Schedule of Tables. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9Preface: About This SpecificationSpecification Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12 Typographical. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12Online Document. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12State Diagram Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 Section1: Introduction and Overview1.1:Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 1.2:Scope . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 1.3:Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 Section2: Data Transmission and Reception2.1:Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 2.2:Block Codes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 2.3:Frame Transmission Procedure. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23 2.3.1:Link-Layer Frame Delineation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 242.3.2:64B/66B Encoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 242.3.3:Serialization and Clock Encoding. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24 2.3.4:Multi-Lane Transmission. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 242.4:Frame Reception Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 2.4.1:Deserialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 2.4.2:64B/66B Decoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 2.4.3:Control Block Stripping. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 262.4.4:Multi-Lane Reception. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 262.5:Data and Separator Block Format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26 Section3: Flow Control3.1:Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29 3.2:Native Flow Control Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 293.3:Native Flow Control Latency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 3.4:Native Flow Control Block Format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 303.5:User Flow Control Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 3.6:User Flow Control Message Format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31Section4: Initialization and Error Handling4.1:Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33 4.2:Aurora Channel Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 344.2.1:Lane Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 344.2.2:Channel Bonding. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36 4.2.3:Wait For Remote . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 374.3:Error Handling. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 384.4:CRC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38 Section5: PCS Layer5.1:Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 395.2:Aurora Encoding. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 395.2.1:Block Codes in 64B/66B. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 395.2.2:Idle/Not Ready/Clock Compensation/Channel Bonding Block Code. . . . . . 405.2.3:Native Flow Control Block Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 425.2.4:Data Block Code for Frame Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 425.2.5:Separator Block Code. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 425.2.6:Separator-7 Block Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 435.2.7:User Flow Control Block Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 435.2.8:Data Block Code for User Flow Control Message . . . . . . . . . . . . . . . . . . . . . . . . 445.2.9:User K-Block Codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 445.3:64B/66B Scrambling. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 455.4:64B/66B Gearbox . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 455.5:Channel Bonding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 455.6:Clock Compensation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45 Section6: Channel Control6.1:Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 476.2:Idle Block Striping. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 476.2.1:Not Ready Blocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 476.2.2:Idle Blocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 476.2.3:Clock Compensation Blocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 476.2.4:Channel Bonding Blocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 476.3:Native Flow Control Striping. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 476.4:Frame Data Striping. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 486.5:Strict-Alignment Frame Data Striping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 486.6:User Flow Control Striping. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 486.7:Strict-Alignment User Flow Control Striping . . . . . . . . . . . . . . . . . . . . . . . . . . . . 486.8:User K-Block Striping. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48 Section7: PMA Layer7.1:Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 497.2:Bit and Byte Ordering Convention. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 497.3:Serialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49Section8: Electrical Specifications8.1:Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 518.2:Signal Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 518.3:Equalization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52 Appendix1: ReferencesSchedule of FiguresPreface: About This SpecificationFigure P-1:Properties of Literals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13Figure P-2:State Machine Diagram Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15Section1: Introduction and OverviewFigure 1-1:Aurora Protocol Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18Figure 1-2:A Simplex Connection Between a Pair of Aurora Lanes . . . . . . . . . . . . . . . . . 18Figure 1-3:A Single-Lane, Simplex Aurora Channel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19Figure 1-4:A Multi-Lane, Simplex Aurora Channel. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19Figure 1-5:A Single-Lane, Full-Duplex Aurora Channel. . . . . . . . . . . . . . . . . . . . . . . . . . . 20Figure 1-6:A Multi-Lane, Full-Duplex Aurora Channel . . . . . . . . . . . . . . . . . . . . . . . . . . . 20Section2: Data Transmission and ReceptionFigure 2-1:Mapping Frames to Encoded Block Codes for Transmission. . . . . . . . . . . . . 23Figure 2-2:Receiving Data from an Aurora Channel . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25Figure 2-3:Data Block Used for Frame Data. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26Figure 2-4:Separator Block. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26Figure 2-5:Separator-7 Block. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27Figure 2-6:Example of Frame Data Transfer through a Single-Lane Channel . . . . . . . . 27Figure 2-7:Example of Frame Data Transfer through a Multi-Lane Channel . . . . . . . . . 27Section3: Flow ControlFigure 3-1:NFC Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30Figure 3-2:UFC Block with UFC Header. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31Figure 3-3:Data Block Used to Carry UFC Message Data . . . . . . . . . . . . . . . . . . . . . . . . . . 31Figure 3-4:Example UFC Messages for Single-Lane Channel . . . . . . . . . . . . . . . . . . . . . . 31Figure 3-5:Example UFC Messages for a Multi-Lane Channel. . . . . . . . . . . . . . . . . . . . . . 32Section4: Initialization and Error HandlingFigure 4-1:Initialization Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34Figure 4-2:Block Sync State Machine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35Section5: PCS LayerFigure 5-1:Idle/Not Ready/NFC Block Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41Figure 5-2:Native Flow Control Block Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42Figure 5-3:Data Block Code Carrying Frame Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42Figure 5-4:Separator Block Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42Figure 5-5:Separator-7 Block Code. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43Figure 5-6:User Flow Control Block Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43 Figure 5-7:Data Block Code Carrying User Flow Control Message Data. . . . . . . . . . . . . 44 Figure 5-8:User K-Block Code Format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44Section6: Channel ControlSection7: PMA LayerFigure 7-1:Serialization Order for Aurora 64B/66B Block Codes. . . . . . . . . . . . . . . . . . . . 49Section8: Electrical SpecificationsFigure 8-1:Differential Peak-To-Peak Voltage of Transmitter or Receiver. . . . . . . . . . . 51Appendix1: ReferencesSchedule of TablesPreface: About This SpecificationTable P-1:Radix Specifics of Literals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13Table P-2:Examples of Extended Values. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13Section1: Introduction and OverviewSection2: Data Transmission and ReceptionTable 2-1:Aurora 64B/66B Blocks Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21Table 2-2:Normal Aurora 64B/66B Block Transmission Priority . . . . . . . . . . . . . . . . . . . . 22Table 2-3:Aurora 64B/66B Block Transmission Priority during Flow Control Countdown 23 Section3: Flow Control Section4: Initialization and Error HandlingTable 4-1:Required Block Transmission during Lane Initialization. . . . . . . . . . . . . . . . . 36Table 4-2:Required State Transition after Lane Initialization . . . . . . . . . . . . . . . . . . . . . . 36Table 4-3:Required State Transition after Successful Channel Bonding. . . . . . . . . . . . . 37Section5: PCS LayerTable 5-1:Valid Block Type Field Values in Aurora 64B/66B. . . . . . . . . . . . . . . . . . . . . . . 40Table 5-2:Valid Octet Count Field Values for Separator Block Code. . . . . . . . . . . . . . . . 43Table 5-3:Valid Block Type Field Values for User K-Blocks . . . . . . . . . . . . . . . . . . . . . . . 44 Section6: Channel Control Section7: PMA LayerSection8: Electrical SpecificationsAppendix1: ReferencesPreface About This SpecificationThis specification describes the Aurora 64B/66B protocol. Aurora is a lightweight link-layer protocol that can be used to move data point-to-point across one or more high-speed serial lanes. Aurora 64B/66B is a version of the protocol using 64B/66B encoding instead of 8B/10B.Specification ContentsThis manual contains the following:Section1, “Introduction and Overview”provides an overview of the Aurora 64B/66B protocol.Section2, “Data Transmission and Reception”describes the procedures for transmitting and receiving data using an Aurora 64B/66B Channel.Section3, “Flow Control”describes the optional flow control features in the Aurora64B/66B protocol.Section4, “Initialization and Error Handling”describes the procedure used to preparean Aurora channel for operation.Section5, “PCS Layer”specifies the functions performed in the physical coding sub-layer (PCS) of the Aurora 64B/66B protocol.Section6, “Channel Control”defines the striping rules for using multi-lane channels. Section7, “PMA Layer”specifies the functions performed in the PMA layer of the Aurora 64B/66B Protocol.Section8, “Electrical Specifications”describes the AC specifications, covering both single- and multi-lane implementations.ConventionsThis document uses the following conventions.T ypographicalThe following typographical conventions are used in this document:Online DocumentThe following conventions are used in this document:NumericalConventionMeaning or UseExampleItalic fontReferences to other manualsSee the Development System Reference Guide for more information.Emphasis in textIf a wire is drawn so that itoverlaps the pin of a symbol, the two nets are not connected.To emphasize a term the first time it is used The state machine uses one-hot encoding.REG[FIELD]Abbreviations or acronyms for registers are shown in uppercasetext. Specific bits, fields, or ranges appear in bracketsREG[11:14]ConventionMeaning or UseExampleBlue textCross-reference link to a location in the current document See the section “AdditionalResources” for details.Refer to “Title Formats” inSection 1 for details.Red textCross-reference link to a location in another document See Figure 2-5 in the Virtex-II Platform FPGA User Guide.Blue, underlined textHyperlink to a website (URL)Go to /doc/10fb3b7b1711cc7931b716ea.htmlfor the latest speed files.Convention Meaning or Usen A decimal value[n:m ]Used to express a numerical range from n to m x Unknown value zHigh impedanceValues of LiteralsLiterals are represented by specifying three of their properties as listed and shown in Figure P-1 and in Table P-1 and Table P-2:1.Width in bits 2.Radix (Base)3.ValueTable P-1 shows the Radix specifics:All values are extended with zero except those with x or z in the most significant place; they extend with x or z respectively. A list of examples is shown in Table P-2:Figure P-1:Properties of LiteralsTable P-1:Radix Specifics of LiteralsRadix SpecifierRadixb Binary d Decimal h Hexadecimal oOctalTable P-2:Examples of Extended ValuesNumber Value Comment8’b000000000An 8-bit binary number with value of zero. (Zero extended to get 8 bits.)8’bx xxxxxxxxAn 8-bit binary number with value unknown. (x extended to get 8 bits.)8’b1x 0000001x An 8-bit binary number with value of 2 or 3, depending on the value of x.8’b0x 0000000x An 8-bit binary number with value of 0 or 1, depending on the value of x.8’hx xxxxxxxx An 8-bit hexadecimal number with value unknown.(x extended to get 8 bits.)8’hzx zzzzxxxx An 8-bit hexadecimal number with the upper four bits not driven and the lower four bitsunknown.8’b100000001An 8-bit binary number with value of one.8’hz1zzzz0001An 8-bit hexadecimal number with the upper four bits not driven and the lower four bits having value of one.8’bx1xxxxxxx1An 8-bit binary number that is odd.8’bx0xxxxxxx0An 8-bit binary number that is even.State Diagram ConventionsThis section describes the conventions used in the state diagrams for this document. The numbered sections correspond to the call-outs shown in the state machine diagram in Figure P-2, page 15.States1. A state is represented by a rectangle.2.The name of the state is indicated in bold.State T ransitions3.State transition is indicated by an arrow annotated in italics.State Machine OutputsOutputs are shown in plain text. Outputs can be shown inside of state rectangles or can be part of the annotation associated with a transition arrow. If a signal is not listed in a state rectangle or on a transition arrow, its value at that time is 0 (not asserted). If a registered output does not appear in the state rectangle or transition arrow annotation, then its value is unchanged from the previous value.Output T ypesOutputs are divided into three classes as shown in the examples below.4.Asserting control signals:go = 1link reset = 15.Register initialization:XYZ Register = 78New Counter = 0xmit = /SP/ (an ordered set)6.Incrementing or decrementing a register:XYZ Register = XYZ Register + 1New Counter = New Counter – 68’hz zzzzzzzz An 8-bit hexadecimal number with value not driven. (z extended to get 8 bits.)8’h0z 0000zzzzAn 8-bit hexadecimal number with upper nibble specified and the lower not driven.11’d n n An 11-bit decimal number with value n .6’h n nA 6-bit hexadecimal number with value n .w’b101(101)A binary number with value 5 and an unknown width.Table P-2:Examples of Extended Values (Cont’d)Number Value CommentFigure P-2:State Machine Diagram ConventionsSection1 Introduction and Overview1.1IntroductionAurora is a lightweight link-layer protocol that can be used to move data point-to-pointacross one or more high-speed serial lanes. Aurora 64B/66B is a version of the protocolusing 64B/66B encoding instead of 8B/10B.1.2ScopeThe Aurora 64B/66B Protocol Specification defines the following:Electrical specifications: This includes signaling levels for an Aurora serial link.PMA layer: This includes specification for serialization bit ordering and byteordering.Physical coding sub-layer (PCS): This includes specification for data encoding anddecoding, data scrambling, the 64B/66B gearbox, clock compensation and channelbonding.Channel control: This includes specifications for multi-lane striping and forscheduling the transmission of data and control information.Cyclic redundancy check (CRC): The Aurora protocol recommends a CRCmechanism compatible with the standard 64B/66B scrambling algorithm.1.3OverviewThe Aurora protocol (Figure1-1, page18) describes the transfer of user data across anAurora channel, consisting of one or more Aurora lanes. Each Aurora lane is a serial dataconnection, either full-duplex or simplex. Devices communicating across the channel arecalled channel partners.Aurora interfaces allow user applications to transfer data through the Aurora channel. Theuser interface on each Aurora interface is not defined in this specification and can bedecided independently for each implementation of the protocol.Aurora channels have the following properties:Data is transferred through the Aurora channel in frames.Frames share the channel with control information such as flow control messages,clock compensation sequences and idles.Frames can be of any length, and can have any format. Only the delineation of framesis defined in this specification.Frames in Aurora do not have to be contiguous — they can be interrupted at any time by flow control messages or idles.There is no gap required between frames in Aurora.Figure 1-1:Aurora Protocol OverviewFigure1-2 shows a simplex connection between a pair of Aurora lanes, depicting the functional blocks comprising the PCS and PMA layers of an Aurora connection. These blocks are specified in detail in this document.Figure 1-2: A Simplex Connection Between a Pair of Aurora LanesAurora interfaces allow applications to communicate using Aurora channels. Aurora interfaces are made up of one or more Aurora lanes, either simplex or full-duplex. The four possible configurations of Aurora interfaces are shown in Figure1-3, Figure1-4,Figure1-5, page20, and Figure1-6, page20.Figure1-3 shows a single-lane, simplex Aurora interface transmitting to another single-lane, simplex Aurora interface. In this configuration, each interface uses a single lane to transmit or receive from the Aurora channel. Channel control in each interface initializes the channel passing control to the user application.Figure 1-3: A Single-Lane, Simplex Aurora ChannelFigure1-4 shows a multi-lane, simplex Aurora interface transmitting to another multi-lane, simplex Aurora interface. In multi-lane configurations, the channel control bonds the lanes to eliminate skew between channels as a part of the channel initialization procedure. During normal operation, the channel control logic distributes data and control information across all the lanes in the channel.Figure 1-4: A Multi-Lane, Simplex Aurora Channel。

CompactPCI+a+Specification标准