NESG3032M14中文资料

EPM3032ATC44-10中文资料

®Altera Corporation 1MAX 3000AProgrammable Logic Device FamilyJune 2002, ver. 3.0Data Sheet DS-M3000A-3.0Features...■High–performance, low–cost CMOS EEPROM–based programmable logic devices (PLDs) built on a MAX ® architecture (see Table 1)■3.3-V in-system programmability (ISP) through the built–in IEEE Std. 1149.1 Joint Test Action Group (JTAG) interface with advanced pin-locking capability –ISP circuitry compliant with IEEE Std. 1532■Built–in boundary-scan test (BST) circuitry compliant with IEEE Std. 1149.1-1990■Enhanced ISP features:–Enhanced ISP algorithm for faster programming –ISP_Done bit to ensure complete programming –Pull-up resistor on I/O pins during in–system programming ■High–density PLDs ranging from 600 to 10,000 usable gates ■4.5–ns pin–to–pin logic delays with counter frequencies of up to 227.3MHz ■MultiVolt TM I/O interface enabling the device core to run at 3.3 V, while I/O pins are compatible with 5.0–V, 3.3–V, and 2.5–V logic levels ■Pin counts ranging from 44 to 256 in a variety of thin quad flat pack (TQFP), plastic quad flat pack (PQFP), plastic J–lead chip carrier (PLCC), and FineLine BGA TM packages ■Hot–socketing support ■Programmable interconnect array (PIA) continuous routing structurefor fast, predictable performance Table 1.MAX3000A Device Features FeatureEPM3032A EPM3064A EPM3128A EPM3256A EPM3512A Usable gates6001,2502,5005,00010,000Macrocells3264128256512Logic array blocks2481632Maximum user I/Opins346696158208t PD (ns)4.5 4.55.0 5.57.5t SU (ns)2.9 2.83.3 3.9 5.6t CO1 (ns)3.0 3.1 3.4 3.54.7f CNT (MHz)227.3222.2192.3172.4116.3捷多邦,您值得信赖的PCB打样专家!MAX 3000A Programmable Logic Device Family Data Sheet...and More Features ■PCI compatible■Bus–friendly architecture including programmable slew–rate control ■Open–drain output option■Programmable macrocell flipflops with individual clear, preset, clock, and clock enable controls■Programmable power–saving mode for a power reduction of over 50% in each macrocell■Configurable expander product–term distribution, allowing up to32 product terms per macrocell■Programmable security bit for protection of proprietary designs■Enhanced architectural features, including:– 6 or 10 pin– or logic–driven output enable signals–Two global clock signals with optional inversion–Enhanced interconnect resources for improved routability–Programmable output slew–rate control■Software design support and automatic place–and–route provided by Altera’s development systems for Windows–based PCs and Sun SPARCstations, and HP 9000 Series 700/800 workstations■Additional design entry and simulation support provided by EDIF2 0 0 and3 0 0 netlist files, library of parameterized modules (LPM),Verilog HDL, VHDL, and other interfaces to popular EDA tools from third–party manufacturers such as Cadence, Exemplar Logic, Mentor Graphics, OrCAD, Synopsys, Synplicity, and VeriBest■Programming support with the Altera master programming unit (MPU), MasterBlaster TM communications cable, ByteBlasterMV TMparallel port download cable, BitBlaster TM serial download cable as well as programming hardware from third–party manufacturers and any in–circuit tester that supports Jam TM Standard Test andProgramming Language (STAPL) Files (.jam), Jam STAPL Byte-Code Files (.jbc), or Serial Vector Format Files (.svf)General Description MAX3000A devices are low–cost, high–performance devices based on the Altera MAX architecture. Fabricated with advanced CMOS technology, the EEPROM–based MAX3000A devices operate with a 3.3-V supply voltage and provide 600 to 10,000 usable gates, ISP, pin-to-pin delays as fast as 4.5 ns, and counter speeds of up to 227.3MHz. MAX3000A devices in the –4, –5, –6, –7, and –10 speed grades are compatible with the timing requirements of the PCI Special Interest Group (PCI SIG) PCI Local Bus Specification, Revision2.2. See Table2.2Altera CorporationAltera Corporation 3MAX 3000A Programmable Logic Device Family Data Sheet The MAX 3000A architecture supports 100% transistor-to-transistor logic (TTL) emulation and high–density small-scale integration (SSI), medium-scale integration (MSI), and large-scale integration (LSI) logic functions. The MAX 3000A architecture easily integrates multiple devices ranging from PALs, GALs, and 22V10s to MACH and pLSI devices. MAX 3000A devices are available in a wide range of packages, including PLCC, PQFP, and TQFP packages. See Table 3.Note:(1)When the IEEE Std. 1149.1 (JTAG) interface is used for in–system programming or boundary–scan testing, four I/O pins become JTAG pins.MAX 3000A devices use CMOS EEPROM cells to implement logic functions. The user–configurable MAX 3000A architecture accommodates a variety of independent combinatorial and sequential logic functions. The devices can be reprogrammed for quick and efficient iterations during design development and debugging cycles, and can be programmed and erased up to 100 times.Table 2.MAX 3000A Speed Grades Device Speed Grade –4–5–6–7–10EPM3032A v v v EPM3064A vv v EPM3128A v v v EPM3256A v v EPM3512A v v Table 3.MAX 3000A Maximum User I/O Pins Note (1)Device 44–Pin PLCC 44–Pin TQFP 100–Pin TQFP 144–Pin TQFP 208–Pin PQFP 256-Pin FineLine BGA EPM3032A 3434EPM3064A 343466EPM3128A 8096EPM3256A 116158EPM3512A 172208MAX 3000A Programmable Logic Device Family Data SheetMAX3000A devices contain 32 to 512 macrocells, combined into groupsof 16 macrocells called logic array blocks (LABs). Each macrocell has aprogrammable–AND/fixed–OR array and a configurable register withindependently programmable clock, clock enable, clear, and presetfunctions. To build complex logic functions, each macrocell can besupplemented with shareable expander and high–speed parallelexpander product terms to provide up to 32 product terms per macrocell.MAX3000A devices provide programmable speed/power optimization.Speed–critical portions of a design can run at high speed/full power,while the remaining portions run at reduced speed/low power. Thisspeed/power optimization feature enables the designer to configure oneor more macrocells to operate at 50% or lower power while adding only anominal timing delay. MAX3000A devices also provide an option thatreduces the slew rate of the output buffers, minimizing noise transientswhen non–speed–critical signals are switching. The output drivers of allMAX3000A devices can be set for 2.5V or 3.3V, and all input pins are2.5–V,3.3–V, and 5.0-V tolerant, allowing MAX3000A devices to be usedin mixed–voltage systems.MAX3000A devices are supported by Altera development systems,which are integrated packages that offer schematic, text—includingVHDL, Verilog HDL, and the Altera Hardware Description Language(AHDL)—and waveform design entry, compilation and logic synthesis,simulation and timing analysis, and device programming. The softwareprovides EDIF 2 0 0 and 3 0 0, LPM, VHDL, Verilog HDL, and otherinterfaces for additional design entry and simulation support from otherindustry–standard PC– and UNIX–workstation–based EDA tools. Thesoftware runs on Windows–based PCs, as well as Sun SPARCstation, andHP 9000 Series 700/800 workstations.f For more information on development tools, see the MAX+PLUS IIProgrammable Logic Development System & Software Data Sheet andtheQuartus Programmable Logic Development System & Software Data Sheet.Functional Description The MAX3000A architecture includes the following elements:■Logic array blocks (LABs)■Macrocells■Expander product terms (shareable and parallel)■Programmable interconnect array (PIA)■I/O control blocksThe MAX3000A architecture includes four dedicated inputs that can be used as general–purpose inputs or as high–speed, global control signals (clock, clear, and two output enable signals) for each macrocell and I/O pin. Figure1 shows the architecture of MAX3000A devices.4Altera CorporationMAX 3000A Programmable Logic Device Family Data Sheet Figure 1. MAX3000A Device Block DiagramNote:(1)EPM3032A, EPM3064A, EPM3128A, and EPM3256A devices have six output enables. EPM3512A devices have10output enables.Logic Array BlocksThe MAX3000A device architecture is based on the linking ofhigh–performance LABs. LABs consist of 16–macrocell arrays, as shownin Figure1. Multiple LABs are linked together via the PIA, a global busthat is fed by all dedicated input pins, I/O pins, and macrocells.Each LAB is fed by the following signals:■36 signals from the PIA that are used for general logic inputs■Global controls that are used for secondary register functionsAltera Corporation 5MAX 3000A Programmable Logic Device Family Data SheetMacrocellsMAX3000A macrocells can be individually configured for eithersequential or combinatorial logic operation. Macrocells consist of threefunctional blocks: logic array, product–term select matrix, andprogrammable register. Figure2 shows a MAX3000A macrocell.Figure 2. MAX3000A MacrocellQCLRNTo PIACombinatorial logic is implemented in the logic array, which providesfive product terms per macrocell. The product–term select matrixallocates these product terms for use as either primary logic inputs (to theOR and XOR gates) to implement combinatorial functions, or as secondaryinputs to the macrocell’s register preset, clock, and clock enable controlfunctions.Two kinds of expander product terms (“expanders”) are available tosupplement macrocell logic resources:■Shareable expanders, which are inverted product terms that are fedback into the logic array■Parallel expanders, which are product terms borrowed from adjacentmacrocellsThe Altera development system automatically optimizes product–termallocation according to the logic requirements of the design.6Altera CorporationMAX 3000A Programmable Logic Device Family Data SheetFor registered functions, each macrocell flipflop can be individuallyprogrammed to implement D, T, JK, or SR operation with programmableclock control. The flipflop can be bypassed for combinatorial operation.During design entry, the designer specifies the desired flipflop type; theAltera development system software then selects the most efficientflipflop operation for each registered function to optimize resourceutilization.Each programmable register can be clocked in three different modes:■Global clock signal mode, which achieves the fastest clock–to–outputperformance.■Global clock signal enabled by an active–high clock enable. A clockenable is generated by a product term. This mode provides an enableon each flipflop while still achieving the fast clock–to–outputperformance of the global clock.■Array clock implemented with a product term. In this mode, theflipflop can be clocked by signals from buried macrocells or I/O pins.Two global clock signals are available in MAX3000A devices. As shownin Figure1, these global clock signals can be the true or the complement ofeither of the two global clock pins, GCLK1 or GCLK2.Each register also supports asynchronous preset and clear functions. Asshown in Figure2, the product–term select matrix allocates product termsto control these operations. Although the product–term–driven presetand clear from the register are active high, active–low control can beobtained by inverting the signal within the logic array. In addition, eachregister clear function can be individually driven by the active–lowdedicated global clear pin (GCLRn).Expander Product TermsAlthough most logic functions can be implemented with the five productterms available in each macrocell, highly complex logic functions requireadditional product terms. Another macrocell can be used to supply therequired logic resources. However, the MAX3000A architecture alsooffers both shareable and parallel expander product terms (“expanders”)that provide additional product terms directly to any macrocell in thesame LAB. These expanders help ensure that logic is synthesized with thefewest possible logic resources to obtain the fastest possible speed. Altera Corporation 78Altera Corporation MAX 3000A Programmable Logic Device Family Data SheetShareable Expanders Each LAB has 16 shareable expanders that can be viewed as a pool of uncommitted single product terms (one from each macrocell) with inverted outputs that feed back into the logic array. Each shareable expander can be used and shared by any or all macrocells in the LAB to build complex logic functions. Shareable expanders incur a small delay (t SEXP ). Figure 3 shows how shareable expanders can feed multiple macrocells.Figure 3. MAX 3000A Shareable Expanders Shareable expanders can be shared by any or all macrocells in an LAB.Parallel Expanders Parallel expanders are unused product terms that can be allocated to a neighboring macrocell to implement fast, complex logic functions. Parallel expanders allow up to 20 product terms to directly feed the macrocell OR logic, with five product terms provided by the macrocell and 15 parallel expanders provided by neighboring macrocells in the LAB. MacrocellProduct-Term Logic Product-Term Select Matrix Macrocell Product-Term Logic 36 Signals from PIA 16 Shared ExpandersMAX 3000A Programmable Logic Device Family Data SheetThe Altera development system compiler can automatically allocate up tothree sets of up to five parallel expanders to the macrocells that requireadditional product terms. Each set of five parallel expanders incurs asmall, incremental timing delay (t PEXP). For example, if a macrocellrequires 14product terms, the compiler uses the five dedicated productterms within the macrocell and allocates two sets of parallel expanders;the first set includes five product terms, and the second set includes fourproduct terms, increasing the total delay by 2 ×t PEXP.Two groups of eight macrocells within each LAB (e.g., macrocells 1through 8 and 9through 16) form two chains to lend or borrow parallelexpanders. A macrocell borrows parallel expanders from lower–numbered macrocells. For example, macrocell 8 can borrow parallelexpanders from macrocell 7, from macrocells 7 and 6, or from macrocells7, 6, and 5. Within each group of eight, the lowest–numbered macrocellcan only lend parallel expanders and the highest–numbered macrocell canonly borrow them. Figure4 shows how parallel expanders can beborrowed from a neighboring macrocell.Figure 4. MAX3000A Parallel ExpandersUnused product terms in a macrocell can be allocated to a neighboring macrocell.Altera Corporation 9MAX 3000A Programmable Logic Device Family Data SheetProgrammable Interconnect ArrayLogic is routed between LABs on the PIA. This global bus is aprogrammable path that connects any signal source to any destination onthe device. All MAX3000A dedicated inputs, I/O pins, and macrocelloutputs feed the PIA, which makes the signals available throughout theentire device. Only the signals required by each LAB are actually routedfrom the PIA into the LAB. Figure5 shows how the PIA signals are routedinto the LAB. An EEPROM cell controls one input to a two-input AND gate,which selects a PIA signal to drive into the LAB.Figure 5. MAX3000A PIA RoutingWhile the routing delays of channel–based routing schemes in masked orFPGAs are cumulative, variable, and path–dependent, the MAX3000APIA has a predictable delay. The PIA makes a design’s timingperformance easy to predict.I/O Control BlocksThe I/O control block allows each I/O pin to be individually configuredfor input, output, or bidirectional operation. All I/O pins have a tri–statebuffer that is individually controlled by one of the global output enablesignals or directly connected to ground or V CC. Figure6 shows the I/Ocontrol block for MAX3000A devices. The I/O control block has 6 or10global output enable signals that are driven by the true or complementof two output enable signals, a subset of the I/O pins, or a subset of theI/O macrocells.10Altera CorporationMAX 3000A Programmable Logic Device Family Data Sheet Figure 6. I/O Control Block of MAX3000A DevicesNote:(1)EPM3032A, EPM3064A, EPM3128A, and EPM3256A devices have six output enables. EPM3512A devices have10output enables.When the tri–state buffer control is connected to ground, the output istri-stated (high impedance), and the I/O pin can be used as a dedicatedinput. When the tri–state buffer control is connected to V CC, the output isenabled.The MAX3000A architecture provides dual I/O feedback, in whichmacrocell and pin feedbacks are independent. When an I/O pin isconfigured as an input, the associated macrocell can be used for buriedlogic.Altera Corporation 1112Altera Corporation MAX 3000A Programmable Logic Device Family Data SheetIn–SystemProgramma-bilityMAX 3000A devices can be programmed in–system via an industry–standard four–pin IEEE Std. 1149.1-1990 (JTAG) interface. In-system programmability (ISP) offers quick, efficient iterations during design development and debugging cycles. The MAX 3000A architecture internally generates the high programming voltages required to program its EEPROM cells, allowing in–system programming with only a single 3.3–V power supply. During in–system programming, the I/O pins are tri–stated and weakly pulled–up to eliminate board conflicts. The pull–up value is nominally 50 k Ω.MAX 3000A devices have an enhanced ISP algorithm for faster programming. These devices also offer an ISP_Done bit that ensures safe operation when in–system programming is interrupted. This ISP_Done bit, which is the last bit programmed, prevents all I/O pins from driving until the bit is programmed.ISP simplifies the manufacturing flow by allowing devices to be mounted on a printed circuit board (PCB) with standard pick–and–place equipment before they are programmed. MAX 3000A devices can be programmed by downloading the information via in–circuit testers, embedded processors, the MasterBlaster communications cable, the ByteBlasterMV parallel port download cable, and the BitBlaster serial download cable. Programming the devices after they are placed on the board eliminates lead damage on high–pin–count packages (e.g., QFP packages) due to device handling. MAX 3000A devices can be reprogrammed after a system has already shipped to the field. For example, product upgrades can be performed in the field via software or modem. The Jam STAPL programming and test language can be used to program MAX 3000A devices with in–circuit testers, PCs, or embedded processors.fFor more information on using the Jam STAPL programming and test language, see Application Note 88 (Using the Jam Language for ISP & ICR via an Embedded Processor), Application Note 122 (Using Jam STAPL for ISP & ICR via an Embedded Processor) and AN 111 (Embedded Programming Using the 8051 and Jam Byte-Code).The ISP circuitry in MAX 3000A devices is compliant with the IEEE Std. 1532 specification. The IEEE Std. 1532 is a standard developed to allow concurrent ISP between multiple PLD vendors.Programmingwith ExternalHardwareMAX 3000A devices can be programmed on Windows–based PCs with an Altera Logic Programmer card, MPU, and the appropriate device adapter. The MPU performs continuity checking to ensure adequate electrical contact between the adapter and the device. fFor more information, see the Altera Programming Hardware Data Sheet.Altera Corporation 13MAX 3000A Programmable Logic Device Family Data SheetThe Altera software can use text– or waveform–format test vectors createdwith the Altera Text Editor or Waveform Editor to test the programmeddevice. For added design verification, designers can perform functionaltesting to compare the functional device behavior with the results ofsimulation.Data I/O, BP Microsystems, and other programming hardwaremanufacturers also provide programming support for Altera devices.fFor more information, see Programming Hardware Manufacturers .IEEE Std.1149.1 (JTAG)Boundary–ScanSupport MAX 3000A devices include the JTAG BST circuitry defined by IEEE Std.1149.1–1990. Table 4 describes the JTAG instructions supported by MAX 3000A devices. The pin-out tables found on the Altera web site ( ) or the Altera Digital Library show the location of the JTAG control pins for each device. If the JTAG interface is notrequired, the JTAG pins are available as user I/O pins.The instruction register length of MAX 3000A devices is 10 bits. TheIDCODE and USERCODE register length is 32 bits. Tables 5 and 6 showthe boundary–scan register length and device IDCODE information forMAX 3000A devices.Table 4.MAX 3000A JTAG InstructionsJTAG InstructionDescription SAMPLE/PRELOADAllows a snapshot of signals at the device pins to be captured and examined during normal device operation, and permits an initial data pattern output at the device pins EXTESTAllows the external circuitry and board–level interconnections to be tested by forcing a test pattern at the output pins and capturing test results at the input pins BYPASS Places the 1–bit bypass register between the TDI and TDO pins, which allows the BSTdata to pass synchronously through a selected device to adjacent devices during normaldevice operationIDCODE Selects the IDCODE register and places it between the TDI and TDO pins, allowing theIDCODE to be serially shifted out of TDOUSERCODE Selects the 32–bit USERCODE register and places it between the TDI and TDO pins,allowing the USERCODE value to be shifted out of TDOISP InstructionsThese instructions are used when programming MAX 3000A devices via the JTAG portswith the MasterBlaster, ByteBlasterMV, or BitBlaster cable, or when using a Jam STAPLfile, JBC file, or SVF file via an embedded processor or test equipment14Altera Corporation MAX 3000A Programmable Logic Device Family Data SheetNotes:(1)The most significant bit (MSB) is on the left.(2)The least significant bit (LSB) for all JTAG IDCODEs is 1.fSee Application Note 39 (IEEE 1149.1 (JTAG) Boundary–Scan Testing in Altera Devices) for more information on JTAG BST.Table 5.MAX 3000A Boundary–Scan Register Length Device Boundary–Scan Register Length EPM3032A 96EPM3064A 192EPM3128A 288EPM3256A 480EPM3512A 624Table 6.32–Bit MAX 3000A Device IDCODE Value Note (1)Device IDCODE (32 bits)Version (4 Bits)Part Number (16 Bits) Manufacturer’s Identity (11 Bits) 1 (1 Bit) (2)EPM3032A 00010111 0000 0011 0010000011011101EPM3064A 00010111 0000 0110 0100000011011101EPM3128A 00010111 0001 0010 1000000011011101EPM3256A 00010111 0010 0101 0110000011011101EPM3512A 00010111 0101 0001 0010000011011101MAX 3000A Programmable Logic Device Family Data SheetFigure7 shows the timing information for the JTAG signals.Figure 7. MAX3000A JTAG WaveformsTable7 shows the JTAG timing parameters and values for MAX3000Adevices.Table 7.JTAG Timing Parameters & Values for MAX3000A DevicesSymbol Parameter Min Max Unitt JCP TCK clock period 100nst JCH TCK clock high time 50nst JCL TCK clock low time 50nst JPSU JTAG port setup time 20nst JPH JTAG port hold time 45nst JPCO JTAG port clock to output25nst JPZX JTAG port high impedance to valid output25nst JPXZ JTAG port valid output to high impedance25nst JSSU Capture register setup time20nst JSH Capture register hold time45nst JSCO Update register clock to output25nst JSZX Update register high impedance to valid output25nst JSXZ Update register valid output to high impedance25ns Altera Corporation 15MAX 3000A Programmable Logic Device Family Data SheetProgrammable Speed/Power Control MAX3000A devices offer a power–saving mode that supports low-power operation across user–defined signal paths or the entire device. This feature allows total power dissipation to be reduced by 50% or more because most logic applications require only a small fraction of all gates to operate at maximum frequency.The designer can program each individual macrocell in a MAX3000A device for either high–speed or low–power operation. As a result, speed-critical paths in the design can run at high speed, while the remaining paths can operate at reduced power. Macrocells that run at low power incur a nominal timing delay adder (t LPA) for the t LAD, t LAC, t IC, t ACL, t EN, t CPPW and t SEXP parameters.Output Configuration MAX3000A device outputs can be programmed to meet a variety of system–level requirements.MultiVolt I/O InterfaceThe MAX3000A device architecture supports the MultiVolt I/O interface feature, which allows MAX3000A devices to connect to systems with differing supply voltages. MAX3000A devices in all packages can be set for 2.5–V, 3.3–V, or 5.0–V I/O pin operation. These devices have one set of V CC pins for internal operation and input buffers (VCCINT), and another set for I/O output drivers (VCCIO).The VCCIO pins can be connected to either a 3.3–V or 2.5–V power supply, depending on the output requirements. When the VCCIO pins are connected to a 2.5–V power supply, the output levels are compatible with 2.5–V systems. When the VCCIO pins are connected to a 3.3–V power supply, the output high is at 3.3V and is therefore compatible with 3.3-V or 5.0–V systems. Devices operating with V CCIO levels lower than 3.0V incur a nominally greater timing delay of t OD2 instead of t OD1. Inputs can always be driven by 2.5–V, 3.3–V, or 5.0–V signals.Table8 summarizes the MAX3000A MultiVolt I/O support.Note:(1)When V CCIO is 3.3 V, a MAX 3000A device can drive a 2.5–V device that has 3.3–Vtolerant inputs.Table 8.MAX3000A MultiVolt I/O SupportV CCIO Voltage Input Signal (V)Output Signal (V)2.53.3 5.0 2.5 3.3 5.02.5v v v v3.3v v v v v v16Altera CorporationMAX 3000A Programmable Logic Device Family Data SheetOpen–Drain Output OptionMAX3000A devices provide an optional open–drain (equivalent toopen-collector) output for each I/O pin. This open–drain output enablesthe device to provide system–level control signals (e.g., interrupt andwrite enable signals) that can be asserted by any of several devices. It canalso provide an additional wired–OR plane.Open-drain output pins on MAX3000A devices (with a pull-up resistor tothe 5.0-V supply) can drive 5.0-V CMOS input pins that require a high V IH.When the open-drain pin is active, it will drive low. When the pin isinactive, the resistor will pull up the trace to 5.0V, thereby meeting CMOSrequirements. The open-drain pin will only drive low or tri-state; it willnever drive high. The rise time is dependent on the value of the pull-upresistor and load impedance. The I OL current specification should beconsidered when selecting a pull-up resistorSlew–Rate ControlThe output buffer for each MAX3000A I/O pin has an adjustable outputslew rate that can be configured for low–noise or high–speedperformance. A faster slew rate provides high–speed transitions forhigh-performance systems. However, these fast transitions may introducenoise transients into the system. A slow slew rate reduces system noise,but adds a nominal delay of 4 to 5 ns. When the configuration cell isturned off, the slew rate is set for low–noise performance. Each I/O pinhas an individual EEPROM bit that controls the slew rate, allowingdesigners to specify the slew rate on a pin–by–pin basis. The slew ratecontrol affects both the rising and falling edges of the output signal. Design Security All MAX3000A devices contain a programmable security bit that controlsaccess to the data programmed into the device. When this bit isprogrammed, a design implemented in the device cannot be copied orretrieved. This feature provides a high level of design security becauseprogrammed data within EEPROM cells is invisible. The security bit thatcontrols this function, as well as all other programmed data, is reset onlywhen the device is reprogrammed.Generic Testing MAX3000A devices are fully tested. Complete testing of eachprogrammable EEPROM bit and all internal logic elements ensures 100%programming yield. AC test measurements are taken under conditionsequivalent to those shown in Figure8. Test patterns can be used and thenerased during early stages of the production flow.Altera Corporation 17。

易格斯直线轴承代号各部分含义

易格斯直线轴承是一种经过设计和制造的精密机械零件,主要用于工业领域的各种设备和机械中。

它的代号中包含了很多不同的部分和含义,下面将逐一解释易格斯直线轴承代号中各部分的含义。

一、通用代号1. YGSL:表示该轴承为易格斯直线轴承的通用代号;2. 22:表示轴承的系列代号,例如22代表薄壁型系列。

二、型号代号1. 22 0411:其中22表示该型号属于薄壁型系列;0411为该型号的具体代号。

三、封边、封盖和密封代号1. TSU:表示轴承无封边;2. TSS:表示轴承有封边;3. LS:表示具有外部封盖;4. ZZ:表示具有外部金属封盖;5. RS:表示具有内部密封;6. 2RS:表示具有内、外部密封。

四、内部结构代号1. M:表示轴承的内部结构为“单列滚珠”;2. S:表示轴承的内部结构为“双列滚珠”;3. E:表示轴承的内部结构为“一对单列滚珠”。

五、清洗、润滑代号1. P0:表示不清洗不润滑;2. P6:表示预润滑;3. P5:表示轴承经过清洗;4. P6:表示轴承经过磷化处理并预润滑。

六、加强式代号1. C:表示轴承采用加强式设计。

七、稳固性代号1. H:表示轴承为高可靠性稳固性设计。

以上就是易格斯直线轴承代号中各部分的含义,通过了解这些代号的含义,我们可以更好地选择和使用适合自己需求的轴承产品。

让我们来详细解释一下易格斯直线轴承代号中各部分的含义以及其在实际应用中的重要性。

一、通用代号1. YGSL:易格斯直线轴承的通用代号。

这个代号是易格斯直线轴承产品的标志,它代表着产品的品牌和质量保证。

作为制造商,易格斯对轴承产品的品质把控非常严格,保证产品的每一个细节都符合标准,以满足客户的需求。

2. 22:这个数字是轴承产品的系列代号。

在易格斯直线轴承产品中,不同的系列代号代表着轴承产品在外形、尺寸、承载能力等方面的不同特点。

了解并选择适合的系列代号对于使用者来说非常重要,因为不同的系列代号适用于不同的工作环境和工作要求。

CR3032中文电池规格书

第 10 页 共 20 页

编号: BL-GGS-009 版本号:

A/0

Lithium manganese dioxide battery

Specifications

Nominal Voltage Nominal Capacity Continuous standard load Operating temperature Weight

Storage characteristics

(EPV 2.0V)(Load 7.5KΩ) (At 23℃)

Voltage (V)

Voltage (V)

2.5 2.0 1.5 1.0 0.5 0 10 100 1000 10000

3.0

3.5 3.0 2.5 2.0 1.5 1.0 0 250 500 750 1000 1250 1500 1750

CR3032

A 27.3 30.0 +0.0 -0.3 2.46(Ref.) 3.2

+0.0 -0.3

3V 500(mAh) 7.5(KΩ) -20~70℃ 6.8g

Dimensions (mm)

B A B D

Temperature characteristics

Discharge characteristics

-20℃

60℃

23℃

500

750

1000

1250

1500

1750

Discharge time (h)

Discharge time (h)

Load vs. Operating voltage

3.4 Discharge depth 40%

Load vs. Capacity

电子安特Eaton GES3032AFM系列G电压电流保护器说明书

Eaton GES3032AFMEaton Series G molded case circuit breaker, EG-frame, GE, adj. thermal, fixed magnetic trip, Three-pole, 32A, 600Y/347 Vac, 85 kAIC at 240 Vac, 40 kAIC at 415 Vac, 35 kAIC at 480 Vac, 22 kAIC at 600Y/347 Vac, Line/load end caps, MetricGeneral specificationsEaton Series G complete molded case circuit breakerGES3032AFM 7821169621502.99 in 5.5 in3 in 2.15 lb Eaton Selling Policy 25-000, one (1) year from the date of installation of the Product or eighteen (18) months from the date of shipment of the Product, whichever occurs first.IEC Rated Product NameCatalog Number UPCProduct Length/Depth Product Height Product Width Product Weight WarrantyCertificationsMetric40 kAIC at 415 Vac85 kAIC at 240 Vac22 kAIC at 600Y/347 Vac35 kAIC at 480 VacEGGEComplete breakerLine and load end caps600Y/347 Vac32 AAdjustable thermal, fixed magnetic Three-pole Application of Tap Rules to Molded Case Breaker Terminals Application of Multi-Wire Terminals for Molded Case Circuit BreakersMulti-wire lugs product aidMotor protection circuit breakers product aidPower metering and monitoring with Modbus RTU product aid StrandAble terminals product aidMolded case circuit breakers providing higher levels of selective coordination product aidHigh performance operating handles for Series G circuit breakers product aidCurrent limiting molded case circuit breaker module product aid Comprehensive circuit protection for control panel applicationsCurrent limiting molded case circuit breaker module for series G, JG and CLCircuit breaker motor operators product aidPlug-in adapters for molded case circuit breakers product aidSeries G MCCB quick selectorBreaker service centersEaton's Volume 4—Circuit ProtectionMolded case circuit breakers catalogFixed and Adjustable Thermal Trip GE Moulded Case Circuit BreakerMOEM MCCB product selection guideEaton Specification Sheet - GES3032AFMNG and ND-Frame molded case circuit breakersMounting hardware Interrupt ratingFrameCircuit breaker type Circuit breaker frame type TerminalsVoltage rating Amperage RatingTrip TypeNumber of poles Application notesBrochuresCatalogsInstallation instructions Specifications and datasheetsEaton Corporation plc Eaton House30 Pembroke Road Dublin 4, Ireland © 2023 Eaton. All Rights Reserved. Eaton is a registered trademark.All other trademarks areproperty of their respectiveowners./socialmedia。

Schneider Electric XUSL4E14F031N 产品数据手册说明书

T h e i n f o r m a t i o n p r o v i d e d i n t h i s d o c u m e n t a t i o n c o n t a i n s g e n e r a l d e s c r i p t i o n s a n d /o r t e c h n i c a l c h a r a c t e r i s t i c s o f t h e p e r f o r m a n c e o f t h e p r o d u c t s c o n t a i n e d h e r e i n .T h i s d o c u m e n t a t i o n i s n o t i n t e n d e d a s a s u b s t i t u t e f o r a n d i s n o t t o b e u s e d f o r d e t e r m i n i n g s u i t a b i l i t y o r r e l i a b i l i t y o f t h e s e p r o d u c t s f o r s p e c i f i c u s e r a p p l i c a t i o n s .I t i s t h e d u t y o f a n y s u c h u s e r o r i n t e g r a t o r t o p e r f o r m t h e a p p r o p r i a t e a n d c o m p l e t e r i s k a n a l y s i s , e v a l u a t i o n a n d t e s t i n g o f t h e p r o d u c t s w i t h r e s p e c t t o t h e r e l e v a n t s p e c i f i c a p p l i c a t i o n o r u s e t h e r e o f .N e i t h e r S c h n e i d e r E l e c t r i c I n d u s t r i e s S A S n o r a n y o f i t s a f f i l i a t e s o r s u b s i d i a r i e s s h a l l b e r e s p o n s i b l e o r l i a b l e f o r m i s u s e o f t h e i n f o r m a t i o n c o n t a i n e d h e r e i n .Product data sheetCharacteristicsXUSL4E14F031NXUSL type 4 - Finger protection - Std sensingrange - Hp = 310 mm, R=14mmProduct availability: Non-Stock - Not normally stocked in distribution facilityMainRange of product Preventa Safety detection Product or component typeSafety light curtain type 4Device short name XUSL4EOutput type2 safety outputs OSSD solid-state PNP arc suppres-sion)Product specific applica-tionFor finger protection [R] Resolution 0.55 in (14 mm)[Sn] nominal sensing distance3.28…19.69 Ft (1…6 m) by cabling 0.00…9.84 ft (0…3 m) by cabling [Hp] Height protected 12.20 in (310 mm)Number of beams 30Type of start / restart Manual Automatic External Device Moni-toring (EDM)Selected by wiringComplementaryDetection system Transmitter-receiver system Response time 5.5 msKit compositionAdjustable mounting bracket(s)1 receiver(s)1 transmitter(s)1 user guide with certificate of conformity on CD-ROM [EAA] effective aperture angle 2.5 ° at 3 mEmissionIR LED 0.000037402 in (950 nm)[Us] rated supply voltage 24 V DC +/- 20 %SupplyPower supply IEC 61496-1Power supply IEC 60204-1[Ie] rated operational current 2 ACurrent consumption42 mA no-load transmitter 83 mA no-load receiver 42 mA transmitter900 mA with maximum load receiver Output current limits 0.4 A safety outputs OSSD Output voltage 24 V Output circuit type DC Maximum voltage drop <0.5 VLocal signalling 1 multi-colour LED transmitter 2 dual colour LEDs receiverElectrical connection 1 male connector M12 5 pins transmitter 1 male connector M12 8 pins receiverFunction availableTestMuting through external safety module XPSLCMUT1160LED display of operating modes and faults Marking CEMaterialAluminium casingPolycarbonate front panel Polypropylene end caps Housing colourRed RAL 3000Fixing mode By fixing bracketsNet weight 1.54 lb(US) (0.7 kg)Offer type Standard distanceEnvironmentDirectives89/336/EEC - electromagnetic compatibility2002/95/EC - RoHS directive98/37/EEC - machinery89/655/EEC - work equipment2002/96/EC - WEEE directiveProduct certifications CULusCETÜVSafety level (correctly wired)Type 4 IEC 61496-1SIL 3 IEC 61508SILCL 3 IEC 62061Category 4 EN/ISO 13849-1PL = e EN/ISO 13849-1Optical characteristic Resistance to light disturbance EN/IEC 61496-2Mission time20 year(s)Safety reliability data PFHd = 1.27E-8 1/h IEC 61508Ambient air temperature for operation-10…55 °C (14…131 °F)-4…131 °F (-20…55 °C)Ambient air temperature for storage-31…158 °F (-35…70 °C)-25…70 °C (-13…158 °F)Relative humidity0…95 % without condensationIP degree of protection IP65IP67Shock resistance10 gn 16 ms IEC 61496-1Vibration resistance0.35 +/- 0.05 mm 10…55 Hz)IEC 61496-1Ordering and shipping detailsCategory22455 - LIGHT CURTAINS - XUSLDiscount Schedule DS2GTIN00785901735632Package weight(Lbs) 1.58 kg (3.49 lb(US))Returnability YesCountry of origin ITOffer SustainabilitySustainable offer status Green Premium productREACh Regulation REACh DeclarationEU RoHS Directive Pro-active compliance (Product out of EU RoHS legal scope)EU RoHS Decla-rationToxic heavy metal free YesMercury free YesRoHS exemption information YesEnvironmental Disclosure Product Environmental ProfileCircularity Profile End Of Life InformationContractual warrantyWarranty18 monthsDimensions Drawings DimensionsBrackets DimensionsMounting and Clearance Mounting and Clearance(1)Insert(2)Bracket(3)Washer(4)Spring washer(5)NutConnections and SchemaWiring DiagramsTransmitter Connections(1)+24 Vdc(2)Configuration_0(3)0 Vdc(4)Configuration_1(5)FEReceiver Connections(1)OSSD1(2)+ 24 V(3)OSSD2(4)Configuration_A(5)K1_K2 Feeback/Restart(6)Configuration_B(7)0 Vdc(8)FEReceiver Configurations and Operating ModesAutomatic Start/RestartWithout External Device Monitoring (EDM) feedback loopWith External Device Monitoring (EDM) feedback loopManual Start/RestartWithout External Device Monitoring (EDM) feedback loop(1)RestartWith External Device Monitoring (EDM) feedback loop(1)RestartConnecting to a Safety Interface1 :Click on Download & Documents2 :Click on Application solutionsTo have all connection schematics concerning our safety module, select "download and document" and download the file "Safety lightcurtains association with safety interfaces"。

MAX3032EEUE+中文资料

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

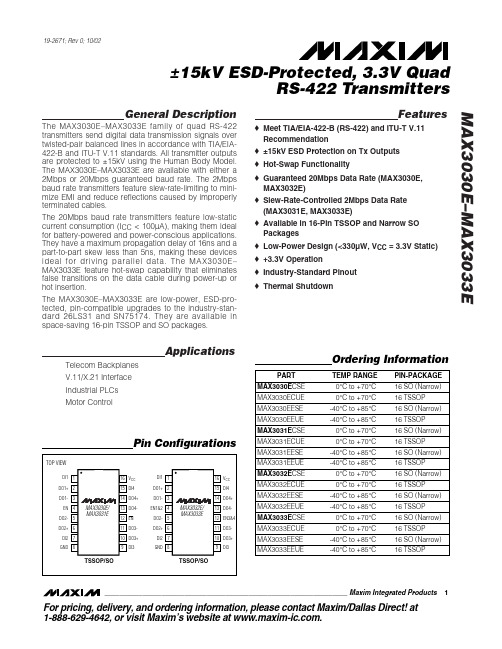

MAX3030E/ MAX3031E

16 VCC 15 DI4 14 DO4+ 13 DO412 EN 11 DO310 DO3+ 9 DI3

TSSOP/SO

DI1 1 DO1+ 2 DO1- 3 EN1&2 4 DO2- 5 DO2+ 6

DI2 7 GND 8

MAX3032E/ MAX3033E

16 VCC 15 DI4 14 DO4+ 13 DO412 EN3&4 11 DO310 DO3+ 9 DI3

Ordering Information

ቤተ መጻሕፍቲ ባይዱ

TEMP RANGE 0°C to +70°C 0°C to +70°C

-40°C to +85°C -40°C to +85°C

斯科茨曼MF22,30,41,51,61制冰机

制冰机 ............................................................................................................ 41

水系统清洁和消毒说明 .......................................................................................... 41

概述和安装............................................................................................................ 12 A. 介绍 ............................................................................................................ 12 B. 拆箱和检查 ..................................................................................................... 12 C. 选择安装位置和调整水平 ................................................................................ 13 D. 电源连接 ......................................................................................................... 14 E. 进水和排水连接 .............................................................................................. 14 F. 安装检查单 ..................................................................................................... 14 G. 安装实例 ......................................................................................................... 15

常用的机床型号含义之欧阳术创编

变换的第二种型式的型号为MB8240/2,依此类推。

CX5112A/WF

C—车床(类代号)

X—数显(通用特性代号)

51—单柱立式车床(组系代号)

12—最大车削直径为1250mm(主参数)

A—第一次重大改进(主参数)

WF—企业代号

时间:2021.02.02

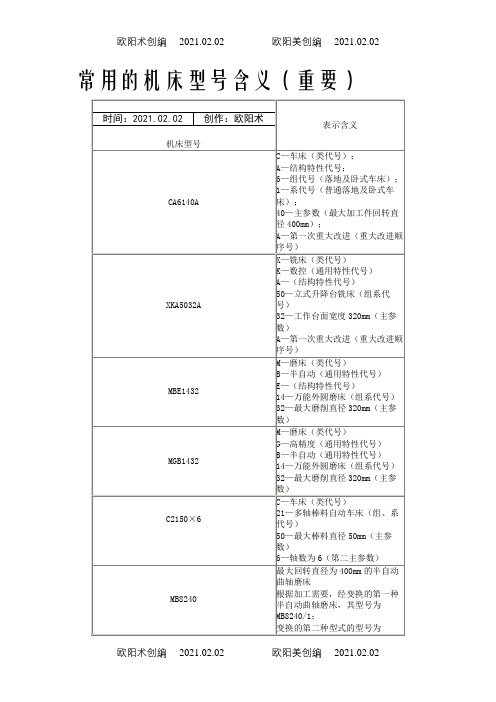

常用的机床型号含义(重要)

时间:2021.02.02

创作:欧阳术

机床型号

表示含义

CA6140A

C—车床(类代号);

A—结构特性代号;

6—组代号(落地及卧式车床);

1—系代号(普通落地及卧式车床);

40—主参数(最大加工件回转直径400mm);

A—第一次重大改进(重大改进顺序号)

XKA5032A

X—铣床(类代号)

创作:欧阳术

K—数控(通用特性代号)

A—(结构特性代号)

50—立式升降台铣床(组系代号)

32—工作台面宽度320mm(主参数)

A—第一次重大改进(重大改进顺序号)

MBE1432

M—磨(类代号)

B—半自动(通用特性代号)

E—(结构特性代号)

14—万能外圆磨床(组系代号)

32—最大磨削直径320mm(主参数)

MGB1432

M—磨床(类代号)

G—高精度(通用特性代号)

B—半自动(通用特性代号)

14—万能外圆磨床(组系代号)

32—最大磨削直径320mm(主参数)

C2150×6

C—车床(类代号)

21—多轴棒料自动车床(组、系代号)

50—最大棒料直径50mm(主参数)

6—轴数为6(第二主参数)

3ag14晶体管参数

3ag14晶体管参数3AG14晶体管参数3AG14晶体管是一种常见的晶体管型号,具有一系列特定的参数,这些参数对于了解和应用晶体管非常重要。

本文将详细介绍3AG14晶体管的各项参数及其作用。

1. 封装类型:3AG14晶体管采用TO-92封装,这是一种常见的小功率晶体管封装形式。

TO-92封装具有体积小、安装方便等特点,适用于小型电子设备的制造。

2. 极性标识:在3AG14晶体管上,通常会标有三个引脚,分别为基极(B)、发射极(E)和集电极(C)。

正确连接晶体管的引脚是确保其正常工作的前提。

3. 最大集电极电流(ICmax):ICmax是3AG14晶体管能够承受的最大集电极电流。

超过该电流值,晶体管可能会过热损坏。

因此,在应用晶体管时,要确保集电极电流不超过该参数。

4. 最大集电极-发射极电压(VCEmax):VCEmax是3AG14晶体管能够承受的最大集电极-发射极电压。

超过该电压值,晶体管可能会击穿或损坏。

因此,在应用晶体管时,要确保集电极-发射极电压不超过该参数。

5. 最大功率(Pmax):Pmax是3AG14晶体管能够承受的最大功率。

超过该功率值,晶体管可能会过热损坏。

在应用晶体管时,要根据电路的功率需求选择合适的晶体管。

6. 最大频率(fT):fT是3AG14晶体管的最大工作频率。

超过该频率值,晶体管的放大能力将大大降低。

在高频电路中,需要选择具有较高fT值的晶体管。

7. 饱和压降(VCEsat):VCEsat是3AG14晶体管在饱和区时的集电极-发射极压降。

该参数决定了晶体管在开关状态下的导通压降大小。

较小的VCEsat值能够减少功耗和发热,提高电路效率。

8. 输入电容(Cib、Cic):输入电容是指3AG14晶体管输入端的电容,分为输入基极电容(Cib)和输入集电极电容(Cic)。

输入电容越小,晶体管在高频电路中的放大能力越强。

9. 输出电容(Cob):输出电容是指3AG14晶体管输出端的电容。

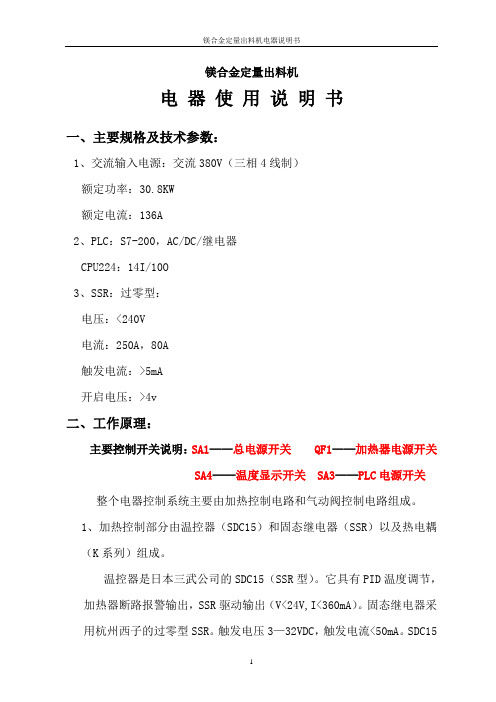

镁合金定量出料机电器说明书

镁合金定量出料机电器使用说明书一、主要规格及技术参数:1、交流输入电源:交流380V(三相4线制)额定功率:30.8KW额定电流:136A2、PLC:S7-200,AC/DC/继电器CPU224:14I/10O3、SSR:过零型:电压:<240V电流:250A,80A触发电流:>5mA开启电压:>4v二、工作原理:主要控制开关说明:SA1——总电源开关 QF1——加热器电源开关 SA4——温度显示开关 SA3——PLC电源开关整个电器控制系统主要由加热控制电路和气动阀控制电路组成。

1、加热控制部分由温控器(SDC15)和固态继电器(SSR)以及热电耦(K系列)组成。

温控器是日本三武公司的SDC15(SSR型)。

它具有PID温度调节,加热器断路报警输出,SSR驱动输出(V<24V,I<360mA)。

固态继电器采用杭州西子的过零型SSR。

触发电压3—32VDC,触发电流<50mA。

SDC15通过热电耦把加热丝的实际温度采样进来与事先设定的温度值比较后由事先设定PID值确定通过事件输出端口向SSR发出通或断的信号。

同时SDC15还设定了PV(现场温度值)低限报警值,一旦加热丝的温度低于此值就向PLC发出报警信号(PLC EM223 I1.6)。

PLC程序就会停止。

2、气动控制部分由传感器,电磁阀,PLC组成。

PLC采用西门子的S7-200,阀门位置传感器和液位传感器、旋转汽缸位置传感器共同组成反馈系统。

3、控制过程:在加热丝加热一段时间后,加热丝温度处于正常值,PLC上电,(此时坩锅内熔液已准备就绪),抽液/放液旋钮从中间位置拨到抽液位置,打开气路单向阀5YV(开始抽真空),真空泵抽管内空气同时二位五通气路换向阀1YV得电(抽液通道)打开,2YV失电(放液通道)断开,利用真空泵产生的负压将坩锅内熔液抽到定量筒中,当定量筒内镁液的液面到达指定位置S1(液面传感器)动作,此时立即关5YV(抽真空结束)关闭真空泵,同时1YV失电(抽液通道)关闭,2YV得电(放液通道)打开。

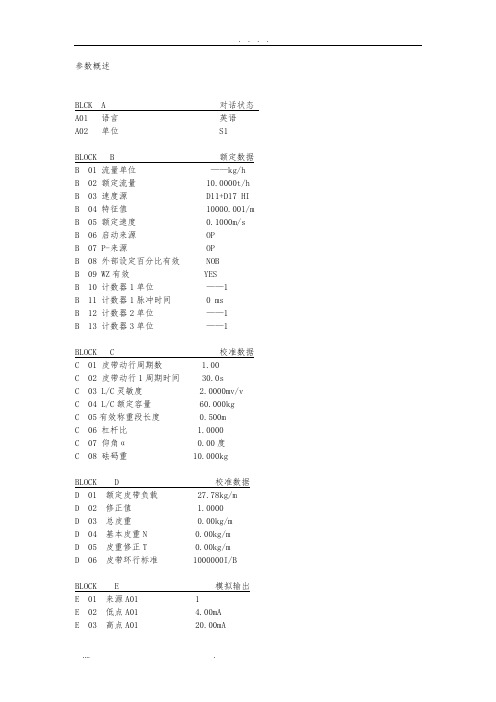

申克秤参数表(经验参数标)

参数概述BLCK A 对话状态A01 语言英语A02 单位 S1BLOCK B 额定数据B 01 流量单位——kg/h B 02 额定流量 10.0000t/h B 03 速度源 D11+D17 HI B 04 特征值 10000.001/m B 05 额定速度 0.1000m/sB 06 启动来源 OPB 07 P-来源 OPB 08 外部设定百分比有效 NOBB 09 WZ有效 YESB 10 计数器1单位——1B 11 计数器1脉冲时间 0 msB 12 计数器2单位——1B 13 计数器3单位——1BLOCK C 校准数据C 01 皮带动行周期数 1.00C 02 皮带动行1周期时间 30.0sC 03 L/C灵敏度 2.0000mv/vC 04 L/C额定容量 60.000kgC 05有效称重段长度 0.500mC 06 杠杆比 1.0000C 07 仰角α 0.00度C 08 砝码重 10.000kgBLOCK D 校准数据D 01 额定皮带负载 27.78kg/mD 02 修正值 1.0000D 03 总皮重 0.00kg/mD 04 基本皮重N 0.00kg/mD 05 皮重修正T 0.00kg/mD 06 皮带环行标准 1000000I/BBLOCK E 模拟输出E 01 来源A01 1E 02 低点A01 4.00mAE 03 高点A01 20.00mAE 04 来源A02 YE 05 低点A02 4.00mA E 06 高点A02 20.00mABLOCK F 极限值F 01 1 MIN 值 5.0%LoF 02 1 MIN 信息级别 W1(L01) F 03 1 MAN 值 120.0%Lo F 04 1 MAN 信息级别 W1(H01)F 05 Q MIN 值 60.0%QF 06 Q MIN 信息级别 W1(L02)F 07 Q MAN 值 120.0%QF 08 Q MAN 信息级别 W1(H02)F 09 V MIN 值 5.0%VF 10 V MIN 信息级别 W1(L03)F 11 V MAN 值 120.0%VF 12 V MAN 信息级别 W1(H03)F 13 待机极限 2%LoF 14 待机 W2(E05)BLOCK G 滤波器设置G 01 给料率显示 3.0sG 02 给料率模拟输出 3.0sG 03 皮带负载显示 3.0sG 04 皮带速度显示 3.0sG 05 L/C 滤波器 1.0sG 06 滤波滞后时间 3.0sBLOCK H 附加设备H 01 ZDO有效 NOH 02 ZDO极限 1.00%QBLOCK I 配料模式I 01 下降时间 3sI 02 配料修正定量 0.000kgI 03 实际匹配 0.5I 04 配料偏差 100000.0000kgI 05 输出偏差 W1(B 01) I 06 自动打印 NOI 09 配料源 OPBLOCK J 滤波器设置J 01 波特率 9600J 02 打印信息 YESJ 03 打印页长度 72BLOCK K 滤波器设置K 01 检修时间 3000hK 02 K01信息级别 W1(S 04) K 03 皮带运行时间 3000hK 04 K03信息级别 W1(S 03)BLOCK L 通用总线L 01 协议类型 MODBUSL 02 主系统暂停 10sL 03 主系统信息级别 W2(S 09)L 04 地址 IL 05 分辨率 4096L 06 字序 1:std/L;std L 07 物理接口中 *RS232L 08 波特率 *19200L 09 格式数据 *8-0-1L 10 浮点表示 SIEMMENS- KGL 11 物理接口 RS422L 12 波特率 9600L 13 格式数据 8-E-1L 14 地址 16L 15 浮点表示 IEEEL 16 配置 FIXED-1L 17 地址 16L 18 波特率 125KL 19 配置 FIXED-1L 20 字节符 low-HighL 21 字序 l:std/L.stdBLOCK M 称体监测M 01 CPD有效 NOM 02 出料平台长度 0.0%LBM 03 皮带传感器有效 NOM 04 传感器来源 DII+D16 HII M 05 BIC 有效 NOM 06 传感器长度 8.40cmM 07 传感器宽度 12.00cmM 08 传感器位移 0.00cmM 09 皮带跑偏 3.00cmM 10 M09信息级别 W1(C04)M 11 皮带变形 4.00cmM 12 M11信息级别 A(C03)M 13 打滑极限 2.00%LB M 14 打滑故障 W1(C08) M 15 皮带跑偏输出点——M 16 皮带变形输出点——M 17 滑动输出点——BLOCK N 信息级别N 01 断电 A(E01) N 02 存储错误 A(S01) N 03 输入速度 A(C02) N 04 速度错误 A(E02) N 05 皮带传感器错误 W1(E03) N 06 L/C输入 A(C01) N 07 未释放 W1(S02) N 08 L/C输入>MAX A(H04) N 09 L/C输出<MIX A(L04) N 10 模拟器有效 W2(S07) N 11 设定值限制 W1(S08)BLOCK O 信息级别O 01 控制器类型 STANDARD O 02 P——比例常数 0.02000mA% O 03 1——积分常数 1.0sO 04 滤波器控制偏差 3.0sO 05 偏差时间 20.0sO 06 最大控制偏差 5.0%O 07 偏差系数 1.0O 08 控制偏差信息级别 W1(B02)O 09 极限控制器具 W1(B03)O 10 低限值 0.00mAO 11 高限值 20.00mAO 12 控制器输出极限 0.00mAO 13 停止点 0O 14 启动周期 0.0UmlO 15 清除方式 0.0UmlO 16 零点设置 0.00mAO 17 设定值围 20.00mAO 18 存储值 NOO 19 容量类型 QconstO 20 待机 0.00mAO 21 滤波器设定值T1 0.0sO 22 滤波器设定值T2 0.0sO 23 设定/实际比较 W-XO 24 设定/实际来源 IO 25 匹配1 NOO 26 匹配2 NOBLOCK P 线性化P 01 线性化 ONP 02 线性化S1 25.00%QP 03 线性化L1 25.00%QP 04 线性化S2 50.00%QP 05 线性化L2 50.00%QP 06 线性化S3 75.00%QP 07 线性化L3 75.00%QP 08 线性化S4 100.00%QP 09 线性化L4 100.00%QP 10 线性化错误 W2(B09)BLOCK Q 数字输入Q 01 断开 DII+.D15 HI Q 02 停止配料输入点———Q 03 确认事件输入点 DII+D.II HI Q 04 容量ON输入点——Q 05 容量模式输入点——BLOCK R 数字输出R 01 报警输出点R 02 预给料ON输出点 DOI+.DO6 HI R 03 给料机输出点 DOI+.DO7 HI R 04 I-MIN 输出点 DOI+.DO1 HI R 05 I-MAX输出点 DOI+.DO2 HI R 06 Q-MIN 输出点——R 07 Q-MAX 输出点——R 08 V-MIN 输出点——R 09 V-MAX 输出点——R 10 配料有效输出点——R 11 满给料输出点——R 12 少量给料输出点——R 13 给料机ON输出点 DOI+.DO4 HI R 14 偏差输出点 DOI+.DO5 HI R 15 容量类型输出点——BLOCK S 简易维护S 01 工作站地址 1S 02 物理接口 RS232 S 03 简易服务波特率 19200 S 04 格式数据 8-0-1。

怀旧!上世纪晶体管收音机中常用的这些电子元器件你还记得吗

怀旧!上世纪晶体管收音机中常用的这些电子元器件你还记得

吗

上世纪七八十年代,收音机是那时的电子爱好者们最喜欢搞的电子制作之一。

那时不像现在有各种收音机专用集成电路,当时的爱好者们都是用三极管、电阻、电容这些分立元件来搞收音机制作的。

这里发一些当时制作收音机常用的电子元器件的图片,来回忆一下我们曾经熟悉的那些元器件吧。

▲锗高频管3AG1是当时收音机里常用的高频放大管之一。

▲3DG201是当时收音机里常用的NPN型硅三极管,其参数与金属壳封装的3DG6基本一样。

▲ 3DX204与3CX204为互补管,它们常用于OTL功放电路中。

▲2AP9、2AP10锗二极管是当时收音机里最常用的检波二极管。

▲上图所示的铝电解电容为当时收音机里常用的一种电容,其外壳为铝壳,没有绝缘层。

▲这种云母电容也是当时收音机里常用的电容。

▲单管收音机。

这款收音机只用一个锗高频管3AG1放大信号,检波电路用两个2AP9,耳机为高阻抗耳机。

MM3032G中文资料

Line Regulation

3.5

Input-output Differential Voltage (V)

Output Voltage (V)

3.0 2.5 2.0 1.5 1.0 0.5 0.0 0 2 4 6 8

Output Current (mA)

Input Voltage (V)

Load Regulation

MITSUMI CMOS Regulator MM303X Series

Pin Assignment

1 2 3 1 2 4 GND VDD VOUT CE

4

3

SC-82AB (TOP VIEW)

Pin Description

Pin No. 1 2 3 Pin name GND VDD VOUT GND Pin Voltage-Supply pin Regulator output pin No connection pin CE L 4 CE H OUTPUT OFF ON Functions

Symbol ISS Istandby VOUT/ VIN VIN VOUT/ Vopt Ilim ICE VCEH VCEL

元器件交易网

MITSUMI CMOS Regulator MM303X Series

Electrical Characteristics 2

(Ambient Temperature, Ta=25°C, VIN=VCE)

Item Operating Temperature Supply Voltage

(Ambient Temperature, Ta=25°C) Ratings -30~+85 VOUT+0.3~8 Unit °C V

moc3032规格书

moc3032规格书MOC3032是一种三端光耦隔离器,具有高电压耐受能力和快速开关速度。

它是MOC30xx系列中的一员,用于在输入和输出之间提供电气隔离和信号转换。

本规格书将详细介绍MOC3032的特点、应用和性能参数。

特点:1. 三端光耦隔离器:MOC3032由一个输入侧LED和一个输出侧光敏三极管组成,在输入和输出之间提供电气隔离。

2. 高电压耐受能力:MOC3032具有400V的高电压耐受能力,能够在高压环境下稳定工作。

3. 快速开关速度:MOC3032具有高速开关特性,能够在短时间内完成开关操作,适用于高频率应用。

4. 低功耗:MOC3032采用低功耗设计,能够有效降低能耗,提高整体效率。

应用:1. 高电压控制:MOC3032可用于高电压控制电路中,例如交流电机驱动、照明系统等,提供可靠的隔离和转换功能。

2. 电力电子:MOC3032广泛应用于电力电子设备中,如变频器、UPS系统、逆变器等,实现输入和输出之间的隔离和信号转换。

3. 工业自动化:MOC3032适用于工业自动化领域,例如PLC控制、传感器信号隔离和处理等,确保可靠的数据传输和控制。

4. 医疗设备:由于MOC3032具有高电压耐受能力和电气隔离特性,它也常被应用于医疗设备中,如心电图仪、血压监护仪等。

性能参数:1. 隔离电压:MOC3032具有高达7500VAC的隔离电压,确保输入和输出之间的电气隔离安全可靠。

2. 最大工作电压:MOC3032的最大工作电压为400V,可适应不同的电压条件。

3. 输出负载电流:MOC3032的最大输出负载电流为50mA,能够满足常见的应用需求。

4. 工作温度范围:MOC3032的工作温度范围为-40℃至+85℃,适用于各种环境条件下的工作。

5. 封装类型:MOC3032采用DIP-6封装,易于安装和布线。

总结:MOC3032是一款卓越的三端光耦隔离器,具有高电压耐受能力、快速开关速度和低功耗的特点。

moc3032规格书

moc3032规格书

MOC3032是一种光耦合器件,通常用于隔离和控制电路中的高

压和低压部分。

以下是关于MOC3032规格书的一些重要信息:

1. 电气特性,MOC3032的电气特性包括工作电压、最大正向耐压、输出器件最大电流等。

这些特性对于设计和选择适当的电路非

常重要。

2. 封装和引脚定义,MOC3032通常采用DIP-6或SMD封装,规

格书中会详细描述每个引脚的功能和连接方式,以便正确地集成到

电路中。

3. 工作温度范围,规格书中会指明MOC3032的工作温度范围,

这对于在不同环境条件下的应用至关重要。

4. 安全和认证,MOC3032通常需要符合一些安全和认证标准,

规格书中会列出相关的认证信息和安全参数。

5. 应用注意事项,规格书中通常也会包含一些关于MOC3032的

应用注意事项,比如输入端的工作电流范围、输出端的负载能力等,

这些信息对于正确使用MOC3032至关重要。

总的来说,MOC3032规格书是设计和使用该器件时的重要参考资料,可以帮助工程师了解器件的性能和特性,从而更好地应用于电路设计中。

MAX3032ECSE+T中文资料

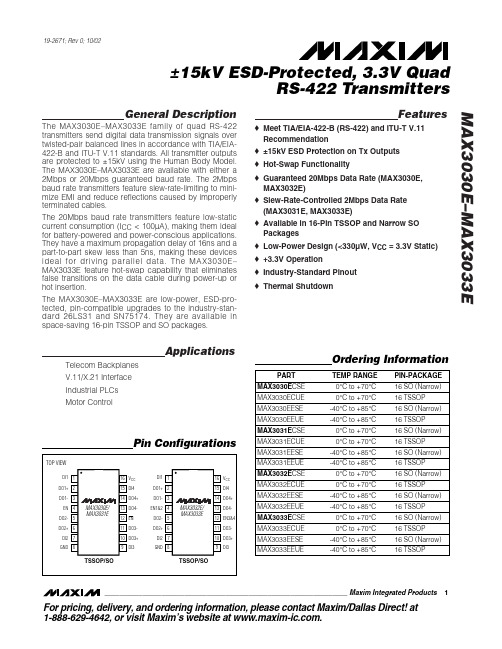

General DescriptionThe MAX3030E–MAX3033E family of quad RS-422transmitters send digital data transmission signals over twisted-pair balanced lines in accordance with TIA/EIA-422-B and ITU-T V.11 standards. All transmitter outputs are protected to ±15kV using the Human Body Model.The MAX3030E–MAX3033E are available with either a 2Mbps or 20Mbps guaranteed baud rate. The 2Mbps baud rate transmitters feature slew-rate-limiting to mini-mize EMI and reduce reflections caused by improperly terminated cables.The 20Mbps baud rate transmitters feature low-static current consumption (I CC < 100µA), making them ideal for battery-powered and power-conscious applications.They have a maximum propagation delay of 16ns and a part-to-part skew less than 5ns, making these devices ideal for driving parallel data. The MAX3030E–MAX3033E feature hot-swap capability that eliminates false transitions on the data cable during power-up or hot insertion.The MAX3030E–MAX3033E are low-power, ESD-pro-tected, pin-compatible upgrades to the industry-stan-dard 26LS31 and SN75174. They are available in space-saving 16-pin TSSOP and SO packages.ApplicationsTelecom Backplanes V.11/X.21 Interface Industrial PLCs Motor ControlFeatureso Meet TIA/EIA-422-B (RS-422) and ITU-T V.11Recommendation o ±15kV ESD Protection on Tx Outputs o Hot-Swap Functionalityo Guaranteed 20Mbps Data Rate (MAX3030E,MAX3032E)o Slew-Rate-Controlled 2Mbps Data Rate (MAX3031E, MAX3033E)o Available in 16-Pin TSSOP and Narrow SO Packages o Low-Power Design (<330µW, V CC = 3.3V Static) o +3.3V Operationo Industry-Standard Pinout o Thermal ShutdownMAX3030E–MAX3033E±15kV ESD-Protected, 3.3V QuadRS-422 Transmitters________________________________________________________________Maxim Integrated Products 1Ordering Information19-2671; Rev 0; 10/02For pricing, delivery, and ordering information,please contact Maxim/Dallas Direct!at 1-888-629-4642, or visit Maxim’s website at .Pin ConfigurationsM A X 3030E –M A X 3033E±15kV ESD-Protected, 3.3V Quad RS-422 Transmitters 2_______________________________________________________________________________________ABSOLUTE MAXIMUM RATINGSDC ELECTRICAL CHARACTERISTICSStresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.(All Voltages Are Referenced to Device Ground, Unless Otherwise Noted)V CC ........................................................................................+6V EN1&2, EN3&4, EN, EN ............................................-0.3V to +6V DI_............................................................................-0.3V to +6V DO_+, DO_- (normal condition).................-0.3V to (V CC + 0.3V)DO_+, DO_- (power-off or three-state condition).....-0.3V to +6V Driver Output Current per Pin.........................................±150mAContinuous Power Dissipation (T A = +70°C)16-Pin SO (derate 8.70mW/°C above +70°C)..............696mW 16-Pin TSSOP (derate 9.40mW/°C above +70°C).......755mW Operating Temperature RangesMAX303_EC_......................................................0°C to +70°C MAX303_EE_...................................................-40°C to +85°C Junction Temperature......................................................+150°C Storage Temperature Range.............................-65°C to +160°C Lead Temperature (soldering, 10s).................................+300°CMAX3030E–MAX3033E±15kV ESD-Protected, 3.3V QuadRS-422 TransmittersSWITCHING CHARACTERISTICS—MAX3030E, MAX3032ESWITCHING CHARACTERISTICS —MAX3031E, MAX3033EM A X 3030E –M A X 3033E±15kV ESD-Protected, 3.3V Quad RS-422 Transmitters 4_______________________________________________________________________________________SWITCHING CHARACTERISTICS —MAX3031E, MAX3033E (continued)(3V ≤V CC ≤3.6V, T A = T MIN to T MAX , unless otherwise noted. Typical values are at V CC = +3.3V and T A = +25°C.)Note 1:All currents into the device are positive; all currents out of the device are negative. All voltages are referenced to deviceground, unless otherwise noted.Note 2:∆V OD and ∆V OC are the changes in V OD and V OC , respectively, when DI changes state. Note 3:Only one output shorted at a time.Note 4:This input current is for the hot-swap enable (EN_, EN, EN ) inputs and is present until the first transition only. After the firsttransition, the input reverts to a standard high-impedance CMOS input with input current I LEAK .DIFFERENTIAL OUTPUT VOLTAGEvs. OUTPUT CURRENTOUTPUT CURRENT (mA)D I F FE R E N T I A L O U T P U T V O L T A G E (V )906030123400120OUTPUT CURRENTvs. TRANSMITTER OUTPUT LOW VOLTAGEM A X 3030E t o c 02OUTPUT LOW VOLTAGE (V)O U T P U T C U R R E N T (m A )32150100150200004OUTPUT CURRENTvs. TRANSMITTER OUTPUT HIGH VOLTAGEM A X 3030E t o c 03OUTPUT HIGH VOLTAGE (V)O U T P U T C U R R E N T (m A )321255075100125150004Typical Operating Characteristics(V CC = +3.3V and T A = +25°C, unless otherwise noted.)MAX3030E–MAX3033E±15kV ESD-Protected, 3.3V QuadRS-422 Transmitters_______________________________________________________________________________________5SUPPLY CURRENT vs. SUPPLY VOLTAGESUPPLY VOLTAGE (V)S U P P L Y C U R R E N T (µA )32120406080100004MAX3030E/MAX3032ESUPPLY CURRENT vs. DATA RATEDATA RATE (bps)S U P P L Y C U R R E N T (m A )10M1M100k10k1k5101520253000.1k100MMAX3031E/MAX3033ESUPPLY CURRENT vs. DATA RATEDATA RATE (bps)S U P P L Y C U R R E N T(m A )1M100k10k1k0.51.01.52.02.50.1k10MMAX3030E/MAX3032ESUPPLY CURRENT vs. DATA RATEDATA RATE (bps)S U P P L Y C U R R E N T (m A )10M1M100k10k1k90100110120130800.1k100MMAX3031E/MAX3033ESUPPLY CURRENT vs. DATA RATEDATA RATE (bps)S U P P L Y C U R R E N T (m A )1M100k10k1k919497100880.1k10MMAX3030EDRIVER PROPAGATION DELAY(LOW TO HIGH)MAX3030E toc0910ns/divDIFFERENTIAL OUTPUT 2V/divDI_1V/divMAX3030EDRIVER PROPAGATION DELAY(HIGH TO LOW)MAX3030E toc1010ns/divDIFFERENTIAL OUTPUT 2V/divDI_1V/divMAX3031EDRIVER PROPAGATION DELAY(LOW TO HIGH)MAX3030E toc1120ns/divDIFFERENTIAL OUTPUT 2V/divDI_1V/divMAX3031EDRIVER PROPAGATION DELAY(HIGH TO LOW)MAX3030E toc1220ns/divDIFFERENTIAL OUTPUT 2V/divDI_1V/divTypical Operating Characteristics (continued)(V CC = +3.3V and T A = +25°C, unless otherwise noted.)M A X 3030E –M A X 3033E±15kV ESD-Protected, 3.3V Quad RS-422 TransmittersENABLE RESPONSE TIMEMAX3030E toc1320ns/div ENABLE 1V/divDIFFERENTIAL OUTPUT 2V/divMAX3033E EYE DIAGRAMMAX3030E toc14100ns/divDO_+1V/divDO_-1V/divTypical Operating Characteristics (continued)(V CC = +3.3V and T A = +25°C, unless otherwise noted.)MAX3030E–MAX3033E±15kV ESD-Protected, 3.3V QuadRS-422 Transmitters_______________________________________________________________________________________7Test Circuits and Timing DiagramsTime Test CircuitFigure 4. Driver Enable/Disable Delays Test CircuitFigure 3. Differential Driver Propagation Delay and Transition WaveformM A X 3030E –M A X 3033EDetailed DescriptionThe MAX3030E –MAX3033E are high-speed quad RS-422 transmitters designed for digital data transmission over balanced lines. They are designed to meet the requirements of TIA/EIA-422-B and ITU-T V.11. The MAX3030E –MAX3033E are available in two pinouts to be compatible with both the 26LS31 and SN75174industry-standard devices. Both are offered in 20Mbps and 2Mbps baud rate. All versions feature a low-static current consumption (I CC < 100µA) that makes them ideal for battery-powered and power-conscious appli-cations. The 20Mbps version has a maximum propaga-tion delay of 16ns and a part-to-part skew less than 5ns, allowing these devices to drive parallel data. The 2Mbps version is slew-rate-limited to reduce EMI and reduce reflections caused by improperly terminated cables.Outputs have enhanced ESD protection providing ±15kV tolerance. All parts feature hot-swap capability that eliminates false transitions on the data cable dur-ing power-up or hot insertion.±15kV ESD ProtectionAs with all Maxim devices, ESD-protection structures are incorporated on all pins to protect against electro-static discharges encountered during handling and assembly. The driver outputs and receiver inputs have extra protection against static electricity. Maxim ’s engi-neers developed state-of-the-art structures to protect these pins against ESD of ±15kV without damage. The ESD structures withstand high ESD in all states: normal operation and power-down. After an ESD event, the MAX3030E –MAX3033E keep working without latchup.ESD protection can be tested in various ways; thetransmitter outputs of this product family are character-ized for protection to ±15kV using the Human Body Model. Other ESD test methodologies include IEC10004-2 Contact Discharge and IEC1000-4-2 Air-Gap Discharge (formerly IEC801-2).ESD Test ConditionsESD performance depends on a variety of conditions.Contact Maxim for a reliability report that documents test setup, test methodology, and test results.Human Body ModelFigure 8 shows the Human Body Model, and Figure 9shows the current waveform it generates when dis-charged into low impedance. This model consists of a 100pF capacitor charged to the ESD voltage of interest,which is then discharged into the test device through a 1.5k Ωresistor.±15kV ESD-Protected, 3.3V Quad RS-422 Transmitters 8_______________________________________________________________________________________Figure 7. Power-Off MeasurementsTest Circuits andTiming Diagrams (continued)Machine ModelThe Machine Model for ESD tests all pins using a 200pF storage capacitor and zero discharge resis-tance. Its objective is to emulate the stress caused by contact that occurs with handling and assembly during manufacturing. Of course, all pins require this protec-tion during manufacturing, not just inputs and outputs.Therefore, after PC board assembly, the Machine Model is less relevant to I/O ports.Hot SwapWhen circuit boards are plugged into a “hot ” back-plane, there can be disturbances to the differential sig-nal levels that could be detected by receivers connected to the transmission line. This erroneous data could cause data errors to an RS-422 system. To avoid this, the MAX3030E –MAX3033E have hot-swap capa-ble inputs.When a circuit board is plugged into a “hot ” backplane,there is an interval during which the processor is going through its power-up sequence. During this time, the processor ’s output drivers are high impedance and are unable to drive the enable inputs of the MAX3030E –MAX3033E (EN, EN , EN_) to defined logic levels.Leakage currents from these high-impedance drivers,of as much as 10µA, could cause the enable inputs of the MAX3030E –MAX3033E to drift high or low.Additionally, parasitic capacitance of the circuit board could cause capacitive coupling of the enable inputs to either G ND or V CC . These factors could cause the enable inputs of the MAX3030E –MAX3033E to drift to levels that may enable the transmitter outputs. To avoid this problem, the hot-swap input provides a method of holding the enable inputs of the MAX3030E –MAX3033E in the disabled state as V CC ramps up. This hot-swap input is able to overcome the leakage currents and par-asitic capacitances that can pull the enable inputs to the enabled state.Hot-Swap Input CircuitryIn the MAX3030E –MAX3033E, the enable inputs feature hot-swap capability. At the input there are two NMOS devices, M1 and M2 (Figure 10). When V CC is ramping up from zero, an internal 6µs timer turns on M2 and sets the SR latch, which also turns on M1. Transistors M2, a 2mA current sink, and M1, a 100µA current sink, pull EN to GND through a 5.6k Ωresistor. M2 is designed to pull the EN input to the disabled state against an external parasitic capacitance of up to 100pF that is trying to enable the EN input. After 6µs, the timer turns M2 off and M1 remains on, holding the EN input low against three-state output leakages that might enable EN. M1 remains on until an external source overcomes the required inputcurrent. At this time the SR latch resets and M1 turns off.When M1 turns off, EN reverts to a standard, high-impedance CMOS input. Whenever V CC drops below 1V, the hot-swap input is reset. The EN1&2 and EN3&4input structures are identical to the EN input. For the EN input, there is a complementary circuit employing two PMOS devices pulling the EN input to V CC .Hot-Swap Line TransientThe circuit of Figure 11 shows a typical offset termina-tion used to guarantee a greater than 200mV offset when a line is not driven. The 50pF capacitor repre-MAX3030E–MAX3033E±15kV ESD-Protected, 3.3V QuadRS-422 Transmitters_______________________________________________________________________________________9Figure 10. Simplified Structure of the Driver Enable Pin (EN)Figure 11. Differential Power-Up Glitch (Hot Swap)M A X 3030E –M A X 3033Esents the minimum parasitic capacitance that would exist in a typical application. In most cases, more capacitance exists in the system and reduces the mag-nitude of the glitch. During a “hot-swap ” event when the driver is connected to the line and is powered up, the driver must not cause the differential signal to drop below 200mV (Figures 12 and 13).Operation of Enable PinsThe MAX3030E –MAX3033E family has two enable-func-tional versions.The MAX3030E/MAX3031E are compatible with 26LS31, where the two enable signals control all four transmitters (global enable).The MAX3032E/MAX3033E are compatible with the SN75174. EN1&2 controls transmitters 1 and 2, and EN 3&4 controls transmitters 3 and 4 (dual enable).Typical ApplicationsThe MAX3030E –MAX3033E offer optimum performance when used with the MAX3094E/MAX3096 3.3V quad differential line receivers. Figure 14 shows a typical RS-422 connection for transmitting and receiving data.±15kV ESD-Protected, 3.3V Quad RS-422 Transmitters 10______________________________________________________________________________________4µs/divFigure 12. Differential Power-Up Glitch (0.1V/µs) 1.0µs/divDO_+DO_+ - DO_-DO_-V 1V/divFigure 13. Differential Power-Up Glitch (1V/µs)EN TX1TX4MODE0Active Active All transmitters active 1High-Z High-Z High-Z All transmitters disabled 0Active Active All transmitters active 1ActiveActiveAll transmitters activeTable 1. MAX3030E/MAX3031E Transmitter ControlsTable 2. MAX3032E/MAX3033E Transmitter ControlsMAX3030E–MAX3033E±15kV ESD-Protected, 3.3V QuadRS-422 Transmitters______________________________________________________________________________________11Figure 14. Typical Connection of a Quad Transmitter and Quad Receiver as a PairM A X 3030E –M A X 3033E±15kV ESD-Protected, 3.3V Quad RS-422 Transmitters 12______________________________________________________________________________________Figure 15. MAX3030E/MAX3031E Functional DiagramFigure 16. MAX3032E/MAX3033E Functional DiagramChip InformationTRANSISTOR COUNT: 1050PROCESS: BiCMOSMAX3030E–MAX3033E±15kV ESD-Protected, 3.3V QuadRS-422 Transmitters______________________________________________________________________________________13Package Information(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information,go to /packages .)M A X 3030E –M A X 3033E±15kV ESD-Protected, 3.3V Quad RS-422 Transmitters Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.14____________________Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600©2002 Maxim Integrated ProductsPrinted USAis a registered trademark of Maxim Integrated Products.Package Information (continued)(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information,go to /packages .)。

3ag14晶体管参数

3ag14晶体管参数3AG14晶体管参数3AG14晶体管是一种常用的NPN型晶体管,具有以下参数:1. 最大集电极电流(Icmax):3AG14晶体管的最大集电极电流是指在正常工作条件下,集电极电流的最大允许值。

它通常决定了晶体管的功率处理能力和热稳定性。

对于3AG14晶体管来说,其最大集电极电流一般为200mA。

2. 最大集电极-基极电压(Vceo):3AG14晶体管的最大集电极-基极电压是指在正常工作条件下,集电极和基极之间的最大允许电压。

它反映了晶体管的电压处理能力和耐压能力。

对于3AG14晶体管来说,其最大集电极-基极电压一般为30V。

3. 最大功耗(Pd):3AG14晶体管的最大功耗是指在正常工作条件下,晶体管能够承受的最大功耗。

它与最大集电极电流和最大集电极-基极电压有关。

对于3AG14晶体管来说,其最大功耗一般为625mW。

4. 最大集电极-发射极电压(Vce(sat)):3AG14晶体管的最大集电极-发射极电压是指在饱和状态下,集电极和发射极之间的电压。

饱和状态是指晶体管工作在最大集电极电流下,且集电极-基极电压低于最大集电极-基极电压的情况。

对于3AG14晶体管来说,其最大集电极-发射极电压一般为0.5V。

5. 最大直流电流增益(hfe):3AG14晶体管的最大直流电流增益是指在正常工作条件下,集电极电流变化与基极电流变化之间的比值。

它反映了晶体管的放大能力。

对于3AG14晶体管来说,其最大直流电流增益一般为100。

6. 最大频率(fT):3AG14晶体管的最大频率是指在正常工作条件下,晶体管能够正常工作的最高频率。

它与晶体管的内部结构和工作状态有关,一般与集电极电流和集电极-基极电压有关。

对于3AG14晶体管来说,其最大频率一般为100MHz。

3AG14晶体管具有200mA的最大集电极电流,30V的最大集电极-基极电压,625mW的最大功耗,0.5V的最大集电极-发射极电压,100的最大直流电流增益以及100MHz的最大频率。

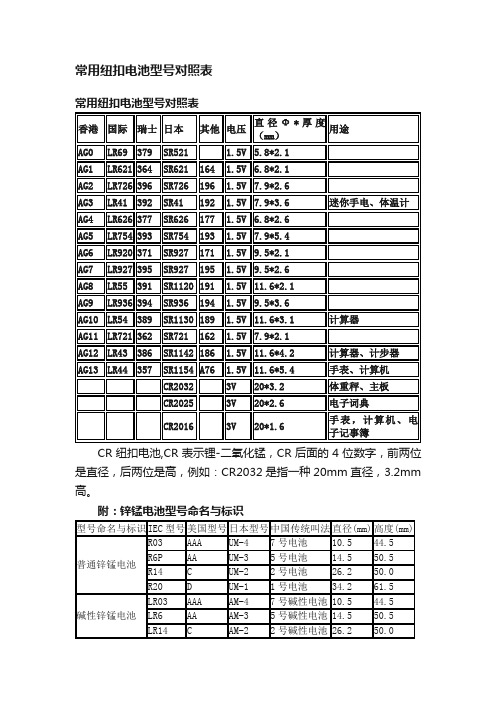

常用纽扣电池型号对照表

常用纽扣电池型号对照表常用纽扣电池型号对照表CR纽扣电池,CR表示锂-二氧化锰,CR后面的4位数字,前两位是直径,后两位是高,例如:CR2032是指一种20mm直径,3.2mm 高。

附:锌锰电池型号命名与标识说明:IEC标准中,R代表圆柱形,L代表碱性,数字代表电池的大小,数字后面的P代表高功率,这里有一个特殊规定,在表示五号普通锌锰电池时,要标识为R6P,而不是R06或者R6。

CR系列也是一种典型的干电池型号,常见的有CR2025、CR2032等。

其中C是以锂金属为负极,以二氧化锰为正极的化学电池体系,R表示电池的形状为圆柱形,如果是方形则F替代;20表示电池的直径是20mm,32代表电池的高度为3.2mm。

除了单支干电池型号命名外,还有一些组合干电池型号的标识表示如下:1、9V电池:6F22是由6个扁平形电池叠层的碳性电池;6LR61则是由6个扁平形电池叠层的碱性电池;2、AG系列:是直径很小的CR电池,分为AG1到AG13计13种,属于碱性电池;3、23A和27A:是由八个同一规格的AG电池叠层的,也称12V 扣式电池,27A大于23A。

这些组合的干电池型号往往是基于特殊电压或者容量的考虑,也只适用于一些特定领域。

由于这些干电池型号有一定的市场容量,知道它们属于干电池序列这一点,就便于把握其价格与特性。

另外还有非锌锰和锂锰系的干电池,如镁锰电池等,因为比较少见,所以对这种干电池及干电池型号介绍不多。

普通充电电池充电时间计算一、充电常识在这里,首先要说明的是,充电是使用充电电池的重要步骤。

适当合理的充电对延长电池寿命很有好处,而野蛮胡乱充电将会对电池寿命有很大影响。

上一篇曾说过,目前的锂电池基本都是根据各个产品单独封装,互不通用的,因此各个产品也提供各自的充电设备,互不通用,在使用时只要遵循各自的说明书使用即可。

所以本篇对电池充电的介绍主要是指镍镉电池和镍氢电池。

对镍隔电池和镍氢电池充电有两种方式,就是我们大家所熟知的“快充”和“慢充”。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

FEATURES• The device is an ideal choice for low noise, high-gain amplification NF = 0.6 dB TYP. @ V CE = 2 V, I C = 6 mA, f = 2.0 GHz• Maximum stable power gain: MSG = 20.5 dB TYP. @ V CE = 2 V, I C = 15 mA, f = 2.0 GHz • SiGe HBT technology (UHS3) adopted: f max = 110 GHz • 4-pin lead-less minimold (M14, 1208 package)ORDERING INFORMATIONPart Number Order Number PackageQuantitySupplying FormNESG3032M14NESG3032M14-A50 pcs (Non reel) NESG3032M14-T3 NESG3032M14-T3-A4-pin lead-less minimold (M14, 1208 package)(Pb-Free)10 kpcs/reel• 8 mm wide embossed taping• Pin 1 (Collector), Pin 4 (Emitter) face the perforation side of the tapeRemark To order evaluation samples, contact your nearby sales office.Unit sample quantity is 50 pcs.ABSOLUTE MAXIMUM RATINGS (T A = +25°C)Parameter Symbol Ratings UnitCollector to Base Voltage V CBO 12.0 V Collector to Emitter Voltage V CEO 4.3 V Emitter to Base Voltage V EBO 1.5 V Collector Current I C 35 mA Total Power Dissipation P totNote150 mWJunction Temperature T j 150 °C Storage TemperatureT stg−65 to +150°CNote Mounted on 1.08 cm 2 × 1.0 mm (t) glass epoxy PWBCaution Observe precautions when handling because these devices are sensitive to electrostatic discharge.NPN SILICON GERMANIUM RF TRANSISTORNESG3032M14NPN SiGe RF TRANSISTOR FORLOW NOISE, HIGH-GAIN AMPLIFICATION4-PIN LEAD-LESS MINIMOLD (M14, 1208 PACKAGE)Document No. PU10575EJ01V0DS (1st edition) Date Published July 2005 CP(K)© NEC Compound Semiconductor Devices, Ltd. 2005ELECTRICAL CHARACTERISTICS (T A = +25°C)Parameter Symbol Test Conditions MIN. TYP. MAX. UnitDC CharacteristicsCollector Cut-off Current I CBO V CB = 5 V, I E = 0 mA − − 100 nA Emitter Cut-off Current I EBO V EB = 1 V, I C = 0 mA − − 100 nA DC Current Gain h FENote 1V CE = 2 V, I C = 6 mA 220 300 380 − RF CharacteristicsInsertion Power Gain ⏐S 21e ⏐2V CE = 2 V, I C = 15 mA, f = 2.0 GHz 15.0 17.5−dBNoise Figure NF V CE = 2 V, I C = 6 mA, f = 2.0 GHz,Z S = Z Sopt , Z L = Z Lopt− 0.60 0.85 dB Associated GainG a V CE = 2 V, I C = 6 mA, f = 2.0 GHz, Z S = Z Sopt , Z L = Z Lopt− 17.5−dBReverse Transfer Capacitance C reNote 2V CB = 2 V, I E = 0 mA, f = 1 MHz − 0.15 0.25 pF Maximum Stable Power GainMSGNote3V CE = 2 V, I C = 15 mA, f = 2.0 GHz 17.520.5−dBGain 1 dB Compression Output Power P O (1 dB) V CE = 3 V, I C (set) = 20 mA,f = 2.0 GHz, Z S = Z Sopt , Z L = Z Lopt − 12.5 − dBm 3rd Order Intermodulation Distortion Output Intercept PointOIP 3V CE = 3 V, I C (set) = 20 mA,f = 2.0 GHz, Z S = Z Sopt , Z L = Z Lopt−24.0−dBmNotes 1. Pulse measurement: PW ≤ 350 µs, Duty Cycle ≤ 2% 2. Collector to base capacitance when the emitter grounded 3. MSG =h FE CLASSIFICATIONRank FB Marking zN h FE Value220 to 380S-PARAMETERSS-parameters/Noise parameters are provided on the NEC Compound Semiconductor Devices Web site in a form (S2P) that enables direct import to a microwave circuit simulator without keyboard input.Click here to download S-parameters. [RF and Microwave] → [Device Parameters]URL /S 21S 12Data Sheet PU10575EJ01V0DS2PACKAGE DIMENSIONS4-PIN LEAD-LESS MINIMOLD (M14, 1208 PACKAGE) (UNIT: mm)PIN CONNECTIONS1. Collector2. Emitter3. Base4. NC (Connected with Pin 2)Data Sheet PU10575EJ01V0DS 3When the product(s) listed in this document is subject to any applicable import or export control laws and regulation of the authority having competent jurisdiction, such product(s) shall not be imported or exported without obtaining the import or export license.M8E 00. 4 - 0110The information in this document is current as of July, 2005. The information is subject to changewithout notice. For actual design-in, refer to the latest publications of NEC's data sheets or data books, etc., for the most up-to-date specifications of NEC semiconductor products. Not all products and/or types are available in every country. Please check with an NEC sales representative for availability and additional information.No part of this document may be copied or reproduced in any form or by any means without prior written consent of NEC. NEC assumes no responsibility for any errors that may appear in this document.NEC does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC semiconductor products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC or others.Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of customer's equipment shall be done under the full responsibility of customer. NEC assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.While NEC endeavours to enhance the quality, reliability and safety of NEC semiconductor products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects in NEC semiconductor products, customers must incorporate sufficient safety measures in their design, such as redundancy, fire-containment, and anti-failure features.NEC semiconductor products are classified into the following three quality grades:"Standard", "Special" and "Specific". The "Specific" quality grade applies only to semiconductor products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of a semiconductor product depend on its quality grade, as indicated below. Customers must check the quality grade of each semiconductor product before using it in a particular application."Standard":Computers, office equipment, communications equipment, test and measurement equipment, audioand visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots"Special":Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disastersystems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)"Specific":Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, lifesupport systems and medical equipment for life support, etc.The quality grade of NEC semiconductor products is "Standard" unless otherwise expressly specified in NEC's data sheets or data books, etc. If customers wish to use NEC semiconductor products in applications not intended by NEC, they must contact an NEC sales representative in advance to determine NEC's willingness to support a given application.(Note)(1)"NEC" as used in this statement means NEC Corporation, NEC Compound Semiconductor Devices, Ltd.and also includes its majority-owned subsidiaries.(2)"NEC semiconductor products" means any semiconductor product developed or manufactured by or forNEC (as defined above).••••••Data Sheet PU10575EJ01V0DS4NEC Compound Semiconductor Devices Hong Kong Limited E-mail: ncsd-hk@ (sales, technical and general)Hong Kong Head Office T aipei Branch OfficeKorea Branch OfficeTEL: +852-3107-7303TEL: +886-2-8712-0478TEL: +82-2-558-2120FAX: +852-3107-7309 FAX: +886-2-2545-3859FAX: +82-2-558-5209NEC Electronics (Europe) GmbH http://www.ee.nec.de/TEL: +49-211-6503-0 FAX: +49-211-6503-1327California Eastern Laboratories, Inc. / TEL: +1-408-988-3500 FAX: +1-408-988-02790504NEC Compound Semiconductor Devices, Ltd. / E-mail: salesinfo@ (sales and general) techinfo@ (technical)Sales Division TEL: +81-44-435-1573 FAX: +81-44-435-1579For further information, please contact4590 Patrick Henry DriveSanta Clara, CA 95054-1817Telephone: (408) 919-2500Facsimile: (408) 988-0279Subject: Compliance with EU DirectivesCEL certifies, to its knowledge, that semiconductor and laser products detailed below are compliant with the requirements of European Union (EU) Directive 2002/95/EC Restriction on Use of Hazardous Substances in electrical and electronic equipment (RoHS) and the requirements of EU Directive 2003/11/EC Restriction on Penta and Octa BDE.CEL Pb-free products have the same base part number with a suffix added. The suffix –A indicates that the device is Pb-free. The –AZ suffix is used to designate devices containing Pb which are exempted from the requirement of RoHS directive (*). In all cases the devices have Pb-free terminals. All devices with these suffixes meet the requirements of the RoHS directive.This status is based on CEL’s understanding of the EU Directives and knowledge of the materials that go into its products as of the date of disclosure of this information.Restricted Substanceper RoHS Concentration Limit per RoHS(values are not yet fixed)Concentration containedin CEL devices-A -AZLead (Pb) < 1000 PPMNot Detected (*) Mercury < 1000 PPM Not DetectedCadmium < 100 PPM Not Detected Hexavalent Chromium < 1000 PPM Not DetectedPBB < 1000 PPM Not DetectedPBDE < 1000 PPM Not DetectedIf you should have any additional questions regarding our devices and compliance to environmental standards, please do not hesitate to contact your local representative.Important Information and Disclaimer: Information provided by CEL on its website or in other communications concerting the substance content of its products represents knowledge and belief as of the date that it is provided. CEL bases its knowledge and belief on information provided by third parties and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. CEL has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. CEL and CEL suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.In no event shall CEL’s liability arising out of such information exceed the total purchase price of the CEL part(s) at issue sold by CEL to customer on an annual basis.See CEL Terms and Conditions for additional clarification of warranties and liability.。