BZX85B91中文资料

HT85XXX中文资料

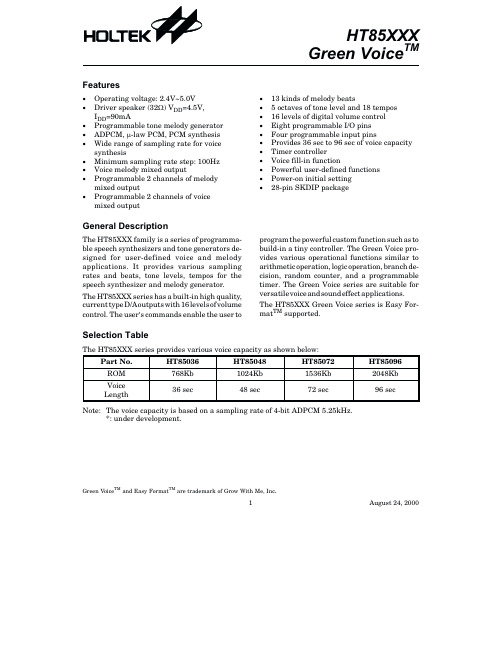

HT85XXX Green VoiceTM

Features

· Operating voltage: 2.4V~5.0V · Driver speaker (32W) VDD=4.5V,

IDD=90mA · Programmable tone melody generator · ADPCM, m-law PCM, PCM synthesis · Wide range of sampling rate for voice

Supply Voltage.................................-0.3V to 6V Input Voltage .................VSS-0.3V to VDD+0.3V

Storage Temperature.................-50°C to 125°C Operating Temperature ..............-20°C to 70°C

21, 22 VSS

¾

¾

Negative power supply, ground

23

OSC

I

¾

Built-in RC oscillator An oscillator resistor is connected between OSC and VSS

Absolute Maximum Ratings

Pin No.

Pin Name

I/O

Internal Connection

Description

1, 2, 8, 24~28

NC

¾

¾

No connection

3, 4, 5

PP0, PDA, PP1

BZX84C16LT1G中文资料

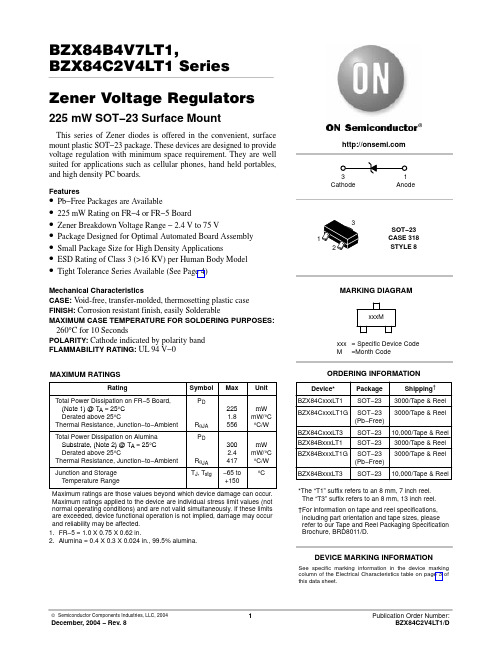

BZX84B4V7LT1,BZX84C2V4LT1 Series Zener Voltage Regulators225 mW SOT−23 Surface MountThis series of Zener diodes is offered in the convenient, surface mount plastic SOT−23 package. These devices are designed to provide voltage regulation with minimum space requirement. They are well suited for applications such as cellular phones, hand held portables,and high density PC boards.Features•Pb−Free Packages are Available•225 mW Rating on FR−4 or FR−5 Board•Zener Breakdown V oltage Range − 2.4 V to 75 V•Package Designed for Optimal Automated Board Assembly •Small Package Size for High Density Applications•ESD Rating of Class 3 (>16 KV) per Human Body Model •Tight Tolerance Series Available (See Page 4)Mechanical CharacteristicsCASE: V oid-free, transfer-molded, thermosetting plastic case FINISH: Corrosion resistant finish, easily SolderableMAXIMUM CASE TEMPERATURE FOR SOLDERING PURPOSES:260°C for 10 SecondsPOLARITY: Cathode indicated by polarity band FLAMMABILITY RATING: UL 94 V−0MAXIMUM RATINGSMaximum ratings are those values beyond which device damage can occur.Maximum ratings applied to the device are individual stress limit values (not normal operating conditions) and are not valid simultaneously. If these limits are exceeded, device functional operation is not implied, damage may occur and reliability may be affected.1.FR−5 = 1.0 X 0.75 X 0.62 in.2.Alumina = 0.4 X 0.3 X 0.024 in., 99.5% alumina.See specific marking information in the device marking column of the Electrical Characteristics table on page 3 of this data sheet.DEVICE MARKING INFORMATION(Pinout: 1-Anode, 2-No Connection, 3-Cathode)(T A = 25°Cunless otherwise noted, V F = 0.95 V Max. @ I F = 10 mA)ELECTRICAL CHARACTERISTICS − BZX84CxxxLT1 SERIES (STANDARD TOLERANCE) (Pinout: 1-Anode, 2-No Connection, 3-Cathode)(T A = 25°C unless otherwise noted, V F = 0.90 V Max. @ I F = 10 mA) (Devices listed in bold, italic are ON Semiconductor Preferred devices.)Z*The “G” suffix indicates Pb−Free package available.ELECTRICAL CHARACTERISTICS − BZX84BxxxL (Tight Tolerance Series)(Pinout: 1-Anode, 2-No Connection, 3-Cathode)(T A = 25°C unless otherwise noted, V F = 0.90 V Max. @ I F = 10 mA)Z*The “G” suffix indicates Pb−Free package available.V Z , T E M P E R A T U R E C O E F F I C I E N T (m V /C )°θV Z , NOMINAL ZENER VOLTAGE (V)− 3− 2012345678Figure 1. Temperature Coefficients (Temperature Range −55°C to +150°C)V Z , T E M P E R A T U R E C O E F F I C I E N T (m V /C )°θ100101V Z , NOMINAL ZENER VOLTAGE (V)Figure 2. Temperature Coefficients (Temperature Range −55°C to +150°C)V Z , NOMINAL ZENER VOLTAGEFigure 3. Effect of Zener Voltage onZener ImpedanceZ Z T , D Y N A M I C I M P E D A N C E ()Ω1000100101V F , FORWARD VOLTAGE (V)Figure 4. Typical Forward VoltageI F , F O R W A R D C U R R E N T (m A )1000100101C , C A P A C I T A N C E (p F )V Z , NOMINAL ZENER VOLTAGE (V)Figure 5. Typical Capacitance 1000100101V Z , ZENER VOLTAGE (V)1001010.10.01I Z , Z E N ER C U R R E N T (m A )V Z , ZENER VOLTAGE (V)1001010.10.01I R , L E A K A G E C U R R E N T (A )µV Z , NOMINAL ZENER VOLTAGE (V)Figure 6. Typical Leakage Current10001001010.10.010.0010.00010.00001I Z , Z E N E R C U R R E N T (m A )Figure 7. Zener Voltage versus Zener Current(V Z Up to 12 V)Figure 8. Zener Voltage versus Zener Current(12 V to 91 V)PACKAGE DIMENSIONSSOT−23TO−236AB CASE 318−09ISSUE AK*For additional information on our Pb−Free strategy and solderingdetails, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.SOLDERING FOOTPRINT*ǒmm inchesǓSCALE 10:1ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

BZX84B6V2LT1G中文资料

BZX84B4V7LT1,BZX84C2V4LT1 Series Zener Voltage Regulators225 mW SOT−23 Surface MountThis series of Zener diodes is offered in the convenient, surface mount plastic SOT−23 package. These devices are designed to provide voltage regulation with minimum space requirement. They are well suited for applications such as cellular phones, hand held portables,and high density PC boards.Features•Pb−Free Packages are Available•225 mW Rating on FR−4 or FR−5 Board•Zener Breakdown V oltage Range − 2.4 V to 75 V•Package Designed for Optimal Automated Board Assembly •Small Package Size for High Density Applications•ESD Rating of Class 3 (>16 KV) per Human Body Model •Tight Tolerance Series Available (See Page 4)Mechanical CharacteristicsCASE: V oid-free, transfer-molded, thermosetting plastic case FINISH: Corrosion resistant finish, easily SolderableMAXIMUM CASE TEMPERATURE FOR SOLDERING PURPOSES:260°C for 10 SecondsPOLARITY: Cathode indicated by polarity band FLAMMABILITY RATING: UL 94 V−0MAXIMUM RATINGSMaximum ratings are those values beyond which device damage can occur.Maximum ratings applied to the device are individual stress limit values (not normal operating conditions) and are not valid simultaneously. If these limits are exceeded, device functional operation is not implied, damage may occur and reliability may be affected.1.FR−5 = 1.0 X 0.75 X 0.62 in.2.Alumina = 0.4 X 0.3 X 0.024 in., 99.5% alumina.See specific marking information in the device marking column of the Electrical Characteristics table on page 3 of this data sheet.DEVICE MARKING INFORMATION(Pinout: 1-Anode, 2-No Connection, 3-Cathode)(T A = 25°Cunless otherwise noted, V F = 0.95 V Max. @ I F = 10 mA)ELECTRICAL CHARACTERISTICS − BZX84CxxxLT1 SERIES (STANDARD TOLERANCE) (Pinout: 1-Anode, 2-No Connection, 3-Cathode)(T A = 25°C unless otherwise noted, V F = 0.90 V Max. @ I F = 10 mA) (Devices listed in bold, italic are ON Semiconductor Preferred devices.)Z*The “G” suffix indicates Pb−Free package available.ELECTRICAL CHARACTERISTICS − BZX84BxxxL (Tight Tolerance Series)(Pinout: 1-Anode, 2-No Connection, 3-Cathode)(T A = 25°C unless otherwise noted, V F = 0.90 V Max. @ I F = 10 mA)Z*The “G” suffix indicates Pb−Free package available.V Z , T E M P E R A T U R E C O E F F I C I E N T (m V /C )°θV Z , NOMINAL ZENER VOLTAGE (V)− 3− 2012345678Figure 1. Temperature Coefficients (Temperature Range −55°C to +150°C)V Z , T E M P E R A T U R E C O E F F I C I E N T (m V /C )°θ100101V Z , NOMINAL ZENER VOLTAGE (V)Figure 2. Temperature Coefficients (Temperature Range −55°C to +150°C)V Z , NOMINAL ZENER VOLTAGEFigure 3. Effect of Zener Voltage onZener ImpedanceZ Z T , D Y N A M I C I M P E D A N C E ()Ω1000100101V F , FORWARD VOLTAGE (V)Figure 4. Typical Forward VoltageI F , F O R W A R D C U R R E N T (m A )1000100101C , C A P A C I T A N C E (p F )V Z , NOMINAL ZENER VOLTAGE (V)Figure 5. Typical Capacitance 1000100101V Z , ZENER VOLTAGE (V)1001010.10.01I Z , Z E N ER C U R R E N T (m A )V Z , ZENER VOLTAGE (V)1001010.10.01I R , L E A K A G E C U R R E N T (A )µV Z , NOMINAL ZENER VOLTAGE (V)Figure 6. Typical Leakage Current10001001010.10.010.0010.00010.00001I Z , Z E N E R C U R R E N T (m A )Figure 7. Zener Voltage versus Zener Current(V Z Up to 12 V)Figure 8. Zener Voltage versus Zener Current(12 V to 91 V)PACKAGE DIMENSIONSSOT−23TO−236AB CASE 318−09ISSUE AK*For additional information on our Pb−Free strategy and solderingdetails, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.SOLDERING FOOTPRINT*ǒmm inchesǓSCALE 10:1ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

XC4085XL资料

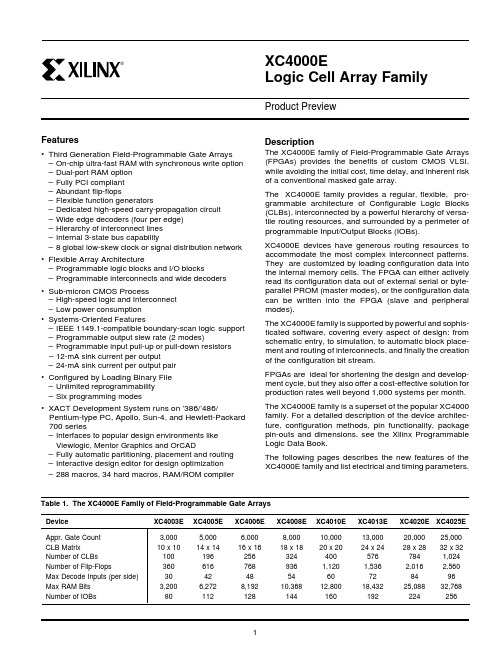

XC4000ELogic Cell Array Family®Product PreviewDeviceXC4003E XC4005E XC4006E XC4008E XC4010E XC4013E XC4020E XC4025E Appr. Gate Count 3,0005,0006,0008,00010,00013,00020,00025,000CLB Matrix10 x 1014 x 1416 x 1618 x 1820 x 2024 x 2428 x 2832 x 32Number of CLBs 1001962563244005767841,024Number of Flip-Flops3606167689361,1201,5362,0162,560Max Decode Inputs (per side)3042485460728496Max RAM Bits 3,2006,2728,19210,36812,80018,43225,08832,768Number of IOBs80112128144160192224256Table 1. The XC4000E Family of Field-Programmable Gate Arrays DescriptionThe XC4000E family of Field-Programmable Gate Arrays (FPGAs) provides the benefits of custom CMOS VLSI,while avoiding the initial cost, time delay, and inherent risk of a conventional masked gate array.The XC4000E family provides a regular, flexible, pro-grammable architecture of Configurable Logic Blocks (CLBs), interconnected by a powerful hierarchy of versa-tile routing resources, and surrounded by a perimeter of programmable Input/Output Blocks (IOBs).XC4000E devices have generous routing resources to accommodate the most complex interconnect patterns.They are customized by loading configuration data into the internal memory cells. The FPGA can either actively read its configuration data out of external serial or byte-parallel PROM (master modes), or the configuration data can be written into the FPGA (slave and peripheral modes).The XC4000E family is supported by powerful and sophis-ticated software, covering every aspect of design: from schematic entry, to simulation, to automatic block place-ment and routing of interconnects, and finally the creation of the configuration bit stream.FPGAs are ideal for shortening the design and develop-ment cycle, but they also offer a cost-effective solution for production rates well beyond 1,000 systems per month.The XC4000E family is a superset of the popular XC4000family. For a detailed description of the device architec-ture, configuration methods, pin functionality, package pin-outs and dimensions, see the Xilinx Programmable Logic Data Book.The following pages describes the new features of the XC4000E family and list electrical and timing parameters.Features•Third Generation Field-Programmable Gate Arrays –On-chip ultra-fast RAM with synchronous write option –Dual-port RAM option –Fully PCI compliant –Abundant flip-flops–Flexible function generators–Dedicated high-speed carry-propagation circuit –Wide edge decoders (four per edge)–Hierarchy of interconnect lines –Internal 3-state bus capability–8 global low-skew clock or signal distribution network •Flexible Array Architecture–Programmable logic blocks and I/O blocks–Programmable interconnects and wide decoders •Sub-micron CMOS Process–High-speed logic and Interconnect –Low power consumption •Systems-Oriented Features–IEEE 1149.1-compatible boundary-scan logic support –Programmable output slew rate (2 modes)–Programmable input pull-up or pull-down resistors –12-mA sink current per output –24-mA sink current per output pair •Configured by Loading Binary File –Unlimited reprogrammability –Six programming modes•XACT Development System runs on ’386/’486/Pentium-type PC, Apollo, Sun-4, and Hewlett-Packard 700 series–Interfaces to popular design environments like Viewlogic, Mentor Graphics and OrCAD–Fully automatic partitioning, placement and routing –Interactive design editor for design optimization –288 macros, 34 hard macros, RAM/ROM compilerXC4000E Logic Cell Array FamilyIOB Clock EnableThe two flip-flops in each IOB have a common clock enable input,which through configuration can be activated indi-vidually for the input or output flip-flop or both. This clock enable operates exactly like the EC pin on the XC4000CLB. This makes the IOBs more versatile, and avoids the need for clock gating.Output DriversThe output pull-up structure can be globally configured to be either a TTL-like totem-pole (n-channel pull-up transis-tor, pulling to a voltage one threshold below Vcc, just like XC4000) or to be CMOS (p-channel pull-up transistor pulling to Vcc). Also, the configurable pull-up resistor in XC4000E is a p-channel transistor that pulls to Vcc,whereas in XC4000 it is an n-channel transistor that pulls to a voltage one threshold below Vcc.Input ThresholdsThe input thresholds can be globally configured for either TTL ( 1.2 V threshold) or CMOS ( 2.5 V threshold ), just like XC2000 and XC3000 inputs. Note that the two global adjustments of input threshold and output level are inde-pendent of each other.Global Signal Access to LogicThere is additional access from global clocks to the F and G function generator inputs.Mode-Pin Pull-Up ResistorsDuring configuration, the three mode pins, M0, M1, and M2, have weak pull-up resistors. For the most popular configuration mode, Slave Serial, the mode pins can thus be left unconnected.For user mode, the three mode inputs can individually be configured with or without weak pull-up or pull-down resistorsThe PROGRAM input pin has a permanent weak pull-up.Soft StartupLike XC3000A, the XC4000E family has “Soft Startup”.When the configuration process is finished and the device starts up in user mode, the first activation of the outputs is automatically slew-rate limited. This avoids the potential ground bounce when all outputs are turned on simulta-neously. After start-up, the slew rate of the individual outputs is, as in the XC4000 family, determined by the individual configuration option.XC4000E compared to XC4000Any XC4000E device is a 100% compatible superset of the equivalent XC4000 device, not only functionally, but also electrically, and in pin-out and configuration bitstream.The XC4000E devices have the following additional func-tions, most of which are invoked through options in the configuration bitstream:Synchronous RAMThe two RAMs in any CLB can be changed to synchronous write operation. In this synchronous mode, the internal write operation is controlled by the same clock that drives the flip-flops. The clock polarity is programmable for the RAM (both F and G function generators together), but is independent of the chosen flip-flop polarity. Address,Data, and WE inputs are latched by this rising or falling clock edge, and a short internal write pulse is generated right after the clock edge. This self-timed write operation is thus effectively edge-triggered.The read operation is not affected by this change to a synchronous write.Dual-Port RAMA separate option converts the 16 x 2 RAM in any CLB into a 16 x 1 dual-port RAM. In this mode, any operation that writes into the F-RAM, automatically also writes into the G-RAM, using the F address. The G-address can, therefore,not be used to write into the G-RAM.The CLB can thus be used as an asymmetrical dual-port RAM, with F being the read address for the F-RAM and the write address for both F- and G-RAM, while G is the read address for the G-RAM. Note that F and G can still be independent read addresses, as they are in XC4000. The two RAMs together have one read/write port using the F address, and one read-only port using the G address.Each CLB can be configured as function generators either asynchronous single-port, synchronous single-port, or synchronous dual-port.H-Function GeneratorIn XC4000E, the H function generator is more versatile. Its inputs can come not only from the F and G function generators but also from up to three control input lines.The H function generator can be totally or partially inde-pendent of the other two function generators.IOB Switching Characteristic GuidelinesTesting of the switching parameters is modeled after testing methods specified by MIL-M-38510/605. All devices are 100%functionally tested. Since many internal timing parameters cannot be measured directly, they are derived from benchmark timing patterns. The following guidelines reflect worst-case values over the recommended operating conditions. For more detailed, more precise, and more up-to-date timing information, use the values provided by the XACT timing calculator and used in the simulator.* Timing is based on the XC4005E. For other devices see XACT timing calculator.** See preceding pageNotes: 1.Timing is measured at pin threshold, with 50 pF external capacitive loads (incl. test fixture). Slew rate limited outputrise/fall times are approximately two times longer than fast output rise/fall times. For the effect of capacitive loads on ground bounce, see pages 8-8 through 8-10.2.Voltage levels of unused (bonded and unbonded) pads must be valid logic levels. Each can be configured with the internal pull-up or pull-down resistor or alternatively configured as a driven output or be driven from an external source.3.Input pad setup times and hold times are specified with respect to the internal clock (IK). To calculate system setup time,subtract clock delay (clock pad to IK) from the specified input pad setup time value, but do not subtract below zero.Negative hold time means that the delay in the input data is adequate for the external system hold time to be zero,provided the input clock uses the Global signal distribution from pad to IK.XC4000E Logic Cell Array FamilyCLB Switching Characteristic GuidelinesTesting of the switching parameters is modeled after testing methods specified by MIL-M-38510/605. All devices are 100% functionally tested. Since many internal timing parameters cannot be measured directly, they are derived from benchmark timing patterns. The following guidelines reflect worst-case values over the recommended operating conditions. For more detailed, more precise, and more up-to-date timing information, use the values provided by the XACT timing calculator and used in the simulator.*Timing is based on the XC4005E. For other devices see XACT timing calculator.。

BZV85-C5V6,113;BZV85-C5V6,133;BZV85-C8V2,113;BZV85-C8V2,133;BZV85-C27,113;中文规格书,Datasheet资料

Product data sheet Supersedes data of 1996 Apr 261999 May 11NXP Semiconductors Product data sheetVoltage regulator diodesBZV85 seriesFEATURES•Total power dissipation: max. 1.3 W •Tolerance series: approx. ±5%•Working voltage range:nom. 3.6 to 75 V (E24 range)•Non-repetitive peak reverse power dissipation: max. 60 W.APPLICATIONS •Stabilization purposes.DESCRIPTIONMedium-power voltage regulator diodes in hermetically sealed leaded glass SOD66 (DO-41) packages. The diodes are available in the normalized E24 approx. ±5% tolerance range. The series consists of 33 types with nominal working voltages from 3.6 to 75 V (BZV85-C3V6 to BZV85-C75).LIMITING VALUESIn accordance with the Absolute Maximum Rating System (IEC 134).Notes1.Device mounted on a printed circuit-board with 1 cm 2 copper area per lead.2.If the leads are kept at T tp = 55 °C at 4 mm from body.ELECTRICAL CHARACTERISTICS Total seriesT j = 25 °C unless otherwise specified.SYMBOL PARAMETERCONDITIONSMIN.MAX.UNIT I F continuous forward current −500mAI ZSMnon-repetitive peak reverse currentt p = 100 μs; square wave;T j = 25 °C prior to surge; see Fig.3see Table “Per type”t p = 10 ms; half sinewave; T j = 25 °C prior to surgesee Table “Per type”P tottotal power dissipationT amb = 25 °C; lead length 10 mm; note 1−1W note 2− 1.3W P ZSM non-repetitive peak reverse power dissipationt p = 100 μs; square wave; T j = 25 °C prior to surge−60W T stg storage temperature −65+200°C T j junction temperature−200°CSYMBOL PARAMETERCONDITIONSMAX.UNIT V Fforward voltageI F = 50 mA; see Fig.41V1999 May 113NXP SemiconductorsProduct data sheetVoltage regulator diodesBZV85 seriesPer typeT j = 25 °C unless otherwise specified.BZV85-CXXXWORKING VOLTAGE V Z (V)at I ZtestDIFFERENTIAL RESISTANCE r dif (Ω)at I Ztest TEMP. COEFF.S Z (mV/K)at I Ztestsee Figs 5 and 6TEST CURRENT I Ztest (mA)DIODE CAP.C d (pF)at f = 1 MHz; V R = 0 VREVERSECURRENT at REVERSE VOLTAGE NON-REPETITIVEPEAK REVERSE CURRENTI ZSM I R (μA)V R (V)at t p = 100 μs;T amb = 25 °C at t p = 10 ms;T amb = 25 °C MIN.MAX.MAX.MIN.MAX.MAX.MAX.MAX. (A)MAX. (mA)3V6 3.4 3.815−3.5−1.06045050 1.08.0 2 0003V9 3.7 4.115−3.5−1.06045010 1.08.0 1 9504V3 4.0 4.613−2.70504505 1.08.0 1 8504V7 4.4 5.013−2.0+0.7453003 1.08.0 1 8005V1 4.8 5.410−0.5+2.2453003 2.08.0 1 7505V6 5.2 6.070 2.7453002 2.08.0 1 7006V2 5.8 6.640.6 3.6352002 3.07.0 1 6206V86.47.2 3.5 1.3 4.3352002 4.07.0 1 5507V57.07.93 2.5 5.5351501 4.5 5.0 1 5008V27.78.75 3.1 6.1251500.7 5.0 5.0 1 4009V18.59.65 3.87.2251500.7 6.5 4.0 1 340109.410.68 4.78.525900.27.0 4.0 1 2001110.411.610 5.39.320850.27.7 3.0 1 1001211.412.710 6.310.820850.28.4 3.0 1 0001312.414.1107.412.020800.29.1 3.09001513.815.6158.913.615750.0510.5 2.57601615.317.11510.715.415750.0511.0 1.757001816.819.12011.817.115700.0512.5 1.756002018.821.22413.619.110600.0514.0 1.755402220.823.32516.622.110600.0515.5 1.55002422.825.63018.324.310550.0517 1.54502725.128.94020.127.58500.0519 1.24003028.032.04522.432.08500.05211.2380/1999 May 114NXP SemiconductorsProduct data sheetVoltage regulator diodesBZV85 series3331.035.04524.835.08450.0523 1.03503634.038.05027.239.98450.05250.93203937.041.06029.643.06450.05270.82964340.046.07534.048.36400.05300.72704744.050.010037.452.54400.05330.62465148.054.012540.856.54400.05360.52265652.060.015046.863.04400.05390.42086258.066.017552.272.54350.05430.41866864.072.020060.581.04350.05480.351717570.080.022566.588.04350.05530.3161BZV85-CXXXWORKING VOLTAGE V Z (V)at I Ztest DIFFERENTIAL RESISTANCE r dif (Ω)at I Ztest TEMP. COEFF.S Z (mV/K)at I Ztestsee Figs 5 and 6TEST CURRENT I Ztest (mA)DIODE CAP.C d (pF)at f = 1 MHz; V R = 0 VREVERSECURRENT at REVERSE VOLTAGE NON-REPETITIVEPEAK REVERSE CURRENTI ZSM I R (μA)V R (V)at t p = 100 μs;T amb = 25 °C at t p = 10 ms;T amb = 25 °C MIN.MAX.MAX.MIN.MAX.MAX.MAX.MAX. (A)MAX. (mA)/Voltage regulator diodes BZV85 seriesTHERMAL CHARACTERISTICSSYMBOL PARAMETER CONDITIONS VALUE UNIT R th j-tp thermal resistance from junction to tie-point lead length 4 mm; see Fig.2110K/W R th j-a thermal resistance from junction to ambient lead length10 mm; note 1175K/W Note1.Device mounted on a printed circuit-board with 1 cm2 copper area per lead.GRAPHICAL DATAVoltage regulator diodes BZV85 seriesVoltage regulator diodes BZV85 seriesPACKAGE OUTLINEHermetically sealed glass package; axial leaded; 2 leads SOD66Voltage regulator diodesBZV85 seriesDATA SHEET STATUSNotes1.Please consult the most recently issued document before initiating or completing a design.2.The product status of device(s) described in this document may have changed since this document was publishedand may differ in case of multiple devices. The latest product status information is available on the Internet at URL . DOCUMENT STATUS (1)PRODUCT STATUS (2)DEFINITIONObjective data sheet Development This document contains data from the objective specification for product development.Preliminary data sheet Qualification This document contains data from the preliminary specification. Product data sheet ProductionThis document contains the product specification.DISCLAIMERSGeneral ⎯ Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties,expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.Right to make changes ⎯ NXP Semiconductors reserves the right to make changes to informationpublished in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.Suitability for use ⎯ NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment orapplications and therefore such inclusion and/or use is at the customer’s own risk.Applications ⎯ Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.Limiting values ⎯ Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) may cause permanent damage to the device. Limiting values are stress ratings only and operation of the device at these or any other conditionsabove those given in the Characteristics sections of this document is not implied. Exposure to limiting values for extended periods may affect device reliability.Terms and conditions of sale ⎯ NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at /profile/terms, including those pertaining to warranty, intellectual property rightsinfringement and limitation of liability, unless explicitly otherwise agreed to in writing by NXP Semiconductors. In case of any inconsistency or conflict between information in this document and such terms and conditions, the latter will prevail.No offer to sell or license ⎯ Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.Export control ⎯ This document as well as the item(s) described herein may be subject to export controlregulations. Export might require a prior authorization from national authorities.Quick reference data ⎯ The Quick reference data is an extract of the product data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding.NXP SemiconductorsCustomer notificationThis data sheet was changed to reflect the new company name NXP Semiconductors. No changes were made to the content, except for the legal definitions and disclaimers.Contact informationFor additional information please visit: For sales offices addresses send e-mail to: salesaddresses@© NXP B.V. 2009All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent- or other industrial or intellectual property rights.Printed in The Netherlands 115002/00/02/pp9 Date of release: 1999 May 11 Document order number: 9397 750 05929分销商库存信息:NXPBZV85-C5V6,113BZV85-C5V6,133BZV85-C8V2,113 BZV85-C8V2,133BZV85-C27,113BZV85-C27,133 BZV85-C16,113BZV85-C16,133BZV85-C15,113 BZV85-C6V2,113BZV85-C6V2,133BZV85-C36,113 BZV85-C12,113BZV85-C12,133BZV85-C33,113 BZV85-C30,133。

BZX84C16V中文资料

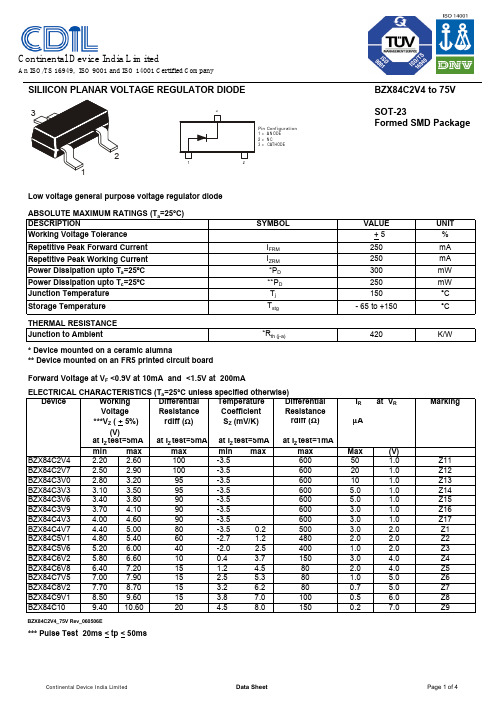

SILIICON PLANAR VOLTAGE REGULATOR DIODEBZX84C2V4 to 75V SOT-23Formed SMD PackageLow voltage general purpose voltage regulator diode ABSOLUTE MAXIMUM RATINGS (T a =25°C)UNIT %Repetitive Peak Forward Current mA Repetitive Peak Working Current mA mW mW °C °CTHERMAL RESISTANCE K/W* Device mounted on a ceramic alumna** Device mounted on an FR5 printed circuit boardELECTRICAL CHARACTERISTICS (T a =25°C unless specified otherwise) Device Temperature DifferentialI R at V RMarkingCoefficient ResistanceS Z (mV/K)rdiff (Ω)µAat I Z test=5mA at I Z test=1mAmin max min max max Max (V)BZX84C2V4 2.20 2.60 -3.560050 1.0Z11BZX84C2V72.50 2.90 -3.560020 1.0Z12BZX84C3V0 2.80 3.20 -3.560010 1.0Z13BZX84C3V3 3.10 3.50 -3.5600 5.0 1.0Z14BZX84C3V6 3.40 3.80 -3.5600 5.0 1.0Z15BZX84C3V9 3.70 4.10-3.56003.0 1.0Z16BZX84C4V34.00 4.60 -3.5600 3.0 1.0Z17BZX84C4V7 4.40 5.00 -3.5 0.2500 3.0 2.0Z1BZX84C5V1 4.80 5.40 -2.7 1.2480 2.0 2.0Z2BZX84C5V6 5.20 6.00 -2.0 2.5400 1.0 2.0Z3BZX84C6V2 5.80 6.60 0.4 3.7150 3.0 4.0Z4BZX84C6V8 6.407.20 1.2 4.580 2.0 4.0Z5BZX84C7V57.007.90 2.5 5.380 1.0 5.0Z6BZX84C8V27.708.70 3.2 6.2800.7 5.0Z7BZX84C9V18.509.60 3.8 7.01000.5 6.0Z8BZX84C109.4010.604.5 8.01500.27.0Z9BZX84C2V4_75V Rev_060506E*** Pulse Test 20ms < tp < 50ms1515152060401015909090801001009595 + 5VALUE max I ZRM Storage Temperature T stg Junction to Ambient*R th (j-a)DESCRIPTIONI FRM Working Voltage Tolerance Power Dissipation upto T a =25ºC SYMBOL *P D ***V Z ( + 5%)(V)at I Z test=5mA Resistance rdiff (Ω)at I Z test=5mA250420300- 65 to +150250Forward Voltage at V F <0.9V at 10mA and <1.5V at 200mAVoltage 150250Differential Working Power Dissipation upto T c =25ºC **P D Junction Temperature T j Pin Configuration1 = A N ODE2 = N C3 =CATHODE12Continental Device India LimitedAn ISO/TS 16949, ISO 9001 and ISO 14001 Certified CompanySILIICON PLANAR VOLTAGE REGULATOR DIODEBZX84C2V4 to 75V SOT-23Formed SMD PackageELECTRICAL CHARACTERISTICS (T a =25°C unless specified otherwise) Device Temperature DifferentialI R at V RMarkingCoefficientResistanceS Z (mV/K)rdiff (Ω)µAat I Z test=5mAat I Z test=1mA min max min max max Max (V)BZX84C1110.4011.60 5.4 9.01500.18Y1BZX84C1211.4012.70 6.0 101500.18Y2BZX84C1312.4014.10 7.0 111700.18Y3BZX84C1513.8015.60 9.2 132000.0510.5Y4BZX84C1615.3017.10 10.4 142000.0511.2Y5BZX84C1816.8019.10 12.4 162250.0512.6Y6BZX84C2018.8021.20 14.4 182250.0514.0Y7BZX84C2220.8023.30 16.4 202500.0515.4Y8BZX84C2422.8025.60 18.4 222500.0516.8Y9at I Z Test=2mA at I Z Test=0.5mABZX84C2725.1028.90 21.4 25.33000.0518.9Y10BZX84C3028.0032.00 24.4 29.43000.0521.0Y11BZX84C3331.0035.00 27.4 33.43250.0523.1Y12BZX84C3634.0038.00 30.4 37.43500.0525.2Y13BZX84C3937.0041.00 33.4 41.23500.0527.3Y14BZX84C4340.0046.00 37.6 46.63750.0530.1Y15BZX84C4744.0050.00 42.0 51.83750.0532.9Y16BZX84C5148.0054.00 46.6 57.24000.0535.7Y17BZX84C5652.0060.00 52.2 63.84250.0539.2Y18BZX84C6258.0066.00 58.8 71.64500.0543.4Y19BZX84C6864.0072.00 65.6 79.84750.0547.6Y20BZX84C7570.0079.0073.4 88.65000.0552.5Y21BZX84C2V4_75V Rev_060506E*** Pulse Test 20ms < tp < 50ms2002152402551301501701808080908025303070at I Z test=5mA at I Z test=5mA max at I Z test=2mAat I Z Test=2mA4045555520Resistance ***V Z ( + 5%)rdiff (Ω)(V)Forward Voltage at V F <0.9V at 10mA and <1.5V at 200mAWorking Differential Voltage Pin Configuration1 = A N ODE2 = N C3 =CATHODE12BZX84C2V4 to 75V SOT-23Formed SMD PackageSOT-23 Package Reel InformationReel specification for W" Packing (13" reel)BZX84C2V4_75V Rev_060506ESOT-23 Formed SMD PackageTape Specification for SOT-23 Surface Mount DeviceS O T -23 T &R3K /reel 10K /reel136 g m /3K p c s 415 g m /10K p c s3" x 7.5" x 7.5"9" x 9" x 9"13" x 13" x 0.5"12 K 51 K 10 K17" x 15" x 13.5"19" x 19" x 19"17" x 15" x 13.5"192 K 408 K 300 K12 k g s 28 k g s 16 k g sPACKAGEN e t W e i g h t /Q t y DetailsS T A N D A R D PACKI N N E R C A R T O N B O XQ t y O U T E R C A R T O N B O XQ t y G r W t SizeSizePacking Detail±0.0114.47.9 – 10.9T R A I L E RF I X I N GT A P EL E A D E R9.2±0.5MAXNOTES:No. of Devices8mm Tape Size of Reel 330 mm (13")10,000 Pcs 8mm Tape Size of Reel 180 mm (7")3,000 Pcs1.The bandolier of 330 mm reel contains at least 10,000 devices.2.The bandolier of 180 mm reel contains at least 3,000 devices.3.No more than 0.5% missing devices / reel. 50 empty compartments for 330 mm reel.15 empty compartments for 180 mm reel.4.Three consecutive empty places might be found provided this gap is followed by 6 consecutive devices.5.The carrier tape (leader) starts with at least 75 empty positions (equivalent to 330 mm).In order to fix the carrier tape a self adhesive tape of 20 to 50 mm is applied. At the end of the bandolier at least 40 empty positions (equivalent to 160 mm) are there.3.15Customer Notes BZX84C2V4 to 75VSOT-23Formed SMD Package1. CDIL Semiconductor Devices are RoHS compliant, customers are requested to pleasedispose as per prevailing Environmental Legislation of their Country.2. In Europe, please dispose as per EU Directive 2002/96/EC on Waste Electrical andElectronic Equipment (WEEE).BZX84C2V4_75V Rev_060506E DisclaimerThe product information and the selection guides facilitate selection of the CDIL's Semiconductor Device(s)best suited for application in your product(s)as per your requirement.It is recommended that you completely review our Data Sheet(s)so as to confirm that the Device(s)meet functionality parameters for your application.The information furnished in the Data Sheet and on the CDIL Web Site/CD are believed to be accurate and reliable.CDIL however,does not assume responsibility for inaccuracies or incomplete information.Furthermore,CDIL does not assume liability whatsoever,arising out of the application or use of any CDIL product;neither does it convey any license under its patent rights nor rights of others. These products are not designed for use in life saving/support appliances or systems.CDIL customers selling these products(either as individual Semiconductor Devices or incorporated in their end products),in any life saving/support appliances or systems or applications do so at their own risk and CDIL will not be responsible for any damages resulting from such sale(s).CDIL strives for continuous improvement and reserves the right to change the specifications of its products without prior notice.CDIL is a registered Trademark ofContinental Device India LimitedC-120 Naraina Industrial Area, New Delhi 110 028, India.Telephone + 91-11-2579 6150, 4141 1112 Fax + 91-11-2579 5290, 4141 1119email@ 。

EA218EI6BTAV中文资料

P R E L I M I N A R Y I N F O R M A T I O Ning modeCharacteristics Continue9Automatically selects the opti-mized mode for forwarding9Allows manual frame forwarding mode selection override Multi-Media ready with QoS supports9Four frame transmission priority queuesComplies with IEEE 802.1 Bridge Standard9Assigns one unique MAC Address for each portVLAN ID Tagging & Stripping 9Auto padding if necessary after stripping Automatic retry frame transmission 9Transmit collision 9Transmit buffer under-runAutomatic receive filtering for bad frames for Store & Forward Mode 9Bad FCS9Short events or frames under 64bytes9Long events or frames over 1518/1522 bytesAutomatic statistic collection for RMONBlock Diagram –EA218E 8-Port Ethernet Access ControllerTypical Application :9 A 16-port Ethernet Switch with 4-Fast EthernetSystem Block Diagram --16-Port Ethernet Switch with 4 Fast Ethernet Up-Links1.PIN ASSIGNMENT1.1Logic SymbolT_MODE P_CS#P_ADS#P_RWC P_BS16#P_RDY#P_INT P_RST#P_CLK P_A[11:1]Tm_RXD Tm_RXC Tm_TXC Tm_TXEN Tm_TXD Tm_LPBK Tm_FD Tm_COL Tm_CRS Tm_LNKS_IRDY S_TABT#S_REQ#S_GNT#S_CLKL_CLK1.2Pin Assignment (Preliminary)Note:#Active low signalInput Input signalIn-ST Input signal with Schmitt-TriggerOutput Output signal (Tri-State driver)Out-OD Output signal with Open-Drain driverI/O-TS Input & Output signal with Tri-State driverI/O-OD Input & Output signal with Open-Drain driver5VT Input with 5V ToleranceOutput signal with programmable polarity.Input or output pins with weak internal pull up resistors (50k to 100k Ohms each)These pins are reserved for internal use only. They should be left unconnected.Pin No(s).Symbol TypeMaxI OL/ I OH Name and FunctionsManagement Bus InterfaceJ25,K26,L24,K25,L26,M24,L25,M26,N24,M25,P24,N26,N25,R24,P26, P25P_D[15:0]TTL I/O-TS (5VT)16mA Management Bus – Data Bit [15:0]C26,D24,C25,E24,D26,D25,F24,E26,E25,G24, F26P_A[11:1]TTL In (5VT)Management Bus – Address Bit [11:1] F25P_ADS#TTL In (5VT)Management Bus – Address StrobeH25P_RWC TTL In (5VT)Management Bus – Read/Write Control J24P_RDY#TTL Out-OD16mA Management Bus – Data ReadyG25P_BS16#TTL Out-OD16mA Management Bus – 16 bit Data BusG26P_CS#TTL In (5VT)Management Bus – Chip SelectH26P_INT CMOS Output4mA Management Bus – Interrupt Request J26P_RST#TTL In-ST (5VT)Management Bus – Master ResetK24P_CLK TTL In (5VT)Management Bus – Bus Clock XpressFlow Bus InterfaceC23,A23,B22,C22,A22S_D[31:27] /P_C[0:4]CMOS I/O-TS12mA XpressFlow Bus – Data Bit [31:27] or Manage-ment Bus Interface Configuration bit [0:4]B21,D20,C21,A21,B20,A20,C20,B19,A19,C19,B18,A18,B17,C18,A17,D17,B16,C17,A16,B15,A15,C16,B14,D15,A14,C15,B13S_D[26:0]CMOS I/O-TS12mA XpressFlow Bus – Data Bit [26:0]B12S_MSGEN#CMOS I/O-TS12mA XpressFlow Bus – Message EnvelopeA12S_EOF#CMOS I/O-TS12mA XpressFlow Bus – End of FrameC14S_IRDY CMOS I/O-TS12mA XpressFlow Bus – Initiator ReadyC13S_TABT#CMOS I/O-OD12mA XpressFlow Bus – Target AbortB23S_HPREQ#CMOS I/O-OD12mA XpressFlow Bus – High Priority Request A24S_REQ#CMOS Output4mA XpressFlow Bus – Bus Request to SC201 B24S_GNT#CMOS Input XpressFlow Bus – Bus Grant from SC201 A13S_OVLD#CMOS Input XpressFlow Bus – Bus OverloadD13S_CLK CMOS Input XpressFlow Bus – ClockPin No(s).Symbol Type Name and FunctionsControl Buffer Memory InterfaceM4,N2,L3,M1,M2,L1,K3,L2,K4,K1,J3,K2,J1,J2,H3,H1,H2,G3,G1,G2,F1,F3,F2,E1,E3,E2,D1,D3,D2,C1,C2,B1L_D[31:0]TTL I/O-TS 8mA Local Memory Bus – Data Bit [31:0]A6,B6,C8,A7,D8,D7,C9,A8,B8,A9,C10,B9,D10,A10,C11,B10,A11L_A[18:2]CMOS Output8mA Local Memory Bus – Address Bit [17:2]C7L_A[19] /L_OE[3]#CMOS Output8mA Local Memory Bus – Address Bit [19] or MemoryRead Chip Select [3]D5,A5,A3L_OE[2:0]#CMOS Output2mA Local Memory Read Chip Select [2:0]D7,E4,B5,C4L_WE[3:0]#CMOS Output2mA Local Memory Write Chip Select [3:0]C6,B4,A4,C5L_BWE[3:0]#CMOS Output8mA Local Memory Byte Write Enable, Byte [3:0] B3L_ADSC#CMOS Output8mA Local Memory Controller Address StatusG4L_CLK CMOS Output8mA Local Memory Clock inputEthernet Access Port cont. [7:0]AF20,AE17,AD12,AD9, AC2,T25T[7:2]_RXD TTL In (5VT) Receive Data – (one for each 10Mbps Serial In-terface Port)AC25,AF6T[1:0]_RXD TTL In (5VT)AD19,AD16,AE14,AF10,AC2 1U24T[7:2]_RXC TTL In (5VT) Receive Clock – (one for each 10Mbps Serial In-terface Port)AC24,AE7T[1:0]_RXC TTL In (5VT)AF18,AD14,AE12,AF8, W2,AA25,AE22,AD1T[7:0]_TXC TTL In (5VT)Transmit Clock – (one for each 10Mbps Serial In-terface Port)AE19,AF15,AF12,AD8, W1,AA24T[7:2]_TXEN CMOS Out 4mA Transmit Enable – (one for each 10Mbps SerialInterface Port)AF22,AF2T[1:0]_TXEN CMOS OutputAE20,AF16,AF13,AE10, Y1,W25T[7:2]_TXD CMOS Out 4mA Transmit Data – (one for each 10Mbps Serial In-terface Port)AF23,AE4T[1:0]_TXD CMOS OutputAD18,AD15,AE13,AF9, Y2,Y26T[7:2]_LPBK CMOS Out 2mA Loop Back Enable – (one for each 10Mbps SerialInterface Port)AE23,AF3T[1:0]_LPBK CMOS OutputAF19,AE16,AD11,AE9, V3,AA26T[7:2]_FD CMOS Out 2mA Full Duplex Mode – (one for each 10Mbps SerialInterface Port)AD21,AE3T[1:0]_FD CMOS OutputAD17,AE15,AF11,AE8, V1,AB26T[7:2]_COL TTL In (5VT) Collision Detected – (one for each 10Mbps SerialInterface Port)AD20,AC23T[1:0]_COL TTL In (5VT)AE18,AD13,AD10,AD7, U3,AB24,T[7:2]_CRS TTL In (5VT) Carrier Sense – (one for each 10Mbps Serial In-terface Port)AF21,AD2T[1:0]_CRS TTL In (5VT)AF17,AF14,AE11,AF7, V2,AB25,T[7:2]_LNK TTL In (5VT) Link Status – (one for each 10Mbps Serial Inter-face Port)AE21,AB3T[1:0]_LNK TTL In (5VT)Pin No(s).Symbol TypeMaxI OL/ I OH Name & FunctionsTest FacilityA25T_MODE CMOS I/O-TS 2mA Test Pin – Set Test Mode upon Reset, and pro-vides test status output during test modeN1,M3,P2,P1,N3,R2,P3,R1,T2R3,T1,R4,U2,T3,U1,U4T_D[15:10] CMOS Output4mA Test Pins – Reserved for internal use onlyPin No(s).Symbol Type Name & FunctionsPower PinsD6,D11,D16,D21,F4,F23,L4,L23,T4,T23,AA4,AA23AC6,AC11,AC16,AC21VDD Power+3.3 Volt DC SupplyA1,A2,A26,B2,B25,B26,C3,C24,D4,D9,D14,D19,D23,H4,J23,N4,P23,V4,W23,AC4,AC8,AC13,AC18,AC23,AD3,AD24,AE1,AE2,AE25,AF1, AF25VSS Power Ground1.3Pin Reference Table: (352 pin BGA)Pin #Signal Name Pin #Signal Name Pin #Signal Name Pin #Signal Name Pin #Signal NameF26P_A[1]C18S_D[13]E3L_D[7] V1T3_COL T2T_D[7] G24P_A[2]B17S_D[14]E1L_D[8] V3T3_FD R1T_D[8] E25P_A[3]A18S_D[15]F2L_D[9] Y2T3_LPBK P3T_D[9] E26P_A[4]B18S_D[16]F3L_D[10] Y1T3_TXD R2T_D[10] F24P_A[5]C19S_D[17]F1L_D[11] W1T3_TXEN N3T_D[11] D25P_A[6]A19S_D[18]G2L_D[12] W2T3_TXC P1T_D[12] D26P_A[7]B19S_D[19]G1L_D[13] AC1T3_RXC P2T_D[13] E24P_A[8]C20S_D[20]G3L_D[14] AC2T3_RXD M3T_D[14] C25P_A[9]A20S_D[21]H2L_D[15] AF7T4_LNK N1T_D[15] D24P_A[10]B20S_D[22]H1L_D[16] AD7T4_CRSC26P_A[11]A21S_D[23]H3L_D[17] AE8T4_COL D6VDDF25P_ADS#C21S_D[24]J2L_D[18] AE9T4_FD D11VDDG26P_CS#D20S_D[25]J1L_D[19] AF9T4_LPBK D16VDDH25P_RWC B21S_D[26]K2L_D[20] AE10T4_TXD D21VDDG25P_BS16#A22S_D[27] / P_C[4]J3L_D[21] AD8T4_TXEN F4VDDJ24P_RDY#C22S_D[28] / P_C[3]K1L_D[22] AF8T4_TXC F23VDDJ26P_RST#B22S_D[29] / P_C[2]K4L_D[23] AF10T4_RXC L4VDDH26P_INT A23S_D[30] / P_C[1]L2L_D[24] AD9T4_RXD L23VDDK24P_CLK C23S_D[31] / P_C[0]K3L_D[25] AE11T5_LNK T4VDDP25P_D[0]L1L_D[26] AD10T5_CRS T23VDDP26P_D[1]A11L_A[2]M2L_D[27] AF11T5_COL AA4VDDR24P_D[2]B10L_A[3]M1L_D[28] AD11T5_FD AA23VDDN25P_D[3]C11L_A[4]L3L_D[29] AE13T5_LPBK AC6VDDN26P_D[4]A10L_A[5]N2L_D[30] AF13T5_TXD AC11VDDP24P_D[5]D10L_A[6]M4L_D[31] AF12T5_TXEN AC16VDDM25P_D[6]B9L_A[7]AE12T5_TXC AC21VDDN24P_D[7]C10L_A[8]AB3T0_LNK AE14T5_RXC A1GNDM26P_D[8]A9L_A[9]AD2T0_CRS AD12T5_RXD A2GNDL25P_D[9]B8L_A[10]AC3T0_COL AF14T6_LNK A26GNDM24P_D[10]A8L_A[11]AE3T0_FD AD13T6_CRS B2GNDL26P_D[11]C9L_A[12]AF3T0_LPBK AE15T6_COL B25GNDK25P_D[12]B7L_A[13]AE4T0_TXD AE16T6_FD B26GNDL24P_D[13]D8L_A[14]AF2T0_TXEN AD15T6_LPBK C3GNDK26P_D[14]A7L_A[15]AD1T0_TXC AF16T6_TXD C24GNDJ25P_D[15]C8L_A[16]AE7T0_RXC AF15T6_TXEN D4GNDB6L_A[17]AF6T0_RXD AD14T6_TXC D9GNDD13S_CLK A6L_A[18]AE21T1_LNK AD16T6_RXC D14GNDA13S_OVLD#C7L_A[19] / OE[3]#AF21T1_CRS AE17T6_RXD D19GNDB23S_HPREQ#D5L_OE[2]#AD20T1_COL AF17T7_LNK D23GNDA24S_REQ#A5L_OE[1]#AD21T1_FD AE18T7_CRS H4GNDB24S_GNT#A3L_OE[0]AE23T1_LPBK AD17T7_COL J23GNDB12S_MSGEN#D7L_WE[3]#AF23T1_TXD AF19T7_FD N4GNDA12S_EOF#E4L_WE[2]#AF22T1_TXEN AD18T7_LPBK P23GNDC14S_IRDY B5L_WE[1]#AE22T1_TXC AE20T7_TXD V4GNDC13S_TABT#C4L_WE[0]#AC24T1_RXC AE19T7_TXEN W23GNDB13S_D[0]C6L_BWE[3]#AC25T1_RXD AF18T7_TXC AC4GNDC15S_D[1]B4L_BWE[2]#AB25T2_LNK AD19T7_RXC AC8GNDA14S_D[2]A4L_BWE[1]#AB24T2_CRS AF20T7_RXD AC13GNDD15S_D[3]C5L_BWE[0]#AB26T2_COL AC18GNDB14S_D[4]B3L_ADSC#AA26T2_FD A25T_MODE AC23GNDC16S_D[5]G4L_CLK Y26T2_LPBK AD3GNDA15S_D[6]B1L_D[0] W25T2_TXD U4T_D[0] AD24GNDB15S_D[7]C2L_D[1] AA24T2_TXEN U1T_D[1] AE1GNDA16S_D[8]C1L_D[2] AA25T2_TXC T3T_D[2] AE2GNDC17S_D[9]D2L_D[3] U24T2_RXC U2T_D[3] AE25GNDB16S_D[10]D3L_D[4] T25T2_RXD R4T_D[4] AF1GNDD17S_D[11]D1L_D[5] V2T3_LNK T1T_D[5] AF25GNDA17S_D[12]E2L_D[6] U3T3_CRS R3T_D[6]Note: Output signals with programmable polarity.Input or output pins with weak internal pull up resistors (50k to 100k Ohms each)These pins are reserved for internal use only. They should be left unconnected.2.FUNCTIONAL DESCRIPTION2.1Local Memory (Local Buffer Memory) InterfaceUses industry standard Synchronous Burst Mode SRAM up to 1M bytes932k x 32, 64k x 32, 128k x 32, or 256k x 32Provides separate Read and Write Chip Selects ( L_OE[3:0]# and L_WE[3:0]# ) for each memory chipSupports back to back Read or Write operations across memory chips2.1.1Pin DescriptionSymbol Type Name and FunctionsL_D[31:0] TTL I/O-TS Local Memory Data Bus Bit [31:0]– a 32-bit synchronous data bus.L_A[18:2]CMOS Output Local Memory Address Bus Bit [18:2] – Bit [18:2] of a synchronous address bus. Thememory address is sampled when L_CS# is enabled and L_ADSC# is asserted.L_A[19] / L_OE[3]#CMOS Output Local Memory Address Bus Bit [19] or Local Memory Read Chip Select [3]– De-pends on memory configuration, this pin can be used as the Local Memory Address Bit[19] or as the Local Memory Read Chip Select [3].L_OE[2:0]#CMOS Output Local Memory Read Chip Select [2:0] – allows up to read one of the 4 banks of mem-ory.L_WE[3:0]#CMOS Output Local Memory Write Chip Select [3:0]– allows up to write one of the 4 banks of mem-ory.L_BWE[3:0]#CMOS Output Local Memory Byte Write Enable [3:0]– use to write individual bytes.L_ADSC#CMOS Output Local Memory Controller Address Status– to load a new address.L_CLK CMOS Output Local Memory Clock– a synchronous clock to memory devices.L_D[31:0]TTL I/O-TS Local Memory Data Bus Bit [31:0]– a 32-bit synchronous data bus.L_A[18:2]CMOS Output Local Memory Address Bus Bit [18:2]– Bit [17:2] of a synchronous address bus. Thememory address is sampled when L_CS# is enabled and L_ADSC# is asserted.L_A[19] / L_WE[3]#CMOS Output Local Memory Address Bus Bit [19] or Local Memory Write Chip Select [3]– De-pends on memory configuration, this pin can be used as the Local Memory Address Bit[19] or as the Local Memory Write Chip Select [3].L_WE[2:0]#CMOS Output Local Memory Write Chip Select [2:0]– allows up to write one of the 4 banks of mem-ory.L_OE[3:0]#CMOS Output Local Memory Read Chip Select [3:0]– allows up to read one of the 4 banks of mem-ory.L_BWE[3:0]#CMOS Output Local Memory Byte Write Enable [3:0]– use to write individual bytes.L_ADSC#CMOS Output Local Memory Controller Address Status– to load a new address.L_CLK CMOS Output Local Memory Clock– a synchronous clock to memory devices.Note: These pins have weak internal pull up resistors (50k to 100k Ohms each).2.1.2Supported Memory ConfigurationsRead/Write Chip Select and High Address BitsChip #3Chip #2Chip #1Chip #0RAM Chip Size # of RAM Chips Total BufferMemory Size L_WE[3]#L_A[19] /L_OE[3]#L_WE[2]#L_OE[2]#L_WE[1]#L_OE[1]#L_WE[0]#L_OE[0]#32k x 321128k bytes ------------------------L_WE[0]#L_OE[0]#2256k bytes ----------------L_WE[1]#L_OE[1]#L_WE[0]#L_OE[0]#4512k bytes L_WE[3]#L_OE[3]#L_WE[2]#L_OE[2]#L_WE[1]#L_OE[1]#L_WE[0]#L_OE[0]#64k x 321256k bytes ------------------------L_WE[0]#L_OE[0]#2512k bytes ----------------L_WE[1]#L_OE[1]#L_WE[0]#L_OE[0]#41M bytes L_WE[3]#L_OE[3]#L_WE[2]#L_OE[2]#L_WE[1]#L_OE[1]#L_WE[0]#L_OE[0]#128k x321512k bytes ------------------------L_WE[0]#L_OE[0]#21M bytes ----------------L_WE[1]#L_OE[1]#L_WE[0]#L_OE[0]#256k x3211M bytes----L_A[19]----------------L_WE[0]#L_OE[0]#2.1.3Bus Cycle WaveformsL_CLK L_ADSC#L_CS#L_A[19:2]L_WE[3:0]#L_BWE[3:0]#L_OE[3:0]#L_D[31:0] (Wr)L_D[31:0] (Rd)Typical Local Memory Access Operations2.2Processor Bus InterfaceSupports various industry standard micro-processors including: 9Intel 186, 386, and 486 family or equivalent9Motorola MPC series embedded processorsEasily adapts to other industry standard CPUsProvides separate Address and Data busSupports Big & Little Endian byte ordering Supports 16-bit Data BusSupports early RDY cycle9Meets timing requirement for Intel/AMD 186 family proc-essorsSupports 1X or 2X CPU Clock92X CPU Clock for 386 family processorsProvides a single interrupt signal to Switch Manager CPU2.2.1Pin DescriptionSymbol Type Name and FunctionsP_C[4:0]CMOS Input Processor Configuration bit [4:0]:– During the Reset Cycle, the P_C[4:0] pins provides theprocessor configuration. By using external weak pull-up or -down resistors, they define the Ex-ternal Management Bus Interface Configuration. These inputs are sampled at the trailing edge ofthe Reset cycle.C[0] – Defines the CPU Clock input is 1X or 2X clockC[1] – Selects either Big or Little Endian byte orderingC[2] – Defines the polarity of the P_RWC (Rd/Wr Control) inputC[3] – Defines the CPU Bus width – For EA-208, it is default to 16-bit CPU Bus interface, andthe setting of this bit is ignored.C[4] – Defines the timing relationship between P_RDY and P_D[15:0] valid. If C[4] is High,the P_D[15:0] are valid along in the same clock period as P_RDY is asserted. If C[4]is Low, the P_RDY is asserted one clock period early ahead of the P_D[15:0] arevalid.C[0]C[1]C[2]C[3]C[4]CPU Clock Byte Order RWC Bus Size RDY TimingLo1X Clock Little Endian P_R/W#n/a NormalHi2x Clock Big Endian P_W/R#n/a EarlyAfter RESET, these pins are used as XpressFlow Bus Data bit [31:27].P_A[11:1]TTL In (5VT)Address Bus Bit [11:1]– I/O port addressP_D[15:0]TTL I/O-TS (5VT)Data Bus Bit [15:0]– a 16-bit synchronous data bus.P_ADS#TTL In (5VT)Address Strobe– indicates valid address is on the busP_RWC TTL Input (5VT)Read/Write Control– indicates the current bus cycle is a read or write cycle.C[1] defines thepolarity of this signal during the Reset cycle.C[1]=Low P_R/W# is used for PowerPC or other similar processors.C[1]=High P_W/R# is used for 386, 486 or other similar processors P_RDY#TTL Out-OD Data Ready– timing indicates for bus data validP_BS16#TTL Out-OD Bus Size 16– response to bus master that the EA208 only supports 16-bit data bus width.P_CS#TTL Input (5VT)Chip Select– indicates the XpressFlow Engine is the target for the current bus operation.P_INT CMOS Output Interrupt Request to Switch Manager CPU The polarity of this signal output is programmablevia chip configuration register.P_RST#TTL In-ST (5VT)CPU Reset– Synchronous reset Input from Switch Manager CPUP_CLK TTL In (5VT)CPU Clock– 2X Clock for 386 family, and 1X Clock for the others2.2.2Motorola MPC801 Processor InterfaceP_CLK {CLKOUT}P_ADS#{TS#}P_A[11:1]{A[20:30]}P_CS#P_RWC {RD/WR#}P_RDY#{TA#}P_D[15:0]{D[0:15]}P_D[15:0]{D[0:15]}(out)(in)Note:Mnemonics with in {} are the equivalent signals defined by MPC801Typical Motorola MPC801 CPU I/O Access Operations2.2.3Intel 486 Processor InterfaceP_CLK P_ADS#P_A[11:1]P_CS#P_W/R#P_RDY#P_D[15:0] (in)P_D[15:0] (out)Typical 486 CPU I/O Access Operations2.2.4Intel 386 Processor InterfaceP_CLKPH2 (internal)P_ADS#P_A[11:1]P_CS#P_W/R#P_RDY#P_D[15:0] (in)P_D15:0] (out)Typical 386 CPU I/O Access OperationsP_CLKPH2 (internal)P_RST#Internal PH2 Clock Synchronization **Note:** See Intel 386 Processor Data Book for more details2.2.5Register MapNote:All 32-bit registers are D-word aligned.All 16-bit registers are also D-word aligned and right justified.For the Little Endian CPUs, register offset bit [1,0] are always set to be 00.For the Big Endian CPUs, register offset bit [1,0] are always set to be 10.This is a Global Register. CPU is allowed to write the Global Register of all devices by a single operation.These registers are reserved for system diagnostic usage only.I/O OffsetRegister Description LittleEndianBigEndianReg.SizeW/R Note:Device Configuration Registers (DCR)GCR Global Control Register hF00hF0216-bit W/-- DCR0Device Status Register hF00hF0216-bit--/RDCR1Signature & Revision Register hF10hF1216-bit--/RDCR2ID Register hF20hF2216-bit W/RDCR3Device Configuration Register hF30hF3216-bit W/RDCR4Interfaces Status Register hF40hF4216-bit--/RDTSR Test Register hF70hF7216-bit W/R Interrupt ControlsISR Interrupt Status Register – Unmasked hF80hF8216-bit--/RISRM Interrupt Status Register – Masked hF90hF9216-bit--/RIMSK Interrupt Mask Register hFA0hFA216-bit W/RIAR Interrupt Acknowledgment Register hFB0hFB216-bit W/--Buffer Memory InterfaceMWAR Memory Write Address Reg. – Single Cycle hE08hE0832-bit W/RMRAR Memory Read Address Reg. – Single Cycle hE18hE1832-bit W/RMBAR Memory Address Register – Burst Mode hE28hE2832-bit W/R MWBS Memory Write Burst Size (in D-words)hE40hE4216-bit W/RMRBS Memory Read Burst Size (in D-words)hE50hE5216-bit W/R MWDR Memory Write Data Register hE68hE6832-bit W/--MWDX Memory Write Data Reg. – Byte Swapping hE6C hE6C32-bit W/--MRDR Memory Read Data Register hE68hE6832-bit--/RMRDX Memory Read Data Reg. – Byte Swapping hE6C hE6C32-bit--/RFCB Buffer & Stack ManagementFCBBA Frame Control Buffer – Base Address hD00hD0216-bit W/R FCBAG Frame Control Buffer – Buffer Aging Status hD30hD3216-bit--/R FCBSL Frame Ctrl Buffer Stack – Size Limit hD90hD9216-bit W/R FCBST Frame Ctrl Buffer Stack – Buffer Low Threshold hDA0hDA216-bit W/R FCBSS Frame Ctrl Buffer Stack – Allocation Status hDB0hDB216-bit--/RI/O OffsetRegister Description LittleEndianBigEndianReg.SizeW/R Note:Access Control Function (Chip Level controls)AVXR VLAN Control Table (VCT) Index Register hC00hC0216-bit W/--AVDR VCT Data Register hC10hC1216-bit W/RAVTC VLAN Type Code hC20hC2216-bit W/RAXSC Transmission Scheduling Control Register hC30hC3216-bit W/RAMIIC MII Command Register hC40hC4032-bit W/--AMIIS MII Status Register hC40hC4032-bit--/RAFCR Flow Control Register hC70hC7216-bit W/RAMAR0Multicast Address. for MAC Control Frames Byte [1,0]hC80hC8216-bit W/RAMAR1Byte [3,2]hC90hC9216-bit W/RAMAR2Byte [5,4]hCA0hCA216-bit W/RAMCT MAC Control FrameType Code Register hCB0hCB216-bit W/RADAR0Base MAC Address Register – Byte [1,0]hCC0hCC216-bit W/RADAR1Base MAC Address Register – Byte [3,2]hCD0hCD216-bit W/RADAR2Base MAC Address Register – Byte [5,4]hCE0hCE216-bit W/R Ethernet MAC Port Control Registers – (substitute [n] with Port Number, n = {0..3] )ECR0MAC Port Control Register h n00h n0216-bit W/RECR1MAC Port Configuration Register h n10h n1216-bit W/RECR2MAC Port Interrupt Mask Register hn20hn2216-bit W/RECR3MAC Port Interrupt Status Register hn30hn3216-bit--/R EXSR MAC Tx Status Register hn40hn4216-bit--/R EXEC MAC Tx Error Counters hn50hn5216-bit--/R ERSR MAC Rx Status Register hn68hn6832-bit--/R EREC MAC Rx Error Counters hn78hn7832-bit--/R2.3XpressFlow Bus OperationZarlink’s optimized XpressFlow Bus architectureProvides 1.6G bps switching bandwidth9-33 1.07G bps9-40 1.28G bps9-50 1.6G bpsFull multi bus master structureAllows XpressFlow Engine to communicate with Access Con-trollers via a message passing protocol9Command Messages for passing control information be-tween devices9Data Messages for forwarding an Ethernet frame from re-ceiving port to transmission portBuilt-in intelligent bus load regulator for data traffic balancing Provides centralized bus arbitration with two level request pri-orities9High priority for Data Messages9Low priority for Command Messages2.3.1Pin DescriptionSymbol Type Name and FunctionsS_D[31:0]CMOSI/O-TS Data Bus Bit [31:0]– a 32-bit synchronous data bus.Note:During the system RESET period, Data Bit [31:28] are used as Processor Interface Configuration bit [0:3]S_MSGEN#CMOSI/O-TS Message Envelope– encompasses the entire period of a message transfer. Targets use the leading edge of this signal to detect the beginning of a message transfer, and to decode the message header for the intended target(s).S_EOF#CMOSI/O-TS End of Frame– only used by frame data transfer messages to identify the end of frame condi-tion. This signal is synchronous with the Rx Frame Status word appended to the end of the message.S_IRDY CMOSI/O-TS Initiator Ready– a normal true signal. When negated, it indicates the initiator had asserted wait state(s) in between command words. Target should use this signal as enable signal for latching the data from the bus.S_TABT#CMOSI/O-OD Target Abort– when asserted, the target had aborted the reception of current message on the bus.S_HPREQ#CMOSI/O-OD High Priority Request– indicates one or more Bus Requester is requesting for high priority message transfer.S_REQ#CMOSOutput Bus Request–Bus Request signals from Access Controller to Bus Access Arbitrator in Xpress-Flow EngineS_GNT#CMOS In-putBus Grant–Bus Grant signals from Bus Arbitrator to Bus RequesterS_OVLD#CMOSOutput Bus Overload– when asserted, all data forwarding bus bandwidth has been allocated. Cannot support additional load for data forwarding traffic.S_CLK CMOSInputXpressFlow Bus Clock– 33MHz system clock2.3.2Bus Cycle WaveformsS_CLKS_MSGEN#S_D[31:0]S_EOF#S_IRDYXpressFlow Bus Data Transfer CycleCommand Cycle Data Xfer w/o Data Aborted CommandS_CLKS_MSGEN#S_D[31:0]S_EOF#S_TABT#Other XpressFlow Bus CyclesS_CLK S_REQ[k]#S_REQ[j]#S_HPREQ#High Priority Request pre-empts the low priority request.S_MSGEN#S_REQ[j]#S_GNT[j]#S_HPREQ#S_REQ[I]#S_GNT[I]#XpressFlow Bus arbitrationS_CLKS_OVLD#Bus Overload pre-empts the data transfer request2.410Mb Serial Interface for Port 0 through 7Fully compliant with IEEE 802.3 10M bit Serial Interface Stan-dard for connecting with external 10Mbps Ethernet Physical Layer TransceiverSupports 10Mbps 10BaseT serial interface Supports both half and full duplex operation2.4.1Pin DescriptionSymbol Type Name and FunctionsTn_RXD TTL In (5VT)Receive Data – (one for each 10M bit Serial Interface Port) a receive data stream.Tn_RXC TTL In (5VT)Receive Clock – (one for each 10M bit Serial Interface Port) from external phy for sampling the receive data from Tn_RXD inputTn_TXC TTL In (5VT)Transmit Clock – (one for each 10M bit Serial Interface Port) a continuous clock input with 35% to 65% duty cycles.Tn_TXEN CMOS Output Transmit Enable – (one for each 10M bit Serial Interface Port)Tn_TXD CMOS Output Transmit Data – (one for each 10M bit Serial Interface Port) a transmit data stream.Tn_LPBK CMOS Output Loop Back Enable – (one for each 10M bit Serial Interface Port) The polarity of this signal is programmable via Port Configuration RegisterTn_FDCMOS Output Full Duplex Mode – (one for each 10M bit Serial Interface Port) The polarity of this signal is programmable via Port Configuration RegisterTn_COL TTL In (5VT)Collision Detected – (one for each 10M bit Serial Interface Port)Tn_CRS TTL In (5VT)Carrier Sense – (one for each 10M bit Serial Interface Port)Tn_LNKTTL In (5VT)Link Status –(one for each 10M bit Serial Interface Port) The polarity of this signal is pro-grammable via Port Configuration RegisterNote :“n” is the port number [7:0]These signals have programmable output polarity.TXCTXENTXD10M bit Serial Interface – Transmit TimingCRSRXCRXD10M bit Serial Interface – Receive Timing2.5Test PinsSymbol Type Name and FunctionsT_MODECMOS I/O-TSTest Mode Selection & Test Output – Set Test Mode upon Reset, and provides test status output during test mode3.DC SPECIFICATION3.1ABSOLUTE MAXIMUM RATINGSStorage Temperature-50°C to +125°COperating Temperature0°C to +70°CSupply Voltage V DD with Respect to V SS+3.0 V to +3.6 VVoltage on 5V Tolerant Input Pins-0.5 V to (V DD+ 1.8 V)Voltage on Other Input Pins-0.5 V to (V DD + 10%)Stresses above those listed may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to Ab-solute Maximum Ratings for extended periods may affect device reliability.3.2DC CHARACTERISTICSV DD= +3.0 V to +3.6 V T AMBIENT= 0°C to +70°CPreliminarySymbol Parameter Description Min Type Max Unitf osc Frequency of Operation (-40)2040.0000MHzFrequency of Operation (-50)2050.0000MHzFrequency of Operation (-66)2066.6667MHzI DD Supply Power – @ 40 MHz (V DD=3.3 V)300 500mASupply Power – @ 50 MHz (V DD=3.3 V)300500mASupply Power – @ 66.67 MHz (V DD=3.3 V)360600mA V OH-CMOS Output High Voltage (CMOS) I OH= maximum V DD- 0.5V V OL-CMOS Output Low Voltage (CMOS) I OL= maximum0.45V V OH-TTL Output High Voltage (TTL) I OH= maximum 2.4V V OL-TTL Output Low Voltage (TTL) I OL= maximum0.45V V IH-CMOS Input High Voltage (CMOS)VDD x 70%V DD+ 10%V V IL-CMOS Input Low Voltage (CMOS)-0.5VDD x 30%V V IH-TTL Input High Voltage (TTL) 2.0V DD+ 10%V V IL-TTL Input Low Voltage (TTL)-0.3+0.8V V IH-5VT Input High Voltage (TTL 5V tolerant) 2.0V DD+ 1.8V V IL-5VT Input Low Voltage (TTL 5V tolerant)-0.3+0.8V±10µAI LI Input Leakage Current (0.1 V ) V IN) V DD)(all pins except those with internal pull-up/pull-down resis-tors)I LO Output Leakage Current (0.1 V ) V OUT) V DD)±15µA60µAI IH Input Leakage Current V IH= V DD- 0.1 V(pins with internal pull-down resistors)-60µAI IL Input Leakage Current V IL= 0.1 V(pins with internal pull-up resistors)C IN Input Capacitance8pFC OUT Output Capacitance8pFC I/O I/O Capacitance10pF Notes:4.AC SPECIFICATION4.1XpressFlow Bus Interface:S_CLK S_D[31:0] S_MSGEN#S_EOF#S_IRDYS_TABT#S_HPREQ#S_GNT#S_OVLD#XpressFlow Bus Interface –Input setup and hold timingS_CLKS_D[31:0]S_MSGEN#S_EOF#S_IRDYXpressFlow Bus Interface –Output float delay timing S_CLKS_D[31:0]S_MSGEN#S_EOF#S_IRDYS_TABT#S_HPREQ#S_REQ#XpressFlow Bus Interface –Output valid delay timing。

C站JUE-85中文操作说明书 07-9-10

明进行了简单的翻译。如有不详之处,请参考原英文说明书,以原厂家英文说明书为准。

BZXH-01-Z产品使用说明书(第二版)

目录1 概述 (2)2 产品型号说明 (3)3 功能特点 (3)4 技术参数 (5)5 结构 (6)6 电气原理 (7)7 自动调谐控制器 (10)7.1 概述 (10)7.2 组成 (10)7.3 主要功能 (10)7.4 使用方法 (13)7.5 运行维护注意事项 (21)8 自动控制屏 (21)9 使用须知 (21)10 消弧限压装置的操作注意事项 (24)11 订货须知 (25)12 附录 (27)1 概述中性点接地方式关系到电力系统的运行可靠性。

目前我国6~66kV电网,一般采用中性点不接地、低阻接地或经消弧线圈接地方式。

对于中性点不接地系统,当系统发生单相接地故障时,系统可带故障运行2小时,可相对提高系统的供电可靠性。

但当系统的接地电容电流较大时,接地处引起的电弧就难以自行熄灭,甚至可能出现间歇性电弧,从而产生谐振过电压,对电网带来不利影响。

采用低电阻接地,可限制弧光接地过电压,对设备绝缘等级要求较低,不足之处在于系统中任何单相接地故障都跳闸,导致跳闸率过高;同时,系统单相接地故障时故障点接地电流很大,对电网带来许多不利影响。

为此,我国电力行标DL/T620-1997中规定:6~10kV不直接连接发电机的系统和35kV、66kV系统,当单相接地故障电容电流超过下列数值又需在接地故障条件下运行时,应采用消弧线圈接地方式:6~10kV架空线路构成的系统和所有35kV、66kV系统,10A;6~10kV 电缆线路构成的系统,30A。

消弧线圈的主要作用是在系统发生单相接地故障时产生电感电流以补偿电网电容电流,使故障点残流变小,达到自动熄弧、消除故障的目的,具有减少跳闸次数、降低接地故障电流的优点,使系统能够在故障条件下继续运行一段时间,为找到故障线路争取时间。

BZXH-01-Z型消弧线圈调谐及选线控制成套装置用于中性点经调匝式消弧线圈接地的系统中,可自动跟踪系统运行方式的改变,调整消弧线圈的档位改变补偿电感电流,使系统残流在设定值之内,当系统发生瞬时性单相接地故障时自动补偿系统电容电流,使故障自动恢复;对非瞬时性单相接地故障,控制消弧线圈进行补偿,同时用最短的时间正确判断接地线路,将故障线路切除,从而提高系统的供电可靠性。

BZX84C18-V中文资料

Document Number Small Signal Zener DiodesFeatures•These diodes are also available in other case styles and other configurationsincluding: the SOD-123 case with type designation BZT52 series, the dual zenerdiode common anode configuration in the SOT-23case with type designation AZ23 series and the dual zener diode common cathode configuration in the SOT-23 case with type designation DZ23series.•The Zener voltages are graded according to the international E 24 standard. Standard Zener volt-age tolerance is ± 5 %. Replace "C" with "B" for ± 2 % tolerance.•Silicon Planar Power Zener Diodes •Lead (Pb)-free component•Component in accordance to RoHS 2002/95/EC and WEEE 2002/96/ECWeight: approx. 8.8 mgPackaging Codes/Options:GS18 / 10 k per 13" reel (8 mm tape), 10 k/box GS08 / 3 k per 7" reel (8 mm tape), 15 k/boxAbsolute Maximum RatingsT amb = 25°C, unless otherwise specified1) Device on fiberglass substrate, see layout.Thermal CharacteristicsT amb = 25°C, unless otherwise specified1)Device on fiberglass substrate, see layout.ParameterT est condition Symbol Value Unit Power dissipationP tot300 1)mWParameterTest condition Symbol Value Unit Thermal resistance junction to ambient air R thJA 420 1)°C/W Junction temperature T j 150°C Storage temperature rangeT S- 65 to + 150°CElectrical CharacteristicsPartnumber MarkingCodeZenerVoltageRangeDynamic Resistance T estCurrentTemp.Coefficientof ZenerVoltageTestCurrentReverse LeakageCurrentV Z @ I ZT1r zj @ I ZT1r zj @ I ZT2I ZT1αVZ @ I ZT1I ZT2I R@ V R VΩmA10-4/°C mAµA Vmin max min maxBZX84C2V4-V Z11 2.2 2.670 (≤100)2755-9.0-4.01501 BZX84C2V7-V Z12 2.5 2.975 (≤100)300 (≤600)5-9.0-4.01201 BZX84C3V0-V Z13 2.8 3.280 (≤95)325 (≤600)5-9.0-3.01101 BZX84C3V3-V Z14 3.1 3.585 (≤95)350 (≤600)5-8.0-3.0151 BZX84C3V6-V Z15 3.4 3.885 (≤90)375 (≤600)5-8.0-3.0151 BZX84C3V9-V Z16 3.7 4.185 (≤90)400 (≤600)5-7.0-3.0131 BZX84C4V3-V Z174 4.680 (≤90)410 (≤600)5-6.0-1.0131 BZX84C4V7-V Z1 4.4550 (≤80)425 (≤500)5-5.0+2.0132 BZX84C5V1-V Z2 4.8 5.440 (≤60)400 (≤480)5-3.0+4.0122 BZX84C5V6-V Z3 5.2615 (≤40)80 (≤400)5-2.0+6.0112 BZX84C6V2-V Z4 5.8 6.6 6.0 (≤10)40 (≤150)5-1.0+7.0134 BZX84C6V8-V Z5 6.47.2 6.0 (≤15)30 (≤80)5+2.0+7.0124 BZX84C7V5-V Z677.9 6.0 (≤15)30 (≤80)5+3.0+7.0115 BZX84C8V2-V Z77.78.7 6.0 (≤15)40 (≤80)5+4.0+7.010.75 BZX84C9V1-V Z88.59.6 6.0 (≤15)40 (≤100)5+5.0+8.010.56 BZX84C10-V Z99.410.68.0 (≤20)50 (≤150)5+5.0+8.010.27 BZX84C11-V Y110.411.610 (≤20)50 (≤150)5+5.0+9.010.18 BZX84C12-V Y211.412.710 (≤25)50 (≤150)5+6.0+9.010.18 BZX84C13-V Y312.414.110 (≤30)50 (≤170)5+7.0+9.010.18 BZX84C15-V Y413.815.610 (≤30)50 (≤200)5+7.0+9.010.050.7 V Znom.BZX84C16-V Y515.317.110 (≤40)50 (≤200)5+8.0+9.510.050.7 V Znom.BZX84C18-V Y616.819.110 (≤45)50 (≤225)5+8.0+9.510.050.7 V Znom.BZX84C20-V Y718.821.215 (≤55)60 (≤225)5+8.0+1010.050.7 V Znom.BZX84C22-V Y820.823.320 (≤55)60 (≤250)5+8.0+1010.050.7 V Znom.BZX84C24-V Y922.825.625 (≤70)60 (≤250)5+8.0+1010.050.7 V Znom.BZX84C27-V Y1025.128.925 (≤80)65 (≤300)2+8.0+100.50.050.7 V Znom.BZX84C30-V Y11283230 (≤80)70 (≤300)2+8.0+100.50.050.7 V Znom.BZX84C33-V Y12313535 (≤80)75 (≤325)2+8.0+100.50.050.7 V Znom.BZX84C36-V Y13343835 (≤90)80 (≤350)2+8.0+100.50.050.7 V Znom.BZX84C39-V Y14374140 (≤130)80 (≤350)2+10+120.50.050.7 V Znom.BZX84C43-V Y15404645 (≤150)85 (≤375)2+10+120.50.050.7 V Znom.BZX84C47-V Y16445050 (≤170)85 (≤375)2+10+120.50.050.7 V Znom.BZX84C51-V Y17485460 (≤180)85 (≤400)2+10+120.50.050.7 V Znom.BZX84C56-V Y18526070 (≤200)100 (≤425)2+9.0+110.50.050.7 V Znom.BZX84C62-V Y19586680 (≤215)100 (≤450)2+9.0+120.50.050.7 V Znom.BZX84C68-V Y20647290 (≤240)150 (≤475)2+10+120.50.050.7 V Znom.BZX84C75-V Y21707995 (≤255)170 (≤500)2+10+120.50.050.7 V Znom. Document Number 85763Document Number Electrical CharacteristicsPartnumberMarking CodeZener Voltage Range Dynamic ResistanceTest CurrentT emp. Coefficient of Zener Voltage T est CurrentReverse LeakageCurrentV Z @ I ZT1r zj @ I ZT1r zj @ I ZT2I ZT1αVZ @ I ZT1I ZT2I R @ V R V ΩmA10-4/°C mAµAVminmax min max BZX84B2V4-V Z50 2.35 2.4570 (≤100)2755-9-41501BZX84B2V7-V Z51 2.65 2.7575 (≤100)300 (≤600)5-9-41201BZX84B3V0-V Z52 2.94 3.0680 (≤95)325 (≤600)5-9-31101BZX84B3V3-V Z53 3.23 3.3785 (≤95)350 (≤600)5-8-3151BZX84B3V6-V Z54 3.53 3.6785 (≤90)375 (≤600)5-8-3151BZX84B3V9-V Z55 3.82 3.9885 (≤90)400 (≤600)5-7-3131BZX84B4V3-V Z56 4.21 4.3980 (≤90)410 (≤600)5-6-1131BZX84B4V7-V Z57 4.61 4.7950 (≤80)425 (≤500)5-52132BZX84B5V1-V Z585 5.240 (≤60)400 (≤480)5-34122BZX84B5V6-V Z59 5.49 5.7115 (≤40)80 (≤400)5-26112BZX84B6V2-V Z60 6.08 6.32 6.0 (≤10)40 (≤150)5-17134BZX84B6V8-V Z61 6.66 6.94 6.0 (≤15)30 (≤80)527124BZX84B7V5-V Z627.357.65 6.0 (≤15)30 (≤80)537115BZX84B8V2-V Z638.048.36 6.0 (≤15)40 (≤80)54710.75BZX84B9V1-V Z648.929.28 6.0 (≤15)40 (≤100)55810.56BZX84B10-V Z659.810.28.0 (≤20)50 (≤150)55810.27BZX84B11-V Z6610.811.210 (≤20)50 (≤150)55910.18BZX84B12-V Z6711.812.210 (≤25)50 (≤150)56910.18BZX84B13-V Z6812.713.310 (≤30)50 (≤170)57910.18BZX84B15-V Z6914.715.310 (≤30)50 (≤200)57910.050.7 V Znom.BZX84B16-V Z7015.716.310 (≤40)50 (≤200)589.510.050.7 V Znom.BZX84B18-V Z7117.618.410 (≤45)50 (≤225)589.510.050.7 V Znom.BZX84B20-V Z7219.620.415 (≤55)60 (≤225)581010.050.7 V Znom.BZX84B22-V Z7321.622.420 (≤55)60 (≤250)581010.050.7 V Znom.BZX84B24-V Z7423.524.525 (≤70)60 (≤250)581010.050.7 V Znom.BZX84B27-V Z7526.527.525 (≤80)65 (≤300)28100.50.050.7 V Znom.BZX84B30-V Z7629.430.630 (≤80)70 (≤300)28100.50.050.7 V Znom.BZX84B33-V Z7732.333.735 (≤80)75 (≤325)28100.50.050.7 V Znom.BZX84B36-V Z7835.336.735 (≤90)80 (≤350)28100.50.050.7 V Znom.BZX84B39-V Z7938.239.840 (≤130)80 (≤350)210120.50.050.7 V Znom.BZX84B43-V Z8042.143.945 (≤150)85 (≤375)210120.50.050.7 V Znom.BZX84B47-V Z8146.147.950 (≤170)85 (≤375)210120.50.050.7 V Znom.BZX84B51-V Z82505260 (≤180)85 (≤400)210120.50.050.7 V Znom.BZX84B56-V Z8354.957.170 (≤200)100 (≤425)29110.50.050.7 V Znom.BZX84B62-V Z8460.863.280 (≤215)100 (≤450)29120.50.050.7 V Znom.BZX84B68-V Z8566.669.490 (≤240)150 (≤475)210120.50.050.7 V Znom.BZX84B75-VZ8673.576.595 (≤255)170 (≤500)210120.50.050.7 V Znom. Document Number 85763Typical Characteristics (Tamb = 25 °C unless otherwise specified)Figure 1. Forward characteristics Figure 2. Admissible Power Dissipation vs. Ambient Temperature Figure3. Pulse Thermal Resistance vs. Pulse Duration1811418115Figure 4. Dynamic Resistance vs. Zener CurrentFigure 5. Capacitance vs. Zener VoltageFigure6. Dynamic Resistance vs. Zener Current1811718118Document Number Figure 7. Dynamic Resistance vs. Zener CurrentFigure 8. Thermal Differential Resistance vs. Zener Voltage Figure9. Dynamic Resistance vs. Zener Voltage18120Figure 10. Temperature Dependence of Zener Voltage vs. ZenerVoltageFigure 11. Change of Zener Voltage vs. Junction TemperatureFigure 12. Temperature Dependence of Zener Voltage vs. ZenerVoltage18124°C18136 Document Number 85763Figure 13. Change of Zener Voltage vs. Junction TemperatureFigure 14. Change of Zener voltage from turn-on up to the point ofthermal equilibrium vs. Zener voltageFigure 15. Change of Zener voltage from turn-on up to the point ofthermal equilibrium vs. Zener voltage181261813718138Document Number Figure 16. Breakdown CharacteristicsFigure17. Breakdown Characteristics1811118112 Document Number 85763Layout for R Theta;JA testThickness: Fiberglass 0.059 in. (1.5 mm)Copper leads 0.012 in. (0.3 mm)Figure18. Breakdown Characteristics18113Package Dimensions in mm (Inches)Document Number Ozone Depleting Substances Policy StatementIt is the policy of Vishay Semiconductor GmbH to1.Meet all present and future national and international statutory requirements.2.Regularly and continuously improve the performance of our products, processes, distribution and operatingsystems with respect to their impact on the health and safety of our employees and the public, as well as their impact on the environment.It is particular concern to control or eliminate releases of those substances into the atmosphere which are known as ozone depleting substances (ODSs).The Montreal Protocol (1987) and its London Amendments (1990) intend to severely restrict the use of ODSs and forbid their use within the next ten years. Various national and international initiatives are pressing for an earlier ban on these substances.Vishay Semiconductor GmbH has been able to use its policy of continuous improvements to eliminate the use of ODSs listed in the following documents.1.Annex A, B and list of transitional substances of the Montreal Protocol and the London Amendmentsrespectively2.Class I and II ozone depleting substances in the Clean Air Act Amendments of 1990 by the EnvironmentalProtection Agency (EPA) in the USA3.Council Decision 88/540/EEC and 91/690/EEC Annex A, B and C (transitional substances) respectively. Vishay Semiconductor GmbH can certify that our semiconductors are not manufactured with ozone depleting substances and do not contain such substances.We reserve the right to make changes to improve technical designand may do so without further notice.Parameters can vary in different applications. All operating parameters must be validated for each customer application by the customer. Should the buyer use Vishay Semiconductors products for any unintended or unauthorized application, the buyer shall indemnify Vishay Semiconductors against all claims, costs, damages, and expenses, arising out of, directly or indirectly, any claim of personal damage, injury or death associated with such unintended or unauthorized use.Vishay Semiconductor GmbH, P.O.B. 3535, D-74025 Heilbronn, Germany Document Number 85763。

WBT-851说明书

重要提示

感谢您使用许继电气股份有限公司的产品。为了安全、正确、高效地使用本装置,请您务必注意以下重要提示:

本说明书仅适用于WBT-851微机备自投保护装置。

请仔细阅读本说明书,并按照说明书的规定调整、测试和操作。如有随机资料,请以随机资料为准。

b.冲击响应:装置能承受GB/T 14537-1993中4.2.1规定的严酷等级为I级冲击响应检验。

c.振动耐久:装置能承受GB/T 11287-2000中4.2.2规定的严酷等级为I级振动耐久检验。

d.冲击耐久:装置能承受GB/T 14537-1993中4.2.2规定的严酷等级为I级冲击耐久检验。

2.6

a.绝缘电阻:各带电的导电电路分别对地(即外壳或外露的非带电金属零件)之间,交流回路和直流回路之间,交流电流回路和交流电压回路之间,用开路电压为500V的测试仪器测试其绝缘电阻值不应小于100MΩ。

b.介质强度:装置通信回路和24V等弱电输入输出端子对地能承受50Hz、500V(有效值)的交流电压,历时1min的检验无击穿或闪络现象;其余各带电的导电电路分别对地(即外壳或外露的非带电金属零件)之间,交流回路和直流回路之间,交流电流回路和交流电压回路之间,能承受50Hz、2kV(有效值)的交流电压,历时1min的检验无击穿或闪络现象。

1

采用Nucleus Plus公司的实时多任务操作系统

装置的实时性、可靠性和运行的稳定性高

采用分层的设计方案

采用模块化设计方案,便于配置

软件的升级方便

完善的软件测试方案

1

遥测采集回路自检

开出回路自检,可以到继电器动作线圈

AD、RAM、EPROM芯片自检

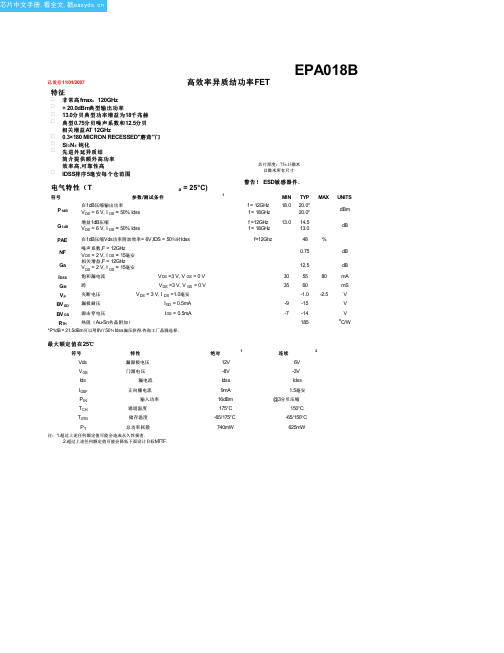

EPA018B中文资料(Excelics Semiconductor)中文数据手册「EasyDatasheet - 矽搜」

6V,半智能决策支持系AG ANG

4.681 169.2 0.010 77.2

4.581 160.2 0.020 71.8

4.476 151.2 0.030 67.3

4.339 142.0 0.037 61.9

4.206 132.9 0.044 54.3

2.852 75.6 0.067 16.4

2.749 69.6 0.069 12.9

2.663 63.4 0.070 9.5

2.585 57.1 0.071 6.7

2.515 50.6 0.074 3.4

2.423 44.1 0.076 0.2

2.341 37.4 0.079 -2.4

2.254 30.8 0.081 -6.3

芯片中文手册,看全文,戳

已发行 11/01/2007

高效率异质结功率FET

EPA018B

特征 非 常 高 fmax: 120GHz + 20.0dBm典型输出功率 13.0分 贝 典 型 功 率 增 益 为 18千 兆 赫 典 型 0.75分 贝 噪 声 系 数 和 12.5分 贝 相关增益AT 12GHz 0.3×180 MICRON RECESSED"蘑菇 "门 Si3N4 钝化

- S11 MAG ANG 1.000 -11.0 0.990 -21.5 0.976 -32.1 0.962 -42.6 0.941 -53.4 0.922 -63.6 0.905 -73.1 0.883 -82.0 0.864 -90.4 0.846 -97.9 0.829 -105.3 0.819 -112.4 0.804 -120.0 0.792 -128.0 0.784 -136.3 0.777 -145.0 0.770 -155.2 0.773 -165.3 0.770 -175.2 0.771 175.3 0.780 169.2 0.777 163.2 0.793 157.9 0.789 154.9 0.796 151.5 0.804 149.6 0.786 147.6 0.788 146.0 0.779 144.4 0.777 140.9 0.769 137.1 0.770 131.7 0.758 126.2 0.764 120.0 0.777 114.3 0.799 107.4 0.824 101.9 0.856 97.2 0.877 92.4 0.884 89.0

SAB-C517A中文资料

On-Chip Emulation Support Module

Oscillator Watchdog

Watchdog Timer T0 T2 T1 10-Bit A/D Converter

XRAM 2K x 8

RAM 256 x 8

Port 0 Port 1

I/O I/O I/O I/O I/O

Power Saving Modes

• • • •

• • •

Ordering Information The ordering code for Siemens microcontrollers provides an exact reference to the required product. This ordering code identifies:

I/O

I/O

MCA03317

Figure 1 C517A Functional Units

Semiconductor Group

1

元器件交易网

C517A

Features (continued) :

• Two full duplex serial interfaces (USART) •

– 500 ns instruction cycle at 24 MHz operation Superset of the 8051 architecture with 8 datapointers On-chip emulation support logic (Enhanced Hooks Technology TM) 32K byte on-chip ROM (with optional ROM protection) – alternatively up to 64K byte external program memory Up to 64K byte external data memory 256 byte on-chip RAM Additional 2K byte on-chip RAM (XRAM) Seven 8-bit parallel I/O ports Two input ports for analog/digital input (further features are on next page)

LBZX84XXXXLT1G中文资料