M9366-BN6T中文资料

LM2596T中文资料

LM2596T中文资料元器件交易网/doc/a66360844.html,3.0A, 150Khz, Step-Down Switching RegulatorFEATURES3.3V, 5.0V, 12V, 15V, and Adjustable Output Versions Adjustable Version Output Voltage Range, 1.23 to 37V +/- 4%. Maximum Over Line and Load Conditions Guaranteed 3.0A Output Current Wide Input Voltage Range Requires Only 4 External Components 150Khz Fixed Frequency Internal Oscillator TTL Shutdown Capability, Low Power Standby Mode High Efficiency Uses Readily Available Standard Inductors Thermal Shutdown and Current Limit Protection Moisture Sensitivity Level(MSL) Equals1 TO-263(D2) TO-220V TO-220LM2596ApplicationsSimple High-Efficiency Step-Down(Buck) Regulator Efficient Pre-Regulator for Linear Regulators On-Card Switching Regulators Positive to Negative Converter(Buck-Boost) Negative Step-Up Converters Power Supply for Battery Chargers1. 2. 3. 4. 5. Vin Output Ground Feedback On/OffDESCRIPTIONThe LM2596 series of regulators are monolithic integrated circuits ideally suited for easy and convenient design of a step-down switching regualtor(buck converter). All circuits of this series are capable of driving a 3.0A load with excellent line and load regulation. These devices are available in fixed output voltages of 3.3V, 5.0V,12V, 15V, and an adjustable output version.ORDERING INFORMATIONDevice LM2596T-X.X LM2596TV-X.X LM2596R MarkingLM2596T-X.X LM2596T-X.X LM2596R-X.X Package TO-220 TO-220V TO-263These regulatiors were designed to minimize the number of externalcomponents to simplify the power supply design. Standard series of inductors optimized for use with the LM2576 are offered by several different inductor manufacturers. Since the LM2596 converter is a switch-mode power supply, its efficiency is significantly higher in comparison with popular three-terminal limear reguators, especially with higher input voltages. In many cases, the power dissipated is so low that no heatsink is required or its size could be reduced dramatically. A standard series of inductors optimized for use with the LM2596 are available from several different manufacturers. This feature greatly simplifies the design of switch-mode power supplies. The LM2596 features include a guaranteed +/- 4% tolerance on output voltage within specified input voltages and output load conditions, and +/-15% on the oscillator frequency (+/- 2% over 0oC to 125 oC). External shutdown is included, featuring 80 uA(typical) standby current. The output switch includes cycle-bycycle current limiting, as well as thermal shutdown for full protection under fault conditions.HTC1Oct 2004 - Rev 0元器件交易网/doc/a66360844.html,3.0A, 15V, Step-Down Switching RegulatorTypical Application (Fixed Output Voltage Versions)LM2596LM2596-5.033 uH680 uF1N5824220 uFFigure 1. Block Diagram and Typical ApplicationABSOLUTE MAXIMUM RATINGS(Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.)Power DissipationTO-220, 5-LeadThermal Resistance, Junction-to-Ambient Thermal Resistance, Junction-to-caseTO-263Thermal Resistance, Junction-to-Ambient Thermal Resistance, Junction-to-caseHTC2Oct 2004 - Rev 0元器件交易网/doc/a66360844.html,3.0A, 15V, Step-Down Switching RegulatorLM2596OPERATING RATINGS (Operating Ratings indicate conditions for which the device is intended to befunctional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics.)ELECTRICAL CHARACTERISTICS / SYSTEM PARAMETERS ([Note 1] Test Circuit Figure 2) (Unless otherwise specified, Vin = 12 V for the 3.3 V, 5.0 V, and Adjustable version, Vin = 25 V for the 12 V version, and Vin = 30 V for the 15 V version. ILoad = 500mA. For typical values TJ = 25°C, for min/max values TJ is the operating junction temperature range that applies [Note 2], unless otherwise noted.)LM2596-3.3 ([ Note 1]. Test Circuit Figure 2 )73 LM2596-5.0 ([ Note 1]. Test Circuit Figure 2 ) 180 LM2596-12 ([ Note 1]. Test Circuit Figure 2 )90 LM2596-15 ([ Note 1]. Test Circuit Figure 2 )98 LM2596-ADJ ([ Note 1]. Test Circuit Figure 2 )73HTC3Oct 2004 - Rev 0元器件交易网/doc/a66360844.html,3.0A, 15V, Step-Down Switching RegulatorELECTRICAL CHARACTERISTICS / Device ParametersLM2596(Unless otherwise specified, Vin = 12 V for the 3.3 V, 5.0 V, and Adjustable version, Vin = 25 V for the 12 V version, and Vin = 30 V for the 15 V version. ILoad = 500 mA. For typical values Tj = 25°C, for min/max values Tj is the operating junction temperature range that applies [Note 2], unless otherwise noted.)10 0 127 110 15050 100 173 1731.16 01.4 1.53.6 3.4100 4.5 6.9 7.5 50 30 102 5 00 2 0 2.0 2.0 2 V LOGIC = 2.5V (Regulator OFF) V LOGIC = 0.5V (Regulator ON) 5 0.02 1.3 1.32500.6 0.6 15 5.01. External components such as the catch diode, inductor, input and output capacitors can affect switching regulator system performance. When the LM2596 is used as shown in the Figure 1 test circuit, system performance will be as shown in system parameters section .2. Tested junction temperature range for the LM2596 : TLOW = –0°C THIGH = +125°C3. The oscillator frequency reduces to approximately 18 kHz in the event of an output short or an overload which causes the regulated output voltage to drop approximately 40% from the nominal output voltage. This self protection feature lowers the average dissipation of the IC by lowering the minimum duty cycle from 5% down to approximately 2%.4. Output (Pin 2) sourcing current. No diode, inductor or capacitor connected to output pin.5. Feedback (Pin 4) removed from output and connected to 0 V.6. Feedback (Pin 4) removed from output and connected to +12 V for the Adjustable, 3.3 V, and 5.0V ersions, and +25 V for the 12 V and15 V versions, to force the output transistor “off”.7. Vin = 40 V.HTC4Oct 2004 - Rev 0元器件交易网/doc/a66360844.html,3.0A, 15V, Step-Down Switching RegulatorTYPICAL PERFORMANCE CHARACTERISTICS (Circuit ofFigure 2)LM2596HTC5Oct 2004 - Rev 0元器件交易网/doc/a66360844.html,3.0A, 15V, Step-Down Switching RegulatorTYPICAL PERFORMANCE CHARACTERISTICS (Circuit of Figure 2)Feedback Pin Bias CurrentLM2596HTC6Oct 2004 - Rev 0元器件交易网/doc/a66360844.html,3.0A, 15V, Step-Down Switching RegulatorTest Circuit and Layout GuidelinesLM2596Figure 2. Typical Test Circuits and Layout GuideAs in any switching regulator, layout is very important. Rapidly switching currents associated with wiring inductance can generate voltage transients which can cause problems. For minimal inductance and ground loops, the wires indicated by heavy lines should be wide printed circuit traces and should be kept as short as possible. For best results, external components should be located as close to the switcher lC as possible using ground plane construction or single point grounding. If open core inductors are used, special care must be taken as to thelocation and positioning of this type of inductor. Allowing the inductor flux to intersect sensitive feedback, lC groundpath and COUT wiring can cause problems. When using the adjustable version, special care must be taken as to the location of the feedback resistors and the associated wiring. Physically locate both resistors near the IC, and route the wiring away from the inductor, especially an open core type of inductor.HTC7Oct 2004 - Rev 0元器件交易网/doc/a66360844.html,3.0A, 15V, Step-Down Switching RegulatorLM2596PIN FUNCTION DESCRIPTION Symbol 1VinDescription This pin is the positive input supply for the LM2596 step–down switching23 45regulator.In order to minimize voltage transients and to supply the switching currents needed by the regulator, a suitable input bypass capacitor must be present .(Cin in Figure 1). Output This is the emitter of the internal switch. The saturation voltage Vsat of this output switch is typically 1.5 V. It should be kept in mind that the PCB area connected to this pin should be kept to a minimum in order to minimize coupling to sensitive circuitry. Circuit ground pin. See the information about the printed circuit board layout. Gnd Feedback This pin senses regulated outputvoltage to complete the feedback loop. The signal is divided by the internal resistor divider network R2, R1 and applied to the non–inverting input of the internal error amplifier. In the Adjustable version of the LM2596 switching regulator this pin is the direct input of the error amplifier and the resistor network R2, R1 is connected externally to allow programming of the output voltage. ON/OFF It allows the switching regulator circuit to be shut down using logic level signals, thus dropping the total input supply current to approximately 80 mA. The threshold voltage is typically 1.4 V. Applying a voltage above this value (up to +Vin) shuts the regulator off. If the voltage applied to this pin is lower than 1.4V or if this pin is left open, the regulator will be in the "on" conditionHTC8Oct 2004 - Rev 0元器件交易网/doc/a66360844.html,3.0A, 15V, Step-Down Switching RegulatorLM2596PACKAGES DIMENSION : TO220-5LHTC9Oct 2004 - Rev 0元器件交易网/doc/a66360844.html,3.0A, 15V, Step-Down Switching RegulatorPACKAGES DIMENSION : TO220V-5LLM2596HTC10Oct 2004 - Rev 0元器件交易网/doc/a66360844.html, 3.0A, 15V, Step-Down Switching RegulatorLM2596PACKAGES DIMENSION : TO263-5LHTC11Oct 2004 - Rev 0。

EM9636BBD产品说明书

EM9636B/BD产品说明书图1声明:此说明书归北京中泰研创科技有限公司所有。

未经本公司授权,任何公司及个人不得以盈利目的进行复制、抄袭、翻译或传播。

订购产品前,请详细了解产品性能是否符合用户需求。

说明书描述了产品的基本功能,若客户有特殊要求需要增加其他功能,请与本公司工程师联系。

说明书的内容力求准确、可靠。

本公司对侵权使用说明书所造成的后果不承担任何法律责任。

安全使用常识:•使用前请务必仔细阅读产品说明书。

•禁止带电插拔,以免瞬间冲击电压过大烧毁敏感元器件。

•避免频繁开机,以免对产品造成损坏。

目录第一章产品介绍 (3)1.1 概述 (3)1.2 特点 (3)1.3 一般特性 (5)第二章安装说明 (6)2.1 初始检查 (6)2.2 跳线分布图 (6)2.3 跳线设置 (6)2.3.1 模拟输入量程跳线说明 (7)2.3.2 模拟输入单端/差分方式跳线说明 (7)2.3.3 模拟输入电压/电流方式跳线说明 (7)2.3.4 模拟输出跳线说明 (8)2.3.5 模拟输出上电状态跳线说明 (8)2.3.6 加载默认网络设置跳线说明 (8)2.3.7 写保护跳线说明 (9)2.4 设备的安装 (9)2.4.1 使用网络接口时硬件安装 (9)2.4.2 使用网络接口时软件安装 (9)2.4.3 使用USB接口时硬件安装 (10)2.4.4 使用USB接口时软件安装 (10)2.4.5 设置更改模块参数设置 (10)第三章连接与测试 (13)3.1 管脚分布图 (13)3.1.1管脚功能定义说明 (13)3.2 模拟输入连接 (14)3.2.1 模拟信号种类 (14)3.2.2 单端模拟输入连接 (15)3.2.3 差分模拟输入连接 (15)3.3 模拟输出连接 (17)3.3.1 电压模拟输出连接 (17)3.3.2 电流模拟输出连接 (17)3.4 计数器输入连接 (18)3.5 数字量输入连接及注意事项 (18)3.6 数字量输出的连接 (19)3.7 编码器输入的连接 (20)3.8 PWM输出的连接 (21)3.9 SD卡的连接 (21)3.10 外触发与外时钟的连接 (21)3.11 测试 (21)3.8.1 模拟输入功能测试 (23)3.8.2 模拟输出功能测试 (24)3.8.3 计数器功能测试 (25)3.8.4 频率输入功能测试 (26)3.8.5 数字量输入功能测试 (27)3.8.6 数字量输出功能测试 (29)第四章原理说明 (31)4.1数据采集触发方式详解 (31)4.1.1采样时钟 (32)4.1.2采样方式 (32)4.1.3 触发信号 (32)4.1.4 边沿触发 (32)4.1.5 电平触发 (33)4.2 指示灯功能详解 (35)4.2.1 红灯,电源指示灯 (35)4.2.2 绿灯,采集指示灯 (35)4.2.3 黄灯,离线采集指示灯 (35)4.3 PWM脉冲生成 (36)第五章结构说明 (36)5.1结构图(尺寸图) (36)附录:....................................................................................................................................................... 错误!未定义书签。

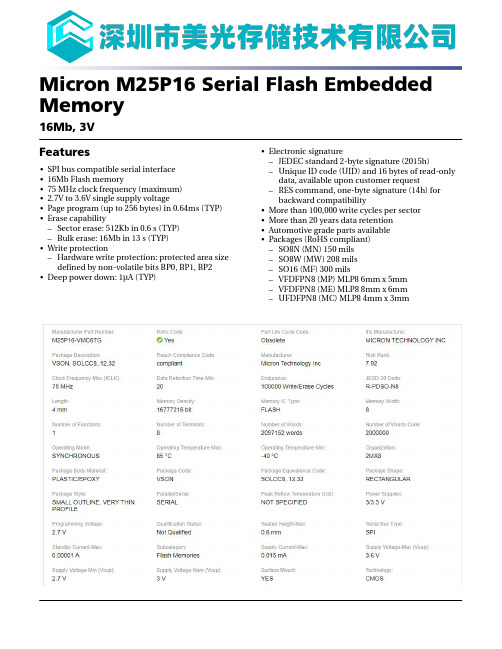

MEMORY存储芯片M25P16-VMC6TG中文规格书

Micron M25P16 Serial Flash Embedded Memory16Mb, 3V Features•SPI bus compatible serial interface •16Mb Flash memory•75 MHz clock frequency (maximum)•2.7V to 3.6V single supply voltage•Page program (up to 256 bytes) in 0.64ms (TYP)•Erase capability–Sector erase: 512Kb in 0.6 s (TYP)–Bulk erase: 16Mb in 13 s (TYP)•Write protection–Hardware write protection: protected area size defined by non-volatile bits BP0, BP1, BP2•Deep power down: 1µA (TYP)•Electronic signature–JEDEC standard 2-byte signature (2015h)–Unique ID code (UID) and 16 bytes of read-only data, available upon customer request–RES command, one-byte signature (14h) for backward compatibility•More than 100,000 write cycles per sector •More than 20 years data retention •Automotive grade parts available •Packages (RoHS compliant)–SO8N (MN) 150 mils –SO8W (MW) 208 mils –SO16 (MF) 300 mils–VFDFPN8 (MP) MLP8 6mm x 5mm –VFDFPN8 (ME) MLP8 8mm x 6mm –UFDFPN8 (MC) MLP8 4mm x 3mmMicron M25P16 Serial Flash Embedded MemoryImportant Notes and WarningsFunctional DescriptionThe M25P16 is an 16Mb (2Mb x 8) serial Flash memory device with advanced write pro-tection mechanisms accessed by a high speed SPI-compatible bus. The device supports high-performance commands for clock frequency up to 75MHz.The memory can be programmed 1 to 256 bytes at a time using the PAGE PROGRAM command. It is organized as 32 sectors, each containing 256 pages. Each page is 256bytes wide. Memory can be viewed either as 8,192 pages or as 2,097,152 bytes. The en-tire memory can be erased using the BULK ERASE command, or it can be erased one sector at a time using the SECTOR ERASE command.This datasheet details the functionality of the M25P16 device based on 110nm process.Figure 1: Logic DiagramS#V CCHOLD#V SSDQ1C DQ0W#Table 1: Signal NamesMicron M25P16 Serial Flash Embedded MemoryFunctional DescriptionFigure 5: Bus Master and Memory Devices on the SPI BusSS2.Resistors (R) ensure that the memory device is not selected if the bus master leaves theS# line High-Z.3.The bus master may enter a state where all I/O are High-Z at the same time; for exam-ple, when the bus master is reset. Therefore, C must be connected to an external pull-down resistor so that when all I/O are High-Z, S# is pulled HIGH while C is pulled LOW.This ensures that S# and C do not go HIGH at the same time and that the t SHCH require-ment is met.4.The typical value of R is 100kΩ, assuming that the time constant R × C p (C p = parasiticcapacitance of the bus line) is shorter than the time during which the bus master leavesthe SPI bus High-Z.5.Example: Given that C p = 50pF (R × C p= 5μs), the application must ensure that the busmaster never leaves the SPI bus High-Z for a time period shorter than 5μs.质量等级领域:宇航级IC、特军级IC、超军级IC、普军级IC、禁运IC、工业级IC,军级二三极管,功率管等;应用领域:航空航天、船舶、汽车电子、军用计算机、铁路、医疗电子、通信网络、电力工业以及大型工业设备祝您:工作顺利,生活愉快!以深圳市美光存储技术有限公司提供的参数为例,以下为M25P16-VMC6TG的详细参数,仅供参考。

Samsung-NAND-FLASH命名规则

三星的pure nand flash〔就是不带其他模块只是nand flash存储芯片〕的命名规那么如下:1. Memory (K)2. NAND Flash : 93. Small Classification(SLC : Single Level Cell, MLC : Multi Level Cell,SM : Smart Media, S/B : Small Block)1 : SLC 1 Chip XD Card2 : SLC 2 Chip XD Card4 : SLC 4 Chip XD CardA : SLC + Muxed I/ F ChipB : Muxed I/ F ChipD : SLC Dual SME : SLC DUAL (S/ B)F : SLC NormalG : MLC NormalH : MLC QDPJ : Non-Muxed OneNandK : SLC Die StackL : MLC DDPM : MLC DSPN : SLC DSPQ : 4CHIP SMR : SLC 4DIE STACK (S/ B)S : SLC Single SMT : SLC SINGLE (S/ B)U : 2 STACK MSPV : 4 STACK MSPW : SLC 4 Die Stack4~5. Density〔注:实际单位应该是bit,而不是Byte〕12 : 512M16 : 16M28 : 128M32 : 32M40 : 4M56 : 256M64 : 64M80 : 8M1G : 1G2G : 2G4G : 4G8G : 8GAG : 16GBG : 32GCG : 64GDG : 128G00 : NONE6~7. Organization00: NONE08: x816: x168. VccA : 1.65V~3.6VB : 2.7V (2.5V~2.9V)C : 5.0V (4.5V~5.5V)D : 2.65V (2.4V ~ 2.9V)E : 2.3V~3.6VR : 1.8V (1.65V~1.95V)Q : 1.8V (1.7V ~ 1.95V)T : 2.4V~3.0VU : 2.7V~3.6VV : 3.3V (3.0V~3.6V)W : 2.7V~5.5V, 3.0V~5.5V0 : NONE9. Mode0 : Normal1 : Dual nCE & Dual R/ nB4 : Quad nCE & Single R/ nB5 : Quad nCE & Quad R/ nB9 : 1st block OTPA : Mask Option 1L : Low grade10. GenerationM : 1st GenerationA : 2nd GenerationB : 3rd GenerationC : 4th GenerationD : 5th Generation11. "─"12. PackageA : COBB : TBGAC : CHIP BIZD : 63-TBGAE : TSOP1 (Lead-Free, 1217)F : WSOP (Lead-Free)G : FBGAH : TBGA (Lead-Free)I : ULGA (Lead-Free)J : FBGA (Lead-Free)K : TSOP1 (1217)L : LGAM : TLGAN : TLGA2P : TSOP1 (Lead-Free)Q : TSOP2 (Lead-Free)S : SMART MEDIAT : TSOP2U : COB (MMC)V : WSOPW : WAFERY : TSOP113. TempC : CommercialI : IndustrialS : SmartMediaB : SmartMedia BLUE0 : NONE (Containing Wafer, CHIP, BIZ, Exceptionhandling code)3 : Wafer Level 314. Bad BlockA : Apple Bad BlockB : Include Bad BlockD : Daisychain SampleK : Sandisk BinL : 1~5 Bad BlockN : ini. 0 blk, add. 10 blkS : All Good Block0 : NONE (Containing Wafer, CHIP, BIZ, Exceptionhandling code)15. NAND-Reserved0 : Reserved16. Packing Type- Common to all products, except of Mask ROM- Divided into TAPE & REEL(In Mask ROM, divided into TRAY, AMMO Packing Separately) 【举例说明】K9GAG08U0M 详细信息如下:1. Memory (K)2. NAND Flash : 93. Small Classification(SLC : Single Level Cell, MLC : Multi Level Cell,SM : SmartMedia, S/B : Small Block)G : MLC Normal4~5. DensityAG : 16G (Note: 这里单位是bit而不是byte,因此实际大小是16Gb=2GB)0 : Normal (x8)7. Organization0 : NONE 8 : x88. VccU : 2.7V~3.6V9. Mode0 : Normal10. GenerationM : 1st Generation11. "─"12. PackageP : TSOP1 (Lead-Free)13. TempC : Commercial14. Customer Bad BlockB : Include Bad Block15. Pre-Program Version0 : None整体描述就是:K9GAG08U0M是,三星的MLC Nand Flash,工作电压为2.7V~3.6V,x8〔即I/O是8位〕,大小是2GB〔16Gb〕,TSOP1封装。

MN6626中文资料

For Audio Equipment

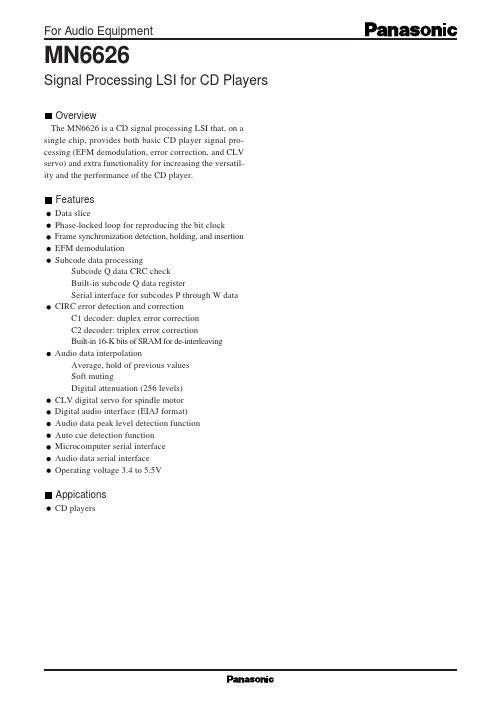

MN6626

Signal Processing LSI for CD Players

Overview

The MN6626 is a CD signal processing LSI that, on a single chip, provides both basic CD player signal processing (EFM demodulation, error correction, and CLV servo) and extra functionality for increasing the versatility and the performance of the CD player.

49

18.70±0.40 (2.35±0.20)

2.60max.

2.20±0.20

0.10±0.10

0.15 -0.05

+0.10

0.15 SEATING PLANE

(1.50±0.20)

0 to 10°

SYNC DETECTION

FLAG

RESY 16K SRAM SUBCODE DEMODULATION

60 EFM DATA DEMODULATION

SYNC INTERPOLATION PROTECTION

INTERPOLATION SOFT MUTING DIGITAL ATTENUATION

LDG RDG SRDATA SCK LRCK IPFLAG BYTCK FCLK WDCK TX MEMP

SBCK SSEL CLDCK BLKCK

50 58 38 39

Q-CODE REGISTER

欧泰克 936 无铅焊台 说明书

使用说明书实际目 录一、包装清单 (1)二、注意事项 (1)三、部件名称 (2)四、焊台的装置和使用 (2)五、烙铁头的维护和使用 (4)六、保养 (5)七、校准烙铁的温度 (5)八、烙铁头 (5)九、排除故障指南 (6)十、如何检查发热元件和组装电线破损 (7)十一、电路图 (9)十二、规格 (9)十三、部件清单……………………………………………………………10一、包装清单请检查包装,以证实所列清单项目正确无误焊台主机 (1)焊台手柄 (1)烙铁架(包括湿海绵) (1)六角头扳手(1.5mm) (1)使用说明书 (1)二、注意事项▲ 警告本使用说明书之“警告”和“注意”的定义如下:● 警告:滥用可能导致使用者死亡或重伤。

● 注意:滥用可能导致使用者受伤或对涉及物体造成实质性破坏。

为您本人安全着想,请严格遵守“注意事项”。

▲ 注意当电源接通时,烙铁头温度高于摄氏200至480度(华氏392至896度)。

鉴于滥用可能导致灼伤或火患,请严格遵守以下事项:● 切勿触及烙铁头附近的金属部分。

● 切勿在易燃物体附近使用烙铁头。

● 通知工厂其它他人士,烙铁头极为灼热,可能引发危险事故。

● 休息时或完工后应关掉电源。

● 更换部件或装置烙铁头时,应关掉电源,并待烙铁头冷却至室温。

B. 添水至下图所示水平面。

小块海绵吸收水分后,可使置于其上的大块海绵一直 保持潮湿状态。

※ 也可以单用大块海绵(省去小块海绵和添水)。

C. 然后沾湿大块清洁海绵,置于烙铁架底座。

2. 连接▲注意:进行连接和解开烙铁时,切记要关掉电源,以免损坏印刷电路板。

A. 将电线装置连接烙铁插座。

B. 将烙铁置放于烙铁座。

C. 将插头插入电源插座。

※ 切记要接地。

3. 设定温度A. 将控温旋钮设定在所需温度点。

B. 锁定控温旋钮。

C. 此焊台配有温度调节钮锁。

按顺时针方向拧紧对准定位然后插入为免损坏焊台,及保持作业环境之安全,应遵守下列事项:● 切勿使用烙铁头进行焊接以外的工作。

6300B系列工业计算机产品选择指南说明书

1 x bootable CFast SATA III slot on board with external rear access 1 x onboard connector for direct insertion of M.2 2242 / 2280 SSD key M PCIex4 2 x onboard connector for 2.5 in. SSD/HDD SATA III 1 or 2 x extractable drawers for 2.5 in. units

Dual 4K Quad core Intel Atom x7-E3950 4 GB

1 x RS232 (DB9M)

1 x DVI-D

2 x PCIe x 4 or 1 x PCI + 1 x PCIe x4 (5 Gb/s), max 10W total

24V DC (18…32V DC) isolated, UPS option (future)

1 x DVI-D 1 x PCI or 1 x PCIe x4 (5 Gb/s) 24V DC (18…32V DC) isolated, UPS option (future)

-20…60 °C

CE, cULus Listed, EAC, KC and RCM Wall, VESA Mount, DIN Rail, Bookshelf, Machine N/A

Dual Single core Intel Atom E3815 1 GB N/A N/A

N/A

Fanless ThinManager® 24V DC

Dell PowerEdge M620 Systems 用户手册说明书

Dell PowerEdge M620 Systems(适用于 Dell PowerEdge VRTX 机柜)用户手册管制型号: HHB管制类型: HHB003注、小心和警告注: “注”表示可以帮助您更好地使用计算机的重要信息。

小心: “小心”表示可能会损坏硬件或导致数据丢失,并说明如何避免此类问题。

警告: “警告”表示可能会造成财产损失、人身伤害甚至死亡。

版权所有© 2014 Dell Inc. 保留所有权利。

本产品受美国、国际版权和知识产权法律保护。

Dell™和 Dell 徽标是 Dell Inc. 在美国和 / 或其他管辖区域的商标。

所有此处提及的其他商标和产品名称可能是其各自所属公司的商标。

2014–10Rev. A01目录1 关于系统 (7)简介 (7)前面板部件和指示灯 (8)使用 USB 软盘或 USB DVD/CD 驱动器 (8)硬盘驱动器功能部件 (8)您可能需要的其他信息 (9)2 使用系统设置程序和引导管理器 (11)选择系统引导模式 (12)进入系统设置 (12)响应错误消息 (12)使用系统设置程序导航键 (12)系统设置选项 (12)系统设置程序主屏幕 (13)系统 BIOS 屏幕 (13)System Information(系统信息)屏幕 (14)Memory Settings(内存设置)屏幕 (14)Processor Settings(处理器设置)屏幕 (15)SATA Settings(SATA 设置)屏幕 (16)Boot Settings(引导设置)屏幕 (16)Integrated Devices(集成设备)屏幕 (17)Serial Communications(串行通信)屏幕 (18)系统配置文件设置屏幕 (18)System Security(系统安全)屏幕 (19)Miscellaneous Settings(其它设置) (20)系统和设置密码功能 (21)分配系统密码和/或设置密码 (21)使用系统密码保护系统安全 (22)删除或更改现有系统密码和/或设置密码 (22)在已启用设置密码的情况下进行操作 (22)进入 UEFI 引导管理器 (23)使用引导管理器导航键 (23)Boot Manager(引导管理器)屏幕 (23)UEFI Boot(UEFI 引导)菜单 (24)嵌入式系统管理 (24)iDRAC 设置公用程序 (24)进入 iDRAC 设置公用程序 (25)3 安装服务器模块组件 (26)建议工具 (26)安装和卸下服务器模块 (26)卸下服务器模块 (26)安装服务器模块 (28)打开与合上服务器模块 (28)打开服务器模块 (28)合上服务器模块 (29)服务器模块内部 (30)冷却导流罩 (30)卸下冷却导流罩 (30)安装冷却导流罩 (31)系统内存 (31)一般内存模块安装原则 (33)模式特定原则 (34)内存配置示例 (35)卸下内存模块 (38)安装内存模块 (39)PCIe 夹层卡 (40)卸下 PCIe 夹层卡 (40)安装 PCIe 夹层卡 (41)管理提升卡 (42)更换 SD 卡 (42)内部 USB 盘 (43)SD vFlash 卡 (43)装回 SD vFlash 卡 (43)网络子卡/LOM 提升卡 (44)卸下网络子卡/LOM 提升卡 (44)安装网络子卡/LOM 提升卡 (45)处理器 (45)卸下处理器 (46)安装处理器 (48)硬盘驱动器 (49)硬盘驱动器/SSD 安装原则 (50)卸下硬盘驱动器/SSD (50)安装硬盘驱动器/SSD (50)进行硬盘驱动器维修前的关机程序 (51)配置引导驱动器 (51)从硬盘驱动器/SSD 托盘中卸下硬盘驱动器/SSD (51)将硬盘驱动器/SSD 安装到硬盘驱动器/SSD 托盘中 (52)硬盘驱动器/SSD 背板 (52)卸下硬盘驱动器/SSD 背板 (52)安装硬盘驱动器/SSD 背板 (53)系统板 (54)卸下系统板 (54)安装系统板 (55)NVRAM 备用电池 (56)更换 NVRAM 备用电池 (56)存储控制器卡 (57)卸下存储控制器卡 (57)安装存储控制器卡 (58)4 系统故障排除 (59)安全第一—为您和您的系统着想 (59)系统内存故障排除 (59)硬盘驱动器故障排除 (59)USB 设备故障排除 (60)内部 SD 卡故障排除 (60)处理器故障排除 (61)系统板故障排除 (61)NVRAM 备用电池故障排除 (61)5 使用系统诊断程序 (63)Dell Online Diagnostics (63)Dell 嵌入式系统诊断程序 (63)何时使用 Embedded System Diagnostics(嵌入式系统诊断程序) (63)运行嵌入式系统诊断程序 (63)从外部介质运行嵌入式系统诊断程序 (64)系统诊断程序控件 (64)6 跳线和连接器 (65)系统板跳线设置 (65)系统板连接器 (66)禁用已忘记的密码 (67)7 技术规格 (68)8 系统消息 (71)LCD 状态信息 (71)查看 LCD 信息 (71)删除 LCD 消息 (71)系统错误消息 (71)警告信息 (141)诊断消息 (142)警报消息 (142)9 获得帮助 (143)联系 Dell (143)1关于系统简介本说明文件提供了有关 Dell PowerEdge M620 服务器模块的信息,该模块专为 PowerEdge VRTX 机柜配置,并且可以通过服务器模块上的标记为PCIe的标签来进行识别。

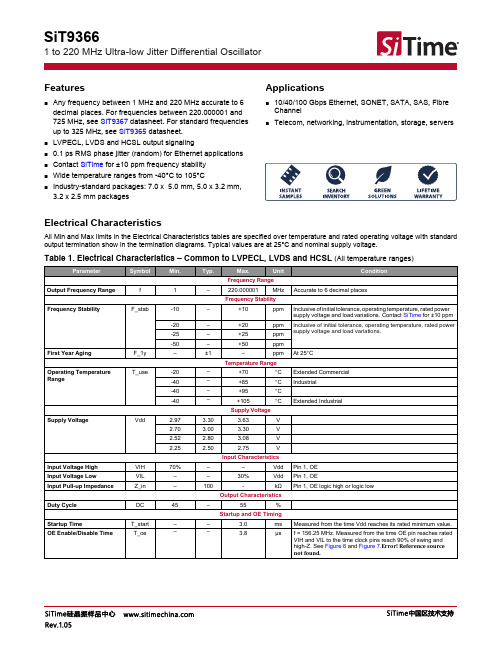

SiT9366数据手册-1-220MHz任意频率SiTime低抖动差分晶振

Output Characteristics VOD ΔVOD VOS ΔVOS Tr, Tf 250 – 1.125 – – – – – – 400 450 50 1.375 50 470 mV mV V mV ps See Figure 4 See Figure 4 See Figure 4 See Figure 4 Measured with 2 pF capacitive loading to GND, 20% to 80%, see Figure 5 f = 100, 156.25 or 212.5 MHz, Vdd = 3.3V or 2.5V f = 156.25 MHz, Integration bandwidth = 12 kHz to 20 MHz, all Vdd levels, includes spurs. Temperature ranges -20 to 70ºC and -40 to 85ºC f = 156.25 MHz, Integration bandwidth = 12 kHz to 20 MHz, all Vdd levels, includes spurs. Temperature ranges -40 to 95ºC and -40 to 105ºC f = 156.25 or 322.265625 MHz, IEEE802.3-2005 10GbE jitter mask integration bandwidth = 1.875 MHz to 20 MHz, includes spurs, all Vdd levels. f = 100, 156.25 or 212.5 MHz, Vdd = 3.3V or 2.5V f = 156.25 MHz, Integration bandwidth = 12 kHz to 20 MHz, all Vdd levels, includes spurs. Temperature ranges -20 to 70ºC and -40 to 85ºC f = 156.25 MHz, Integration bandwidth = 12 kHz to 20 MHz, all Vdd levels, includes spurs. Temperature ranges -40 to 95ºC and -40 to 105ºC f = 156.25 or 322.265625 MHz, IEEE802.3-2005 10GbE jitter mask integration bandwidth = 1.875 MHz to 20 MHz, includes spurs, all Vdd levels.

PC87366中文资料

PC87366 128-Pin LPC SuperI/O with System Hardware Monitoring, MIDI and Game PortsGeneral DescriptionThe PC87366,a member of National Semiconductor’s 128-pin LPC SuperI/O family,combines National’s System Hardware Monitoring capability with a Musical Instrument Digital Interface (MIDI)Port and game port inputs for up to two joysticks.The PC87366is PC99and ACPI compliant,and offers a single-chip solution to the most commonly used PC I/O peripherals.System Hardware Monitoring provides minimum power con-sumption and maximum operating efficiency within the system environment.It integrates National’s diode-based or thermistor-based Temperature Sensor (TMS)with National’s Voltage Lev-el Monitor (VLM)for full,PC system thermal control.The PC87366monitors system voltages using 8-bit Analog to Dig-ital (A/D)conversion with seven analog input channels and four internal measuring points.The PC87366also incorporates:Fan Speed Control and Monitor (FSCM)for three fans,extended wake-up support for a wide range of wake-up events,system design protection features,a Floppy Disk Controller (FDC),a Keyboard and Mouse Controller (KBC),a full IEEE 1284Parallel Port,two enhanced Serial Ports (UARTs),one with Infrared (IR)sup-port,ACCESS.bus ®Interface (ACB),System Wake-Up Control (SWC),General-Purpose Input/Output (GPIO)sup-port for 40ports,Interrupt Serializer for Parallel IRQs and an enhanced WATCHDOG ™ timer (WDT).Outstanding FeaturesqSystem Hardware Monitoring including:—Diode-based or thermistor-based T emperature Sen-sor (TMS)—Voltage Level Monitor (VLM) with VID inputs q MIDI interface compatible with MPU-401UART mode q Game port inputs for up to two joysticksqExtended Wake-Up support,including legacy/ACPI power button support,direct power supply control in response to wake-up events,power-fail recovery qProtection features,including chassis intrusion detection,GPIO lock and pin configuration lockq Fan Speed Control and Monitor for three fans q Serial IRQ support (15options)q Interrupt Serializer (11Parallel IRQs to Serial IRQ)qBus interface,based on Intel’s LPC Interface Specifi-cation Revision 1.0,September 29th,1997q ACCESS.bus interface,SMBus physical layer compatible q40GPIO Ports (29standard,including 15with Assert IRQ/SMI/PWUREQs interrupts;11V SB -powered)q Blinking LEDsq128-pin PQFP PackageBlock DiagramSystem Wake-UpSerial Port 2IEEE 1284Parallel PortPorts Keyboard &Mouse I/F SCL ACCESS.bus Floppy Disk ControllerFloppy Drive InterfaceKeyboard &Serial Infrared Interface InterfaceControl Bus InterfaceLPC Interface I/O3 Control WATCHDOGTimer WDOSerial Port 1Serial InterfaceOutputs Fan Speed Control & Monitor Interface Mouse Controllerwith IRGPIO Ports3 Monitor InputsSDA Serial IRQ Analog Inputs System Parallel Port Interface Diode InterfaceSMI PortsHardware MonitoringV REF MIDIInterface MIDI &Game PortsGame Inputs Wake-Up EventsPWUREQ Power Control V DD V BdAT V SBAV DD ACCESS.bus® is a registered trademark of Digital Equipment Corporation.I2C® is a registered trademark of Philips Corporation.IBM®, MicroChannel®, PC-AT® and PS/2® are registered trademarks of International Business Machines Corporation.Microsoft® and Windows® are registered trademarks of Microsoft Corporation.TRI-STATE® is a registered trademark of National Semiconductor Corporation.WATCHDOG‰ is a trademark of National Semiconductor Corporation.SMBus® is a registered trademark of Intel Corporation.© 1999 National Semiconductor CorporationPRELIMINARYJanuary 11,1999PC87366128-Pin LPC SuperI/O with System Hardware Monitoring,MIDI and Game PortsFeatures•Voltage Level Monitor (VLM)—Seven analog inputs that can support both positive and negative voltages—Four internal measuring points—Three thermistor-based temperature monitoring channels—Internal or external V REF—VID inputs—Meets ACPI and DMI requirements for system volt-age monitoring•Temperature Sensor (TMS)—Up to two remote diode inputs—Environment temperature sensing via an internal di-ode—A/D analog channels provide thermal inputs to di-rectly sense die temperature of remote diodes —Meets ACPI and DMI requirements for thermal man-agement—Standby mode to minimize power consumption •Extended Wake-Up—Legacy and ACPI power button support—Direct power supply control in response to wake-up events—Power-fail recovery•Musical Instrument Digital Interface (MIDI) Port —Compatible with MPU-401 UART mode—16-byte Receive and T ransmit FIFOs—Loopback mode supportq Game Port—Full digital implementation—Supports up to two analog joysticks •Protection—Chassis intrusion detection (CHASI, CHASO)—GPIO lock—Pin configuration lock•40 General-Purpose I/O (GPIO) Ports—29standard,with Assert IRQ/SMI/PWUREQ for15 ports—11 V SB-powered—Programmable drive type for each output pin(open-drain, push-pull or output disable)—Programmable option for internal pull-up resistor on each input pin—Output lock option—Input debounce mechanism•Fan Speed Control and Fan Speed Monitor (FSCM)—Supports different fan types—Speed monitoring for three fanst Digital filtering of the tachometer input signalt Alarm for fan slower than programmable thresh-old speedt Alarm for fan stop—Three speed control lines with Pulse Width Modula-tion (PWM)t Output signal in the range of 6 Hz to 93.75 KHzt Duty cycle resolution of 1/256•LPC System Interface—Synchronous cycles, up to 33 MHz bus clock—8-bit I/O cycles—Up to four DMA channels—8-bit DMA cycles—Basic read,write and DMA bus cycles are13clock cycles long•PC99 and ACPI Compliant—PnP Configuration Register structure—Flexible resource allocation for all logical devices t Relocatable base addresst15 IRQ routing optionst4optional8-bit DMA channels(where applicable)•Floppy Disk Controller (FDC)—Programmable write protect—FM and MFM mode support—Enhanced mode command for three-mode Floppy Disk Drive (FDD) support—Perpendicular recording drive support for 2.88 MB—Burst and non-burst modes—Full support for IBM T ape Drive register(TDR)im-plementation of AT and PS/2 drive types—16-byte FIFO—Software compatible with the PC8477,which con-tains a superset of the FDC functions in themicroDP8473,the NEC microPD765A and theN82077—High-performance, digital separator—Standard 5.25” and 3.5” FDD support•Parallel Port—Software or hardware control—Enhanced Parallel Port(EPP)compatible with new version EPP 1.9 and IEEE 1284 compliant—EPP support for version EPP1.7of the Xircom spec-ification—EPP support as mode4of the Extended Capabilities Port (ECP)—IEEE 1284 compliant ECP, including level 2—Selection of internal pull-up or pull-down resistor for Paper End (PE) pin—PCI bus utilization reduction by supporting a de-mand DMA mode mechanism and a DMA fairnessmechanism—Protection circuit that prevents damage to the paral-lel port when a printer connected to it powers up oris operated at high voltages,even if the device is inpower-down—Output buffers that can sink and source 14 mA•Serial Port 1 (UART1)—Software compatible with the 16550A and the 164502Features(Continued)3—Shadow register support for write-only bit monitoring —UART data rates up to 1.5 Mbaud•Serial Port 2 with Infrared (UART2)—Software compatible with the 16550A and the 16450—Shadow register support for write-only bit monitoring —UART data rates up to 1.5 Mbaud —HP-SIR—ASK-IR option of SHARP-IR —DASK-IR option of SHARP-IR—Consumer Remote Control supports RC-5,RC-6,NEC, RCA and RECS 80—Non-standard DMA support −1 or 2 channels —PnP dongle support •Keyboard and Mouse Controller (KBC)—8-bit microcontroller—Software compatible with the 8042AH and PC87911microcontrollers— 2 KB custom-designed program ROM —256 bytes RAM for data—Five programmable dedicated open-drain I/O lines —Asynchronous access to two data registers and onestatus register during normal operation —Support for both interrupt and polling —93 instructions —8-bit timer/counter—Support for binary and BCD arithmetic—Operation at 8MHz,12MHz or 16MHz (programma-ble option)—Can be customized by using the PC87323,which in-cludes a RAM-based KBC as a development plat-form for KBC code•ACCESS.bus Interface (ACB)—Serial interface compatible with SMBus physical layer —Compatible with Philips’ I 2C ®—ACB master and slave—Supports polling and interrupt controlled operation —Optional internal pull-up on SDA and SCL pins•WATCHDOG Timer (WDT)—Times out the system based on user-programmabletime-out period—System power-down capability for power saving —User-defined trigger events to restart WATCHDOG —Optional routing of WATCHDOG output on IRQand/or SMI lines•System Wake-Up Control (SWC)—Power-up request upon detection of Keyboard,Mouse,RI1,RI2,RING activity and General-Pur-pose Input Events, as follows:t Preprogrammed Keyboard or Mouse sequence t External modem ring on serial portt Ring pulse or pulse train on the RING input signal t Preprogrammed CEIR address in a preselectedstandard (NEC, RCA or RC-5)t General-Purpose Input Events t IRQs of internal logical devices —Optional routing of power-up request on IRQ,SMIand/or PWBTOUT—Battery-backed event configuration—Programmable V SB -powered output for blinkingLEDs (LED1, LED2) control•Clock Sources—48 MHz clock input—LPC clock, up to 33 MHz—On-chip low frequency clock generator for wake-up•Power Supplies— 3.3V supply operation —Main (V DD and AV DD )—Standby (V SB )—Battery backup (V BA T )—All pins are 5V tolerant and back-drive protected,ex-cept LPC bus pins•Strap Configuration—Base Address (BADDR)strap to determine the baseaddress of the Index-Data register pair—T est strap to force the device into test mode (re-served for National Semiconductor use)—Power Supply and LED Configuration (PSLDC0,1)straps to determine the power suppy control func-tions and the V SB power-up defaults of LED2—Power Supply On Polarity (PSONPOL)strap to setPSON active state and output typeDatasheet Revision RecordRevision Date Status CommentsNovember1998Draft0.3Specification subject to change without notice;MIDI andGame Port information is incompleteJanuary1999Preliminary1.0Specification subject to change without notice;PowerSupply Control and LED sections in Chapter2areincompleteItem Topic Change/Correction Location 4Table of ContentsDatasheet Revision Record (4) (4)1.0Signal/Pin Connection and Description1.1CONNECTION DIAGRAM (16)1.2BUFFER TYPES AND SIGNAL/PIN DIRECTORY (17)1.3PIN MULTIPLEXING (22)1.4DETAILED SIGNAL/PIN DESCRIPTIONS (24)1.4.1ACCESS.bus Interface (ACB) (24)1.4.2Bus Interface (24)1.4.3Clock (24)1.4.4Fan Speed Control and Monitor (FSCM) (24)1.4.5Floppy Disk Controller (FDC) (25)1.4.6Game Port (26)1.4.7General-Purpose Input/Output (GPIO) Ports (26)1.4.8Infrared (IR) (26)1.4.9Keyboard and Mouse Controller (KBC) (27)1.4.10Musical Instrument Digital Interface (MIDI) Port (27)1.4.11Parallel Port (28)1.4.12Power and Ground (28)1.4.13Protection (29)1.4.14Serial Port 1 and Serial Port 2 (29)1.4.15Strap Configuration (30)1.4.16System Hardware Monitoring (30)1.4.17System Wake-Up Control (31)1.4.18WATCHDOG Timer (WDT) (31)1.5INTERNAL PULL-UP AND PULL-DOWN RESISTORS (32)2.0Device Architecture and Configuration2.1OVERVIEW (34)2.2CONFIGURATION STRUCTURE AND ACCESS (34)2.2.1The Index-Data Register Pair (34)2.2.2Banked Logical Device Registers Structure (36)2.2.3Standard Logical Device Configuration Register Definitions (37)2.2.4Standard Configuration Registers (39)2.2.5Default Configuration Setup (40)2.2.6Power States (40)2.2.7Address Decoding (41)2.3PROTECTION (41)2.3.1Chassis Intrusion Detection (41)2.3.2Pin Configuration Lock (41)2.3.3GPIO Pin Function Lock (42)2.4POWER SUPPLY CONTROL (PSC) (42)2.5LED OPERATION AND STATES (44)2.6POWER SUPPLY CONTROL AND LED CONFIGURATION (44)2.7REGISTER TYPE ABBREVIATIONS (45)2.8SUPERI/O CONFIGURATION REGISTERS (45)2.8.1SuperI/O ID Register (SID) (46)2.8.2SuperI/O Configuration 1 Register (SIOCF1) (46)2.8.3SuperI/O Configuration 2 Register (SIOCF2) (47)2.8.4SuperI/O Configuration 3 Register (SIOCF3) (48)2.8.5SuperI/O Configuration 4 Register (SIOCF4) (49)2.8.6SuperI/O Configuration 5 Register (SIOCF5) (50)2.8.7SuperI/O Revision ID Register (SRID) (50)2.8.8SuperI/O Configuration 8 Register (SIOCF8) (51)2.8.9SuperI/O Configuration A Register (SIOCFA) (52)2.8.10SuperI/O Configuration B Register (SIOCFB) (53)2.8.11SuperI/O Configuration C Register (SIOCFC) (54)2.8.12SuperI/O Configuration D Register (SIOCFD) (55)2.9FLOPPY DISK CONTROLLER (FDC) CONFIGURATION (56)2.9.1General Description (56)2.9.2Logical Device 0 (FDC) Configuration (56)2.9.3FDC Configuration Register (57)2.9.4Drive ID Register (58)2.10PARALLEL PORT CONFIGURATION (59)2.10.1General Description (59)2.10.2Logical Device 1 (PP) Configuration (60)2.10.3Parallel Port Configuration Register (60)2.11SERIAL PORT 2 CONFIGURATION (61)2.11.1General Description (61)2.11.2Logical Device 2 (SP2) Configuration (61)2.11.3Serial Port 2 Configuration Register (61)2.12SERIAL PORT 1 CONFIGURATION (62)2.12.1Logical Device 3 (SP1) Configuration (62)2.12.2Serial Port 1 Configuration Register (62)2.13SYSTEM WAKE-UP CONTROL (SWC) CONFIGURATION (63)2.13.1Logical Device 4 (SWC) Configuration (63)2.14KEYBOARD AND MOUSE CONTROLLER (KBC) CONFIGURATION (64)2.14.1General Description (64)2.14.2Logical Devices 5 and 6 (Mouse and Keyboard) Configuration (65)2.14.3KBC Configuration Register (66)2.15GENERAL-PURPOSE INPUT/OUTPUT (GPIO) PORTS CONFIGURATION (67)2.15.1General Description (67)2.15.2Implementation (67)2.15.3Logical Device 7 (GPIO) Configuration (68)2.15.4GPIO Pin Select Register (69)2.15.5GPIO Pin Configuration Register (70)2.15.6GPIO Event Routing Register (71)62.16ACCESS.BUS INTERFACE (ACB) CONFIGURATION (72)2.16.1General Description (72)2.16.2Logical Device 8 (ACB) Configuration (72)2.16.3ACB Configuration Register (73)2.17FAN SPEED CONTROL AND MONITOR (FSCM) CONFIGURATION (74)2.17.1General Description (74)2.17.2Logical Device 9 (FSCM) Configuration (74)2.17.3Fan Speed Control and Monitor Configuration 1 Register (75)2.17.4Fan Speed Control and Monitor Configuration 2 Register (76)2.17.5Fan Speed Control OTS Configuration Register (76)2.18WATCHDOG TIMER (WDT) CONFIGURATION (77)2.18.1Logical Device 10 (WDT) Configuration (77)2.18.2WATCHDOG Timer Configuration Register (77)2.19GAME PORT (GMP) CONFIGURATION (78)2.19.1Logical Device 11 (GMP) Configuration (78)2.19.2Game Port Configuration Register (78)2.20MIDI PORT (MIDI) CONFIGURATION (79)2.20.1Logical Device 12 (MIDI) Configuration (79)2.20.2MIDI Port Configuration Register (79)2.21VOLTAGE LEVEL MONITOR (VLM) CONFIGURATION (80)2.21.1Logical Device 13 (VLM) Configuration (80)2.22TEMPERATURE SENSOR (TMS) CONFIGURATION (80)2.22.1Logical Device 14 (TMS) Configuration (80)3.0System Wake-Up Control (SWC)3.1OVERVIEW (81)3.2FUNCTIONAL DESCRIPTION (82)3.3EVENT DETECTION (83)3.3.1Modem Ring (83)3.3.2Telephone Ring (83)3.3.3Keyboard and Mouse Activity (84)3.3.4CEIR Address (84)3.3.5Standby General-Purpose Input Events (84)3.3.6GPIO-Triggered Events (84)3.3.7Software Event (84)3.3.8Module IRQ Wake-Up Event (85)3.4SWC REGISTERS (85)3.4.1SWC Register Map (85)3.4.2Wake-Up Events Status Register 0 (WK_STS0) (88)3.4.3Wake-Up Events Status Register (WK_STS1) (89)3.4.4Wake-Up Events Enable Register (WK_EN0) (90)3.4.5Wake-Up Events Enable Register 1 (WK_EN1) (91)3.4.6Wake-Up Configuration Register (WK_CFG) (92)3.4.7Wake-Up Events Routing to SMI Enable Register 0 (WK_SMIEN0) (93)3.4.8Wake-Up Events Routing to SMI Enable Register 1 (WK_SMIEN1) (94)3.4.9Wake-Up Events Routing to IRQ Enable Register 0 (WK_IRQEN0) (95)3.4.10Wake-Up Events Routing to IRQ Enable Register 1 (WK_IRQEN1) (96)3.4.11Wake-Up Extension 1 Enable Register 0 (WK_X1EN0) (97)3.4.12Wake-Up Extension 1 Enable Register 1 (WK_X1EN1) (98)3.4.13Wake-Up Extension 2 Enable Register 0 (WK_X2EN0) (99)3.4.14Wake-Up Extension 2 Enable Register 1 (WK_X2EN1) (100)3.4.15Wake-Up Extension 3 Enable Register 0 (WK_X3EN0) (101)3.4.16Wake-Up Extension 3 Enable Register 1 (WK_X3EN1) (102)3.4.17PS/2 Keyboard and Mouse Wake-Up Events (103)3.4.18PS/2 Protocol Control Register (PS2CTL) (104)3.4.19Keyboard Data Shift Register (KDSR) (104)3.4.20Mouse Data Shift Register (MDSR) (105)3.4.21PS/2 Keyboard Key Data Registers (PS2KEY0 - PS2KEY7) (105)3.4.22CEIR Wake-Up Control Register (IRWCR) (106)3.4.23CEIR Wake-Up Address Register (IRWAD) (107)3.4.24CEIR Wake-Up Address Mask Register (IRWAM) (107)3.4.25CEIR Address Shift Register (ADSR) (108)3.4.26CEIR Wake-Up Range 0 Registers (108)3.4.27CEIR Wake-Up Range 1 Registers (109)3.4.28CEIR Wake-Up Range 2 Registers (109)3.4.29CEIR Wake-Up Range 3 Registers (110)3.4.30Standby General-Purpose I/O (SBGPIO) Register Overview (111)3.4.31Standby GPIO Pin Select Register (SBGPSEL) (114)3.4.32Standby GPIO Pin Configuration Register (SBGPCFG) (115)3.4.33Standby GPIOE/GPIE Data Out Register 0 (SB_GPDO0) (117)3.4.34Standby GPIOE/GPIE Data In Register 0 (SB_GPDI0) (117)3.4.35Standby GPOS Data Out Register 1 (SB_GPDO1) (118)3.4.36Standby GPIS Data In Register 1 (SB_GPDI1) (118)3.5SWC REGISTER BITMAP (119)4.0Fan Speed Control4.1OVERVIEW (123)4.2FUNCTIONAL DESCRIPTION (123)4.3FAN SPEED CONTROL REGISTERS (124)4.3.1Fan Speed Control Register Map (124)4.3.2Fan Speed Control Pre-Scale Register (FCPSR) (124)4.3.3Fan Speed Control Duty Cycle Register (FCDCR) (125)4.4FAN SPEED CONTROL BITMAP (125)5.0Fan Speed Monitor5.1OVERVIEW (126)5.2FUNCTIONAL DESCRIPTION (126)5.3FAN SPEED MONITOR REGISTERS (127)5.3.1Fan Speed Monitor Register Map (127)85.3.2Fan Monitor Threshold Register (FMTHR) (128)5.3.3Fan Monitor Speed Register (FMSPR) (128)5.3.4Fan Monitor Control and Status Register (FMCSR) (128)5.4FAN SPEED MONITOR BITMAP (129)6.0General-Purpose Input/Output (GPIO) Port6.1OVERVIEW (130)6.2BASIC FUNCTIONALITY (131)6.2.1Configuration Options (131)6.2.2Operation (131)6.3EVENT HANDLING AND SYSTEM NOTIFICATION (132)6.3.1Event Configuration (132)6.3.2System Notification (132)6.4GPIO PORT REGISTERS (133)6.4.1GPIO Pin Configuration (GPCFG) Register (134)6.4.2GPIO Pin Event Routing (GPEVR) Register (135)6.4.3GPIO Port Runtime Register Map (135)6.4.4GPIO Data Out Register (GPDO) (136)6.4.5GPIO Data In Register (GPDI) (136)6.4.6GPIO Event Enable Register (GPEVEN) (137)6.4.7GPIO Event Status Register (GPEVST) (137)7.0WATCHDOG Timer (WDT)7.1OVERVIEW (138)7.2FUNCTIONAL DESCRIPTION (138)7.3WATCHDOG TIMER REGISTERS (139)7.3.1WATCHDOG Timer Register Map (139)7.3.2WATCHDOG Timeout Register (WDTO) (139)7.3.3WATCHDOG Mask Register (WDMSK) (140)7.3.4WATCHDOG Status Register (WDST) (141)7.4WATCHDOG TIMER REGISTER BITMAP (141)8.0ACCESS.bus Interface (ACB)8.1OVERVIEW (142)8.2FUNCTIONAL DESCRIPTION (142)8.2.1Data Transactions (142)8.2.2Start and Stop Conditions (142)8.2.3Acknowledge (ACK) Cycle (143)8.2.4Acknowledge after Every Byte Rule (144)8.2.5Addressing Transfer Formats (144)8.2.6Arbitration on the Bus (144)8.2.7Master Mode (145)8.2.8Slave Mode (147)8.2.9Configuration (147)8.3ACB REGISTERS (148)8.3.1ACB Register Map (148)8.3.2ACB Serial Data Register (ACBSDA) (148)8.3.3ACB Status Register (ACBST) (149)8.3.4ACB Control Status Register (ACBCST) (150)8.3.5ACB Control Register 1 (ACBCTL1) (151)8.3.6ACB Own Address Register (ACBADDR) (152)8.3.7ACB Control Register 2 (ACBCTL2) (152)8.4ACB REGISTER BITMAP (153)9.0Game Port (GMP)9.1OVERVIEW (154)9.2FUNCTIONAL DESCRIPTION (154)9.2.1Game Device Axis Position Indication (154)9.2.2Capturing the Position (155)9.2.3Button Status Indication (156)9.2.4Operation Modes (156)9.2.5Operation Control (157)9.3GAME PORT REGISTERS (158)9.3.1Game Port Register Map (158)9.3.2Game Port Control Register (GMPCTL) (159)9.3.3Game Port Legacy Status Register (GMPLST) (160)9.3.4Game Port Extended Status Register (GMPXST) (161)9.3.5Game Port Interrupt Enable Register (GMPIEN) (162)9.3.6Game Device A X-Axis Position Low Byte (GMPAXL) (163)9.3.7Game Device A X-Axis Position High Byte (GMPAXH) (163)9.3.8Game Device A YAxis Position Low Byte (GMPAYL) (163)9.3.9Game Device A Y-Axis Position High Byte (GMPAYH) (163)9.3.10Game Device B X-Axis Position Low Byte (GMPBXL) (164)9.3.11Game Device B X-Axis Position High Byte (GMPBXH) (164)9.3.12Game Device B Y-Axis Position Low Byte (GMPBYL) (164)9.3.13Game Device B Y-Axis Position High Byte (GMPBYH) (164)9.3.14Game Port Event Polarity Register (GMPEPOL) (165)9.4GAME PORT BITMAP (166)10.0Musical Instrument Digital Interface (MIDI) Port10.1OVERVIEW (167)10.2FUNCTIONAL DESCRIPTION (167)10.2.1Internal Bus Interface Unit (168)10.2.2Port Control and Status Registers (168)10.2.3Data Buffers and FIFOs (168)10.2.4MIDI Communication Engine (168)10.2.5MIDI Signals Routing Control Logic (169)10.2.6Operation Modes (169)10.2.7MIDI Port Status Flags (170)1010.2.8MIDI Port Interrupts (171)10.2.9Enhanced MIDI Port Features (172)10.3MIDI PORT REGISTERS (173)10.3.1MIDI Port Register Map (173)10.3.2MIDI Data In Register (MDI) (173)10.3.3MIDI Data Out Register (MDO) (173)10.3.4MIDI Status Register (MSTAT) (174)10.3.5MIDI Command Register (MCOM) (174)10.3.6MIDI Control Register (MCNTL) (175)10.4MIDI PORT BITMAP (176)11.0Voltage Level Monitor (VLM)11.1OVERVIEW (177)11.2FUNCTIONAL DESCRIPTION (177)11.2.1Voltage Measurement, Channels 0 through 10 (178)11.2.2Thermistor-Based Temperature Measurement, Channels 11 to 13 (179)11.2.3 V OS, V HIGH and V LOW Limits, OTS and ALERT Output, IRQ and SMI (179)11.2.4Power-On Reset Default States (180)11.2.5Standby Mode (180)11.3ANALOG SUPPLY CONNECTION (180)11.3.1Recommendations (180)11.3.2Reference Voltage (181)11.4REGISTER BANK OVERVIEW (181)11.5VLM REGISTERS (182)11.5.1VLM Register Map (182)11.5.2Voltage Event Status Register 0 (VEVSTS0) (183)11.5.3Voltage Event Status Register 1 (VEVSTS1) (183)11.5.4Voltage Event to SMI Register 0 (VEVSMI0) (184)11.5.5Voltage Event to SMI Register 1 (VEVSMI1) (185)11.5.6Voltage Event to IRQ Register 0 (VEVIRQ0) (186)11.5.7Voltage Event to IRQ Register 1 (VEVIRQ1) (186)11.5.8Voltage ID Register (VID) (187)11.5.9Voltage Conversion Rate Register (VCNVR) (188)11.5.10VLM Configuration Register (VLMCFG) (189)11.5.11VLM Bank Select Register (VLMBS) (189)11.5.12Voltage Channel Configuration and Status Register (VCHCFST) (190)11.5.13Read Channel Voltage Register (RDCHV) (191)11.5.14Channel Voltage High Limit Register (CHVH) (191)11.5.15Channel Voltage Low Limit Register (CHVL) (191)11.5.16Overtemperature Shutdown Limit Register (OTSL) (191)11.6VLM REGISTER BITMAP (192)11.6.1VLM Control and Status Registers (192)11.6.2VLM Channel Registers (192)11.7USAGE HINTS (193)11.7.2Measuring Out of Range Positive and Negative Voltages (194)12.0Temperature Sensor (TMS)12.1OVERVIEW (195)12.2FUNCTIONAL DESCRIPTION (195)12.2.1Register Bank Overview (196)12.2.2T OS, T HIGH and T LOW Limits, OTS and ALERT Output, IRQ and SMI (196)12.2.3ALERT Response Read Sequence (197)12.2.4Power-On Reset Default States (197)12.2.5Temperature Data Format (198)12.2.6Standby Mode (198)12.2.7Diode Fault Detection (198)12.3TMS REGISTERS (199)12.3.1TMS Register Map (199)12.3.2Temperature Event Status Register (TEVSTS) (200)12.3.3Temperature Event to SMI Register (TEVSMI) (201)12.3.4Temperature Event to IRQ Register (TEVIRQ) (202)12.3.5TMS Configuration Register (TMSCFG) (203)12.3.6TMS Bank Select Register (TMSBS) (203)12.3.7Temperature Channel Configuration and Status Register (TCHCFST) (204)12.3.8Read Channel Temperature Register (RDCHT) (205)12.3.9Channel Temperature High Limit Register (CHTH) (205)12.3.10Channel Temperature Low Limit Register (CHTL) (205)12.3.11Channel Overtemperature Limit Register (CHOTL) (205)12.4TMS REGISTER BITMAP (206)12.4.1TMS Control and Status Registers (206)12.4.2TMS Channel Registers (206)12.5USAGE HINTS (206)12.5.1Remote Diode Selection (206)12.5.2ADC Noise Filtering (207)12.5.3PC Board Layout (207)12.5.4Twisted Pair and Shielded Cables (209)13.0Legacy Functional Blocks13.1KEYBOARD AND MOUSE CONTROLLER (KBC) (210)13.1.1General Description (210)13.1.2KBC Register Map (210)13.1.3KBC Bitmap Summary (210)13.2FLOPPY DISK CONTROLLER (FDC) (211)13.2.1General Description (211)13.2.2FDC Register Map (211)13.2.3FDC Bitmap Summary (212)13.3PARALLEL PORT (213)13.3.1General Description (213)13.3.3Parallel Port Bitmap Summary (214)13.4UART FUNCTIONALITY (SP1 AND SP2) (216)13.4.1General Description (216)13.4.2UART Mode Register Bank Overview (216)13.4.3SP1 and SP2 Register Maps for UART Functionality (217)13.4.4SP1 and SP2 Bitmap Summary for UART Functionality (219)13.5IR FUNCTIONALITY (SP2) (221)13.5.1General Description (221)13.5.2IR Mode Register Bank Overview (221)13.5.3SP2 Register Map for IR Functionality (222)13.5.4SP2 Bitmap Summary for IR Functionality (223)14.0Device Characteristics14.1GENERAL DC ELECTRICAL CHARACTERISTICS (225)14.1.1Recommended Operating Conditions (225)14.1.2Absolute Maximum Ratings (225)14.1.3Capacitance (225)14.1.4Power Consumption under Recommended Operating Conditions (226)14.2DC CHARACTERISTICS OF PINS, BY I/O BUFFER TYPES (226)14.2.1Input, CMOS Compatible (226)14.2.2Input, PCI 3.3V (226)14.2.3Input, SMBus Compatible (227)14.2.4Input, Strap Pin (227)14.2.5Input, TTL Compatible (227)14.2.6Input, TTL Compatible with Schmitt Trigger (227)14.2.7Output, PCI 3.3V (228)14.2.8Output, Totem-Pole Buffer (228)14.2.9Output, Open-Drain Buffer (228)14.2.10Input, Analog (228)14.2.11Input, Analog (228)14.2.12Input, Analog (229)14.2.13Output, Analog (229)14.2.14Output, Analog (229)14.2.15Exceptions (229)14.3INTERNAL RESISTORS (230)14.3.1Pull-Up Resistor (230)14.3.2Pull-Down Resistor (230)14.4ANALOG CHARACTERISTICS (230)14.4.1VLM (230)14.4.2TMS (230)14.5AC ELECTRICAL CHARACTERISTICS (232)14.5.1AC Test Conditions (232)14.5.2Clock Timing (232)14.5.3LCLK and LRESET (233)14.5.5Serial Port, Sharp-IR, SIR and Consumer Remote Control Timing (235)14.5.6Modem Control Timing (236)14.5.7FDC Write Data Timing (236)14.5.8FDC Drive Control Timing (237)14.5.9FDC Read Data Timing (237)14.5.10Standard Parallel Port Timing (238)14.5.11Enhanced Parallel Port Timing (238)14.5.12Extended Capabilities Port (ECP) Timing (239)。

iw3616、3617、3630datasheet中文翻译(绝对真实)

产品特色大幅简化离线式LED驱动器设计●单级功率因数校正(PFC)与精确恒流(CC)输出相结合●输入/输出电容和变压器体积小●一次侧反馈控制,无需光耦电路,简化了电路设计●简化初级侧PWM调光接口●符合IEC61000-3-2标准高效节能和高兼容性●大幅提升效率,可达到85%以上●减少元件数量●总谐波失真<15%且PF>0.95●前沿、后沿和数字调光器●传感器和定时器精确稳定的性能●LED负载恒流精度不低于±5%●支持LED负载热插拔●1%-100%宽范围调光,调光无闪烁先进的保护及安全特性●通过自动重启动提供短路保护●开路故障检测模式●自动热关断重启动无论在PCB板上还是在封装上,都保证高压漏极引脚与其他所有信号引脚之间满足高压爬电要求应用●LED离线固态照明说明G7617 是一款的适用于LED调光控制的离线式两级交流/直流电源控制器,是适用于25W 输出功率的可调光LED 灯具的最优之选。

G7617符合电磁兼容性(EMC) IEC61000-3-2 标准,在120V AC或230V AC输入电压下其功率因数(PF) 可达到0.95 以上。

采用先进的数控技术来检测调光器的类型和相位,为调光器提供动态阻抗的同时可调节LED发光亮度,自动检测调光器类型和相位,从而实现了业内与模拟及数字调光器最广泛的兼容性。

G7617工作于准谐振工作模式,工作效率高,可工作于前沿后沿调光模式,也可工作于R 型、R-C型或R-L型调光控制模式。

G7617 符合热插拔LED 模块的固态照明行业标准Zhaga,同时还集成了调光功能的映射选项(位于白炽灯替代灯的NEMA SSL6 调光曲线内)。

G7617 系列有两个版本:针对120V AC输入应用进行优化的G7617-00 和针对230V AC 应用进行优化的G7617-01。

订购信息应用框图图1典型应用内部框图Vcc VinVcbVT CFGASU BisenseBdrvFdrvFisensePGNDAGND C O R E图2 内部框图引脚功能描述BV SENSE V IN BI SENSE B DRV CFG ASU V CCV CBV TFV SENSEFI SENSEF DRVAGNDPGND 图3. 引脚布局BV SENSE引脚:PFC电感电压反馈点,用于感知Boost电感的磁通状态。

ITR9606中文资料

160

140

2

120

100 80

60

40

20

0 0 10 20 30 40 50 60 70

Fig.5 Collector Dark Current vs.

Ambient Temperature

10

10 10

10

10

0

25

50 75 100

Fig.4 Collector Current vs. Irradiance

1.3

1.2 IF=20mA

1.1

Ie-Radiant Intensity (mW/sr)

0 25 50 75 100 120

1 25 50 75 100 120

Everlight Electronics Co., Ltd. Device No:CDRX-096-004

http:\\ Prepared date:08-08-2005

http:\\ Prepared date:08-08-2005

Rev 3

Page: 3 of 6

Prepared by:Denky

元器件交易网

█ Typical Electrical/Optical/Characteristics Curves for IR

--- --- 10 μA

VR=5V

--- 940 --- nm

IF=20mA

--- 60 --- Deg

IF=20mA

--- --- 100 nA VCE=20V,Ee=0mW/cm2

VCE(sat) --- --- 0.4 V

IC=2mA ,Ee=1mW/cm2

Collect Current Transfer

M24C04-W1BN6T中文资料

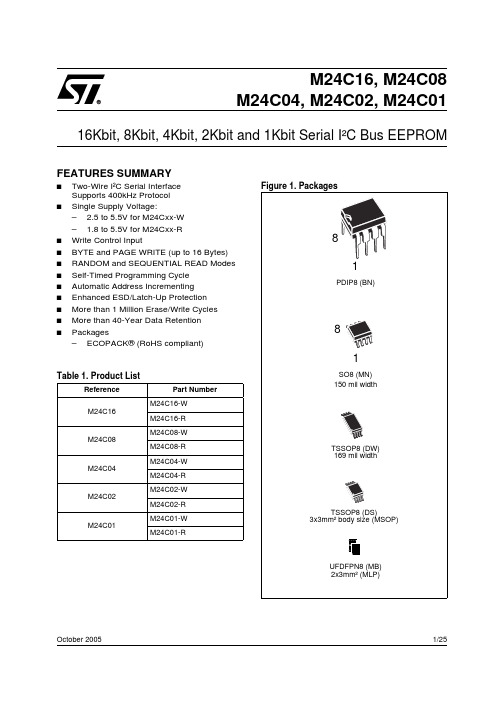

1/25October 2005M24C16, M24C08M24C04, M24C02, M24C0116Kbit, 8Kbit, 4Kbit, 2Kbit and 1Kbit Serial I²C Bus EEPROMFEATURES SUMMARY■Two-Wire I²C Serial Interface Supports 400kHz Protocol ■Single Supply Voltage:– 2.5 to 5.5V for M24Cxx-W – 1.8 to 5.5V for M24Cxx-R ■Write Control Input■BYTE and PAGE WRITE (up to 16 Bytes)■RANDOM and SEQUENTIAL READ Modes ■Self-Timed Programming Cycle ■Automatic Address Incrementing ■Enhanced ESD/Latch-Up Protection ■More than 1 Million Erase/Write Cycles ■More than 40-Year Data Retention ■Packages–ECOPACK® (RoHS compliant)Table 1. Product ListReference Part NumberM24C16M24C16-W M24C16-R M24C08M24C08-W M24C08-R M24C04M24C04-W M24C04-R M24C02M24C02-W M24C02-R M24C01M24C01-W M24C01-RM24C16, M24C08, M24C04, M24C02, M24C01TABLE OF CONTENTSFEATURES SUMMARY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1SUMMARY DESCRIPTION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3 Device internal reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3SIGNAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4Serial Clock (SCL). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4 Serial Data (SDA) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4 Chip Enable (E0, E1, E2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4 Write Control (WC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4DEVICE OPERATION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6Start Condition. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6 Stop Condition. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6 Acknowledge Bit (ACK) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6 Data Input. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6 Memory Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6 Write Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7 Byte Write. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7 Page Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7 Minimizing System Delays by Polling On ACK. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9 Read Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10 Random Address Read. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10 Current Address Read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10 Sequential Read. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11 Acknowledge in Read Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11INITIAL DELIVERY STATE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11 MAXIMUM RATING. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12 DC and AC PARAMETERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13 PACKAGE MECHANICAL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18 PART NUMBERING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23 REVISION HISTORY. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .242/253/25M24C16, M24C08, M24C04, M24C02, M24C01SUMMARY DESCRIPTIONThese I²C-compatible electrically erasable pro-grammable memory (EEPROM) devices are orga-nized as 2048/1024/512/256/128x 8 (M24C16,M24C08, M24C04, M24C02 and M24C01).In order to meet environmental requirements, ST offers these devices in ECOPACK® packages.ECOPACK® packages are Lead-free and RoHS compliant.ECOPACK is an ST trademark. ECOPACK speci-fications are available at: .I²C uses a two-wire serial interface, comprising a bi-directional data line and a clock line. The devic-es carry a built-in 4-bit Device Type Identifier code (1010) in accordance with the I²C bus definition.The device behaves as a slave in the I²C protocol,with all memory operations synchronized by the serial clock. Read and Write operations are initiat-ed by a Start condition, generated by the bus mas-ter. The Start condition is followed by a Device scribed in Table 3.), terminated by an acknowl-edge bit.When writing data to the memory, the device in-serts an acknowledge bit during the 9th bit time,following the bus master’s 8-bit transmission.When data is read by the bus master, the bus master acknowledges the receipt of the data byte in the same way. Data transfers are terminated by a Stop condition after an Ack for Write, and after a NoAck for Read.Table 2. Signal NamesDevice internal resetIn order to prevent inadvertent Write operations during Power-up, a Power On Reset (POR) circuit is included. At Power-up (continuous rise of V CC ),the device will not respond to any instructions until the V CC has reached the Power On Reset threshold voltage (this threshold is lower than the V CC min. operating voltage defined in DC and AC PARAMETERS ). When V CC has passed over the POR threshold, the device is reset and is in Standby Power mode. At Power-down (continuous decay of V CC ), as soon as V CC drops from the normal operating voltage to below the Power On Reset threshold voltage, the device stops responding to any instruction sent to it.Prior to selecting and issuing instructions to the memory, a valid and stable V CC voltage must be applied. This voltage must remain stable and valid until the end of the transmission of the instruction and, for a Write instruction, until the completion of the internal write cycle (t W ).Note: 1.NC = Not Connected2.See PACKAGE MECHANICAL section for package dimensions, and how to identify pin-1.E0, E1, E2Chip Enable SDA Serial Data SCL Serial Clock WCWrite Control V CC Supply Voltage V SSGroundM24C16, M24C08, M24C04, M24C02, M24C014/25SIGNAL DESCRIPTIONSerial Clock (SCL).This input signal is used to strobe all data in and out of the device. In applica-tions where this signal is used by slave devices to synchronize the bus to a slower clock, the bus master must have an open drain output, and a pull-up resistor can be connected from Serial Clock (SCL) to V CC . (Figure 5. indicates how the value of the pull-up resistor can be calculated). In most applications, though, this method of synchro-nization is not employed, and so the pull-up resis-tor is not necessary, provided that the bus master has a push-pull (rather than open drain) output.Serial Data (SDA).This bi-directional signal is used to transfer data in or out of the device. It is an open drain output that may be wire-OR’ed with other open drain or open collector signals on the bus. A pull up resistor must be connected from Se-rial Data (SDA) to V CC . (Figure 5. indicates how the value of the pull-up resistor can be calculated).Chip Enable (E0, E1, E2).These input signals are used to set the value that is to be looked for on the three least significant bits (b3, b2, b1) of the 7-bit Device Select Code. These inputs must be tied to V CC or V SS , to establish the Device Select Code as shown in Figure 4.for protecting the entire contents of the memory from inadvertent write operations. Write opera-tions are disabled to the entire memory array when nected, the signal is internally read as V IL , and Write operations are allowed.Select and Address bytes are acknowledged,Data bytes are not acknowledged.M24C16, M24C08, M24C04, M24C02, M24C01Table 3. Device Select CodeDevice Type Identifier1Chip Enable2,3RWb7b6b5b4b3b2b1b0M24C01 Select Code1010E2E1E0RWM24C02 Select Code1010E2E1E0RWM24C04 Select Code1010E2E1A8RWM24C08 Select Code1010E2A9A8RWM24C16 Select Code1010A10A9A8RW Note: 1.The most significant bit, b7, is sent first.2.E0, E1 and E2 are compared against the respective external pins on the memory device.3.A10, A9 and A8 represent most significant bits of the address.5/25M24C16, M24C08, M24C04, M24C02, M24C016/25DEVICE OPERATIONThe device supports the I²C protocol. This is sum-marized in Figure 6.. Any device that sends data on to the bus is defined to be a transmitter, and any device that reads the data to be a receiver.The device that controls the data transfer is known as the bus master, and the other as the slave de-vice. A data transfer can only be initiated by the bus master, which will also provide the serial clock for synchronization. The M24Cxx device is always a slave in all communication.Start ConditionStart is identified by a falling edge of Serial Data (SDA) while Serial Clock (SCL) is stable in the High state. A Start condition must precede any data transfer command. The device continuously monitors (except during a Write cycle) Serial Data (SDA) and Serial Clock (SCL) for a Start condition,and will not respond unless one is given.Stop ConditionStop is identified by a rising edge of Serial Data (SDA) while Serial Clock (SCL) is stable and driv-en High. A Stop condition terminates communica-tion between the device and the bus master. A Read command that is followed by NoAck can be followed by a Stop condition to force the device into the Stand-by mode. A Stop condition at the end of a Write command triggers the internal Write cycle.Acknowledge Bit (ACK)The acknowledge bit is used to indicate a success-ful byte transfer. The bus transmitter, whether it be bus master or slave device, releases Serial Data (SDA) after sending eight bits of data. During the 9th clock pulse period, the receiver pulls Serial Data (SDA) Low to acknowledge the receipt of the eight data bits.Data InputDuring data input, the device samples Serial Data (SDA) on the rising edge of Serial Clock (SCL).For correct device operation, Serial Data (SDA)must be stable during the rising edge of Serial Clock (SCL), and the Serial Data (SDA) signal must change only when Serial Clock (SCL) is driv-en Low.Memory AddressingTo start communication between the bus master and the slave device, the bus master must initiate a Start condition. Following this, the bus master sends the Device Select Code, shown in Table 3.(on Serial Data (SDA), most significant bit first).The Device Select Code consists of a 4-bit Device Type Identifier, and a 3-bit Chip Enable “Address”(E2, E1, E0). To address the memory array, the 4-bit Device Type Identifier is 1010b.Each device is given a unique 3-bit code on the Chip Enable (E0, E1, E2) inputs. When the Device Select Code is received, the device only responds if the Chip Enable Address is the same as the val-ue on the Chip Enable (E0, E1, E2) inputs. How-ever, those devices with larger memory capacities (the M24C16, M24C08 and M24C04) need more address bits. E0 is not available for use on devices that need to use address line A8; E1 is not avail-able for devices that need to use address line A9,and E2 is not available for devices that need to use address line A10 (see Figure 3. and Table 3. for details). Using the E0, E1 and E2 inputs, up to eight M24C02 (or M24C01), four M24C04, two M24C08 or one M24C16 devices can be connect-ed to one I²C bus. In each case, and in the hybrid cases, this gives a total memory capacity of 16Kbits, 2KBytes (except where M24C01 devic-es are used).The 8th set to 1 for Read and 0 for Write operations.If a match occurs on the Device Select code, the corresponding device gives an acknowledgment on Serial Data (SDA) during the 9th bit time. If the device does not match the Device Select code, it deselects itself from the bus, and goes into Stand-by mode.Table 4. Operating ModesNote: 1.X = V IH or V IL .ModeRW bit WC 1Bytes Initial SequenceCurrent Address Read 1X 1START , Device Select, RW = 1Random Address Read 0X 1START , Device Select, RW = 0, Address 1X reST ART, Device Select, RW = 1Sequential Read 1X ≥ 1Similar to Current or Random Address Read Byte Write 0V IL 1START , Device Select, RW = 0Page WriteV IL≤ 16START , Device Select, RW = 0M24C16, M24C08, M24C04, M24C02, M24C01Figure 7. Write Mode Sequences with WC=1 (data write inhibited)Following a Start condition the bus master sends a Device Select Code with the Read/Write bit (RW) reset to 0. The device acknowledges this, as shown in Figure 8., and waits for an address byte. The device responds to the address byte with an acknowledge bit, and then waits for the data byte. When the bus master generates a Stop condition immediately after the Ack bit (in the “10th bit” time slot), either at the end of a Byte Write or a Page Write, the internal Write cycle is triggered. A Stop condition at any other time slot does not trigger the internal Write cycle.During the internal Write cycle, Serial Data (SDA) and Serial Clock (SCL) are ignored, and the de-vice does not respond to any requests.Byte WriteAfter the Device Select code and the address byte, the bus master sends one data byte. If the ad-dressed location is Write-protected, by Write Con-trol (WC) being driven High (during the period from byte), the device replies to the data byte with NoAck, as shown in Figure 7., and the location is not modified. If, instead, the addressed location is not Write-protected, the device replies with Ack. The bus master terminates the transfer by gener-ating a Stop condition, as shown in Figure 8.. Page WriteThe Page Write mode allows up to 16 bytes to be written in a single Write cycle, provided that they are all located in the same page in the memory: that is, the most significant memory address bits are the same. If more bytes are sent than will fit up to the end of the page, a condition known as ‘roll-over’ occurs. This should be avoided, as data starts to become overwritten in an implementation dependent way.The bus master sends from 1 to 16 bytes of data, each of which is acknowledged by the device if Write Control (WC) is Low. If the addressed loca-ing driven High (during the period from the Start7/25M24C16, M24C08, M24C04, M24C02, M24C018/25condition until the end of the address byte), the de-vice replies to the data bytes with NoAck, as shown in Figure 7., and the locations are not mod-ified. After each byte is transferred, the internalbyte address counter (the 4 least significant ad-dress bits only) is incremented. The transfer is ter-minated by the bus master generating a Stop condition.M24C16, M24C08, M24C04, M24C02, M24C01During the internal Write cycle, the device discon-nects itself from the bus, and writes a copy of the data from its internal latches to the memory cells. The maximum Write time (t w) is shown in Table 13. and Table 14., but the typical time is shorter. To make use of this, a polling sequence can be used by the bus master.The sequence, as shown in Figure 9., is:–Step 1: the bus master issues a Start condition followed by a Device Select Code (the firstbyte of the new instruction).–Step 2: if the device is busy with the internal Write cycle, no Ack will be returned and thebus master goes back to Step 1. If the device has terminated the internal Write cycle, itresponds with an Ack, indicating that thedevice is ready to receive the second part of the instruction (the first byte of this instruction having been sent during Step 1).9/25M24C16, M24C08, M24C04, M24C02, M24C0110/25Read OperationsRead operations are performed independently of The device has an internal address counter which is incremented each time a byte is read.Random Address ReadA dummy Write is first performed to load the ad-dress into this address counter (as shown in Fig-ure 10.) but without sending a Stop condition.Then, the bus master sends another Start condi-tion, and repeats the Device Select Code, with the Read/Write bit (RW) set to 1. The device acknowl-edges this, and outputs the contents of the ad-dressed byte. The bus master must not acknowledge the byte, and terminates the transfer with a Stop condition.Current Address ReadFor the Current Address Read operation, following a Start condition, the bus master only sends a De-to 1. The device acknowledges this, and outputs the byte addressed by the internal address counter. The counter is then incremented. The bus master terminates the transfer with a Stop condi-tion, as shown in Figure 10., without acknowledg-ing the byte.Sequential ReadThis operation can be used after a Current Ad-dress Read or a Random Address Read. The bus master does acknowledge the data byte output, and sends additional clock pulses so that the de-vice continues to output the next byte in sequence. To terminate the stream of bytes, the bus master must not acknowledge the last byte, and must generate a Stop condition, as shown in Figure 10.. The output data comes from consecutive address-es, with the internal address counter automatically incremented after each byte output. After the last memory address, the address counter ‘rolls-over’, and the device continues to output data from memory address 00h.Acknowledge in Read ModeFor all Read commands, the device waits, aftereach byte read, for an acknowledgment during the 9th bit time. If the bus master does not drive Serial Data (SDA) Low during this time, the device termi-nates the data transfer and switches to its Stand-by mode.INITIAL DELIVERY STATEThe device is delivered with all bits in the memory array set to 1 (each byte contains FFh).11/2512/25MAXIMUM RATINGStressing the device outside the ratings listed in Table 5. may cause permanent damage to the de-vice. These are stress ratings only, and operation of the device at these, or any other conditions out-side those indicated in the Operating sections of this specification, is not implied. Exposure to Ab-solute Maximum Rating conditions for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE Program and other relevant quality documents.Table 5. Absolute Maximum RatingsNote: pliant with JEDEC Std J-STD-020C (for small body, Sn-Pb or Pb assembly), the ST ECOPACK ® 7191395 specification, andthe European directive on Restrictions on Hazardous Substances (RoHS) 2002/95/EU2.AEC-Q100-002 (compliant with JEDEC Std JESD22-A114A, C1=100pF, R1=1500Ω, R2=500Ω)Symbol ParameterMin.Max.Unit T A Ambient Operating Temperature –40125°C T STG Storage Temperature–65150°C T LEAD Lead T emperature during Soldering 1°C V IO Input or Output range –0.50 6.5V V CC Supply Voltage–0.50 6.5V V ESDElectrostatic Discharge Voltage (Human Body model) 2–40004000V13/25DC AND AC PARAMETERSThis section summarizes the operating and mea-surement conditions, and the DC and AC charac-teristics of the device. The parameters in the DC and AC Characteristic tables that follow are de-rived from tests performed under the Measure-ment Conditions summarized in the relevant tables. Designers should check that the operating conditions in their circuit match the measurement conditions when relying on the quoted parame-ters.Table 6. Operating Conditions (M24Cxx-W)Table 7. Operating Conditions (M24Cxx-R)Table 8. DC Characteristics (M24Cxx-W, Device Grade 6)Note: 1.The voltage source driving only E0, E1 and E2 inputs must provide an impedance of less than 1kOhm.Symbol ParameterMin.Max.Unit V CC Supply Voltage2.5 5.5V T AAmbient Operating T emperature (Device Grade 6)–4085°C Ambient Operating T emperature (Device Grade 3)–40125°CSymbol ParameterMin.Max.Unit V CC Supply Voltage1.8 5.5V T AAmbient Operating T emperature–4085°CSymbol ParameterTest Condition(in addition to those in Table 6.)Min.Max.Unit I LI Input Leakage Current(SCL, SDA, E0, E1,and E2)V IN = V SS or V CC± 2µA I LO Output Leakage Current V OUT = V SS or V CC, SDA in Hi-Z ± 2µA I CCSupply CurrentV CC =5V , f c =400kHz (rise/fall time < 30ns)2mA V CC =2.5V , f c =400kHz (rise/fall time < 30ns)1mA I CC1Stand-by Supply Current V IN = V SS or V CC , V CC = 5V 1µA V IN = V SS or V CC , V CC = 2.5V0.5µA V IL Input Low Voltage (1)–0.450.3V CC V V IH Input High Voltage (1)0.7V CCV CC +1V V OLOutput Low VoltageI OL = 2.1mA, V CC = 2.5V0.4V14/25Table 9. DC Characteristics (M24Cxx-W, Device Grade 3)Note: 1.The voltage source driving only E0, E1 and E2 inputs must provide an impedance of less than 1kOhm.Table 10. DC Characteristics (M24Cxx-R)Note: 1.The voltage source driving only E0, E1 and E2 inputs must provide an impedance of less than 1kOhm.Table 11. AC Measurement ConditionsSymbol ParameterTest Condition(in addition to those in Table 6.)Min.Max.Unit I LI Input Leakage Current(SCL, SDA, E0, E1,and E2)V IN = V SS or V CC± 2µA I LO Output Leakage Current V OUT = V SS or V CC, SDA in Hi-Z ± 2µA I CCSupply CurrentV CC =5V , f C =400kHz (rise/fall time < 30ns)3mA V CC =2.5V , f C =400kHz (rise/fall time < 30ns)3mA I CC1Stand-by Supply Current V IN = V SS or V CC , V CC = 5V 5µA V IN = V SS or V CC , V CC = 2.5V2µA V IL Input Low Voltage (1)–0.450.3V CC V V IH Input High Voltage (1)0.7V CCV CC +1V V OLOutput Low VoltageI OL = 2.1mA, V CC = 2.5V0.4VSymbol ParameterTest Condition(in addition to those in Table 7.)Min.Max.Unit I LI Input Leakage Current(SCL, SDA, E0, E1,and E2)V IN = V SS or V CC± 2µA I LO Output Leakage Current V OUT = V SS or V CC, SDA in Hi-Z ± 2µA I CC Supply CurrentV CC =1.8V , f c =400kHz (rise/fall time < 30ns)0.8mA I CC1Stand-by Supply Current V IN = V SS or V CC , V CC = 1.8V0.3µA V IL Input Low Voltage (1) 2.5V ≤ V CC –0.450.3V CC V 1.8V ≤ V CC < 2.5V–0.450.25V CC V V IH Input High Voltage (1)0.7V CC V CC +1V V OLOutput Low VoltageI OL = 0.7mA, V CC = 1.8V 0.2VSymbol ParameterMin.Max.Unit C LLoad Capacitance 100pF Input Rise and Fall Times 50ns Input Levels0.2V CC to 0.8V CC V Input and Output Timing Reference Levels0.3V CC to 0.7V CCV15/25Table 12. Input ParametersNote: 1.T A = 25°C, f = 400kHz2.Sampled only, not 100% tested.Symbol Parameter 1,2Test ConditionMin.Max.Unit C IN Input Capacitance (SDA)8pF C IN Input Capacitance (other pins)6pF Z WCL WC Input Impedance V IN < 0.3V 1570k ΩZ WCH WC Input Impedance V IN > 0.7V CC 500k Ωt NSPulse width ignored(Input Filter on SCL and SDA)Single glitch100nsTable 13. AC Characteristics (M24Cxx-W)Test conditions specified in Table 6. and Table 11.Symbol Alt.Parameter Min.Max.Unitf C f SCL Clock Frequency400kHzt CHCL t HIGH Clock Pulse Width High600ns t CLCH t LOW Clock Pulse Width Low1300nst DL1DL2 2t F SDA Fall Time20300ns t DXCX t SU:DAT Data In Set Up Time100ns t CLDX t HD:DA T Data In Hold Time0ns t CLQX t DH Data Out Hold Time200ns t CLQV 3t AA Clock Low to Next Data Valid (Access Time)200900ns t CHDX 1t SU:ST A Start Condition Set Up Time600ns t DLCL t HD:ST A Start Condition Hold Time600ns t CHDH t SU:STO Stop Condition Set Up Time600ns t DHDL t BUF Time between Stop Condition and Next Start Condition1300ns t W 4t WR Write Time5ms Note: 1.For a reSTART condition, or following a Write cycle.2.Sampled only, not 100% tested.3.To avoid spurious START and STOP conditions, a minimum delay is placed between SCL=1 and the falling or rising edge of SDA.4.Previous devices bearing the process letter “L” in the package marking guarantee a maximum write time of 10ms. For more infor-mation about these devices and their device identification, please ask your ST Sales Office for Process Change Notices PCN MPG/ EE/0061 and 0062 (PCEE0061 and PCEE0062).Table 14. AC Characteristics (M24Cxx-R)Test conditions specified in Table 7. and Table 10.Symbol Alt.Parameter Min. 4Max. 4Unitf C f SCL Clock Frequency400kHzt CHCL t HIGH Clock Pulse Width High600ns t CLCH t LOW Clock Pulse Width Low1300nst DL1DL2 2t F SDA Fall Time20300ns t DXCX t SU:DAT Data In Set Up Time100ns t CLDX t HD:DA T Data In Hold Time0ns t CLQX t DH Data Out Hold Time200ns t CLQV 3t AA Clock Low to Next Data Valid (Access Time)200900ns t CHDX 1t SU:ST A Start Condition Set Up Time600ns t DLCL t HD:ST A Start Condition Hold Time600ns t CHDH t SU:STO Stop Condition Set Up Time600ns t DHDL t BUF Time between Stop Condition and Next Start Condition1300ns t W t WR Write Time10ms Note: 1.For a reSTART condition, or following a Write cycle.2.Sampled only, not 100% tested.3.To avoid spurious START and STOP conditions, a minimum delay is placed between SCL=1 and the falling or rising edge of SDA.4.This is preliminary information.16/2517/25PACKAGE MECHANICALTable 15. PDIP8 – 8 pin Plastic DIP, 0.25mm lead frame, Package Mechanical DataSymb.mm inchesTyp.Min.Max.Typ.Min.Max.A 5.330.210A10.380.015A2 3.30 2.92 4.950.1300.1150.195 b0.460.360.560.0180.0140.022 b2 1.52 1.14 1.780.0600.0450.070 c0.250.200.360.0100.0080.014 D9.279.0210.160.3650.3550.400 E7.877.628.260.3100.3000.325 E1 6.35 6.107.110.2500.2400.280e 2.54––0.100––eA7.62––0.300––eB10.920.430 L 3.30 2.92 3.810.1300.1150.15018/25Note:Drawing is not to scale.Table 16. SO8 narrow – 8 lead Plastic Small Outline, 150 mils body width, Package Mechanical DataSymb.mm inchesTyp.Min.Max.Typ.Min.Max.A 1.35 1.750.0530.069A10.100.250.0040.010B0.330.510.0130.020C0.190.250.0070.010D 4.80 5.000.1890.197E 3.80 4.000.1500.157e 1.27––0.050––H 5.80 6.200.2280.244h0.250.500.0100.020L0.400.900.0160.035α0°8°0°8°N88CP0.100.00419/25Note: 1.Drawing is not to scale.2.The central pad (the area E2 by D2 in the above illustration) is pulled, internally, to V SS. It must not be allowed to be connected toany other voltage or signal line on the PCB, for example during the soldering process.Table 17. UFDFPN8 (MLP8) 8-lead Ultra thin Fine pitch Dual Flat Package No lead 2x3mm², DataSymbolmm inchesTyp.Min.Max.Typ.Min.Max.A0.550.500.600.0220.0200.024 A10.000.050.0000.002 b0.250.200.300.0100.0080.012D 2.000.079D2 1.55 1.650.0610.065 ddd0.050.002E 3.000.118E20.150.250.0060.010 e0.50––0.020––L0.450.400.500.0180.0160.020 L10.150.006 L30.300.012N8820/25。

M9366-TRDS3T中文资料