基于多相时钟的pcie2.0物理层实现——徐涛

基于FPGA的PCIe设计

基于FPGA的PCIe设计1. PCIe简介1.1. PCIe基本架构PCIe的优势以其复杂性为代价。

PCIe是基于分组的串行连接协议,估计比PCI并行总线复杂10倍以上。

这种复杂性部分源于在千兆赫速率所要求的并行到串行的数据转换以及转向基于分组的实现。

PCIe保持了PCI基于加载存储的基本架构,包括对PCI-X增加的对分割事务的支持。

此外,它引进了一系列底层信息传送要件来管理链接(如链路层流量控制)以模仿传统并行总线的边带线,且提供了更高水平的robustness和功能。

该规范定义了许多特性、能同时支持当今的需求和未来的扩展需要,且同时与PCI保持了软件兼容。

PCI Express的先进特性包括:主动电源管理;先进的错误报告;通过端对端循环冗余校验(ECRC)支持的端对端的可靠性;支持热插拔以及服务质量(QoS)流通类。

一个简化系统的拓扑结构包括四个功能类型,根联合体根联合体(root complex)、交换器(switch)、端点(multiple Endpoints)和桥(bridge)。

1.ROOT Complex:根联合体对整个PCIe建构实施初始化并配置各链路。

它通常把中央处理单元(CPU)与其它三个功能中的一或多个——PCIe交换器、PCIe端点和PCIe到PCI桥——连接起来;2.Endpoint:端点通常位于终端应用内,它负责连接应用与系统内的PCIe网络。

端点要求并完成PCIe事务传输。

一般来说,系统内的端点比任何其他类型的PCIe部件都要多;(1)Legacy Endpoint;(2)PCI Express Endpoint;(3)Root Complex Integrated Endpoint;3.Switch:PCIe交换器把数据路由至下游多个PCIe端口,并分别从其中每个端口路由到上游唯一一个根联合体。

PCIe交换器也可以灵活地把数据从一个下游端口路由到另一个下游端口(点对点),它消除了传统PCI系统限制性的树状结构;4.Root Complex Event Collector;5.PCI Express-PCI Bridge:桥用于连接PCIe与系统内诸如PCI/PCI-X等其他PCI总线标准,这样的系统同时采用上述各总线架构;1.2. PCIe协议规格PCIe 规范对于设备的设计采用分层的结构,有事务层、数据链路层和物理层组成,各层有都分为发送和接收两功能块。

(完整版)xilinxPCIE2.0接口EP端设计总结,推荐文档

1.PCIE说明PCIE协议定义了多种设备:根复合体(Root Complex),交换器(Switch),端点(Endpoingt),断就(Port),PCIE到PCI/PCI-X的桥(Bridge)等。

根复合体是将CPU和主存储器连接到PCIE 线路结构上的设备,能带包CPI启动PCIE事务和访问主存储器;交换器可以将任务由一个端口路由到另一个端口,在系统中用于多设备的互联,具体的路由方法包括ID路由,地址路由,隐含路由;Endpoint是指一个世纪的设备(请求者或完成者);port是设备与链路的接口;Bridge 则是用来实现PCIE设备与PCI/PCI-X设备之间的连接,实现两种不同协议之间的相互转换。

PCIE核在多种模式中使用包来互换信息。

包是在事务和数据链层中形成来从发送端到接收端的信息传递。

必要的信息被添加到传输的包中。

在接收结束,接收单元的每一层处理接收到的包,提取相关的信息并发送包到下一层。

接收到的包是从他们物理层发送到数据链层和事务层的。

PCIe 规范对于设备的设计采用分层的结构,有事务层、数据链路层和物理层组成,各层有都分为发送和接收两功能块。

PCIe的事务层是协议的最上层,其主要功能是根据应用层提供的信息生成相应的请求包传递给数据链路层,并且处理由数据链路层发来的包,将其转换成应用层能识别的信息,协助数据链路层完成信用管理,实现协议规定的配置事务,IO事务,存储事务和消息事务。

在设备的发送部分,首先根据来自设备核和应用程序的信息,在事务层形成事务层包(TLP),储存在发送缓冲器里,等待推向下层;在数据链路层,在TLP 包上再串接一些附加信息,这些信息是对方接收TLP 包时进行错误检查要用到的;在物理层,对TLP 包进行编码,占用链路中的可用通道,从查封发送器发送出去。

事务层包(TLP),数据链路层包(DLLP),物理层(PLP)产生于各自所在层,最后通过电或光等介质和另一方通讯。

PCIe基本原理

xx

xx

Transaction

Link

xx

PIPE

Logical

Electrical Mechanical

Physical Interface (PIPE)

为什么PCIe的工程设计难度要大得多呢?图4显示了在高速设计方案中这些问题的实例以及标准的FR4 电路板材料对于信号的影响度。此图左侧显示了一个1.25 Gbps数据流和一个5 Gbps数据流的二进制眼 图,并对应于通过26英寸的标准FR4电路板材料进行传输。右侧的对应二进制眼图表明,目的地处的信 号性能出现了衰减。而1.25 Gbps数据流在这种传输路程中保存得非常完好,但5 Gbps眼图的大小和清 晰度均出现了显著的衰减,这是因为低成本FR4基底材料以及互连线材料在大于1 GHz的频率下所发生的 介电损失现象而造成的。

• 端点通常驻留在应用内,用于在系统中将应用连接到PCIe网络。端点具有请求和完成PCIe事务处理的 功能。此系统内的端点数量通常多于其它任何类型的PCIe组件。

• 桥接器用于将PCIe与其它PCI总线标准(如PCI/PCI-X)相连接,适用于那些同时采用了这些体系架构 与PCIe的系统。

PCIe协议规格

转向PCIe主要是为了实现显著增强系统吞吐量、扩容性和灵活性的目标,同时还要降低制造成本,而这 些都是基于总线的传统互连标准所达不到的。PCI Express标准在设计时着眼于未来,并且能够继续演 进,从而为系统提供更大的吞吐量。第一代PCIe规定的吞吐量是每秒2.5千兆比特(Gbps),第二代规 定的吞吐量是5.0 Gbps,而最近公布PCIe 3.0标准已经支持8.0 Gbps的吞吐量。在PCIe标准继续充分利 用最新技术来提供不断加大的吞吐量的同时,采用分层协议也便于PCI向PCIe的演进,并保持了与现有 PCI应用的驱动程序软件兼容性。

PCIE简介

PCI ExpressPCI Express ,简称PCI-E ,是电脑总线PCI 的一种,它沿用了现有的PCI 编程概念及通讯标准,但建基于更快的串行通信系统。

英特尔是该接口的主要支援者。

PCIe 仅应用于内部互连。

由于PCIe 是基于现有的PCI 系统,只需修改物理层而无须修改软件就可将现有PCI 系统转换为PCIe 。

PCIe 拥有更快的速率,以取代几乎全部现有的内部总线(包括AGP 和PCI )。

英特尔希望将来能用一个PCIe 控制器和所有外部设备交流,取代现有的南桥/北桥方案。

除了这些,PCIe 设备能够支援热拔插以及热交换特性,支援的三种电压分别为+3.3V 、3.3Vaux 以及+12V 。

考虑到现在显卡功耗的日益增加,PCIe 而后在规范中改善了直接从插槽中取电的功率限制,16x 的最大提供功率达到了75W ,比AGP 8X 接口有了很大的提升。

基本可以满足当时(2004年)中高阶显卡的需求。

这一点可以从AGP 、PCIe 两个不同版本的6600GT 显卡上就能明显地看到,后者并不需要外接电源。

PCIe 只是南桥的扩展总线,它与操作系统无关,所以也保证了它与原有PCI 的兼容性,也就是说在很长一段时间内在主板上PCIe 接口将和PCI 接口共存,这也给用户的升级带来了方便。

由此可见,PCIe 最大的意义在于它的通用性,不仅可以让它用于南桥和其他设备的连接,也可以延伸到芯片组间的连接,甚至也可以用于连接图形芯片,这样,整个I/O 系统重新统一起来,将更进一步简化计算机系统,增加计算机的可移植性和模块化。

历史在2001年的春季英特尔开发者论坛(IDF )上Intel 公布了取代PCI 总线的第三代I/O 技术,被称为“3GIO ”。

该总线的规范由Intel 支持的AWG (Arapahoe Work Group )负责制定。

2002年4月17日,AWG 正式宣布3GIO 1.0规范草稿制定完毕,移交PCI 特殊兴趣组织(PCI-SIG )进行审核,2002年7月23日经过审核后正式公布,改名为“PCI Express ”,并根据开发蓝图2006年正式推出Spec2.0(2.0规范)。

PCIe物理层实现了一对收发差分对,可以实现全双工的通信方式

PCIe 物理层实现了一对收发差分对,可以实现全双

工的通信方式

首先,回顾一下,之前看了很多遍的PCIe 的Layer 结构图:

PCIe 中的物理层主要完成编解码(8b/10b for Gen1&Gen2,128b/130b for Gen3 and later)、扰码与解扰码、串并转换、差分发送与接收、链路训练等功能。

其中链路训练主要通过物理层包Ordered Sets 来实现。

PCIe Spec 将物理层分为两个部分——逻辑子层和电气子层,如下图所示:

如上图所示,PCIe 物理层实现了一对收发差分对,因此可以实现全双工

的通信方式。

需要注意的是,PCIe Spec 只是规定了物理层需要实现的功能、

性能与参数等,置于如何实现这些却并没有明确的说明。

也就是说,厂商可

以根据自己的需要和实际情况,来设计PCIe 的物理层。

下面将以Mindshare

书中的例子来简要的介绍PCIe 的物理层逻辑部分,可能会与其他的厂商的设

备的物理层实现方式有所差异,但是设计的目标和最终的功能是基本一致

的。

物理层逻辑子层的发送端部分的结构图如下图所示:。

PCIE学习笔记

PCIE学习笔记文档主要包括四个部分:1)Magwizard中例化模块的说明;2)内部结构;3)结合实际应用介绍应用层接口信号(我们主要帮客户解决这部分的问题,底层软件驱动部分由客户自己开发,Altera不负责支持);4)学习初期疑问及AE的解答。

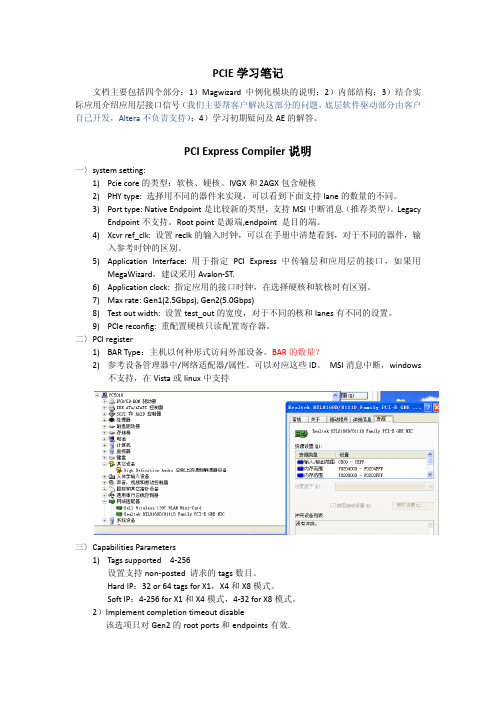

PCI Express Compiler说明一〉system setting:1)Pcie core的类型:软核、硬核。

IVGX和2AGX包含硬核2)PHY type: 选择用不同的器件来实现,可以看到下面支持lane的数量的不同。

3)Port type: Native Endpoint是比较新的类型,支持MSI中断消息(推荐类型)。

LegacyEndpoint不支持。

Root point是源端,endpoint 是目的端。

4)Xcvr ref_clk: 设置reclk的输入时钟,可以在手册中清楚看到,对于不同的器件,输入参考时钟的区别。

5)Application Interface: 用于指定PCI Express中传输层和应用层的接口,如果用MegaWizard,建议采用Avalon-ST.6)Application clock: 指定应用的接口时钟,在选择硬核和软核时有区别。

7)Max rate: Gen1(2.5Gbps), Gen2(5.0Gbps)8)Test out width: 设置test_out的宽度,对于不同的核和lanes有不同的设置。

9)PCIe reconfig: 重配置硬核只读配置寄存器。

二〉PCI register1)BAR Type:主机以何种形式访问外部设备。

BAR的数量?2)参考设备管理器中/网络适配器/属性。

可以对应这些ID。

MSI消息中断,windows不支持,在Vista或linux中支持三〉Capabilities Parameters1)Tags supported 4-256设置支持non-posted 请求的tags数目。

PCIe总线基础及FPGA设计实战

PCI Express总线基础及FPGA设计实战1. PCI Express基础PCIe总线是基于PCI总线发展起来的,很多基本概念都来自于PCI总线,有必要在介绍PCIe之前了解PCI总线。

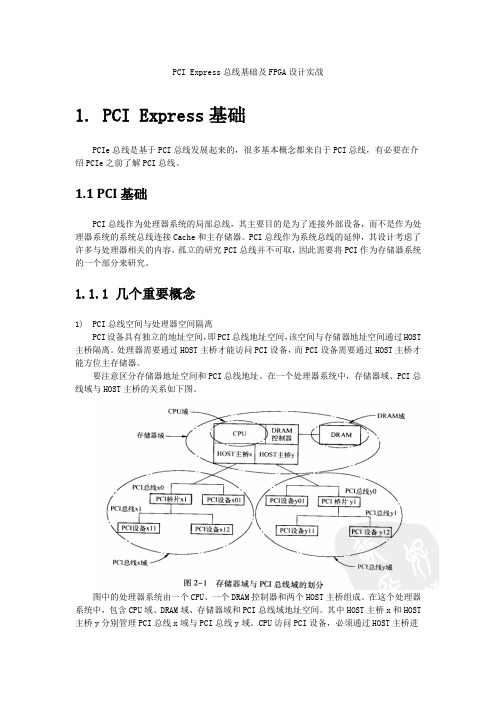

1.1 PCI基础PCI总线作为处理器系统的局部总线,其主要目的是为了连接外部设备,而不是作为处理器系统的系统总线连接Cache和主存储器。

PCI总线作为系统总线的延伸,其设计考虑了许多与处理器相关的内容,孤立的研究PCI总线并不可取,因此需要将PCI作为存储器系统的一个部分来研究。

1.1.1 几个重要概念1)PCI总线空间与处理器空间隔离PCI设备具有独立的地址空间,即PCI总线地址空间,该空间与存储器地址空间通过HOST 主桥隔离。

处理器需要通过HOST主桥才能访问PCI设备,而PCI设备需要通过HOST主桥才能方位主存储器。

要注意区分存储器地址空间和PCI总线地址。

在一个处理器系统中,存储器域、PCI总线域与HOST主桥的关系如下图。

图中的处理器系统由一个CPU、一个DRAM控制器和两个HOST主桥组成。

在这个处理器系统中,包含CPU域、DRAM域、存储器域和PCI总线域地址空间。

其中HOST主桥x和HOST 主桥y分别管理PCI总线x域与PCI总线y域。

CPU访问PCI设备,必须通过HOST主桥进行地址转换,而PCI设备访问存储器设备,也需要HOST主桥进行地址转换。

HOST主桥的一个重要作用就是将存储器访问的存储器地址转换成PCI总线地址。

CPU域地址空间是指CPU所能直接访问的地址空间集合。

DRAM域地址空间是指DRAM控制器所能访问的地址空间集合,又称为主主存储器域。

存储器域是CPU域和DRAM域的集合。

存储器域包括CPU内部的通用寄存器、存储器映射寻址的寄存器、主存储器空间和外部设备空间。

在Intel的x86处理系统中,外部设备空间与PCI总线域地址空间等效。

因为在x86处理器系统中,使用PCI总线同一管理全部外部设备。

PCI-E资料(全)

TxData Command Status RxData PClk

Transaction Link xx

State machines for Link Training and Status State Machine (LTSSM) and lane0lane deskew

转向PCIe主要是为了实现显著增强系统吞吐量、扩容性和灵活性的目标,同时还要降低制造成本,而这 些都是基于总线的传统互连标准所达不到的。PCI Express标准在设计时着眼于未来,并且能够继续演 进,从而为系统提供更大的吞吐量。第一代PCIe规定的吞吐量是每秒2.5千兆比特(Gbps),第二代规 定的吞吐量是5.0 Gbps,而最近公布PCIe 3.0标准已经支持8.0 Gbps的吞吐量。在PCIe标准继续充分利 用最新技术来提供不断加大的吞吐量的同时,采用分层协议也便于PCI向PCIe的演进,并保持了与现有 PCI应用的驱动程序软件兼容性。

Chip Set with Root Complex

PCIe RC Controller

PHY

PHY PCIe Endpoint

Endpoint

图3:SoC芯片内的PHY和控制器运用

正如上文所述,2个端口之间的虚线代表着链路。PCIe链路是单向的,并采用了低压差分信号。PCIe规 格定义了链路可以包含多达32个并行通道,用于将PCIe 1.x(2.5Gbps)链路的吞吐量扩展至80 Gbps, 或将PCIe 2.0(5.0 Gbps)的吞吐量扩展至160 Gbps。同一链路内的每个线路(Lane)均提供了自己的 内嵌时钟信号,因而无需在PC电路板上实现线路长度匹配——这种匹配是以前PCI接口为了保持时序所 必需的。

PCIe规格内所定义的此协议遵循的是开源促进会(OSI)模型。此协议分隔成5个基本层,如图2左侧所 示。本节对机械层和物理层进行了综述;后续各节将针对链路层、事务处理层和应用层进行说明。

PCIE接口介绍-修改

PCIe接口介绍PCIe接口简介PCIe(Peripheral Component Interconnect Express)总线的诞生与PC(Personal Computer)的蓬勃发展密切相关,是由PCISIG (PCI Special Interest Group,主要是intel)推出的一种局部并行总线标准,主要应用于电脑和服务器的主板上(目前几乎所有的主板都有PCIe 的插槽),功能是连接外部设备(如显卡、存储、网卡、声卡、数据采集卡等)。

PCI总线规范最早在上世纪九十年代提出,属于单端并行信号的总线,目前已淘汰,被PCIe总线(在2001年发布,采用点对点串行连接)替代。

目前PCIe的主流应用是3.0,4.0还没正式推出,但标准已经制定的差不多了。

PCI总线使用并行总线结构,在同一条总线上的所有外部设备共享总线带宽,而PCIe总线使用了高速差分总线,并采用端到端的连接方式,因此在每一条PCIe链路中只能连接两个设备。

这使得PCIe与PCI总线采用的拓扑结构有所不同。

PCIe总线除了在连接方式上与PCI总线不同之外,还使用了一些在网络通信中使用的技术,如支持多种数据路由方式,基于多通路的数据传递方式,和基于报文的数据传送方式,并充分考虑了在数据传送中出现服务质量QoS (Quality of Service)问题。

每一个Lane上使用的总线频率与PCIe总线使用的版本相关。

不相同。

PCIe总线V1.x和V2.0规范在物理层中使用8/10b编码,即在PCIe链路上的10 bit中含有8 bit的有效数据;而V3.0规范使用128/130b编码方式,即在PCIe链路上的130 bit中含有128 bit的有效数据。

实际使用中,PCIe无法一直维持在峰值传输状态,因为编码方式、链路管理消耗、存储时间延迟等原因,一般只有50%~60%的效率。

PCIe接口原理连接方式PCIe链路使用“端到端的数据传送方式”,发送端和接收端中都含有TX(发送逻辑)和RX(接收逻辑),其结构如图一。

基于XilinxFPGA的PCIE接口实现

微 处 理 机M I CROPROCESS ORS基于Xilinx FPG A 的PC IE 接口实现石 峰,吴建飞,刘 凯,徐 欣(长沙国防科技大学,长沙410073) 摘 要:介绍了单通道物理层收发器PX1011A 以及PC I Exp ress 总线体系的结构与特点;简述了基于PX1011A 收发器芯片的硬件电路设计;重点研究了采用Xilinx P I PE Core 实现PC I E 总线协议的方法。

关键词:PC I Exp ress 总线;I P 核;协议中图分类号:TP31 文献标识码:B 文章编号:1002-2279(2008)06-0019-03PC I E Po rt D eve l o p B a sed o n Xili nx FP GASH I Feng,WU J ian -fei,L I U Kai,XU Xin(N ational U niversity of D efense Technology,Changsha 410073,China ) Abstract:This paper intr oduces PC I Exp ress stand -al one X1PHY PX1011A as well as the syste m configurati on and characteristics of PC I Exp ress bus;Si m p ly dep icts the hardware design based on PX1011A;Particularly sho ws the design of PC I Ex p ress bus by Xilinx P I PE Core .Key words:PC I Exp ress BUS;I Pcore;Specificati on1 前 言随着系统性能、功能和带宽的日益增长,总线技术也在迅速的发展。

PCIe

.1 PCIe总线的基础知识(2011-05-27 15:59:56)转载标签:分类:浅谈PCIe体系结构杂谈与PCI总线不同,PCIe总线使用端到端的连接方式,在一条PCIe链路的两端只能各连接一个设备,这两个设备互为是数据发送端和数据接收端。

PCIe总线除了总线链路外,还具有多个层次,发送端发送数据时将通过这些层次,而接收端接收数据时也使用这些层次。

PCIe总线使用的层次结构与网络协议栈较为类似。

4.1.1 端到端的数据传递PCIe链路使用“端到端的数据传送方式”,发送端和接收端中都含有TX(发送逻辑)和RX(接收逻辑),其结构如图4-1所示。

由上图所示,在PCIe总线的物理链路的一个数据通路(Lane)中,由两组差分信号,共4根信号线组成。

其中发送端的TX部件与接收端的RX部件使用一组差分信号连接,该链路也被称为发送端的发送链路,也是接收端的接收链路;而发送端的RX部件与接收端的TX 部件使用另一组差分信号连接,该链路也被称为发送端的接收链路,也是接收端的发送链路。

一个PCIe链路可以由多个Lane组成。

高速差分信号电气规范要求其发送端串接一个电容,以进行AC耦合。

该电容也被称为AC耦合电容。

PCIe链路使用差分信号进行数据传送,一个差分信号由D+和D-两根信号组成,信号接收端通过比较这两个信号的差值,判断发送端发送的是逻辑“1”还是逻辑“0”。

与单端信号相比,差分信号抗干扰的能力更强,因为差分信号在布线时要求“等长”、“等宽”、“贴近”,而且在同层。

因此外部干扰噪声将被“同值”而且“同时”加载到D+和D-两根信号上,其差值在理想情况下为0,对信号的逻辑值产生的影响较小。

因此差分信号可以使用更高的总线频率。

此外使用差分信号能有效抑制电磁干扰EMI(Electro Magnetic Interference)。

由于差分信号D+与D-距离很近而且信号幅值相等、极性相反。

这两根线与地线间耦合电磁场的幅值相等,将相互抵消,因此差分信号对外界的电磁干扰较小。

PCIE接口介绍-修改

PCIe接口介绍PCIe接口简介PCIe(Peripheral Component Interconnect Express)总线的诞生与PC(Personal Computer)的蓬勃发展密切相关,是由PCISIG (PCI Special Interest Group,主要是intel)推出的一种局部并行总线标准,主要应用于电脑和服务器的主板上(目前几乎所有的主板都有PCIe 的插槽),功能是连接外部设备(如显卡、存储、网卡、声卡、数据采集卡等)。

PCI总线规范最早在上世纪九十年代提出,属于单端并行信号的总线,目前已淘汰,被PCIe总线(在2001年发布,采用点对点串行连接)替代。

目前PCIe的主流应用是3.0,4.0还没正式推出,但标准已经制定的差不多了。

PCI总线使用并行总线结构,在同一条总线上的所有外部设备共享总线带宽,而PCIe总线使用了高速差分总线,并采用端到端的连接方式,因此在每一条PCIe链路中只能连接两个设备。

这使得PCIe与PCI总线采用的拓扑结构有所不同。

PCIe总线除了在连接方式上与PCI总线不同之外,还使用了一些在网络通信中使用的技术,如支持多种数据路由方式,基于多通路的数据传递方式,和基于报文的数据传送方式,并充分考虑了在数据传送中出现服务质量QoS (Quality of Service)问题。

每一个Lane上使用的总线频率与PCIe总线使用的版本相关。

不相同。

PCIe总线V1.x和V2.0规范在物理层中使用8/10b编码,即在PCIe链路上的10 bit中含有8 bit的有效数据;而V3.0规范使用128/130b编码方式,即在PCIe链路上的130 bit中含有128 bit的有效数据。

实际使用中,PCIe无法一直维持在峰值传输状态,因为编码方式、链路管理消耗、存储时间延迟等原因,一般只有50%~60%的效率。

PCIe接口原理连接方式PCIe链路使用“端到端的数据传送方式”,发送端和接收端中都含有TX(发送逻辑)和RX(接收逻辑),其结构如图一。

PCIE基础知识

PCIe总线概述随着现代处理器技术的发展,在互连领域中,使用高速差分总线替代并行总线是大势所趋。

与单端并行信号相比,高速差分信号可以使用更高的时钟频率,从而使用更少的信号线,完成之前需要许多单端并行数据信号才能达到的总线带宽。

PCI总线使用并行总线结构,在同一条总线上的所有外部设备共享总线带宽,而PCIe 总线使用了高速差分总线,并采用端到端的连接方式,因此在每一条PCIe链路中只能连接两个设备。

这使得PCIe与PCI总线采用的拓扑结构有所不同。

PCIe总线除了在连接方式上与PCI总线不同之外,还使用了一些在网络通信中使用的技术,如支持多种数据路由方式,基于多通路的数据传递方式,和基于报文的数据传送方式,并充分考虑了在数据传送中出现服务质量QoS (Quality of Service)问题。

PCIe总线的基础知识与PCI总线不同,PCIe总线使用端到端的连接方式,在一条PCIe链路的两端只能各连接一个设备,这两个设备互为是数据发送端和数据接收端。

PCIe总线除了总线链路外,还具有多个层次,发送端发送数据时将通过这些层次,而接收端接收数据时也使用这些层次。

PCIe 总线使用的层次结构与网络协议栈较为类似。

1.1 端到端的数据传递PCIe链路使用“端到端的数据传送方式”,发送端和接收端中都含有TX(发送逻辑)和RX(接收逻辑),其结构如图4-1所示。

由上图所示,在PCIe总线的物理链路的一个数据通路(Lane)中,由两组差分信号,共4根信号线组成。

其中发送端的TX部件与接收端的RX部件使用一组差分信号连接,该链路也被称为发送端的发送链路,也是接收端的接收链路;而发送端的RX部件与接收端的TX部件使用另一组差分信号连接,该链路也被称为发送端的接收链路,也是接收端的发送链路。

一个PCIe链路可以由多个Lane组成。

高速差分信号电气规范要求其发送端串接一个电容,以进行AC耦合。

该电容也被称为AC 耦合电容。

PCIe基本原理

定义和采用了一种接口,这种接口称为PCI Express物理接口(PIPE)。PIPE接口让设计方案能够采 用一种标准接口和/或采购多种能够配合运行的组件,甚至可以向多个供货商进行采购。 • 物理层的电气子层用于实现各种模拟元器件,包括收发器、模拟缓冲器、串化器/解串器(SerDes) 和10位接口。 • 物理编码子层(PCS)用于每一个8位数据字节与10位代码之间的编码/解码。这种编码功能不仅能对 有效字符进行校验,而且还限制了所发送的0和1数量之间的差异度,从而在发送器与接收器之间保持 了一种直流平衡度,进而显著增强了电磁兼容性(EMC)以及电气信号性能。 • 物理层内的PIPE接口的另一个方面包括了链路训练和状况状态机(LTSSM)、通道间去偏移(laneto-lane de-skew)、特殊序列检测和生成,等等。

Endpoint

Switch

Endpoint

Endpoint

图1 4种PCIe功能类型

2

• 根联合体用于初始化整个PCIe结构并配置每条链路。根联合体通常用于将中央处理器(CPU)与其它3 项功能之中的一个或多个相连接,包括PCIe交换器、PCIe端点和PCIe-PCI桥接器。

• PCIe交换器用于将数据向下游路由给多个PCIe端口,以及从每个独立端口将数据向上游路由至单一的 根联合体。PCIe交换器也可以从一个下游端口灵活地向另一个下游端口路由数据(对等),不再局限 于传统PCI系统所要求的严格的树形结构。

下面两节更深入地探讨了PHY和控制器的设计问题。

PCIe SerDes设计难题

为PCIe设计PCIe PHY对于设计人员尤有难度,原因在于:

PCIE2.0的超远距离传输实现

PCIE2.0的超远距离传输实现袁焱;李晋文;曹跃胜;胡军【摘要】PCIE2.0作为用于芯片间和板间互连的、高性能、点对点、基于报文互换的新型I/O互连技术,已被公认为行业的标准,在计算机系统中得到了广泛应用.PCIE2.0在物理层采用基于SERDES的串行通信技术,数据传输速率可达5Gbps,最多支持32通道.随着信号频率的增加,信号完整性问题变得日益突出,衰减、串扰和抖动的共同作用导致信号严重失真,传输距离受到限制.采用一种高效能的中继芯片,对PCIE2.0总线高速串行信号进行中继,实现了远距离传输,并在实际系统中得到了验证.%PCIE2.0 as between chips and boards used for interconnects, high-performance, point-based message exchange in the new I / O interconnect technology, has been recognized as the industry standard in the computer system has been widely used. PCIE2.0 at the physical layer of serial communication based SERDES technology, data transmission rates up to 5 Gbps, the total number of channels up to 32 channels. With the increase in signal frequency, signal integrity issues become increasingly prominent, attenuation, crosstalk and jitter jointly lead to serious distortion of the signal transmission distance is limited. A high-performance relay chip, high-speed serial bus for PCIE2.0 to relay the signal to achieve the long-distance transmission, and in the actual system has been verified.【期刊名称】《计算机技术与发展》【年(卷),期】2011(021)010【总页数】4页(P150-153)【关键词】PCIE2.0;信号完整性;中继【作者】袁焱;李晋文;曹跃胜;胡军【作者单位】国防科技大学计算机学院,湖南长沙410073;国防科技大学计算机学院,湖南长沙410073;国防科技大学计算机学院,湖南长沙410073;国防科技大学计算机学院,湖南长沙410073【正文语种】中文【中图分类】TN9150 引言PCI Express作为面向芯片间和板间互连的、高性能、点对点、基于报文交换的新型I/O互连技术,已被公认为行业的标准[1~3]。

基于PCIE接口的IPSec加速SoC设计

基于PCIE接口的IPSec加速SoC设计杭彦希;徐金甫;南龙梅;杨宇航;王周闯【摘要】为达到IPSec实现的高速性、灵活性以及安全性,设计一个IPSec加速SoC.引入高速PCIE接口突破主机与SoC通信速度瓶颈;采取多核设计技术和层次化存储结构,构建以交叉存储为主的高速数据交换区和以邮箱为主的引擎间状态通信区;采用指令级并行和流水线并行技术,对IPSec协议中算法进行多核映射.实验结果表明,该SoC对于IPSec中典型分组密码算法AES的吞吐率可达1 Gbps,对于认证算法SM3可达2 Gbps,较好地满足了高速网络处理需求.%To achieve the high speed, flexibility and security in the implementation of IPSec protocol, an accelerating SoC for the IPSec protocol was designed.High-speed PCIE interface was introduced to break the bottleneck of the communication between the host computer and external SoC.The multi-core design technology and hierarchical storage structure were adopted to build the exchange area for high-speed data based on cross storage and the communication area for engine state based on email boxes.Instruction level parallelism and pipelining parallel technology was used to map the multicore.Experimental results show that the throughput of the typical block cipher AES in IPSec protocol can reach 1 Gbps, while the authentication algorithm SM3 can reach 2 Gbps, which can better meet the requirements of high-speed network processing.【期刊名称】《计算机工程与设计》【年(卷),期】2017(038)005【总页数】5页(P1212-1215,1257)【关键词】IPSec协议;SoC;高速;多核;PCIE接口【作者】杭彦希;徐金甫;南龙梅;杨宇航;王周闯【作者单位】信息工程大学,河南郑州 450001;信息工程大学,河南郑州 450001;信息工程大学,河南郑州 450001;信息工程大学,河南郑州 450001;信息工程大学,河南郑州 450001【正文语种】中文【中图分类】TP336目前IPsec协议主要有3种实现方式,软件实现、硬件实现和软硬件协同实现。

PCIe总线物理层弹性缓冲设计与实现

PCIe总线物理层弹性缓冲设计与实现廖寅龙;田泽;赵强;马超【摘要】PCIe是在PCI总线的基础上提出的新一代总线和接口标准,它原来的名称为“3GIO”,是由英特尔在2001年提出的。

PCIe属于高速串行点对点双通道高带宽传输,所连接的设备分配独享通道带宽,不共享总线带宽,主要支持主动电源管理、错误报告、端对端的可靠性传输、热插拔以及服务质量( QOS)等功能。

PCIe作为高速串行数据总线以其众多的优点在计算机、通讯、航空航天等领域得到了广泛应用。

为了实现稳定可靠的数据通讯,必须解决总线恢复时钟域数据和本地时钟域数据的同步问题,弹性缓冲区是实现PCIe总线接口数据同步机制的有效方法。

文中根据PCIe协议要求,分析PCIe总线通信中时钟偏差的多种场景,设计了一款采用20位数据总线,读写时钟频率可达250 MHz的弹性缓冲,有效解决了PCIe总线通信中总线恢复时钟域与本地时钟域的数据同步问题。

%PCIe is a new generation of bus and interface based on PCI bus,its original name is"3GIO",was introduced by Intel in 2001. PCIe belongs to dual channel high bandwidth transmission of high speed serial point to point,the connected equipment allocates unshared bandwidth of channel that do not share bus bandwidth,mainly supporting the functions including active power management,bug reports, end to end transmission of the reliability,hot swappable and Quality of Service ( QoS) etc. PCIe had been widely applied in computer, communication,aeronautics and astronautics and other fields as the high-speed-serial data bus. In order to realize stable and reliable com-munication,elastic-buffer is considered as necessary in PCIe which is used to ensure data integrity between the recovered clockdomain and the local clock domain. It analyzes the clock-skew under the variable scenes based on PCIe specification and designs a kind of elastic-buffer with 20 bits data bus and 250 MHz R/W clock frequency,solving the problem of data synchronization between bus recovery clock domain and local clock domain.【期刊名称】《计算机技术与发展》【年(卷),期】2016(026)006【总页数】3页(P168-170)【关键词】PCIe;弹性缓冲;同步FIFO;半满【作者】廖寅龙;田泽;赵强;马超【作者单位】西安航空计算技术研究所集成电路与微系统设计航空科技重点实验室,陕西西安 710068;西安航空计算技术研究所集成电路与微系统设计航空科技重点实验室,陕西西安 710068;西安航空计算技术研究所集成电路与微系统设计航空科技重点实验室,陕西西安 710068;西安航空计算技术研究所集成电路与微系统设计航空科技重点实验室,陕西西安 710068【正文语种】中文【中图分类】TP39PCIe(PCI Express)是从PCI发展而来的一种系统互联接口标准。

基于PCIE总线多主互连系统的设计与实现

基于PCIE总线多主互连系统的设计与实现邹昀辛;吴楫捷;王伟;孙大东;张明庆【摘要】For high-performance computing network with large bandwidth,low latency characteristics,a multi-host interconnection network switching system based on PCIe bus was presented.Differing from the traditional high-speed interconnection network,a method for separation of host and network IO was used,multiple conversions of data signals were avoided,network latency was reduced,and the utilization of network bandwidth was increased,ensuring the high availability of the network.Test results show that the system has larger bandwidth and lower latency.%针对高性能计算网络的高带宽、低延迟的特点,提出一种基于PCIe总线的多主互连的网络交换系统.区别于传统的高速互连网络,采用一种主机与网络IO分离的方法,避免数据信号的多次转换,降低网络延迟,增加网络带宽的利用率,确保网络的高可用性.仪器测试结果表明,该系统具有较高的带宽利用率和较低的数据延迟.【期刊名称】《计算机工程与设计》【年(卷),期】2017(038)009【总页数】5页(P2314-2318)【关键词】PCIe总线;多主互连;高带宽;低延迟;交换系统【作者】邹昀辛;吴楫捷;王伟;孙大东;张明庆【作者单位】中国航天科工集团第二研究院七〇六所,北京 100854;解放军61206部队,北京 100088;中国电子科技集团第十五研究所,北京 100083;中国航天科工集团第二研究院七〇六所,北京 100854;中国航天科工集团第二研究院七〇六所,北京100854【正文语种】中文【中图分类】TP393随着互联网信息技术爆炸式的发展,网络的数据量成井喷式的增加,单路服务器千兆的网络带宽已经满足不了当前信息处理需求,光纤卡和InfiniBand卡成了当前服务器的主流网卡[1]。

PCIE时钟

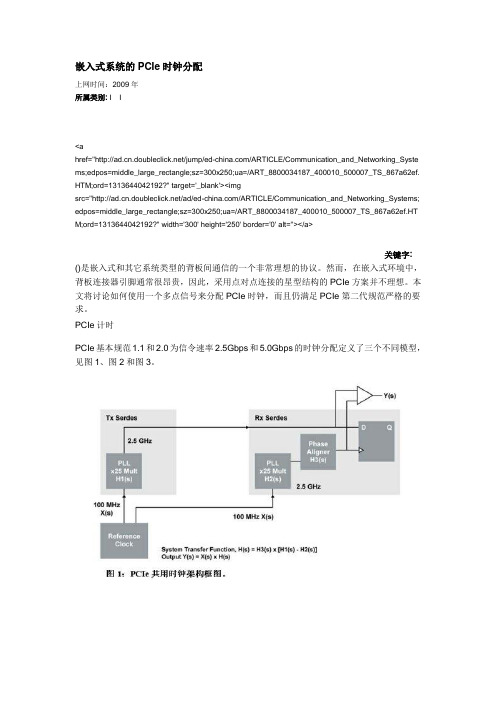

嵌入式系统的PCIe时钟分配上网时间:2009年所属类别: I I<ahref="/jump//ARTICLE/Communication_and_Networking_Syste ms;edpos=middle_large_rectangle;sz=300x250;ua=/ART_8800034187_400010_500007_TS_867a62ef. HTM;ord=1313644042192?" target='_blank'><imgsrc="/ad//ARTICLE/Communication_and_Networking_Systems; edpos=middle_large_rectangle;sz=300x250;ua=/ART_8800034187_400010_500007_TS_867a62ef.HT M;ord=1313644042192?" width='300' height='250' border='0' alt=''></a>关键字: ()是嵌入式和其它系统类型的背板间通信的一个非常理想的协议。

然而,在嵌入式环境中,背板连接器引脚通常很昂贵,因此,采用点对点连接的星型结构的PCIe方案并不理想。

本文将讨论如何使用一个多点信号来分配PCIe时钟,而且仍满足PCIe第二代规范严格的要求。

PCIe计时PCIe基本规范1.1和2.0为信令速率2.5Gbps和5.0Gbps的时钟分配定义了三个不同模型,见图1、图2和图3。

共用时钟架构成为最常使用的方法有很多理由。

首先,大多数支持PCIe接口的商用芯片只适用于这种架构。

其次,这种架构是唯一可以直接支持展频计时(Spread Spectrum clocki ng,简称SSC)的架构。