STM32F407ZGT的时钟深入剖析(32M_40M_72M灵活切换)

stm32f407定时器时钟频率的问题

stm32f407定时器时钟频率的问题

从时钟树中我们可以得知(时钟树的图片可以直接参考6楼,感谢6楼xkwy补上的图):

(1)高级定时器timer1, timer8以及通用定时器timer9, timer10, timer11的时钟来源是APB2总线

(2)通用定时器timer2~timer5,通用定时器timer12~timer14以及基本定时器timer6,timer7的时钟来源是APB1总线

从STM32F4的内部时钟树可知,当APB1和APB2分频数为1的时候,TIM1、TIM8~TIM11的时钟为APB2的时钟,TIM2~TIM7、TIM12~TIM14的时钟为APB1的时钟;而如果APB1和APB2分频数不为1,那么TIM1、TIM8~TIM11的时钟为APB2的时钟的两倍,TIM2~TIM7、TIM12~TIM14的时钟为APB1的时钟的两倍。

因为系统初始化SystemInit函数里初始化APB1总线时钟为4分频即42M,APB2总线时钟为2分频即84M,所以TIM1、TIM8~TIM11的时钟为APB2时钟的两倍即168M,TIM2~TIM7、TIM12~TIM14的时钟为APB1的时钟的两倍即84M。

知道定时器的时钟源频率我们用定时器做延时就很方便了,只要设定合适的分频系数即可,附一下用中断实现延时的公式:(摘自原子的STM32F4开发指南)

Tout = ((arr+1)*(psc+1))/T clk;

公式中psc就是分频系数,arr就是计数值,达到这个计数就会发生溢出中断,T clk就是我上述分析的时钟源频率的倒数。

STM32F407运用总结

STM32运用总结主要分为IO口,定时器的PWM和QEI,中断,ADC,DAC和DMA介绍。

在STM32的运用中第一步一般是使能相应模块的时钟,然后配置IO 口,最后配置相应的寄存器。

1.IO口STM32的IO口非常多,而且与其它外设模块通常是复用的。

在不同的外设中IO口的设置是不一样的。

这一部分介绍普通的数值IO口。

IO口有A-G共7组,每组16口。

1.IO口在时钟总线AHB1上,使能对应端口的时钟。

在寄存器RCC->AHB1ENR中。

2.配置IO口的模式,普通的IO口配置为普通的输入输出模式。

配置IO口是悬空还是上拉或者下拉。

以上两步分别在寄存器GPIOx->MODER和GPIOx-> PUPDR(x=A,B,C,D,E,F,G)3.其中配置为输出模式时还要设置速度和相应的输出方式,开漏或者推挽,以上两步分别在寄存器GPIOx-> OSPEEDR和GPIOx->OTYPER(x=A,B,C,D,E,F,G)。

4.设置IO口的高低电平。

在寄存器GPIOx->BSRRH中置相应的位为1就是将相应的位置0,在寄存器GPIOx->BSRRL中置相应的位为1就是将相应的位置1.另外还可以设置GPIOx_ODR寄存器来设置输出电平以及读取GPIOx_IDR寄存器来获取输入电平。

2.PWMSTM32的定时器也非常之多,用到的主要是两个部分:用定时器产生PWM和定时触发ADC,这里一部分介绍PWM。

(高级定时器的配置和这差不多,由于在STM32F103里面已经尝试过在STM32F407里面就没有再写)1.配置IO口。

我们说过STM32的外设模块主要是和IO口复用的,因此在使用外设模块时首先配置好相应的IO口。

比如使用A口的PA1作为定时器Timer2的PWM输出。

则应按照如下的步骤来配置PA1。

1)使能A口的时钟。

在寄存器RCC->AHB1ENR中。

2)配置PA1为复用功能。

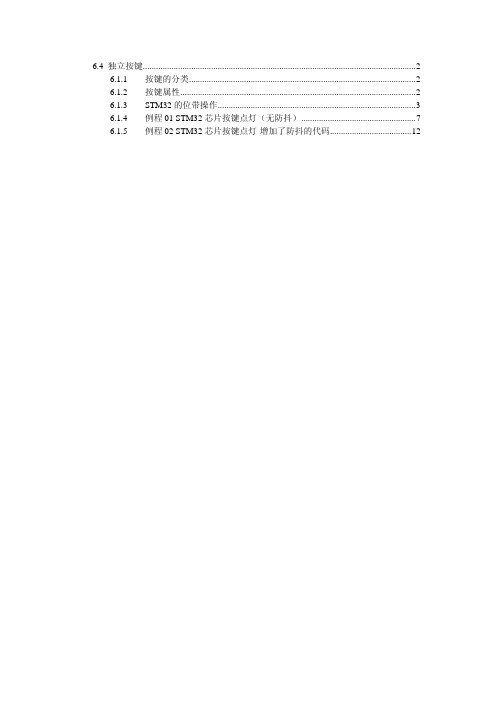

6.4 STM32F407ZGT独立按键功能深入剖析(神舟王407)

6.4 独立按键 (2)6.1.1 按键的分类 (2)6.1.2 按键属性 (2)6.1.3 STM32的位带操作 (3)6.1.4 例程01 STM32芯片按键点灯(无防抖) (7)6.1.5 例程02 STM32芯片按键点灯-增加了防抖的代码 (12)6.4 独立按键6.1.1按键的分类目前,按键有多种形式。

有机械接触式,电容式,轻触式等。

1.按制作工艺分:硬板按键:带弹簧的按键焊接在印刷电路板上软板键盘:以导电橡胶作为接触材料放在以聚脂薄膜作为基底的印刷电路上所形成的按键。

2.按工艺原理分:可以将键盘分为编码键盘和非编码键盘,编码键盘的键盘电路内包含有硬件编码器,当按下某—个键后,键盘电路能直接提供与该键相对应的编码信息,例如ASCII码。

非编码键盘的键盘电路中只有较简单的硬件,采用软件来识别按下键的位置,并提供与按下键相对应的中间代码送主机,然后由软件将中间代码转换成相应的字符编码,例如ASCII码;非编码键盘主要靠软件编程来识别的,在单片机组成的各种系统中,用的较多的是非编码键盘。

非编码键盘又分为独立键盘和行列式(又称矩阵式)键盘。

6.1.2按键属性键盘实际上就是一组按键,在单片机外围电路中,通常用到的按键都是机械弹性开关,当开关闭合时,线路导通,开关断开时,线路断开,下图是几种单片机系统常见的按键:弹性小按键被按下时闭合,松手后自动断开;自锁式按键按下时闭合且会自动锁住,只有再次按下时才弹起断开。

单片机的外围输入控制用小弹性按键较好,单片机检测按键的原理是:单片机的I/O口既可作为输出也可作为输入使用,当检测按键时用的是它的输入功能,我们把按键的一端接地,另一端与单片机的某个I/O口相连,开始时先给该I/O口赋一高电平,然后让单片机不断地检测该I/O口是否变为低电平,当按键闭合时,即相当于该I/O口通过按键与地相连,变成低电平,程序一旦检测到I/O口变为低电平则说明按键被按下,然后执行相应的指令。

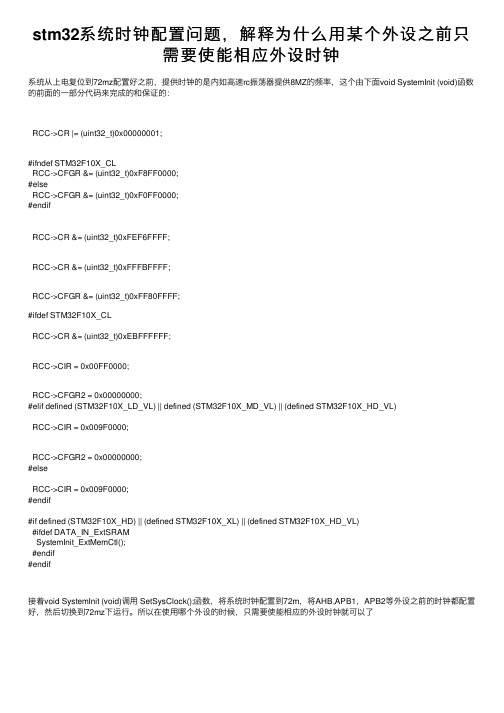

stm32系统时钟配置问题

stm32系统时钟配置问题系统从上电复位到72mz 配置好之前,提供时钟的是内如高速rc 振荡器提供8MZ 的频率,这个由下面void SystemInit (void)函数的前面的一部分代码来完成的和保证的:RCC->CR |= (uint32_t)0x00000001;#ifndef STM32F10X_CLRCC->CFGR &= (uint32_t)0xF8FF0000;#elseRCC- >CFGR &= (uint32_t)0xF0FF0000;#endif RCC->CR &= (uint32_t)0xFEF6FFFF; RCC->CR &= (uint32_t)0xFFFBFFFF;RCC->CFGR &= (uint32_t)0xFF80FFFF;#ifdef STM32F10X_CLRCC->CR &= (uint32_t)0xEBFFFFFF;RCC->CIR = 0x00FF0000;RCC->CFGR2 = 0x00000000;#elif defined (STM32F10X_LD_VL) || defined (STM32F10X_MD_VL) || (defined STM32F10X_HD_VL)RCC->CIR =0x009F0000;RCC->CFGR2 = 0x00000000;#elseRCC->CIR = 0x009F0000;#endif#if defined (STM32F10X_HD) || (defined STM32F10X_XL) || (defined STM32F10X_HD_VL)#ifdefDATA_IN_ExtSRAMSystemInit_ExtMemCtl();#endif#endif接着void SystemInit (void)调用SetSysClock();函数,将系统时钟配置到72m,将AHB,APB1,APB2 等外设之前的时钟都配置好,然后切换到72mz 下运行。

6.3 STM32的时钟深入剖析(32M,40M,72M灵活切换)

率不再有固定的关系,下面来详细解析 STM32 微控制器的时钟树。下图是 STM32 微控制 器的时钟树:

下表是结合图表明出来的: 标号

释义

1

内部低速振荡器(LSI,40Khz)

2

外部低速振荡器(LSE,32.768Khz)

6.1.4 例程01 STM32芯片32MHZ频率下跑点灯程序

1. 示例简介

我们先用一根杜邦线将 P0.0(PB8)和 JP19 上的 1 脚连起来(其实,连 JP19 上的任意一脚都可)。点灯程序在时钟主频 32MHz 下面运行,LED 灯的正极接的是

3.3V 电源,所以我们编程让 LED 负极拉低即 GPIO 引脚端口 B 的管脚 8 拉低,即 PB8 拉低,那么 LED 灯就会变亮,相关电路图如下图所示:

6.1.2 STM32的时钟

系统时钟的选择是在启动时进行,复位时内部 8MHZ 的 RC 振荡器被选为默认的 CPU 时钟,随后可以选择外部的、具失效监控的 4-16MHZ 时钟;当检测到外部时钟失效时,它 将被隔离,系统将自动地切换到内部的 RC 振荡器。

在 STM32 中,有五个时钟源,为 HSI、HSE、LSI、LSE、PLL,它们都是时钟所提供 的来源: 1. HSI 是高速内部时钟,RC 振荡器,频率默认为 8MHz,可以从 STM32 时钟树中看到

而“分支”很显然是最终的外部设备比如通用输入输出设备(GPIO)。这样可以轻易找出第

一条时钟的“脉络”:

3——5——7——21——8——9——11——13

对此条时钟路径做如下解析:

对于 3,首先是外部的 3-25MHz(前文已假设为 8MHz)输入;

正点原子stm32f407rtc时钟外部电路_概述说明

正点原子stm32f407rtc时钟外部电路概述说明1. 引言1.1 概述本文将介绍正点原子stm32f407rtc时钟外部电路的概述,并详细说明其设计要点以及与外部设备的接口和协议技术要点。

该外部电路旨在提供稳定、精确的时钟信号给STM32F407RTC芯片,以确保系统时间的准确性。

1.2 文章结构本文共分为五个部分,每个部分都涵盖了具体的内容。

- 第一部分是引言,主要介绍文章目录和概述。

- 第二部分是正点原子STM32F407RTC时钟外部电路概述说明,包括简要介绍STM32F407RTC芯片以及RTC外部电路设计要点和外部晶振选型及连接方法。

- 第三部分是原子STM32F407RTC外部时钟模块设计考虑因素,涵盖了电源与地线设计、防干扰措施和滤波器设计,以及时钟频率精度和稳定性考虑。

- 第四部分是STM32F407RTC与外部设备的接口与协议技术要点,详细介绍了I2C接口通信配置技巧、SPI接口通信配置技巧以及UART接口通信配置技巧。

- 最后一部分是结论,对整篇文章进行总结和回顾。

1.3 目的本文旨在帮助读者更好地理解正点原子STM32F407RTC时钟外部电路的设计原理和要点。

通过阐述电路设计考虑因素以及接口和协议技术要点,读者可以了解如何有效地搭建一个稳定、可靠的时钟外部电路,并且能够与其他设备进行良好的通信。

此外,我们也将探讨一些优化技巧和经验教训,以帮助读者在实际应用中避免常见问题和错误。

最终,希望读者能够在正点原子STM32F407RTC开发中有所启发并取得成功。

2. 正点原子stm32f407rtc时钟外部电路概述说明2.1 STM32F407RTC简介正点原子stm32f407rtc是一款基于STM32F407芯片的实时时钟模块,具有高度精确的计时功能。

它可以用于各种需要准确时间计量的应用场景,如智能家居系统、工业自动化控制等。

2.2 RTC外部电路设计要点在设计正点原子stm32f407rtc时钟外部电路时,需要考虑以下要点:首先,在供电方面,应保证稳定可靠的供电源并避免电压波动对时钟模块造成影响。

stm32f407的标准库的时间基准

《探究STM32F407的标准库时间基准》1. 引言在嵌入式系统开发中,时间基准是非常重要的,尤其是对于STM32F407这样的微控制器。

本文将深入探讨STM32F407标准库的时间基准,并分析其在嵌入式系统中的应用和优势。

2. STM32F407的时间基准STM32F407微控制器是STMicroelectronics推出的一款高性能、低功耗的ARM Cortex-M4内核微控制器。

它内置了丰富的外设和功能模块,其中包括多种定时器和计数器,这些外设提供了丰富的时间基准功能。

2.1 定时器STM32F407内置了多个通用定时器(TIM),这些定时器可以提供精确的定时和计数功能。

通过配置TIM的各种参数,可以实现不同精度和周期的时间基准。

2.2 SysTick定时器除了通用定时器外,STM32F407还内置了SysTick定时器。

SysTick 定时器是一个24位向下计数器,可以提供多种时钟频率的选择和中断功能。

它适用于系统级的时间基准。

3. STM32F407标准库的时间基准应用在嵌入式系统开发中,时间基准通常用于任务调度、周期性操作、时序控制等方面。

STM32F407标准库提供了丰富的时间基准功能,可以应用于各种实际场景。

3.1 任务调度通过配置定时器的定时周期和中断触发,可以实现多任务的精确调度。

在实时操作系统(RTOS)中,时间基准是任务调度的重要依据,STM32F407标准库的时间基准为任务调度提供了可靠的支持。

3.2 时序控制许多嵌入式系统需要精确的时序控制,例如通信协议处理、传感器采样等。

通过STM32F407的定时器和计数器,可以实现精确的时序控制,保证系统的稳定性和可靠性。

4. 个人观点和总结对于嵌入式系统开发者来说,熟练掌握STM32F407标准库的时间基准是非常重要的。

时间基准不仅可以提高系统的性能和稳定性,还可以为开发者提供便利和灵活性。

我建议在实际项目中充分利用STM32F407的时间基准功能,以实现更加可靠和高效的嵌入式系统。

STM32时钟详解

STM32中有一个全速功能的USB模块,其串行接口引擎需要一个频率为48MHz的时钟源。该时钟源只能从PLL输出端获 取,可以选择为1.5分频或者1分频,也就是,当需要使用USB模块时,PLL必须使能,并且时钟频率配置为48MHz或72MHz。

在以上的时钟输出中,有很多是带使能控制的,例如AHB总线时钟、内核时钟、各种APB1外设、APB2外设等等。当需要 使用某模块时,记得一定要先使能对应的时钟。

需要注意的是定时器的倍频器,当APB的分频为1时,它的倍频值为1,否则它的倍频值就为2。

连接在APB1(低速外设)上的设备有:电源接口、备份接口、CAN、USB、I2C1、I2C2、UART2、UART3、SPI2、窗口看门 狗、Timer2、Timer3、Timer4。注意USB模块虽然需要一个单独的48MHz时钟信号,但它应该不是供USB模块工作的时钟,而 只是提供给串行接口引擎(SIE)使用的时钟。USB模块工作的时钟应该是由APB1提供的。

同时这种设定也是有规律可循的设定参数也是有顺序规范的这是应用中应当注意的例如pll的设定需要在使能之前一旦pll使能后参数不可更经过此番设置后由于我的电路板上是8mhz晶振所以系统时钟为72mhz高速总线和低速总线2都为72mhz低速总线1为36mhzadc时钟为12mhzusb时钟经过15分频设置就可以实现48mhz的数据传输

static void RCC_Config(void)

第2页

STM32时钟讲解.txt {

/* 这里是重置了RCC的设置,类似寄存器复位 */ RCC_DeInit();

STM32F407使用总结

STM32运用总结主要分为IO口,定时器的PWM和QEI,中断,ADC,DAC和DMA介绍。

在STM32的运用中第一步一般是使能相应模块的时钟,然后配置IO口,最后配置相应的寄存器。

1.IO口STM32的IO口非常多,而且与其它外设模块通常是复用的。

在不同的外设中IO口的设置是不一样的。

这一部分介绍普通的数值IO口。

IO口有A-G共7组,每组16口。

1.IO口在时钟总线AHB1上,使能对应端口的时钟。

在寄存器RCC->AHB1ENR中。

2.配置IO口的模式,普通的IO口配置为普通的输入输出模式。

配置IO口是悬空还是上拉或者下拉。

以上两步分别在寄存器GPIOx->MODER和GPIOx->PUPDR(x=A,B,C,D,E,F,G)3.其中配置为输出模式时还要设置速度和相应的输出方式,开漏或者推挽,以上两步分别在寄存器GPIOx-> OSPEEDR和GPIOx->OTYPER(x=A,B,C,D,E,F,G)。

4.设置IO口的高低电平。

在寄存器GPIOx->BSRRH中置相应的位为1就是将相应的位置0,在寄存器GPIOx->BSRRL中置相应的位为1就是将相应的位置1.另外还可以设置GPIOx_ODR寄存器来设置输出电平以及读取GPIOx_IDR寄存器来获取输入电平。

2.PWMSTM32的定时器也非常之多,用到的主要是两个部分:用定时器产生PWM和定时触发ADC,这里一部分介绍PWM。

(高级定时器的配置和这差不多,由于在STM32F103里面已经尝试过在STM32F407里面就没有再写)1.配置IO口。

我们说过STM32的外设模块主要是和IO口复用的,因此在使用外设模块时首先配置好相应的IO口。

比如使用A口的PA1作为定时器Timer2的PWM输出。

则应按照如下的步骤来配置PA1。

1)使能A口的时钟。

在寄存器RCC->AHB1ENR中。

2)配置PA1为复用功能。

基于stm32f407的精确时钟同步协议的实现

1 引言

工业现场的数据采集变得越来越模块化,但当 需要测量多个外部的数据时,可能需要多个模块。 将这些由传感器采集的数据通过网络上传的时候, 由于没有时间信息,远程上位机不能很好将采集数 据融合处理,一般只能独立的对采集上来的数据处 理。为了实现对采集数据的时钟同步,需要对数据 采集模块间进行时钟同步。

当 前 几 种 比 较 流 行 的 时 间 同 步 协 议 有 NTP (Network Time Protocol)[1]和 PTP(Precision Time Protocol)[2],两者的原理类似,都是实现主时钟节点 和从时钟节点间的时间同步,其中 PTP 协议是网络 测量和控制系统时钟同步协议(IEEE1588 协议)的 简称,具体的差异如图 1 所示。从图中可以看出, NTP 和 PTP 时间戳的截取的位置不同。NTP 获取 的时间戳的位置是应用层,而 PTP 时间戳的截取的 位置是在物理层。正是由于获取时间戳的位置不

ZHANG Duanyang XIAO Li FU Zhongmin (School of Automation,Huazhong University of Science and Technology,Wuhan 430074)

Abstract In the field of industrial data acquisition,each node is more and more intelligent and networked,so the high-preci⁃ sion time synchronization between multiple nodes becomes more and more urgent. The method of clock synchronization and time stamp are used to collect the data,which brings great convenience to the processing of the later data,especially in the multi-sensor data fusion.“Precision Clock Synchronization Protocol for Networked Measurement and Control Systems”referred to as the IEEE1588 protocol come into being.In this paper,the stm32f407 microcontroller as the core of the development board is used to achieve the IEEE1588 protocol as the slave clock,and the LAN host computer is configured as the master clock to complete the pre⁃ cise clock synchronization between the slave clock and the master clock.In this paper,the master clock is synchronized with the slave clock,and the master clock is synchronized with multiple slave clocks,and the clock accuracy between them is 2us.

stm32系统时钟配置问题,解释为什么用某个外设之前只需要使能相应外设时钟

stm32系统时钟配置问题,解释为什么⽤某个外设之前只需要使能相应外设时钟系统从上电复位到72mz配置好之前,提供时钟的是内如⾼速rc振荡器提供8MZ的频率,这个由下⾯void SystemInit (void)函数的前⾯的⼀部分代码来完成的和保证的:RCC->CR |= (uint32_t)0x00000001;#ifndef STM32F10X_CLRCC->CFGR &= (uint32_t)0xF8FF0000;#elseRCC->CFGR &= (uint32_t)0xF0FF0000;#endifRCC->CR &= (uint32_t)0xFEF6FFFF;RCC->CR &= (uint32_t)0xFFFBFFFF;RCC->CFGR &= (uint32_t)0xFF80FFFF;#ifdef STM32F10X_CLRCC->CR &= (uint32_t)0xEBFFFFFF;RCC->CIR = 0x00FF0000;RCC->CFGR2 = 0x00000000;#elif defined (STM32F10X_LD_VL) || defined (STM32F10X_MD_VL) || (defined STM32F10X_HD_VL)RCC->CIR = 0x009F0000;RCC->CFGR2 = 0x00000000;#elseRCC->CIR = 0x009F0000;#endif#if defined (STM32F10X_HD) || (defined STM32F10X_XL) || (defined STM32F10X_HD_VL)#ifdef DATA_IN_ExtSRAMSystemInit_ExtMemCtl();#endif#endif接着void SystemInit (void)调⽤ SetSysClock();函数,将系统时钟配置到72m,将AHB,APB1,APB2等外设之前的时钟都配置好,然后切换到72mz下运⾏。

STM32的各种时钟系统的应用解析

STM32的各种时钟系统的应用解析时钟系统是处理器的核心,所以在学习STM32所有外设之前,认真学习时钟系统是必要的,有助于深入理解STM32。

重要的时钟:PLLCLK,SYSCLK,HCKL,PCLK1,PCLK2 之间的关系要弄清楚;1、HSI:高速内部时钟信号STM32单片机内带的时钟(8M频率)精度较差2、HSE:高速外部时钟信号精度高来源(1)HSE外部晶体/陶瓷谐振器(晶振)(2)HSE用户外部时钟3、LSE:低速外部晶体32.768kHz 主要提供一个精确的时钟源一般作为RTC时钟使用在STM32中,有五个时钟源,为HSI、HSE、LSI、LSE、PLL。

①、HSI是高速内部时钟,RC振荡器,频率为8MHz。

②、HSE是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为4MHz~16MHz。

③、LSI是低速内部时钟,RC振荡器,频率为40kHz。

④、LSE是低速外部时钟,接频率为32.768kHz的石英晶体。

⑤、PLL为锁相环倍频输出,其时钟输入源可选择为HSI/2、HSE或者HSE/2。

倍频可选择为2~16倍,但是其输出频率最大不得超过72MHz。

其中40kHz的LSI供独立看门狗IWDG使用,另外它还可以被选择为实时时钟RTC的时钟源。

另外,实时时钟RTC的时钟源还可以选择LSE,或者是HSE的128分频。

RTC的时钟源通过RTCSEL[1:0]来选择。

STM32中有一个全速功能的USB模块,其串行接口引擎需要一个频率为48MHz的时钟源。

该时钟源只能从PLL输出端获取,可以选择为1.5分频或者1分频,也就是,当需要使用USB模块时,PLL必须使能,并且时钟频率配置为48MHz或72MHz。

另外,STM32还可以选择一个时钟信号输出到MCO脚(PA8)上,可以选择为PLL输出的2分频、HSI、HSE、或者系统时钟。

STM32f407系统定时器时钟配置计算

STM32f407系统定时器时钟配置计算首先,我们需要配置系统定时器的时钟源。

STM32F407的系统定时器可以使用内部时钟源(HCLK/8)或外部时钟源。

通过软件配置,我们可以选择其中一种时钟源。

1.配置内部时钟源:要使用内部时钟源,可以通过RCC寄存器来配置。

具体需要做以下几步:a. 使能系统定时器时钟:在 RCC_APBxENR 寄存器中设置位SysTickEN=1,其中 x 为适当的 APBx 总线索引。

b.配置系统定时器时钟源:在STK_CTRL寄存器中设置位CLKSOURCE=12.配置外部时钟源:如果要使用外部时钟源作为系统定时器的时钟源,我们需要将外部时钟源与系统的时钟树相连。

具体的配置方法因时钟源的不同而不同,可参考具体芯片的参考手册。

配置了系统定时器的时钟源后,我们可以计算定时器中断的时间间隔。

系统定时器中断的时间间隔=(计数器周期)*(重载值+1)/(时钟频率)其中,计数器周期为24位,取值范围为0~2^24-1、时钟频率为系统定时器的时钟源频率。

重载值是计数器的初始值,当计数器减到0时,会触发定时中断。

举个例子,假设系统定时器的时钟源频率为8MHz,我们希望计算系统定时器中断每100ms触发一次的重载值。

中断触发周期 = 100ms = 0.1s时钟频率=8MHz=8*10^6Hz由于重载值需要为整数,我们可以将计算结果四舍五入为最接近的整数,即重载值为477以上就是STM32F407系统定时器时钟配置和计算方法的简要介绍。

配置完系统定时器的时钟源,并计算出需要的重载值后,我们可以通过编程设置相关寄存器,来开始使用系统定时器进行定时中断的任务。

STM32F407运用总结教学内容

STM32运用总结主要分为IO口,定时器的PWM和QEI,中断,ADC,DAC和DMA介绍。

在STM32的运用中第一步一般是使能相应模块的时钟,然后配置IO口,最后配置相应的寄存器。

1.IO口STM32的IO口非常多,而且与其它外设模块通常是复用的。

在不同的外设中IO口的设置是不一样的。

这一部分介绍普通的数值IO口。

IO口有A-G共7组,每组16口。

1.IO口在时钟总线AHB1上,使能对应端口的时钟。

在寄存器RCC->AHB1ENR中。

2.配置IO口的模式,普通的IO口配置为普通的输入输出模式。

配置IO口是悬空还是上拉或者下拉。

以上两步分别在寄存器GPIOx->MODER和GPIOx-> PUPDR(x=A,B,C,D,E,F,G)3.其中配置为输出模式时还要设置速度和相应的输出方式,开漏或者推挽,以上两步分别在寄存器GPIOx-> OSPEEDR和GPIOx->OTYPER(x=A,B,C,D,E,F,G)。

4.设置IO口的高低电平。

在寄存器GPIOx->BSRRH中置相应的位为1就是将相应的位置0,在寄存器GPIOx->BSRRL中置相应的位为1就是将相应的位置1.另外还可以设置GPIOx_ODR寄存器来设置输出电平以及读取GPIOx_IDR寄存器来获取输入电平。

2.PWMSTM32的定时器也非常之多,用到的主要是两个部分:用定时器产生PWM和定时触发ADC,这里一部分介绍PWM。

(高级定时器的配置和这差不多,由于在STM32F103里面已经尝试过在STM32F407里面就没有再写)1.配置IO口。

我们说过STM32的外设模块主要是和IO口复用的,因此在使用外设模块时首先配置好相应的IO口。

比如使用A口的PA1作为定时器Timer2的PWM输出。

则应按照如下的步骤来配置PA1。

1)使能A口的时钟。

在寄存器RCC->AHB1ENR中。

2)配置PA1为复用功能。

STM32时钟配置方法详解

STM32时钟配置方法详解STM32是意法半导体(STMicroelectronics)公司推出的一系列32位Flash微控制器,被广泛应用于各种嵌入式系统中。

时钟是STM32微控制器的核心部分,正确配置时钟可以确保系统正常工作并达到预期的性能。

本文将详细介绍STM32时钟配置的方法。

1.时钟源:STM32微控制器提供了多个时钟源,包括内部时钟(HSI、LSI)和外部时钟(HSE、LSE)。

其中,HSI(高速内部时钟)是一个高频率(通常为8MHz)的内部RC振荡器,适用于低功耗应用;LSI(低速内部时钟)是一个低频率(通常为40kHz)的内部RC振荡器,用于RTC(实时时钟)模块;HSE(高速外部时钟)是一个外接的高频晶振,用于提供更精确的时钟信号;LSE(低速外部时钟)是一个外接的低频晶振,适用于RTC模块。

2.主频和系统时钟:主频是指CPU的时钟频率,系统时钟是指STM32微控制器的总线时钟,包括AHB(高性能总线)、APB1(低速外设总线)和APB2(高速外设总线)。

在进行STM32时钟配置之前,需要按照以下几个步骤来完成。

1.启用对应的时钟源:根据具体需求,选择合适的时钟源并启用相应的时钟。

可以通过设置RCC_CR寄存器和RCC_APB1ENR/RCC_APB2ENR寄存器来实现。

例如,要使用HSE作为时钟源,需要首先启用HSE时钟。

2.配置时钟分频器:为了使系统时钟不超过芯片规格要求的最大频率,需要对时钟进行分频。

分频器有两个,即AHB分频器和APB分频器。

可以通过设置RCC_CFGR寄存器来实现。

例如,将AHB分频器设置为8,将APB1和APB2分频器分别设置为4,可以将主频分别分频为8MHz、32MHz和64MHz。

3.等待时钟稳定:当启用外部时钟源时,需要等待时钟稳定。

可以通过读取RCC_CR寄存器的特定标志位来判断时钟是否稳定。

4. 配置Flash存储器的延时:根据主频的不同,需要设置Flash存储器的访问延时,以确保正常读写数据。

stm32f407之通用定时器

stm32f407之通用定时器

通用定时器

通用定时器(TIM2 to TIM5)包括由可编程的分频器驱动一个的16位或32位自动重载计数器。

它们可用于多种用途,包括测量输入信号的脉冲长度(输入捕获)或生成的输出波形(输出比较和PWM)。

可以使用定时器的预分频器和RCC时钟控制器分频器调制从几微秒到几毫秒的脉冲长度和波形周期。

它们是完全独立的,不共享任何资源。

主要特点:

通用TIMx定时器功能包括:

1. 16位(TIM3和TIM4)或32位(TIM2和TIM5)计数器,向上,向下,向上/向下自动重装计数。

2. 16位可编程预分频器(可在运行时改变)用于在1到65535之间细分计数器的时钟频率。

3. 多达4个独立的通道可用于:

- 输入捕捉

- 输出比较

- PWM生成(边缘和中心对齐模式)

- 单脉冲输出模式

4. 使用外部信号控制定时器和定时器互连的同步电路

5. 对以下事件中断/ DMA的生成:

- 更新:计数器溢出/下溢,计数器初始化(通过软件或内部/外部触发)

- 触发事件(计数器开始,停止,初始化或内部/外部触发计数)

- 输入捕捉

- 输出比较

6. 支持针对定位增量(正交)编码器和霍尔传感器电路

7. 触发输入作为外部时钟或者按周期的电流管理。

(完整版)STM32F407运用总结

(完整版)STM32F407运⽤总结STM32运⽤总结主要分为IO⼝,定时器的PWM和QEI,中断,ADC,DAC和DMA介绍。

在STM32的运⽤中第⼀步⼀般是使能相应模块的时钟,然后配置IO⼝,最后配置相应的寄存器。

1.IO⼝STM32的IO⼝⾮常多,⽽且与其它外设模块通常是复⽤的。

在不同的外设中IO⼝的设置是不⼀样的。

这⼀部分介绍普通的数值IO⼝。

IO⼝有A-G共7组,每组16⼝。

1.IO⼝在时钟总线AHB1上,使能对应端⼝的时钟。

在寄存器RCC->AHB1ENR中。

2.配置IO⼝的模式,普通的IO⼝配置为普通的输⼊输出模式。

配置IO⼝是悬空还是上拉或者下拉。

以上两步分别在寄存器GPIOx->MODER和GPIOx-> PUPDR(x=A,B,C,D,E,F,G)3.其中配置为输出模式时还要设置速度和相应的输出⽅式,开漏或者推挽,以上两步分别在寄存器GPIOx-> OSPEEDR和GPIOx->OTYPER(x=A,B,C,D,E,F,G)。

4.设置IO⼝的⾼低电平。

在寄存器GPIOx->BSRRH中置相应的位为1就是将相应的位置0,在寄存器GPIOx->BSRRL中置相应的位为1就是将相应的位置1.另外还可以设置GPIOx_ODR寄存器来设置输出电平以及读取GPIOx_IDR寄存器来获取输⼊电平。

2.PWMSTM32的定时器也⾮常之多,⽤到的主要是两个部分:⽤定时器产⽣PWM和定时触发ADC,这⾥⼀部分介绍PWM。

(⾼级定时器的配置和这差不多,由于在STM32F103⾥⾯已经尝试过在STM32F407⾥⾯就没有再写)1.配置IO⼝。

我们说过STM32的外设模块主要是和IO⼝复⽤的,因此在使⽤外设模块时⾸先配置好相应的IO⼝。

⽐如使⽤A⼝的PA1作为定时器Timer2的PWM输出。

则应按照如下的步骤来配置PA1。

1)使能A⼝的时钟。

在寄存器RCC->AHB1ENR中。

6.4 STM32F407ZGT独立按键功能深入剖析(神舟王407)

6.4 独立按键 (2)6.1.1 按键的分类 (2)6.1.2 按键属性 (2)6.1.3 STM32的位带操作 (3)6.1.4 例程01 STM32芯片按键点灯(无防抖) (7)6.1.5 例程02 STM32芯片按键点灯-增加了防抖的代码 (12)6.4 独立按键6.1.1按键的分类目前,按键有多种形式。

有机械接触式,电容式,轻触式等。

1.按制作工艺分:硬板按键:带弹簧的按键焊接在印刷电路板上软板键盘:以导电橡胶作为接触材料放在以聚脂薄膜作为基底的印刷电路上所形成的按键。

2.按工艺原理分:可以将键盘分为编码键盘和非编码键盘,编码键盘的键盘电路内包含有硬件编码器,当按下某—个键后,键盘电路能直接提供与该键相对应的编码信息,例如ASCII码。

非编码键盘的键盘电路中只有较简单的硬件,采用软件来识别按下键的位置,并提供与按下键相对应的中间代码送主机,然后由软件将中间代码转换成相应的字符编码,例如ASCII码;非编码键盘主要靠软件编程来识别的,在单片机组成的各种系统中,用的较多的是非编码键盘。

非编码键盘又分为独立键盘和行列式(又称矩阵式)键盘。

6.1.2按键属性键盘实际上就是一组按键,在单片机外围电路中,通常用到的按键都是机械弹性开关,当开关闭合时,线路导通,开关断开时,线路断开,下图是几种单片机系统常见的按键:弹性小按键被按下时闭合,松手后自动断开;自锁式按键按下时闭合且会自动锁住,只有再次按下时才弹起断开。

单片机的外围输入控制用小弹性按键较好,单片机检测按键的原理是:单片机的I/O口既可作为输出也可作为输入使用,当检测按键时用的是它的输入功能,我们把按键的一端接地,另一端与单片机的某个I/O口相连,开始时先给该I/O口赋一高电平,然后让单片机不断地检测该I/O口是否变为低电平,当按键闭合时,即相当于该I/O口通过按键与地相连,变成低电平,程序一旦检测到I/O口变为低电平则说明按键被按下,然后执行相应的指令。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

时钟频率的配置

{开始

ቤተ መጻሕፍቲ ባይዱ

{ /**** 程序总共 2 部分之第 1 部分 时钟频率的配置 ********************/

/***** 以下是关于 RCC 时钟 详细请见《STM32F20XXX 参考手册》5.3 节 RCC 寄存 器描述 *******/

unsigned char sws = 0; RCC->CR |= 0X00010000; //使能外部高速时钟 HSEON while(!(RCC->CR>>17)); //将 RCC_CR 寄存器的值右移 17 位,等待 HSERDY 就绪, 即外部时钟就绪

对于 5, 通过 PLL 选择位预先选择后续 PLL 分支的输入时钟(假设选择外部晶振);

对于 7,设置外部晶振的分频数(假设 1 分频);

对于 21,选择 PLL 倍频的时钟源(假设选择经过分频后的外部晶振时钟);

对于 8,设置 PLL 倍频数(假设 9 倍频);

对于 9,选择系统时钟源(假设选择经过 PLL 倍频所输出的时钟);

众所周知,微控制器(处理器)的运行必须要依赖周期性的时钟脉冲来驱动——往往由 一个外部晶体振荡器提供时钟输入为始,最终转换为多个外部设备的周期性运作为末,这种 时钟“能量”扩散流动的路径,犹如大树的养分通过主干流向各个分支,因此常称之为“时 钟树”。在一些传统的低端 8 位单片机诸如 51,AVR,PIC 等单片机,其也具备自身的一个 时钟树系统,但其中的绝大部分是不受用户控制的,亦即在单片机上电后,时钟树就固定在 某种不可更改的状态(假设单片机处于正常工作的状态)。比如 51 单片机使用典型的 12MHz 晶振作为时钟源,则外设如 IO 口、定时器、串口等设备的驱动时钟速率便已经是固定的, 用户无法将此时钟速率更改,除非更换晶振。

而“分支”很显然是最终的外部设备比如通用输入输出设备(GPIO)。这样可以轻易找出第

一条时钟的“脉络”:

3——5——7——21——8——9——11——13

对此条时钟路径做如下解析:

对于 3,首先是外部的 3-25MHz(前文已假设为 8MHz)输入;

对于 5,通过 PLL 选择位预先选择后续 PLL 分支的输入时钟(假设选择外部晶振);

6.2 时钟

6.1.1 什么是时钟

从 CPU 的时钟说起。 计算机是一个十分复杂的电子设备。它由各种集成电路和电子器件组成,每一块集成电 路中都集成了数以万计的晶体管和其他电子元件。这样一个十分庞大的系统,要使它能够正 常地工作,就必须有一个指挥,对各部分的工作进行协调。各个元件的动作就是在这个指挥 下按不同的先后顺序完成自己的操作的,这个先后顺序我们称为时序。时序是计算机中一个 非常重要的概念,如果时序出现错误,就会使系统发生故障,甚至造成死机。那么是谁来产 生和控制这个操作时序呢?这就是“时钟”。“时钟”可以认为是计算机的“心脏”,如同人 一样,只有心脏在跳动,生命才能够继续。不要把计算机的“时钟”等同于普通的时钟,它 实际上是由晶体振荡器产生的连续脉冲波,这些脉冲波的幅度和频率是不变的,这种时钟信 号我们称为外部时钟。它们被送入 CPU 中,再形成 CPU 时钟。不同的 CPU,其外部时钟 和 CPU 时钟的关系是不同的,下表列出了几种不同 CPU 外部时钟和 CPU 时钟的关系。 CPU 时钟周期通常为节拍脉冲或T周期,它是处理操作的最基本的单位。 在微程序控制器中,时序信号比较简单,一般采用节拍电位——节拍脉冲二级体制。就 是说它只要一个节拍电位,在节拍电位又包含若干个节拍脉冲(时钟周期)。节拍电位表示 一个CPU周期的时间,而节拍脉冲把一个CPU周期划分为几个叫较小的时间间隔。根据 需要这些时间间隔可以相等,也可以不等。 指令周期是取出并执行一条指令的时间。 指令周期常常有若干个CPU周期,CPU周期也称为机器周期,由于CPU访问一次 内存所花费的时间较长,因此通常用内存中读取一个指令字的最短时间来规定CPU周期。 这就是说,这就是说一条指令取出阶段(通常为取指)需要一个CPU周期时间。而一个C PU周期时间又包含若干个时钟周期(通常为节拍脉冲或T周期,它是处理操作的最基本的 单位)。这些时钟周期的总和则规定了一个CPU周期的时间宽度。

6.1.4 例程01 STM32芯片32MHZ频率下跑点灯程序

1. 示例简介 让点灯程序在时钟主频 32MHz 下面运行,LED 灯的正极接的是 3.3V 电源,所以我们编 程让 LED 负极拉低即 GPIO 引脚端口 F 的管脚 10 拉低,即 PD2 拉低,那么 LED 灯就 会变亮,相关电路图如下图所示:

6.2 时钟...............................................................................................................................2 6.1.1 什么是时钟.......................................................................................................2 6.1.2 STM32 的时钟..................................................................................................2 6.1.3 STM32 的时钟深入分析..................................................................................4 6.1.4 例程 01 STM32 芯片 32MHZ频率下跑点灯程序 ..........................................7 6.1.1 例程 02 STM32 芯片 40MHZ频率下跑点灯程序 ........................................14 6.1.2 例程 03 STM32 芯片 72MHZ频率下跑点灯程序 ........................................15

17

ADC预分频寄存器

18

ADC外设

19

PLL2分频数寄存器

20

PLL2倍频寄存器

21

PLL 时钟源选择寄存器

22

独立看门狗设备

23

RTC 设备

在认识这颗时钟树之前,首先要明确“主干”和最终的“分支”。假设使用外部 8MHz

晶振作为 STM32 的时钟输入源(这也是最常见的一种做法),则这个 8MHz 便是“主干”,

对于 11,设置 AHB 总线分频数(假设 1 分频); 对于 15,设置 APB2 总线分频数(假设 1 分频) 对于 16,时钟到达 APB2 总线; 现在来计算一下 GPIO 设备的最大驱动时钟速率(各个条件已在上述要点中假设):

1) 由 3 所知晶振输入为 8MHz,由○5——○21 知 PLL 的时钟源为经过分频后的外部 晶振时钟,并且此分频数为 1 分频,因此首先得出 PLL 的时钟源为:8MHz / 1 = 8MHz。

2) 由 8、9 知 PLL 倍频 9,且将 PLL 倍频后的时钟输出选择为系统时钟,则得出系统 时钟为 8MHz * 9 = 72MHz。

3) 时钟到达 AHB 预分频器,由 11 知时钟经过 AHB 预分频器之后的速率仍为 72MHz。 4) 时钟到达 APB2 预分频器,由 15 经过 APB2 预分频器后速率仍为 72MHz。 5) 时钟到达 APB2 总线外设 上面是原理的剖析,如果再不明白的,可以接下来看例程代码,理论联系实践是最好的老师。

对于 13,时钟到达 AHB 总线;

在上一章节中所介绍的 GPIO 外设属于 APB2 设备,即 GPIO 的时钟来源于 APB2 总线,

同样在上图中也可以寻获 GPIO 外设的时钟轨迹:

3——5——7——21——8——9——11——15——16

对于 3,首先是外部的 3-25MHz(前文已假设为 8MHz)输入;

3

外部高速振荡器(HSE,3-25MHz)

4

内部高速振荡器(HSI,8MHz)

5

PLL输入选择位

6

RTC时钟选择位

7

PLL1分频数寄存器

8

PLL1倍频寄存器

9

系统时钟选择位

10

USB分频寄存器

11

AHB分频寄存器

12

APB1分频寄存器

13

AHB总线

14

APB1外设总线

15

APB2分频寄存器

16

APB2外设总线

2. 调试说明: 下载代码,并且按下【复位】键,在神舟王 407 板上找到 LED2,可以看到该 LED1 灯

一亮一灭。

3. 关键代码: /*************** 程 序 总 共 2 部 分 之 第 1 部 分 *********************************/ /************ *******/ int main(void)

我们在这里,因为 STM32 神舟王 207 开发板上的晶振是 25MHZ 的,我们先 25 分 频,再 128 倍频,再 4 分频,输出就能达到 STM32 的 32MHZ 工作频率,分别先后用到了, PLLCFGR 中的 0-5 位、6-14 位、16-17 位。*/

RCC->PLLCFGR |= 0x19; //25 分频 RCC->PLLCFGR |=0x1<<13; //128 倍频 RCC->PLLCFGR |=0x1<<16; //4 分频

FLASH->ACR|=0x1; //CPU 和 FLASH 的频率不一样,所以需要等待

RCC->CR |= 1<<24; //将 PLL 使能 while(!(RCC->CR>>25)); //监控寄存器 CR 的 PLLRDY 位,等待 PLL 时钟就绪