DSP第5章-F28335-概述

DSP5-F28335中断系统及定时器

CPU定时器0 CPU定时器2 CPU定时器1

பைடு நூலகம்

GPIO MUX

注:外部中断3…7类似: 引脚对应GPIO32…63; 参见TI手册SPRUFB0D。

MUX

MUX

MUX

1

DMA

中断控制 XNMICR[15:0] XNMICTR[15:0]

XNMI_ XINT13

锁存

…

GPIOXNMISEL(4:0)

4、中断相关寄存器 a、中断标志寄存器--IFR

D15

D14

RTOSINT DLOGINT

RW-0

RW-0

D13 INT14

RW-0

D12 INT13

RW-0

……

D0 INT1

RW-0

Dx=1时,对应的中断请求信号已发生; Dx=0时,对应的中断请求信号未发生。

CPU响应中断后,对应的中断标志位自动清0。

全国教育科学“十一五”规划课题研究成果

《 DSP控制器原理与应用教程》

---基于TMS320F28335 & CCS5

主编 李全利 马骏杰 张思艳

高等教育出版社 2016.11

第五章 F28335中断系统及定时器

(一)、F28335的中断系统 (二)、F28335的CPU定时器 (三)、中断和CPU定时器应用示例

MUX INT12

(使能)

PIEIER12[INTx8:INTx1]

PIEACK

PIEACK[11]

INT1.1

PieCtrlRegs.PIEIER1.bit.INTx7=1

INT1.7 INT1.8

(标志)

PIEIFR1[INTx8:INTx1]

F28335课程设计

F28335课程设计一、课程目标知识目标:1. 学生能理解F28335的基本架构和功能特点,掌握其内部资源分配和使用方法。

2. 学生能运用C语言编写程序,实现对F28335的控制和数据处理。

3. 学生了解F28335在不同应用场景中的使用,理解其优缺点。

技能目标:1. 学生能够熟练使用开发工具对F28335进行编程,具备调试程序的能力。

2. 学生能够运用所学的知识,解决实际问题,具备一定的项目实践能力。

情感态度价值观目标:1. 学生培养对电子技术、嵌入式系统的兴趣,激发创新精神和探索欲望。

2. 学生树立正确的价值观,认识到所学知识在国家和个人发展中的重要性,增强社会责任感和使命感。

3. 学生养成团队协作、沟通交流的良好习惯,提高解决问题的能力。

课程性质分析:本课程为电子技术学科,针对高年级学生,以实践操作为主,理论联系实际。

课程内容紧密围绕F28335芯片的应用,旨在提高学生的实际操作能力和项目实践能力。

学生特点分析:高年级学生对电子技术有一定的基础,具备一定的编程能力,对新技术充满好奇,有较强的自主学习能力。

教学要求:1. 结合学生特点,注重实践操作,提高学生的动手能力。

2. 强化理论知识与实际应用的联系,培养学生的创新意识。

3. 注重团队协作,提高学生的沟通与表达能力。

二、教学内容1. F28335芯片概述:介绍F28335的基本架构、功能特点、性能参数,以及在各领域的应用。

- 教材章节:第1章 嵌入式系统概述2. F28335编程环境搭建:学习F28335的开发工具、编程环境和调试方法。

- 教材章节:第2章 嵌入式系统开发环境3. F28335编程语言:掌握C语言编程基础,学习针对F28335的编程技巧。

- 教材章节:第3章 嵌入式C语言编程4. F28335内部资源使用:学习F28335内部外设的使用,如GPIO、中断、定时器等。

- 教材章节:第4章 嵌入式系统内部资源5. F28335应用实例:分析F28335在不同场景下的应用,如电机控制、信号处理等。

DSP原理与应用2011-第五章TMS320F28335片(精)

DSP 原理与应用The Technology & Applications of DSPs第五章: TMS320F28335片内外设北京交通大学电气工程学院夏明超郝瑞祥万庆祝***************.cn**************.cn**************.cn:TMS320F28335第五讲: TMS320F28335片内外设教学目标:掌握TMS320F28335内核结构,例如A/D转换、串行通信接口、串行外设接口。

外设接重点:TMS320F28335A/DCS308335内部/C 的正确使用,串行通信接口应用。

难点:TMS320F28335的ADC 寄存器操作和串行通信寄存器操作。

教学内容分两部分51§5.1:TMS320F28335内模拟/数字转换§5.2 :TMS320F28335系列串行通信接口SCI 和Modbus 协议介绍DSP 原理与应用2DSP原理与应用3 ADC 有关引脚§5.1 TMS320F28335内模拟/数字转换§5.1 .1Features and functions of ADC module:◆core with built-in dual sample-and-hold◆Simultaneous sampling or sequential sampling modesp g q p g ◆Analog input: ◆Fast conversion time runs at ADC clock orFast conversion time runs at , ADC clock, or 6.25 MSPSmultiplexed inputs◆, multiplexed inputs◆capability provides up to 16 " t i " i i l i E h i "autoconversions" in a single session. Each conversioncan be to select any 1 of 16 input channels.DSP 原理与应用4Sequencer can be operated as two independent 8-state ◆Sequencer can be operated as two independent 8-state sequencers or as one large 16-state sequencer (i.e., two cascaded 8-state sequencerstwo cascaded 8state sequencers.◆(individually addressable to store conversion values store conversion valuesA/DC digital value:DSP 原理与应用2012年9月3日5◆for the start-of-conversion sequence–S/W -software immediate start–ePWM 1-6–GPIO XINT2◆allows interrupt request on every end-of-sequence (EOS or every other EOSy q ( y◆Sequencer can operate in mode, allowing multiple "time-sequenced triggers" to synchronize p q gg yconversions.Sample-and-hold (S/Hacquisition time window has ◆Sample and hold (S/H acquisition time window has separateA/DC模块框图(Block diagram of A/DC Module)§5.1. 2ADC 有关的寄存器控制寄存器通道顺序选择寄存器结果寄存器ADC有关的寄存器(序)控制寄存器状态寄存器参考电压选择寄存器偏移电压调整寄存器§5.1.3 ADC操作模式1 顺序采样模式(Sequential Sampling Mode)根据采样模式划分,包括顺序采样和同步采样2同步采样模式(Simultaneous Sampling Mode)DSP 原理与应用2012年9月3日11根据转换模式划分,包括:级联模式转换和和双序列模式转换1)级联模式转换DSP 原理与应用2012年9月3日122)双序列模式转换DSP 原理与应用2012年9月3日13 单序列模式和级联模式对比DSP 原理与应用2012年9月3日14§5.1.4 ADC电压参考默为使用内部电压参考也以使用外部电压参考允许值为●默认为使用内部电压参考,也可以使用外部电压参考,允许值为2.048V ,1.5V 和1.024V 。

DSP原理与应用2011-第五章 TMS320F28335片内外设_ad转换SCI

掌握TMS320F28335内核结构,例如A/D转换、串行通信接口、 串行 外设接口。

重点:

TMS320F28335内部A/DC的正确使用,串行通信接口应用。

难点:

TMS320F28335的ADC寄存器操作和串行通信寄存器操作。

教学内容分两部分

§5.1:TMS320F28335内模拟/数字转换 §5.2 :TMS320F28335系列串行通信接口SCI和Modbus协议介绍

7

§5.1 .2 ADC有关的寄存器

控制寄存器

通道顺序选 择寄存器

结 果 寄 存 器

DSP原理与应用

2012年9月3日

8

ADC有关的寄存器(序)

控制寄存器 状态寄存器

参考电压选择寄存器 偏移电压调整寄存器

DSP原理与应用

2012年9月3日

9

§5.1.3 ADC 操作模式

根据采样模式划分,包括顺序采样和同步采样 1) 顺序采样模式(Sequential Sampling Mode)

DSP原理与应用

2012年9月3日

10

2) 同步采样模式(Simultaneous Sampling Mode)

DSP原理与应用

2012年9月3日

11

根据转换模式划分,包括: 级联模式转换和和双序列模式转换 1) 级联模式转换

DSP原理与应用

2012年9月3日

12

2) 双序列模式转换

DSP原理与应用

DSP原理与应用

4

Sequencer can be operated as two independent 8-state sequencers or as one large 16-state sequencer (i.e., two cascaded 8-state sequencers).

dsp课课程设计28335

dsp课课程设计28335一、教学目标本章节的教学目标包括以下三个方面:1.知识目标:使学生掌握DSP28335的基本结构、工作原理和编程方法,了解其在数字信号处理领域的应用。

2.技能目标:培养学生具备使用DSP28335进行数字信号处理的能力,能独立完成相关项目和实验。

3.情感态度价值观目标:激发学生对DSP技术的兴趣,培养其创新意识和团队协作精神,认识到DSP技术在现代社会中的重要性。

二、教学内容本章节的教学内容主要包括以下几个部分:1.DSP28335的基本结构和工作原理:介绍DSP28335的内部结构、各部分功能和工作原理。

2.DSP28335的编程方法:讲解DSP28335的编程语言、编程环境和编程技巧。

3.DSP28335在数字信号处理中的应用:介绍DSP28335在通信、图像处理、音频处理等领域的应用案例。

4.相关实验和实践项目:安排一系列实验和实践项目,使学生能够动手操作,巩固所学知识。

三、教学方法本章节的教学方法包括以下几种:1.讲授法:用于讲解DSP28335的基本原理、编程方法和应用案例。

2.讨论法:学生分组讨论,分享学习心得和解决问题的方法。

3.案例分析法:分析实际应用案例,使学生更好地理解DSP28335在工程中的应用。

4.实验法:安排实验和实践项目,让学生动手操作,提高其实际操作能力。

四、教学资源本章节的教学资源包括以下几种:1.教材:选用合适的教材,为学生提供系统、科学的学习资料。

2.参考书:推荐相关参考书籍,丰富学生的知识储备。

3.多媒体资料:制作课件、视频等多媒体资料,提高课堂趣味性和教学效果。

4.实验设备:准备DSP28335开发板和相关实验设备,为学生提供实践操作的机会。

五、教学评估本章节的教学评估主要包括以下几个方面:1.平时表现:评估学生在课堂上的参与程度、提问回答等情况,占总评的30%。

2.作业:评估学生完成作业的质量和进度,占总评的30%。

3.考试:安排一次期末考试,评估学生对DSP28335知识的掌握程度,占总评的40%。

TMS320F28335中文资料(难得的资料)

EALLOW; // This is needed to write to EALLOW protected registers

PieVectTable.XINT2 = &ISRExint; //告诉中断入口地址

EDIS; // This is needed to disable write to EALLOW protected registers

F28335 是带浮点运算的,动态范围更大。 F2833x 的执行速度,比相同时钟频率的 F28xx 系列定点芯片,快 50%。处理数学运算性能提

升 2.45 倍,控制算法性能提升 1.57 倍,DSP 性能提升 1.38 倍。总体性能提升近 2 倍。

TMS320F28335 的 ADC

TMS320F28335 上有 16 通道、12 位的模数转换器 ADC。他可以被配置为两个独立的 8 通道输 入模式,也可以通过配置 AdcRegs.ADCTRL1.bit.SEQ_CASC=1,将其设置为一个 16 通道的级 联输入模式。输入的方式可以通过配置 AdcRegs.ADCTRL1.bit.ACQ_PS=1,将其设置为顺序

{

EALLOW; // Before setting PLLCR turn off missing clock detect logic

SysCtrlRegs.PLLSTS.bit.MCLKOFF = 1; SysCtrlRegs.PLLCR.bit.DIV = val; EDIS;

// Optional: Wait for PLL to lock. // During this time the CPU will switch to OSCCLK/2 until // the PLL is staPU will

DSP5-F28335中断系统及定时器

中断向量表描述为:

struct PIE_VECT_TABLE { PINT PIE1_RESERVED; … … … … … … … ; PINT LUF; // Latched underflow }

中断向量表的存储器定位

向量名称 Not used INT1 …… INT12 INT13 INT14 Datalog …… USER12 INT1.1 …… PIE 向量地址 0x00 0D00 0x00 0D02 …… 0x00 0D18 0x00 0D1A 0x00 0D1C 0x00 0D1D …… 0x00 0D3E 0x00 0D40 …… PIE 向量描述 Reset Vector Never Fetched Here INT1 re-mapped below …… re-mapped below INT12 re-mapped below XINT1 Interrupt Vector Timer2 – RTOS Vector Data logging vector …… User defined TRAP PIEINT1.1 interrupt PDPINTA ……

全国教育科学“十一五”规划课题研究成果

《 DSP控制器原理与应用教程》

---基于TMS320F28335 & CCS5

主编

李全利 马骏杰 张思艳

高等教育出版社 2016.11

第五章 F28335中断系统及定时器

(一)、F28335的中断系统

(二)、F28335的CPU定时器 (三)、中断和CPU定时器应用示例

3、PIE配置和控制寄存器

寄存器 PIECTRL PIEACK PIEIER1 PIEIFR1 地址(H) 00 0CE0 00 0CE1 00 0CE2 00 0CE3 长度(x16) 1 1 1 1 说明 PIE控制寄存器 PIE中断响应寄存器 PIE,INT1组中断使能寄存器 PIE,INT1组中断标志寄存器

F28335的位域和寄存器结构的学习

F28335的位域和寄存器结构的学习F28335的位域和寄存器结构的学习以前一直在使用C5000系列的DSP,具体型号为VC5509A。

不久前也接触了C2000系列的28335。

在学习这款DSP的过程中,感觉和C55X差别不少。

特别是在编程方面,两者对底层寄存器的操作方式有很大区别。

F28335拥有很丰富的外设资源,这也就说明了它必然有比较复杂的存储单元映射和中断管理体系。

关于存储单元映射,TI提供了C/C++ Header files文件来管理,这个和CSL有些类似,但和CSL并不完全相同。

首先在CSL使用最多的是宏伪指令,而在F28335中使用最多的是位域和寄存器文件结构体。

同CSL 相比,有利也有弊。

在下面会详细列出两者的优缺点。

这是我认为的最有用的一块,它为F28335提供了一个硬件抽象层,使得编程者无需去记忆大量寄存器名称。

而且它提供了一个很好的编程规范,是以后编程很好的参考。

所以花了一番功夫研究位域和寄存器文件结构体。

现将其中重要的部分描述如下:1、宏与位域和寄存器结构优缺点的对比传统的#define宏提供了地址编号或者是指向寄存器地址的指针。

这样做的优点是:1、简单,快,很容易通过键盘敲出。

2、变量名和寄存器名一致,容易记忆。

缺点是:1、具体位不容易获取,必须生成掩码来对某个位操作。

2、不能够在CCS的watch window中方便的显示某些位的值。

3、宏不能够利用CCS的自动完成功能。

4、宏不能对相同外设重复使用。

位域和寄存器结构体的优点如下:1、TI提供,无需自己编写,规范性好。

2、容易读、写、升级,效率高。

3、很好的利用了CCS的自动完成功能。

4、可以在CCS的观察窗口中查看具体位的值。

2、实现位域和寄存器文件结构体的具体步骤(以SCI外设为例)1)、定义一个寄存器文件结构体,SCI外设的寄存器在结构体中按实际的地址由低向高依次列出。

/************************************************************** ****** * SCI header file* Defines a register file structure for the SCI peripheral*************************************************************** *****/ #define Uint16unsigned int#define Uint32unsigned longstruct SCI_REGS {Uint16 SCICCR_REG SCICCR;// Communications control register Uint16 SCICTL1_REG SCICTL1; // Control register 1 Uint16 SCIHBAUD; // Baud rate (high) registerUint16 SCILBAUD; // Baud rate (low) registerUint16 SCICTL2_REG SCICTL2; // Control register 2Uint16SCIRXST_REG SCIRXST; // Receive status registerUint16SCIRXEMU; // Receive emulation buffer register Uint16SCIRXBUF_REG SCIRXBUF; // Receive data buffer Uint16rsvd1; // reservedUint16SCITXBUF;// Transmit data bufferUint16SCIFFTX_REG SCIFFTX; // FIFO transmit registerUint16SCIFFRX_REG SCIFFRX; // FIFO receive registerUint16SCIFFCT_REG SCIFFCT; // FIFO control registerUint16rsvd2; // reservedUint16rsvd3; // reservedUint16SCIPRI_REG SCIPRI; // FIFO Priority control};2)、上面的定义本身并没有建立任何的变量,只是定义了一个结构体,而并没有实例化。

DSP第5章-F28335-概述

3个32位CPU定时器:定时器0、1、2。T0、T1为一般定时器 ,T0连接至PIE,T1连接至中断INT13,T2用作DSP/BIOS的

5.1 F28335的性能

串行端口外设:2个eCAN2.0B; 3个SCI(UART);2个 McBSP;1个SPI; 1个I2C总线接口。

16通道12位模数转换模块:转换时间80ns,2X8通道复用输入 接口;2个采样保持电路;单/连续通道转换;内部或外部参考电 压

5.5 总结

外设帧的寄存器映射如下图所示。

5.5 总结

外设帧的寄存器映射如下图所示。

5.6 F28335与F2812的比 较

5.6 F28335与F2812的比 较

5.3.5 Flash的流水线模式

可提高Flash中线性代码的执行效率 对FOPT寄存器中的ENPIPE置位来使能流水线模式 独立于CPU的流水线模式

5.3.6 Flash 和OTP的寄存器

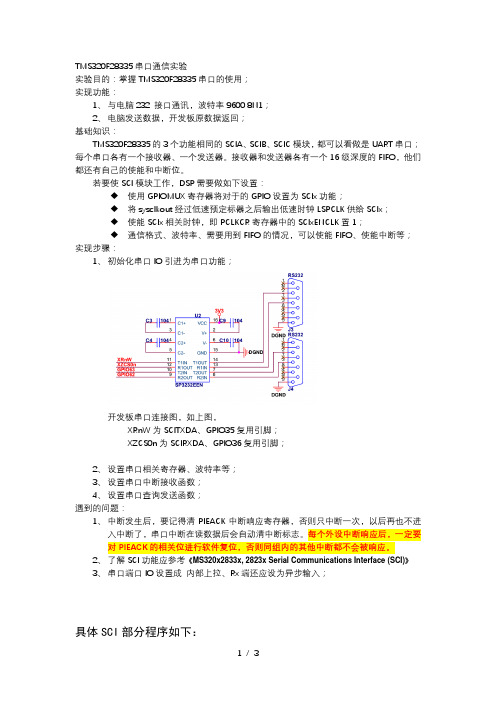

DSP实验五、TMS320F28335-串口通信实验

TMS320F28335串口通信实验实验目的:掌握TMS320F28335串口的使用;实现功能:1、与电脑232 接口通讯,波特率9600 8N1;2、电脑发送数据,开发板原数据返回;基础知识:TMS320F28335的3个功能相同的SCIA、SCIB、SCIC模块,都可以看做是UART串口;每个串口各有一个接收器、一个发送器。

接收器和发送器各有一个16级深度的FIFO,他们都还有自己的使能和中断位。

若要使SCI模块工作,DSP需要做如下设置:◆使用GPIOMUX寄存器将对于的GPIO设置为SCIx功能;◆将sysclkout经过低速预定标器之后输出低速时钟LSPCLK供给SCIx;◆使能SCIx相关时钟,即PCLKCR寄存器中的SCIxENCLK置1;◆通信格式、波特率、需要用到FIFO的情况,可以使能FIFO、使能中断等;实现步骤:1、初始化串口IO引进为串口功能;开发板串口连接图,如上图,XRnW为SCITXDA、GPIO35复用引脚;XZCS0n为SCIRXDA、GPIO36复用引脚;2、设置串口相关寄存器、波特率等;3、设置串口中断接收函数;4、设置串口查询发送函数;遇到的问题:1、中断发生后,要记得清PIEACK中断响应寄存器,否则只中断一次,以后再也不进入中断了,串口中断在读数据后会自动清中断标志。

每个外设中断响应后,一定要对PIEACK的相关位进行软件复位,否则同组内的其他中断都不会被响应。

2、了解SCI功能应参考《MS320x2833x, 2823x Serial Communications Interface (SCI)》3、串口端口IO设置成内部上拉、Rx端还应设为异步输入;具体SCI部分程序如下:/** ======= sci_uart ========*** Created on: 2017年9月19日* Author: liu*/#include"DSP2833x_Device.h"// DSP2833x Header File#include"DSP2833x_Examples.h"// DSP2833x Examples Include File#include"sci_uart.h"__interrupt void sciaRxIsr(void);/** ======== sci_uart_init ========*/void SCIA_uart_init(void){//GPIO35、36复用功能选择EALLOW;GpioCtrlRegs.GPBMUX1.bit.GPIO35 = 1 ; //SCIA_TXDAGpioCtrlRegs.GPBMUX1.bit.GPIO36 = 1 ; //SCIA_RXDAGpioCtrlRegs.GPBPUD.bit.GPIO35 = 0; // Enable pull-up for GPIO29 (SCITXDA)GpioCtrlRegs.GPBPUD.bit.GPIO36 = 0; // Enable pull-up for GPIO28 (SCIRXDA)//定义管脚为异步输入GpioCtrlRegs.GPBDIR.bit.GPIO36 = 0 ;//输入GpioCtrlRegs.GPBQSEL1.bit.GPIO36 = 3;//异步输入EDIS;//基本通信参数设置// Note: Clocks were turned on to the SCIA peripheral// in the InitSysCtrl() functionSciaRegs.SCICCR.all =0x0007; // 1 stop bit, No loopback// No parity,8 char bits,// async mode, idle-line protocolSciaRegs.SCICTL1.all =0x0003; // enable TX, RX, internal SCICLK,// Disable RX ERR, SLEEP, TXWAKESciaRegs.SCICTL2.all =0x0003;SciaRegs.SCICTL2.bit.TXINTENA =0; //查询发送SciaRegs.SCICTL2.bit.RXBKINTENA =1;//中断接收SciaRegs.SCIHBAUD=488>>8;// 9600 135MHz@LSPCLK = 33.75MHz /(9600*8)-1=4394 150MHz@LSPCLK = 37.5MHz /(9600*8)-1=488SciaRegs.SCILBAUD=488;SciaRegs.SCICTL1.all =0x0023; // Relinquish SCI from Reset// Initialize the SCI FIFO 禁止FIFO功能SciaRegs.SCIFFTX.bit.SCIFFENA = 0 ; //禁止SCI FIFO功能EALLOW;// This is needed to write to EALLOW protected registersPieVectTable.SCIRXINTA = &sciaRxIsr;EDIS;// This is needed to disable write to EALLOW protected registersPieCtrlRegs.PIEIER9.bit.INTx1=1;// PIE Group 9, int1IER |= M_INT9;// Enable CPU INTEINT;}void SCIA_UART_Send_Byte( unsigned char Dat){while(SciaRegs.SCICTL2.bit.TXRDY !=1);//等待SCIRXBUF准备好才写入下一个所要发送的数据SciaRegs.SCITXBUF = Dat;}//SCIA串口中断接收处理函数__interrupt void sciaRxIsr(void){if(SciaRegs.SCIRXST.bit.RXRDY == 1){SCIA_UART_Send_Byte( SciaRegs.SCIRXBUF.bit.RXDT );}PieCtrlRegs.PIEACK.all=PIEACK_GROUP9;}。

5、F28335存储器以及地址分配全解

片外扩展存储器

程序空间

F28335对数据空间和程序空间进行了统 一编址,图5.1的映射表就像是各个空间的地

保留

M0向量 RAM(32 X 32)

图一样,有些空间既可以作为数据空间也可 以作为程序空间,有些空间只能作为数据空

0x00 到密码模块保护,有些空 间地址是作为保留的,具体内容就要仔细对 照这个地图来进行查阅了。

一种全为0,另一种全为1,一个新的FLASH或FLASH被擦除后,就变为全1了,这样只要读一下密码区,

就能破解了,还一种情况,就是全为0,这时候器件是被加密了,但是不管密钥寄存器的内容是什么, 器件都处在加密状态,即该器件无法解锁了,这时候芯片就被完全锁住了。因此不要用全0作为密码。 如果在擦除FLASH的期间,芯片复位了,那这个芯片的密码就不确定了,也不能解锁。

TMS320F28335内存保护特点

地址范围 片上存储器 数据空间 0x00 0000 0x00 0040 0x00 0400 0x00 0800 0x00 0D00 M0 SRAM(1k X16) M1 SRAM(1k X16) PF0 PIE 中断 向量表 0x00 0E00 0x00 2000 0x00 5000 0x00 6000 0x00 7000 0x00 8000 0x00 9000 0x00 A000 0x00 B000 0x00 C000 0x00 D000 0x00 E000 0x00 F000 0x01 0000 0x30 0000 0x33 FFF8 0x34 0000 0x38 0000 0x38 0400 0x38 0800 0x3F 8000 0x3F 9000 0x3F A000 0x3F B000 0x3F C000 0x3F E000 0x3F FFFC PF0 保留 PF3 DMA PF1 PF2

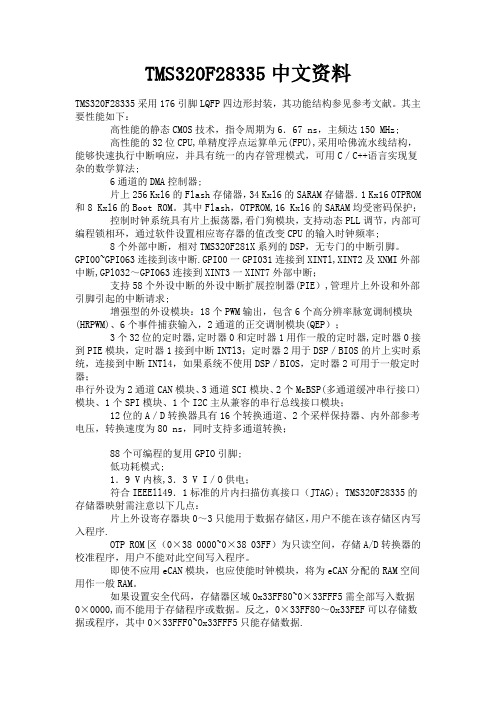

TMS320F28335中文资料

TMS320F28335中文资料TMS320F28335采用176引脚LQFP四边形封装,其功能结构参见参考文献。

其主要性能如下:高性能的静态CMOS技术,指令周期为6.67 ns,主频达150 MHz;高性能的32位CPU,单精度浮点运算单元(FPU),采用哈佛流水线结构,能够快速执行中断响应,并具有统一的内存管理模式,可用C/C++语言实现复杂的数学算法;6通道的DMA控制器;片上256 Kxl6的Flash存储器,34 Kxl6的SARAM存储器.1 Kx16 OTPROM 和8 Kxl6的Boot ROM。

其中Flash,OTPROM,16 Kxl6的SARAM均受密码保护;控制时钟系统具有片上振荡器,看门狗模块,支持动态PLL调节,内部可编程锁相环,通过软件设置相应寄存器的值改变CPU的输入时钟频率;8个外部中断,相对TMS320F281X系列的DSP,无专门的中断引脚。

GPI00~GPI063连接到该中断.GPI00一GPI031连接到XINTl,XINT2及XNMI外部中断,GPl032~GPI063连接到XINT3一XINT7外部中断;支持58个外设中断的外设中断扩展控制器(PIE),管理片上外设和外部引脚引起的中断请求;增强型的外设模块:18个PWM输出,包含6个高分辨率脉宽调制模块(HRPWM)、6个事件捕获输入,2通道的正交调制模块(QEP);3个32位的定时器,定时器0和定时器1用作一般的定时器,定时器0接到PIE模块,定时器1接到中断INTl3;定时器2用于DSP/BIOS的片上实时系统,连接到中断INTl4,如果系统不使用DSP/BIOS,定时器2可用于一般定时器;串行外设为2通道CAN模块、3通道SCI模块、2个McBSP(多通道缓冲串行接口)模块、1个SPI模块、1个I2C主从兼容的串行总线接口模块;12位的A/D转换器具有16个转换通道、2个采样保持器、内外部参考电压,转换速度为80 ns,同时支持多通道转换;88个可编程的复用GPIO引脚;低功耗模式;1.9 V内核,3.3 V I/O供电;符合IEEEll49.1标准的片内扫描仿真接口(JTAG);TMS320F28335的存储器映射需注意以下几点:片上外设寄存器块0~3只能用于数据存储区,用户不能在该存储区内写入程序.OTP ROM区(0×38 0000~0×38 03FF)为只读空间,存储A/D转换器的校准程序,用户不能对此空间写入程序。

28335概述

代表器件:TMS320F28335

C2000系列DSP

Roadmap

High-Precision Control

High-end Derivatives

Control Performance

F2812 179-u*BGA

F2810 176-LQFP 128-LQFP

Application specific versions

TCK TMS TDI

8 7 7 9 7 6

N M 12 14 P1 M 0 12 M 9 N1 2

TDO

EMUO

7 7

8 5

K9 N1 3

L1 1 N7

JTAG扫描输出,测试数据输出.在TCK的下降沿,将被选择寄存器的内容 从TDO移出

仿真•引脚.当TRST为高电平时,该引脚作为中断输入或中断来自仿真系 统. 并通过JTAG扫描定义为输入/输出•当EMU0在逻辑高位而EMU1在逻辑 低 位时,TRST的上升沿会将设备锁存至边界扫描模式。建 议外接上拉电 咀连在这个引脚上.这个电驵值应该根据调试器设计的骐动能力 而定,一 般取2. 2〜4.7 k欧姆之间 仿真引脚1.当TRST为高电平时,该引脚作为中断输入或中断来自仿真系 统, 并通过JTAG扫描定义为I/O•当EMU0为逻辑高而EMU1为逻辑低时, TRST的上升沿会将设备锁存至边界扫描模式,外接上拉 电阻同EMU0

XCLKIN XI X2

105 104 102

J14 J13 Jll

G13 G14 H14

AD转换器A的8通道模拟输入

ADCINA7 35 K4 ADCINA6 ADCINA5 ADC1NA 4 ADCINA3 ADCINA2 36 J5 37 L1 38 L2 39 L3 40 Ml K1 K2 L1 L2 L3 Ml

25_TI DSP入门芯片TMS320F28335

作为一个电子硬件工程师,怎么不能懂DSP,或者我们中有一些同学对DSP的理解还不是很多,今天就让我们给大家介绍一个DSP的入门芯片,来自TI的TMS320F28335。

相信看过了这一系列的内容,大家会对DSP有初步的了解。

TMS320F28335简介:TMS320F28335采用176引脚LQFP四边形封装,其功能结构参见参考文献。

其主要性能如下:高性能的静态CMOS技术,指令周期为6.67 ns,主频达150 MHz;高性能的32位CPU,单精度浮点运算单元(FPU),采用哈佛流水线结构,能够快速执行中断响应,并具有统一的内存管理模式,可用C/C++语言实现复杂的数学算法;6通道的DMA控制器;片上256 Kxl6的Flash存储器,34 Kxl6的SARAM存储器.1 Kx16 OTPROM和8 Kxl6的Boot ROM。

其中Flash,OTPROM,16 Kxl6的SARAM均受密码保护;控制时钟系统具有片上振荡器,看门狗模块,支持动态PLL调节,内部可编程锁相环,通过软件设置相应寄存器的值改变CPU的输入时钟频率;8个外部中断,相对TMS320F281X系列的DSP,无专门的中断引脚。

GPI00~GPI063连接到该中断。

GPI00一GPI031连接到XINTl,XINT2及XNMI外部中断,GPl032~GPI063连接到XINT3一XINT7外部中断;支持58个外设中断的外设中断扩展控制器(PIE),管理片上外设和外部引脚引起的中断请求;增强型的外设模块:18个PWM输出,包含6个高分辨率脉宽调制模块(HRPWM)、6个事件捕获输入,2通道的正交调制模块(QEP);3个32位的定时器,定时器0和定时器1用作一般的定时器,定时器0接到PIE模块,定时器1接到中断INTl3;定时器2用于DSP/BIOS的片上实时系统,连接到中断INTl4,如果系统不使用DSP/BIOS,定时器2可用于一般定时器;串行外设为2通道CAN模块、3通道SCI模块、2个McBSP(多通道缓冲串行接口)模块、1个SPI模块、1个I2C主从兼容的串行总线接口模块;12位的A/D转换器具有16个转换通道、2个采样保持器、内外部参考电压,转换速度为80 ns,同时支持多通道转换;88个可编程的复用GPIO引脚;低功耗模式;1.9 V内核,3.3 V I/O供电;符合IEEEll49.1标准的片内扫描仿真接口(JTAG);TMS320F28335的存储器映射需注意以下几点:片上外设寄存器块0~3只能用于数据存储区,用户不能在该存储区内写入程序。

DSPF28335---中断系统

DSPF28335---中断系统28335的中断系统中断概述通过硬件或软件驱动的信号,使CPU将当前的程序挂起,执行另一个称为中断服务子程序称为中断。

28335内部有16根中断线,其中有两个不可屏蔽中断(RESET、NMI)与16个可屏蔽中断(INT1-14、RTOSINT、DLOGINT),这里主要说明INT1-14。

在28335中,CPU定时器1、2一般预留给实时操作系统使用,中断线单独分配给INT13、INT14。

其余12个可屏蔽中断直接连接在外设中断扩展模块PIE上,供外部中断和处理器内部单元使用。

这就有一个问题,28335内部有很多个外设模块,这些外设都有自己的中断而且有很多个,那么剩余12个中断怎么够用。

为了解决这个问题所有引入PIE模块。

PIE通过12根线与28335核的12个中断线相连。

而PIE的另外一侧有12*8=96根线分别连接到外设,如AD、SPI、EXINT等等。

说明:PIE和CPU的中断标志寄存器由硬件来清零;但外部中断的标志位要通过软件来清零。

一.三级中断1.外设级中断如果有外设产生中断事件,则寄存器中相应的中断标志位被置一,如果相应的中断使能为(IE)被置位,那么外设就像PIE发出一个中断请求。

如果外设使能位没有被置位,那么中断标志(IF)位将保持为1直到软件清除。

2.PIE中断对于复用的中断源,PIE模块有相应的标志寄存器[PIEIFR(x,y) x=1-12,y=1-8]和中断使能寄存器PIEIER(x,y) ;对于每一个PIE中断组来说还有一个中断应答寄存器PIEACKx。

当有中断请求进入PIE模块的时候,如果相应的PIE中断标志位PIEIFR(x.y)和中断使能寄存器PIEIER(x,y)置1;这是PIE控制器就会检查PIEACKx标志位看CPU 是否已经准备好接收这个PIE中断组的中断。

说明:如果PIEACKZx被清零,PIE会把这个中断请求送到CPU 级的INTx。

F28335EPWM各模块简介

F28335EPWM各模块简介F28335 EPWM各模块简介以DSP为基础的数字信号控制器(DSC)执行电动马达相位控制时,其核心组件为事件管理器(Event Manager)。

由于以DSP为基础的控制器应用范围正逐渐扩大到高效能电子产品的触发与控制等各种相关领域,因此这类事件管理器也需要一套全新架构。

以德州仪器(TI)基于DSP的24x和F28x数字信号控制器来看,事件管理器是由DSP 的可程式逻辑电路构成,以便产生脉冲宽度调变(PWM)信号。

这些事件管理器虽然是为了三相系统所设计,却拥有极大弹性,可以高效率应用在多相位或其它特殊需求应用(或许再加上一些软件)。

事件管理器的功能已通过数个世代的处理器考验与测试,只需要进行一些细部调整即可。

针对新的应用需求,TI开发出一套称为加强型事件管理器(eEVM)的架构,将应用于F28x衍生系列的新元件,包括TMS320F2801、TMS320F2806和TMS320F2808控制器(TMS320F2801已实作部份功能)。

加强型事件管理器的PWM产生方式与过去有很大差异。

如图1所示,事件管理器总共有6个加强型PWM(EPWM)模组,每个都能产生两组独立的PWM信号。

这6个模组拥有完全相同的功能和设定方式,因此每个模组都能独立产生中断要求、并在不同的时间点上触发模拟数字转换器。

除此之外,这些模组还能同步操作以便在同样的时基上产生PWM信号。

举例来说,若有两个完全相同的三相电动马达,就可以让EPWM1模组的时基与EPWM2和EPWM3同步,同时也让EPWM4的时基与EPWM5和EPWM6同步,以便使两个马达独立操作。

另一种做法是让EPWM1的时基与另外五个模组同步,这样两个马达就能在同一时间启动操作。

图1:F2808控制器的加强型事件管理器共有6个EPWM模组EPWM模组的架构如图2所示,每个模组都包含数个次模组。

如果要产生PWM信号,至少需要连接一个计时器和相关逻辑电路,以便在可程式设定的不同时间产生事件。

TMS320F28335的DSP实验指导书

语音单元

开关量输入输出单元

液晶显示单元

键盘单元

信号扩展单元

CPLD模块单元

模拟信号源

EL-NC2100电子创新设计平台扩展总线接口

直流电源单元

1、CPU板接口(Techv总线)

Techv总线接口是和TI公司DSK兼容的信号扩展接口,可连接我公司各种Techv总线的CPU板和扩展板如:图像处理、高速AD、DA、USB/以太网等扩展板,也可以连接TI公司的标准DSK扩展信号板,扩展到CPU的IO空间和数据空间。CPU接口用来扩展CPU模块,信号定义如下图:

+5V

+5V电源

23

A03|XA05

地址线

O

24

A02|XA04

地址线

O

25

A01|XA03

地址线

O

26

A00|XA02

地址线

O

27

A21|BE3

地址线

O

28A20ຫໍສະໝຸດ BE2地址线O29

NC|BE1

地址线

O

30

NC|BE0

地址线

O

31

GND

地

32

GND

地

33

D31

数据线

IO

34

D30

数据线

IO

35

D29

46

SYS

CPU信号

IO

47

AD1/USER

扩展板AD输入1

I

48

AD2/USER

扩展板AD输入2

I

49

AD3/USER

扩展板AD输入3

I

50

AD4/USER

DSP28335很好的资料

TMS320F28335 TechV_28335目录1DSP的PWM信号 (1)1.1简介 (1)1.2端口对应关系 (2)1.3初始化程序注释 (2)2DSP的CAN通信 (4)2.1CAN2.0B协议简述 (4)2.2CAN总线电平 (5)2.3CAN总线上的120欧电阻 (6)2.4DSP的CAN时钟模块 (6)2.5邮箱初始化例程注解 (7)2.6消息发送和接收 (8)2.7CAN的适配器存在的一些问题 (9)3DSP的32位浮点运算测试 (10)4DSP定时器中断 (11)4.1DSP28335的定时器 (11)4.2定时器分频 (11)4.3计数器计数 (12)4.4定时器时钟周期 (12)5DSP看门狗复位 (12)5.1看门狗时钟 (12)5.2看门狗系统控制和状态寄存器(SCSR) (13)5.3看门狗计数寄存器(WDCNTR) (13)5.4看门狗重启管理器(WDKEY) (14)5.5看门狗控制寄存器(WDCR) (14)6软件报错与处理 (15)6.1CCS Setup中仿真器的配置 (15)6.2Connect报错——1145——换仿真器解决 (17)6.3CAN口测试A发B收,数据发不出去 (19)6.4编译Pwm测试文件出错 (19)6.5could not open source file "DSP2833x_Device.h (20)7备注与注意事项 (22)8附录C源程序 (22)8.1PWM初始化及脉冲产生函数 (22)8.2邮箱初始化函数 (33)8.3浮点运算测试函数 (36)8.4定时器中断初始化函数 (38)8.5采用定时器的延时函数 (39)8.6看门狗初始化函数 (40)1DSP的PWM信号1.1简介DSP28335共12路16位的ePWM,能进行频率和占空比控制。

ePWM的时钟TBCLK=SYSCLKOUT/(HSPCLKDIV×CLKDIV):PWM信号频率由时基周期寄存器TBPDR和时基计数器的计数模式决定。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

外设总线: 用于外设互联,复用多种总线。

5.3.3 外设

1. ePWM:6个,可单独控制各个引脚,功能更强大 2.eCAP:6个 3.eQEP:2个,测速更加方便 4.ADC:12位,16路,80ns转换时间 5.Watchdog Timer:1个 6.McBSP:2个,用于连接高速外设,如音频处理模块 7.SPI:1个,连接具有SPI借口的外设

得益于F28335浮点运算单元,从而简化软件开发,缩 短开发周期,降低开发成本。

5.1 F28335的性能

高性能静态CMOS技术:主频150MHZ,指令周期6.67ns; 低功

耗设计,1.9V/1.8V内核电压,3.3VI/O引脚电压;Flash编 程电压为3.3V

高性能32位CPU:IEEE-754单精度浮点运算单元(FPU) ;

3个32位CPU定时器:定时器0、1、2。T0、T1为一般定时器 ,T0连接至PIE,T1连接至中断INT13,T2用作DSP/BIOS的

5.1 F28335的性能

串行端口外设:2个eCAN2.0B; 3个SCI(UART);2个 McBSP;1个SPI; 1个I2C总线接口。

16通道12位模数转换模块:转换时间80ns,2X8通道复用输入 接口;2个采样保持电路;单/连续通道转换;内部或外部参考电 压

▪32位定点CPU架构,支持16位和32位指令操作。前者减 少存储,提高代码密度。后者加快指令执行时间。 ▪32位IEEE-754单精度FPU,具有高效C/C++引擎,可使 用高级语言编程。 ▪32X32位MAC64位处理能力。 ▪快速中断响应。 ▪“原子指令”读写简化机制。执行更快,代码更少。

5.3.2 总线

5.3.3 外设

8.SCI:3个,UART功能 9.I2 C:集成电路模块总线 10.CAN:2个 11.GPIO: 12.DMA:6通道

5.3.4 存储器

1.Flash存储器:多扇区,代码安全,低功耗,可配置等待 状态 2.OTP,即一次可编程存储器, 1KX16位OTP统一映射 到程序和数据存储空间,可存放数据或代码。只能被用户 写一次,不能再次擦除。 3.单周期访问RAM(SARAM) 4.片外存储 5.BOOT ROM,出厂预先固化好程序。

第五章 TMS320F28335 DSP概述

5.1 F28335的性能

TMS320F28335 DSP具有150MHz的高速处理能力, 具备32位浮点处理单元,6个DMA通道支持ADC、 McBSP和EMIF,有多达18路的PWM输出,其中有6 路 为TI特有的更高精度的PWM输出(HRPWM),12位16通 道ADC。与前代DSP相比,平均性能提升50%,并与定点 C28x控制器软件兼容。

5.3.6 Flash 和OTP的寄存器

5.3.6 Flash 和OTP的寄存器

5.4 代码安全模块(CSM)

5.3.5 Flash的流水线模式

可提高Flash中线性代码的执行效率 对FOPT寄存器中的ENPIPE置位来使能流水线模式 独立于CPU的流水线模式

5.3.6 TP的寄存器

5.3.6 Flash 和OTP的寄存器

5.3.6 Flash 和OTP的寄存器

JTAG边界扫描支持IEEE 1149.1-1990标准测试端口

先进的仿真调试功能:分析和断点功能;硬件实时调试

低功耗模式和省电模式:支持IDLE,STANDBY,HALT模式; 禁止外设独立时钟

179引脚BGA封装或176引脚LQFP封装

5.2 F28335的封装与引脚描述

5.2.1: 176脚

16*16和 32*32介质访问控制(MAC)运算;16*16双 MAC;哈佛总线架构;快速中断响应和处理能力;统一存储器 编程模型和高效代码(使用C/C++ 和汇编语言)。

6通道DMA处理器(用于ADC,McBSP,ePWM,XINTF ,SARAM)

5.1 F28335的性能

16位或32位外部接口(XINTF):可处理超过2M*16位 地址范围

5.1 F28335的性能

GPIO 0-GPIO 63引脚可以连接到8个外部内核中断其中的一 个

可支持全部58个外设中断的外设中断扩展(PIE)块

128位安全密钥/锁:保护flash/OTP/RAM模块,防止逆向 工程

增强型控制外设:多达18个PWM输出;高达6个支持150ps 微边界定位(MEP)分辨率的高分辨率脉宽调制器(HRPWM )输出;高达6个事件捕捉输入;多达2个正交编码器接口;高 达8个32位定时器(6个eCAP和2个eQEP);

PZ LQFP 封装

5.2.2 引脚信号说明

5.2.2 引脚信号说明

5.2.2 引脚信号说明

5.2.2 引脚信号说明

5.2.2 引脚信号说明

5.2.2 引脚信号说明

5.2.2 引脚信号说明

5.3 F28335 功能 概述

1.CPU 2.总线 3.存储单元 4.外设

5.3.1 CPU

5.3.4 存储器

存储空间映射如右图

5.3.4 Flash和OTP存储器的低功耗模式

Reset or Sleep State 芯片复位后的状态

Standby State 耗能比Sleep状态多,但转为下个状态时间短

Active or Read State CPU在flash和OTP读取访问由FBANKWAIT寄存器和 FOTPWAIT寄存器控制

片内存储器:最多达256K × 16位的Flash存储器;34K

× 16位的单周期访问RAM(SARAM);1K × 16位一次性

可编程(OTP )ROM

引导(BOOT)ROM(8K X 16):支持软件引导模式( 通过SCI、SPI、CAN、McBSP、XINTF和并行I/O),支持 标准数学表

时钟和系统控制:支持动态锁相环(PLL)比率系数;片 载振荡器;安全装置定时器模块