CYV15G0104TRB-BGXC中文资料

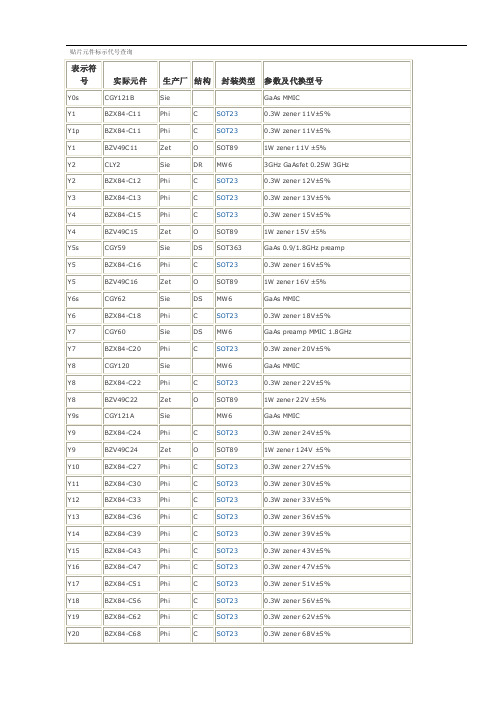

贴片元件标示代号查询

F

n-ch jfe t ultra low i/p Ig

Na t

F

n-ch jfe t ultra low i/p Ig

Na t

F

n-ch jfe t ultra low i/p Ig

Na t

F

n-ch jfe t sw/choppe r

Na t

F

n-ch jfe t sw/choppe r

Na t

Y5

BZV49C 16

Ze t

O

SOT89

1W zene r 16V ±5%

Y 6s

C GY62

Sie

DS MW 6

GaAs MMIC

Y6

BZX84 -C1 8

Phi

C

SOT23

0.3W zene r 18V±5%

Y7

C GY60

Sie

DS MW 6

GaAs preamp MMIC 1.8GHz

Y7

Y 83

BZX84 - A56

Phi

C

SOT23

0.3W zene r 56V ±1%

Y 84

BZX84 - A62

Phi

C

SOT23

0.3W zene r 62V ±1%

Y 85

BZX84 - A68

Phi

C

SOT23

0.3W zene r 68V ±1%

Y 86

BZX84 - A75

Phi

C

SOT23

I

SOD110

0.4W zene r 4.7V E12 ±5%

YW

BZX284-C 5V1 Phi

I

SOD110

西贝通达TDSV系列伺服驱动器使用手册

TDSV系列数字式交流伺服驱动器使用说明书北京西贝通达科技有限公司V1.2 Build 1522010年09月目录1概要 (1)2安全、正确使用规定 (2)2.1一般说明 (2)2.2防止触电伤害注意事项 (2)2.3防止损伤及设备损坏注意事项 (2)2.4防止火灾注意事项 (3)2.5其他注意事项 (3)2.5.1环境要求 (3)2.5.2安装及连接 (3)2.5.3运行 (4)3型号名称及技术规格 (6)3.1驱动器型号名称 (6)3.2技术规格 (6)4安装 (8)5信号与连接 (9)5.1信号定义 (9)5.1.1主回路强电端子 (9)5.1.2编码器反馈插头--CN1 (11)5.1.3控制信号插头—CN2 (12)5.1.4通讯插头—CN3 (17)5.2典型外部连接 (18)5.2.1主电路强电连接 (18)5.2.2模拟速度控制信号连接 (19)5.2.3模拟力矩控制信号连接 (20)5.2.4通讯接口信号连接 (20)6参数说明 (21)6.1参数设定及调整方法 (21)6.2参数的初始调整 (21)6.2.1电机参数的调整 (21)6.2.2运行方式参数的调整 (21)6.2.3控制回路调节参数的调整 (22)6.2.4专用功能参数的调整 (22)6.2.5通讯控制参数的调整 (22)6.3参数说明 (23)6.3.1电机参数 (23)6.3.2运行方式设定参数 (24)6.3.3运行指令参数 (31)6.3.4控制调节器参数 (35)6.3.6监视参数 (44)6.3.7专用功能设定参数 (49)6.3.7.1定位功能设定参数 (49)6.3.7.2摆动及切换变速比功能设定参数 (53)6.3.7.3模拟量刚性攻丝功能设定参数 (55)6.3.7.4模拟量铰孔功能设定参数 (56)6.3.7.5脉冲位置控制功能(C轴功能)设定参数 (57)6.3.8通讯参数 (59)6.4参数总表 (60)7操作面板 (68)7.1概述 (68)7.1.1指示灯状态及功能 (68)7.1.2按键功能 (68)7.1.3上电初始状态 (69)7.2数码管显示模式 (69)7.2.1数码管主菜单显示模式 (69)7.2.2参数管理模式子菜单显示 (69)7.2.3监控模式子菜单显示 (69)7.2.4辅助功能模式子菜单显示 (70)7.3参数管理模式 (71)7.3.1读取参数值 (71)7.3.2修改参数值 (71)7.3.3快速切换参数号 (72)7.4监控模式 (72)7.4.1切换监控参数 (72)7.4.2显示监控参数值 (73)7.5辅助功能模式 (73)7.5.1试运行电机 (73)7.5.2报警追踪 (74)7.5.3密码权限 (75)8TMS-WIN监控软件 (77)8.1概述 (77)8.2状态监控界面 (77)8.2.1驱动器工作状态 (78)8.2.2驱动器实时数据 (78)8.2.3电机控制 (79)8.2.4工具栏及状态栏 (80)8.2.5考机功能 (80)8.3参数界面 (81)8.3.1参数浏览 (81)8.3.2参数修改 (81)8.3.4I/O端口调试 (83)8.4图形界面 (84)8.4.1数据采样 (84)8.4.2图形设置 (86)8.4.3数据测量 (87)8.5用户权限 (87)8.6软件菜单 (88)9常见报警及处理方法 (91)10维护与检修 (93)10.1维护及检修内容 (93)10.2易损件更换 (94)10.3存储 (94)TDSV系列交流伺服驱动器使用说明书1概要感谢您购买TDSV系列交流伺服驱动器产品。

ASEMI肖特基二极管型号大全,找找MBR4045PT属于哪一类

编辑:GGASEMI肖特基二极管的型号众多,接下来所列型号主要以电流电压大小,分为大类,再以封装区分作为辅助分类。

ASEMI肖特基二极管型号大全,找找MBR4045PT属于哪一类1A~5A 20V~150V 肖特基二极管两者型号都在用SS封装:SS110 、SS14 。

10A 45V~200V 肖特基二极管采用TO-220AC封装的有:MBR10200AC、MBR10150AC、MBR10100AC、MBR1060AC、MBR1045AC、MBR1040AC采用TO-220封装的有:MBR1040FCT、MBR10200FCT、MBR10100FCT、MBR10150FCT、 MBR1040CT、MBR10200CT、MBR1040FCT、MBT1045FCT、 MBR1045CT、MBR1040CT、 MBR1045CT、MBR1060CT、MBR1060FCT、MBR10100CT、MBT10100FCT、MBR10150CT该封装有FCT和CT结尾的型号命名,区别于前者是塑封封装、后者是铁头封装。

采用TO-251封装的有:BD1045CT、BD1060CT、BD10100CT、BD10150CT、BD10200CT、BD1040CT采用TO-252封装的有:BD1040CS、BD1045CS、BD1060CS、BD10100CS、BD10150CS、 BD10200CS 采用TO-263封装的有:MBR10200DC、MBR1040DC、MBR1045DC、MBR1060DC、MBR10100DC、MBR10150DC20A 45V~200V肖特基二极管采用TO-220AC封装的有:MBR20200AC、MBR20150AC、MBR20100AC、MBR2060AC、 MR2045AC采用TO-251封装的有:BD2060CT、BD2045CT、BD20100CT、BD20150CT、BD20200CT、采用TO-252封装的有:BD20100CS、BD20150CS、BD20200CS、BD2045CS、BD2060CS采用TO-263封装的有:MBR2045DC、MBR2060DC、MBR20100DC、MBR20150DC、MBR20200DC采用TO-220封装的有:MBR2045CT、MBR2045FCT、MBR20200FCT、MBR2060CT、 MBR20100FCT、MBR2060FCT、MBR20100CT、MBR20100FCT、 MBR20150CT、MBR20150FCT、MBR20200CT、MBR20200FCT采用TO-247/3封装的有:MBR20200PT30A 45V~200V 肖特基二极管采用TO-247/3P封装的有:MBR3045PT、MBR3060PT、MBR30100PT、MBR30150PT、MBR30200PT采用TO-263封装的有:MBR30200DC、MBR3060DC、MBR30100DC、MBR30150DC、MBR3045DC采用TO-220封装的有:MBR3045CT、MBR3045FCT、MBR3060CT、MBR3060FCT、MBR30100CT、MBT30100FCT、MBR30150CT、MBR30150FCT、 MBR30200CT、MBR30200FCT 40A 45V~200V 肖特基二极管采用TO-263封装的有:MBR4045DC、MBR40200DC、MBR4060DC、MBR40100DC、MBR40150DC采用TO-247/3P封装的有:MBR40200PT、MBR4045PT、MBR4060PT、MBR40100PT、 MBR40150PT、采用TO-220封装的有:MBR4045FCT、MBR4045CT、MBR4060FCT、MB40100FCT、 MBR4060CT、MBR40100CT60A 45V~220V 肖特基二极管采用TO-247/3P封装的有:MBR6045PT、MBR6060PT、MBR60100PT、MBR60150PT、 MBR60200PT 10A~60A 20V~100V 肖特基二极管采用ITO-220AB封装的有:SBT10150UCT、SBT10100UCT、SBT1060UCT、SBT1045UCT、SBT10150VCT、SBT10100VCT、SBT1060VCT、SBT1045VCT、SBT30150UCT、SBT2045VCT、SBT2060VCT、SBT20100VCT、SBT20150VCT、SBT2045UCT、 SBT2060UCT、SBT20100UCT、 SBT20150UCT、SBT3045VCT、SBT3060VCT、SBT30100VCT、 SBT30150VCT、SBT3045UCT、SBT3060UCT、SBT30100UCT、SBT1045UFCT、SBT30100UFCT、SBT1060UFCT、SBT10150VFCT、SBT10100VFCT、SBT1060VFCT、SBT1045VFCT、SBT10100UFCT、SBT2045VFCT、SBT10150UFCT、 SBT2060VFCT、SBT20100VFCT、SBT20150VFCT、SBT2045UFCT、SBT2060UFCT、SBT20100UFCT、SBT20150UFCT、SBT3045VFCT、SBT3060VFCT、SBT30100VFCT、 SBT30150VFCT、SBT3045UFCT、SBT3060UFCT、SBT30150UFCT、SBT1045UFCT、 SB10100LCT、SB10150LCT、SB1045LFCT、SB1045LFCT、SB30100LFCT、 SB1060LFCT、SB30150LFCT、SB10100LFCT、SB2045LFCT、SB10150LFCT、SB2060LFCT、SB20100LFCT、SB3060LCT采用TO-220AB封装的有:SB1060LCT、SB30150LCT、SB30150LCT、SB10100LCT、SB2060LCT、SB10150LCT、SB20150LCT、SB3060LCT、SB30100LCT、SB1045LCT采用TO-277封装的有:10V45这款肖特基二极管型号是超低压降、贴片小封装的。

TXS0104E 4位双向多电压电平转换器说明书

适用于漏极开路和推挽应用的 TXS0104E 4 位双向多电压电平转换器1 特性•无需方向控制信号•最大数据速率–24Mbps(推挽)–2Mbps(开漏)•采用德州仪器 (TI) NanoFree™封装• A 端口支持 1.65V 至 3.6V 的电压,B 端口支持2.3V 至 5.5V 的电压 (V CCA≤ V CCB)•无需电源排序– V CCA或 V CCB均可优先斜升•闩锁性能超过 100mA,符合 JESD 78 II 类规范的要求•ESD 保护性能超过 JESD 22 规范要求–A 端口•2000V 人体放电模型 (A114-B)•200V 机器模型 (A115-A)•1000V 充电器件模型 (C101)–B 端口•15kV 人体放电模型 (A114-B)•200V 机器模型 (A115-A)•1000V 充电器件模型 (C101)•IEC 61000-4-2 ESD(B 端口)–±8kV 接触放电–±10kV 气隙放电2 应用•手持终端•智能手机•平板电脑•台式计算机3 说明这个 4 位同相转换器使用两个独立的可配置电源轨。

A 端口设计用于跟踪 V CCA。

V CCA支持从 1.65V 到 3.6V 范围内的任意电源电压。

V CCA必须低于或等于V CCB。

B 端口旨在用于跟踪 V CCB。

V CCB支持从 2.3V 到5.5V 范围内的任意电源电压。

这使得该器件可在 1.8V、2.5V、3.3V 和 5V 电压节点之间任意进行低压双向转换。

当输出使能端 (OE) 输入为低电平时,所有输出都被置于高阻抗状态。

TXS0104E 被设计成由 V CCA为 OE 输入电路供电。

为确保在加电或断电期间处于高阻抗状态,应将 OE 通过下拉电阻器接地;该电阻器的最小值取决于驱动器的拉电流能力。

(1)(1)如需了解所有可用封装,请参阅数据表末尾的可订购产品附录。

OutputVoltage(V)Input Voltage (V)C001N 沟道晶体管的传输特征内容1 特性...................................................................................12 应用...................................................................................13 说明...................................................................................14 修订历史记录.....................................................................25 引脚配置和功能.................................................................4引脚功能:ZXU/ NMN.......................................................4引脚功能:DSBGA...........................................................5引脚功能:D 、PW 或 RGY...............................................66 规格...................................................................................76.1 绝对最大额定值...........................................................76.2 ESD 等级....................................................................76.3 建议运行条件..............................................................86.4 热性能信息:ZXU 、YZT 和 NMN...............................86.5 热性能信息:D 、PW 和 RGY.....................................96.6 电气特性......................................................................96.7 时序要求:V CCA = 1.8V ± 0.15V...............................106.8 时序要求:V CCA = 2.5V ± 0.2V.................................106.9 时序要求:V CCA = 3.3V ± 0.3V.................................106.10 开关特性:V CCA = 1.8V ± 0.15V.............................116.11 开关特性:V CCA = 2.5V ± 0.2V...............................136.12 开关特性:V CCA = 3.3V ± 0.3V...............................156.13 典型特性..................................................................167 参数测量信息...................................................................177.1 负载电路.. (17)7.2 电压波形....................................................................188 详细说明..........................................................................198.1 概述...........................................................................198.2 功能方框图................................................................198.3 特性说明....................................................................208.4 器件功能模式............................................................209 应用和实现.......................................................................219.1 应用信息....................................................................219.2 典型应用....................................................................2110 电源相关建议.................................................................2311 布局................................................................................2411.1 布局布线指南...........................................................2411.2 布局示例..................................................................2412 器件和文档支持.............................................................2512.1 文档支持..................................................................2512.2 接收文档更新通知...................................................2512.3 社区资源..................................................................2512.4 商标.........................................................................2513 接收文档更新通知..........................................................2514 支持资源........................................................................2515 静电放电警告.................................................................2516 术语表............................................................................2517 机械、封装和可订购信息.. (25)4 修订历史记录注:以前版本的页码可能与当前版本的页码不同Changes from Revision H (May 2018) to Revision I (October 2020)Page•更新了整个文档的表、图和交叉参考的编号格式................................................................................................1•添加了 NMN 封装 12 引脚 nFBGA......................................................................................................................4Changes from Revision G (September 2017) to Revision H (May 2018)Page•更改了开关特性:V CCA = 3.3V ± 0.3V 表中最大数据速率的最大值..................................................................15Changes from Revision F (December 2014) to Revision G (September 2017)Page•更改了“器件信息”表........................................................................................................................................1•通篇删除了 GXU 引用.........................................................................................................................................4•在绝对最大额定值 中添加了结温........................................................................................................................7•重新编排了电气特性 ..........................................................................................................................................9•将电压转换基础知识 添加到“相关文档”........................................................................................................25•添加了接收文档更新通知 和社区资源 (25)Changes from Revision E (August 2013) to Revision F (December 2014)Page•添加了引脚配置和功能 部分、处理等级 表、特性说明 部分、器件功能模式、应用和实施 部分、电源相关建议 部分、布局 部分、器件和文档支持 部分以及机械、封装和可订购信息 部分......................................................1•从“绝对最大额定值”表中删除了封装热阻信息,并将其添加到“热性能信息”表中将 T stg 行移到了新的“处理额定值”表中...................................................................................................................................................7•将第一个开关特性表中最后 2 行的“最小值最大值”中的最大值 24 和最大值 2 更改到最小值列. (11)TXS0104EZHCSI61I – JUNE 2006 – REVISED OCTOBER 2020Changes from Revision D (May 2008) to Revision E (August 2013)Page•删除了订购表 (1)TXS0104EZHCSI61I – JUNE 2006 – REVISED OCTOBER 20205 引脚配置和功能图 5-1. ZXU 封装顶视图图 5-2. NMN 顶视图引脚功能:ZXU/ NMNTXS0104EZHCSI61I – JUNE 2006 – REVISED OCTOBER 2020图 5-3. YZT 封装 12 引脚 DSBGA 顶视图引脚功能:DSBGATXS0104EZHCSI61I – JUNE 2006 – REVISED OCTOBER 20201147823456131211109B1B2B3B4NCA1A2A3A4NCO EV G N DC C BV C C ANC - 无内部连接图 5-4. RGY 封装 14 引脚 VQFN 顶视图NC - 无内部连接图 5-5. D 和 PW 封装 14 引脚 SOIC 和 TSSOP 顶视图引脚功能:D 、PW 或 RGYTXS0104EZHCSI61I – JUNE 2006 – REVISED OCTOBER 20206 规格6.1 绝对最大额定值(1)(1)应力超出绝对最大额定值 下所列的值可能会对器件造成损坏。

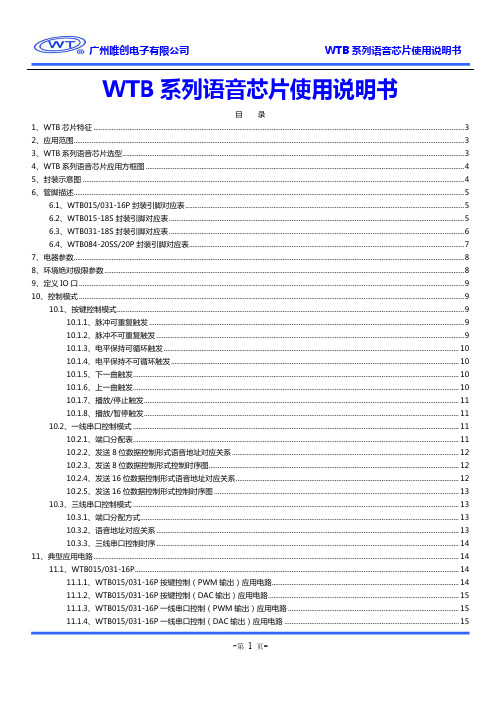

广州唯创电子 WTB 系列语音芯片说明书

WTB系列语音芯片使用说明书目录1、WTB芯片特征 (3)2、应用范围 (3)3、WTB系列语音芯片选型 (3)4、WTB系列语音芯片应用方框图 (4)5、封装示意图 (4)6、管脚描述 (5)6.1、WTB015/031-16P封装引脚对应表 (5)6.2、WTB015-18S封装引脚对应表 (5)6.3、WTB031-18S封装引脚对应表 (6)6.4、WTB084-20SS/20P封装引脚对应表 (7)7、电器参数 (8)8、环境绝对极限参数 (8)9、定义IO口 (9)10、控制模式 (9)10.1、按键控制模式 (9)10.1.1、脉冲可重复触发 (9)10.1.2、脉冲不可重复触发 (9)10.1.3、电平保持可循环触发 (10)10.1.4、电平保持不可循环触发 (10)10.1.5、下一曲触发 (10)10.1.6、上一曲触发 (10)10.1.7、播放/停止触发 (11)10.1.8、播放/暂停触发 (11)10.2、一线串口控制模式 (11)10.2.1、端口分配表 (11)10.2.2、发送8位数据控制形式语音地址对应关系 (12)10.2.3、发送8位数据控制形式控制时序图 (12)10.2.4、发送16位数据控制形式语音地址对应关系 (12)10.2.5、发送16位数据控制形式控制时序图 (13)10.3、三线串口控制模式 (13)10.3.1、端口分配方式 (13)10.3.2、语音地址对应关系 (13)10.3.3、三线串口控制时序 (14)11、典型应用电路 (14)11.1、WTB015/031-16P (14)11.1.1、WTB015/031-16P按键控制(PWM输出)应用电路 (14)11.1.2、WTB015/031-16P按键控制(DAC输出)应用电路 (15)11.1.3、WTB015/031-16P一线串口控制(PWM输出)应用电路 (15)11.1.4、WTB015/031-16P一线串口控制(DAC输出)应用电路 (15)11.1.5、WTB015/031-16P三线串口控制(PWM输出)应用电路 (16)11.1.6、WTB015/031-16P三线串口控制(DAC输出)应用电路 (16)11.2、WTB015/031-18S (16)11.2.1、WTB015/031-18S按键控制(PWM输出)应用电路 (16)11.2.2、WTB031-18S按键控制(DAC输出)应用电路 (17)11.2.3、WTB015/031-18S一线串口控制(PWM输出)应用电路 (17)11.2.4、WTB015/031-18S一线串口控制(DAC输出)应用电路 (17)11.2.5、WTB015/031-18S三线串口(PWM输出)应用电路 (18)11.2.6、WTB015/031-18S三线串口(DAC输出)应用电路 (18)11.3、WTB084-20SS/20P (19)11.3.1、WTB084-20SS/20P按键控制(PWM输出)应用电路 (19)11.3.2、WTB084-20SS/20P按键控制(DAC输出)应用电路 (19)11.3.3、WTB084-20SS/20P一线串口(PWM输出)应用电路 (19)11.3.4、WTB084-20SS/20P一线串口(DAC输出)应用电路 (20)11.3.5、WTB084-20SS/20P三线串口(PWM输出)应用电路 (20)11.3.6、WTB084-20SS/20P三线串口(DAC输出)应用电路 (20)12、应用范例电路 (21)12.1、电动车应用电路 (21)12.2、定时药盒应用电路 (22)13、控制程序范例 (22)13.1、一线串口(发送8位数据控制形式)控制程序范例 (22)13.2、一线串口(发送16位数据控制形式)控制程序范例 (24)13.3、三线串口控制程序范例 (27)14、封装尺寸 (29)14.1、WTB015/031-16P封装尺寸 (29)14.2、WTB015/031-18S封装尺寸 (30)15、货源信息 (31)16、说明书版本记录 (31)1、WTB芯片特征WTB语音芯片是一款低成本OTP语音芯片;工业级性能,确保产品在多种场合下正常工作;内置音频合成器的4位微型语音处理器及4位数字逻辑运算器;WTB语音芯片完备的内部资源包括EPROM、RAM和I/O端口等;可定义多路输入端和输出端;随意定义控制输入端触发功能;自动休眠功能,有效降低功耗;支持WAV音频和两通道MIDI播放;可工作于4MHz和8MHz两种震荡模式,不同模式下的音频最高采样率分别为14KHz和28KHz;WTB系列语音芯片包括WTB015、WTB031、WTB084、WTB170,其存储时间分别为15秒、31秒、84秒、170秒,目前库存有WTB015、WTB031和WTB084三种;可加载128段语音进行控制播放;单芯片方案,可掩膜投产,降低批量生产成本;支持9bit D/A和8bit PWM输出;工作电压:DC2.2V~5.5V。

启珑微电子产品手册说明书

产品手册PRODUCT MANUAL(北京︶有限公司并一直致力于为工业智能控制、医疗设备、轨道交通、智能交通以及智能家居等领域提供更优质的产品与服务。

公司具有深厚的文化底蕴,由多位有欧美留学、工作经历的归国人员创办,坚实的理论功底和丰富的芯片设计经验奠定了启珑微电子的高起点和高水准,并迅速成长为业内具有自主知识产权的中国IC设计品牌之一。

产品手册01序号产品型号封装形式产品概述兼容型号1CLM811HST-AXC TQFP-48SL811HST-AXC 2CLCP82C55AZ DIP-40CP82C55AZ 3CLIP82C55AZ DIP-40IP82C55AZ 4CLCS82C55AZ PLCC-44CS82C55AZ 5CLIS82C55AZ PLCC-44IS82C55AZ 6CLCQ82C55AZ MQFP-44CQ82C55AZ 7CLIQ82C55AZ MQFP-44IQ82C55AZ 8CLID82C55AZ DIP-40ID82C55A 9CLMD82C55A/B DIP-40MD82C55A/B 10CLMD82C55QA DIP-40MD82C55QA 11CLM65HVD230D SOIC-8SN65HVD230D 12CLM65HVD230QD SOIC-8SN65HVD230QD 13CLM65HVD231D SOIC-8SN65HVD231D 14CLM65HVD231QD SOIC-8SN65HVD231QD 15CLM65HVD232D SOIC-8SN65HVD232D 16CLM65HVD232QD SOIC-8SN65HVD232QD 17CLM65HVD233D SOIC-8具有待机模式和环回功能的 3.3V SN65HVD233D 18CLM65HVD233HD SOIC-8具有待机模式和环回功能的 3.3V SN65HVD233HD 19CLM65HVD233QDRQ1SOIC-8具有待机模式和环回功能的 3.3V SN65HVD233QDRQ120CLM65HVD233MDREP SOIC-8具有待机模式和环回功能的 3.3V SN65HVD233MDREP产品手册02序号产品型号封装形式产品概述兼容型号21CLM65HVD234D SOIC-8SN65HVD234D 22CLM65HVD234QDRQ1SOIC-8SN65HVD234QDRQ123CLM65HVD235D SOIC-8SN65HVD235D 24CLM65HVD235QDRQ1SOIC-8SN65HVD235QDRQ125CLM75176BPS SOIC-8SN75176BPSR 26CLM75176BDR SOIC-8SN75176BDR 27CLM75176ADR SOIC-8SN75176ADR 28CLM75176AP DIP-8SN75176AP 29CLM76176BP DIP-8SN75176BP 30CLM75179BPS SOIC-8SN75179BPS 31CLM75179BDR SOIC-8SN75179BDR 32CLM75179AP DIP-8SN75179AP 33CLM75179BP DIP-8SN75179BP 34CLM65HVD08D SOIC-8SN65HVD08D 35CLM65HVD08P DIP-8SN65HVD08P 36CLM65HVD75D SOIC-8具有IEC ESD保护功能和20Mbps的SN65HVD75D 37CLM65HVD75DGK VSSOIC-8具有IEC ESD保护功能和20Mbps的SN65HVD75DGK 38CLM65HVD75DRBT VDFN-8具有IEC ESD保护功能和20Mbps的SN65HVD75DRBT 39CLM3085CPA+DIP-8(10Mbps)、限摆率RS-485/MAX3085CPA+40CLM3085EPA+DIP-8(10Mbps)、限摆率RS-485/MAX3085EPA+产品手册03序号产品型号封装形式产品概述兼容型号41CLM3085EEPA DIP-8(10Mbps)、限摆率RS-485/MAX3085EEPA 42CLM3085CSA+T SOIC-8(10Mbps)、限摆率RS-485/MAX3085CSA+43CLM3085ECSA+T MSOIC-8(10Mbps)、限摆率RS-485/MAX3085ECSA+T 44CLM3085ESA+T SOIC-8(10Mbps)、限摆率RS-485/MAX3085ESA+45CLM3085EESA+T SOIC-8(10Mbps)、限摆率RS-485/MAX3085EESA+46CLM3088CSA+T SOIC-8MAX3088CSA+T 47CLM3088ECSA+T SOIC-8MAX3088ECSA+T 48CLM3088ESA+T SOIC-8MAX3088ESA+T 49CLM3088EESA+T SOIC-8MAX3088EESA+T 50CLM3088CPA+DIP-8MAX3088CPA+51CLM3088ECPA+DIP-8MAX3088ECPA+52CLM3088EPA+DIP-8MAX3088EPA+53CLM3088EEPA+DIP-8MAX3088EEPA+54CLM485CPA+DIP-8低功耗、限摆率、RS-485/RS-422MAX485CPA+55CLM485ECPA+DIP-8低功耗、限摆率、RS-485/RS-422MAX485ECPA+56CLM485EPA+DIP-8低功耗、限摆率、RS-485/RS-422MAX485EPA+57CLM485EEPA+DIP-8低功耗、限摆率、RS-485/RS-422MAX485EEPA+58CLM485CSA+SOIC-8低功耗、限摆率、RS-485/RS-422MAX485CSA+59CLM485ESA+SOIC-8低功耗、限摆率、RS-485/RS-422MAX485ESA+60CLM485EESA+SOIC-8低功耗、限摆率、RS-485/RS-422MAX485EESA+产品手册04序号产品型号封装形式产品概述兼容型号61CLM3490CSA+SOIC-8 3.3V供电、10Mbps、限摆率、真MAX3490CSA+62CLM3490ECSA+SOIC-8 3.3V供电、10Mbps、限摆率、真MAX3490ESA+63CLM3490ESA+SOIC-8 3.3V供电、10Mbps、限摆率、真MAX3490ESA+64CLM3490EESA+SOIC-8 3.3V供电、10Mbps、限摆率、真MAX3490EESA+65CLM3491CSD SOP-14 3.3V供电、10Mbps、限摆率、真MAX3491CSD+66CLM3491ECSD+SOP-14 3.3V供电、10Mbps、限摆率、真MAX3491ECSD+67CLM3491ESD+SOP-14 3.3V供电、10Mbps、限摆率、真MAX3491ESD+68CLM3491EESD+SOP-14 3.3V供电、10Mbps、限摆率、真MAX3491EESD+69CLM490CSA+SOIC-8低功耗、限摆率、RS-485/RS-422MAX490CSA+70CLM490ECSA+SOIC-8低功耗、限摆率、RS-485/RS-422MAX490ECSA+71CLM490ESA+SOIC-8低功耗、限摆率、RS-485/RS-422MAX490ESA+72CLM490EESA+SOIC-8低功耗、限摆率、RS-485/RS-422MAX490EESA+73CLM490CPA+DIP-8低功耗、限摆率、RS-485/RS-422MAX490CPA+74CLM490ECPA+DIP-8低功耗、限摆率、RS-485/RS-422MAX490ECPA+75CLM490EPA+DIP-8低功耗、限摆率、RS-485/RS-422MAX490EPA+76CLM490EEPA+DIP-8低功耗、限摆率、RS-485/RS-422MAX490EEPA+77CLM488CSA+SOIC-8低功耗、限摆率、RS-485/RS-422MAX488CSA+78CLM488ECSA+SOIC-8低功耗、限摆率、RS-485/RS-422MAX488ECSA+79CLM488ESA+SOIC-8低功耗、限摆率、RS-485/RS-422MAX488ESA+80CLM488EESA+SOIC-8低功耗、限摆率、RS-485/RS-422MAX488EESA+产品手册序号产品型号封装形式产品概述兼容型号81CLM488CPA+DIP-8MAX488CPA+82CLM488ECPA+DIP-8MAX488ECPA+83CLM488EPA+DIP-8MAX488EPA+84CLM488EEPA+DIP-8MAX488EEPA+85CLM232CSE SOIC-16MAX232CSE+T86CLM232ECSE SOIC-16MAX232ECSE+87CLM232ESE SOIC-16MAX232ESE+T88CLM232EESE SOIC-16MAX232EESE+T89CLM232CPE DIP-16MAX232CPE+90CLM232ECPE DIP-16MAX232ECPE+91CLM232EPE DIP-16MAX232EPE+92CLM232EEPE DIP-16MAX232EEPE+93CLM232CWE SOIC-16MAX232CWE+T94CLM232ECWE SOIC-16MAX232ECWE+T95CLM232EWE SOIC-16MAX232EWE+T96CLM232EEWE SOIC-16MAX232EEWE+T97CLM232ACWE SOIC-16MAX232ACWE+T98CLM232AEWE SOIC-16MAX232AEWE+99CLM3232CSE SOIC-16MAX3232CSE+T 100CLM3232ECSE SOIC-16MAX3232ECSE+T05产品手册06序号产品型号封装形式产品概述兼容型号101CLM3232ESE SOIC-16MAX3232ESE+T 102CLM3232EESE SOIC-16MAX3232EESE+T 103CLM1302S SOIC-8DS1302S+T&R 104CLM1302SN+SOIC-8DS1302SN+T&R 105CLM1302Z+T SOIC-8DS1302Z+T&R 106CLM1302ZN+SOIC-8DS1302ZN+T&R 107CLM1302+DIP-8DS1302+108CLM1302N+DIP-8DS1302N+109CLM307Z+SOIC-8DS1307Z+T&R 110CLM1307ZN+SOIC-8DS1307ZN+T&R 111CLM1307+DIP-8DS1307+112CLM1307N+DIP-8DS1307N+113CLM4717EUB+MSOP-10拟开关MAX4717EUB+114CLM231N/NOPB DIP-8LM231N/NOPB 115CLM231AN/NOPB DIP-8LM231AN/NOPB 116CLM331N/NOPB DIP-8LM331N/NOPB 117CLM331AN/NOPB DIP-8LM331AN/NOPB 118CLM298N Multiwatt-15L298N 119CLM298P POWERSO-20L298P 120CLM2543CDW SOIC-20TLC2543CDW产品手册07序号产品型号封装形式产品概述兼容型号121CLM2543IDW SOIC-20TLC2543IDW 122CLM2543CDB SSOP-20TLC2543CDB 123CLM2543IDB SSOP-20TLC2543IDB 124CLM2543CN DIP-20TLC2543CN 125CLM2543IN DIP-20TLC2543IN 126CLM1543CDW SOIC-20TLC1543CDW 127CLM1543IDW SOIC-20TLC1543IDW 128CLM1543CN DIP-20TLC1543CN 129CLM1543IN DIP-20TLC1543IN 130CLM5615CDGK VSSOIC-8趋稳时间为12.5us并具备上电复位功能的10位、单通道、低功耗DAC TLC5615CDGK 131CLM5615IDGK VSSOIC-8趋稳时间为12.5us并具备上电复位功能的10位、单通道、低功耗DAC TLC5615IGGK 132CLM5615CD SOIC-8趋稳时间为12.5us并具备上电复位功能的10位、单通道、低功耗DAC TLC5615CD 133CLM5615ID SOIC-8趋稳时间为12.5us并具备上电复位功能的10位、单通道、低功耗DAC TLC5615ID 134CLM5615CP DIP-8趋稳时间为12.5us并具备上电复位功能的10位、单通道、低功耗DAC TLC5615CP 135CLM5615IP DIP-8趋稳时间为12.5us并具备上电复位功能的10位、单通道、低功耗DAC TLC5615IP 136CLM3616-00SOP-14IW3616-00137CLM3616-01SOP-14IW3616-01138CLM3617-00SOP-14IW3617-00139CLM3617-01SOP-14IW3617-01140CLM3630-00SOP-14IW3630-00产品手册序号产品型号封装形式产品概述兼容型号141CLM1100-0001BGA-128ASIC从站控制ET1100-0001142CLM1100-0002BGA-128ASIC从站控制ET1100-0002143CLM1100-0003BGA-128ASIC从站控制ET1100-0003144CLM1200-0001QFN-48ASIC从站控制ET1200-0001145CLM1200-0002QFN-48ASIC从站控制ET1200-0002146CLM1200-0003QFN-48ASIC从站控制ET1200-0003147CLM8656ARZ SOIC-8AD8656ARZ148CLM8656ARMZ MSOIC-8AD8656ARMZ149CLM1040T/CM,118SOIC-8TJA1040T/CM,118 150CLM1042T/CM,118SOIC-8TJA1042T/CM,118 151CLM1050T/CM,118SOIC-8TJA1050T/CM,118 152CLM1051T/CM,118SOIC-8TJA1051T/CM,118 153CLM82C250T/YM SOIC-8PCA82C250T/YM 154CLM82C251T/YM SOIC-8PCA82C251T/YM 155CLMEE80C196KC20PLCC-68EE80C196KC20 156CLMEN80C196KC20PLCC-68EN80C196KC20 157CLMN80C196KC20PLCC-68N80C196KC20 158CLMTN80C196KC20PLCC-68TN80C196KC20 159CLMEE87C196KC20PLCC-68EE87C196KC20 160CLMEN87C196KC20PLCC-68EN87C196KC2008产品手册09序号产品型号封装形式产品概述兼容型号161CLMN87C196KC20PLCC-68N87C196KC20162CLMTN87C196KC20PLCC-68TN87C196KC20163CLM8051F020-GQ TQFP-100C8051F020-GQ 164CLM8051F021-GQ TQFP-64C8051F021-GQ 165CLM8051F330-GM VFQFN-20C8051F330-GM 166CLM8051F500-IQ TQFP-48C8051F500-IQ 167CLM8051F500-IM VFQFN-48C8051F500-IM 168CLM8051F502-IQ LQFP-32C8051F502-IQ 169CLM8051F502-IM QFN-32C8051F502-IM170CLM08D1500CIYB/NOPB HLQFP-128ADC08D1500CIYB/NOPB 171CLM083000CIYB/NOPB HLQFP-128ADCADC083000CIYB/NOPB 172CLM10AQ190AVTPY EBGA-38010位5GSPS ADC EV10AQ190AVTPY 173CLM9680BCPZ-1250LFCSP-64双通道14位1GSPS ADC AD9680BCPZ-1250174CLM9739BBCZ BGA-16014位、2.5 GSPS、RF数模AD9739BBCZ 175CLM9779ABSVZ TQFP-100双通道16位1GSPS DAC AD9779ABSVZ 176CLM12DS130AVZPY FPBGA-19612位3GSPS DAC EV12DS130AVZPY 177CLM12DS460AVZP FPBGA-19612位6.4GSPS DAC EV12DS460AVZP 178CLM9434BCPZ-370LFCSP-5612位370MSPS ADC AD9434BCPZ-370179CLM9434BCPZ-500LFCSP-5612位500MSPS ADC AD9434BCPZ-500180CLM4149IRGZTVQFN-4814位250MSPS ADCADS4149IRGZT产品手册10序号产品型号封装形式产品概述兼容型号181CLM9467BCPZ-200LFCSP-7216位200MSPS ADC AD9467BCPZ-200182CLM9467BCPZ-250LFCSP-7216位250MSPS ADC AD9467BCPZ-250183CLM9656BCPZ-125LFCSP-56四通道16位125MSPS ADC AD9656BCPZ-125184CLM9245BCPZ-40LFCSP-3214位40MSPS ADC AD9245BCPZ-40185CLM9245BCPZ-65LFCSP-3214位65MSPS ADC AD9245BCPZ-80186CLM9245BCPZ-80LFCSP-3214位80MSPS ADC AD9245BCPZ-80187CLM9783BCPZ LFCSP-72双通道16位500MSPS DAC AD9783BCPZ 188CLM7656BSTZ-REEL LQFP-64六通道16位250KSPS ADC AD7656BSTZ-REEL 189CLM7960BCPZLFCSP-3218位2MSPS ADC AD7960BCPZ190CLM128S102CIMTX/NOPB TSSOP-1612位1MSPS ADC ADC128S102CIMTX/NOPB 191CLM5638IDR SOIC-8DACTLV5638IDR 192CLM7606BSTZ LQFP-64AD7606BSTZ 193CLM9625BBPZ-2.5BGA-19612位2.6GSPS ADC AD9625BBPZ-2.5194CLM9164BBCZ BGA-16516位12GSPS DAC AD9164BBCZ 195CLM9154BCPZ LFCSP-88四通道16位2.4GSPS DAC AD9154BCPZ 196CLM2160IUK#PBF QFN-4816位25MSPS ADC LTC2160IUK#PBF 197CLM9652BBCZ-310BGA-144双通道16位310MSPS ADC AD9652BBCZ-310198CLM7779ACPZ-RL LFCSP-6424位16KSPS ADC AD7779ACPZ-RL 199CLM9208BBPZ-3000BGA-196双通道14位3GSPS ADCAD9208BBPZ-3000200CLM320VC33PGE120LQFP-144TMS320VC33PGE120产品手册序号产品型号封装形式产品概述兼容型号201CLM320VC33PGEA120LQFP-144TMS320VC33PGEA120 202CLM320VC33PGE150LQFP-144TMS320VC33PGE150203CLM320VC5402PGE100LQFP-144TMS320VC5402PGE100 204CLM320F28335PGFA LQFP-176TMS320F28335PGFA205CLM320LF2406APZA LQFP-100TMS320LF2406APZA206CLM320LF2406APZS LQFP-100TMS320LF2406APZS207CLM320LF2407APGES LQFP-144TMS320LF2407APGES208CLM320LF2407APGEA LQFP-144TMS320LF2407APGEA 209CLM320C6713BPYP200HLQFP-208TMS320C6713BPYP200 210CLM320C6713BZDP225BGA-272TMS320C6713BZDP225 211CLM320C6713BGDP225BGA-272TMS320C6713BGDP225 212CLM320C6713BZDP300BGA-272TMS320C6713BZDP300 213CLM320C6713BGDG300BGA-272TMS320C6713BGDP30011邮箱:*******************。

leuze electronic GSU 14C说明书

leuze electronic GSU 14C说明书物理数据口宽 4mm 口深 68mm 标签长度≥ 5mm 标签宽度≥ 10mm 标签间隙≥ 2mm 传送带速度≤ 240m/min (4m/s) 传送带速度≤ 50m/min(0.83m/s) 典型响应时间≤ 200 µs 重复性 1)1)取决于传送带速度、标签长度和标签之间的间距± 0.2mm 启动前的延迟≤ 300ms 符合IEC 60947-5-2标准电气数据工作电压UB 2) 2)对于UL应用:仅适用于NEC规定的2级电路中12VDC (-5%) ...30VDC (包括残余纹波) 残余纹波≤UB的15% 开路电流≤80mA 开关输出 3) .../663)推挽式开关输出端不得并列连接2个推挽式开关输出针脚4:PNP光开关,NPN暗开关针脚2:PNP暗开关,NPN光开关 (66)2个推挽式开关输出针脚4:PNP暗开关,NPN光开关针脚2:PNP 光开关,NPN暗开关 .../6 1个推挽式开关输出针脚4:PNP光开关,NPN暗开关 .../6D 1个推挽式开关输出针脚4。

PNP暗开关,NPN明开关警告输出2) 1个推挽式开关输出引脚2:低电平有效(正常操作高电平,事件情况低电平)功能开关输出 IGSU明/暗开关,可调信号电压高/低≥(UB-2V)/≤2V 输出电流≤100mA 容性负载≤0. 5µF 指示器绿色LED准备就绪绿色LED,闪烁的示教激活黄色LED开关点在标签间隙红色LED示教错误/功能错误机械数据外壳压铸锌,涂漆颜色红色/黑色重量 270克连接方式M12连接器,5针脚环境数据环境温度(操作/储存)0°C ... +60°C/-40°C ... +70°C 保护电路 4) 4) 1=极性反转保护,2=所有输出的短路保护1, 2VDE 安全等级 III 保护等级 IP 65 适用标准 IEC 60947-5-2 认证 UL 508, C22.2 No.14-13 2) 5)5) 这些接近开关在现场安装时,应与额定为30V、0.5A的UL认证电缆组件一起使用,或与之相当(类别:CYJV/CYJV7或PVVA/PVVA7)。

FPGA可编程逻辑器件芯片XCZU15EG-2FFVB1156E中文规格书

Zynq UltraScale+ MPSoCsA comprehensive device family, Zynq UltraScale+ MPSoCs offer single-chip, all programmable,heterogeneous multiprocessors that provide designers with software, hardware, interconnect, power, security, and I/O programmability. The range of devices in the Zynq UltraScale+MPSoC family allows designers to target cost-sensitive as well as high-performance applications from a single platform using industry-standard tools. While each Zynq UltraScale+MPSoC contains the same PS, the PL, Video hard blocks, and I/O resources vary between the devices.•Automotive: Driver assistance, driver information, and infotainment•Wireless Communications: Support for multiple spectral bands and smart antennas•Wired Communications: Multiple wired communications standards and context-aware network services •Data Centers: Software Defined Networks (SDN), data pre-processing, and analytics •Smarter Vision: Evolving video-processing algorithms, object detection, and analytics•Connected Control/M2M: Flexible/adaptable manufacturing, factory throughput, quality, and safetyThe UltraScale MPSoC architecture provides processor scalability from 32 to 64 bits with support for virtualization, the combination of soft and hard engines for real-time control, graphics/video processing, waveform and packet processing, next-generation interconnect and memory, advanced powermanagement, and technology enhancements that deliver multi-level security, safety, and reliability. Xilinx offers a large number of soft IP for the Zynq UltraScale+MPSoC family. Stand-alone and Linux device drivers are available for the peripherals in the PS and the PL. Xilinx’s Vivado® Design Suite, SDK™, and PetaLinux development environments enable rapid product development for software, hardware, and systems engineers. The Arm-based PS also brings a broad range of third-party tools and IP providers in combination with Xilinx's existing PL ecosystem.The Zynq UltraScale+MPSoC family delivers unprecedented processing, I/O, and memory bandwidth in the form of an optimized mix of heterogeneous processing engines embedded in a next-generation, high-performance, on-chip interconnect with appropriate on-chip memory subsystems. Theheterogeneous processing and programmable engines, which are optimized for different application tasks, enable the Zynq UltraScale+ MPSoCs to deliver the extensive performance and efficiency required to address next-generation smarter systems while retaining backwards compatibility with the original Zynq-7000 All Programmable SoC family. The UltraScale MPSoC architecture also incorporates multiple levels of security, increased safety, and advanced power management, which are critical requirements of next-generation smarter systems. Xilinx’s embedded UltraFast™ design methodology fully exploits the Table 7:Zynq UltraScale+ MPSoC Device FeaturesCG DevicesEG DevicesEV DevicesAPU Dual-core Arm Cortex-A53Quad-core Arm Cortex-A53Quad-core Arm Cortex-A53RPU Dual-core Arm Cortex-R5Dual-core Arm Cortex-R5Dual-core Arm Cortex-R5GPU –Mali-400MP2Mali-400MP2VCU––H.264/H.265找FPGA 和CPLD 可编程逻辑器件,上深圳宇航军工半导体有限公司ASIC-class capabilities afforded by the UltraScale MPSoC architecture while supporting rapid system development.The inclusion of an application processor enables high-level operating system support, e.g., Linux. Other standard operating systems used with the Cortex-A53 processor are also available for theZynq UltraScale+MPSoC family. The PS and the PL are on separate power domains, enabling users to power down the PL for power management if required. The processors in the PS always boot first, allowing a software centric approach for PL configuration. PL configuration is managed by software running on the CPU, so it boots similar to an ASSP.Programmable LogicThis section covers the information about blocks in the Programmable Logic (PL).Device LayoutUltraScale architecture-based devices are arranged in a column-and-grid layout. Columns of resources are combined in different ratios to provide the optimum capability for the device density, target market or application, and device cost. At the core of UltraScale+MPSoCs is the processing system that displaces some of the full or partial columns of programmable logic resources. Figure 1 shows a device-level view with resources grouped together. For simplicity, certain resources such as the processing system, integrated blocks for PCIe, configuration logic, and System Monitor are not shown.Resources within the device are divided into segmented clock regions. The height of a clock region is 60CLBs. A bank of 52 I/Os, 24 DSP slices, 12 block RAMs, or 4 transceiver channels also matches the height of a clock region. The width of a clock region is essentially the same in all cases, regardless of device size or the mix of resources in the region, enabling repeatable timing results. Each segmented clock region contains vertical and horizontal clockrouting that span its full height and width. These horizontal and vertical clock routes can be segmented at the clock region boundary to provide a flexible, high-performance, low-power clock distribution architecture. Figure 2 is a representation of a device divided into regions.Figure 1:Device with Columnar ResourcesFigure 2:Column-Based Device Divided into Clock RegionsHigh-Speed Serial TransceiversUltra-fast serial data transmission between devices on the same PCB, over backplanes, and across even longer distances is becoming increasingly important for scaling to 100Gb/s and 400Gb/s line cards. Specialized dedicated on-chip circuitry and differential I/O capable of coping with the signal integrity issues are required at these high data rates.Three types of transceivers are used in Zynq UltraScale+ MPSoCs: GTH, GTY, and PS-GTR. All transceivers are arranged in groups of four, known as a transceiver Quad. Each serial transceiver is a combined transmitter and receiver. Table 10 compares the available transceivers.The following information in this section pertains to the GTH and GTY only.The serial transmitter and receiver are independent circuits that use an advanced phase-locked loop (PLL) architecture to multiply the reference frequency input by certain programmable numbers between 4 and 25 to become the bit-serial data clock. Each transceiver has a large number of user-definable features and parameters. All of these can be defined during device configuration, and many can also be modified during operation.Table 10:Transceiver InformationZynq UltraScale+ MPSoCsType PS-GTRGTH GTY Qty40–440–28Max. Data Rate 6.0Gb/s 16.3Gb/s 32.75Gb/s Min. Data Rate1.25Gb/s0.5Gb/s0.5Gb/sApplications•PCIe Gen2•USB•Ethernet•Backplane •HMC•100G+Optics •Chip-to-Chip •25G+Backplane •HMC。

Type-C连接器商品说明书

Material declaration MATERIAL

DESCRIPTION

-

HIGH TEMP[Black]

COPPER ALLOY【G/F】 Au:15μ” PLATING OVERALL;[t=0.12mm]銅鎳硅合金

Universal Serial Bus Connectors

Technical parameter

PROJECT

╲ ╲

LEVEL Contact Rating

Electrical

Initial Contact Resulation Resistance

Withstand Voltage

A10

SSRXn2

SuperSpeed RX differential pair

B3

Positive half of second

A11

SSRXp2

SuperSpeed RX differential pair

B2

A12

GND

Ground return

B1

Signal NAME GND

SSRXp1

SSRXn1 V BUS SBU2

COPPER ALLOY【G/F】 Au:15μ” PLATING OVERALL;[t=0.12mm]銅鎳硅合金

STAINLESS【G/F】

STAINLESS STEEL(t=0.15mm)

STAINLESS【G/F】

STAINLESS STEEL/ Ni PLATING(t=0.10mm)

STAINLESS【G/F】

Durable Performance

ZXCTN 9004(V2.08.31)分组传送产品硬件描述

2.1 子架结构 ............................................................................................................2-1 2.2 风扇插箱 ............................................................................................................2-2 2.3 子架板位资源 .....................................................................................................2-3

3.5.1 单板功能 ..................................................................................................3-4 3.5.2 单板原理 ..................................................................................................3-5 3.5.3 面板说明 ..................................................................................................3-6 3.5.4 指示灯状态 ...............................................................................................3-7 3.5.5 告警、性能、事件 ....................................................................................3-8 3.6 P90S1-2XGE-XFP ............................................................................................ 3-11 3.6.1 单板功能 ................................................................................................ 3-11 3.6.2 单板原理 ................................................................................................ 3-11 3.6.3 面板说明 ................................................................................................ 3-13 3.6.4 指示灯状态 ............................................................................................. 3-13 3.6.5 告警、性能、事件 .................................................................................. 3-13 3.7 P90S1-4XGE-XFP ............................................................................................ 3-15 3.7.1 单板功能 ................................................................................................ 3-15 3.7.2 单板原理 ................................................................................................ 3-16

FPGA可编程逻辑器件芯片XCZU15EG-FFVB1156AA7中文规格书

Table 5:XPHY Clocking Attributes AttributeDescription CONTINUOUS_DQSAlong with RX_GATING, determines if and how the strobe is gated.DQS_SRCDetermines where the strobe is being received from (NIBBLESLICE[0], inter-nibble clocking,inter-byte clocking, or PLL_CLK for serial mode).EN_CLK_TO_LOWEREnables outputting the strobe to certain numerically lower nibbles (inter-byte clocking).EN_CLK_TO_UPPER Enables outputting the strobe to certain numerically higher nibbles (inter-byte clocking).EN_OTHER_NCLKEnables sourcing the n-side of the strobe from inter-nibble clocking.EN_OTHER_PCLKEnables sourcing the p-side of the strobe from inter-nibble clocking.INV_RXCLKInverts the incoming strobe to NIBBLESLICE[0].REFCLK_FREQUENCYSet to the frequency of PLL_CLK.RX_CLK_PHASE_P,RX_CLK_PHASE_NControls strobe (p-clk and n-clk in this case) centering for source-synchronous interfaces.RX_GATINGAlong with CONTINUOUS_DQS, determines if and how the strobe is gated.TX_GATINGUses PHY_WREN to gate the transmit data and/or outgoing strobe/capture clock.NIBBLESLICE[1] cannot be affected by TX_GATING.TX_OUTPUT_PHASE_90_<0-5>Used to center the strobe/capture clock to data on the transmitter side. Applied to the NIBBLESLICE(s) sending the strobe/capture clock, causing it to be center-aligned to the data.IMPORTANT! The phase detector in the XPLL is recommended to be used for all PL-XPHY interfaces. If the interface spans multiple banks, only the phase detector in the XPLL providing the clock to the PLshould be used. Refer to Versal ACAP Clocking Resources Architecture Manual (AM003) for moreinformation.While transmit interface clocking is sourced from XPLLs, receiver clocking for source-synchronous interfaces can take advantage of inter-nibble and inter-byte clocking for forwarding the strobe. If an interface spans more than one nibble, then inter-nibble and/or inter-byte clocking can be used to route the strobe to other nibbles:•Inter-nibble clocking is supported within nibble-pairs, as shown in the following figure. Nibble-pairs are XPHY nibbles (0,1), (2,3), (4,5), and (6,7)•Inter-byte clocking is supported between specific XPHY nibbles within an XPIO bank, as shown in the table below. While inter-nibble clocking can only occur between two nibbles,inter-byte clocking can forward a strobe further by using each nibble receiving the inter-byte clock to also forward it. Nibbles receiving a clock through inter-byte clocking can generate an inter-nibble clock, though nibbles receiving an inter-nibble clock cannot use it to generate an inter-byte clock. CLK_FROM_OTHER_XPHY of the source nibble starting the inter-byte clocking should be set to 1'b1.•XPHY nibble 8 is not part of a nibble-pair and thus is not capable of inter-nibble clocking, but can receive an inter-byte clock from XPHY nibble 6. Use CLK_TO_LOWER when performing inter-byte clocking from XPHY nibble 6 to XPHY nibble 8. This is the exception to theCLK_TO_LOWER/CLK_TO_UPPER naming scheme.•When SERIAL_MODE = TRUE, inter-nibble/byte clocking is not supported. Instead, each nibble generates its own capture clock from the PLL_CLK input.Chapter 2: XPHY ArchitectureAM010 (v1.2) April 2, 2021Versal ACAP SelectIO Resources Architecture ManualRevision HistoryAM010 (v1.2) April 2, 2021Versal ACAP SelectIO Resources Architecture Manual。

英飞拓产品型号

英飞拓产品型号英飞拓产品型号渠道产品,价格优惠,不满意可退货 150********2.1 固定摄像机-PALV5101-A50142 ⼀体化摄像机2.3 因定半球摄像机2.4 V1700A系列快球2.5 V1750A系列充氮快球2.6 V1700S系列内置单模光端机的快球2.7 V1900A系列快球2.8⼀体化云台摄像机2.9恒速球形护罩/云台2.10快球零部件1.模拟监控前端产品2.1 固定摄像机V5101-A2014 V5101-A3014 V5101-A5014 V5101-A2019 V5101-A3019 V5102-A2014 V5102⽇夜型因定摄像机V5102-A3014 V5102-A5014V5102-A3019 V5102-A2019V5103宽动态彩⾊固定摄像机V5103-A3014V1025-1H⾼解析度彩⾊摄像机V1025-1HV1026-1⾼解析度⽇夜转换型摄像机V1026-1V1027-1 1/2英⼨宽动态⾼灵敏度低照度彩⾊摄像机V1027-1V1033-1宽动态⽇夜转换型摄像机V1033-12.2⼀体化摄像机PALV1224⼀体化彩⾊摄像机V1224-22A14V1244⼀体化⽇夜转换摄像机V1244-23A14 V1244-26A14 V5411-A2014ST V5411-A2014SU V5411-A2014SV 2.3固定半球摄像机PALV5411-A2014SW V5411-A2014SX V5411-A2014SYV5411-A2014SZ480线⼿动变焦⾃动光圈镜头V5411-A2014 SBV5411-A2014 SDV5411-A2014SE V5411-A2014SC V5411-A2014SF520线固定焦距镜头V5411-A3014ST V5411-A3014SU V5411-A3014SV V5411-A3014SW V5411-A3014SX V5411-A3014SY V5411-A3014SZ520线⼿动变焦⾃动光圈镜头V5411-A3014SB V5411-A3014SD V5411-A3014SE V5411-A3014SCV5512室内⽇夜型因定半球摄像机V5411-A3014SF V5512-A2014SB V5512-A2014SE520线⼿动变焦⾃动光圈镜头V5512-A3014SB V5512-A3014SEV5413室内宽动态彩⾊固定半球摄像机V5512-A3014SB V5413-A3024SB V5413-A3024SE2.3固定半球摄像机PALV5411-A2014ST V5411-A2014SU V5411-A2014SV V5411-A2014SW V5411-A2014SXV5411-A2014SY480线⼿动变焦⾃动光圈镜头V5411-A2014SZ V5411-A2014SB V5411-A2014SD V5411-A2014SE V5411-A2014SC V5411-A2014SF520线固定焦距镜头V5411-A3014ST V5411-A3014SU V5411-A3014SV V5411-A3014SW V5411-A3014SZ V5411-A3014SY V5411-A3014SX520线⼿动变焦⾃动光圈镜头V5411-A3014SB V5411-A3014SD V5411-A3014SE V5411-A3014SCV5512室内⽇夜型因定半球摄像机V5411-A3014SF V5512-A2014SB520线⼿动变焦⾃动光圈镜头V5512-A2014SE V5512-A3014SB V5512-A3014SB V5512-A3014SEV5413室内宽动态彩⾊固定半球摄像机V5413-A3024SBV1700A系列快球PAL室内吸顶装快球V1725A-C1C2C6 V1726A-C1C2C6 V1727A-C1C2C6 V1728A-C1C2C6 V1724A-C1C2C6 V1729A-C1C2C6 V1723A-C1C2C6室内⽀架装快球V1725A-C1C2B6 V1726A-C1C2B6 V1727A-C1C2B6 V1728A-C1C2B6 V1724A-C1C2B6 V1729A-C1C2B6 V1723A-C1C2B6室外吸顶装快球V1745A-C1C2C6 V1746A-C1C2C6 V1747A-C1C2C6 V1748A-C1C2C6 V1744A-C1C2C6 V1749A-C1C2C6 V1743A-C1C2C6室外⽀架装快球V1745A-C1C2B6 V1746A-C1C2B6 V1747A-C1C2B6 V1748A-C1C2B6 V1744A-C1C2B6 V1749A-C1C2B6 V1743A-C1C2B62.5 V1750A 系列充氮快球-PAL室内充氮吊装快球V1757A-C1C3B6 V1758A-C1C3B6 V1759A-C1C3B6 V1753A-C1C3B6 V1791室内内置单模光端机吸顶装快球V1725S-C1C2C6 V1726S-C1C2C6 V1727S-C1C2C6 V1728S-C1C2C6 V1729S-C1C2C6 V1723S-C1C2C6室内内置单模光端机⽀架装快球V1725S-C1C2B6V1726S-C1C2B6V1727S-C1C2B6 V1728S-C1C2B6 V1729S-C1C2B6 V1723S-C1C2B6室外内置单模光端机吸顶装快球V1745S-C1C2C6 V1746S-C1C2C6 V1747S-C1C2C6 V1748S-C1C2C6 V1743S-C1C2C6 V17243S-C1C2C6室外内置单模光端机⽀架装快球V1745S-C1C2B6 V1746S-C1C2B6 V1747S-C1C2B6 V1748S-C1C2B6 V1749S-C1C2B6 V1724S-C1C2B62.7V1900A系列快球PAL室内吸顶装快球V1901A-C1C2C6 V1902A-C1C2C6 V1903A-C1C2C6 V1904A-C1C2C6 V1906A-C1C2C6室内⽀架装快球V1901A-C1C2B6 V1902A-C1C2B6 V1903A-C1C2B6 V1904A-C1C2B6 V1906A-C1C2B6室外吸顶装快球V1911A-C1C2C6 V1912A-C1C2C6 V1913A-C1C2C6 V1914A-C1C2C6 V1916A-C1C2B6 V1917A-C1C2B6室外⽀架装快球V1911A-C1C2B6 V1912A-C1C2B6 V1913A-C1C2B6 V1914A-C1C2B6 V1916A-C1C2B6 V1917A-C1C2B62.8 ⼀体化云台摄像机V1492-18A15 V1492-23A15 V1492-26A15 V1492-35A15 V1492-36A15 V1492-18A16 V1492-23A16 V1492-26A16 V1492-35A16 V1492-36A16 V1492-18A17 V1492-23A17 V1492-26A17 V1492-35A17 V1492-36A17 V1492-18A18 V1492-23A18 V1492-26A18 V1492-35A18V1492-36A18⼀体化云台⽀架(适⽤于V1492、V1493)V1662-W1 V1662-S1 V1662-C1 V1662-DV1493中型⾼速云台V1493-D16V7A15 V1493-DP16V7A15 V1493-A15 V1493-D16V7A16 V1493-DP16V7A16 V1493-A16 V1493-D16V7A17 V1493-DP16V7A17 V1493-A17 V1493-D16V7A18 V1493-DP16V7A18 V1493-A18V1631隔爆云台摄像机V1631-23A19 V1631-25A19防爆护罩V1421-15SHB6-2V1421-15SHB8-2V1421-15A6-2V1421-15A8-2隔爆云台⽀架V1664-W V1664-C V1664-S V1665-W12.9恒速球形护罩/云台V1682 系列室内/室外恒速球形云台V1682-C2B-9HBPV1682-C2B-9HBP2.10 快球零部件V1761 V1761L V1762 V1763 V1764 V1764A V1764B V1765 V1765A V1766适⽤V1750A系列充氮快球V1761S V1762S V1763S球芯V1700N系列⽹络快球球芯(PAL)(坜另配视频缟码卡)V1825N-C16 V1826N-C16 V1827N-C16 V1828N-C16 V1829N-C16 V1825N-C15 V1826N-C15 V1827N-C15V1828N-C16 V1829N-C16V1700A系列快球球芯(PAL)V1825A-C16 V1826A-C16 V1827A-C16 V1828A-C16 V1829A-C16 V1825N-C15 V1826N-C15 V1827N-C15V1828N-C16 V1829N-C16V1750A系列充氮快球球芯(PAL)V1825AP-C16 V1826AP-C16 V1827AP-C16 V1828AP-C16 V1829AP-C16 V1825AP-C15 V1826AP-C15 V1827AP-C15 V1828AP-C15 V1829AP-C15V1700S系列光端机快球球芯(PAL)V1825AF-C16 V1826 AF-C16 V1827 AF-C16 V1828 AF-C16 V1829 AF-C16 V1825AF-C15 V1826 AF-C15 V1827 AF-C15 V1828 AF-C15 V1829 AF-C15V1900A系列快球球芯(PAL)V1901A-C16 V1902A-C16 V1903A-C16 V1904A-C16 V1905A-C16 球罩快球下罩(不带法兰)V1840-C2 V1840-S2 V1840-C3 V1840-S3室内吸顶装配罩下罩(带法兰)V1840-C2C V1840-S2C V1840-C3C V1840-S3C室内⽀架装配罩下罩(带法兰)V1840-C2B V1840-S2B V1840-C3B V1840-S3B室外⽀架装和吸顶装配罩下罩(带法兰和加热器)V1840-C2O V1840-S2O V1840-C3O V1840-S3O V1840P-C3OV1840P-S3O快球上罩(带法兰)V1850-IC V1850-IB V1850-OC V1850-OB V1850P-OB V1852-IC V1852-IB V1852-OC V1852-OB快球电源板V1860A-C6 V1860N-L6 V1860A-C5 V1860N-L5快球电源V3922-24A-26.键盘及辅助设备6.1 键盘V2100 V2109X V2111X V2110 V2115 V2116X7.3 V2020系列中型矩阵切换/控制器V2020AX-16X4 V2020AX-16X8 V2020AX-16X12 -16X16 V2020AX-16X20 V2020AX-16X24 V2020AX-16X28V2020AX-16X32 V2020AX-32X4 V2020AX-32X8 V2020AX-32X12 V2020AX-32X16 V2020AX-32X20 V2020AX-32X24 V2020AX-32X28 V2020AX-32X32 V2020AX-48X4 V2020AX-48X8V2020AX-48X12 V2020AX-48X16 V2020AX-48X20 V2020AX-48X24 V2020AX-48X28 V2020AX-48X32 V2020AX-64X4 V2020AX-64X8 V2020AX-64X12 V2020AX-64X16 V2020AX-64X20 V2020AX-64X24 V2020AX-64X28 V2020AX-64X32 V2020AX-80X4 V2020AX-80X8 V2020AX-80X12 V2020AX-80X16 V2020AX-80X20 V2020AX-80X24V2020AX-80X28 V2020AX-80X32 V2020AX-96X4 V2020AX-96X8 V2020AX-96X12 V2020AX-96X16 V2020AX-96X20 V2020AX-96X24 V2020AX-96X28 V2020AX-96X32V2020AX-112X4 V2020AX-112X8 V2020AX-112X12 V2020AX-112X16 V2020AX-112X20 V2020AX-112X24V2020AX-112X28 V2020AX-112X32 V2020AX-128X4 V2020AX-128X8 V2020AX-128X12 V2020AX-128X16V2020AX-128X20 V2020AX-128X24 V2020AX-128X28 V2020AX-128X32 V2020AX-144X4 V2020AX-144X8V2020AX-144X12 V2020AX-144X16 V2020AX-144X20 V2020AX-144X24 V2020AX-144X28 V2020AX-144X32V2020AX-160X4 V2020AX-160X8 V2020AX-160X12 V2020AX-160X16 V2020AX-160X20 V2020AX-160X24V2020AX-160X28 V2020AX-160X32 V2020AX-176X4 V2020AX-176X8 V2020AX-176X12 V2020AX-176X16V2020AX-176X20 V2020AX-176X24 V2020AX-176X28 V2020AX-176X32 V2020AX-192X4 V2020AX-192X8V2020AX-192X12 V2020AX-192X16 V2020AX-192X20 V2020AX-192X24 V2020AX-192X28 V2020AX-192X32 V2020AX-208X4 V2020AX-208X8 V2020AX-208X12 V2020AX-208X16 V2020AX-208X20 V2020AX-208X24V2020AX-208X28 V2020AX-208X32 V2020AX-224X4 V2020AX-224X8 V2020AX-224X12 V2020AX-224X16V2020AX-224X20 V2020AX-224X24 V2020AX-224X28 V2020AX-224X32 V2020AX-240X4 V2020AX-240X8 V2020AX-240X12 V2020AX-240X16 V2020AX-240X20 V2020AX-240X24 V2020AX-240X28 V2020AX-240X32V2040AX-16X4 V2040AX-16X8 V2040AX-16X12 V2040AX-16X16 V2040AX-16X20 V2040AX-16X24V2040AX-16X28 V2040AX-16X32 V2040AX-32X4 V2040AX-32X8 V2040AX-32X12 V2040AX-32X16V2040AX-32X20 V2040AX-32X24 V2040AX-32X28 V2040AX-32X32 V2040AX-48X4 V2040AX-48X8V2040AX-48X12 V2040AX-48X16 V2040AX-48X20 V2040AX-48X24 V2040AX-48X28 V2040AX-48X32V2040AX-64X4 V2040AX-64X8 V2040AX-64X12 V2040AX-64X16 V2040AX-64X20 V2040AX-64X24 V2040AX-64X28 V2040AX-64X32 V2040AX-80X4 V2040AX-80X8 V2040AX-80X12 V2040AX-80X16 V2040AX-80X20V2040AX-80X24 V2040AX-80X28 V2040AX-80X32V2040AX-96X4 V2040AX-96X8 V2040AX-96X12 V2040AX-96X16 V2040AX-96X20 V2040AX-96X24 V2040AX-96X28 V2040AX-96X32 V2040AX-112X4 V2040AX-112X8 V2040AX-112X12 V2040AX-112X16 V2040AX-112X20 V2040AX-112X24 V2040AX-112X28V2040AX-112X32 V2040AX-128X4 V2040AX-128X8 V2040AX-128X12 V2040AX-128X16V2040AX-128X20 V2040AX-128X24 V2040AX-128X28 V2040AX-128X32 V2040AX-144X4V2040AX-144X8 V2040AX-144X12 V2040AX-144X16 V2040AX-144X20 V2040AX-144X24V2040AX-144X28 V2040AX-144X32 V2040AX-160X4 V2040AX-160X8 V2040AX-160X12V2040AX-160X16 V2040AX-160X20 V2040AX-160X24 V2040AX-160X28 V2040AX-160X32 V2040AX-176X4V2040AX-176X8 V2040AX-176X12 V2040AX-176X16 V2040AX-176X20V2040AX-176X24 V2040AX-176X28 V2040AX-176X32 V2040AX-192X4 V2040AX-192X8V2040AX-192X12 V2040AX-192X16 V2040AX-192X20 V2040AX-192X24 V2040AX-192X28V2040AX-192X32V2040AX-208X4 V2040AX-208X8 V2040AX-208X12 V2040AX-208X16 V2040AX-208X20 V2040AX-208X24V2040AX-208X28 V2040AX-208X32 V2040AX-224X4 V2040AX-224X8 V2040AX-224X12 V2040AX-224X16V2040AX-224X20 V2040AX-224X24 V2040AX-224X28 V2040AX-224X32 V2040AX-240X4 V2040AX-240X8V2040AX-240X12 V2040AX-240X16 V2040AX-240X20 V2040AX-240X24 V2040AX-240X28 V2040AX-240X32V2040AX-256X4V2040AX-256X8 V2040AX-256X12 V2040AX-256X16 V2040AX-256X20 V2040AX-256X24V2040AX-256X28 V2040AX-256X32A2011X-16X5 A2011X-32X5 A2020X-16X4 A2020X-16X8 A2020X-16X12 A2020X-16X16 A2020X-16X20 A2020X-16X24 A2020X-16X28 A2020X-16X32 A2020X-32X4 A2020X-32X8 A2020X-32X12 A2020X-32X16 A2020X-32X20 A2020X-32X24 A2020X-32X28A2020X-32X32 A2020X-48X4 A2020X-48X8 A2020X-48X12 A2020X-48X16 A2020X-48X20A2020X-48X24 A2020X-48X28 A2020X-48X32 A2020X-64X4 A2020X-64X8 A2020X-64X12A2020X-64X16 A2020X-64X20 A2020X-64X24 A2020X-64X28 A2020X-64X32 A2020X-80X4A2020X-80X8 A2020X-80X12 A2020X-80X16 A2020X-80X20 A2020X-80X24 A2020X-80X28A2020X-80X32 A2020X-96X4 A2020X-96X8 A2020X-96X12 A2020X-96X16 A2020X-96X20 A2020X-96X24 A2020X-96X28 A2020X-96X32 A2020X-112X4A2020X-112X8 A2020X-112X12 A2020X-112X16 A2020X-112X20 A2020X-112X24A2020X-112X28 A2020X-112X32 A2020X-128X4 A2020X-128X8 A2020X-128X12 A2020X-128X16 A2020X-128X20 A2020X-128X24 A2020X-128X28 A2020X-128X32A2020X-144X4 A2020X-144X8 A2020X-144X12 A2020X-144X16 A2020X-144X20 A2020X-144X24 A2020X-144X28 A2020X-144X32 A2020X-160X4 A2020X-160X8 A2020X-160X12 A2020X-160X16 A2020X-160X20 A2020X-160X24 A2020X-160X28A2020X-160X32 A2020X-176X4 A2020X-176X8 A2020X-176X12 A2020X-176X16 A2020X-176X20A2020X-176X24 A2020X-176X28 A2020X-176X32 A2020X-192X4 A2020X-192X8 A2020X-192X12 A2020X-192X16 A2020X-192X20 A2020X-192X24 A2020X-192X28 A2020X-192X32 A2020X-208X4 A2020X-208X8。

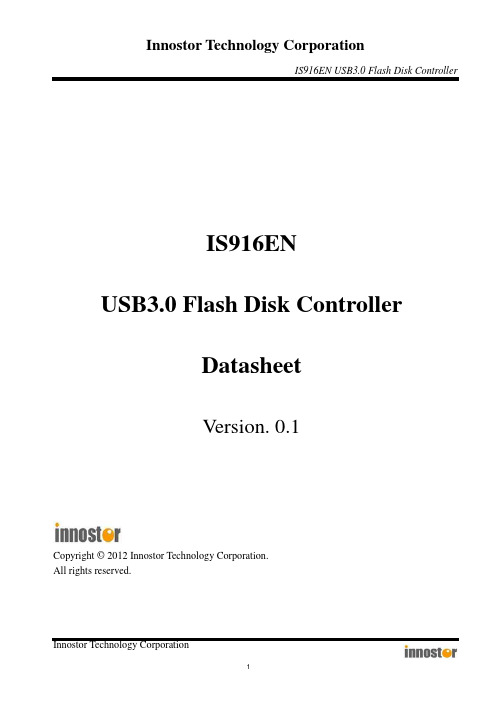

银灿主控芯片规格书

IS916ENUSB3.0 Flash Disk ControllerDatasheetVersion. 0.1Copyright © 2012 Innostor Technology Corporation.All rights reserved.Innostor Technology Corporation© Copyright Innostor Technology CorporationAll Rights Reserved.No part of this document may be reproduced or transmitted in any form or by any means. All information contained in this document is subject to change without notice. The products described in this document are not intended for use implantation or other life supports application where malfunction may result in injury or death to persons. The information contained in this document does not affect or change Innostor Technology Corporation product specification or warranties. Nothing in this document shall operate as an express or implied license or environments, and is presented as an illustration. The results obtained in other operating environments may vary.THE INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED ON AN “AS IS” BASE. In no event will Innostor be liable for damages arising directly or indirectly from any use of the information contained in this document.Innostor Technology Corporation2F, No.8, Lane 32, Xianzheng 5th St.,Jhubei City, Hsinchu County 302, TaiwanInnostor Technology CorporationTable of Contents :1.DESCRIPTION (5)2.FEATURES (5)3.PIN ASSIGNMENT (6)3.1QFN-48 Pin Assignment (6)3.2 Pin Descriptions (7)4.SYSTEM APPLICATION CONFIGURATIONS (9)4.1 QFN-48 configuration examples (9)5.ELECTRICAL CHARACTERISTICS (10)5.1Absolute Maximum Ratings (10)5.2Operating Conditions (10)5.3Reference Clock Source and Crystal Specification (10)5.4DC Characteristics (11)5.5DC Characteristics of 3.3V IO (11)6. PACKAGE INFORMATION (12)6.1QFN-48 package outline dimension (12)Innostor Technology CorporationRevision HistoryNo Date History V.0.10 2012/04/20 Initial versionInnostor Technology Corporation1. DescriptionIS916EN is the latest USB-3.0 interface Nand Flash Controller. With flexible firmware codesupporting, IS916EN can support various flash technology including 4k / 8k / 16k page TLC / MLC / SLC by different 2xnm / 2ynm / 1xnm process for major flash vendors.2. FeaturesOne Channel data bus by small footprint packageUp to 4 CEs supportedECC protect up to 70 bit ( configurable ) by 1K bytes2xnm, 2ynm, 1xnm : SLC / MLC / TLC types NAND Flash supportedEF-NAND Flash supportedONFI 2.1 spec. interface supportedToggle DDR interface supportedCompliant with USB 3.0 spec. version 1.0Compliant with USB 2.0 spec. backward compatible with USB1.1Compliant with USB Mass Storage Class spec. version 1.0High performance 1T 8051 with hardware acceleration DMAF/W off-load engine embedded1.2V low power consumption designLED indicator to show link status and r/w trafficCustomized VID/ PID with serial numberBuilt-in LDO regulator30Mhz CrystalInnostor Technology CorporationInnostor Technology Corporation 3. Pin Assignment3.1 QFN-48 Pin Assignment3.2 Pin DescriptionsPin Name Pin #Pullup/DownAttribute DescriptionRE# 1 O Flash Channel RE#DAT[7] 2 Down I/O Flash data bit [7]DAT[6] 3 Down I/O Flash data bit [6]DAT[5] 4 Down I/O Flash data bit [5]DAT[4] 5 Down GND Flash data bit [4]DVDD33 6 PWR 3.3V IO Power SupplyDQS 7 Down I/O Flash DQSDAT[3] 8 Down I/O Flash data bit [3]DAT[2] 9 Down I/O Flash data bit [2]DAT[1] 10 Down I/O Flash data bit [1]DAT[0] 11 Down GND Flash data bit [0]V5IN 12 I Regulator 5.0V inputV33O 13 O Regulator 3.3V outputGND 14 GND GNDV33I 15 I Regulator 3.3V inputV12O 16 O Regulator 1.2V outputGPIO[5] 17 I/O General Purpose I/ODVDD12 18 PWR 1.2V Core power supplyCLE 19 O Flash Channel Command latch ALE 20 O Flash Channel Address latch DVDD33 21 PWR 3.3V IO power supplyWE# 22 O Flash Channel WE#WP# 23 O Flash write protectionRST_N 24 Up I Chip reset, low activeXSCO 25 O Crystal 30Mhz outputXSCI 26 I Crystal 30Mhz inputInnostor Technology CorporationPin Name Pin #PullUp/DownAttribute DescriptionGND 27 GND GNDDP 28 I/O USB 2.0 differential pin plusDM 29 I/O USB 2.0 differential pin minusVCC33A 30 PWR 3.3V analog power supplySS_TXM 31 O USB 3.0 differential transmit pin negative SS_TXP 32 O USB 3.0 differential transmit pin positive VCC12A 33 PWR 1.2V analog power supplySS_RXM 34 I USB 3.0 differential receive pin negative SS_RXP 35 I USB 3.0 differential receive pin positive GND 36 GND GNDMODE[2] 37 Down I Test mode pin, tie to GNDMODE[1] 38 Down I Test mode pin, tie to GNDMODE[0] 39 Down I Test mode pin, tie to GNDLED_U3 40 O LED to show link at U3 modeLED_RW 41 O LED to show link status and r/w traffic DVDD12 42 PWR 1.2V Core power supplyCE_3 43 O Flash chip enable 3CE_2 44 O Flash chip enable 2DVDD33 45 PWR 3.3V IO power supplyCE_1 46 O Flash chip enable 1CE_0 47 O Flash chip enable 0RB# 48 O Flash Ready / Busy StatusInnostor Technology CorporationInnostor Technology Corporation 4. System Application Configurations4.1 QFN-48 configuration examplesTSOP Flash Package5. Electrical Characteristics5.1 Absolute Maximum RatingsParameter Symbol Min. Max. Unit Storage Temperature T storage-40 150 C5.0V supply power V in50-0.3 5.5 V3.3V supply power V in33-0.3 3.63 V1.2V supply power V in12-0.3 1.32 V5.2 Operating ConditionsParameter Symbol Min. Max. Unit Operating Temperature T operating0 70 C USB VBUS VBUS 4.5 5.5 VRegulator 5V IN V5IN 4.5 5.5 VRegulator 3.3V IN V33I 3.0 3.6 VAnalog 3.3V power VCC33A 3.15 3.45 VAnalog 1.2V power VCC12A 1.14 1.26 VDigital 3.3V power DVDD33 2.97 3.63 VDigital 1.2V power DVDD12 1.08 1.32 V5.3 Reference Clock Source and Crystal SpecificationParameter Symbol Min. Typ. Max. Unit Reference clock XSCI 30 Mhz Crystal freq. tolerance -50 +50 ppmInnostor Technology Corporation5.4 DC CharacteristicsParameter Symbol Min. Typ. Max. Unit USB bus power VBUS_cur 310 mA Analog 3.3V power U3 V33A_cur_u3 18 mAAnalog 1.2V power U3 V12A_cur_u3 103 mAAnalog 3.3V power U2 V33A_cur_u3 32 mAAnalog 1.2V power U2 V12A_cur_u3 3 mAAnalog 3.3V Suspend V33A_cur_sus 0.3 mAAnalog 1.2V Suspend V12A_cur_sus 0.6 mADigital 3.3V power DVDD33_cur TBD mADigital 1.2V power DVDD12_cur TBD mA5.5 DC Characteristics of 3.3V IOParameter Symbol Min. Typ. Max. Unit Digital 3.3V power DVDD33 2.97 3.3 3.63 VInput low voltage Vil 0.8 VInput high voltage Vih 2.0 VOutput low voltage Vol 0.4 VOutput high voltage Voh 2.4 VPull-up resistance Rpu 40 75 190 KΩPull-down resistance Rpd 30 75 190 KΩInnostor Technology CorporationInnostor Technology Corporation 6. Package Information6.1 QFN-48 package outline dimension。

FPGA可编程逻辑器件芯片XCZU15EG-FFVB1156ES中文规格书

Chapter 5:Recommended PCB Design RulesBoard Level Routing Challenges1.0mm Ball Pitch, Fine-Pitch BGAXilinx fine-pitch BGA packages have a full matrix of solder balls (Figure5-4). Thesepackages are made of multilayer BT substrates. Signal balls are in a perimeter formatextending up to eight rows in FG676 packages and up to ten rows in FG1156 packages.Power and ground pins are grouped together appropriately.Figure 5-4:Fine Pitch BGA Pin AssignmentsThe number of layers required for effective routing of fine-pitch BGA packages is dictatedby the layout of pins on each package. If several other technologies and components arealready present on the board, the system cost is factored with every added board layer. Theintent of a board designer is to optimize the number of layers required considering bothcost and performance. This application note provides guidelines to minimize the requiredboard layers for routing fine-pitch BGA products using standard PCB technologies(5/5mils lines/space or 6/6mils lines/space).For high performance and other system needs, designers can use premium technologieswith finer lines/spaces on the board. The pin assignment and pin grouping scheme on fullarray fine-pitch BGA packages enables an efficient way of routing the board with anoptimum number of required board layers.Board Routing StrategyMinimum RequirementsThe diameter of a land pad on the component side is provided by Xilinx. This informationis required prior to the start of the board layout to design the board pads to match thecomponent side land geometry. The typical values of these land pads are described inFigure5-4.For FG series packages, NSMD (non-solder mask defined) pads on the board aresuggested. This allows a clearance between the land metal (diameter L) and the soldermask opening (diameter M) as shown in Figure5-3. The space between the NSMD pad andDevice Package User GuideUG112 (v3.7) September 5, 2012Device Package User GuideUG112 (v3.7) September 5, 2012Additional Power Management Options•Exposed metal heatsink packages: All thermally enhanced BGAs with dies facingdown (including these package codes - BG352, BG432, BG560, FG680, FG860, and flip-chip BGAs) are offered with an exposed metal heatsink at the top. These areconsidered high-end thermal packages and they lend themselves to the application of external heatsinks (passive or active) for further heat removal efficiency. Again,precautions should be taken to prevent component damage when a bulky heatsink is attached.•Active heatsinks can include a simple heatsink incorporating a mini fan or even Peltier Thermoelectric Coolers (TECs) with a fan to carry away any heat generated.Any consideration of applying TEC in heat management should include consultation with experts in using the devices, as these devices can be reversed and this might damage components. Also, condensation can be an issue.•Molded packages (FG456, FG676, FG1156, PQs, etc.) without exposed metal at the top also can use these heatsinks at the top for further heat reduction. These BGA packages are similar in construction to those used in graphic cards in PC applications, andheatsinks used for those applications can easily be used for these packages as well. In this case, the θJC resistance will be the limiting consideration.•Outside the package itself, the board on which the package sits can have a significantimpact on thermal performance. Board designs can be implemented to take advantage of a board’s ability to spread heat. Heat flows to the outside of a package and is sunk into the board to be conducted away – through heatpipes or by normal convection.The effect of the board will be dependent on the size and how it conducts heat. Board size, the level of copper traces on it, and the number of buried copper planes all lower the θJA thermal resistance for a package mounted on it. Some of the heatsink packages –like HQ, with the exposed heatsink on the board side – can be glued to the board with thermal compound to enhance heat removal into the board. BGA packages with full matrix of balls can be cooled with this scheme. Users need to be aware that a direct heat path to the board from a component also exposes the component to theFigure 3-14:Heatsink with Clips UG112_C3_13_111208Figure 3-15:Example of Active Heatsink for BGA (Malico)UG112_C3_14_111208。

FPGA可编程逻辑器件芯片XCZU15EG-1FFVB1156E中文规格书

Package MarkingAll Virtex-6 devices have package top-markings similar to the example shown in Figure 6-1 and explained in Table 6-1.Note:The informational product change customer notice XCN11022: Product Marking Change outlines a change to the top marking process from an ink mark to laser marking. The previous top mark included an ink patch.Figure 6-1:Virtex-6 Device Package MarkingTable 6-1:Xilinx Device Marking Definition—ExampleItem DefinitionXilinx Logo Xilinx logo, Xilinx name with trademark, and trademark-registered status.Family Brand Logo Virtex-6 family name with trademark and trademark-registered status. This line is optional and could appear blank.Pb-Free Logo If the Pb-Free logo appears, the package is RoHS compliant. If the logo does not appear, the package is RoHS compliant if it has the G detailed in the 2nd Line definition below.1st LineDevice type.Table5-1 shows the thermal resistance data for Virtex-6 devices (grouped in the packagesoffered). The data includes junction-to-ambient in still air, junction-to-case, and junction-to-board data based on standard JEDEC four-layer measurements.Note:The data in Table5-1 is for device/package comparison purposes only. Do not apply directly toyour system design. Attempts to recreate this data are only valid using the steady-state measurementtechnique outlined in JESD51-2a, JESD51-6, and JESD51-8.Table 5-1:Thermal Resistance Data—All DevicesPackagePackageBody SizeDevicesθJA(°C/W)θJB(°C/W)θJC(°C/W)θJA (°C/W)@ 250 LFMθJA (°C/W)@ 500 LFMθJA (°C/W)@ 750 LFMFF484 FFG48423x23XC6VLX75T13.1 3.50.288.97.4 6.8XC6VLX130T12.6 3.10.178.37.0 6.4FF784FFG784 RF78429x29XC6VLX75T11.8 3.50.287.5 6.4 5.8XC6VLX130TXQ6VLX130T11.2 3.10.177.1 6.0 5.4XC6VLX195T10.9 2.90.147.0 5.8 5.3XC6VLX240TXQ6VLX240T10.8 2.70.11 6.8 5.7 5.2FF1154 FFG115435x35XC6VHX250T9.7 2.50.09 5.8 4.8 4.3XC6VHX380T9.5 2.30.06 5.6 4.6 4.1FF1155 FFG115535x35XC6VHX255T9.5 2.30.06 5.6 4.6 4.1XC6VHX380T9.5 2.30.06 5.6 4.6 4.1FF1156FFG1156 RF115635x35XC6VLX130TXQ6VLX130T10.0 2.90.16 6.1 5.1 4.6XC6VLX195T9.9 2.70.12 6.0 5.0 4.5XC6VLX240TXQ6VLX240T9.8 2.60.10 5.9 4.9 4.4XC6VLX365T9.6 2.40.08 5.7 4.7 4.2XC6VSX315TXQ6VSX315T9.6 2.40.08 5.7 4.7 4.2XC6VSX475TXQ6VSX475T9.3 2.10.10 5.4 4.4 4.0determined by those using these guidelines. For complete information on packagemoisture / reflow classification and package reflow conditions, refer to the JointIPC/JEDEC Standard J-STD-020C.Sn/Pb Reflow SolderingFigure5-4 shows typical conditions for solder reflow processing of Sn/Pb soldering usingIR/convection. Both IR and convection furnaces are used for BGA assembly. The moisturesensitivity of PSMCs must be verified prior to surface-mount flow.Figure 5-4:Typical Conditions for IR Reflow Soldering of Sn/Pb Solder Notes for Figure5-4:1.Maximum temperature range = 220°C (body). Minimum temperature range before205°C (leads/balls).2.Preheat drying transition rate 2–4°C/s3.Preheat dwell 95–180°C for 120–180 seconds4.IR reflow must be performed on dry packagesPb-Free Reflow SolderingXilinx uses SnAgCu (SAC305) solder balls for BGA packages. In addition, suitable materialare qualified for the higher reflow temperatures (245°C–250°C) required by Pb-freesoldering processes. Xilinx recommends soldering SAC305 BGA packages with SAC305solder paste.The optimal profile must take into account the solder paste/flux used, the size of theboard, the density of the components on the board, and the mix between large componentsand smaller, lighter components. Profiles should be established for all new board designsusing thermocouples at multiple locations on the component. In addition, if there is amixture of devices on the board, then the profile should be checked at various locations onthe board. Ensure that the minimum reflow temperature is reached to reflow the largercomponents and at the same time, the temperature does not exceed the thresholdtemperature that might damage the smaller, heat sensitive components.Table5-4 and Figure5-5 provide guidelines for profiling Pb-free solder reflow.In general, a gradual, linear ramp into a spike has been shown by various sources to be theoptimal reflow profile for Pb-free solders (Figure5-5). SAC305 alloy reaches full liquidusSoldering Guidelines temperature at 235°C. When profiling, identify the possible locations of the coldest solder joints and ensure that those solder joints reach a minimum peak temperature of 235°C for at least 10 seconds. It might not be necessary to ramp to peak temperatures of 260°C. Reflowing at high peak temperatures of 260°C and above can damage the heat sensitive components and cause the board to warp.Users should reference the latest IPC/JEDEC J-STD-020 standard for the allowable peak temperature on the component body. The allowable peak temperature on the component body is dependent on the size of the component. Refer to Table5-4 for peak package reflow body temperature information. In any case, use a reflow profile with the lowest peak temperature possible.Table 5-4:Pb-Free Reflow Soldering GuidelinesProfile Feature Convection, IR/ConvectionRamp-up rate2°C/s maximumPreheat Temperature 150°–200°C60–120 secondsTemperature maintained above 217°C60–150 seconds (60–90 seconds typical)Time within 5°C of actual peak temperature30 seconds maximumPeak Temperature (lead/ball)235°C minimum, 245°C typical (depends onsolder paste, board size, components mixture) Peak Temperature (body)245°C–250°C, package body size dependent(reference Table5-5)Ramp-down Rate2°C/s maximumTime 25°C to Peak Temperature 3.5 minutes minimum, 5.0 minutes typical,8minutes maximumFigure 5-5:Typical Conditions for Pb-Free Reflow SolderingChapter 6:Package Marking。

高速超导闪电跳变接收器(非镍金属、RoHS合规)产品包装尺寸说明书

BYG24DH to BYG24JH

200 to 600 140

20 at 1

1.5

1.5 at 1

150

x

1.5

1.15 at 1

150

x

AR3PDH to AR3PJH

x

200 to 1000 120 (140)

3

1.6 (1.9) at 3

175

AR3PKH to AR3PMH

x

SMPC (TO-277A) 4.75 x 6.65 x 1.2

VISH AY INTERTECHN OLOGY, INC.

AVALANCHE RECTIFIERS

Sinterglass and Plastic

Ultrafast Avalanche Rectifiers (Halogen-Free, RoHS-Compliant)

Product

BYT53A to BYT53G BYV26A to BYV26E BYV27-50 to BYV27-200

2

1.1 at 1

175

x

x

n/a

x

No

200 to 400 100

3.0

1.1 at 3

x

x

x

200 to 400 100

3

1.1 at 3

20 at 1

x

x

x

4.2 x Ø 4.3

200 to 1000 100 (150) 3 (2.9) 1.6 (1.78) at 3

50 to 1000 100

3

1.4 at 3

x

x

x

x

x

x

800 to 1000 250

BZX84C16LT1G中文资料

BZX84C16LT1G中⽂资料BZX84B4V7LT1,BZX84C2V4LT1 Series Zener Voltage Regulators225 mW SOT?23 Surface MountThis series of Zener diodes is offered in the convenient, surface mount plastic SOT?23 package. These devices are designed to provide voltage regulation with minimum space requirement. They are well suited for applications such as cellular phones, hand held portables,and high density PC boards.FeaturesPbFree Packages are Available225 mW Rating on FR4 or FR5 BoardZener Breakdown V oltage Range 2.4 V to 75 VPackage Designed for Optimal Automated Board Assembly Small Package Size for High Density ApplicationsESD Rating of Class 3 (>16 KV) per Human Body ModelTight Tolerance Series Available (See Page 4)Mechanical CharacteristicsCASE: V oid-free, transfer-molded, thermosetting plastic case FINISH: Corrosion resistant finish, easily Solderable MAXIMUM CASE TEMPERATURE FOR SOLDERING PURPOSES:260°C for 10 SecondsPOLARITY: Cathode indicated by polarity band FLAMMABILITY RATING: UL 94 V?0MAXIMUM RATINGSMaximum ratings are those values beyond which device damage can occur.Maximum ratings applied to the device are individual stress limit values (not normal operating conditions) and are not valid simultaneously. If these limits are exceeded, device functional operation is not implied, damage may occur and reliability may be affected.1.FR?5 = 1.0 X 0.75 X 0.62 in.2.Alumina = 0.4 X 0.3 X 0.024 in., 99.5% alumina.See specific marking information in the device marking column of the Electrical Characteristics table on page 3 of this data sheet.DEVICE MARKING INFORMATION/doc/1413279559.html(Pinout: 1-Anode, 2-No Connection, 3-Cathode)(T A = 25°Cunless otherwise noted, V F = 0.95 V Max. @ I F = 10 mA)ELECTRICAL CHARACTERISTICS ? BZX84CxxxLT1 SERIES (STANDARD TOLERANCE) (Pinout: 1-Anode, 2-No Connection, 3-Cathode)(T A = 25°C unless otherwise noted, V F = 0.90 V Max. @ I F = 10 mA) (Devices listed in bold, italic are ON Semiconductor Preferred devices.)Z*The “G” suffix indicates Pb?Free package available.ELECTRICAL CHARACTERISTICS ? BZX84BxxxL (Tight Tolerance Series)(Pinout: 1-Anode, 2-No Connection, 3-Cathode)(T A = 25°C unless otherwise noted, V F = 0.90 V Max. @ I F = 10 mA)Z*The “G” suffix indicates Pb?Free package available.V Z , T E M P E R A T U R E C O E F F I C I E N T (m V /C )°θV Z , NOMINAL ZENER VOLTAGE (V)32012345678Figure 1. Temperature Coefficients (Temperature Range ?55°C to +150°C)V Z , T E M P E R A T U R E C O E F F I C I E N T (m V /C )°θ100101V Z , NOMINAL ZENER VOLTAGE (V)Figure 2. Temperature Coefficients (Temperature Range ?55°C to +150°C)V Z , NOMINAL ZENER VOLTAGEFigure 3. Effect of Zener Voltage onZener ImpedanceZ Z T , D Y N A M I C I M P E D A N C E ()1000100101V F , FORWARD VOLTAGE (V)Figure 4. Typical Forward VoltageI F , F O R W A R D C U R R E N T (m A )1000100101C , C A P A C I T A N C E (p F )V Z , NOMINAL ZENER VOLTAGE (V)Figure 5. Typical Capacitance 1000100101V Z , ZENER VOLTAGE (V)1001010.10.01I Z , Z E N ER C U R R E N T (m A )V Z , ZENER VOLTAGE (V)1001010.10.01I R , L E A K A G E C U R R E N T (A )µV Z , NOMINAL ZENER VOLTAGE (V)Figure 6. Typical Leakage Current10001001010.10.010.0010.00010.00001I Z , Z E N E R C U R R E N T (m A )Figure 7. Zener Voltage versus Zener Current(V Z Up to 12 V)Figure 8. Zener Voltage versus Zener Current(12 V to 91 V)PACKAGE DIMENSIONSSOT?23TO?236AB CASE 318?09ISSUE AK*For additional information on our Pb?Free strategy and solderingdetails, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D. SOLDERING FOOTPRINT*ǒmm inchesǔSCALE 10:1ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

欧姆龙视觉传感器介绍

ৃ㓪ࠊ఼ CJ2 CPUऩܗ

ᴎ఼Ҏࠊ఼

FQ-M EtherCAT⬉㓚 FQ-MWNL/-WN (RJ45/M12)

FQ-MS@@@ FQ-MS@@@-M

FQ-M I/O⬉㓚FQ-MWDL/-MWD

䚼✻ᯢ˄FL㋏߫˅

✻ᯢࠊ఼ FL-TCC1

⬉⑤ DC24V

㾺থ䕧ܹ Ӵᛳ఼

䞣 ᮟ䕀㓪ⷕ఼

CCTV镜头

类型

FL系列用

型号 FQ-MWDL005 FQ-MWDL010 FQ-MWD005 FQ-MWD010

型号 FQ-XPM FQ-AC@ * FQ-BAT1 FQ-XT FQ-XH HMC-SD291 HMC-SD491

型号

W4S1-03B W4S1-05B W4S1-05C

型号

GX-JC03 GX-JC06

新的基于轮廓的检索算法为取放应用带来独一无二的性能。变化的照明条件、反射、物体倾斜或部分 隐藏的物体不再是问题。无论同时检测的物体数量多少,即便高速时,FQ-M也可获得稳定的结果。

同类最佳的性能

360°检测、

每分钟5000件的高速处理。

30

物 25 体 数 20

15

10 146

15ms

时间(ms)

161

FQ-M EtherCAT ⬉㓚 FQ-MWNEL/-MWNE (M12/M12)

FQ-M I/O⬉㓚

FQ-M EtherCAT ⬉㓚 FQ-MWNL/-WN (M12/RJ45)

⬉⑤ DC24V

㾺থ䕧ܹ Ӵᛳ఼

䞣 ᮟ䕀㓪ⷕ఼

⫼Ѣ I/O ࠊⱘ PLC

* Sysmac Studio㾺ᓣপ᱃఼᮴⊩ϔ䍋Փ⫼DŽ䖲Ѡ㗙ᯊˈSysmac StudioᇚӬܜDŽ Փ⫼Sysmac Studioᷛޚ⠜ᴀᇍᴎ఼㞾ࡼ࣪ࠊ఼NJ㋏߫䖯㸠䆒ᅮᯊˈ䇋⫼USB䖲Ethernet㔥㒰䖲⬉㛥ϢNJDŽ

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。