pichiapink_strain_secsig_media_man

Bosch NDC-265-P 720p IP Dome Camera 说明书

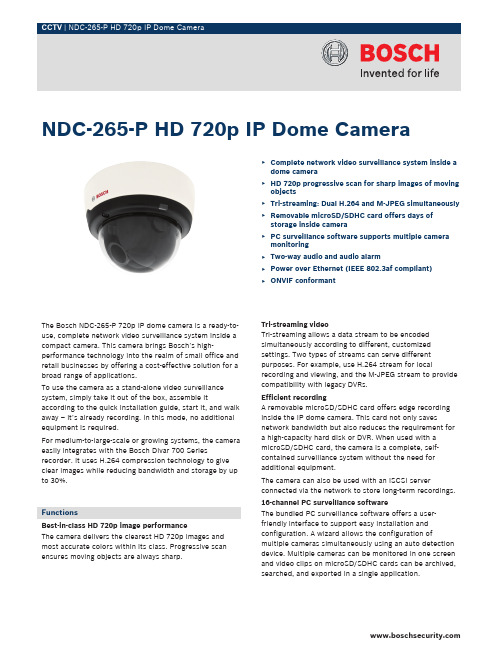

The Bosch NDC-265-P 720p IP dome camera is a ready-to-use, complete network video surveillance system inside a compact camera. This camera brings Bosch’s high-performance technology into the realm of small office and retail businesses by offering a cost-effective solution for a broad range of applications.To use the camera as a stand-alone video surveillance system, simply take it out of the box, assemble it according to the quick installation guide, start it, and walk away – it’s already recording. In this mode, no additional equipment is required.For medium-to-large-scale or growing systems, the camera easily integrates with the Bosch Divar 700 Series recorder. It uses H.264 compression technology to give clear images while reducing bandwidth and storage by up to 30%.FunctionsBest-in-class HD 720p image performanceThe camera delivers the clearest HD 720p images and most accurate colors within its class. Progressive scan ensures moving objects are always sharp.Tri-streaming videoTri-streaming allows a data stream to be encoded simultaneously according to different, customized settings. Two types of streams can serve different purposes. For example, use H.264 stream for local recording and viewing, and the M-JPEG stream to provide compatibility with legacy DVRs.Efficient recordingA removable microSD/SDHC card offers edge recording inside the IP dome camera. This card not only saves network bandwidth but also reduces the requirement for a high-capacity hard disk or DVR. When used with a microSD/SDHC card, the camera is a complete, self-contained surveillance system without the need for additional equipment.The camera can also be used with an iSCSI server connected via the network to store long-term recordings. 16-channel PC surveillance softwareThe bundled PC surveillance software offers a user-friendly interface to support easy installation and configuration. A wizard allows the configuration of multiple cameras simultaneously using an auto detection device. Multiple cameras can be monitored in one screen and video clips on microSD/SDHC cards can be archived, searched, and exported in a single application.NDC-265-P HD 720p IP Dome Camera▶Complete network video surveillance system inside adome camera▶HD 720p progressive scan for sharp images of movingobjects▶Tri-streaming: Dual H.264 and M-JPEG simultaneously▶Removable microSD/SDHC card offers days ofstorage inside camera▶PC surveillance software supports multiple cameramonitoring▶Two-way audio and audio alarm▶Power over Ethernet (IEEE 802.3af compliant)▶ONVIF conformant2ONVIF 1.0 conformantThe latest Open Network Video Interface Forum (ONVIF) standard ensures compatibility with other surveillance products. This will contribute to a reduction in future upgrade or migration costs.Two-way audio and audio alarmTwo-way audio allows remote users to listen in on an area and communicate messages to visitors or intruders via an external loudspeaker (not included). Audio detection can be used to generate an alarm, if needed.Tamper and motion detectionA wide range of configuration options is available for alarms signaling camera tampering. A built-in algorithm for detecting movement in the video can also be used for alarm signaling.Power-over-EthernetPower for the camera can be supplied via a Power-over-Ethernet (IEEE 802.3af) compliant network cable connection. With this configuration, only a single cable connection is required to view, power, and control the camera.Certifications and ApprovalsSafety EU: EN 60950-1: 2006,Reference IEC 60950-1:2005US: UL 60950-1:1st edition dated October 31, 2007Canada: CAN/CSA-C22.2 NO. 60950-1-03EMC EN 50130-4:1995 + A1:1998 + A2:2003FCC Part15 Subpart B, Class BEMC directive 2004/108/ECEN 55022 class BEN 61000-3-2 :2006EN 61000-3-3 : 1995+A1 :2001+A2 :2005EN 55024AS/NZS CISPR 22 (equal to CISPR 22)ICES-003 Class BEN 50121-4:2006Product Certifica-tionsCE, FCC, UL, cUL, C-tick, CB, VCCIPower supply CE, UL, cUL, PSE, CCC Installation/Configuration NotesConnections1I/O2Power 12 VDC3Ethernet RJ454Audio Line-out5Audio Line-inDimensionsmm (in)Parts IncludedQuantity Component1NDC-265-P 720p IP Dome camera1Quick Installation Guide1Installation paper sticker1Torx screwdriver for Dome cover1CD ROM1Camera fixing screw kit1MicroSDHC card (warranty provided by card manufacturer) 1Universal power supply with US, EU and UK plug3Technical SpecificationsPowerInput voltage+12 VDC orPower-over-EthernetPower consumption 4.2 W (max)VideoSensor type¼-inch CMOSSensor pixels1280 x 800Sensitivity 1.0 lxVideo resolution720p, 4CIF/D1, VGA, CIF, QVGA Video compression H.264 MP (Main Profile); H.264 BP+(Baseline Profile Plus); M-JPEGMax. frame rate30 fps (M-JPEG frame rate can vary de-pending on system loading)LensLens type Varifocal 2.7 to 9 mm, DC Iris F1.2 tocloseLens mount Board mountedConnectionAnalog video out 2.5 mm jack for installation onlyAlarm input Short or DC 5V activationRelay out Input rating Maximum 1 A 24 VAC/VDC AudioAudio input Built-in microphoneLine in jack connectorAudio output Line out jack connectorAudio communication Two-way, full duplexAudio compression G.711, L16 (live and recording)Local StorageMemory card slot Supports up to 32 GB microSD/SDHCcard(An SD card of Class 4 or higher is recom-mended for HD recording) Recording Continuous recording, ring recording.alarm/events/schedule recording Software ControlUnit configuration Via web browser or PC surveillance soft-wareNetworkProtocols HTTP, HTTPs, SSL, TCP, UDP, ICMP,RTSP, RTP, Telnet, IGMPv2/v3, SMTP,SNTP, FTP, DHCP client, ARP, DNS,DDNS, NTP, SNMP, UPnP, 802.1X, iSCSI Ethernet10/100 Base-T, auto-sensing, half/full du-plex, RJ45PoE IEEE 802.3af compliant MechanicalDimensions Diameter: 135 mm (5.32 in)Height: 102 mm (4 in)Weight568 g (1.25 lb) approx. EnvironmentalOperating temperatureCamera-10 ºC to +50 ºC (14 ºF to +122 ºF)Operating temperatureUniversal Power Supply Unit0 ºC to +40 ºC (+32 ºF to +104 ºF) Storage temperature-20 ºC to +70 ºC (-4 ºF to +158 ºF) Humidity10% to 80% relative humidity (non con-densing)Ordering InformationNDC-265-P 720p IP Dome CameraHD 720p IP Dome Camera System includingvarifocal lens and power supplyNDC-265-P4Americas:Bosch Security Systems, Inc. 130 Perinton Parkway Fairport, New York, 14450, USA Phone: +1 800 289 0096 Fax: +1 585 223 9180***********************.com Europe, Middle East, Africa:Bosch Security Systems B.V.P.O. Box 800025600 JB Eindhoven, The NetherlandsPhone: + 31 40 2577 284Fax: +31 40 2577 330******************************Asia-Pacific:Robert Bosch (SEA) Pte Ltd, Security Systems11 Bishan Street 21Singapore 573943Phone: +65 6258 5511Fax: +65 6571 2698*****************************Represented by© Bosch Security Systems Inc. 11 | Data subject to change without notice T7233796747 | Cur: en-US, V2, 5 Jan 2011。

SDIO spec

f in eo nIn fio nI n fTechnical Committee SD Card Associationf in eo nIn fi ne o n I nf in eo nIRevision HistoryDate Version Changes compared to previous issueApril 3, 2006 1.10 Simplified Version Initial ReleaseFebruary 8, 20072.00(1) Added method to change bus speed (Normal Speed up to 25MHzand High Speed up to 50 MHz)(2) Operational Voltage Requirement is extended to 2.7-3.6V(3) Combine sections 12 (Physical Properties) and 13 (MechanicalExtensions) and add miniSDIO to the new section 13 (Physical Properties)(4) Add Embedded SDIO ATA Standard Function Interface Code (5) Reference of Physical Ver2.00 supports SDHC combo card. (6) Some typos in Ver1.10 are fixed.f in eo nIn fi ne o n I nf in eo nI Release of SD Simplified SpecificationThe following conditions apply to the release of the SD simplified specification ("Simplified Specification") by the SD Card Association. The Simplified Specification is a subset of the complete SD Specification which is owned by the SD Card Association.Publisher:SD Association2400 Camino Ramon, Suite 375 San Ramon, CA 94583 USA Telephone: +1 (925) 275-6615 Fax: +1 (925) 886-4870 E-mail: office@Copyright Holder: The SD Card AssociationNotes:This Simplified Specification is provided on a non-confidential basis subject to the disclaimers below. Any implementation of the Simplified Specification may require a license from the SD Card Association or other third parties.Disclaimers:The information contained in the Simplified Specification is presented only as a standard specification for SD Cards and SD Host/Ancillary products and is provided "AS-IS" without any representations or warranties of any kind. No responsibility is assumed by the SD Card Association for any damages, any infringements of patents or other right of the SD Card Association or any third parties, which may result from its use. No license is granted by implication, estoppel or otherwise under any patent or other rights of the SD Card Association or any third party. Nothing herein shall be construed as an obligation by the SD Card Association to disclose or distribute any technical information, know-how or other confidential information to any third party.f in eo nIn fi ne o n I nf in eo nConventions Used in This DocumentNaming ConventionsSome terms are capitalized to distinguish their definition from their common English meaning. Words not capitalized have their common English meaning.Numbers and Number BasesHexadecimal numbers are written with a lower case “h” suffix, e.g., FFFFh and 80h. Binary numbers are written with a lower case “b” suffix (e.g., 10b).Binary numbers larger than four digits are written with a space dividing each group of four digits, as in 1000 0101 0010b.All other numbers are decimal.Key WordsMay: Indicates flexibility of choice with no implied recommendation or requirement.Shall: Indicates a mandatory requirement. Designers shall implement such mandatory requirements to ensure interchangeability and to claim conformance with the specification.Should: Indicates a strong recommendation but not a mandatory requirement. Designers should give strong consideration to such recommendations, but there is still a choice in implementation.Application NotesSome sections of this document provide guidance to the host implementers as follows: Application Note:This is an example of an application note.f in eo nIn fi ne o n I nf in eo nTable of Contents1. General Description.................................................................................................................................1 1.1 SDIO Features....................................................................................................................................1 1.2 Primary Reference Document.............................................................................................................1 1.3 Standard SDIO Functions....................................................................................................................1 2. SDIO Signaling Definition........................................................................................................................2 2.1 SDIO Card Types................................................................................................................................2 2.2 SDIO Card modes...............................................................................................................................2 2.2.1 SPI (Card mandatory support).....................................................................................................2 2.2.2 1-bit SD Data Transfer Mode (Card Mandatory Support).............................................................2 2.2.3 4-bit SD Data Transfer Mode (Mandatory for High-Speed Cards, Optional for Low-Speed).........2 2.3 SDIO Host Modes...............................................................................................................................2 2.4 Signal Pins..........................................................................................................................................3 3. SDIO Card Initialization............................................................................................................................4 3.1 Differences in I/O card Initialization.....................................................................................................4 3.2 The IO_SEND_OP_COND Command (CMD5).................................................................................10 3.3 The IO_SEND_OP_COND Response (R4)........................................................................................11 3.4 Special Initialization considerations for Combo Cards.......................................................................12 3.4.1 Re-initialize both I/O and Memory..............................................................................................12 3.4.2 Using a Combo Card as SDIO only or SD Memory only after Combo Initialization....................12 3.4.3 Acceptable Commands after Initialization..................................................................................12 3.4.4 Recommendations for RCA after Reset.....................................................................................12 3.4.5 Enabling CRC in SPI Combo Card.............................................................................................14 4. Differences with SD Memory Specification..........................................................................................15 4.1 SDIO Command List.........................................................................................................................15 4.2 Unsupported SD Memory Commands...............................................................................................15 4.3 Modified R6 Response......................................................................................................................16 4.4 Reset for SDIO..................................................................................................................................16 4.5 Bus Width..........................................................................................................................................16 4.6 Card Detect Resistor.........................................................................................................................17 4.7 Timings..............................................................................................................................................17 4.8 Data Transfer Block Sizes.................................................................................................................18 4.9 Data Transfer Abort...........................................................................................................................18 4.9.1 Read Abort.................................................................................................................................18 4.9.2 Write Abort.................................................................................................................................18 4.10 Changes to SD Memory Fixed Registers..........................................................................................18 4.10.1 OCR Register.............................................................................................................................19 4.10.2 CID Register...............................................................................................................................19 4.10.3 CSD Register.............................................................................................................................19 4.10.4 RCA Register.............................................................................................................................19 4.10.5 DSR Register.............................................................................................................................19 4.10.6 SCR Register.............................................................................................................................19 4.10.7 SD Status...................................................................................................................................19 4.10.8 Card Status Register..................................................................................................................19 5. New I/O Read/Write Commands............................................................................................................21 5.1 IO_RW_DIRECT Command (CMD52)..............................................................................................21 5.2 IO_RW_DIRECT Response (R5)......................................................................................................22 5.2.1 CMD52 Response (SD modes)..................................................................................................22 5.2.2 R5, IO_RW_DIRECT Response (SPI mode).............................................................................23 5.3 IO_RW_EXTENDED Command (CMD53). (24)f in eo nIn fi ne o n I nf in eo nI 5.3.2 Special Timing for CMD53 Multi-Block Read..............................................................................25 6. SDIO Card Internal Operation................................................................................................................26 6.1 Overview...........................................................................................................................................26 6.2 Register Access Time........................................................................................................................26 6.3 Interrupts...........................................................................................................................................26 6.4 Suspend/Resume..............................................................................................................................27 6.5 Read Wait..........................................................................................................................................27 6.6 CMD52 During Data Transfer............................................................................................................27 6.7 SDIO Fixed Internal Map...................................................................................................................27 6.8 Common I/O Area (CIA)....................................................................................................................28 6.9 Card Common Control Registers (CCCR).........................................................................................28 6.10 Function Basic Registers (FBR)........................................................................................................35 6.11 Card Information Structure (CIS).......................................................................................................37 6.12 Multiple Function SDIO Cards...........................................................................................................37 6.13 Setting Block Size with CMD53.........................................................................................................37 6.14 Bus State Diagram............................................................................................................................38 7. Embedded I/O Code Storage Area (CSA).............................................................................................39 7.1 CSA Access.......................................................................................................................................39 7.2 CSA Data Format..............................................................................................................................39 8. SDIO Interrupts.......................................................................................................................................40 8.1 Interrupt Timing.................................................................................................................................40 8.1.1 SPI and SD 1-bit Mode Interrupts ..............................................................................................40 8.1.2 SD 4-bit Mode............................................................................................................................40 8.1.3 Interrupt Period Definition ..........................................................................................................40 8.1.4 Interrupt Period at the Data Block Gap in 4-bit SD Mode (Optional)..........................................40 8.1.5 Inhibited Interrupts (Removed Section)......................................................................................40 8.1.6 End of Interrupt Cycles...............................................................................................................40 8.1.7 Terminated Data Transfer Interrupt Cycle ..................................................................................41 8.1.8 Interrupt Clear Timing.................................................................................................................41 9. SDIO Suspend/Resume Operation........................................................................................................42 10. SDIO Read Wait Operation.....................................................................................................................43 11. Power Control.........................................................................................................................................44 11.1 Power Control Overview....................................................................................................................44 11.2 Power Control support for SDIO Cards.............................................................................................44 11.2.1 Master Power Control ................................................................................................................44 11.2.2 Power Selection.........................................................................................................................45 11.2.3 High-Power Tuples.....................................................................................................................45 11.3 Power Control Support for the SDIO Host.........................................................................................45 11.3.1 Version 1.10 Host.......................................................................................................................45 11.3.2 Power Control Operation............................................................................................................46 12. High-Speed Mode...................................................................................................................................47 12.1 SDIO High-Speed Mode....................................................................................................................47 12.2 Switching Bus Speed Mode in a Combo Card...................................................................................47 13. SDIO Physical Properties......................................................................................................................48 13.1 SDIO Form Factors...........................................................................................................................48 13.2 Full-Size SDIO ..................................................................................................................................48 13.3 miniSDIO...........................................................................................................................................48 14. SDIO Power.............................................................................................................................................48 14.1 SDIO Card Initialization Voltages......................................................................................................48 14.2 SDIO Power Consumption................................................................................................................48 15. Inrush Current Limiting..........................................................................................................................50 16. CIS Formats.. (51)f in eo nIn fi ne o n I nf in eo nI 16.2 Basic Tuple Format and Tuple Chain Structure.................................................................................51 16.3 Byte Order Within Tuples ..................................................................................................................51 16.4 Tuple Version ....................................................................................................................................52 16.5 SDIO Card Metaformat......................................................................................................................52 16.6 CISTPL_MANFID: Manufacturer Identification String Tuple..............................................................53 16.7 SDIO Specific Extensions..................................................................................................................53 16.7.1 CISTPL_FUNCID: Function Identification Tuple.........................................................................53 16.7.2 CISTPL_FUNCE: Function Extension Tuple..............................................................................54 16.7.3 CISTPL_FUNCE Tuple for Function 0 (common).......................................................................54 16.7.4 CISTPL_FUNCE Tuple for Function 1-7....................................................................................55 16.7.5 CISTPL_SDIO_STD: Function is a Standard SDIO Function.....................................................58 16.7.6 CISTPL_SDIO_EXT: Tuple Reserved for SDIO Cards...............................................................58 Appendix A.....................................................................................................................................................59 A.1 SD and SPI Command List....................................................................................................................59 Appendix B.....................................................................................................................................................61 B.1 Normative References...........................................................................................................................61 Appendix C.....................................................................................................................................................62 C.1 Abbreviations and Terms...................................................................................................................62 Appendix D.. (64)f in eo nIn fi ne o n I nf in eo nI Table of TablesTable 3-1 OCR Values for CMD5.....................................................................................................................10 Table 4-1 Unsupported SD Memory Commands.............................................................................................16 Table 4-2 R6 response to CMD3.....................................................................................................................16 Table 4-3 SDIO R6 Status Bits.........................................................................................................................16 Table 4-4 Combo Card 4-bit Control................................................................................................................17 Table 4-5 Card Detect Resistor States.............................................................................................................17 Table 4-6 is blanked.........................................................................................................................................17 Table 4-7 SDIO Status Register Structure .......................................................................................................20 Table 5-1 Flag data for IO_RW_DIRECT SD Response..................................................................................23 Table 5-2 IO_RW_ EXTENDED command Op Code Definition.......................................................................24 Table 5-3 Byte Count Values ...........................................................................................................................25 Table 6-1 Card Common Control Registers (CCCR).......................................................................................29 Table 6-2 CCCR bit Definitions........................................................................................................................34 Table 6-3 Function Basic Information Registers (FBR)....................................................................................35 Table 6-4 FBR bit and field definitions.............................................................................................................36 Table 6-5 Card Information Structure (CIS) and reserved area of CIA.............................................................37 Table 11-1 Reference Tuples by Master Power Control and Power Select......................................................45 Table 16-1 Basic Tuple Format........................................................................................................................51 Table 16-2 Tuples Supported by SDIO Cards..................................................................................................52 Table 16-3 CISTPL_MANFID: Manufacturer Identification Tuple.....................................................................53 Table 16-4 CISTPL_FUNCID Tuple.................................................................................................................53 Table 16-5 CISTPL_FUNCE Tuple General Structure.....................................................................................54 Table 16-6 TPLFID_FUNCTION Tuple for Function 0 (common)....................................................................54 Table 16-7 TPLFID_FUNCTION Field Descriptions for Function 0 (common).................................................54 Table 16-8 TPLFID_FUNCTION Tuple for Function 1-7..................................................................................55 Table 16-9 TPLFID_FUNCTION Field Descriptions for Functions 1-7.............................................................57 Table 16-10 TPLFE_FUNCTION_INFO Definition...........................................................................................57 Table 16-11 TPLFE_CSA_PROPERTY Definition...........................................................................................57 Table 16-12 CISTPL_SDIO_STD: Tuple Reserved for SDIO Cards................................................................58 Table 16-13 CISTPL_SDIO_EXT: Tuple Reserved for SDIO Cards.................................................................58 Table A-14 SD Mode Command List................................................................................................................59 Table A-15 SPI Mode Command List (60)f in eo nIn fi ne o n I nf in eo nI Table of FiguresFigure 2-1 Signal connection to two 4-bit SDIO cards.......................................................................................3 Figure 3-1 SDIO response to non-I/O aware initialization..................................................................................4 Figure 3-2 Card initialization flow in SD mode (SDIO aware host)....................................................................7 Figure 3-3 Card initialization flow in SPI mode (SDIO aware host)....................................................................9 Figure 3-4 IO_SEND_OP_COND Command (CMD5).....................................................................................10 Figure 3-5 Response R4 in SD mode...............................................................................................................11 Figure 3-6 Response R4 in SPI mode..............................................................................................................11 Figure 3-7 Modified R1 Response....................................................................................................................11 Figure 3-8 Re-Initialization Flow for I/O Controller...........................................................................................13 Figure 3-9 Re-Initialization Flow for Memory controller ...................................................................................13 Figure 5-1 IO_RW_DIRECT Command...........................................................................................................21 Figure 5-2 R5 IO_RW_DIRECT Response (SD modes)..................................................................................22 Figure 5-3 IO_RW_DIRECT Response in SPI Mode.......................................................................................23 Figure 5-4 IO_RW_EXTENDED Command.....................................................................................................24 Figure 6-1 SDIO Internal Map..........................................................................................................................28 Figure 6-2 State Diagram for Bus State Machine (38)f in eo nIn fi ne o n I nf in eo nI 1. General DescriptionThe SDIO (SD Input/Output) card is based on and compatible with the SD memory card. This compatibility includes mechanical, electrical, power, signaling and software. The intent of the SDIO card is to provide high-speed data I/O with low power consumption for mobile electronic devices. A primary goal is that an SDIO card inserted into a non-SDIO aware host shall cause no physical damage or disruption of that host or it’s software. In this case, the SDIO card should simply be ignored. Once inserted into an SDIO aware host, the detection of the card proceeds via the normal means described in this specification with some extensions. In this state, the SDIO card is idle and draws a small amount of power (15 mA averaged over 1 second). During the normal initialization and interrogation of the card by the host, the card identifies itself as an SDIO card. The host software then obtains the card information in a tuple (linked list) format and determines if that card’s I/O function(s) are acceptable to activate. This decision is based on such parameters as power requirements or the availability of appropriate software drivers. If the card is acceptable, it is allowed to power up fully and start the I/O function(s) built into it.1.1 SDIO Features• Targeted for portable and stationary applications• Minimal or no modification to SD Physical bus is required • Minimal change to memory driver software• Extended physical form factor available for specialized applications • Plug and play (PnP) support• Multi-function support including multiple I/O and combined I/O and memory • Up to 7 I/O functions plus one memory supported on one card. • Allows card to interrupt host• Operational Voltage range: 2.7-3.6V (Operational Voltage is used for Initialization) • Application Specifications for Standard SDIO Functions. • Multiple Form Factors:• Full-Size SDIO • miniSDIO1.2 Primary Reference DocumentThis specification is based on and refers extensively to the SDA document:SD Memory Card SpecificationsPart 1 PHYSICAL LAYER SPECIFICATION Version 2.00 May 9, 2006The reader is directed to this document for more information on the basic operation of SD cards. In addition, other documents are referenced in this specification. A complete list can be found in appendix B.1.This specification can apply to any released versions of Physical Layer Specification after Version 2.00.1.3 Standard SDIO FunctionsAssociated with the base SDIO specification, there are several Application Specifications for Standard SDIO Functions. These common functions such as cameras, Bluetooth cards and GPS receivers have a standard register interface, a common operation method and a standard CIS extension. Implementation of the standard interfaces are optional for any card vendor, but compliance with the standard allows the use of standard drivers and applications which will increase the appeal of these cards to the consumer. Full information on these standard interfaces can be found in the Application Specifications for Standard SDIO Functions maintained by the SDA.。

Cisco UCS B200 M4 Blade Server 产品概述说明书

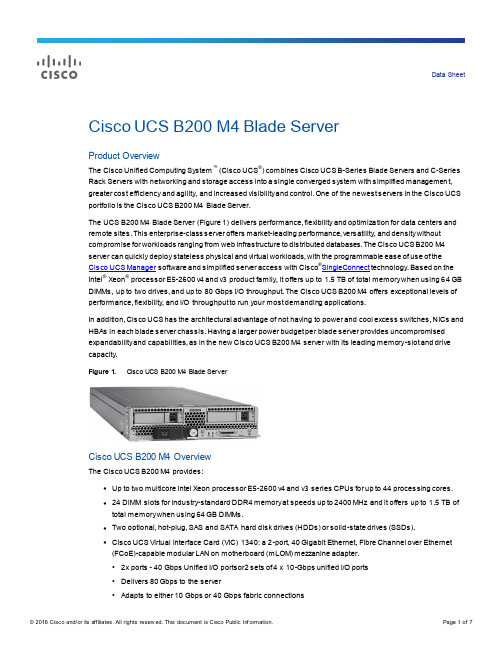

Data SheetCisco UCS B200 M4 Blade ServerProduct OverviewThe Cisco Unified Computing System ™ (Cisco UCS ®) combines Cisco UCS B-Series Blade Servers and C-SeriesRack Servers with networking and storage access into a single converged system with simplified managemen t,greater cost efficiency and agility, and increased visibility and control. One of the newest servers in the Cisco UCSportfolio is the Cisco UCS B200 M4 Blade Server.The UCS B200 M4 Blade Server (Figure 1) delivers performance, flexibility and optimiza tion for data centers andremote sites. This enterprise-class server offers market-leading performance, versatility, and density withoutcompromise for workloads ranging from web infrastructure to distributed databases. The Cisco UCS B200 M4server can quickly deploy stateless physical and virtual workloads, with the programmable ease of use of theCisco UCS Manager software and simplified server access with Cisco ®SingleConnect technology. Based on theIntel ® Xeon ® processor E5-2600 v4 and v3 product family, it offers up to 1.5 TB of total memory when using 64 GBDIMMs, up to two drives, and up to 80 Gbps I/O throughput. The Cisco UCS B200 M4 offers exceptional levels ofperformance, flexibility, and I/O throughput to run your most demanding applications.In addition, Cisco UCS has the architectural advantage of not having to power and cool excess switches, NICs andHBAs in each blade server chassis. Having a larger power budget per blade server provides uncompromisedexpandability and capabilities, as in the new Cisco UCS B200 M4 server with its leading memory-slot and drivecapacity.Figure 1.Cisco UCS B200 M4 Blade ServerCisco UCS B200 M4 OverviewThe Cisco UCS B200 M4 provides:●Up to two multicore Intel Xeon processor E5-2600 v4 and v3 series CPUs for up to 44 processing cores. ● 24 DIMM slots for industry-standard DDR4 memory at speeds up to 2400 MHz and it offers up to 1.5 TB oftotal memory when using 64 GB DIMMs.● Two optional, hot-plug, SAS and SATA hard disk drives (HDDs) or solid-state drives (SSDs).●Cisco UCS Virtual Interface Card (VIC) 1340: a 2-port, 40 Gigabit Ethernet, Fibre Channel over Ethernet(FCoE)-capable modular LAN on motherboard (mLOM) mezzanine adapter. ◦ 2x ports - 40 Gbps Unified I/O portsor2 sets of 4 x 10-Gbps unified I/O ports◦ Delivers 80 Gbps to the server◦ Adapts to either 10 Gbps or 40 Gbps fabric connections●Cisco FlexStorage local drive storage subsystem provides flexible boot and local storage capabilities. Itallows you to:◦Support for optional NVIDIA M6 GPU◦Configure the Cisco UCS B200 M4 to meet your local storage requirements without having to buy,power and cool components that you do not need.◦Choose an enterprise-class RAID controller, or go without any controller or drive bays if not utilizing local drives◦Easily add, change, or remove Cisco FlexStorage modules●The Cisco UCS B200 M4 server is a half-width blade. Up to eight can reside in the 6-rack-unit (6RU) CiscoUCS 5108 Blade Server Chassis, offering one of the highest densities of servers per rack unit of bladechassis in the industry.OverviewThe Cisco UCS B200 M4 server is suited for a broad spectrum of IT workloads, including:●IT and web infrastructure●Virtualized workloads●Consolidating applications●Virtual desktops●Middleware●ERP and CRM applications●Single-instance and distributed databasesThe Cisco UCS B200 M4 Blade Server is one member of the Cisco UCS B-Series Blade Servers platform.As part of Cisco UCS, Cisco UCS B-Series servers incorporate many innovative Cisco technologies to help customers handle their most challenging workloads. Cisco UCS B-Series servers within a Cisco UCSmanagement framework incorporate a standards-based unified network fabric, Cisco Data Center VM-FEX virtualization support, Cisco UCS Manager, Cisco UCS Central, Cisco UCS Director software, and Cisco fabric extender architecture (Figure 2)Figure 2. Cisco UCS Server Innovations Change the E conomics of the Data Center by E nabling Customer Workloads to Benefit from Cisco UCS Simplification and Operational E fficienciesFeatures and Benefits of the Cisco UCS B200 M4 ServerTable 1 lists the main features and benefits of the Cisco UCS B200 M4.Table 1. Main Features and BenefitsSpecificationsTable 2 provides specifications for the Cisco UCS B200 M4. Table 2. P roduct SpecificationsTable 3. Regulatory Standards ComplianceWarranty InformationFind warranty information at on the Product Warranties page.Cisco Unified Computing ServicesUsing a unified view of data center res ources, Cisco and our industry-leading partners deliver services that accelerate your transition to a unified computing environment. Cisco Unified Computing Services can help you create an agile infrastructure that accelerates time to value, reduces costs and risks, and maintains availability during deployment and migration. After deployment, our services can help you improve performance, availability, and resiliency as your business needs evolve, and mitigate risk further. Quickly deploy your data center r esources and optimize ongoing operations to better meet your business needs. For more information about these and other Cisco Data Center Services offerings, visit /go/unifiedcomputingservices or/go/dcservices.Cisco CapitalFinancing to Help You Achieve Your ObjectivesCisco Capital can help you acquire the technology you need to achieve your objective s and stay competitive. We can help you reduce CapEx. Accelerate your growth. Optimize your investment dollars and ROI. Cisco Capital financing gives you flexibility in acquiring hardware, software, services, and complementary third-party equipment. And th ere’s just one predictable payment. Cisco Capital is available in more than 100 countries. Learn more.For More InformationFor more information about Cisco UCS B-Series Blade Servers, visit/en/US/products/ps10280/index.html or contact your local Cisco representative.Printed in USA C78-732434-04 11/16。

PCI-E 标准

PCI Express™Card Electromechanical SpecificationRevision 1.1March 28, 2005Revision RevisionHistory Daterelease. 7/22/021.0 Initial1.0a Incorporated WG Errata C1-C7 and E1. 4/15/031.1 Incorporated approved Errata and ECNs. 03/28/05PCI-SIG disclaims all warranties and liability for the use of this document and the information contained herein and assumes no responsibility for any errors that may appear in this document, nor does PCI-SIG make a commitment to update the information contained herein.Contact the PCI-SIG office to obtain the latest revision of the specification.Questions regarding this specification or membership in PCI-SIG may be forwarded to:Membership ServicesE-mail: administration@Phone: 503-291-2569Fax: 503-297-1090Technical Supporttechsupp@DISCLAIMERThis PCI Express Card Electromechanical Specification is provided “as is” with nowarranties whatsoever, including any warranty of merchantability, noninfringement,fitness for any particular purpose, or any warranty otherwise arising out of any proposal,specification, or sample. PCI-SIG disclaims all liability for infringement of proprietaryrights, relating to use of information in this specification. No license, express or implied,by estoppel or otherwise, to any intellectual property rights is granted herein.PCI Express is a trademark of PCI-SIG.All other product names are trademarks, registered trademarks, or service marks of theirrespective owners.Copyright © 2002-2005 PCI-SIGContents1.INTRODUCTION (7)1.1.TERMS AND DEFINITIONS (7)1.2.REFERENCE DOCUMENTS (9)1.3.SPECIFICATION CONTENTS (9)1.4.OBJECTIVES (10)1.5.ELECTRICAL OVERVIEW (10)1.6.MECHANICAL OVERVIEW (11)2.AUXILIARY SIGNALS (13)2.1.REFERENCE CLOCK (14)2.1.1.Low Voltage Swing, Differential Clocks (14)2.1.2.Spread Spectrum Clocking (SSC) (15)2.1.3.REFCLK AC Specifications (16)2.1.4.REFCLK Phase Jitter Specification (19)2.2.PERST# SIGNAL (20)2.2.1.Initial Power-Up (G3 to L0) (20)2.2.2.Power Management States (S0 to S3/S4 to S0) (21)2.2.3.Power Down (22)2.3.WAKE# SIGNAL (24)2.4.SMBUS (OPTIONAL) (27)2.4.1.Capacitive Load of High-power SMBus Lines (27)2.4.2.Minimum Current Sinking Requirements for SMBus Devices (28)2.4.3.SMBus “Back Powering” Considerations (28)2.4.4.Power-on Reset (28)2.5.JTAG PINS (OPTIONAL) (29)2.6.AUXILIARY SIGNAL PARAMETRIC SPECIFICATIONS (30)2.6.1.DC Specifications (30)2.6.2.AC Specifications (31)3.HOT INSERTION AND REMOVAL (33)3.1.SCOPE (33)3.2.PRESENCE DETECT (33)4.ELECTRICAL REQUIREMENTS (35)4.1.POWER SUPPLY REQUIREMENTS (35)4.2.POWER CONSUMPTION (36)4.3.POWER SUPPLY SEQUENCING (37)4.4.POWER SUPPLY DECOUPLING (38)4.5.ELECTRICAL TOPOLOGIES AND LINK DEFINITIONS (38)4.5.1.Topologies (38)4.5.2.Link Definition (40)4.6.ELECTRICAL BUDGETS (41)4.6.1.AC Coupling Capacitors (42)4.6.2.Insertion Loss Values (Voltage Transfer Function) (42)4.6.3.Jitter Values (44)4.6.4.Crosstalk (46)ne-to-Lane Skew (46)4.6.6.Equalization (47)4.6.7.Skew within the Differential Pair (47)4.7.EYE DIAGRAMS AT THE ADD-IN CARD INTERFACE (47)4.7.1.Add-in Card Transmitter Path Compliance Eye-Diagram (48)4.7.2.Add-in Card Minimum Receiver Path Sensitivity Requirements (49)4.7.3.System Board Transmitter Path Compliance Eye Diagram (50)4.7.4.System Board Minimum Receiver Path Sensitivity Requirements (52)5.CONNECTOR SPECIFICATION (53)5.1.CONNECTOR PINOUT (53)5.2.CONNECTOR INTERFACE DEFINITIONS (58)5.3.SIGNAL INTEGRITY REQUIREMENTS AND TEST PROCEDURES (62)5.4.CONNECTOR ENVIRONMENTAL AND OTHER REQUIREMENTS (65)5.4.1.Environmental Requirements (65)5.4.2.Mechanical Requirements (67)5.4.3.Current Rating Requirement (68)5.4.4.Additional Considerations (69)6.ADD-IN CARD FORM FACTORS AND IMPLEMENTATION (71)6.1.ADD-IN CARD FORM FACTORS (71)6.2.CONNECTOR AND ADD-IN CARD LOCATIONS (81)6.3.CARD INTEROPERABILITY (87)ACKNOWLEDGEMENTS (89)FiguresFIGURE 1-1: VERTICAL EDGE-CARD CONNECTOR (11)FIGURE 1-2: EXAMPLE SERVER I/O BOARD WITH PCI EXPRESS SLOTS ON A RISER (12)FIGURE 2-1: DIFFERENTIAL REFCLK WAVEFORM (14)FIGURE 2-2: EXAMPLE REFERENCE CLOCK SOURCE TERMINATION (15)FIGURE 2-3: SINGLE-ENDED MEASUREMENT POINTS FOR ABSOLUTE CROSS POINT AND SWING (17)FIGURE 2-4: SINGLE-ENDED MEASUREMENT POINTS FOR DELTA CROSS POINT (17)FIGURE 2-5: SINGLE-ENDED MEASUREMENT POINTS FOR RISE AND FALL TIME MATCHING (18)FIGURE 2-6: DIFFERENTIAL MEASUREMENT POINTS FOR DUTY CYCLE AND PERIOD18 FIGURE 2-7: DIFFERENTIAL MEASUREMENT POINTS FOR RISE AND FALL TIME (18)FIGURE 2-8: DIFFERENTIAL MEASUREMENT POINTS FOR RINGBACK (18)FIGURE 2-9: REFERENCE CLOCK SYSTEM MEASUREMENT POINT AND LOADING (19)FIGURE 2-10: POWER UP (21)FIGURE 2-11: POWER MANAGEMENT STATES (22)FIGURE 2-12: OUT-OF-TOLERANCE THRESHOLD WINDOWS (23)FIGURE 2-13: POWER DOWN (23)FIGURE 2-14: WAKE# RISE AND FALL TIME MEASUREMENT POINTS (31)FIGURE 3-1: PRESENCE DETECT IN A HOT-PLUG ENVIRONMENT (34)FIGURE 4-1: PCI EXPRESS ON THE SYSTEM BOARD (39)FIGURE 4-2: PCI EXPRESS CONNECTOR ON SYSTEM BOARD WITH AN ADD-IN CARD.39 FIGURE 4-3: PCI EXPRESS CONNECTOR ON A RISER CARD WITH AN ADD-IN CARD (40)FIGURE 4-4: LINK DEFINITION FOR TWO COMPONENTS (41)FIGURE 4-5: EXAMPLE INTERCONNECT TERMINATED AT THE CONNECTOR INTERFACE (42)FIGURE 4-6: INSERTION LOSS BUDGETS (43)FIGURE 4-7: JITTER BUDGET (44)FIGURE 4-8: ADD-IN CARD TRANSMITTER PATH COMPLIANCE EYE DIAGRAM (48)FIGURE 4-9: REPRESENTATIVE COMPOSITE EYE DIAGRAM FOR ADD-IN CARD RECEIVER PATH COMPLIANCE (49)FIGURE 4-10: SYSTEM BOARD TRANSMITTER PATH COMPOSITE COMPLIANCE EYE DIAGRAM (50)FIGURE 4-11: TWO-PORT MEASUREMENT MODEL (51)FIGURE 4-12: REPRESENTATIVE COMPOSITE EYE DIAGRAM FOR SYSTEM BOARD RECEIVER PATH COMPLIANCE (52)FIGURE 5-1: CONNECTOR FORM FACTOR (58)FIGURE 5-2: RECOMMENDED FOOTPRINT (59)FIGURE 5-3: ADD-IN CARD EDGE-FINGER DIMENSIONS (60)FIGURE 5-4: ILLUSTRATION OF ADJACENT PAIRS (65)FIGURE 5-5: CONTACT RESISTANCE MEASUREMENT POINTS (66)FIGURE 6-1: STANDARD HEIGHT PCI EXPRESS ADD-IN CARD WITHOUT THE I/O BRACKET (72)FIGURE 6-2: STANDARD HEIGHT PCI EXPRESS ADD-IN CARD WITH THE I/O BRACKET AND CARD RETAINER (73)FIGURE 6-3: ADDITIONAL FEATURE AND KEEPOUTS ON THE X16 GRAPHICS CARD (74)FIGURE 6-4: STANDARD ADD-IN CARD I/O BRACKET (75)FIGURE 6-5: BRACKET DESIGN WITH THE MOUNTING TABS MOUNTED ON THE PRIMARY SIDE OF THE ADD-IN CARD (76)FIGURE 6-6: ADD-IN CARD RETAINER (77)FIGURE 6-7: LOW PROFILE PCI EXPRESS ADD-IN CARD WITHOUT THE I/O BRACKET.78 FIGURE 6-8: LOW PROFILE PCI EXPRESS ADD-IN CARD WITH THE I/O BRACKET (79)FIGURE 6-9: LOW PROFILE I/O BRACKET (80)FIGURE 6-10: EXAMPLE OF A PC SYSTEM IN MICROATX FORM FACTOR (81)FIGURE 6-11: INTRODUCTION OF A PCI EXPRESS CONNECTOR IN A MICROATX SYSTEM (82)FIGURE 6-12: MORE PCI EXPRESS CONNECTORS ARE INTRODUCED ON A MICROATX SYSTEM BOARD (83)FIGURE 6-13: PCI EXPRESS CONNECTOR LOCATION IN A MICROATX SYSTEM WITH ONE PCI EXPRESS CONNECTOR (84)FIGURE 6-14: PCI EXPRESS CONNECTOR LOCATION IN A MICROATX SYSTEM WITH TWO PCI EXPRESS CONNECTORS (85)FIGURE 6-15: CARD ASSEMBLED IN CONNECTOR (86)TablesTABLE 2-1: REFCLCK DC SPECIFICATIONS AND AC TIMING REQUIREMENTS (16)TABLE 2-2: MAXIMUM ALLOWED PHASE JITTER WHEN APPLIED TO FIXED FILTER CHARACTERISTIC (20)TABLE 2-3: AUXILIARY SIGNAL DC SPECIFICATIONS - PERST#, WAKE#, AND SMBUS30 TABLE 2-4: POWER SEQUENCING AND RESET SIGNAL TIMINGS (31)TABLE 4-1: POWER SUPPLY RAIL REQUIREMENTS (35)TABLE 4-2: ADD-IN CARD POWER DISSIPATION (36)TABLE 4-3: ALLOCATION OF INTERCONNECT PATH INSERTION LOSS BUDGET (43)TABLE 4-4: TOTAL SYSTEM JITTER BUDGET (45)TABLE 4-5: ALLOCATION OF INTERCONNECT JITTER BUDGET (45)TABLE 4-6: ALLOWABLE INTERCONNECT LANE-TO-LANE SKEW (47)TABLE 4-7: ADD-IN CARD TRANSMITTER PATH COMPLIANCE EYE REQUIREMENTS..48 TABLE 4-8: ADD-IN CARD MINIMUM RECEIVER PATH SENSITIVITY REQUIREMENTS49 TABLE 5-1: PCI EXPRESS CONNECTORS PINOUT (53)TABLE 5-2: SIGNAL INTEGRITY REQUIREMENTS AND TEST PROCEDURES (63)TABLE 5-3: TEST DURATIONS (66)TABLE 5-4: MECHANICAL TEST PROCEDURES AND REQUIREMENTS (67)TABLE 5-5: END OF LIFE CURRENT RATING TEST SEQUENCE (68)TABLE 5-6: ADDITIONAL REQUIREMENTS (69)TABLE 6-1: ADD-IN CARD SIZES (71)TABLE 6-2: CARD INTEROPERABILITY (87)11. IntroductionThis specification is a companion for the PCI Express Base Specification, Revision 1.1. Its primary focus is the implementation of an evolutionary strategy with the current PCI desktop/server mechanical and electrical specifications. The discussions are confined to ATX or ATX-based form factors.Other form factors, such as PCI Express Mini Card are covered in other separate specifications.51.1. TermsDefinitionsandAdd-in card A card that is plugged into a connector and mounted in a chassisslot.ATX A system board form factor. Refer to the ATX Specification,2.2.Revision.10ATX-based form factor Refers to the form factor that does not exactly conform to theATX specification, but uses the key features of the ATX, such asthe slot spacing, I/O panel definition, etc.Auxiliary signals Signals not required by the PCI Express architecture but necessaryfor certain desired functions or system implementation, for15example, the SMBus signals.Basic bandwidth Contains one PCI Express Lanex1, x4, x8, x16 x1 refers to one PCI Express Lane of basic bandwidth; x4 refers to acollection of four PCI Express Lanes; etc.Down-plugging Plugging a larger Link card into a smaller Link connector; for example, 20plugging a x4 card into a x1 connectorDown-shifting Plugging a PCI Express card into a connector that is not fullyrouted for all of the PCI Express Lanes; for example, plugginga x4 card into a x8 capable connector with only four Lanesroutedbeing25Evolutionary strategy A strategy to develop the PCI Express connector and card formfactors within today’s chassis and system board form factorconstraints.infrastructureHigh bandwidth Supports larger number of PCI Express Lanes, such as a x16 cardconnector.or30Hot-Plug Insertion and/or removal of a card into an active backplane orsystem board as defined in PCI Standard Hot-Plug Controller andSubsystem Specification, Revision. 1.0. No special card support is required.Hot swap Insertion and/or removal of a card into a passive backplane. Thecard must satisfy specific requirements to support Hot swap.5Interoperability Ability to plug a PCI Express card into different Link connectorsand the system works, for example, plugging a x1 PCI ExpressI/O card into a x16 graphics slot.Link A collection of one or more PCI Express LanesLow profile card An add-in card whose height is no more than 68.90 mm10(2.731 inches)microATX An ATX-based system board form factor. Refer to the microATXMotherboard Interface Specification, Revision 1.2.PCI Express Mini Card PCI Express for mobile form factor, similar to Mini PCIPCI Express Lane One PCI Express Lane contains two differential lines for15Transmitter and two differential lines for Receiver. A by-N Linkis composed of N Lanes.sideband signaling A method for signaling events and conditions using physicalsignals separate from signals forming the Link between twocomponents.20Standard height card An add-in card whose height is no more than 111.15 mminches)(4.376Up-plugging Plug a smaller Link card into a larger Link connector; forexample, plugging a x1 card into a x4 connectorwakeup A mechanism used by a component to request the reapplication of25main power when in the L2 Link state. Two such mechanisms aredefined in the PCI Express Base Specification, Revision 1.1: Beacon andWAKE#. This specification requires the use of WAKE# on any add-incard or system board that supports wakeup functionality.Documents1.2. ReferenceThis specification references the following documents:PCI Express Base Specification, Revision 1.1PCI Local Bus Specification, Revision 3.0PCI Express Jitter Modeling5PCI Express Jitter and BERATX Specification, Revision 2.2microATX Motherboard Interface Specification, Revision 1.2SMBus Specification, Revision 2.0JTAG Specification (IEEE1149.1)10PCI Standard Hot-Plug Controller and Subsystem Specification, Revision 1.0Compact PCI Hot Swap SpecificationEIA-364-1000.01: Environmental Test Methodology for Assessing the Performance of Electrical Connectors and Sockets Used in Business Office ApplicationsEIA-364: Electrical Connector/Socket Test Procedures Including Environmental Classifications15Contents1.3. SpecificationThis specification contains the following information:Auxiliary signalsAdd-in card hot insertion and removalPower delivery20Add-in card electrical budgetConnector specificationCard form factors and implementation1.4. ObjectivesThe objectives of this specification are:Support 2.5 Gb/s data rate (per direction) with headroom for future bandwidth increasesEnable Hot-Plug and hot swap where they are neededLeverage desktop and server commonality5Facilitate smooth transitionsAllow co-existence of both PCI and PCI Express add-in cardsNo chassis or other PC infrastructure changesForward looking for future scalabilityExtensible for future bandwidth needs10Allows future evolution of PC architectureMaximize card interoperability for user flexibilityLow cost1.5. Electrical OverviewThe electrical part of this specification covers auxiliary signals, hot insertion and removal, power15delivery, and add-in card interconnect electrical budgets for the evolutionary strategy. The PCIExpress Transmitter and Receiver electrical requirements are specified in the PCI Express BaseSpecification, Revision 1.1.Besides the signals that are required to transmit/receive data on the PCI Express interface, there arealso signals that may be necessary to implement the PCI Express interface in a system environment, 20or to provide certain desired functions. These signals are referred to as the auxiliary signals. They include:Reference clock (REFCLK), must be supplied by the system (see Section 2.1.1)Add-in card presence detect pins (PRSNT1# and PRSNT2#), requiredPERST#, required25JTAG, optionalSMBus, optionalWake (WAKE#), required only if the device/system supports wakeup+3.3Vaux, optionalREFCLK, JTAG, SMBus, PERST#, and WAKE# are described in Chapter 2; +3.3Vaux is30described in Chapter 4; and PRSNT1# and PRSNT2# are described in Chapter 3.Both Hot-Plug and hot swap of PCI Express add-in cards are supported, but their implementation isoptional. Hot-Plug is supported with the evolutionary add-in card form factor. Hot swap issupported with other form factors and will be described in other specifications.To support Hot-Plug, presence detect pins (PRSNT1# and PRSNT2#) are defined in each end of the connectors and add-in cards. Those presence detect pins are staggered on the add-in cards such 5that they are last-mate and first-break, detecting the presence of the add-in cards. Chapter 3discusses the detailed implementation of PCI Express Hot-Plug.Chapter 4 specifies the PCI Express add-in card electrical requirements, which include powerdelivery and interconnect electrical budgets. Power is delivered to the PCI Express add-in cards viaadd-in card connectors, using three voltage rails: +3.3V, +3.3Vaux, and +12V. Note that the10+3.3Vaux voltage rail is not required for all platforms (refer to Section 4.1 for more information on the required usage of 3.3Vaux). The maximum add-in card power definitions are based on the card size and Link widths, and are described in Section 4.2. Chapter 4 describes the interconnectelectrical budgets, focusing on the add-in card loss and jitter requirements.Overview1.6. MechanicalPCI Express can be used in many different applications in desktop, mobile, server, as well as15networking and communication equipment. Consequently, multiple variations of form factors and connectors will exist to suit the unique needs of these different applications.Figure 1-1 shows an example of the vertical edge-card PCI Express connector to be used in ATX or ATX-based systems. There will be a family of such connectors, containing one to 16 PCI ExpressLanes. The basic bandwidth (BW) version supports one PCI Express Lane and could be used as the 20replacement for the PCI connector. The high bandwidth version will support 16 PCI Express Lanes and will be used for applications that require higher bandwidth, such as graphics.OM14739Figure 1-1: Vertical Edge-Card ConnectorVertical edge card connectors also have applications in the server market segment. Figure 1-2 shows an example of a server configuration using a PCI Express riser card.OM14740Figure 1-2: Example Server I/O Board with PCI Express Slots on a Riser Mobile applications require a right angle edge card connector. The definition of such a connector will be covered in a separate document.For certain server and network applications there may also be a need for a Compact PCI-like PCI Express connector, or other backplane-type PCI Express connectors.PCI Express cable connectors may also be needed for within-system applications, both internally 5(inside the chassis) and externally (outside the chassis).While the reality of multiple variations of PCI Express connectors and form factors is recognized, no attempt will be made to define every possible PCI Express connector and form factor variation in this specification. They will be defined later as the need arises in other specifications. Thisspecification, instead, focuses on the vertical edge card PCI Express connectors and form factor 10requirements by covering the following:Connector mating interfaces and footprintsElectrical, mechanical, and reliability requirements of the connectors, including the connector testing proceduresAdd-in card form factors15Connector and add-in card locations, as well as keep-outs on a typical desktop system board (ATX/microATX form factor)Connector definitions and requirements are addressed in Chapter 5 and add-in card form factors and implementation are discussed in Chapter 6.2. Auxiliary SignalsThe auxiliary signals are provided on the connector to assist with certain system level functionality or implementation. These signals are not required by the PCI Express architecture. The high-speed signal voltage levels are compatible with advanced silicon processes. The optional low speed signals are defined to use the +3.3V or +3.3Vaux supplies, as they are the lowest common voltage available. 5Most ASIC processes have high voltage (thick gate oxide) I/O transistors compatible with 3.3 V. Use of the 3.3 V supply allows PCI Express signaling to be used with existing control bus structures, avoiding a buffered set of signals and bridges between the buses.The PCI Express connector and add-in card interfaces support the following auxiliary signals:REFCLK-/REFCLK+ (required): low voltage differential signals.10 PERST# (required): indicates when the applied main power is within the specified tolerance andstable. PERST# goes inactive after a delay of T PVPERL time from the power rails achieving specified tolerance on power up.WAKE#: an open-drain, active low signal that is driven low by a PCI Express function to re-activate the PCI Express Link hierarchy’s main power rails and reference clocks. It is required 15on any add-in card or system board that supports wakeup functionality compliant with this specification.SMBCLK (optional): the SMBus interface clock signal. It is an open-drain signal. SMBDAT (optional): the SMBus interface address/data signal. It is an open-drain signal. JTAG (TRST#, TCLK, TDI, TDO, and TMS) (optional): the pins to support IEEE Standard201149.1, Test Access Port and Boundary Scan Architecture (JTAG). They are included as an optional interface for PCI Express devices. IEEE Standard 1149.1 specifies the rules and permissions for designing an 1149.1-compliant IC.PRSNT1# (required): Add-in card presence detect pin. See Chapter 3 for a detailed description.PRSNT2# (required): Add-in card presence detect pin. See Chapter 3 for a detailed description.25Note that the SMBus interface pins are collectively optional for both the add-in card and the system board. If the optional management features are implemented, SMBCLK and SMBDAT are both required. Similarly, the JTAG pins are collectively optional. If this test mode is implemented, all the JTAG pins are required. Refer to the PCI Local Bus Specification, Revision. 3.0, Section 4.3.3 for additional system requirements related to these signals.3022.1. Reference Clock2.1.1. Low Voltage Swing, Differential ClocksTo reduce jitter and allow for future silicon fabrication process changes, low voltage swing,differential clocks are being used, as illustrated in Figure 2-1. The nominal single-ended swing for each clock is 0 to 0.7 V and a nominal frequency of 100 MHz ±300 PPM. The clock has a defined 5crossover voltage range and monotonic edges through the input threshold regions as specified in Chapter 4.REFCLK–REFCLK+OM14741Figure 2-1: Differential REFCLK WaveformThe reference clock pair is routed point-to-point to each connector from the system boardaccording to best-known clock routing rules. The reference clock distribution to all devices must be matched to within 15 inches on the system board. The phase delay between the transmitter and 10receiver clock is assumed to be less than 10 ns. The combination of the maximum reference clock mismatch and the maximum channel length will contribute approximately 7-8 ns and the remaining time is allocated to the difference in the insertion delays of the Tx and Rx devices. The routing of each signal in any given clock pair between the clock source and the connector must be well matched in length (< 0.005 inch) and appropriately spaced away from other non-clock signals to 15avoid excessive crosstalk.The add-in card is not required to use the reference clock on the connector. However, the add-in card is required to maintain the 600-ppm data rate matching specified in Section 4.3.1.1 of the PCI Express Base Specification, Revision 1.1.Any terminations required by the clock are to be on the system board. An example termination 20topology for a current-mode clock generator is shown in Figure 2-2. EMI emissions will be reduced if clocks to open sockets are shut down at the clock source. The method for detecting the presence of a card in a slot and controlling the clock gating is platform specific and is not covered in this specification.A-0439Figure 2-2: Example Reference Clock Source Termination Termination on the add-in card is allowed, but is not covered by the specifications in Section 2.1.3.While the same measurement techniques can be used as specified in that section, receivertermination will reduce the nominal swing and rise and fall times by half. The low input swing and low slew rates need to be validated against the clock receiver requirements as they can causeexcessive jitter in some clock input buffer designs.5The reference clock timings are based on nominal 100 Ω, differential pair routing withapproximately 5-mil trace widths. This timing budget allows for a maximum add-in card tracelength of 4.0 inches. No specific trace geometry, however, is explicitly defined in this specification.2.1.2. Spread Spectrum Clocking (SSC)The reference clocks may support spread spectrum clocking. Any given system design may or may 10not use this feature due to platform-level timing issues. The minimum clock period cannot beviolated. The preferred method is to adjust the spread technique to not allow for modulation above the nominal frequency. This technique is often called “down-spreading.” The requirements for spread spectrum modulation rate and magnitude are given in the PCI Express Base Specification,Revision 1.1.152.1.3. REFCLK AC SpecificationsAll specifications in Table 2-1 are to be measured using a test configuration as described in Note 11 with a circuit as shown in Figure 2-9.Table 2-1: REFCLCK DC Specifications and AC Timing Requirements100 MHz Input Unit Note Symbol ParameterMin MaxRise Edge Rate Rising Edge Rate 0.6 4.0 V/ns 2, 3Fall Edge Rate Falling Edge Rate 0.6 4.0 V/ns 2, 3V IH Differential Input High Voltage +150 mV 2V IL Differential Input Low Voltage -150 mV 2V CROSS Absolute crossing point voltage +250 +550 mV 1,4,5V CROSS DELTA Variation of V CROSS over all risingclock edges+140 mV 1,4,9V RB Ring-back Voltage Margin -100 +100 mV 2,12 T STABLE Time before V RB is allowed 500 ps 2,12 T PERIOD AVG Average Clock Period Accuracy -300 +2800 ppm 2,10,13T PERIOD ABS Absolute Period (including Jitterand Spread Spectrum)9.847 10.203 ns 2,6T CCJITTER Cycle to Cycle jitter 150 ps 2 V MAX Absolute Max input voltage +1.15 V 1,7 V MIN Absolute Min input voltage - 0.3 V 1,8 Duty Cycle Duty Cycle 40 60 % 2Rise-Fall Matching Rising edge rate (REFCLK+) tofalling edge rate (REFCLK-)matching20 % 1,14Z C-DC Clock source DC impedance 40 60 Ω1,11Notes:1. Measurement taken from single ended waveform.52. Measurement taken from differential waveform.3. Measured from -150 mV to +150 mV on the differential waveform (derived from REFCLK+ minusREFCLK-). The signal must be monotonic through the measurement region for rise and fall time.The 300 mV measurement window is centered on the differential zero crossing. See Figure 2-7.4. Measured at crossing point where the instantaneous voltage value of the rising edge of REFCLK+10equals the falling edge of REFCLK-. See Figure 2-3.5. Refers to the total variation from the lowest crossing point to the highest, regardless of which edgeis crossing. Refers to all crossing points for this measurement. See Figure 2-3.6. Defines as the absolute minimum or maximum instantaneous period. This includes cycle to cyclejitter, relative PPM tolerance, and spread spectrum modulation. See Figure 2-6.157. Defined as the maximum instantaneous voltage including overshoot. See Figure 2-3. 8. Defined as the minimum instantaneous voltage including undershoot. See Figure 2-3.9. Defined as the total variation of all crossing voltages of Rising REFCLK+ and Falling REFCLK-.This is the maximum allowed variance in VCROSS for any particular system. See Figure 2-4. 10. Refer to Section 4.3.2.1 of the PCI Express Base Specification, Revision 1.1 for information5regarding PPM considerations.11. System board compliance measurements must use the test load card described in Figure 2-9.REFCLK+ and REFCLK- are to be measured at the load capacitors CL. Single ended probes must be used for measurements requiring single ended measurements. Either single ended probes with math or differential probe can be used for differential measurements. Test load C L = 2 pF.1012. T STABLE is the time the differential clock must maintain a minimum ±150 mV differential voltage afterrising/falling edges before it is allowed to droop back into the V RB ±100 mV differential range. See Figure 2-8.13. PPM refers to parts per million and is a DC absolute period accuracy specification. 1 PPM is1/1,000,000thof 100.000000 MHz exactly or 100 Hz. For 300 PPM then we have a error budget of 15100 Hz/PPM * 300 PPM = 30 kHz. The period is to be measured with a frequency counter with measurement window set to 100 ms or greater. The ±300 PPM applies to systems that do not employ Spread Spectrum or that use common clock source. For systems employing SpreadSpectrum there is an additional 2500 PPM nominal shift in maximum period resulting from the 0.5% down spread resulting in a maximum average period specification of +2800 PPM2014. Matching applies to rising edge rate for REFCLK+ and falling edge rate for REFCLK-. It ismeasured using a ±75 mV window centered on the median cross point where REFCLK+ rising meets REFCLK- falling. The median cross point is used to calculate the voltage thresholds the oscilloscope is to use for the edge rate calculations. The Rise Edge Rate of REFCLK+ should be compared to the Fall Edge Rate of REFCLK-, the maximum allowed difference should not exceed 2520% of the slowest edge rate. See Figure 2-5.REFCLK–A-0437REFCLK+V MAX = 1.15 VV MIN = -0.30 VV CROSS MAX = 550 mV V CROSS MIN = 250 mVFigure 2-3: Single-Ended Measurement Points for Absolute Cross Point and SwingREFCLK–A-0438REFCLK+VFigure 2-4: Single-Ended Measurement Points for Delta Cross Point。

夜叉AX4 4-流量AX3000无线路由器数据表说明书