MC1DU128NCFC-0QC00中文资料

MC1DU128NDVA-0QC00中文资料

MultiMediaCard SpecificationVersion : Ver. 0.9Date 4 – June - 2004Samsung Electronics Co., LTDSemiconductor Flash Memory Product Planning & Applications1 Introduction to the MultiMediaCard ----------------------------------------------------------- 51.1 System Features ----------------------------------------------------------------------------------------- 5-------------------------------------------------------------------------------------- 51.2 ProductModel2 Function Description ------------------------------------------------------------------------------- 72.1 Flash Technology Independence ------------------------------------------------------------------ 72.2 Defect and Error Management --------------------------------------------------------------------- 72.3 Endurance ----------------------------------------------------------------------------------------------- 72.4 Automatic Sleep Mode ------------------------------------------------------------------------------- 72.5 Hot Insertion -------------------------------------------------------------------------------------------- 82.6 MultiMediaCard Mode -------------------------------------------------------------------------------- 82.6.1 MultiMediaCard Standard Compliance ----------------------------------------------------------- 82.6.2 Negotiation Operation Conditions ----------------------------------------------------------------- 82.6.3 Card Acquisition and Identification ---------------------------------------------------------------- 82.6.4 Card Status ---------------------------------------------------------------------------------------------- 82.6.5 Memory Array Partitioning --------------------------------------------------------------------------- 92.6.6 Read and Write Operations ------------------------------------------------------------------------- 92.6.7 Data Transfer Rate ------------------------------------------------------------------------------------102.6.8 Data Protection in the Flash Card -----------------------------------------------------------------10-----------------------------------------------------------------------------------------------------10 2.6.9 Erase2.6.10 Write Protection ----------------------------------------------------------------------------------------102.6.11 Copy Bit ------------------------------------------------------------------------------------------------- 102.6.12 The CSD Register ------------------------------------------------------------------------------------ 112.7 SPI Mode ----------------------------------------------------------------------------------------------- 112.7.1 Negotiating Operation Conditions ---------------------------------------------------------------- 112.7.2 Card Acquisition and Identification --------------------------------------------------------------- 112.7.3 Card Status --------------------------------------------------------------------------------------------- 112.7.4 Memory Array Partitioning -------------------------------------------------------------------------- 112.7.5 Read and Write Operations ------------------------------------------------------------------------- 112.7.6 Data Transfer Rate ------------------------------------------------------------------------------------ 112.7.7 Data Protection in the MultiMediaCard ----------------------------------------------------------- 1212-----------------------------------------------------------------------------------------------------2.7.8 Erase2.7.9 Write Protection ---------------------------------------------------------------------------------------- 123 Product Specifications ----------------------------------------------------------------------------- 133.1 Recommended Operating Conditions ------------------------------------------------------------------------- 133.2 Operating Characteristis ----------------------------------------------------------------- 143.3 System Environmental Specifications ----------------------------------------------------------------- 153.4 System Reliability and Maintenance -------------------------------------------------------------- 153.5 Physical Specifications ------------------------------------------------------------------------------- 164 MultiMediaCard Interface Description --------------------------------------------------------- 174.1 Pin Assignments in MultiMediaCard Mode ------------------------------------------------------- 174.2 Pin Assignments in SPI Mode ---------------------------------------------------------------------- 184.3 MultiMediaCard Bus Topology ---------------------------------------------------------------------- 184.4 SPI Bus Topology -------------------------------------------------------------------------------------------------- 194.4.1 SPI Interface Concept ------------------------------------------------------------------------------------------- 194.4.2 SPI Bus Topology ------------------------------------------------------------------------------------------------ 1920------------------------------------------------------------------------------------------------- 4.5 Registers4.5.1 Operation Condition Register (OCR) ---------------------------------------------------------------------------204.5.2 Card Identification (CID) ------------------------------------------------------------------------------214.5.3 Relative Card Address (RCA) ----------------------------------------------------------------------- 21 4.5.4 Card Specific Data (CSD) ---------------------------------------------------------------------------- 22 4.6 MultiMediaCard Communication -------------------------------------------------------------------- 3030----------------------------------------------------------------------------------------------- 4.6.1 Commands4.7 Read, Write and Erase Time-out Conditions ----------------------------------------------------- 33 4.8 Card Identification Mode ------------------------------------------------------------------------------ 34 4.8.1 Operating Voltage Range Validation --------------------------------------------------------------- 35 4.9 Data Transfer Mode ------------------------------------------------------------------------------------ 35 4.9.1 Block Read ----------------------------------------------------------------------------------------------- 37 4.9.2 Block Write ----------------------------------------------------------------------------------------------- 3738------------------------------------------------------------------------------------------------------ 4.9.3 Erase4.9.4 Write Protect Management -------------------------------------------------------------------------- 38 4.9.5 Card Lock/Unlock Operation ------------------------------------------------------------------------ 38----------------------------------------------------------------------------------------------- 41 4.9.6 Responses4.9.7 Status ------------------------------------------------------------------------------------------------------ 42 4.9.8 Command Response Timing ------------------------------------------------------------------------ 4448 4.9.9 Reset------------------------------------------------------------------------------------------------------ 4.10 SPI Communication ----------------------------------------------------------------------------------- 49 4.10.1 Mode Selection ----------------------------------------------------------------------------------------- 49 4.10.2 Bus Transfer Protection ------------------------------------------------------------------------------ 49 4.10.3 Data Read Overview ---------------------------------------------------------------------------------- 50 4.10.4 Data Write Overview ---------------------------------------------------------------------------------- 51 4.10.5 Erase and Write Protect Management ----------------------------------------------------------- 52 4.10.6 Reading CID/CSD Registers ------------------------------------------------------------------------ 53 4.10.7 Reset Sequence --------------------------------------------------------------------------------------- 53 4.10.8 Error Conditions ---------------------------------------------------------------------------------------- 53 4.10.9 Memory Array Partitioning --------------------------------------------------------------------------- 53 4.10.10 Card Lock/Unlock -------------------------------------------------------------------------------------- 53 4.10.11 Commands ----------------------------------------------------------------------------------------------- 54 4.10.12 Responses ----------------------------------------------------------------------------------------------- 56 4.10.13 Data Tokens --------------------------------------------------------------------------------------------- 58 4.10.14 Data Error Token --------------------------------------------------------------------------------------- 59 4.10.15 Clearing Status Bits ------------------------------------------------------------------------------------ 60 4.11 SPI Bus Timing ----------------------------------------------------------------------------------------- 61 4.12 Error Handling ------------------------------------------------------------------------------------------ 64 4.12.1 Error Correction Code (ECC) ----------------------------------------------------------------------- 64 4.12.2 Cyclic Redundancy Check (CRC) ----------------------------------------------------------------- 642 Function Description2.1 Flash Technology IndependenceThe 512 byte sector size of the MultiMediaCard is the same as that in an IDE magnetic disk drive. To write or read a sector (or multiple sectors), the host computer software simply issues a Read or Write command to the MultiMediaCard. This command contains the address and the number of sectors to write/read. The host software then waits for the command to complete. The host software does not get involved in the details of how the flash memory is erased, programmed or read. This is extremely important as flash devices are expected to get more and more complex in the future. Because the MultiMediaCard uses an intelligent on-board controller, the host system software will not require changing as new flash memory evolves. In other words, systems that support the MultiMediaCard today will be able to access future MultiMediaCards built with new flash technology without having to update or change host software.2.2 Defect and Error ManagementMultiMediaCards contain a sophisticated defect and error management system. This system is analogous to the systems found in magnetic disk drives and in many cases offers enhancements. For instance, disk drives do not typically perform a read after write to confirm the data is written correctly because of the performance penalty that would be incurred. MultiMediaCards do a read after write under margin conditions to verify that the data is written correctly (except in the case of a Write without Erase Command). In the rare case that a bit is found to be defective, MultiMediaCards replace this bad bit with a spare bit within the sector header. If necessary, MultiMediaCards will even replace the entire sector with a spare sector. This is completely transparent to the host and does not consume any user data space.The MultiMediaCards soft error rate specification is much better than the magnetic disk drive specification. In the extremely rare case a read error does occur, MultiMediaCards have innovative algorithms to recover the data. This is similar to using retries on a disk drive but is much more sophisticated. The last line of defense is to employ powerful ECC to correct the data. If ECC is used to recover data, defective bits are replaced with spare bits to ensure they do not cause any future problems.These defect and error management systems coupled with the solid-state construction give MultiMediaCards unparalleled reliability2.3 EnduranceMultiMediaCards have an endurance specification for each sector of 1,000,000 writes (reading a logical sector is unlimited). This is far beyond what is needed in nearly all applications of MultiMediaCards. Even very heavy use of the MultiMediaCard in cellular phones, personal communicators, pagers and voice recorders will use only a fraction of the total endurance over the typical device’s five year lifetime. For instance, it would take over 100 years to wear out an area on the MultiMediaCard on which a files of any size (from 512 bytes to capacity) was rewritten 3 times per hour, 8 hours a day, 365 days per year.With typical applications the endurance limit is not of any practical concern to the vast majority of users.2.4 Automatic Sleep ModeAn important feature of the MultiMediaCard is automatic entrance and exit from sleep mode. Upon completion of an operation, the MultiMediaCard will enter the sleep mode to conserve power if no further commands are received within 5 msec The host does not have to take any action for this to occur. In most systems, the MultiMediaCard is in sleep mode except when the host is accessing it, thus conserving power. When the host is ready to access the MultiMediaCard and it is in sleep mode, any command issued to the MultiMediaCard will cause it to exit sleep and respond. The host does not have to issue a reset first. It may do this if desired, but it is not needed. By not issuing the reset, performance is improved through the reduction of overhead.2.5 Hot InsertionSupport for hot insertion will be required on the host but will be supported through the connector. Connector manufacturers will provide connectors that have power pins long enough to be powered before contact is made with the other pins. Please see connector data sheets for more details. This approach is similar to that used in PCMCIA to allow for hot insertion. This applies to both MultiMediaCard and SPI modes.2.6 MultiMediaCard Mode2.6.1 MultiMediaCard Standard ComplianceThe MultiMediaCard is fully compliant with MultiMediaCard standard specification V3.31.The structure of the Card Specific Data (CSD) register is compliant with CSD structure V1.2.2.6.2 Negotiating Operation ConditionsThe MultiMediaCard supports the operation condition verification sequence defined in the MultiMediaCard standard specifications. The MultiMediaCard host should define an operating voltage range that is not supported by the MultiMediaCard. It will put itself in an inactive state and ignore any bus communication. The only way to get the card out of the inactive state is by powering it down and up again. In addition the host can explicitly send the card to the inactive state by using the GO_INACTIVE_STATE command.2.6.3 Card Acquisition and IdentificationThe MultiMediaCard bus is a single master (MultiMediaCard host) and multi-slaves (cards) bus. The host can query the bus and find out how many cards of which type are currently connected. The MultiMediaCard’s CID register is pre-programmed with a unique card identification number which is used during the acquisition and identification procedureIn addition, the MultiMediaCard host can read the card’s CID register using the READ_CID MultiMediaCard command. The CID register is programmed during the MultiMediaCard testing and formatting procedure, on the manufacturing floor. The MultiMediaCard host can only read this register and not write to it.2.6.4 Card StatusMultiMediaCard status is stored in a 32 bit status register which is sent as the data field in the card respond to host commands. Status register provides information about the card’s current state and completion codes for the last host command. The card status can be explicitly read (polled) with the SEND_STATUS command.2.6.7 Data Protection in the Flash CardEvery sector is protected with an Error Correction Code (ECC). The ECC is generated (in the memory card) when the sectors are written and validated when the data is read. If defects are found, the data is corrected prior to transmission to the host.The MultiMediaCard can be considered error free and no additional data protection is needed. However, if an application uses additional, external, ECC protection, the data organization is defined in the user writeable section of the CSD register2.6.8 EraseThe smallest erasable unit in the MultiMediaCard is a erase group. In order to speed up the erase procedure, multiple erase groups can be erased in the same time. The erase operation is divided into two stages.Tagging - Selecting the Sectors for ErasingTo facilitate selection, a first command with the starting address is followed by a second command with the final address, and all erase groups within this range will be selected for erase.Erasing - Starting the Erase ProcessTagging can address erase groups. An arbitrary selection of erase groups may be erased at one time. Tagging and erasing must follow a strict command sequence (refer to the MultiMediaCard standard specification for details).2.6.9 Write ProtectionThe MultiMediaCard erase groups are grouped into write protection groups. Commands are provided for limiting and enabling write and erase privileges for each group individually. The current write protect map can be read using SEND_WRITE_PROT command.In addition two, permanent and temporary, card levels write protection options are available.Both can be set using the PROGRAM_CSD command (see below). The permanent write protect bit, once set, cannot be cleared.The One Time Programmable (OTP) characteristic of the permanent write protect bit is implemented in the MultiMediaCard controller firmware and not with a physical OTP cell.2.6.10 Copy BitThe content of an MultiMediaCard can be marked as an original or a copy using the copy bit in the CSD register. Once the Copy bit is set (marked as a copy) it cannot be cleared.The Copy bit of the MultiMediaCard is programmed (during test and formatting on the manufacturing floor) as a copy. The MultiMediaCard can be purchased with the copy bit set (copy) or cleared, indicating the card is a master.The One Time Programmable (OTP) characteristic of the Copy bit is implemented in the MultiMediaCard controller firmware and not with a physical OTP cell.2.6.11 The CSD RegisterAll the configuration information of the MultiMediaCard is stored in the CSD register. The MSB bytes of the register contain manufacturer data and the two least significant bytes contains the host controlled data - the card Copy and write protection and the user ECC register.The host can read the CSD register and alter the host controlled data bytes using the SEND_CSD and PROGRAM_CSD commands.2.7 SPI ModeThe SPI mode is a secondary (optional) communication protocol offered for MultiMediaCard. This mode is a subset of the MultiMediaCard protocol, designed to communicate with an SPI channel, commonly found in Motorola’s (and lately a few other vendors’) microcontrollers.2.7.1 Negotiating Operation ConditionsThe operating condition negotiation function of the MultiMediaCard bus is not supported in SPI mode. The host must work within the valid voltage range (2.7 to 3.6 volts) of the card.2.7.2 Card Acquisition and IdentificationThe card acquisition and identification function of the MultiMediaCard bus is not supported in SPI mode. The host must know the number of cards currently connected on the bus. Specific card selection is done via the CS signal.2.7.3 Card StatusIn SPI mode only 16 bits (containing the errors relevant to SPI mode) can be read out of the MultiMediaCard status register.2.7.4 Memory Array PartitioningMemory partitioning in SPI mode is equivalent to MultiMediaCard mode. All read and write commands are byte addressable.2.7.5 Read and Write OperationsIn SPI mode, only single block read/write mode is supported.2.7.6 Data Transfer RateIn SPI mode only block mode is supported. The typical access time (latency) for each data block, in read operation, is 1.5mS. The write typical access time (latency) for each data block, in read operation, is 1.5mS. The write block operation is done in handshake mode. The card will keep DataOut line low as long as the write operation is in progress and there are no write buffers available.2.7.7 Data Protection in the MultiMediaCardSame as for the MultiMediaCard mode.2.7.8 EraseSame as in MultiMediaCard mode2.7.9 Write ProtectionSame as in MultiMediaCard modeFigure 3-1 Timing Diagram of Data Input and Output3.5 Physical SpecificationsDimensions of Normal MMC(24mm x 32mm x 1.4mm)Dimensions of RS-MMC(24mm x 18mm x 1.4mm)rising and falling edges). If the host does not allow the switchable R OD implementation, a fix R CMD can be used. Consequently the maximum operating implementation, a fix R CMD can be used. Consequently the maximum operating frequency in the open drain mode has to be reduced in this case.4.4 SPI Bus Topology4.4.1 SPI Interface ConceptThe Serial Peripheral Interface (SPI) is a general-purpose synchronous serial interface originally found on certain Motorola micro-controllers. The MultiMediaCard SPI interface is compatible with SPI hosts available on the market. As any other SPI device the MultiMediaCard SPI channel consists of the following 4 signals:- CS : Host to card chip select signal- CLK : Host to card clock signal- DataIn : Host to card data signal- DataOut : Card to host data signalAnother SPI common characteristic, which is implemented in the MultiMediaCard card as well, is byte transfers. All data tokens are multiples of 8 bit bytes and always byte aligned to the CS signal. The SPI standard defines the physical link only and not the complete data transfer protocol. The MultiMediaCard uses a subset of the MultiMediaCard protocol and command set.4.4.2 SPI Bus TopologyThe MultiMediaCard card identification and addressing algorithms are replaced by hardware Chip Select (CS) signal. There are no broadcast commands. A card (slave) is selected, for every command, by asserting (active low) the CS signal (see Figure 4-3). The CS signal bust is continuously active for the duration of the SPI transaction (command, response and data). The only exception is card-programming time. At this time the host can de-assert the CS signal without affecting the programming process. The bi-directional CMD and DAT lines are replaced by unidirectional dataIn and dataOut signals. This eliminates the ability of executing commands while data is being read or written and, therefore, eliminates the sequential and multi block read/write operations. The SPI channel supports only single block read/write.Figure 4-3 SPI Bus SystemReadThe read access time is defined as the sum of the two times given by the CSD parameters TAAC and NSAC (refer to Table “Card Specific Data (CSD)”). These card parameters define the typical delay between the end bit of the read command and the start bit of the data block. This number is card dependent and should be used by the host to calculate throughput and the maximal frequency for stream read.WriteThe R2W_FACTOR field in the CSD is used to calculate the typical block program time obtained by multiplying the read access time by this factor. It applies to all write/erase commands (e.g. SET(CLEAR)_WRITE_PROTECT, PROGRAM_CSD(CID) and the block write commands). It should be used by the host to calculate throughput.EraseThe duration of an erase command will be (order of magnitude) the number of sectors to be erased multiplied by the block write delay.4.8 Card Identification ModeAll the data communication in the card identification mode uses only the command line (CMD). MultiMediaCard State Diagram (Card Identification Mode)Figure 4-2 MultiMediaCard State Diagram (Card Identification Mode)The host starts the card identification process in open drain mode with the identification clock rate f OD(generated by a push pull driver stage). The open drain driver stages on the CMD line allow the parallel card operation during card identification. After the bus is activated the host will request the cards to send their valid operation conditions with the command SEND_OP_COND (CMD1). Since the bus is in open drain mode, as long as there is more than one card with operating conditions restrictions, the host gets in the response to the CMD1 a “wired or” operation condition restrictions of those cards. The host then must pick a common denominator for operation and notify the application that cards with out of range parameters (from the host perspective) are connected to the bus. Incompatible cards go into Inactive State (refer to also Chapter “Operating Voltage Range Validation”). The busy bit in the CMD1 response can be used by a card to tell the host that it is still working on its power-up/reset procedure (e.g. downloading the register information from memory field) and is not ready yet for communication. In this case the host must repeat CMD1 until the busy bit is cleared. After an operating mode is established, the host asks all cards for their unique card identification (CID) number with the broadcast command ALL_SEND_CID (CMD2).All not already identified cards (i.e. those which are in Ready State) simultaneously start sending their CID numbers serially, while bit-wise monitoring their outgoing bitstream. Those cards, whose outgoing CID bits do not match the corresponding bits on the command line in any one of the bit periods, stop sending their CID immediately and must wait for the next identification cycle (cards stay in the Ready State). There should be only one card which successfully sends its full CID-number to the host. This card then goes into the Identification State. The host assigns to this card (using CMD3, SET_RELATIVE_ADDR) a relative card address (RCA, shorter than CID), which will be used to address the card in future communication (faster than with the CID). Once the RCA is received the card transfers to the Standby State and does not react to further identification cycles. The card also switches the output drivers from the open-drain to the push-pull mode in this state. The host repeats the identification process as long as it receives a response (CID) to its identification command (CMD2). When no card responds to this command, all cards have been identified. The time-out condition to recognize this, is waiting for the start bit for more than 5 clock periods after sending CMD24.8.1 Operating Voltage Range ValidationThe MultiMediaCard standards operating range validation is intended to support reduced voltage range MultiMediaCards. The MultiMediaCard supports the range of 2.7 V to 3.6V supply voltage. So the MultiMediaCard sends a R3 response to CMD1 which contains an OCR value of 0x80FF8000 if the busy flag is set to “ready” or 0x00FF8000 if the busy flag is active (refer to Chapter “Responses”). By omitting the voltage range in the command, the host can query the card stack and determine the common voltage range before sending out-of-range cards into the Inactive State. This bus query should be used if the host is able to select a common voltage range or if a notification to the application of non usable cards in the stack is desired. Afterwards, the host must choose a voltage for operation and reissue CMD1 with this condition sending incompatible cards into the Inactive State.4.9 Data Transfer ModeWhen in Standby State, both CMD and DAT lines are in the push-pull mode. As long as the content of all CSD registers is not known, the f PushPull clock rate is equal to the slow f OpenDrain clock rate. SEND_CSD (CMD9) allows the host to get the Card Specific Data (CSD register), e.g. ECC type, block length, card storage capacity, maximum clock rate etc..。

第2章MC9S12DG128的结构与工作原理

2.1 MC9S12DG128的内部结构

2.1.1 CPU12内核(Star Core)

(2)间址/变址寄存器(Index Register) X、Y

❖ CPU12内部有两个16位地址寄存器IX和IY,称为间接寻址寄 存器,简称间址寄存器或变址寄存器。一般情况下作为指针 寄存器,用于多种寻址方式下的地址计算,也可用于临时存 放数据或参与一些运算,只能按照16位方式访问。

❖ 若把一个16位数据存入累加器D中,则高8位在A寄存器中,低8位在B 寄存器中。与此相对应,若把D寄存器中的一个16位数据存入存储器, 则高8位在存储器的低位地址,低8位在存储器的高位地址。

❖ 注意,任何Motorola (Freescale)公司独立设计的16位、32位CPU中, 寄存器与存储器字节的对应关系都是高位数据存放于低位地址,低位数 据占用高位地址,这与Intel公司的CPU数据存放格式正好相反。

2.1 MC9S12DG128的内部结构

2.1.1 CPU12内核(Star Core)

❖ SP主要用于堆栈管理,用于中断和子程序调用时保存系统地址信息,也 可以存储临时信息,一般不做他用。

❖ 在不影响其内容的前提下,也可替补用作所有变址寻址方式下的变址寄 存器,通常不参与运算。

❖ 惟一例外的是,在符号扩展指令中用作目的寄存器。此外,还具有自身 的加、减1指令。

(Program State Word),但不同的是,它还可以参与控制CPU的行为。 ❖ 条件码寄存器中各位的定义:

CCR中的各位包括两部分: ➢5个算术特征位(Arithmetic Flag Bit) ,即H、N、Z、V、C,它们反映上一条指令执 行结果的特征(状态); ➢3个MCU控制位,即中断屏蔽位X、I和STOP指令控制位,这3位通常由软件设定, 以控制CPU的行为。复位后,X、I两位默认状态为1,屏蔽系统中断。CCR是真正的 专用寄存器,除了C、H位以外,其他各位不参与任何运算。

六讲MCS单片机IO接口和功能模块

使用PORTJ中断口功能旳例子,本例旳原理是: 设置A口为输出口,PTA旳第6脚跟PTJ旳第6脚 硬件相连,PTB输出,用来控制8个LED灯, PTJ开中断,而且设置为上升沿触发。首先PTA 初始化为0,PTB为0xFF,此时等灭。在大循环 冲设置PTA第6位为高电平,产生中断,灯低4 个亮,高4个不亮。使用单步运营查看效果。

数据旳格式,一共有8种情况。 SCAN:连续转换队列旳模式。此位定义了A/D 转换是连续进行

还是只进行一次。1=连续队列转换;0=单次队列转换。 MULT:当这位为0 时,ATD 旳队列控制器只从指定旳输入通道

进行采样,能够使用ATDCTL5寄存器中旳CC、CB 和CA 三位来 指定需要采样旳模拟量输入通道。当这位为1 时,则对多种旳通 道进行采样,每次采样旳通道数量由S8C、S4C、S2C 和S1C 控制 位来指定,第一种采样通道由CC、CB 和CA 控制位来指定,其 他采样通道由通道选择码CC、CB 和CA 旳增长来决定。 CC、CB、CA:模拟输入通道选择码。和MULT配合使用。

设置方向寄存器(DDRx)为输入(0X00) 随时读取I/O口旳数据寄存器(PORTx)

I/O口作为输出使用

设置方向寄存器(DDRx)为输出(0XFF) 设置驱动能力寄存器(非必须) 拉电阻选择(非必须) 随时写入I/O口数据寄存器(PORTx)

1、通用I/O接口

I/O口作为外部中断接受使用

MC9S12DG128B单片机I/O口

PORTA

连接按键

PORTB

连接发光二极管

PORTE

特殊功能

PORTJ

中断输入,没有PJ0-PJ5

PORTP

中断输入,没有PP6

PORTM

ATmega128L单片机的Micro+SD卡读写

机开始所有的总线传输。数据从单片机的MOSI引脚同 步输入Micro SD卡的DI引脚,并由Micro SD卡的D0线 同步输入单片机的MISO引脚,数据在CLK信号的上升 沿同步输入和输出。在每个数据传输的结尾还必须提供 8个额外的时钟,以允许Micro SD卡完成任何未完结的 操作。由于Micro SD卡的电压为3.3 V,所以选择需要支 持3.3 V的I/O端口输出的ATmegal28L单片机。另 外,使用SPI模式时,为了防止在无卡接人或卡驱动器呈 高阻态时总线悬空,根据SD卡规范,这些信号需要在主 机端用10 kfl ̄lOO kQ的上拉电阻。其硬件连接电路如图 1所示。

模式选择信息,因为卡选择(CS)引脚在该命令和其他所

有SPI命令传送过程中都保持为低电平。Micro SD卡以

Rl作为响应。空闲状态位被置为高电平,此时Micro SD

卡进入空闲状态,此阶段的SPI时钟频率不能超过400

kHz(将SPCR寄存器设置为0x53)。Micro SD卡进入

SPI模式后,主机应该先发一条初始化指令CMDl。此时

//打开文件

if(FAT_Delltem(&FileInfo))return 1,//删除文件记录项

return 0;

}

结语

本设计将Micro SD卡的存储方式应用到电脑横机控 制系统中,简化了花型文件数据存储设计,减小了系统的 尺寸,提高了系统的可靠性,使得花型文件的读出和存取 简单易行,裁剪了FAT32实现了嵌入式文件系统,提高了 系统的存储能力。采用ATmegal28L高性能单片机的串 行外设接口sPI,满足访问Micro SD卡的功能要求,加快 了整个系统的设计进程。实践证明,该文件系统读取Mi— cro SD卡上花型文件的速度满足该控制系统的要求。该 嵌入式文件系统只需对底层驱动进行简单修改就可移植

MCK12140D中文资料

PIN CONNECTIONS

VCC 8 R 7 V 6 VEE 5

LOGIC DIAGRAM

1 U (fR > fV) R R S S R V D (fV > fR) Device MCH1214OD MCK12140D Q D (fV > fR) Q U (fR > fV) U

2 U

3 D

4 D

元器件交易网

Order this document By MCH12140/D

Phase Frequency Detector

The MCH/K12140 is a phase frequency-detector intended for phase-locked loop applications which require a minimum amount of phase and frequency difference at lock. When used in conjunction with the MC12147, MC12148 or MC12149 VCO, a high bandwidth PLL can be realized. The device is functionally compatible with the MC12040 phase-frequency detector, however the MOSAIC™ III process is used to push the maximum frequency to 800 MHz and significantly reduce the dead zone of the detector. When the Reference (R) and VCO (V) inputs are unequal in frequency and/or phase, the differential UP (U) and DOWN (D) outputs will provide pulse streams which when subtracted and integrated provide an error voltage for control of a VCO. The device is packaged in a small outline, surface mount 8-lead SOIC package. There are two versions of the device to provide I/O compatibility to the two existing ECL standards. The MCH12140 is compatible with MECL10H™ logic levels while the MCK12140 is compatible to 100K ECL logic levels. This device can also be used in +5.0 V systems. Please refer to Motorola Application Note AN1406/D, “Designing with PECL (ECL at +5.0 V)” for more information.

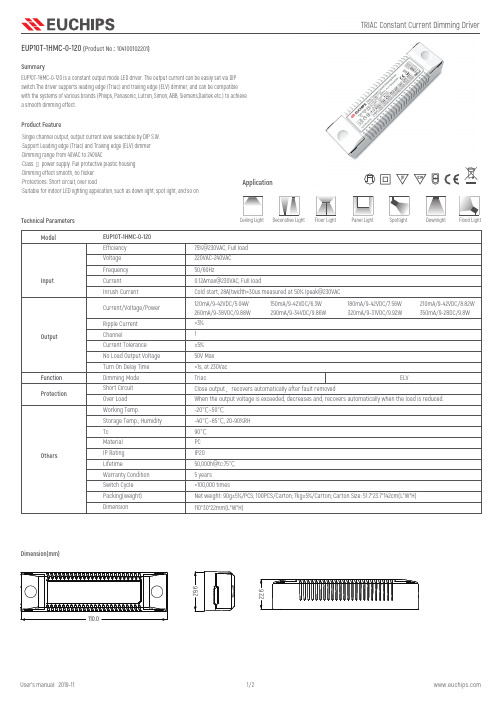

EUP10T-1HMC-0-120商品说明书

EUP10T-1HMC-0-120 (Product No.: 104100102201)SummaryProduct FeatureDimension(mm)ELV220VAC-240VAC 50/60Hz75%@230VAC, Full load Cold start, 28A(twidth=30us measured at 50% Ipeak@230VAC 0.12Amax@230VAC, Full load110*30*22mm(L*W*H)IP20-20℃~50℃-40℃~85℃, 20-90%RH 90℃PC 50,000h@tc:75℃50V Max ±5%<3%Triac>100,000 times1120mA/9-42VDC/5.04W 260mA/9-38VDC/9.88W 150mA/9-42VDC/6.3W 290mA/9-34VDC/9.86W180mA/9-42VDC/7.56W 320mA/9-31VDC/9.92W210mA/9-42VDC/8.82W 350mA/9-28DC/9.8WEUP10T-1HMC-0-120Tc LifetimeMaterialDimensionNet weight: 90g±5%/PCS; 100PCS/Carton; 7kg±5%/Carton; Carton Size: 51.7*23.7*142cm(L*W*H) Packing(weight)IP Rating Working Temp.Storage Temp.; Humidity Dimming Mode Switch Cycle 5 years Warranty Condition No Load Output Voltage Turn On Delay Time<1s, at 230Vac Efficiency Current Inrush Current Current/Voltage/Power Ripple CurrentChannel Current Tolerance Voltage FrequencyShort Circuit Over Load When the output voltage is exceeded, decreases and, recovers automatically when the load is reduced.Close output ,recovers automatically after fault removedOthersFunction ModelOutputInputProtectionTechnical ParametersApplicationDownlight Panel Light Flood LightSpotlight Ceiling Light Floor Light Decorative Light EUP10T-1HMC-0-120 is a constant output mode LED driver. The output current can be easily set via DIP switch.The driver supports leading edge (Triac) and trailing edge (ELV) dimmer, and can be compatible with the systems of various brands (Philips, Panasonic, Lutron, Simon, ABB, Siemens,Dalitek etc.) to achieve a smooth dimming effect.·Single channel output, output current level selectable by DIP S.W.·Support Leading edge (Triac) and Trailing edge (ELV) dimmer ·Dimming range from 40VAC to 240VAC·Class Ⅱ power supply. Full protective plastic housing ·Dimming effect smooth, no flicker ·Protections: Short circuit, over load·Suitable for indoor LED lighting application, such as down light, spot light, and so onAmbient Temperature(℃)L o a d (%)20406080100120-20-101020304050600Current Selection TableRemark: Function default setting is: 120mA (@switch are all OFF state)Dimming CurveDerating Curve※ The contents of this manual are updated without prior notice. If the function of the product you are using is inconsistent with the instructions, the function of the product shall prevail.Please contact us if you have any questions .L NTRIAC DimmerLampCautions1.The product shall be installed and serviced by a qualified person.2.This product is non-waterproof. Please avoid the sun and rain. When installed outdoors please ensure it is mounted in a water proof enclosure.3.Good heat dissipation will prolong the working life of the controller. Please ensure good ventilation.4.Please check if the output voltage and current of any LED power supplies used comply with the requirement of the product.5.Please ensure that adequate sized cable is used from the controller to the LED lights to carry the current. Please also ensure that the cable is secured tightly in the connector.6.For safety consideration, PVC or rubber cord of 0.75-1.5mm2 is recommended for input and output terminal(s) . Flat power cord is not suitable. Ensure all wire connections and polarities are correct before applying power to avoid any damages to the LED lights.7.If a fault occurs please return the product to your supplier. Do not attempt to fix this product by yourself.00612182430374349556167737985919720406080100120Input (%)O u t p u t (%)EUP10T-1HMC-0-120 (产品代码: 104100102201)概述产品特点EUP10T-1HMC-0-120 是一款可以提供120/150/180/210/260/290/320/350 8档电流的LED 驱动器,输出电流可以通过DIP 拨码开关简易设置,这款驱动器支持前沿切相和后沿切相调光器,可以与多品牌系统(飞利浦,ABB ,路创,西门子,西蒙,松下,邦奇等)配合使用,调光曲线平滑。

通讯设备mci中文手册与指令手册

读串口:OK//接收响应OK

读串口:^SISW:0,1//接收网络响应,收到则已经发送成功

(6)AT^SISW(InternetServiceWriteData)

命令格式:AT^SISW=<srvProfileId>,<reqWriteLength>

接收GPRS的数据,即接收已经连接上的服务器发来的数据,可以通过串行口从GPRS模块中读取,按以下顺序进行操作:

at^siso=1//打开端口,开始工作

(3)AT^SISO(InternerServiceOpen)

命令格式:AT^SISO=<srvProfileId>//启动GPRS连接。

(4)AT^SISC(InternetServiceClose)

命令格式:AT^SISC=<srvProfileId>//关闭GPRS连接。

1.SocketClientandServerforTCP,ClientforUDP;

2.FTPClient;

3.HTTPClient;

4.SMTPClient;

5.POP3Client;

该两款模块最大的区别在于,MC52i是2波段(900MHz/1800MHz)的gprs模块,而MC55i是4波段(850MHz/900MHz/1800MHz/1900MHz)的gprs模块,其中MC55i模块可以在全世界任何国家的GSM网使用。

读串口:^SISR:0,1//接收到该信息则准备接收数据

写串口:at^sisr=0,20//发送需要接收的数据长度

读串口:^SISR:0,20//返回实际的数据长度

读串口:OK //接收成功

◇MC52iGPRS模块技术特点

感应ic硬件说明消费机食堂ic机

Thank You!感谢您购买:消费机。

消费机使用TCP/IP 局域网络通讯技术。

消费机是在总结以往消费机各种缺点和用户需求等的基础上开发的专业消费设备。

专门针对食堂、餐厅、超市、食堂、餐厅、小卖部等消费场所设计,淘汰以往采用的现金、饭票、ID 卡、接触式智能卡等消费结账方式,使用Philips Mifare One S50非接触式IC卡作为电子钱包,提供强大的卡保密性能和更轻松简洁的消费方式。

有效的解决了传统的饭票流通所带来的不卫生、零钱不够找、偷饭票、伪造饭票等一系列让管理者费尽心思的疑难问题。

台式消费机集成了最新的MCU,可以存储10000条感应卡消费记录,使用人数无限制,联网设备无限制,可无限扩展使用人员,无限扩展使用场地。

内置后备电池,断电后能继续使用长达8小时的不间断工作,消费信息不会因电源断电而丢失,确保消费系统良好的运行,保证消费信息的安全。

台式消费机高可靠高稳定,功能强大安装简便,是应用于超市、食堂、餐厅、小卖部及大型消费场所的最好消费设备。

请在使用本机前阅读本说明书,并将其保存好以备将来参考。

感谢您对我司的支持,感谢您选购我们的一卡通系统。

我们将为您提供最优质的服务。

目录一.设备外观 (3)二.消费系统配置表 (4)三.详细参数 (5)四.键盘标识 (10)五.消费、充值及查询 (20)六.网线连接 (3)七.系统拓补示意图 (4)八.系统组成部份 (5)九.硬件菜单操作 (3)十.新机快速操作 (10)十一.维护与保养 (20)一.设备外观出厂默设置二.消费系统配置表包装内设备标准配置表其它配套设备三.详细参数基本参数设备特性⏹消费机采用TCP/IP 局域网通讯技术;⏹消费机可查询IC卡余额、最近一次消费金额、未采集总消费次数;⏹消费机支持联网和脱网工作,联网时,支持实时采集并显示即时消费记录;⏹消费机支持定额消费模式、不定额消费模式、菜单编号消费模式,适合任何消费场所;⏹消费刷卡记录采用固化芯片储存方式储存,掉电数据不丢失;⏹软件系统可扩展考勤、门禁,实现1张IC卡1个数据库1个管理软件进行一卡通管理;⏹支持误操作退款,可退回最近一次的消费金额;⏹使用消费机键盘操作即可轻松统计并显示当天消费记录的总和;⏹支持个人与全体两种折扣功能;⏹支持消费积分功能;⏹支持订餐功能,有效防止食物浪费;⏹支持信息查询机,可查询卡内金额情况、清费记录、持卡人姓名等信息⏹菜单编号消费,支持1-5位编码,可显示中文菜名,单价,份数等⏹具备日限额、次限额等,有效防止恶意消费⏹具备超额密码消费功能;⏹具备卡有效期限制功能⏹具备交易回退功能:扣错款的情况下,可回退该笔交易;⏹可外接小票打印机,可打印中文菜名,单价,份数等⏹支持密码数字键盘功能(选配功能)⏹支持条码扫描枪输入功能(选配功能)⏹双面4行中文液晶显示屏,可显示部门与姓名,也可显示菜名等⏹本机自带后备电源,即使在停电的情况下也能连续工作8小时以上四.键盘标识台式消费机使用键盘操作。

铭道通信R1008P录音卡说明书

由于产品版本升级或其他原因,本文档内容会不定期进行更新。除非另有约定,本文档仅作 为使用指导,本文档中的所有陈述、信息或建议不构成任何明示或暗示的担保

2

目录

前言...............................................................................................................................................................................4

4 附录.....................................................................................................................................................................11

0579-85218087-8008

11

防雷击:4级

win2000,win2003,winXP

≤0.5Ω(联合接地方式) 0℃~55℃ 5%~80%(非凝结) -20℃~+85℃ 0%~95%(非凝结)

3 技术指标

10

4 附录

4.1 技术/销售支持

当您在使用产品的过程中,有任何的问题,都可以联系我们,我们将竭尽全力为您解决问题, 诚心为您服务 联系方式

1.3

性能特点.............................................................................................................................................. 6

MC9S12XS128中文资料

飞思卡尔智能汽车竞赛XS128主要模块实验指导书第一章端口整合模块端口A,B和K为通用I/O接口端口E 整合了IRQ,XIRQ中断输入端口T 整合了1个定时模块端口S 整合了2个SCI模块和1个SPI模块端口M 整合了1个MSCAN端口P 整合了PWM 模块,同时可用作外部中断源输入端口H 和J 为通用I/O接口,同时可用作外部中断源输入端口AD 整合了1个16位通道ATD模块大部分I/O引脚可由相应的寄存器位来配置选择数据方向、驱动能力,使能上拉或下拉式装置。

当用作通用IO口时,所有的端口都有数据寄存器和数据方向寄存器。

对于端口T, S, M, P, H, 和J 有基于每个针脚的上拉和下拉控制寄存器。

对于端口AD 有基于每个针脚的上拉寄存器。

对于端口A、B、E 和K,有一个基于端口的上拉控制寄存器。

对于端口T, S, M, P, H, J, 和AD,有基于每个针脚的降额输出驱动控制寄存器。

对于端口A, B, E, 和K,有一个基于端口的降额输出驱动控制寄存器。

对于端口S、M,有漏极开路(线或)控制寄存器。

对于端口P、H 和J,有基于每个针脚的中断标志寄存器。

纯通用IO端口共计有41个,分别是:PA[7:0]PB[7:0]PE[6:5]PE[3:2]PK[7,5:0]PM[7:6]PH[7:0] (带中断输入)PJ[7:6] (带中断输入)PJ[1:0] (带中断输入)第二章脉冲宽度调制模块XS128具有8位8通道的PWM,相邻的两个通道可以级联组成16位的通道。

PWME:PWM通道使能寄存器。

PWMEx=1将立即使能该通道PWM波形输出。

若两个通道级联组成一个16位通道,则低位通道(通道数大的)的使能寄存器成为该级联通道的使能寄存器,高位通道(通道数小的)的使能寄存器和高位的波形输出是无效的。

PWMPOL:PWM极性寄存器。

PPOLx=1,则该通道的周期初始输出为高电平,达到占空比后变为低电平;相反,若PPOLx=0,则初始输出为低电平,达到占空比后变为高电平。

厦华总线

菜单 → 静音 → 静音 → 浏览 → 进入工厂菜单。

进入工厂菜单之后,按节目 键选择调整项目,按音量 键调整大小。

按“菜单”键退出工厂菜单。也可使用RC-F82遥控器:依次按以下按键即可

菜单 → 静音 → 静音 → 扫视 → 进入工厂菜单。

孤心狐 发表于 2006-11-28 09:49

19、G295系列:M37225+LA76810

进出菜单方法:

进入-------方法1:按遥控器[ ]键,并保持4秒后,立刻按[MENU]键,屏幕上出现“TEST”。

方法2:短路主板TEST IN

退出-------按 [STANDBY]键,TV进入待机状态,再按[STANDBY]键,TV工作,此时已退出菜单。

操作:1,有画中画机型,遥控器画中画的三排按键即是操作功能键——第一排右4键为关键,进入要按所属功

能键[第二排功能键],进入某个项目后,调整数据按遥控器中左右键箭头键;

2,无画中画机型,将遥控器上盖取出,导电橡胶从开关键往下数第六排右4键为维修菜单开关键,第七

排为功能键。

孤心狐 发表于 2006-11-27 16:09

5、W系列(W2935,W3416,W3430)

主要芯片: TMPA8807超级单片机

进入工厂调整菜单

依次按遥控器上的SLEEP→PIC→DSP→MENU键(按两键的时间间隔应少于5 s),屏幕上即出现工厂调试菜单。

3.2 工厂菜单操作

选择调整项目及调整:进入工厂调整模式后,按数字键即可选择M0~M9 共10个工厂主菜单,再利用“P+”,“P+”两个键可上下改变调整项目,利用“V+”,“V-”两个键可调整数据。

NC5200C交换设备

MC9S12_datasheet中文

目录 .................................................................................................................................................. I 第一章 PWM模块 ...........................................................................................................................1 第一节 PWM模块介绍 .........................................................................................................1 第二节 PWM寄存器简介 .......................................................................2 2.1 PWME寄存器 ........................................................................................................2 2.2 PWMPOL寄存器...................................................................................................2 2.3 PWMCLK寄存器 ..................................................................

MC9S12XS128单片机简介

MC9S12XS128 单片机简介1、HCS12X 系列单片机简介Freescale 公司的16 位单片机主要分为HC12 、HCS12、HCS12X 三个系列。

HC12核心是16 位高速CPU12 核,总线速度8MHZ;HCS12 系列单片机以速度更快的CPU12 内核为核心,简称S12 系列,典型的S12 总线速度可以达到25MHZ。

HCS12X 系列单片机是Freescale 公司于2005 年推出的HCS12 系列增强型产品,基于S12 CPU 内核,可以达到25MHz 的HCS12 的2-5 倍性能。

总线频率最高可达40 MHz。

S12X 系列单片机目前又有几个子系列:MC9S12XA 系列、MC9S12XB 系列、MC9S12XD 系列、MC9S12XE 系列、MC9S12XF系列、MC9S12XH 系列和MC9S12XS 系列。

MC9S12XS128 就是S12X 系列中的一个成员。

2、MC9S12XS128 性能概述MC9S12XS128 是16 位单片机,由16 位中央处理单元(CPU12X)、128KB 程序Flash(P-lash)、8KB RAM、8KB 数据Flash(D-lash)组成片内存储器。

主要功能模块包括:内部存储器内部PLL 锁相环模块2 个异步串口通讯SCI1 个串行外设接口SPIMSCAN 模块1 个8 通道输入/输出比较定时器模块TIM周期中断定时器模块PIT16 通道A/D 转换模块ADC1 个8 通道脉冲宽度调制模块PWM输入/输出数字I/O 口3、输入/输出数字I/O 口MC9S12XS128 有3 种封装,分别为64 引脚、80 引脚、112 引脚封装。

其全名分别为MC9S12XS128MAE、MC9S12XS128MAA、MC9S12XS128MAL。

MC9S12XS 系列具有丰富的输入/输出端口资源,同时集成了多种功能模块,端口包括PORTA、PORTB、PORTE、PORTK、PORTT、PORTS、PORTM、PORTP、PORTH、PORTJ 和PORTAD 共11 个端口。

Loop-E1200 FE1 CSU DSU系列产品介绍说明书

Loop-E1200FE1 CSU/DSU SeriesDescriptionLoop Telecom's Loop-E1200 FE1 CSU/DSU series provides an economic solution for E1 network access at a fraction of the costelsewhere. This series utilizes only parts of the 31 data channels and users pay a fraction of full E1 charges. The Loop-E1200 FE1CSU/DSU series supports High Density Bipolar 3 (HDB3) coding and provides continuous error checking, performance polling, and in-service diagnostics. The versatile Loop-E1200 FE1 CSU/DSU series provides up to four sets of DTE equipment with operating rates from 56 to 1984 Kbps and one Drop and Insert DTE operating at E1 (2048 Kbps) to be connected directly to the E1 network services. This series enables users to interconnect LANs and WANs, CAD and CAM, video conferencing, mainframe hosts, and more.Loop-E1200 FE1 CSU/DSU series supports local control and diagnostics with a 2-line by 40-character LCD display and keypads. The series enables users to configure the unit, execute in-service diagnostics, and monitor network status and availability. The Loop-E1200 also provides LED status indicators. It supports SNMP network management toremotely control and diagnose Loop-E products from anywhere in the network. In addition, Loop Telecom also provides an optional Windows based GUI network management system called LoopView.Ordering InformationTo specify options, choose from the list below.NOTE: RoHS compliant units are identified by the letter G appearing at the end of the ordering code.Model (non RoHS compliant) Model(RoHS compliant) SNMPLoop-E120x-y-dte-ww-SNMP-pp Loop-E120x-y-dte-ww-SNMP-pp-G YESAccessoriesConversion Cable (The conversion cables shown below are RoHS compliant.) Loop-ACC-CAB-DB25M-30-1M37FDB25(male) to M34 V.35 conversion cable, 30cmLoop-ACC-CAB-DB25M-30-1DB37F DB25(male) to DB37 RS449/V.36 conversion cable, 30cmDTE CardE1200-EIA530 E1200-EIA530-G Additional DTE 3/4 (EIA530) Card Power Cord (All power cords are RoHS compliant.)Features● DSU (Data Service Unit) functionality integrated with an intelligent CSU (Channel Service Unit) ● SNMP Network Management● Connect LAN/WAN, CAD/CAM, or Hosts to 2Mbps E1 Network Services ● Optional GUI NMS LoopView● Compliance with ITU-T G.703, G.704, G.706,G.732, G.736, G.823, ETSI ETS 300420, and ETS 300419 ● RoHS compliantLoop-ACC-PC-USA AC power cord forTaiwan/USALoop-ACC-PC-EU AC power cord for Europe Loop-ACC-PC-UK AC power cord for the UK Loop-ACC-PC-AUS AC power cord for Australia Loop-ACC-PC-CH AC power cord for China User’s ManualLoop-E1200-UM User’s Manual (optional paper copy). A CD version of the manual is included with every order.Ear Mounts19”/23’ ear mounts A pair of 19”/23” ear mounts is already included with every order.Note: For other sizes, please contact your nearest Loop sales representative.Where x=x=1 for no D&I, 2 for D&I porty=2 for 2 DTE port, 4 for 4 DTE portdte=33 for EIA530 DTE interfaceww=75 for 75 ohm BNC E1 interface120 for 120 ohm twisted pair E1 interfacepp = DC for -24 to -48 VdcAC for 100 to 240 Vac, 50/60 Hz (For AC, choose an appropriate power cord)Example:Loop-E1201-2-33-75-DCFor model 1200 with no D&I port, 2 DTE ports, E1A530 DTE interface with DB25 connector, 75 ohm BNC E1 interface, no SNMP option, and DC power.NOTE:Order conversion cable for RS449/V.36 and X.21.Loop-E1200 FE1 CSU/DSU Series Product SpecificationNetwork Line Interface (E1 Interface)Line Rate 2.048 Mbps ± 50 ppm Framing ITU G.704Line Code AMI / HDB3 (selectable) Input Signal ITU G.703 to -26dBOutput Signal ITU G.703 Connector BNC / RJ48C (specify on order) Jitter ITU G.823 Electrical 75Ω Coax / 120Ω twisted pair Customer Equipment Interface⏹E1 Drop and Insert Port (optional)Line Rate 2.048 Mbps ± 50 ppm Framing ITU G.704Line Code AMI / HDB3 (selectable) Input Signal ITU G.703 to -10dBOutput Signal ITU G.703 Connector BNC / RJ48C(specify on order) Jitter ITU G.823 Electrical 75Ω Coax / 120Ω twisted pair⏹ DTE Data PortNumber of Ports 2 + 2 (optional) ports Data Rate 56 or 64 Kbps * n ( n = 1 - 31 ) Connector EIA530 (DB25P), DB25P to V.35, RS449, or X.21 conversion cable (optional)⏹DS0 MappingMaps Two switchable sets of DS0 maps for DTE and D&I portsRemote Sending Sending active DS0 maps to a remote sitePerformance MonitorPerformance Store Last 24 hours performance in 15 minutes intervals and last 7 days in 24-hoursummary line, user, D&I port, and remote sitePerformance Reports Date & Time, Errored Second, Degraded Minutes, Unavailable Second, BurstyErrored Second, Severe Errored Second, and Controlled Slip Second. Alsoavailable in Statistics (%)Alarm History Date & Time, Alarm Type (i.e. Master Clock Loss, RAI, AIS, LOS, BPV, ES, CS),and Location (i.e. line, DTE)Alarm Queue Maximum 40 alarm records which record the latest alarm type, location, and date &timeThreshold Bursty Seconds, Severely Errored Second, Degraded MinutesSystem Configuration ParametersActive Configuration, Stored Configuration, and Default Configuration (Stored in Non-volatile Memory)Diagnostics TestLoopback Line Loopback, Payload Loopback, Local Loopback, and DTE LoopbackTest Pattern 20 bits QRSS, 3-in-24, 1-in-8, 2-in-8, 1:1 patternsIdle Channel Use of idle channel to perform PRBS diagnostic testRemote Loopback Line Loopback, Payload Loopback, and DTE Channel Loopback (V.54 or Loopproprietary)Front Panel and Console PortConsole Port RS232 with VT100 terminal mode. Embedded SNMP (optional)LCD/LED 2 lines by 40 characters LCD display, 9 status LEDs(Power, Line, D&I, DTEn, RLB, and ACO)Keypad 4 operation keys and ACO keyBantam Jack 6 bantam jacks for Line and D&I port break and insertAlarm RelayAlarm Relay Fuse alarm and performance alarmActivation RAI, AIS, LOS, LOF, BPV, ES, UAS, CS of line and D&I port, and DTE port alarmPhysical/ ElectricalDimensions 430 x 43.7 x 306.5 mm (WxHxD) Humidity 0-95% RH (non-condensing)Power -48V 450mA DC, 100-240V AC Mounting Desk-top stackable, 19/23 inch rack mountable Temperature 0-50 C Weight 7.7 lb., (3.5 kg)ComplianceETSI ETS 300420, ETS 300419 ITU G.703, G.704, G.706, G.732,G.736, G.823Pan European CTR 12/13, CE 168X EMI/EMC EN50082-1 EN55022 Class ABABT NTR4 Safety EN41003。

康耐德 C2000-B2-UJE0801-CB1 使用说明书

2020年9月14日 更新C2000-B2-UJE0801-CB1 使用说明书Ethernet ⇋ 8 * RS485/422/232串口设备联网 — 串口服务器深圳市中联创新自控系统有限公司Shenzhen United Innovation Automatic Control System Co., Ltd.2555791017171920222323252525252526262727273643484851565659626465目录目录1. 快速使用1.1. 使用前准备1.2. 设备接线1.3. 软件安装及设置1.3.1. 设备搜索1.3.2. 设备配置2. 硬件说明2.1. 技术参数2.2. 产品外观2.3. 指示灯2.4. 端口说明2.5. 尺寸2.6. 安装方式3. 产品功能3.0.1. 透明传输3.0.2. 支持虚拟串口通信3.0.3. 支持Socket 进行通讯3.0.4. 支持UDP 进行通讯3.0.5. 支持网页设置3.0.6. 支持控件协议二次开发4. 参数设置及测试4.1. 使用虚拟串口进行通信4.1.1. 设备做为客户端模式4.1.2. 设备做为服务器模式4.1.3. 虚拟串口测试4.2. 使用Socket 连接进行通信4.2.1. 设备作为TCP Client 4.2.2. 设备作为TCP Serv er 4.3. 使用UDP 进行通信4.3.1. UDP_Appointed 工作模式4.3.2. UDP_Normal 工作模式4.4. 使用Web 设置参数5. 装箱清单6. 产品服务【版权声明】©2000 - 2020 中联创新版权所有【商标声明】及其它中联创新服务相关的商标均为深圳市中联创新自控系统有限公司及其关联公司所有。

本文档涉及的第三方主体的商标,依法由权利人所有。

【免责声明】本文档仅提供有关康耐德产品的信息。

本文档并未授予任何知识产权的许可,包括未以明示或暗示、以禁止发言或其他方式授予任何知识产权许可。

MC9S12DG128实验系统使用手册

MC9S12DG128实验系统使用手册目录第一章系统概述 (2)第二章硬件电路原理 (4)2.1子板硬件原理 (4)2.1.1、MCU引脚接口部分 (5)2.1.2、串口通信部分 (5)2.1.3、电源部分 (6)2.1.4、复位电路部分 (6)2.1.5、I/O端口电路部分 (7)2.1.6、晶振电路与BDM插头部分 (7)2.2母板硬件原理 (8)2.2.1、电源部分 (8)2.2.2、MC9S12DG128开发板与各接口部分 (9)2.2.3、串口通信部分 (11)2.2.4、LED数码管显示部分 (12)2.2.5、8位数字量输入输出部分 (13)2.2.6、红外发射接收部分 (14)2.2.7、LCD显示部分 (15)2.2.8、模拟量输入部分 (15)2.2.9、蜂鸣器和喇叭部分 (15)2.2.10、键盘输入部分 (16)2.2.11、继电器部分 (16)2.2.12、打印机部分 (17)2.2.13、CAN总线部分 (17)第三章 MC9S12DG128教学平台快速入门 (18)3.1硬件连接 (18)3.2软件应用 (20)第一章系统概述天津工业大学Freescale MCU/DSP研发中心开发的DG128实验系统,其功能基本上和美国MCUSLK系统相同,而且根据中国的教学情况重新设计了一些功能、力求达到更好的实验效果。

DG128实验系统由主板和独立的MCU子板构成。

DG128实验系统的主板插槽和美国的MCUSLK 系统相互兼容,主板的插槽可以插包括S12、S08、 HC08各系列MCU子板。

MCU子板可以单独调试运行,也可以插在主板上调试,充分利用主板丰富的硬件资源。

MC9S12DG128具有16位中央处理器(HCS12 CPU)、128KB Flash EEPROM、8KB RAM、2KB EEPROM,以及定时器通道、键盘中断和A/D通道等接口。

MC9S12DG128实验系统可以直接与CodeWarrior相连,具有下载程序、在线单步运行、断点调试、连续运行、修改寄存器和存储单元等特点,可以很方便的进行教学。

MC9S12XS128单片机简介

MC9S12XS128 单片机简介1、HCS12X 系列单片机简介Freescale 公司的16 位单片机主要分为HC12 、HCS12、HCS12X 三个系列。

HC12核心是16 位高速CPU12 核,总线速度8MHZ;HCS12 系列单片机以速度更快的CPU12 内核为核心,简称S12 系列,典型的S12 总线速度可以达到25MHZ。

HCS12X 系列单片机是Freescale 公司于2005 年推出的HCS12 系列增强型产品,基于S12 CPU 内核,可以达到25MHz 的HCS12 的2-5 倍性能。

总线频率最高可达40 MHz。

S12X 系列单片机目前又有几个子系列:MC9S12XA 系列、MC9S12XB 系列、MC9S12XD 系列、MC9S12XE 系列、MC9S12XF系列、MC9S12XH 系列和MC9S12XS 系列。

MC9S12XS128 就是S12X 系列中的一个成员。

2、MC9S12XS128 性能概述MC9S12XS128 是16 位单片机,由16 位中央处理单元(CPU12X)、128KB 程序Flash(P-lash)、8KB RAM、8KB 数据Flash(D-lash)组成片内存储器。

主要功能模块包括:内部存储器内部PLL 锁相环模块2 个异步串口通讯SCI1 个串行外设接口SPIMSCAN 模块1 个8 通道输入/输出比较定时器模块TIM周期中断定时器模块PIT16 通道A/D 转换模块ADC1 个8 通道脉冲宽度调制模块PWM输入/输出数字I/O 口3、输入/输出数字I/O 口MC9S12XS128 有3 种封装,分别为64 引脚、80 引脚、112 引脚封装。

其全名分别为MC9S12XS128MAE、MC9S12XS128MAA、MC9S12XS128MAL。

MC9S12XS 系列具有丰富的输入/输出端口资源,同时集成了多种功能模块,端口包括PORTA、PORTB、PORTE、PORTK、PORTT、PORTS、PORTM、PORTP、PORTH、PORTJ 和PORTAD 共11 个端口。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

MultiMediaCard SpecificationVersion : Ver. 0.9Date 4 – June - 2004Samsung Electronics Co., LTDSemiconductor Flash Memory Product Planning & Applications1 Introduction to the MultiMediaCard ----------------------------------------------------------- 51.1 System Features ----------------------------------------------------------------------------------------- 5-------------------------------------------------------------------------------------- 51.2 ProductModel2 Function Description ------------------------------------------------------------------------------- 72.1 Flash Technology Independence ------------------------------------------------------------------ 72.2 Defect and Error Management --------------------------------------------------------------------- 72.3 Endurance ----------------------------------------------------------------------------------------------- 72.4 Automatic Sleep Mode ------------------------------------------------------------------------------- 72.5 Hot Insertion -------------------------------------------------------------------------------------------- 82.6 MultiMediaCard Mode -------------------------------------------------------------------------------- 82.6.1 MultiMediaCard Standard Compliance ----------------------------------------------------------- 82.6.2 Negotiation Operation Conditions ----------------------------------------------------------------- 82.6.3 Card Acquisition and Identification ---------------------------------------------------------------- 82.6.4 Card Status ---------------------------------------------------------------------------------------------- 82.6.5 Memory Array Partitioning --------------------------------------------------------------------------- 92.6.6 Read and Write Operations ------------------------------------------------------------------------- 92.6.7 Data Transfer Rate ------------------------------------------------------------------------------------102.6.8 Data Protection in the Flash Card -----------------------------------------------------------------10-----------------------------------------------------------------------------------------------------10 2.6.9 Erase2.6.10 Write Protection ----------------------------------------------------------------------------------------102.6.11 Copy Bit ------------------------------------------------------------------------------------------------- 102.6.12 The CSD Register ------------------------------------------------------------------------------------ 112.7 SPI Mode ----------------------------------------------------------------------------------------------- 112.7.1 Negotiating Operation Conditions ---------------------------------------------------------------- 112.7.2 Card Acquisition and Identification --------------------------------------------------------------- 112.7.3 Card Status --------------------------------------------------------------------------------------------- 112.7.4 Memory Array Partitioning -------------------------------------------------------------------------- 112.7.5 Read and Write Operations ------------------------------------------------------------------------- 112.7.6 Data Transfer Rate ------------------------------------------------------------------------------------ 112.7.7 Data Protection in the MultiMediaCard ----------------------------------------------------------- 1212-----------------------------------------------------------------------------------------------------2.7.8 Erase2.7.9 Write Protection ---------------------------------------------------------------------------------------- 123 Product Specifications ----------------------------------------------------------------------------- 133.1 Recommended Operating Conditions ------------------------------------------------------------------------- 133.2 Operating Characteristis ----------------------------------------------------------------- 143.3 System Environmental Specifications ----------------------------------------------------------------- 153.4 System Reliability and Maintenance -------------------------------------------------------------- 153.5 Physical Specifications ------------------------------------------------------------------------------- 164 MultiMediaCard Interface Description --------------------------------------------------------- 174.1 Pin Assignments in MultiMediaCard Mode ------------------------------------------------------- 174.2 Pin Assignments in SPI Mode ---------------------------------------------------------------------- 184.3 MultiMediaCard Bus Topology ---------------------------------------------------------------------- 184.4 SPI Bus Topology -------------------------------------------------------------------------------------------------- 194.4.1 SPI Interface Concept ------------------------------------------------------------------------------------------- 194.4.2 SPI Bus Topology ------------------------------------------------------------------------------------------------ 1920------------------------------------------------------------------------------------------------- 4.5 Registers4.5.1 Operation Condition Register (OCR) ---------------------------------------------------------------------------204.5.2 Card Identification (CID) ------------------------------------------------------------------------------214.5.3 Relative Card Address (RCA) ----------------------------------------------------------------------- 21 4.5.4 Card Specific Data (CSD) ---------------------------------------------------------------------------- 22 4.6 MultiMediaCard Communication -------------------------------------------------------------------- 3030----------------------------------------------------------------------------------------------- 4.6.1 Commands4.7 Read, Write and Erase Time-out Conditions ----------------------------------------------------- 33 4.8 Card Identification Mode ------------------------------------------------------------------------------ 34 4.8.1 Operating Voltage Range Validation --------------------------------------------------------------- 35 4.9 Data Transfer Mode ------------------------------------------------------------------------------------ 35 4.9.1 Block Read ----------------------------------------------------------------------------------------------- 37 4.9.2 Block Write ----------------------------------------------------------------------------------------------- 3738------------------------------------------------------------------------------------------------------ 4.9.3 Erase4.9.4 Write Protect Management -------------------------------------------------------------------------- 38 4.9.5 Card Lock/Unlock Operation ------------------------------------------------------------------------ 38----------------------------------------------------------------------------------------------- 41 4.9.6 Responses4.9.7 Status ------------------------------------------------------------------------------------------------------ 42 4.9.8 Command Response Timing ------------------------------------------------------------------------ 4448 4.9.9 Reset------------------------------------------------------------------------------------------------------ 4.10 SPI Communication ----------------------------------------------------------------------------------- 49 4.10.1 Mode Selection ----------------------------------------------------------------------------------------- 49 4.10.2 Bus Transfer Protection ------------------------------------------------------------------------------ 49 4.10.3 Data Read Overview ---------------------------------------------------------------------------------- 50 4.10.4 Data Write Overview ---------------------------------------------------------------------------------- 51 4.10.5 Erase and Write Protect Management ----------------------------------------------------------- 52 4.10.6 Reading CID/CSD Registers ------------------------------------------------------------------------ 53 4.10.7 Reset Sequence --------------------------------------------------------------------------------------- 53 4.10.8 Error Conditions ---------------------------------------------------------------------------------------- 53 4.10.9 Memory Array Partitioning --------------------------------------------------------------------------- 53 4.10.10 Card Lock/Unlock -------------------------------------------------------------------------------------- 53 4.10.11 Commands ----------------------------------------------------------------------------------------------- 54 4.10.12 Responses ----------------------------------------------------------------------------------------------- 56 4.10.13 Data Tokens --------------------------------------------------------------------------------------------- 58 4.10.14 Data Error Token --------------------------------------------------------------------------------------- 59 4.10.15 Clearing Status Bits ------------------------------------------------------------------------------------ 60 4.11 SPI Bus Timing ----------------------------------------------------------------------------------------- 61 4.12 Error Handling ------------------------------------------------------------------------------------------ 64 4.12.1 Error Correction Code (ECC) ----------------------------------------------------------------------- 64 4.12.2 Cyclic Redundancy Check (CRC) ----------------------------------------------------------------- 642 Function Description2.1 Flash Technology IndependenceThe 512 byte sector size of the MultiMediaCard is the same as that in an IDE magnetic disk drive. To write or read a sector (or multiple sectors), the host computer software simply issues a Read or Write command to the MultiMediaCard. This command contains the address and the number of sectors to write/read. The host software then waits for the command to complete. The host software does not get involved in the details of how the flash memory is erased, programmed or read. This is extremely important as flash devices are expected to get more and more complex in the future. Because the MultiMediaCard uses an intelligent on-board controller, the host system software will not require changing as new flash memory evolves. In other words, systems that support the MultiMediaCard today will be able to access future MultiMediaCards built with new flash technology without having to update or change host software.2.2 Defect and Error ManagementMultiMediaCards contain a sophisticated defect and error management system. This system is analogous to the systems found in magnetic disk drives and in many cases offers enhancements. For instance, disk drives do not typically perform a read after write to confirm the data is written correctly because of the performance penalty that would be incurred. MultiMediaCards do a read after write under margin conditions to verify that the data is written correctly (except in the case of a Write without Erase Command). In the rare case that a bit is found to be defective, MultiMediaCards replace this bad bit with a spare bit within the sector header. If necessary, MultiMediaCards will even replace the entire sector with a spare sector. This is completely transparent to the host and does not consume any user data space.The MultiMediaCards soft error rate specification is much better than the magnetic disk drive specification. In the extremely rare case a read error does occur, MultiMediaCards have innovative algorithms to recover the data. This is similar to using retries on a disk drive but is much more sophisticated. The last line of defense is to employ powerful ECC to correct the data. If ECC is used to recover data, defective bits are replaced with spare bits to ensure they do not cause any future problems.These defect and error management systems coupled with the solid-state construction give MultiMediaCards unparalleled reliability2.3 EnduranceMultiMediaCards have an endurance specification for each sector of 1,000,000 writes (reading a logical sector is unlimited). This is far beyond what is needed in nearly all applications of MultiMediaCards. Even very heavy use of the MultiMediaCard in cellular phones, personal communicators, pagers and voice recorders will use only a fraction of the total endurance over the typical device’s five year lifetime. For instance, it would take over 100 years to wear out an area on the MultiMediaCard on which a files of any size (from 512 bytes to capacity) was rewritten 3 times per hour, 8 hours a day, 365 days per year.With typical applications the endurance limit is not of any practical concern to the vast majority of users.2.4 Automatic Sleep ModeAn important feature of the MultiMediaCard is automatic entrance and exit from sleep mode. Upon completion of an operation, the MultiMediaCard will enter the sleep mode to conserve power if no further commands are received within 5 msec The host does not have to take any action for this to occur. In most systems, the MultiMediaCard is in sleep mode except when the host is accessing it, thus conserving power. When the host is ready to access the MultiMediaCard and it is in sleep mode, any command issued to the MultiMediaCard will cause it to exit sleep and respond. The host does not have to issue a reset first. It may do this if desired, but it is not needed. By not issuing the reset, performance is improved through the reduction of overhead.2.5 Hot InsertionSupport for hot insertion will be required on the host but will be supported through the connector. Connector manufacturers will provide connectors that have power pins long enough to be powered before contact is made with the other pins. Please see connector data sheets for more details. This approach is similar to that used in PCMCIA to allow for hot insertion. This applies to both MultiMediaCard and SPI modes.2.6 MultiMediaCard Mode2.6.1 MultiMediaCard Standard ComplianceThe MultiMediaCard is fully compliant with MultiMediaCard standard specification V3.31.The structure of the Card Specific Data (CSD) register is compliant with CSD structure V1.2.2.6.2 Negotiating Operation ConditionsThe MultiMediaCard supports the operation condition verification sequence defined in the MultiMediaCard standard specifications. The MultiMediaCard host should define an operating voltage range that is not supported by the MultiMediaCard. It will put itself in an inactive state and ignore any bus communication. The only way to get the card out of the inactive state is by powering it down and up again. In addition the host can explicitly send the card to the inactive state by using the GO_INACTIVE_STATE command.2.6.3 Card Acquisition and IdentificationThe MultiMediaCard bus is a single master (MultiMediaCard host) and multi-slaves (cards) bus. The host can query the bus and find out how many cards of which type are currently connected. The MultiMediaCard’s CID register is pre-programmed with a unique card identification number which is used during the acquisition and identification procedureIn addition, the MultiMediaCard host can read the card’s CID register using the READ_CID MultiMediaCard command. The CID register is programmed during the MultiMediaCard testing and formatting procedure, on the manufacturing floor. The MultiMediaCard host can only read this register and not write to it.2.6.4 Card StatusMultiMediaCard status is stored in a 32 bit status register which is sent as the data field in the card respond to host commands. Status register provides information about the card’s current state and completion codes for the last host command. The card status can be explicitly read (polled) with the SEND_STATUS command.2.6.7 Data Protection in the Flash CardEvery sector is protected with an Error Correction Code (ECC). The ECC is generated (in the memory card) when the sectors are written and validated when the data is read. If defects are found, the data is corrected prior to transmission to the host.The MultiMediaCard can be considered error free and no additional data protection is needed. However, if an application uses additional, external, ECC protection, the data organization is defined in the user writeable section of the CSD register2.6.8 EraseThe smallest erasable unit in the MultiMediaCard is a erase group. In order to speed up the erase procedure, multiple erase groups can be erased in the same time. The erase operation is divided into two stages.Tagging - Selecting the Sectors for ErasingTo facilitate selection, a first command with the starting address is followed by a second command with the final address, and all erase groups within this range will be selected for erase.Erasing - Starting the Erase ProcessTagging can address erase groups. An arbitrary selection of erase groups may be erased at one time. Tagging and erasing must follow a strict command sequence (refer to the MultiMediaCard standard specification for details).2.6.9 Write ProtectionThe MultiMediaCard erase groups are grouped into write protection groups. Commands are provided for limiting and enabling write and erase privileges for each group individually. The current write protect map can be read using SEND_WRITE_PROT command.In addition two, permanent and temporary, card levels write protection options are available.Both can be set using the PROGRAM_CSD command (see below). The permanent write protect bit, once set, cannot be cleared.The One Time Programmable (OTP) characteristic of the permanent write protect bit is implemented in the MultiMediaCard controller firmware and not with a physical OTP cell.2.6.10 Copy BitThe content of an MultiMediaCard can be marked as an original or a copy using the copy bit in the CSD register. Once the Copy bit is set (marked as a copy) it cannot be cleared.The Copy bit of the MultiMediaCard is programmed (during test and formatting on the manufacturing floor) as a copy. The MultiMediaCard can be purchased with the copy bit set (copy) or cleared, indicating the card is a master.The One Time Programmable (OTP) characteristic of the Copy bit is implemented in the MultiMediaCard controller firmware and not with a physical OTP cell.2.6.11 The CSD RegisterAll the configuration information of the MultiMediaCard is stored in the CSD register. The MSB bytes of the register contain manufacturer data and the two least significant bytes contains the host controlled data - the card Copy and write protection and the user ECC register.The host can read the CSD register and alter the host controlled data bytes using the SEND_CSD and PROGRAM_CSD commands.2.7 SPI ModeThe SPI mode is a secondary (optional) communication protocol offered for MultiMediaCard. This mode is a subset of the MultiMediaCard protocol, designed to communicate with an SPI channel, commonly found in Motorola’s (and lately a few other vendors’) microcontrollers.2.7.1 Negotiating Operation ConditionsThe operating condition negotiation function of the MultiMediaCard bus is not supported in SPI mode. The host must work within the valid voltage range (2.7 to 3.6 volts) of the card.2.7.2 Card Acquisition and IdentificationThe card acquisition and identification function of the MultiMediaCard bus is not supported in SPI mode. The host must know the number of cards currently connected on the bus. Specific card selection is done via the CS signal.2.7.3 Card StatusIn SPI mode only 16 bits (containing the errors relevant to SPI mode) can be read out of the MultiMediaCard status register.2.7.4 Memory Array PartitioningMemory partitioning in SPI mode is equivalent to MultiMediaCard mode. All read and write commands are byte addressable.2.7.5 Read and Write OperationsIn SPI mode, only single block read/write mode is supported.2.7.6 Data Transfer RateIn SPI mode only block mode is supported. The typical access time (latency) for each data block, in read operation, is 1.5mS. The write typical access time (latency) for each data block, in read operation, is 1.5mS. The write block operation is done in handshake mode. The card will keep DataOut line low as long as the write operation is in progress and there are no write buffers available.2.7.7 Data Protection in the MultiMediaCardSame as for the MultiMediaCard mode.2.7.8 EraseSame as in MultiMediaCard mode2.7.9 Write ProtectionSame as in MultiMediaCard modeFigure 3-1 Timing Diagram of Data Input and Output3.5 Physical SpecificationsDimensions of Normal MMC(24mm x 32mm x 1.4mm)Dimensions of RS-MMC(24mm x 18mm x 1.4mm)rising and falling edges). If the host does not allow the switchable R OD implementation, a fix R CMD can be used. Consequently the maximum operating implementation, a fix R CMD can be used. Consequently the maximum operating frequency in the open drain mode has to be reduced in this case.4.4 SPI Bus Topology4.4.1 SPI Interface ConceptThe Serial Peripheral Interface (SPI) is a general-purpose synchronous serial interface originally found on certain Motorola micro-controllers. The MultiMediaCard SPI interface is compatible with SPI hosts available on the market. As any other SPI device the MultiMediaCard SPI channel consists of the following 4 signals:- CS : Host to card chip select signal- CLK : Host to card clock signal- DataIn : Host to card data signal- DataOut : Card to host data signalAnother SPI common characteristic, which is implemented in the MultiMediaCard card as well, is byte transfers. All data tokens are multiples of 8 bit bytes and always byte aligned to the CS signal. The SPI standard defines the physical link only and not the complete data transfer protocol. The MultiMediaCard uses a subset of the MultiMediaCard protocol and command set.4.4.2 SPI Bus TopologyThe MultiMediaCard card identification and addressing algorithms are replaced by hardware Chip Select (CS) signal. There are no broadcast commands. A card (slave) is selected, for every command, by asserting (active low) the CS signal (see Figure 4-3). The CS signal bust is continuously active for the duration of the SPI transaction (command, response and data). The only exception is card-programming time. At this time the host can de-assert the CS signal without affecting the programming process. The bi-directional CMD and DAT lines are replaced by unidirectional dataIn and dataOut signals. This eliminates the ability of executing commands while data is being read or written and, therefore, eliminates the sequential and multi block read/write operations. The SPI channel supports only single block read/write.Figure 4-3 SPI Bus SystemReadThe read access time is defined as the sum of the two times given by the CSD parameters TAAC and NSAC (refer to Table “Card Specific Data (CSD)”). These card parameters define the typical delay between the end bit of the read command and the start bit of the data block. This number is card dependent and should be used by the host to calculate throughput and the maximal frequency for stream read.WriteThe R2W_FACTOR field in the CSD is used to calculate the typical block program time obtained by multiplying the read access time by this factor. It applies to all write/erase commands (e.g. SET(CLEAR)_WRITE_PROTECT, PROGRAM_CSD(CID) and the block write commands). It should be used by the host to calculate throughput.EraseThe duration of an erase command will be (order of magnitude) the number of sectors to be erased multiplied by the block write delay.4.8 Card Identification ModeAll the data communication in the card identification mode uses only the command line (CMD). MultiMediaCard State Diagram (Card Identification Mode)Figure 4-2 MultiMediaCard State Diagram (Card Identification Mode)The host starts the card identification process in open drain mode with the identification clock rate f OD(generated by a push pull driver stage). The open drain driver stages on the CMD line allow the parallel card operation during card identification. After the bus is activated the host will request the cards to send their valid operation conditions with the command SEND_OP_COND (CMD1). Since the bus is in open drain mode, as long as there is more than one card with operating conditions restrictions, the host gets in the response to the CMD1 a “wired or” operation condition restrictions of those cards. The host then must pick a common denominator for operation and notify the application that cards with out of range parameters (from the host perspective) are connected to the bus. Incompatible cards go into Inactive State (refer to also Chapter “Operating Voltage Range Validation”). The busy bit in the CMD1 response can be used by a card to tell the host that it is still working on its power-up/reset procedure (e.g. downloading the register information from memory field) and is not ready yet for communication. In this case the host must repeat CMD1 until the busy bit is cleared. After an operating mode is established, the host asks all cards for their unique card identification (CID) number with the broadcast command ALL_SEND_CID (CMD2).All not already identified cards (i.e. those which are in Ready State) simultaneously start sending their CID numbers serially, while bit-wise monitoring their outgoing bitstream. Those cards, whose outgoing CID bits do not match the corresponding bits on the command line in any one of the bit periods, stop sending their CID immediately and must wait for the next identification cycle (cards stay in the Ready State). There should be only one card which successfully sends its full CID-number to the host. This card then goes into the Identification State. The host assigns to this card (using CMD3, SET_RELATIVE_ADDR) a relative card address (RCA, shorter than CID), which will be used to address the card in future communication (faster than with the CID). Once the RCA is received the card transfers to the Standby State and does not react to further identification cycles. The card also switches the output drivers from the open-drain to the push-pull mode in this state. The host repeats the identification process as long as it receives a response (CID) to its identification command (CMD2). When no card responds to this command, all cards have been identified. The time-out condition to recognize this, is waiting for the start bit for more than 5 clock periods after sending CMD24.8.1 Operating Voltage Range ValidationThe MultiMediaCard standards operating range validation is intended to support reduced voltage range MultiMediaCards. The MultiMediaCard supports the range of 2.7 V to 3.6V supply voltage. So the MultiMediaCard sends a R3 response to CMD1 which contains an OCR value of 0x80FF8000 if the busy flag is set to “ready” or 0x00FF8000 if the busy flag is active (refer to Chapter “Responses”). By omitting the voltage range in the command, the host can query the card stack and determine the common voltage range before sending out-of-range cards into the Inactive State. This bus query should be used if the host is able to select a common voltage range or if a notification to the application of non usable cards in the stack is desired. Afterwards, the host must choose a voltage for operation and reissue CMD1 with this condition sending incompatible cards into the Inactive State.4.9 Data Transfer ModeWhen in Standby State, both CMD and DAT lines are in the push-pull mode. As long as the content of all CSD registers is not known, the f PushPull clock rate is equal to the slow f OpenDrain clock rate. SEND_CSD (CMD9) allows the host to get the Card Specific Data (CSD register), e.g. ECC type, block length, card storage capacity, maximum clock rate etc..。