SDmini_spec_rev1.02

SDIO spec

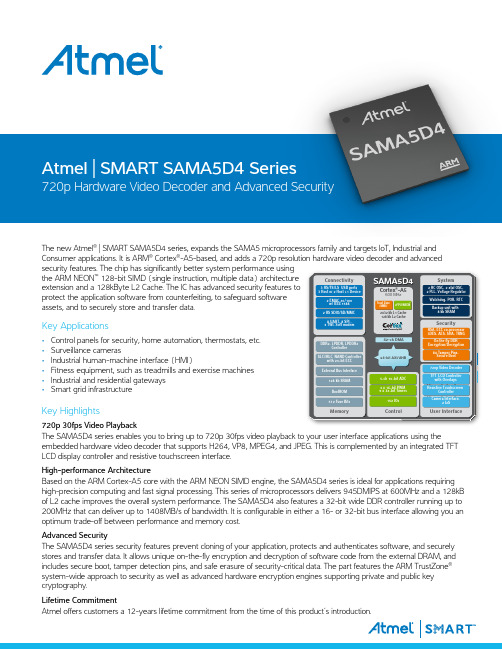

f in eo nIn fio nI n fTechnical Committee SD Card Associationf in eo nIn fi ne o n I nf in eo nIRevision HistoryDate Version Changes compared to previous issueApril 3, 2006 1.10 Simplified Version Initial ReleaseFebruary 8, 20072.00(1) Added method to change bus speed (Normal Speed up to 25MHzand High Speed up to 50 MHz)(2) Operational Voltage Requirement is extended to 2.7-3.6V(3) Combine sections 12 (Physical Properties) and 13 (MechanicalExtensions) and add miniSDIO to the new section 13 (Physical Properties)(4) Add Embedded SDIO ATA Standard Function Interface Code (5) Reference of Physical Ver2.00 supports SDHC combo card. (6) Some typos in Ver1.10 are fixed.f in eo nIn fi ne o n I nf in eo nI Release of SD Simplified SpecificationThe following conditions apply to the release of the SD simplified specification ("Simplified Specification") by the SD Card Association. The Simplified Specification is a subset of the complete SD Specification which is owned by the SD Card Association.Publisher:SD Association2400 Camino Ramon, Suite 375 San Ramon, CA 94583 USA Telephone: +1 (925) 275-6615 Fax: +1 (925) 886-4870 E-mail: office@Copyright Holder: The SD Card AssociationNotes:This Simplified Specification is provided on a non-confidential basis subject to the disclaimers below. Any implementation of the Simplified Specification may require a license from the SD Card Association or other third parties.Disclaimers:The information contained in the Simplified Specification is presented only as a standard specification for SD Cards and SD Host/Ancillary products and is provided "AS-IS" without any representations or warranties of any kind. No responsibility is assumed by the SD Card Association for any damages, any infringements of patents or other right of the SD Card Association or any third parties, which may result from its use. No license is granted by implication, estoppel or otherwise under any patent or other rights of the SD Card Association or any third party. Nothing herein shall be construed as an obligation by the SD Card Association to disclose or distribute any technical information, know-how or other confidential information to any third party.f in eo nIn fi ne o n I nf in eo nConventions Used in This DocumentNaming ConventionsSome terms are capitalized to distinguish their definition from their common English meaning. Words not capitalized have their common English meaning.Numbers and Number BasesHexadecimal numbers are written with a lower case “h” suffix, e.g., FFFFh and 80h. Binary numbers are written with a lower case “b” suffix (e.g., 10b).Binary numbers larger than four digits are written with a space dividing each group of four digits, as in 1000 0101 0010b.All other numbers are decimal.Key WordsMay: Indicates flexibility of choice with no implied recommendation or requirement.Shall: Indicates a mandatory requirement. Designers shall implement such mandatory requirements to ensure interchangeability and to claim conformance with the specification.Should: Indicates a strong recommendation but not a mandatory requirement. Designers should give strong consideration to such recommendations, but there is still a choice in implementation.Application NotesSome sections of this document provide guidance to the host implementers as follows: Application Note:This is an example of an application note.f in eo nIn fi ne o n I nf in eo nTable of Contents1. General Description.................................................................................................................................1 1.1 SDIO Features....................................................................................................................................1 1.2 Primary Reference Document.............................................................................................................1 1.3 Standard SDIO Functions....................................................................................................................1 2. SDIO Signaling Definition........................................................................................................................2 2.1 SDIO Card Types................................................................................................................................2 2.2 SDIO Card modes...............................................................................................................................2 2.2.1 SPI (Card mandatory support).....................................................................................................2 2.2.2 1-bit SD Data Transfer Mode (Card Mandatory Support).............................................................2 2.2.3 4-bit SD Data Transfer Mode (Mandatory for High-Speed Cards, Optional for Low-Speed).........2 2.3 SDIO Host Modes...............................................................................................................................2 2.4 Signal Pins..........................................................................................................................................3 3. SDIO Card Initialization............................................................................................................................4 3.1 Differences in I/O card Initialization.....................................................................................................4 3.2 The IO_SEND_OP_COND Command (CMD5).................................................................................10 3.3 The IO_SEND_OP_COND Response (R4)........................................................................................11 3.4 Special Initialization considerations for Combo Cards.......................................................................12 3.4.1 Re-initialize both I/O and Memory..............................................................................................12 3.4.2 Using a Combo Card as SDIO only or SD Memory only after Combo Initialization....................12 3.4.3 Acceptable Commands after Initialization..................................................................................12 3.4.4 Recommendations for RCA after Reset.....................................................................................12 3.4.5 Enabling CRC in SPI Combo Card.............................................................................................14 4. Differences with SD Memory Specification..........................................................................................15 4.1 SDIO Command List.........................................................................................................................15 4.2 Unsupported SD Memory Commands...............................................................................................15 4.3 Modified R6 Response......................................................................................................................16 4.4 Reset for SDIO..................................................................................................................................16 4.5 Bus Width..........................................................................................................................................16 4.6 Card Detect Resistor.........................................................................................................................17 4.7 Timings..............................................................................................................................................17 4.8 Data Transfer Block Sizes.................................................................................................................18 4.9 Data Transfer Abort...........................................................................................................................18 4.9.1 Read Abort.................................................................................................................................18 4.9.2 Write Abort.................................................................................................................................18 4.10 Changes to SD Memory Fixed Registers..........................................................................................18 4.10.1 OCR Register.............................................................................................................................19 4.10.2 CID Register...............................................................................................................................19 4.10.3 CSD Register.............................................................................................................................19 4.10.4 RCA Register.............................................................................................................................19 4.10.5 DSR Register.............................................................................................................................19 4.10.6 SCR Register.............................................................................................................................19 4.10.7 SD Status...................................................................................................................................19 4.10.8 Card Status Register..................................................................................................................19 5. New I/O Read/Write Commands............................................................................................................21 5.1 IO_RW_DIRECT Command (CMD52)..............................................................................................21 5.2 IO_RW_DIRECT Response (R5)......................................................................................................22 5.2.1 CMD52 Response (SD modes)..................................................................................................22 5.2.2 R5, IO_RW_DIRECT Response (SPI mode).............................................................................23 5.3 IO_RW_EXTENDED Command (CMD53). (24)f in eo nIn fi ne o n I nf in eo nI 5.3.2 Special Timing for CMD53 Multi-Block Read..............................................................................25 6. SDIO Card Internal Operation................................................................................................................26 6.1 Overview...........................................................................................................................................26 6.2 Register Access Time........................................................................................................................26 6.3 Interrupts...........................................................................................................................................26 6.4 Suspend/Resume..............................................................................................................................27 6.5 Read Wait..........................................................................................................................................27 6.6 CMD52 During Data Transfer............................................................................................................27 6.7 SDIO Fixed Internal Map...................................................................................................................27 6.8 Common I/O Area (CIA)....................................................................................................................28 6.9 Card Common Control Registers (CCCR).........................................................................................28 6.10 Function Basic Registers (FBR)........................................................................................................35 6.11 Card Information Structure (CIS).......................................................................................................37 6.12 Multiple Function SDIO Cards...........................................................................................................37 6.13 Setting Block Size with CMD53.........................................................................................................37 6.14 Bus State Diagram............................................................................................................................38 7. Embedded I/O Code Storage Area (CSA).............................................................................................39 7.1 CSA Access.......................................................................................................................................39 7.2 CSA Data Format..............................................................................................................................39 8. SDIO Interrupts.......................................................................................................................................40 8.1 Interrupt Timing.................................................................................................................................40 8.1.1 SPI and SD 1-bit Mode Interrupts ..............................................................................................40 8.1.2 SD 4-bit Mode............................................................................................................................40 8.1.3 Interrupt Period Definition ..........................................................................................................40 8.1.4 Interrupt Period at the Data Block Gap in 4-bit SD Mode (Optional)..........................................40 8.1.5 Inhibited Interrupts (Removed Section)......................................................................................40 8.1.6 End of Interrupt Cycles...............................................................................................................40 8.1.7 Terminated Data Transfer Interrupt Cycle ..................................................................................41 8.1.8 Interrupt Clear Timing.................................................................................................................41 9. SDIO Suspend/Resume Operation........................................................................................................42 10. SDIO Read Wait Operation.....................................................................................................................43 11. Power Control.........................................................................................................................................44 11.1 Power Control Overview....................................................................................................................44 11.2 Power Control support for SDIO Cards.............................................................................................44 11.2.1 Master Power Control ................................................................................................................44 11.2.2 Power Selection.........................................................................................................................45 11.2.3 High-Power Tuples.....................................................................................................................45 11.3 Power Control Support for the SDIO Host.........................................................................................45 11.3.1 Version 1.10 Host.......................................................................................................................45 11.3.2 Power Control Operation............................................................................................................46 12. High-Speed Mode...................................................................................................................................47 12.1 SDIO High-Speed Mode....................................................................................................................47 12.2 Switching Bus Speed Mode in a Combo Card...................................................................................47 13. SDIO Physical Properties......................................................................................................................48 13.1 SDIO Form Factors...........................................................................................................................48 13.2 Full-Size SDIO ..................................................................................................................................48 13.3 miniSDIO...........................................................................................................................................48 14. SDIO Power.............................................................................................................................................48 14.1 SDIO Card Initialization Voltages......................................................................................................48 14.2 SDIO Power Consumption................................................................................................................48 15. Inrush Current Limiting..........................................................................................................................50 16. CIS Formats.. (51)f in eo nIn fi ne o n I nf in eo nI 16.2 Basic Tuple Format and Tuple Chain Structure.................................................................................51 16.3 Byte Order Within Tuples ..................................................................................................................51 16.4 Tuple Version ....................................................................................................................................52 16.5 SDIO Card Metaformat......................................................................................................................52 16.6 CISTPL_MANFID: Manufacturer Identification String Tuple..............................................................53 16.7 SDIO Specific Extensions..................................................................................................................53 16.7.1 CISTPL_FUNCID: Function Identification Tuple.........................................................................53 16.7.2 CISTPL_FUNCE: Function Extension Tuple..............................................................................54 16.7.3 CISTPL_FUNCE Tuple for Function 0 (common).......................................................................54 16.7.4 CISTPL_FUNCE Tuple for Function 1-7....................................................................................55 16.7.5 CISTPL_SDIO_STD: Function is a Standard SDIO Function.....................................................58 16.7.6 CISTPL_SDIO_EXT: Tuple Reserved for SDIO Cards...............................................................58 Appendix A.....................................................................................................................................................59 A.1 SD and SPI Command List....................................................................................................................59 Appendix B.....................................................................................................................................................61 B.1 Normative References...........................................................................................................................61 Appendix C.....................................................................................................................................................62 C.1 Abbreviations and Terms...................................................................................................................62 Appendix D.. (64)f in eo nIn fi ne o n I nf in eo nI Table of TablesTable 3-1 OCR Values for CMD5.....................................................................................................................10 Table 4-1 Unsupported SD Memory Commands.............................................................................................16 Table 4-2 R6 response to CMD3.....................................................................................................................16 Table 4-3 SDIO R6 Status Bits.........................................................................................................................16 Table 4-4 Combo Card 4-bit Control................................................................................................................17 Table 4-5 Card Detect Resistor States.............................................................................................................17 Table 4-6 is blanked.........................................................................................................................................17 Table 4-7 SDIO Status Register Structure .......................................................................................................20 Table 5-1 Flag data for IO_RW_DIRECT SD Response..................................................................................23 Table 5-2 IO_RW_ EXTENDED command Op Code Definition.......................................................................24 Table 5-3 Byte Count Values ...........................................................................................................................25 Table 6-1 Card Common Control Registers (CCCR).......................................................................................29 Table 6-2 CCCR bit Definitions........................................................................................................................34 Table 6-3 Function Basic Information Registers (FBR)....................................................................................35 Table 6-4 FBR bit and field definitions.............................................................................................................36 Table 6-5 Card Information Structure (CIS) and reserved area of CIA.............................................................37 Table 11-1 Reference Tuples by Master Power Control and Power Select......................................................45 Table 16-1 Basic Tuple Format........................................................................................................................51 Table 16-2 Tuples Supported by SDIO Cards..................................................................................................52 Table 16-3 CISTPL_MANFID: Manufacturer Identification Tuple.....................................................................53 Table 16-4 CISTPL_FUNCID Tuple.................................................................................................................53 Table 16-5 CISTPL_FUNCE Tuple General Structure.....................................................................................54 Table 16-6 TPLFID_FUNCTION Tuple for Function 0 (common)....................................................................54 Table 16-7 TPLFID_FUNCTION Field Descriptions for Function 0 (common).................................................54 Table 16-8 TPLFID_FUNCTION Tuple for Function 1-7..................................................................................55 Table 16-9 TPLFID_FUNCTION Field Descriptions for Functions 1-7.............................................................57 Table 16-10 TPLFE_FUNCTION_INFO Definition...........................................................................................57 Table 16-11 TPLFE_CSA_PROPERTY Definition...........................................................................................57 Table 16-12 CISTPL_SDIO_STD: Tuple Reserved for SDIO Cards................................................................58 Table 16-13 CISTPL_SDIO_EXT: Tuple Reserved for SDIO Cards.................................................................58 Table A-14 SD Mode Command List................................................................................................................59 Table A-15 SPI Mode Command List (60)f in eo nIn fi ne o n I nf in eo nI Table of FiguresFigure 2-1 Signal connection to two 4-bit SDIO cards.......................................................................................3 Figure 3-1 SDIO response to non-I/O aware initialization..................................................................................4 Figure 3-2 Card initialization flow in SD mode (SDIO aware host)....................................................................7 Figure 3-3 Card initialization flow in SPI mode (SDIO aware host)....................................................................9 Figure 3-4 IO_SEND_OP_COND Command (CMD5).....................................................................................10 Figure 3-5 Response R4 in SD mode...............................................................................................................11 Figure 3-6 Response R4 in SPI mode..............................................................................................................11 Figure 3-7 Modified R1 Response....................................................................................................................11 Figure 3-8 Re-Initialization Flow for I/O Controller...........................................................................................13 Figure 3-9 Re-Initialization Flow for Memory controller ...................................................................................13 Figure 5-1 IO_RW_DIRECT Command...........................................................................................................21 Figure 5-2 R5 IO_RW_DIRECT Response (SD modes)..................................................................................22 Figure 5-3 IO_RW_DIRECT Response in SPI Mode.......................................................................................23 Figure 5-4 IO_RW_EXTENDED Command.....................................................................................................24 Figure 6-1 SDIO Internal Map..........................................................................................................................28 Figure 6-2 State Diagram for Bus State Machine (38)f in eo nIn fi ne o n I nf in eo nI 1. General DescriptionThe SDIO (SD Input/Output) card is based on and compatible with the SD memory card. This compatibility includes mechanical, electrical, power, signaling and software. The intent of the SDIO card is to provide high-speed data I/O with low power consumption for mobile electronic devices. A primary goal is that an SDIO card inserted into a non-SDIO aware host shall cause no physical damage or disruption of that host or it’s software. In this case, the SDIO card should simply be ignored. Once inserted into an SDIO aware host, the detection of the card proceeds via the normal means described in this specification with some extensions. In this state, the SDIO card is idle and draws a small amount of power (15 mA averaged over 1 second). During the normal initialization and interrogation of the card by the host, the card identifies itself as an SDIO card. The host software then obtains the card information in a tuple (linked list) format and determines if that card’s I/O function(s) are acceptable to activate. This decision is based on such parameters as power requirements or the availability of appropriate software drivers. If the card is acceptable, it is allowed to power up fully and start the I/O function(s) built into it.1.1 SDIO Features• Targeted for portable and stationary applications• Minimal or no modification to SD Physical bus is required • Minimal change to memory driver software• Extended physical form factor available for specialized applications • Plug and play (PnP) support• Multi-function support including multiple I/O and combined I/O and memory • Up to 7 I/O functions plus one memory supported on one card. • Allows card to interrupt host• Operational Voltage range: 2.7-3.6V (Operational Voltage is used for Initialization) • Application Specifications for Standard SDIO Functions. • Multiple Form Factors:• Full-Size SDIO • miniSDIO1.2 Primary Reference DocumentThis specification is based on and refers extensively to the SDA document:SD Memory Card SpecificationsPart 1 PHYSICAL LAYER SPECIFICATION Version 2.00 May 9, 2006The reader is directed to this document for more information on the basic operation of SD cards. In addition, other documents are referenced in this specification. A complete list can be found in appendix B.1.This specification can apply to any released versions of Physical Layer Specification after Version 2.00.1.3 Standard SDIO FunctionsAssociated with the base SDIO specification, there are several Application Specifications for Standard SDIO Functions. These common functions such as cameras, Bluetooth cards and GPS receivers have a standard register interface, a common operation method and a standard CIS extension. Implementation of the standard interfaces are optional for any card vendor, but compliance with the standard allows the use of standard drivers and applications which will increase the appeal of these cards to the consumer. Full information on these standard interfaces can be found in the Application Specifications for Standard SDIO Functions maintained by the SDA.。

MICRO SD 3.0 SPEC

MicroSD3.0 UHS-I SpecificationRev B2Sep-23-2014NOTE: INFORMATION IN THIS PRODUCT SPECIFICATION IS SUBJECT TO CHANGE AT ANYTIME WITHOUT NOTICE, ALL PRODUCT SPECIFICATIONS ARE PROVIDED FOR REFERENCE ONLY.TO ANY INTELLECTUAL, PROPERTY RIGHTS IN LONGSYS ELECTRONICS CO.,LTD. ALL INFORMATION IN THIS DOCUMENT IS PROVIDED.Contents1. Overview (4)1.1 Product Description (4)1.2 Features Summary (4)2. Pin Assignment (5)3. Product List (5)4. Current Consumption (7)5. Operational Environment (7)6. Card Registers (7)6.1 Card Identification Register (CID) (7)6.2 Card-Specific Data Register (CSD) (8)7. Bus Operation Conditions (9)7.1 For 3.3V Signaling (9)7.1.1 Threshold Level for High Voltage Range (9)7.1.2 Peak Voltage and Leakage Current (9)7.1.3 Bus Signal Line Load (10)7.1.4 Bus Signal Levels (10)7.1.5 Bus Timing(Default) (10)7.1.6 Bus Timing(High-Speed Mode) (12)7.2 For 1.8V Signaling (13)7.2.1 Threshold Level for High Voltage Range (13)7.2.2 Peak Voltage and Leakage Current (13)7.2.3 Bus Timing Specification in SDR12 (13)7.2.3.1 Clock Timing (14)7.2.3.2 Card Input Timing (14)7.2.3.3 Card Output Timing (14)7.2.3.3.1 Output Timing of Fixed Data Window (15)7.2.3.3.2 Output Timing of Variable Window (SDR104) (15)8. Physical Dimension (15)1. Overview1.1 Product DescriptionThe Longsys MicroSD3.0 Cards are fully compatible with Physical Layer Specification, Version 3.0 (this specification is available from the SDA), support Ultra High Speed(UHS), provides high write/read speed and high IOPS, It was designed to meet the security, high capacity, high performance and environmental requirements inherent in next generation consumer electronic devices.The MicroSD3.0 card system is a new mass-storage system based on innovations in semiconductor technology. It has been developed to provide an inexpensive, mechanically robust storage medium in card form for multimedia consumer applications. MicroSD card allows the design of inexpensive players and drivers without moving parts. A low power consumption and a wide supply voltagerange favors consumer electronic devices.Ultra High Speed (UHS) CardIt provides up to 104MB/s* performance. UHS cards are backward compatible on non-UHS hosts. *Based on internal testing; performance may vary depending upon host device.1 megabyte(MB)=1,000,000bytes.1.2 Features Summary-Capacity: 4GB/8GB/16GB/32GB/64GB/128GB-Complies to SD specifications version 3.00-Voltage operating: 2.7~3.6V.-Targeted for portable and stationary applications-Greater Performance Choices-Bus Speed Mode:DS-Default Speed mode: 3.3V signaling, frequency up to 25MHz, up to 12.5MB/secHS-High Speed mode: 3.3V signaling, frequency up to 50MHz, up to 25MB/secSDR12-1.8V signaling, frequency up to 25MHz, up to 12.5MB/secSDR25-1.8V signaling, frequency up to 50MHz, up to 25MB/secSDR50-1.8V signaling, frequency up to 100MHz, up to 50MB/secSDR104-1.8V signaling, frequency up to 208MHz, up to 104MB/secDDR50-1.8V signaling, frequency up to 50MHz, sampled on both clock edges, up to 50MB/s-Switch function command supports Bus Speed Mode, Command System, Drive Strength, and future functions.-password protection (CMD42-LOCK_UNLOCK)-Sophisticated system for error recovery including a powerful ECC-Global Wear Leveling-Power management for low power operation-Add TF card adapter can be used in SD card socket.2. Pin AssignmentPin No.SD ModeName Type Description 1 Dat2 I/O/PP Data Line [Bit 2]2CD/DAT3I/O/PP3Card Detect / Data Line [Bit 3]3 CMD PP Command/Response4 VDD S Supply voltage5 CLK I Clock6 VSS S Supply voltage ground7 DAT0 I/O/PP Data Line [Bit 0] 8DAT1I/O/PPData Line [Bit 1]S: power supply; I: input; O: output; PP: I/O using push-pull driversTable 1: Pin Assignment3. Product ListPart NumberCapacityActual Size(Min ) (note2)Speed Class (note1) Write Speed (Typical) (note1) UHS-I (note1)TypeNCIX4XX-004G 4GB 3.6GB Class4 4 MB/S SDR50/SDR104 SDHC NCIX6XX-004G 4GB 3.6GB Class6 6 MB/S SDR50/SDR104 SDHC NCIXAXX-004G 4GB 3.6GB Class10 10 MB/S SDR50/SDR104 SDHC NCIX4XX-008G 8GB 7.3GB Class4 4 MB/S SDR50/SDR104 SDHC NCIX6XX-008G8GB7.3GBClass66 MB/SSDR50/SDR104SDHCNCIXAXX-008G 8GB 7.3GB Class10 10 MB/S SDR50/SDR104 SDHC NCIXBXX-008G 8GB 7.3GB Class10 133X SDR104 SDHC NCIXCXX-008G 8GB 7.3GB Class10 150X SDR104 SDHC NCIXAXX-016G 16GB 14.7GB Class10 10 MB/S SDR50/SDR104 SDHC NCIXBXX-016G 16GB 14.7GB Class10 133X SDR104 SDHC NCIXCXX-016G 16GB 14.7GB Class10 150X SDR50/SDR104 SDHC NCIXDXX-016G 16GB 14.7GB Class10 233X SDR104 SDHC NCIXEXX-016G 16GB 14.7GB Class10 266X SDR104 SDHC NCIXFXX-016G 16GB 14.7GB Class10 300X SDR104 SDHC NCIXAXX-032G 32GB 29.4GB Class10 10 MB/S SDR50/SDR104 SDHC NCIXBXX-032G 32GB 29.4GB Class10 133X SDR104 SDHC NCIXCXX-032G 32GB 29.4GB Class10 150X SDR104 SDHC NCIXDXX-032G 32GB 29.4GB Class10 233X SDR50/SDR104 SDHC NCIXEXX-032G 32GB 29.4GB Class10 266X SDR104 SDHC NCIXFXX-032G 32GB 29.4GB Class10 300X SDR104 SDHC NCIXGXX-032G 32GB 29.4GB Class10 333X SDR104 SDHC NCIXHXX-032G 32GB 29.4GB Class10 400X SDR104 SDXC NCIXAXX-064G 64GB 58.9GB Class10 10 MB/S SDR50/SDR104 SDXC NCIXHXX-064G 64GB 58.9GB Class10 333X SDR104 SDXC NCIXHXX-064G 64GB 58.9GB Class10 400X SDR104 SDXC NCIXBXX-128G 128GB 118GB Class10 150X SDR104 SDXCTable 2: Product Listnote1:*Measurement based on VTE3100 TestMetrix device, SW 3.2A software or up version, test script:SD_Card(Spec3.0_High&Extended-Capacity_UHS-I and Non-UHS-I)_Compliance [rev31R].vte*SDR50@SDR50-100MHzSDR104@SDR104-208MHz.*1X=150KByte/snote2: *1Gigabyte (GB) = 1 billion bytes. Some capacity not available for data storage*Maximum speed differs from the bus I/F speed. It varies depending upon the card performance. The average speed that a device writes to a MicroSD memory card may vary depending upon the device and the operation it is performing. The speed may also depend on how other data is stored on the MicroSD memory card. Normal and high-speed cards can also be used with UHS-I host devices, but the high performance enabled by a UHS-I host device can only be achieved with a UHS-I memory card.4. Current ConsumptionStandby current: 500uA(Maximum value)Standby current: 150uA(average value)Operating current: 250mA(Maximum value)Operating current: 100mA(average value)*Test condition: Realtek5308 card reader (Voltage 3.3V), Fluke289C multi-meter.5. Operational EnvironmentParameter RangeTemperatureOperating 0℃~ 70℃Non-Operating -40℃~ 85℃HumidityOperating 25% to 85%, non-condensing Non-Operating 25% to 85%, non-condensingDurability insertion/removal cycles 10,000 Data Retention10yearsTable 3: Operational Environment6. Card Registers6.1 Card Identification Register (CID)The Card Identification (CID) register is 128 bit wide. It contains the card identification information used during the card identification phase. Every individual flash card shall have a unique identification number.The structure of the CID register is defined in the following table.CID Bit Width Name Field[127:120] 8 ManufactureID MID [119:104] 16 OEM/ApplicationID OID [103:64] 40 ProductName PNM [63:56] 8 ProductRevision PRV [55:24] 32 Product Serial Number PSN[23:20] 4 Reserved ---[19:8] 12 ManufacturingDate MDT [7:1] 7 CRC7 check sum CRC[0] 1 Notused,always”1 ---Table 4: CID Table- All contents in the CID table are programmable; Manufacturers can update the CID data through utility.- Manufacturers should license MID and OID field form the SD Card Association(SDA)6.2 Card-Specific Data Register (CSD)The Card-Specific Data register provides information on how to access the card contents. The defines the data format, error correction type, maximum data access time, data transfer speed, whether the DSR register can be used etc. The programmable part of the register can be changed by CMD27.The CSD Table Version 2.0(as shown below) is applied to SDHC and SDXC Cards. Note that bits [15:0] are programmable by the host side. Refer to the SD specification for detailed information CSD BitWidth NameFieldValueNote [127:126] 2 CSD structureCSD_STRUCTURE 01bV2.0(>2GB Card) [125:120] 6 Reserved --- --- --- [119:112]8Data read access-time 1 (TAAC)0E h[111:104] 8 Data read access-time2 in CLK cycles(NSA*100)(NSAC) 00 h[103:96] 8 Max data transfer rate (TRAN_SPEED)32 h5A h 0B h 2B h[95:84] 12 Card command classes CCC5B5 h[83:80] 4 Max. read data block length (READ_BL_LEN) 9 h 512 Byte[79] 1 Partial block read allowed (READ_BL_PARTIA L)[78]1Write block misalignment(WRITE_BLK_MISA LIGN)[77] 1 Read block misalignment(READ_BLK_MISAL IGN) 0[76] 1 DSR implemented DSR_IMP x[75:70] 6 Reserve --- --- [69:48] 22 Device size C_SIZE xxxxxxh[47] 1 Reserved --- 0 [46] 1 Erase single block enable (ERASE_BLK_EN) 1[45:39] 7 Erase sector size (SECTOR_SIZE) 7F h [38:32] 7 Write protect group size C_SIZE0 b[31] 1 Write protect group enable --- 0 [30:29] 2 Reserved(ERASE_BLK_EN) 0 b [28:26] 3 Write speed factor(SECTOR_SIZE)010 b [25:22]4Max. write data block (WP_GRP_SIZE)9 hlength[21] 1 Partial block write allowed (WP_GRP_ENABLE)[20:16] 5 Reserved --- ---[15] 1Fileformatgroup (FILE_FORMAT_GRP)[14] 1Copyflag COPY x[13] 1Permanentwriteprotection PERM_WRITE_PROTECTx[12] 1 Temporary write protection TMP_WRITE_PROTECTx[11:10] 2 File format (FILE_FORMAT) 00 b[9:8] 2 Reserved --- 00b[7:1] 7 CRC CRC ---[0] 1Notused,always’1’ --- 1Table 5: CSD (Version 2.0) Table7. Bus Operation Conditions7.1 For 3.3V Signaling7.1.1 Threshold Level for High Voltage RangeParameter Symbol Min Max Unit Remark Supply Voltage V DD 2.7 3.6 VOutput High Voltage V OH 0.75*V DD V I OH=2mA V DD min Output Low Voltage V OL0.125*V DD V I OL=2mA V DD min Input High Voltage V IH 0.625*V DD V DD+0.3 VInput Low Voltage V IL V ss-0.3 0.25*V DD VPower Up Time 250 ms From 0V to V DD minTable 6: Threshold Level for High Voltage7.1.2 Peak Voltage and Leakage CurrentParameter Symbol Min Max Unit Remark Peak voltage on all lines VAll InputsInput Leakage Current -10 10 uAAll OutputsOutput Leakage Current -10 10 uATable 7: Peak Voltage and Leakage Current7.1.3 Bus Signal Line LoadParameter SymbolMin Max Unit RemarkPull-up resistance R CMDR DAT10 100 KΏTo prevent bus floatingTotal bus capacitance for each signal line C L40 pF1 card C HOST+C BUS shall notexceed 30pFCard capacitance foreach signal pinC CARD10 pFMaximum signalinductance16 nHPull-up resistance insidecard(pin1)R DAT3 10 90 KΏMay be used for card detectionCapacity Connected toPower Line C C 5 uF To prevent inrush currentTable 8: Bus Operating Conditions - Signal Line's Load7.1.4 Bus Signal LevelsAs the bus can be supplied with a variable supply voltage,all sigelnal levels are related to the supply valtage.Figure 1: Bus Signal LevelsTo meet the requirements of the the JEDEC specification JESD8-1A and JESD8-7,the card input and output voltages shall be within the specifide ranges shown in Table 6 for any V DD of the allowed valtage range.7.1.5 Bus Timing(Default)Figure 2:Card input Timing(Default Speed Card)Figure 3:Card Output Timing(Default Speed Mode)Unit RemarkParameter Symbo Min. MaxClock CLK (All values are referred to min(V IH)and max(V IL))Clock frequency data transfer fpp 0 25 MHz C≤ 10pF (1 card)CARDClock frequency Identification f0(1)/100 400 KHz C CARD≤ 10pF (1 card)ODClock low time t WL 10 ns C CARD≤ 10pF (1 card) Clock high time t WH 10 ns C CARD≤ 10pF (1 card) Clock rise time t TLH10 ns C CARD≤ 10pF (1 card) Clock fall time t THL10 ns C CARD≤ 10pF (1 card) Inputs CMD, DAT (referenced to CLK)Input set-up time t ISU 5 ns C CARD≤ 10pF (1 card)Input hold time t TH 5 nsC CARD≤ 10pF (1 card) Outputs CMD, DAT (referenced to CLK)Output Delay time during Datat ODLY 0 14 ns C L≤ 40pF (1 card) Transfer ModeOutput Hold time t OH 0 50 ns C L≤ 40pF (1 card) (1)0 Hz means to stop the clock.The given minimum frequency range is for cases were continuesclock is required (refer to Chapter 4.4-Clock Control)Table 9:Bus Timing-Parameters Values (Default Speed)7.1.6 Bus Timing(High-Speed Mode)Figure 4: Card Input Timing(High Speed Card)Figure5: Card Output Timing(High Speed Mode)Parameter Symbo Min. Max Unit RemarkClock CLK (All values are referred to min(V IH)and max(V IL))Clock frequency data transfer fpp 0 50 MHz CCARD≤ 10pF (1 card) Clock low time t WL 7 ns C CARD≤ 10pF (1 card) Clock high time t WH 7 ns C CARD≤ 10pF (1 card) Clock rise time t TLH 3 ns C CARD≤ 10pF (1 card) Clock fall time t THL 3 ns C CARD≤ 10pF (1 card) Inputs CMD, DAT (referenced to CLK)Input set-up time t ISU 6 ns C CARD≤ 10pF (1 card) Input hold time t TH 2 nsC CARD≤ 10pF (1 card) Outputs CMD, DAT (referenced to CLK)Output Delay time during DataTransfer Modet ODLY14 ns C L≤ 40pF (1 card) Output Hold time t OH 2.5 ns C L≥ 15pF (1 card)Total System capacitance for each line1C L40 pF1card1)In order to satisty sever timing , host shall drive only one card.Table 10 :Bus Tinming – Parameters Values(High Speed)7.2 For 1.8V Signaling7.2.1 Threshold Level for High Voltage RangeParameter Symbol Min Max Unit Remark Supply Voltage V DD 2.7 3.6 VRegulator Voltage V DDIO 1.7 1.95 V Generated by V DD Output High Voltage V OH 1.4 V I OH=2mA V DD min Output Low Voltage V OL0.45 V I OL=2mA V DD min Input High Voltage V IH 1.27 2.0 VInput Low Voltage V IL V ss-0.3 0.58 VTable 11: Threshold Level for High Voltage7.2.2 Peak Voltage and Leakage CurrentParameter Symbol Min Max Unit Remark Input Leakage Current -2 2 uA DAT3 pull-up isdisconnectedTable 12: Peak Voltage and Leakage Current7.2.3 Bus Timing Specification in SDR12, SDR25, SDR50 and SDR104 Modes7.2.3.1 Clock TimingFigure 6: Clock Signal TimingSymbolMinMaxUnitRemarkt CLK 4.8 - ns208MHz (Max.), Between rising edge,V CT =0.975Vt CR , t CF - 0.2* t CLK nst CR , t CF < 2.00ns (max.) at 208MHz, C CARD =10pF t CR , t CF < 2.00ns (max.) at 100MHz, C CARD =10pFThe absolute maximum value of t CR , t CF is 10ns regardless of clock frequence. Clock Duty3070%Table 13:Clock Signal Timing7.2.3.2 Card Input TimingFigure 7: Card Input TimingSymbolMinMaxUnitSDR104 modet IS 1.40 - ns C CARD = 10pF , V CT = 0.975V t IH 0.80 ns C CARD = 5pF , V CT = 0.975V SymbolMinMaxUnitSDR12, SDR25 and SDR50 modest IS 3.00 - ns C CARD = 10pF , V CT = 0.975V t IH 0.80 - nsC CARD = 5pF , V CT = 0.975V Table 14: SDR50 and SDR104 Input Timing7.2.3.3 Card Output Timing7.2.3.3.1 Output Timing of Fixed Data Window (SDR12, SDR25 and SDR50)Figure 8:Output Timing of Fixed Date WindowSymbolMinMaxUnitRemarkt ODLY - 7.5 nst CLK ≥10.0ns, CL=30pF, using driver Type B,for SDR50. t ODLY 14 nst CLK ≥20.0ns, CL=40pF, using driver Type B,for SDR25 and SDR12. t OH1.5-nsHold time at the t ODLY (min.). CL=15pFTable 15: Output Timing of Fixed Data Window7.2.3.3.2 Output Timing of Variable Window (SDR104)Figure 9: Output Timing of Variable Data WindowSymbol Min Max Unit Remarkt OP -2UICard Output Phase△t OP-350 +1550 psDelay variation due to temperature change after tuningt ODW 0.60 - UIt ODW = 2.88ns at 208MHz Table 16: Output Timing of Variable Data Window8. Physical DimensionType MeasurementLength15mm+/-0.1mm(B)Width11mm+/-0.1mm(A)Thickness 1.0mm+/-0.1mm(C)0.7mm+/-0.1mm(C1)Weight 0.33gram MaxTable 17: MicroSD card physical dimension (Unit in mm) Mechanical form factor as follows: (Unit in mm)Figure 10: Bottom ViewFigure 11: TOP View。

博世 安全系统-法拉登VIVIDIO应用程序 步骤配置 说明书

From Nuremberg BT-VS/MKP-XPT Product Management 20.04.2023Release LetterProduct: VIDEOJET decoder 7000 VJD-7513Version: Firmware 10.40.0055This letter contains latest information about the above-mentioned product.1. GeneralThis firmware release 10.40.0055 is a feature release based on FW 10.31.0005.Changes since last release FW 10.31.0005 are marked in blue.VIDEOJET decoder 7000 uses robust, fan-less technology designed for ambitious environmental conditions while providing maximum performance on minimum space in a nicely designed industrial housing.VIDEOJET decoder 7000 displays video from Standard Definition (SD), High Definition (HD), 4K Ultra High Definition (UHD), and Megapixel (MP) cameras and encoders using H.265, H.264 or MPEG-4 encoding at up to 60 frames per second over IP networks.VIDEOJET decoder 7000 is the successor of VIDEOJET decoder 8000 (VJD-8000, VJD-8000-N). It is using the same housing but comes with different video output interfaces and provides improved performance and functionality.Notes:•Firmware update may take several minutes due to a large cumulative Microsoft patch.•This firmware includes OpenSSL.From NurembergBT-VS/MKP-XPT Product Management 20.04.20232. Applicable products•VIDEOJET decoder 7000, VJD-75133. New Features•SRTP for encrypted multicast traffic is supported. This allows fully secured communication with and video streaming from CPP13 and CPP14 cameras in multicast environments.•SNMPv3 trap service has been added, including the support of SNMP-related RCP+ commands for configuration.• A JPEG snapshot is now possible from each of the displays, including JPEG quality settings parameter.•Display order can be re-arranged in case Windows display detection differs from mechanical order.•The default layout is depending on the display number to simplify the identification of display order. The number of video windows per display increases as square of the display number.•The web interface of the decoder has been updated to the latest style guide and re-structured to ease usage for installation, licensing, and integration purposes.o The new web pages provide links to documentation and include a live preview.o Maintenance log file creation and download is supported by a workflow mechanism.o A keyboard emulator supports initial setup for IP Matrix even without keyboard connected.From NurembergBT-VS/MKP-XPT Product Management 20.04.20234. Changes•The Video SDK as one of the core components for the decoder firmware has been updated to latest version 6.40, providing a great number of improvements and fixes, mainly aroundONVIF and RTSP support, increasing the overall robustness.•An issue is fixed for banner upload when banners are activated.•An issue is fixed for zooming out in client dewarping mode of panoramic camera streams.•An issue is fixed where client dewarping was not working on line 1 of a panoramic camera in onboard dewarping mode. Onboard dewarping is only available for lines 2 and higher, line 1 always provides the full warped image circle.•An issue with DNS server configuration is fixed.•An issue is fixed where CPP13 and CPP14 cameras were not correctly connected in camera sequences.•Maintenance log file download is improved, supported by the new web interface structure.•An issue is fixed where daylight saving time was incorrectly reflected in time zone offset calculation.5. System RequirementsFor configuration purposes:•Configuration Manager 7.61 or newerFor operation purposes:•Bosch Video Management System 12.0 or higherNote that not all features may be supported by BVMS yet.Please refer to BVMS release notes.From NurembergBT-VS/MKP-XPT Product Management 20.04.20236. Restrictions; Known Issues•Connecting encrypted streams without proper signalling may result in crashing the software decoder instance, resulting in black video displayed.•Alarms will not be signaled with a red border around the cameo if connection was established using CONNECT_PRIMITIVE.•Using CONNECT_PRIMITIVE via TCP is not possible.•CONNECT_PRIMITIVE does not support "first available" feature.•Audio may remain audible despite layout change to other than single view.•RCP+ command CONF_ALARM_CONNECT_TO_IP is not supported.•Alarm connection does not support audio, nor does it include metadata.•Maximum password length is 19 characters.•With “Reconnect last devices” active camera connections are stored and automatically reconnected after reboot. To avoid deadlock in case of an overload situation the automaticreconnect will be deactivated after the decoder was forced into reboot for ten times within 10 minutes.•Monitors may be swapped after update. Swap back is possible using Configuration Manager.•IP Matrix pre-requisites for multi-decoder clustering:o Fixed IP addresses must be assigned; DHCP configuration is not functional.o Passwords for service level must be same on all clustered decoders.o Passwords for user level must be same on all clustered decoders.•After removing a slave decoder from the IP Matrix master, both decoders must be restarted.•Camera sequences are paused when picture-in-picture mode is activated.•Time related settings may appear in Configuration Manager only with delay or after a reboot.•Monitors connected to the Display Port via USB-C may not always be detected during booting.In this case, unplug and reconnect the adapter or cable to the monitor. If only one monitor isused it is recommended to connect to the direct HDMI output.•Log file download stability may be affected by workload of decoder. As a workaround, the download may need to be repeated, or the workload of the decoder may need to be reduced (disconnect all camera streams).•Time zone configuration is only supported via TIME_ZONE_STRING.•The KBD-DIGITAL keyboard is locked automatically during start-up of the decoder, or with re-connect. It will be unlocked after entering the PIN but the lock screen will remain until the next action on the keyboard.•Certificates used with the decoder must not have any Windows policies defined.•DNS resolution is not implemented yet, thus time server entry only works with IP addresses.•Dewarping zoom does not work correctly for panoramic cameras in on-board dewarping mode for camera line 1.•Overload messages and traps may appear too sensitive in cases where display refresh rates are lower than video stream frame rates.From NurembergBT-VS/MKP-XPT Product Management 20.04.20237. Previous Revisions7.1. New Features with 10.31.0005•Support for HOST_NAME to get and set the device’s hostname; only supported in extended configuration mode.•Support for DNS_SERVER_IP_STRING to get and set primary and secondary DNS server IPv4 addresses.7.2. Changes with 10.31.0005•Optimized transparent data processing time to allow adequate transparent data pass-through for serial PTZ keyboard.•An issue is fixed to apply e-PTZ presets correctly in camera sequences.•Feature loss due to suppressing encrypted UDP multicast connections for Bosch IP cameras with firmware 8 and higher, and fall back to TCP, tunneled via HTTPS control connection.(This feature will be added again with FW 10.40.)From NurembergBT-VS/MKP-XPT Product Management 20.04.20237.3. New Features with 10.30.0005•The default setting for Automatic IPv4 address assignment is set to “DHCP plus Link-Local”.Though this might seem a small change, it may have an impact:The former default IP address 192.168.0.200 will virtually become obsolete.Instead, the camera will assign itself an auto-IP address out of the range 169.254.1.0 to169.254.254.255 as long as there is no other IP address assigned by a DHCP server.(https:///wiki/Link-local_address)The advantage is that there are no more duplicate IP addresses, which is consideredprohibited in a network.•Network authentication 802.1x with EAP/TLS has been added.Please note that the server certificate needs to get the usages ‘Trust’ and ‘EAP_TLS_Trusted’ assigned.The client certificate will get the necessary usages assigned automatically.•The possibility of large banner overlays has been introduced.o Banners can be uploaded as images that can be displayed over three areas: top, center and bottom. The images are scaled to fill the area and cropped wherenecessary.o Banners can be sequenced with a configurable dwell time.o Configuration Manager 7.60 is supporting this with upload and banner sequence configuration, including banner previews.•Set and recall prepositions for moving cameras (AUTODOME, MIC) as well as for ONVIF PTZ cameras via keyboard has been added to the IP Matrix functionality.•Images can be uploaded to the decoder for two purposes, using Configuration Manager. The images shall be in JPG format and must be named as follows:o‘monitor background’ image, shown as background of an empty video window: ‘Logo.jpg’o‘’no camera’ image, shown on connection failure: ‘NoCamLogo.jpg’7.4. Changes with 10.30.0005•An issue was fixed where uploading a new video loss image did not break the software seal.From NurembergBT-VS/MKP-XPT Product Management 20.04.20237.5. Changes with 10.23.0002• A security vulnerability has been fixed where a crafted configuration packet sent by an authenticated administrative user can be used to execute arbitrary commands in systemcontext (CVE-2021-23862).For more details refer to our Security Advisory BOSCH-SA-043434-BT, published at ourSecurity Advisory web pagehttps:///xc/en/support/product-security/security-advisories.htmlor visit our PSIRT website at https://.7.6. New Features with 10.22.0038•APIPA (link-local address, Auto-IP) is used instead of a default IP address when DHCP is on and no DHCP server responded.•Transparent data pass-through for serial PTZ keyboard (SERIAL_PORT_APP_VAL and TRANSFER_TRNSPARENT_DATA) has been added.•Support of RCP+ via CGI (including WRITE commands) has been added.•HTTP digest authentication is supported for RCP+ via CGI.•Display orientation can be changed per line via RCP+.•RCP+ WRITE command MONITOR_NAME now supported for custom monitor names.•Updated RCP+ documentation is now available via the VIDEOJET decoder webpage.•Download of screen and tile snapshots via snap.jpg is now supported (requires at least user privileges).•Firmware update on-screen countdown dialog now shows a heartbeat whenever a single update step takes longer.•Support of CONNECT_URL read queries to get current video connection details, including current digital and dewarping zoom settings, has been added.•Support of various digital and dewarping zoom persistence modes(DIGITAL_ZOOM_PERSISTENCE_MODE) has been added.•Support of SYSTEM_DATETIME_V2 to read/write UTC system time has been added.•Support for new Sentinel RMS licenses has been added. Legacy licenses can now also be based on new installation code (lock code from Sentinel RMS).From NurembergBT-VS/MKP-XPT Product Management 20.04.20237.7. Changes with 10.22.0038•IP Matrix initialization is now working also for camera lines larger than 1.•RCP+ response for query on connected cameras is now working correctly.•URL extension for camera configuration in IP Matrix is no longer truncated.•An issue with an unexpected application restart has been fixed.•The DECODER_GROUP command is no longer supported when decoder IP address is not static. This disables the whole IP matrix configuration pages in Configuration Manager until a static IP is configured in the decoder’s network settings.•Improvements were made for log export via webpage and via Configuration Manager.•KBD-DIGITAL keyboard PIN is now used immediately without application restart.•KBD-DIGITAL keyboard PIN is now required whenever keyboard is attached and at application start.•Display orientation is now working for further monitor types.•Support of further USB to serial COM port adapters for KBD-DIGITAL keyboard connectivity.o Current: Prolific PL2303 [hardware ID USB\VID_067B&PID_2303]o New: Prolific PL2303GT [hardware ID USB\VID_067B&PID_23C3]o New: ATEN UC232A [hardware ID USB\VID_0557&PID_2008]o New: Unitek Y-108 [hardware ID FTDIBUS\VID_0403+PID_6001]o CableCreation CD0489 (PL2303) [hardware ID USB\VID_067B&PID_2303] is compatible to the already supported Prolific PL2303 adapter.Please note that the KBD-DIGITAL keyboard connectivity requires continuous maintenance, since new or not listed USB-to-serial COM port adapters typically require the installation of a suitable driver on the VIDEOJET decoder and an adaption of the hardware ID filter in thekeyboard detection software module. Newer USB adapters may require a firmware update to become supported.From NurembergBT-VS/MKP-XPT Product Management 20.04.20237.8. New Features with 10.01.0036Security• A protected configuration mode has been implemented, allowing too enable SSD encryption (BitLocker) and too disable USB ports, e.g. for installation of the decoder in public areas.•The configuration of the decoder can be protected by Software Sealing, similar to IP cameras.•The latest Microsoft Windows security updates have been included.Miscellaneous• A dewarped cutout from panoramic cameras can be defined with PTZ coordinates.• A new way to control and integrate the decoder into a management system has been added by a JSON RPC API. This allows to send commands and retrieve status information via JSON remote procedure calls. The API documentation is added to the distribution package.• A video output capture service (VOCS) has been implemented which could be activated via a license, applicable per display output. This service captures the memory of the video outputand encodes it into a camera-like video stream, which can be recorded via Video StreamingGateway (VSG) onto iSCSI storage.• A time server can be added to synchronize the decoder.•Decoder log file can be downloaded via Configuration Manager. This is especially recommended when download of the log file is not working correctly via web browser.7.9. Changes with 10.01.0036•Upload of background image and connection loss image to the decoder and reverting them to default is now also possible with service password set. The former restriction is obsolete.•Various minor bug fixes.From NurembergBT-VS/MKP-XPT Product Management 20.04.20237.10. New Features with 9.60.0017IP Matrix enhancements•KBD-DIGITAL is supported in addition to KBD-UNIVERSAL XF.This keyboard requires a serial-to-USB adapter to connect to the decoder.Both keyboards can be mixed in a clustered multi-decoder IP Matrix, one keyboard perdecoder.•Playback from local recording is supported.Permission is configured via Configuration Manager for the whole IP Matrix, valid for all users.•Buttons for next and previous camera have been added to the KBD-UXF functions.•Audio can be switched on or off via keyboard.•Camera channels can be extended via license up to 64 cameras per decoder unit.Note:IP Matrix manual is now separated intoo One configuration manual for IP Matrixo One operation manual for IP Matrix using KBD-UXFo One operation manual for IP Matrix using KBD-DIGITALSecurity•The latest Microsoft Windows security updates have been included.Miscellaneous•Background image and connection loss image can be uploaded to the decoder, replacing the default images. Reverting them to default is done by uploading an empty image.Note: Upload is only possible in conjunction with an empty service password.7.11. Changes with 9.60.0017•Temperature control margin increased to improve maximum performance at the specified maximum temperature, covering component tolerances, and to ensure that all productsadhere fully to their specification.•Various minor bug fixes.Security SystemsFromNuremberg BT-VS/MKP-XPT Product Management 20.04.202311BOSCH and the symbol are registered trademarks of Robert Bosch GmbH, Germany 7.12. Features with initial release 9.51• VIDEOJET decoder 7000 displays video from Standard Definition (SD), High Definition (HD),4K Ultra High Definition (UHD), and Megapixel (MP) cameras and encoders using H.264 or MPEG -4 encoding at up to 60 frames per second over IP networks.• VIDEOJET decoder 7000 provides an HDMI and a DisplayPort (via USB-C connector) output, both capable of driving up to 4K UHD displays simultaneously.• Display settings are automatically discovered and set for optimal display performance. • Monitor layouts can be switched independently for each display.• Upright monitors (portrait mode) are supported.• Video window (cameo) aspect ratio can be set to 16:9, 9:16, 3:4, or 1:1.• Active camera connections and layout are stored and automatically reconnected after reboot if configured. To avoid deadlock in case of an overload situation the automatic reconnect will be deactivated after VIDEOJET decoder 7000 was forced into reboot for 3 times within 10 minutes.• Video smoothing can be configured.• RTSP connections are supported, enabling connectivity to 3rd party and ONVIF cameras. • Discovery port is configurable.• Cameo distance is configurable.• VIDEOJET decoder 7000 supports IP Matrix application as built-in feature.• VIDEOJET decoder 7000 is able to display VCA metadata.• VIDEOJET decoder 7000 provides bi-directional G.711 audio for the video stream shown in single view on the first monitor.• Configuration is done using the Configuration Manager.• The number of decoders presented in capabilities is configurable to regulate the consumption of VMS licenses. Default value is 30.• System access is password-protected with two levels.• The system firmware can be upgraded remotely.• System API is compatible to predecessor VIDEOJET decoder 8000 for easy plug-and-play integration.• Operating temperature iso 0 °C to +50 °C (+32 °F to +122 °F) ambient temperature, with airflow o 0 °C to +40 °C (+32 °F to +104 °F) ambient temperature, still airFor detailed functional description of inherited firmware features, please refer to the VIDEOJET decoder 8000 firmware 9.51 release notes.For detailed technical specification, please refer to the datasheet.。

iSee mini升级指南

iSee mini升级指导1.下载升级包a)下载升级包“iSee mini升级工具包”解压得到如下文件三个文件夹(SD-CardMaker、Format Flash、Auto update)2.制作升级卡a)使用读卡器将SD卡(推荐使用256MB以上,8GB以下的Micro SD卡)连接电脑;b)打开SD-CardMaker文件夹,运行 SDcardMaker.exe(操作系统推荐使用windows XP,windows 7请以管理员身份运行,不支持windows 8),选择SD卡所指向的可移动磁盘,勾选“是否重新分区并格式化”后面的“是”,点击打开选择SD-CardMaker文件夹里的u-boot.bin文件。

如图所示点击“制作启动卡”弹出分区完成窗口,点击确定,在弹出的格式化窗口里选择开始,如图所示格式化完毕后点击关闭,弹出制作完成窗口,点击确定即可。

3.清除iSee mini内部数据a)将Format Flash文件夹内的“wsot_factory_format.wst”文件复制到SD卡里面。

b)在iSee mini关机状态下插入SD卡,用遥控开机,观察两侧喇叭处有蓝灯以1Hz的频率交替闪烁(此过程很快大约2秒钟),此时,内部数据清空完毕。

c)用适配器圆形插头顶一下iSee mini背部的复位孔,使其断电关机(若有外部其它设备对其充电请先断开),弹出SD卡。

4.刷入新的升级包刷入新的升级包前请务必确认你的iSee mini的版本,否则导致升级失败。

这里以双频WiFi版演示,单频WiFi版本操作一样只是ROM不一样。

单双频可以查看iSee mini的包装盒查看,若参数栏标有双频WiFi即为双频版否则为单频版本(寄回厂家做过硬件升级的是双频版的)。

a)将SD卡连接电脑删除SD卡内的所有文件,复制Auto update文件夹下的“双频WiFi版”里的“factory_update_param.aml、ISEEMINI_20140812_HA_NO_6330、recovery”三个文件到SD卡里面。

STMicroelectronics DfuSe USB设备固件升级用户手册说明书