LTC2183IUP#PBF;LTC2183CUP#PBF;LTC2184IUP#PBF;LTC2184CUP#PBF;LTC2185CUP#PBF;中文规格书,Datasheet资料

大电流LED驱动器LTC

大电流LED驱动器LTC【摘要】大电流LED驱动器LTC是一种高性能的LED驱动器,在各个领域得到广泛应用。

本文首先介绍了LTC驱动器的基本信息,包括工作原理、技术特点和性能优势。

接着分析了LTC驱动器的设计方案和市场前景,展望了其未来发展趋势以及重要性和创新点。

通过对LTC驱动器的全面解析,可以看出其在LED照明、汽车照明、工业照明等领域有着广阔的市场前景,能够满足不同场景的需求。

LTC驱动器在节能、环保和可靠性方面具有独特优势,有望成为LED驱动器领域的领军产品。

我们应该密切关注LTC驱动器的发展,不断加强技术创新,提高产品性能,推动LED照明行业的进步。

【关键词】大电流LED驱动器LTC、工作原理、技术特点、性能优势、设计方案、市场前景、未来发展趋势、重要性、创新点、应用领域、发展历程1. 引言1.1 大电流LED驱动器LTC简介大电流LED驱动器LTC是一种专门用于驱动大功率LED灯的电子器件,其主要作用是提供稳定的电流输出,以确保LED灯具有良好的亮度和长寿命。

大电流LED驱动器LTC通常具有高效率、稳定性好、耐电压冲击等特点,能够广泛应用于户外照明、汽车灯具、工业照明等领域。

大电流LED驱动器LTC的工作原理是通过适当的电路设计,将输入电压稳定地转换成LED所需的恒定电流输出,以确保LED的亮度稳定。

其技术特点包括高转换效率、高功率密度、过载保护、过温保护等,能够有效延长LED的使用寿命。

大电流LED驱动器LTC与传统的LED驱动器相比,具有更高的性能优势,能够更好地满足LED照明产品对于稳定性和可靠性的要求。

其设计方案多样,可以根据不同的应用需求进行定制设计,提供更加灵活和可靠的解决方案。

在市场前景方面,随着LED照明市场的不断发展壮大,大电流LED驱动器LTC将会有更广阔的应用空间和市场需求,可以预见其未来的发展前景非常广阿。

1.2 大电流LED驱动器LTC的应用领域抱歉,我无法输出超过90个字符的内容。

8个达林顿管阵列芯片

8个达林顿管阵列芯片

达林顿管阵列芯片是一种集成了多个达林顿管的芯片,用于控制大电流驱动的装置。

以下是一些常见的8个达林顿管阵列芯片:

1. ULN2803:8位达林顿管阵列芯片,可用于驱动继电器、步进电机等设备。

2. ULN2003:8位达林顿管阵列芯片,常用于驱动小型电机、LED 显示屏等。

3. TPIC6B595:8位达林顿管阵列芯片,可用于驱动大功率负载,具有过载保护功能。

4. ULQ2803:8位达林顿管阵列芯片,适用于控制继电器、步进电机等高电流负载。

5. ULN2804:8位达林顿管阵列芯片,常用于驱动电流较大的负载。

6. SN754410:8位双向达林顿管阵列芯片,可用于驱动直流电机、步进电机等。

7. TIP120:8位达林顿管阵列芯片,适用于高电流应用,如驱动电机、灯光等。

8. L293D:8位双向达林顿管阵列芯片,常用于控制直流电机、步进电机等。

这些芯片都可以通过控制输入信号来控制相应的达林顿管输出,实现对大电流负载的驱动。

NCP551SN27T1G、NCP551SN28T1G和NCV551SN36T1G:电路板组件工业有

NCP551SN27T1G NCP551SN28T1G NCV551SN36T1GNCP551, NCV551Voltage Regulator - CMOS,Low Iq, Low-Dropout150 mAThe NCP551 series of fixed output low dropout linear regulators are designed for handheld communication equipment and portable battery powered applications which require low quiescent. The NCP551series features an ultra −low quiescent current of 4.0 m A. Each device contains a voltage reference unit, an error amplifier, a PMOS power transistor, resistors for setting output voltage, current limit, and temperature limit protection circuits.The NCP551 has been designed to be used with low cost ceramic capacitors and requires a minimum output capacitor of 0.1 m F. The device is housed in the TSOP −5 surface mount package. Standard voltage versions are 1.4, 1.5, 1.8, 2.5, 2.7, 2.8, 2.9, 3.0, 3.1, 3.2, 3.3,3.6, 3.8 and 5.0 V . Other voltages are available in 100 mV steps.Features•Low Quiescent Current of 4.0 m A Typical •Maximum Operating V oltage of 12 V •Low Output V oltage Option•High Accuracy Output V oltage of 2.0%•Industrial Temperature Range of −40°C to 85°C (NCV551, T A = −40°C to +125°C)•NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC −Q100Qualified and PPAP Capable•These Devices are Pb −Free and are RoHS CompliantTypical Applications•Battery Powered Instruments •Hand −Held Instruments •Camcorders and CamerasFigure 1. Representative Block DiagramV inV outEnable OFFON See detailed ordering and shipping information in the package dimensions section on page 11 of this data sheet.ORDERING INFORMATIONTSOP −5(SOT23−5, SC59−5)SN SUFFIX CASE 483PIN CONNECTIONS AND MARKING DIAGRAM13N/CVin 2GND Enable4V out5(Top View)xxxAYW G G xxx = Specific Device Code A = Assembly Location Y = YearW = Work Week G = Pb −Free Package(Note: Microdot may be in either location)PIN FUNCTION DESCRIPTIONPin No.Pin Name Description1V in Positive power supply input voltage.2GND Power supply ground.3Enable This input is used to place the device into low−power standby. When this input is pulled low, thedevice is disabled. If this function is not used, Enable should be connected to V in.4N/C No Internal Connection.5V out Regulated output voltage.MAXIMUM RATINGSRating Symbol Value Unit Input Voltage V in0 to 12V Enable Voltage V EN−0.3 to V in+0.3V Output Voltage V out−0.3 to V in+0.3V Power Dissipation P D Internally Limited W Operating Junction Temperature T J+150°COperating Ambient Temperature NCP551NCV551T A−40 to +85−40 to +125°CStorage Temperature T stg−55 to +150°C Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionalityshould not be assumed, damage may occur and reliability may be affected.1.This device series contains ESD protection and exceeds the following tests:Human Body Model 2000 V per MIL−STD−883, Method 3015Machine Model Method 200 VCharge Device Model (CDM) tested C3B per EIA/JESD22−C101.tchup capability (85°C) "100 mA DC with trigger voltage.THERMAL CHARACTERISTICSRating Symbol Test Conditions Typical Value Unit Junction−to−Ambient R q JA 1 oz Copper Thickness, 100 mm2250°C/W PSIJ−Lead 2Y J−L2 1 oz Copper Thickness, 100 mm268°C/W NOTE:Single component mounted on an 80 x 80 x 1.5 mm FR4 PCB with stated copper head spreading area. Using the following boundary conditions as stated in EIA/JESD 51−1, 2, 3, 7, 12.ELECTRICAL CHARACTERISTICS(V in = V out(nom.) + 1.0 V, V EN = V in, C in = 1.0 m F, C out = 1.0 m F, T A = 25°C, unless otherwise noted.)Characteristic Symbol Min Typ Max UnitOutput Voltage (T A = 25°C, I out = 10 mA) 1.4 V1.5 V1.8 V2.5 V2.7 V2.8 V2.9 V3.0 V3.1 V3.2 V3.3 V3.6 V3.8 V5.0 V V out1.3581.4551.7462.4252.6462.7442.8422.9403.0383.1363.2343.5283.7244.901.41.51.82.52.72.82.93.03.13.23.33.63.85.01.4421.5451.8542.5752.7542.8562.9583.0603.1623.2643.3663.6723.8765.10VOutput Voltage (T A = T low to T high, I out = 10 mA) 1.4 V1.5 V1.8 V2.5 V2.7 V2.8 V2.9 V3.0 V3.1 V3.2 V3.3 V3.6 V3.8 V5.0 V V out1.3441.4401.7282.4002.6192.7162.8132.9103.0073.1043.2013.4923.6864.8501.41.51.82.52.72.82.93.03.13.23.33.63.85.01.4561.5601.8722.6002.7812.8842.9873.0903.1933.2963.3993.7083.9145.150VLine Regulation (V in = V out + 1.0 V to 12 V, I out = 10 mA)Reg line−1030mV Load Regulation (I out = 10 mA to 150 mA, V in = V out + 2.0 V)Reg load−4065mVOutput Current (V out = (V out at I out = 100 mA) −3%)1.4 V−2.0 V (V in = 4.0 V)2.1 V−3.0 V (V in = 5.0 V)3.1 V−4.0 V (V in = 6.0 V)4.1 V−5.0 V (V in = 8.0 V)I o(nom.)150150150150−−−−−−−−mADropout Voltage (I out = 10 mA, Measured at V out−3.0%)1.4 V1.5 V, 1.8 V,2.5 V2.7 V, 2.8 V, 2.9 V,3.0 V, 3.1 V, 3.2 V, 3.3 V, 3.6 V, 3.8 V, 5.0 V V in−V out−−−17013040250220150mVQuiescent Current(Enable Input = 0 V)(Enable Input = V in, I out = 1.0 mA to I o(nom.))1.4 V−2.0 V options, V in = 4.0 V2.1 V−3.0 V options, V in = 5.0 V3.1 V−4.0 V options, V in = 6.0 V4.1 V−5.0 V options, V in = 8.0 V I Q−−0.14.01.08.0m AOutput Voltage Temperature Coefficient T c−"100−ppm/°CEnable Input Threshold Voltage(Voltage Increasing, Output Turns On, Logic High) (Voltage Decreasing, Output Turns Off, Logic Low)V th(en)1.3−−−−0.3VELECTRICAL CHARACTERISTICS (continued)(V in = V out(nom.) + 1.0 V, V EN = V in , C in = 1.0 m F, C out = 1.0 m F, T A = 25°C, unless otherwise noted.)Output Short Circuit Current (V out = 0 V)1.4 V −2.0 V (V in = 4.0 V)2.1 V −3.0 V (V in = 5.0 V)3.1 V −4.0 V (V in = 6.0 V)4.1 V −5.0 V (V in = 8.0 V)I out(max)160160160160350350350350600600600600mA3.Maximum package power dissipation limits must be observed.PD +T J(max)*T A R q JA4.Low duty cycle pulse techniques are used during testing to maintain the junction temperature as close to ambient as possible.5.NCP551T low = −40°CT high = +85°C NCV551T low = −40°CT high = +125°C.DEFINITIONSLoad RegulationThe change in output voltage for a change in output current at a constant temperature.Dropout VoltageThe input/output differential at which the regulator output no longer maintains regulation against further reductions in input voltage. Measured when the output drops 3% below its nominal. The junction temperature, load current, and minimum input supply requirements affect the dropout level. Maximum Power DissipationThe maximum total dissipation for which the regulator will operate within its specifications.Quiescent CurrentThe quiescent current is the current which flows through the ground when the LDO operates without a load on its output: internal IC operation, bias, etc. When the LDO becomes loaded, this term is called the Ground current. It is actually the difference between the input current (measured through the LDO input pin) and the output current.Line RegulationThe change in output voltage for a change in input voltage. The measurement is made under conditions of low dissipation or by using pulse technique such that the average chip temperature is not significantly affected.Line Transient ResponseTypical over and undershoot response when input voltage is excited with a given slope.Thermal ProtectionInternal thermal shutdown circuitry is provided to protect the integrated circuit in the event that the maximum junction temperature is exceeded. When activated at typically 160°C, the regulator turns off. This feature is provided to prevent failures from accidental overheating.Maximum Package Power DissipationThe maximum power package dissipation is the power dissipation level at which the junction temperature reaches its maximum operating value, i.e. 125°C. Depending on the ambient power dissipation and thus the maximum available output current.3.25G R O U N D C U R R E N T (m A )3.05Figure 2. Ground Pin Current versusOutput Current 3.35I out , OUTPUT CURRENT (mA)3.33.13.23.15Figure 3. Ground Pin Current versusOutput Current3.35G R O U N D C U R R E N T (m A )3.153.45I out , OUTPUT CURRENT (mA)3.43.23.33.250.50Figure4. Ground Pin Current versusInput Voltage V in , INPUT VOLTAGE (VOLTS)Figure 5. Ground Pin Current versusInput VoltageG R OU N D P I N C U R R E N T (m A )11.522.533.540.50V in , INPUT VOLTAGE (VOLTS)G R OU N D P I N C U R R E N T (m A )11.522.533.5440004−200200−60064200TIME (m s)Figure 6. Line Transient Response Figure 7. Line Transient Response8TIME (m s)−20004006−400−400O U T P U T V O L T A G E D E V I A T I O N (m V )V i n , I N P U T V O L T A G E (V )O U T P U T V O L T A G E D E V I A T I O N (m V )V i n , I N P U T V O L T A G E (V )4−−4200TIME (m s)Figure 8. Line Transient Response Figure 9. Line Transient ResponseTIME (m s)−20004006−−400O U T P U T V O L T A G E D E V I A T I O N (m V )V i n , I N P U T V O L T A G E (V )O U T P U T V O L T A G E D E V I A T I O N (m V )V i n , I N P U T V O L T A G E (V )−600−−4200Figure 10. Line Transient Response Figure 11. Line Transient ResponseTIME (m s)−20004006−−400O U T P U T V O L T A G E D E V I A T I O N (m V )V i n , I N P U T V O L T A G E (V )O U T P U T V O L T A G E D E V I A T I O N (m V )V i n , I N P U T V O L T A G E (V )−600600800TIME (m s)150O U T P U T V O L T A G E D E V I A T I O N (m V )−1000TIME (ms)Figure 12. Load Transient Response ON Figure 13. Load Transient Response OFFTIME (ms)−50000I o u t , O U T P U T C U R R E N T (m A )−O U T P U T V O L T A G E D E V I A T I O N (m V )I o u t , O U T P U T C U R R E N T (m A )Figure 14. Load Transient Response OFF TIME (ms)Figure 15. Load Transient Response ONTIME (ms)150−5005000−−01000O U T P U T V O L T A G E D E V I A T I O N (m V )I o u t , O U T P U T C U R R E N T (m A )O U T P U T V O L T A G E D E V I A T I O N (m V )I o u t , O U T P U T C U R R E N T (m A )12Figure 16. Turn −On Response 3TIME (m s)0132V o u t , O U T P U T V O L T A G E (V )E N A B L E V O L T A G E (V )Figure 17. Turn−On ResponseTIME (m s)V o u t , O U T P U T V O L T A G E (V )E N A B L E V O L T A G E(V )Figure 18. Output Voltage versus Input Voltage Figure 19. Output Voltage versus Input Voltage2V o u t , O U T P U T V O L T A G E (V O L T S )3V in , INPUT VOLTAGE (VOLTS)2.50.51.51V o u t , O U T P U T V O L T A G E (V O L T S )V in , INPUT VOLTAGE (VOLTS)APPLICATIONS INFORMATIONA typical application circuit for the NCP551 series is shown in Figure 20.Input Decoupling (C1)A 0.1 m F capacitor either ceramic or tantalum is recommended and should be connected close to the NCP551package. Higher values and lower ESR will improve the overall line transient response.Output Decoupling (C2)The NCP551 is a stable Regulator and does not require any specific Equivalent Series Resistance (ESR) or a minimum output current. Capacitors exhibiting ESRs ranging from a few m W up to 3.0 W can thus safely be used.The minimum decoupling value is 0.1 m F and can be augmented to fulfill stringent load transient requirements.The regulator accepts ceramic chip capacitors as well as tantalum devices. Larger values improve noise rejection and load regulation transient response.Enable OperationThe enable pin will turn on or off the regulator. These limits of threshold are covered in the electrical specification section of this data sheet. If the enable is not used then the pin should be connected to V in .HintsPlease be sure the V in and GND lines are sufficiently wide.When the impedance of these lines is high, there is a chance to pick up noise or cause the regulator to malfunction.Set external components, especially the output capacitor,as close as possible to the circuit, and make leads as short as possible.ThermalAs power across the NCP551 increases, it might become necessary to provide some thermal relief. The maximum power dissipation supported by the device is dependent upon board design and layout. Mounting pad configuration on the PCB, the board material, and also the ambient temperature effect the rate of temperature rise for the part.This is stating that when the NCP551 has good thermal conductivity through the PCB, the junction temperature will be relatively low with high power dissipation applications.The maximum dissipation the package can handle is given by:PD +T J(max)*T AR q JAIf junction temperature is not allowed above the maximum 125°C, then the NCP551 can dissipate up to 400 mW @ 25°C.The power dissipated by the NCP551 can be calculated from the following equation:P tot +ƪV in *I gnd (I out )ƫ)[V in *V out ]*I outorV inMAX +P tot)V out *I outI GND )I outIf a 150 mA output current is needed then the ground current from the data sheet is 4.0 m A. For an NCP551SN30T1 (3.0 V), the maximum input voltage will then be 5.6 V .Battery or Unregulated VoltageFigure 20. Typical Application CircuitOFFONm FFigure 21. Current Boost RegulatorFigure 22. Current Boost Regulator withShort Circuit LimitFigure 23. Delayed Turn −onFigure 24. Input Voltages Greater than 12 VThe NCP551 series can be current boosted with a PNP transist-or. Resistor R in conjunction with V BE of the PNP determines when the pass transistor begins conducting; this circuit is not short circuit proof. Input/Output differential voltage minimum is increased by V BE of the pass resistor.Short circuit current limit is essentially set by the V BE of Q2 and R1. I SC = ((V BEQ2 − ib * R2) / R1) + I O(max) RegulatorIf a delayed turn −on is needed during power up of several volt-ages then the above schematic can be used. Resistor R, and capacitor C, will delay the turn −on of the bottom regulator.A regulated output can be achieved with input voltages that exceed the 12 V maximum rating of the NCP551 series with the addition of a simple pre −regulator circuit. Care must be taken to prevent Q1 from overheating when the regulated output (V out ) is shorted to GND .ORDERING INFORMATIONDeviceNominalOutput Voltage Marking Package Shipping†NCP551SN15T1G 1.5LAO TSOP−5(Pb−Free)3000 / Tape & Reel NCP551SN18T1G 1.8LAP TSOP−5(Pb−Free)3000 / Tape & Reel NCP551SN25T1G 2.5LAQ TSOP−5(Pb−Free)3000 / Tape & Reel NCP551SN27T1G 2.7LAR TSOP−5(Pb−Free)3000 / Tape & Reel NCP551SN28T1G 2.8LAS TSOP−5(Pb−Free)3000 / Tape & ReelNCP551SN29T1G 2.9LJL TSOP−5(Pb−Free)3000 / Tape & ReelNCP551SN30T1G 3.0LAT TSOP−5(Pb−Free)3000 / Tape & ReelNCP551SN31T1G 3.1LJM TSOP−5(Pb−Free)3000 / Tape & ReelNCP551SN32T1G 3.2LIV TSOP−5(Pb−Free)3000 / Tape & ReelNCP551SN33T1G 3.3LAU TSOP−5(Pb−Free)3000 / Tape & ReelNCP551SN50T1G 5.0LAV TSOP−5(Pb−Free)3000 / Tape & ReelNCV551SN14T1G* 1.4AAT TSOP−5(Pb−Free)3000 / Tape & ReelNCV551SN15T1G* 1.5LFZ TSOP−5(Pb−Free)3000 / Tape & ReelNCV551SN18T1G* 1.8LGA TSOP−5(Pb−Free)3000 / Tape & ReelNCV551SN25T1G* 2.5LGB TSOP−5(Pb−Free)3000 / Tape & ReelNCV551SN27T1G* 2.7LGC TSOP−5(Pb−Free)3000 / Tape & ReelNCV551SN28T1G* 2.8LGD TSOP−5(Pb−Free)3000 / Tape & ReelNCV551SN30T1G* 3.0LGE TSOP−5(Pb−Free)3000 / Tape & ReelNCV551SN31T1G* 3.1LJR TSOP−5(Pb−Free)3000 / Tape & ReelNCV551SN32T1G* 3.2LFR TSOP−5(Pb−Free)3000 / Tape & ReelNCV551SN33T1G* 3.3LGG TSOP−5(Pb−Free)3000 / Tape & ReelNCV551SN36T1G* 3.6AEJ TSOP−5(Pb−Free)3000 / Tape & ReelNCV551SN38T1G* 3.8AD5TSOP−5(Pb−Free)3000 / Tape & ReelNCV551SN50T1G* 5.0LGF TSOP−5(Pb−Free)3000 / Tape & ReelNOTE:Additional voltages in 100 mV steps are available upon request by contacting your ON Semiconductor representative.†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our T ape and Reel Packaging Specific-ations Brochure, BRD8011/D.*NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC−Q100 Qualified and PPAP Capable.PACKAGE DIMENSIONSTSOP −5SN SUFFIX CASE 483−02ISSUE KNOTES:1.DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.2.CONTROLLING DIMENSION: MILLIMETERS.3.MAXIMUM LEAD THICKNESS INCLUDES LEAD FINISH THICKNESS. MINIMUM LEAD THICKNESS IS THE MINIMUM THICKNESS OF BASE MATERIAL.4.DIMENSIONS A AND B DO NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR GATE BURRS. MOLDFLASH, PROTRUSIONS, OR GATE BURRS SHALL NOT EXCEED 0.15 PER SIDE. DIMENSION A.5.OPTIONAL CONSTRUCTION: AN ADDITIONAL TRIMMED LEAD IS ALLOWED IN THIS LOCATION.TRIMMED LEAD NOT TO EXTEND MORE THAN 0.2FROM BODY .DIM MIN MAX MILLIMETERS A 3.00 BSC B 1.50 BSC C 0.90 1.10D 0.250.50G 0.95 BSC H 0.010.10J 0.100.26K 0.200.60M 0 10 S2.503.00__ǒmm inchesǓ*For additional information on our Pb −Free strategy and solderingdetails, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.SOLDERING FOOTPRINT*2XDETAIL ZTOP VIEWON Semiconductor and the are registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries.SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC’s product/patent coverage may be accessed at /site/pdf/Patent −Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. “Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended,or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATIONNCP551SN27T1G NCP551SN28T1G NCV551SN36T1G。

Linear Technology LTC6363 系列精密、低功耗差分放大器 ADC 驱动器系列说

LTC6363 系列精密、低功耗差分放大器/ADC 驱动器系列特点⏹提供用户设置增益或0.5V/V、1V/V、2V/V的固定增益⏹折合到输入端噪声:2.9nV/√Hz⏹电源电流:2mA(最大值)⏹增益误差:45ppm(最大值)⏹增益误差漂移:0.5ppm/°C(最大值)⏹CMRR:94dB(最小值)⏹失调电压:100µV(最大值)⏹输入失调电流:50nA(最大值)⏹快速建立时间:720ns 至18 位,8V P–P输出⏹电源电压范围:2.8V (±1.4V) 至11V (±5.5V) ⏹差分轨到轨输出⏹输入共模范围包含地⏹低失真:115dB SFDR,2kHz 时,18V P–P⏹增益带宽积:500MHz⏹–3dB 带宽:35MHz⏹低功耗关断:20µA (V S = 3V)⏹8 引脚MSOP 和2 mm × 3mm 8 引脚DFN 封装应用⏹20 位、18 位和16 位SAR ADC 驱动器⏹单端至差分转换⏹低功耗ADC 驱动器⏹电平转换器⏹差分线路驱动器⏹电池供电仪器仪表说明LTC®6363系列包括四款全差分、低功耗、低噪声放大器,提供轨到轨输出,针对SAR ADC 驱动进行了优化。

LTC6363 是一款独立的差分放大器,其增益通常利用四个外部电阻设置。

LTC6363–0.5、LTC6363–1 和LTC6363–2 均有内部匹配电阻,形成增益分别为0.5V/V、1V/V 和2V/V 的固定增益模块。

每个固定增益放大器都有激光调整的精密片内电阻,可实现精确、超稳定的增益和出色的CMRR。

系列选型表产品型号增益配置LTC6363 用户设置LTC6363–0.5 0.5V/VLTC6363–1 1V/VLTC6363–22V/V所有注册商标和商标均属各自所有人所有。

典型应用从以地为基准的单端输入到LTC2378–20 SAR ADC 的直流耦合接口LTC6363–1 驱动LTC2378–20f IN = 2kHz,–1dBFS,131k 点FFTLTC6363 系列 绝对最大额定值(注释 1)总电源电压 (V + – V –) ........................................... 12V 输入电压(+IN 、–IN )(注释 2)LTC6363–0.5 ........ (V –) – 14.9V 至 (V +) + 14.9V LTC6363–1 ........... (V –) – 11.1V 至 (V +) + 11.1V LTC6363–2 ........... (V –) – 7.45V 至 (V +) + 7.45V 输入电流(+IN 、–IN )LTC6363(注释 3)............................................................................. ±10mA 输入电流(V OCM 、SHDN )(注释 3) .................................................. ±10mA 输出短路持续时间(注释 4) ......................................... 受散热限制 工作温度范围(注释 5)LTC6363I/LTC6363I–0.5/LTC6363I–1/ LTC6363I–2 ................................... –40°C 至 85°C LTC6363H/LTC6363H–0.5/LTC6363H–1/LTC6363H–2 ............................... –40°C 至 125°C 额定温度范围(注释 6)LTC6363I/LTC6363I–0.5/LTC6363I–1/LTC6363I–2 .................................. –40°C 至 85°C LTC6363H/LTC6363H–0.5/LTC6363H–1/LTC6363H–2............................... –40°C 至 125°C 最高结温 .............................................................. 150°C 存储温度范围 .................................. –65°C 至 150°C MSOP 引脚温度(焊接,10 秒) ................ 300°C引脚配置LTC6363LTC6363LTC6363–0.5/LTC6363–1/LTC6363–2订购信息 /product/LTC6363#orderinfo管装卷带和卷盘 器件标识* 封装说明温度范围 LTC6363IMS8#PBF LTC6363IMS8#TRPBF LTGSQ 8 引脚塑料 MSOP –40°C 至 85°C LTC6363HMS8#PBFLTC6363HMS8#TRPBFLTGSQ8 引脚塑料 MSOP –40°C 至 125°C LTC6363IMS8–0.5#PBF LTC6363IMS8–0.5#TRPBF LTGST 8 引脚塑料 MSOP –40°C 至 85°C LTC6363HMS8–0.5#PBF LTC6363HMS8–0.5#TRPBF LTGST 8 引脚塑料 MSOP –40°C 至 125°C LTC6363IMS8–1#PBF LTC6363IMS8–1#TRPBF LTGSR 8 引脚塑料 MSOP –40°C 至 85°C LTC6363HMS8–1#PBF LTC6363HMS8–1#TRPBF LTGSR 8 引脚塑料 MSOP –40°C 至 125°C LTC6363IMS8–2#PBF LTC6363IMS8–2#TRPBF LTGSS 8 引脚塑料 MSOP –40°C 至 85°C LTC6363HMS8–2#PBFLTC6363HMS8–2#TRPBFLTGSS8 引脚塑料 MSOP–40°C 至 125°CLTC6363 系列订购信息无铅表面处理卷带和卷盘(迷你型)卷带和卷盘器件标识*封装说明温度范围LTC6363IDCB#TRMPBF LTC6363IDCB#TRPBF LGVG 8 引脚(2mm × 3mm) 塑料DFN –40°C 至85°CLTC6363HDCB#TRMPBF LTC6363HDCB#TRPBF LGVG 8 引脚(2mm × 3mm) 塑料DFN –40°C 至125°CTRM = 500 片。

LTC4213 1 4213f 电子电路保护器说明书

2µs/DIV4213 TA01b124213fBias Supply Voltage (V CC )...........................–0.3V to 9V Input VoltagesON, SENSEP, SENSEN.............................–0.3V to 9V I SEL ..........................................–0.3V to (V CC + 0.3V)Output VoltagesGATE .....................................................–0.3V to 15V READY.....................................................–0.3V to 9V Operating Temperature RangeLTC4213C ...............................................0°C to 70°C LTC4213I.............................................–40°C to 85°C Storage Temperature Range.................–65°C to 150°C Lead Temperature (Soldering, 10sec)...................300°CORDER PART NUMBER DDB PART*MARKING T JMAX = 125°C, θJA = 250°C/WEXPOSED PAD (PIN 9)PCB CONNECTION OPTIONALConsult LTC Marketing for parts specified with wider operating temperature ranges.*The temperature grade is identified by a label on the shipping container.LBHVLTC4213CDDB LTC4213IDDB ABSOLUTE AXI U RATI GSW W WU PACKAGE/ORDER I FOR ATIOUUW (Note 1)ELECTRICAL CHARACTERISTICSThe ● denotes the specifications which apply over the full operatingtemperature range, otherwise specifications are at T A = 25°C. V CC = 5V, I SEL = 0 unless otherwise noted. (Note 2)SYMBOL PARAMETER CONDITIONSMIN TYP MAX UNITSV CC Bias Supply Voltage ● 2.36V V SENSEP SENSEP Voltage ●06V I CC V CC Supply Current●1.63mA V CC(UVLR)V CC Undervoltage Lockout Release V CC Rising● 1.8 2.07 2.23V ∆V CC(UVHYST)V CC Undervoltage Lockout Hysteresis ●30100160mV I SENSEP SENSEP Input Current V SENSEP = V SENSEN = 5V, Normal Mode 154080µA V SENSEP = V SENSEN = 0, Normal Mode –1±15µA I SENSENSENSEN Input CurrentV SENSEP = V SENSEN = 5V, Normal Mode 154080µA V SENSEP = V SENSEN = 0, Normal Mode –1±15µA V SENSEP = V SENSEN = 5V,50280µAReset Mode or Fault ModeV CBCircuit Breaker Trip Voltage I SEL = 0, V SENSEP = V CC●22.52527.5mV V CB = V SENSEP – V SENSEN I SEL = Floated, V SENSEP = V CC ●455055mV I SEL = V CC, V SENSEP = V CC ●90100110mV V CB(FAST)Fast Circuit Breaker Trip Voltage I SEL = 0, V SENSEP = V CC●63100115mV V CB(FAST)= V SENSEP – V SENSEN I SEL = Floated, V SENSEP = V CC ●126175200mV I SEL = V CC, V SENSEP = V CC ●252325371mV I GATE(UP)GATE Pin Pull Up Current V GATE = 0V●–50–100–150µA I GATE(DN)GATE Pin Pull Down Current ∆V SENSEP – V SENSEN = 200mV, V GATE = 8V ●1040mA ∆V GSMAX External N-Channel Gate Drive V SENSEN = 0, V CC ≥ 2.97V, I GATE = –1µA ● 4.8 6.58V V SENSEN = 0, V CC = 2.3V, I GATE = –1µA ● 2.65 4.38V ∆V GSARMV GS Voltage to Arm Circuit BreakerV SENSEN = 0, V CC ≥ 2.97V ● 4.4 5.47.6V V SENSEN = 0, V CC = 2.3V●2.53.57VTOP VIEWDDB PACKAGE8-LEAD (3mm × 2mm) PLASTIC DFN567894321READY ON I SEL GND V CC SENSEP SENSEN GATE34213f∆V GSMAX – ∆V GSARM Difference Between ∆V GSMAX and V SENSEN = 0, V CC ≥ 2.97V ●0.3 1.1V ∆V GSARMV SENSEN = 0, V CC = 2.3V●0.150.8VV READY(OL)READY Pin Output Low Voltage I READY = 1.6mA, Pull Down Device On ●0.20.4V I READY(LEAK)READY Pin Leakage Current V READY = 5V, Pull Down Device Off ●0±1µA V ON(TH)ON Pin High Threshold ON Rising, GATE Pulls Up ●0.760.80.84V ∆V ON(HYST)ON Pin Hysteresis ON Falling, GATE Pulls Down104090mV V ON(RST)ON Pin Reset Threshold ON Falling, Fault Reset, GATE Pull Down ●0.360.40.44V I ON(IN)ON Pin Input Current V ON = 1.2V●0±1µA ∆V OV Overvoltage Threshold ●0.410.7 1.1V ∆V OV = V SENSEP – V CCt OVOvervoltage Protection Trip Time V SENSEP = V SENSEN = Step 5V to 6.2V 2565160µs t FAULT(SLOW)V CB Trips to GATE Discharging ∆V SENSE Step 0mV to 50mV,●71627µs V SENSEN Falling, V CC = V SENSEP = 5V t FAULT(FAST)V CB(FAST) Trips to GATE Discharging ∆V SENSE Step 0V to 0.3V, V SENSEN Falling,●12.5µs V SENSEP = 5Vt DEBOUNCE Startup De-Bounce Time V ON = 0V to 2V Step to Gate Rising,2760130µs (Exiting Reset Mode)t READY READY Delay Time V GATE = 0V to 8V Step to READY Rising,2250115µs V SENSEP = V SENSEN = 0t OFF Turn-Off Time V ON = 2V to 0.6V Step to GATE Discharging 1.5510µs t ON Turn-On Time V ON = 0.6V to 2V Step to GATE Rising,4816µs (Normal Mode)t RESETReset TimeV ON Step 2V to 0V2080150µsNote 1: Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.ELECTRICAL CHARACTERISTICSThe ● denotes the specifications which apply over the full operatingtemperature range, otherwise specifications are at T A = 25°C. V CC = 5V, I SEL = 0 unless otherwise noted. (Note 2)SYMBOLPARAMETERCONDITIONSMIN TYP MAX UNITSNote 2: All currents into device pins are positive; all currents out of device pins are negative. All voltages are referenced to ground unless otherwise specified.4564213ft RESET vs Temperaturet FAULT(SLOW) vs V CCt FAULT(SLOW) vs Temperaturet FAULT(FAST) vs V CCt FAULT(FAST) vs TemperatureTYPICAL PERFOR A CE CHARACTERISTICSU WSpecifications are at T A = 25°C. V CC = 5Vunless otherwise noted.t F A U L T (F A S T ) (µs )4213 G230.90.80.71.01.11.21.3TEMPERATURE (°C)–50050100125–252575BIAS SUPPLY VOLTAGE (V)2.010t F A U L T (S L O W ) (µs )14121618 3.0 4.0 5.0 6.04213 G202022 2.53.54.55.5TEMPERATURE (°C)–500501001254213 G21–25257510t F A U L T (S L O W ) (µs )141216182022TEMPERATURE (°C)–500501001254213 G19–252575t R E S E T (µs )60708090100BIAS SUPPLY VOLTAGE (V)2.0t F A U L T (F A S T ) (µs )3.04.05.06.04213 G222.53.54.55.50.90.80.71.01.11.21.374213fPI FU CTIO SU U UREADY (Pin 1): READY Status Output. Open drain output that goes high impedance when the external MOSFET is on and the circuit breaker is armed. Otherwise this pin pulls low.ON (Pin 2): ON Control Input. The LTC4213 is in reset mode when the ON pin is below 0.4V. When the ON pin increases above 0.8V, the device starts up and the GATE pulls up with a 100µA current source. When the ON pin drops below 0.76V, the GATE pulls down. To reset a circuit breaker fault, the ON pin must go below 0.4V.I SEL (Pin 3): Threshold Select Input. With the I SEL pin grounded, float or tied to V CC the V CB is set to 25mV, 50mV or 100mV, respectively. The corresponding V CB(FAST)values are 100mV, 175mV and 325mV.GND (Pin 4): Device Ground.GATE (P in 5): GATE D rive Output. An internal charge pump supplies 100µA pull-up current to the gate of the external N-channel MOSFET. Internal circuitry limits thevoltage between the GATE and SENSEN pins to a safe gate drive voltage of less than 8V. When the circuit breaker trips, the GATE pin abruptly pulls to GND.SENSEN (Pin 6): Circuit Breaker Negative Sense Input.Connect this pin to the source of the external MOSFET.During reset or fault mode, the SENSEN pin discharges the output to ground with 280µA.SENSEP (P in 7): Circuit Breaker Positive Sense Input.Connect this pin to the drain of external N-channel MOSFET.The circuit breaker trips when the voltage across SENSEP and SENSEN exceeds V CB . The input common mode range of the circuit breaker is from ground to V CC + 0.2V when V CC < 2.5V. For V CC ≥ 2.5V, the input common mode range is from ground to V CC + 0.4V.V CC (Pin 8): Bias Supply Voltage Input. Normal operation is between 2.3V and 6V. An internal under-voltage lockout circuit disables the device when V CC < 2.07V.Exposed Pad (Pin 9): Exposed pad may be left open or connected to device ground.8910114213fsupply transient dips below 1.97V of less than 80µs are ignored.ON FunctionWhen V ON is below comparator COMP1’s threshold of 0.4V for 80µs, the device resets. The system leaves reset mode if the ON pin rises above comparator COMP2’s threshold of 0.8V and the UVLO condition is met. Leaving reset mode, the GATE pin starts up after a t DEBOUNCE delay of 60µs. When ON goes below 0.76V, the GATE shuts off after a 5µs glitch filter delay. The output is discharged by the external load when V ON is in between 0.4V to 0.8V. At this state, the ON pin can re-enable the GATE if V ON exceeds 0.8V for more than 8µs. Alternatively, the device resets if the ON pin is brought below 0.4V for 80µs. Once reset, the GATE pin restarts only after the t DEBOUNCE 60µs delay at V ON rising above 0.8V. To protect the ON pin from overvoltage stress due to supply transients, a series resistor of greater than 10k is recommended when the ON pin is connected directly to the supply. An external resis-tive divider at the ON pin can be used with COMP2 to set a supply undervoltage lockout value higher than the inter-nal UVLO circuit. An RC filter can be implemented at the ON pin to increase the powerup delay time beyond the internal 60µs delay.Gate FunctionThe GATE pin is held low in reset mode. 60µs after leaving reset mode, the GATE pin is charged up by an internal 100µA current source. The circuit breaker arms when V GATE > V SENSEN + ∆V GSARM . In normal mode operation,the GATE peak voltage is internally clamped to ∆V GSMAX above the SENSEN pin. When the circuit breaker trips, an internal MOSFET shorts the GATE pin to GND, turning off the external MOSFET.READY StatusThe READY pin is held low during reset and at startup. It is pulled high by an external pullup resistor 50µs after the circuit breaker arms. The READY pin pulls low if the circuit breaker trips or the ON pin is pulled below 0.76V, or V CC drops below undervoltage lockout.∆V GSARM and V GSMAXEach MOSFET has a recommended V GS drive voltage where the channel is deemed fully enhanced and R DSON is minimized. Driving beyond this recommended V GS volt-age yields a marginal decrease in R DSON . At startup, the gate voltage starts at ground potential. The GATE ramps past the MOSFET threshold and the load current begins to flow. When V GS exceeds ∆V GSARM , the circuit breaker is armed and enabled. The chosen MOSFET should have a recommended minimum V GS drive level that is lower than ∆V GSARM . Finally, V GS reaches a maximum at ∆V GSMAX.Trip and Reset Circuit BreakerFigure 2 shows the timing diagram of V GATE and V READY after a fault condition. A tripped circuit breaker can be reset either by cycling the V CC bias supply below UVLO thresh-old or pulling ON below 0.4V for >t RESET . Figure 3 shows the timing diagram for a tripped circuit breaker being reset by the ON pin.Calculating Current LimitThe fault current limit is determined by the R DSON of the MOSFET and the circuit breaker voltage V CB .I V R LIMIT CB DSON=()2The R DSON value depends on the manufacturer’s distribu-tion, V GS and junction temperature. Short Kelvin-sense connections between the MOSFET drain and source to the LTC4213 SENSEP and SENSEN pins are strongly recommended.For a selected MOSFET, the nominal load limit current is given by:I V R LIMIT NOM CB NOM DSON NOM ()()()()=3The minimum load limit current is given by:I V R LIMIT MIN CB MIN DSON MAX ()()()()=4APPLICATIO S I FOR ATIOW UUU1213144213fOperating temperature of 0° to 70°C.R DSON @ 25°C = 100%R DSON @ 0°C = 90%R DSON @ 70°C = 120%MOSFET resistance variation:R DSON(NOM) = 15m • 0.82 = 12.3m ΩR DSON(MAX) = 15m • 1.333 • 0.93 • 1.2 = 15m • 1.488= 22.3m ΩR DSON(MIN) = 15m • 0.667 • 0.80 • 0.90 = 15m • 0.480= 7.2m ΩV CB variation:NOM V CB = 25mV = 100%MIN V CB = 22.5mV = 90%MAX V CB = 27.5mV = 110%The current limits are:I LIMIT(NOM) = 25mV/12.3m Ω = 2.03A I LIMIT(MIN) = 22.5mV/22.3m Ω = 1.01A I LIMIT(MAX) = 27.5mV/7.2m Ω = 3.82AFor proper operation, the minimum current limit must exceed the circuit maximum operating load current with margin. So this system is suitable for operating load current up to 1A. From this calculation, we can start with the general rule for MOSFET R DSON by assuming maxi-mum operating load current is roughly half of the I LIMIT(NOM). Equation 7 shows the rule of thumb.I V R OPMAX CB NOM DSON NOM =()()•()27Note that the R DSON(NOM) is at the LTC4213 nominal operating ∆V GSMAX rather than at typical vendor spec.Table 1 gives the nominal operating ∆V GSMAX at the various operating V CC . From this table users can refer to the MOSFET’s data sheet to obtain the R DSON(NOM) value.Table 1. Nominal Operating ∆V GSMAX for Typical Bias Supply VoltageV CC (V)∆V GSMAX (V)2.3 4.32.5 5.02.7 5.63.0 6.53.37.05.07.06.07.0Load Supply Power-Up after Circuit Breaker Armed Figure 4 shows a normal power-up sequence for the circuit in Figure 1 where the V IN load supply power-up after circuit breaker is armed. V CC is first powered up by an auxiliary bias supply. V CC rises above 2.07V at time point 1. V ON exceeds 0.8V at time point 2. After a 60µs debounce delay, the GATE pin starts ramping up at time point 3. The external MOSFET starts conducting at time point 4. At time point 5, V GATE exceed ∆V GSARM and the circuit breaker is armed. After 50µs (t READY delay), READY pulls high by an external resistor at time point 6. READY signals the V IN load supply module to start its ramp. The load supply begins soft-start ramp at time point 7. The load supply ramp rate must be slow to prevent circuit breaker tripping as in equation (8).∆∆V t I I C IN OPMAX LOADLOAD<−()8Where I OPMAX is the maximum operating current defined by equation 7.For illustration, V CB = 25mV and R DSON = 3.5m Ω at the nominal operating ∆V GSMAX . The maximum operating current is 3.5A (refer to equation 7). Assuming the load can draw a current of 2A at power-up, there is a margin of 1.5A available for C LOAD of 100µF and V IN ramp rate should be <15V/ms. At time point 8, the current through the MOSFET reduces after C LOAD is fully charged.APPLICATIO S I FOR ATIOW UUU1516174213fThe selected MOSFET V GS absolute maximum rating should meet the LTC4213 maximum ∆V GSMAX of 8V.Other MOSFET criteria such as V BDSS , I DMAX , and R DSON should be reviewed. Spikes and ringing above maximum operating voltage should be considered when choosing V BDSS . I DMAX should be greater than the current limit. The maximum operating load current is determined by the R DSON value. See the section on “Calculating Current Limit” for details.Supply RequirementsThe LTC4213 can be powered from a single supply or dual supply system. The load supply is connected to the SENSEP pin and the drain of the external MOSFET. In the single supply case, the V CC pin is connected to the load supply, preferably with an RC filter. With dual supplies,V CC is connected to an auxiliary bias supply V AUX where V AUX voltage should be greater or equal to the load supply voltage. The load supply voltage must be capable of sourcing more current than the circuit breaker limit. If the load supply current limit is below the circuit breaker trip current, the LTC4213 may not react when the output overloads. Furthermore, output overloads may trigger UVLO if the load supply has foldback current limit in a single supply system.V IN Transient and Overvoltage ProtectionInput transient spikes are commonly observed whenever the LTC4213 responds to overload. These spikes can be large in amplitude, especially given that large decoupling capacitors are absent in hot swap environments. These short spikes can be clipped with a transient suppressor of adequate voltage and power rating. In addition, the LTC4213can detect a prolonged overvoltage condition. WhenAPPLICATIO S I FOR ATIOW UUU point 6 should be within the circuit breaker limits. Other-wise, the system fails to start and the circuit breaker trips immediately after arming. In most applications additional external gate capacitance is not required unless C LOAD is large and startup becomes problematic. If an external gate capacitor is employed, its capacitance value should not be excessive unless it is used with a series resistor. This is because a big gate capacitor without resistor slows down the GATE turn off during a fault. An alternative method would be a stepped I SEL pin to allow a higher current limit during startup.In the event of output short circuit or a severe overload, the load supply can collapse during GATE ramp up due to load supply current limit. The chosen MOSFET must withstand this possible brief short circuit condition before time point 6 where the circuit breaker is allowed to trip. Bench short circuit evaluation is a practical verification of a reliable design. To have current limit while powering a MOSFET into short circuit conditions, it is preferred that the load supply sequences to turn on after the circuit breaker is armed as described in an earlier section.Power-Off CycleThe system can be powered off by toggling the ON pin low.When ON is brought below 0.76V for 5µs, the GATE and READY pins are pulled low. The system resets when ON is brought below 0.4V for 80µs.MOSFET SelectionThe LTC4213 is designed to be used with logic (5V) and sub-logic (3V) MOSFETs for V CC potentials above 2.97V with ∆V GSMAX exceeding 4.5V. For a V CC supply range between 2.3V and 2.97V, sub-logic MOSFETs should be used as the minimum ∆V GSMAX is less than 4.5V.1819Information furnished by Linear Technology Corporation is believed to be accurate and reliable.However, no responsibility is assumed for its use. Linear Technology Corporation makes no represen-tation that the interconnection of its circuits as described herein will not infringe on existing patent rights.201630 McCarthy Blvd., Milpitas, CA 95035-7417(408) 432-1900 ● FAX: (408) 434-0507 ● © LINEAR TECHNOLOGY CORPORA TION 2005LT/TP 0405 500 • PRINTED IN USA。

LTC4263CS LTC4263CDE 示例电路981A B主板, 单端口自主PSE DAUGHT

LTC4263 in single port Power Over Ethernet (PoE) Power Sourcing Equipment (PSE) Midspan and End-point solutions. The LTC4263 is an autonomous sin-gle-channel PSE controller for use in IEEE802.3af compliant PoE systems. It includes an on-board pla-nar power MOSFET, internal inrush, current limit, and short circuit control, Powered Device (PD) detection and classification circuitry, and selectable AC or DC disconnect sensing. On-board control algorithms provide complete PSE Control operation without the need of a microcontroller. The LTC4263 simplifies ply and a small number of passive support compo-nents. Other options shown on the DC981A include Legacy PD detection enable, Midspan back off timer enable, power class enforce mode, power manage-ment enable. An LED for each port is driven by the respective LTC4263 to indicate the state of the port. Design files for this circuit board are available. Call the LTC factory.LTC is a trademark of Linear Technology CorporationTable 1. Typical DC981 Performance Summary (T A = 25°C)PARAMETER CONDITION VALUE Supply Voltage Voltage for IEEE802.3af Compliance at Port Output 46V to 57V Midspan Mode Detection Backoff Midspan Enabled, Failed Detection 3.2 seconds Detection Range Valid IEEE802.3af PD Detection 17k to 29.7k Set Maximum Allocated Power Power Management Enabled 17WEthernet Powered Pairs Pinout Endpoint PSE, Alternative A (MDI)Midspan PSE, Alternative B1/2(+), 3/6(-)4/5(+) , 7/8 (-)QUICK START PROCEDUREDemonstration circuit 981 is easy to set up to evaluate the performance of the LTC4263. Refer to Figure 2 for proper measurement equipment setup and follow the procedure below.1.Place jumpers in the following positions:ENENDISACACEN 2.Insert daughter card (DC981B) to main board (DC981A) at polarized connector J3.3.Apply 48V across VDD48 and VSS.4.Connect a scope probe at VOUT_MD and VOUT_EP both referenced to positive rail VDD48.5.Connect a valid PD to either Midspan PSE or Endpoint PSE.6.Connect a second PD to the open port.JP1 JP2 JP3 JP4 JP5 JP6Figure 1.Basic DC981A/B Equipment Setupto power the board. This in turn provides power to the Midspan PSE and Endpoint PSE outputs. On each solution, an LTC4263 provides detection of a PD, classification, power management, safe power on of the PD, port current limit, and disconnect detection. Midspan PSE and Midspan ModeIn the Midspan solution, a device (router, switch, etc.) that does not have PoE is connected to MIDSPAN IN. Data is passed through to MIDSPAN OUT along with PoE which goes out to a PD. Power is applied di-rectly to Ethernet pairs 4/5 and 7/8. The LTC4263 circuitry sits in a small layout area behind the RJ45 connector and switches power on the negative rail. To show the different functions of the LTC4263, jumpers allow for the user to select the options of AC or DC disconnect, legacy detection, Midspan backoff timing, and class enforcement. An LED that shows the status of the port is driven by a switcher in the LTC4263 to improve efficiency when VDD5 is pro-vided internally. Push button switch SW1 ties the shutdown pin to ground to disable the LTC4263 in the Midspan solution.A PSE implementing AlternativeB pin out must back off from detection for at least 2 seconds after a failed attempt. This is to avoid conflict of Detection, for ex-ample, should a potential Endpoint PSE and Midspan PSE be connected to the same PD. To enable this feature, set JP2 to DIS. JP2 ties the MIDSPAN pin to VDD5 to enable the LTC4263 backoff timer or to VSS to disable. A 3.2 second delay occurs after every failed detect cycle unless the result is open circuit. If held at VSS, no delay occurs after failed detect cycles. Endpoint PSEThe Endpoint solution is primarily shown on a small daughter card (DC981B). This card is the same height and width as the integrated RJ45 connector that it slides behind on the main board (DC981A). The RJ45 includes Ethernet magnetics and common ter card are VSS, VDD48 and VOUT. Power is switched over from the daughter card out to the Ethernet data pairs (1/2 and 7/8). A PHY can be con-nected to the “TO PHY” to pass data through to the data pairs along with PoE. LED drive and power management pins are also brought out for additional board functions. The board is set up for AC discon-nect, but can be reworked for DC disconnect by re-moving components and replacing with shorts in cer-tain locations. Two solder jumpers also provide se-lectable options for legacy detection and class en-force.Power ManagementThe Midspan and Endpoint PSE, although separate solutions on the DC981, are tied together at the PWRMGT pin for demonstration of the LTC4263 power management capability. Programmable on-board power management circuitry allows multiple LTC4263s to allocate and share power in multi-port systems, allowing maximum utilization of the 48V power supply – all without the intervention of a host processor.The LTC4263 sources current at the PWRMGT pin proportional to the class of the PD that it is powering. The voltage of this pin is checked before powering the port. The port will not turn on if this pin is more than 1V above VSS. The PWRMGT pins of the LTC4263s are tied together and connect to a resistor (RPM) and capacitor (CPM) in parallel to VSS to implement power management among multiple ports. This re-sistor is selected with the following equation:RPM= 213k * W / PFULL_LOADOn the DC981A, the default RPMis 12.4k for a full load power of 17W.19 33 73*RPM= 12.4kTable 3. Powered Device CombinationsPD COMBINATION 1ST PD 2ND PDClass 1 / Class 1 Powered PoweredClass 1 / Class 2 Powered PoweredClass 1 / Class 3** Powered Power Denied Class 2 / Class 2 Powered PoweredClass 2 / Class 3** Powered Power Denied Class 3 **/ Class 3** Powered Power Denied**Class 3 substitutable with Class 0 or 4.If power management is not used, move JP6 to DIS to tie the PWRMGT pins to VSS and disable this fea-ture.Class Enforce ModeENFORCE CLASS jumper JP1 ties the ENFCLS pin of the LTC4263 to either VDD5 or VSS to respectively enable or disable class enforce current limits. If held at VDD5, the LTC4263 will reduce the ICUT threshold for Class 1 or Class 2 PDs. If ENFCLS is held at VSS, ICUT remains at 375mA (typical) for all classes. Table 4. Port Current Limit According to ClassPD CLASS CURRENT THRESHOLD (TYPICAL)Class 1 100mAClass 2 175mAClass 0, 3, 4, or Class En-force Disabled375mALED DriveAn LED pin indicates the state of the port controlled by the LTC4263. When the port is powered, the LED is on; when disconnected or detecting, the LED is off. If an invalid signature is detected or a fault occurs, the LED will flash a pattern that the user or host sys-The logic 5V power supply can be supplied from the internal LTC4263 5V supply or an external 5V supply when above the internal supply. If the internal regula-tor is used, this pin should only be connected to the bypass capacitor and to any logic pins of the LTC4263 that are being held at VDD5.AC and DC DisconnectAC and DC disconnect are two different methods of detecting whether a valid PD is present and requires power. AC disconnect is the default method for the DC981 but can be converted to DC disconnect in the Midspan solution through two jumpers. Moving DISCON (JP4) to DC will short the ACCOUT pin to VSS and configure the LTC4263 to DC disconnect. Moving jumper setting for ACCOMP (JP5) to DC by-passes the AC blocking diode and removes the RC used for AC disconnect from the main circuit. Legacy DetectionLEGACY jumper JP3 controls whether legacy detect is enabled. If the LEGACY pin is held at VDD5 (EN se-lected), legacy detect is enabled and testing for a large capacitor is performed to detect the presence of a legacy PD on the port. If held at VSS (DIS se-lected), only IEEE 802.3af compliant PDs are de-tected. If left floating (no jumper), the LTC4263 enters force-power-on mode and any PD that generates be-tween 1V and 10V when biased with 270µA of detec-tion current will be powered as a legacy device. This mode is useful if the system uses a differential detec-tion scheme to detect legacy devices. Warning: Leg-acy modes are not IEEE 802.3af compliant.Figure 2.DC981 Options。

LTC2302资料

123026fT YPICAL APPLICATIONF EATURESA PPLICATIONSD ESCRIPTION 1-/2-Channel, 12-Bit ADCsThe L TC ®2302/L TC2306 are low noise, 500ksps, 1-/2-chan-nel, 12-bit ADCs with an SPI/MICROWIRE compatible serial interface. These ADCs include a fully differential sample-and-hold circuit to reduce common mode noise. The internal conversion clock allows the external serial output data clock (SCK) to operate at any frequency up to 40MHz.The L TC2302/L TC2306 operate from a single 5V supply and draw just 2.8mA at a sample rate of 500ksps. The auto-shutdown feature reduces the supply current to 14μA at a sample rate of 1ksps.The L TC2302/L TC2306 are packaged in a tiny 10-pin 3mm × 3mm DFN. The low power consumption and small size make the L TC2302/L TC2306 ideal for battery-operated and portable applications, while the 4-wire SPI compat-ible serial interface makes these ADCs a good match for isolated or remote data acquisition systems.8192 Point FFT , f IN = 1kHz (L TC2306)n12-Bit Resolutionn 500ksps Sampling Rate n Low Noise: SINAD = 72.8dB n Guaranteed No Missing Codes n Single 5V SupplynAuto-Shutdown Scales Supply Current with Sample Raten Low Power: 14mW at 500ksps 70μW at 1ksps 35μW Sleep Moden 1-Channel (L TC2302) and 2-Channel (L TC2306) Versionsn Unipolar or Bipolar Input Ranges (Software Selectable)n Internal Conversion Clockn SPI/MICROWIRE ™ Compatible Serial Interface n Separate Output Supply OV DD(2.7V to 5.25V)n Software Compatible with the L TC2308n 10-Pin (3mm × 3mm) DFN PackagenHigh Speed Data Acquisition n Industrial Process Control n Motor Control n Accelerometer Measurements n Battery-Operated Instrumentsn Isolated and/or Remote Data AcquisitionTYPENUMBER OF INPUT CHANNELS128Int Reference L TC2308Ext ReferenceL TC2302L TC2306L , L T , L TC and L TM are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.CH0 (IN +CH1 (IN –ANALOG INPUTS 0V TO 4.096V UNIPOLAR±2.048V BIPOLAR REFFREQUENCY (kHz)0–40–20020023026 TA01b–60–8050100150250–100–120–50–30–10–70–90–110–130–140M A G N I T U D E (d B )f SMPL = 500kHz SINAD = 72.8dB THD = –88.7dB223026fA BSOLUTE MAXIMUM RATINGS Supply Voltage (V DD , OV DD ) .........................–0.3V to 6V Analog Input Voltage (Note 3) C H0(IN +)-CH1(IN –),REF ..............................(GND – 0.3V) to (V DD + 0.3V)Digital Input Voltage (Note 3) .............................(GND – 0.3V) to (V DD + 0.3V)(Notes 1, 2)LEAD FREE FINISH TAPE AND REEL PART MARKING*PACKAGE DESCRIPTIONTEMPERATURE RANGE L TC2302CDD#PBF L TC2302CDD#TRPBF LDGV 10-Lead (3mm × 3mm) Plastic DFN 0°C to 70°C L TC2302IDD#PBF L TC2302IDD#TRPBF LDGV 10-Lead (3mm × 3mm) Plastic DFN –40°C to 85°C L TC2306CDD#PBF L TC2306CDD#TRPBF LDGW 10-Lead (3mm × 3mm) Plastic DFN 0°C to 70°C L TC2306IDD#PBFL TC2306IDD#TRPBFLDGW10-Lead (3mm × 3mm) Plastic DFN–40°C to 85°CConsult L TC Marketing for parts specifi ed with wider operating temperature ranges. *The temperature grade is identifi ed by a label on the shipping container .Consult L TC Marketing for information on non-standard lead based fi nish parts.For more information on lead free part marking, go to: http://www.linear .com/leadfree/ For more information on tape and reel specifi cations, go to: http://www.linear .com/tapeandreel/ORDER INFORMATIONTOP VIEW11L TC2302DD PACKAGE10-LEAD (3mm s 3mm) PLASTIC DFN10967845321OV DD SCK SDI GND V REFSDO CONVST V DD IN +IN –T JMAX = 150°C, θJA = 43°C/WEXPOSED PAD (PIN 11) IS GND, MUST BE SOLDERED TO PCBTOP VIEW11L TC2306DD PACKAGE10-LEAD (3mm s 3mm) PLASTIC DFN10967845321OV DD SCK SDI GND V REFSDO CONVST V DD CH0CH1T JMAX = 150°C, θJA = 43°C/WEXPOSED PAD (PIN 11) IS GND, MUST BE SOLDERED TO PCBP IN CONFIGURATION Digital Output Voltage ...(GND – 0.3V) to (OV DD + 0.3V)Power Dissipation ...............................................500mW Operating Temperature RangeL TC2302C/L TC2306C ...............................0°C to 70°C L TC2302I/L TC2306I ..............................–40°C to 85°C Storage Temperature Range ...................–65°C to 150°C323026fCONVERTER AND MULTIPLEXER CHARACTERISTICS SYMBOL PARAMETERCONDITIONS MIN TYP MAX UNITSV IN +Absolute Input Range (CH0, CH1, IN +)(Note 9)l –0.05V DD V V IN –Absolute Input Range (CH0, CH1, IN –)Unipolar (Note 9)Bipolar (Note 9)l l –0.05–0.05V DD /2V DDV V V IN + – V IN –Input Differential Voltage Range V IN = V IN + – V IN – (Unipolar)V IN = V IN + – V IN – (Bipolar)l l 0 to V REF ±V REF /2V VI IN Analog Input Leakage Current l±1μA C IN Analog Input CapacitanceSample Mode Hold Mode555pF pF CMRRInput Common Mode Rejection Ratio70dBThe l denotes the specifi cations which apply over the full operating temperature range, otherwise specifi cations are at T A = 25°C. (Notes 4, 5)PARAMETERCONDITIONSMIN TYP MAX UNITS Resolution (No Missing Codes)l12Bits Integral Linearity Error (Note 6)l ±0.3±1LSB Differential Linearity Error l±0.25±1LSB Bipolar Zero Error (Note 7)l±1±6LSB Bipolar Zero Error Drift 0.002LSB/°C Unipolar Zero Error (Note 7)l±1±6LSB Unipolar Zero Error Drift0.002LSB/°C Unipolar Zero Error Match (L TC2306)±0.3±3LSB Bipolar Full-Scale Error (Note 8)l ±1.5±8LSB Bipolar Full-Scale Error Drift 0.05LSB/°C Unipolar Full-Scale Error (Note 8)l±1.2±6LSB Unipolar Full-Scale Error Drift0.05LSB/°C Unipolar Full-Scale Error Match (L TC2306)±0.3±3LSBANALOG INPUT The l denotes the specifi cations which apply over the full operating temperature range, otherwisespecifi cations are at T A = 25°C. (Note 4)SYMBOLPARAMETER CONDITIONSMIN TYP MAX UNITSV REF Input Rangel 0.1V DD V I REF Reference Input Current f SMPL = 0ksps, V REF = 4.096Vf SMPL = 500ksps, V REF = 4.096Vl l5023080260μA μA C REFReference Input Capacitance55pFREFERENCE INPUT The l denotes the specifi cations which apply over the full operating temperature range,otherwise specifi cations are at T A = 25°C. (Note 4)423026fSYMBOL PARAMETERCONDITIONS MIN TYP MAX UNITSV IH High Level Input Voltage V DD = 5.25V l 2.4V V IL Low Level Input Voltage V DD = 4.75V l 0.8V I IN High Level Input Current V IN = V DDl±10μA C IN Digital Input Capacitance 5pF V OH High Level Output Voltage OV DD = 4.75V , I OUT = –10μAOV DD = 4.75V , I OUT = –200μA l 44.74V VV OL Low Level Output Voltage OV DD = 4.75V , I OUT = 160μA OV DD = 4.75V , I OUT = 1.6mA l 0.050.4V V I OZ Hi-Z Output Leakage V OUT = 0V to OV DD , CONVST High l±10μA C OZ Hi-Z Output Capacitance CONVST High 15pF I SOURCE Output Source Current V OUT = 0V –10mA I SINKOutput Sink CurrentV OUT = OV DD10mADIGITAL INPUTS AND DIGITAL OUTPUTS The l denotes the specifi cations which apply over thefull operating temperature range, otherwise specifi cations are at T A = 25°C. (Note 4)SYMBOL PARAMETER CONDITIONSMIN TYP MAX UNITSV DD Supply Voltagel 4.755 5.25V OV DD Output Driver Supply Voltage l 2.75.25V I DD Supply CurrentSleep Mode C L = 25pFCONVST = 5V , Conversion Done l l2.873.515mA μA P DPower Dissipation Sleep Mode1435mW μWPOWER REQUIREMENTS The l denotes the specifi cations which apply over the full operating temperaturerange, otherwise specifi cations are at T A = 25°C. (Note 4)SYMBOL PARAMETERCONDITIONS MIN TYP MAX UNITS SINAD Signal-to-(Noise + Distortion) Ratio f IN = 1kHz l 7172.8dB SNR Signal-to-Noise Ratio f IN = 1kHzl 7173.2dBTHD Total Harmonic Distortion f IN = 1kHz, First 5 Harmonics l –88–78dB SFDRSpurious Free Dynamic Range f IN = 1kHz l7989dB Channel-to-Channel Isolation f IN = 1kHz –109dB Full Linear Bandwidth (Note 11)700kHz –3dB Input Linear Bandwidth 25MHz Aperature Delay 13ns T ransient ResponseFull-Scale Step 240nsDYNAMIC ACCURACY The l denotes the specifi cations which apply over the full operating temperature range,otherwise specifi cations are at T A = 25°C. A IN = –1dBFS. (Notes 4, 10)TIMING CHARACTERISTICSThel denotes the specifi cations which apply over the full operating temperature range, otherwise specifi cations are at T A = 25°C. (Note 4)SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS f SMPL(MAX)Maximum Sampling Frequency l500kHz f SCK Shift Clock Frequency l40MHz t WHCONV CONVST High Time(Note 9)l20ns t HD Hold Time SDI After SCK↑l 2.5ns t SUDI Setup Time SDI Stable Before SCK↑l0ns t WHCLK SCK High Time f SCK = f SCK(MAX)l10ns t WLCLK SCK Low Time f SCK = f SCK(MAX)l10ns t WLCONVST CONVST Low Time During Data T ransfer(Note 9)l410ns t HCONVST Hold Time CONVST Low After Last SCK↓(Note 9)l20ns t CONV Conversion Time l 1.3 1.6μs t ACQ Acquisition Time7th SCK↑ to CONVST↑ (Note 9)l240ns t dDO SDO Data Valid After SCK↓C L = 25pF (Note 9)l10.812.5ns t hDO SDO Hold Time SCK↓C L = 25pF l4ns t en SDO Valid After CONVST↓C L = 25pF l1115ns t dis Bus Relinquish Time C L = 25pF l1115ns t r SDO Rise Time C L = 25pF4ns t f SDO Fall Time C L = 25pF4ns t CYC Total Cycle Time2μsNote 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.Note 2: All voltage values are with respect to ground with V DD and OV DD wired together (unless otherwise noted).Note 3: When these pin voltages are taken below ground or above V DD, they will be clamped by internal diodes. These products can handle input currents greater than 100mA below ground or above V DD without latchup. Note 4: V DD = 5V, OV DD = 5V, V REF = 4.096V, f SMPL = 500ksps, unless otherwise specifi ed.Note 5: Linearity, offset and full-scale specifi cations apply for a single-ended analog input with respect to GND for the L TC2306 and IN+ with respect to IN– tied to GND for the L TC2302.Note 6: Integral nonlinearity is defi ned as the deviation of a code from a straight line passing through the actual endpoints of the transfer curve. The deviation is measured from the center of the quantization band.Note 7: Bipolar zero error is the offset voltage measured from –0.5LSB when the output code fl ickers between 0000 0000 0000 and 1111 1111 1111. Unipolar zero error is the offset voltage measured from +0.5LSB when the output code fl ickers between 0000 0000 0000 and 0000 0000 0001.Note 8: Full-scale bipolar error is the worst-case of –FS or +FS untrimmed deviation from ideal fi rst and last code transitions and includes the effect of offset error. Unipolar full-scale error is the deviation of the last code transition from ideal and includes the effect of offset error.Note 9: Guaranteed by design, not subject to test.Note 10: All specifi cations in dB are referred to a full-scale ±2.048V input with a 4.096V reference voltage.Note 11: Full linear bandwidth is defi ned as the full-scale input frequency at which the SINAD degrades to 60dB or 10 bits of accuracy.523026f623026fT YPICAL PERFORMANCE CHARACTERISTICS Integral Nonlinearity vs Output CodeDifferential Nonlinearity vsOutput Code1kHz Sine Wave 8192 Point FFT PlotSNR vs Input FrequencySINAD vs Input FrequencyTHD vs Input FrequencySupply Current vs Sampling FrequencySupply Current vs Temperature(L TC2302) T A = 25°C, V DD = OV DD = 5V , V REF = 4.096V , f SMPL= 500ksps, unless otherwise noted.OUTPUT CODEI N L (L S B )00.250.50409623026 G01–0.25–0.50–1.00102420483072–0.751.000.75OUTPUT CODED N L (L S B )0.250.50409623026 G02–0.25–0.50–1.00102420483072–0.751.000.75FREQUENCY (kHz)0–40–20020023026 G03–60–8050100150250–100–120–50–30–10–70–90–110–130–140M A G N I T U D E (d B )SNR = 73.2dB SINAD = 72.8dBTHD = –89.5dBFREQUENCY (kHz)150S N R (d B )70758010100100023026 G04656055FREQUENCY (kHz)150S I N A D (d B )70758010100100023026 G05656055FREQUENCY (kHz)1–80T HD (d B )–70–6010100100023026 G06–90–85–75–65–95–100SAMPLING FREQUENCY (ksps)12.0S U P P L Y C U RR E N T (m A )2.53.03.510100100023026 G071.51.00.50TEMPERATURE (°C)–502.0SU P P L Y C U R R E N T (m A )2.22.62.83.04.03.40507523026 G082.43.63.83.2–2525100125723026fSleep Current vs TemperatureTYPICAL PERFORMANCE CHARACTERISTICSAnalog Input Leakage Current vs TemperatureOffset Error vs TemperatureFull-Scale Error vs Temperature(L TC2302) T A = 25°C, V DD = OV DD = 5V , V REF = 4.096V , f SMPL = 500ksps, unless otherwise noted.TEMPERATURE (°C)–500S L E E P C U R R E N T (μA )13451070507523026 G092896–2525100125TEMPERATURE (°C)–500I N P U T L E A K A G E C U R R E N T (n A )10030040050010007000507523026 G10200800900600–2525100125TEMPERATURE (°C)–50–1.0–1.5–2.0–2.5O F F S E T E R R O R (L S B )–0.50.51.01.52.50507523026 G1102.0–2525100125TEMPERATURE (°C)–50F U L L -S C A L E E R R O R (L S B )1.52523026 G120–1.0–2550–1.5–2.02.01.00.5–0.575100125823026fT YPICAL PERFORMANCE CHARACTERISTICS Integral Nonlinearity vs Output CodeDifferential Nonlinearity vsOutput Code1kHz Sine Wave 8192 Point FFT PlotSNR vs Input FrequencySINAD vs Input FrequencyTHD vs Input FrequencySupply Current vs Sampling FrequencySupply Current vs Temperature(L TC2306) T A = 25°C, V DD = OV DD = 5V , V REF = 4.096V , f SMPL = 500ksps, unless otherwise noted.OUTPUT CODEI N L (L S B)00.250.50409623026 G13–0.25–0.50–1.00102420483072–0.751.000.75–0.751.000.75M A G N I T U D E (d B )FREQUENCY (kHz)150S N R (d B )70758010100100023026 G16656055FREQUENCY (kHz)150S I N A D (d B )70758010100100023026 G17656055FREQUENCY (kHz)1–80T H D (d B )–70–6010100100023026 G18–90–85–75–65–95–100SAMPLING FREQUENCY (ksps)12.0S U P P L Y C U R R E N T (m A )2.53.03.510100100023026 G191.51.00.5TEMPERATURE (°C)–502.0S U P P L Y C U R R E N T (m A )2.22.62.83.04.03.40507523026 G202.43.63.83.2–2525100125923026fSleep Current vs TemperatureTYPICAL PERFORMANCE CHARACTERISTICSAnalog Input Leakage Current vs TemperatureOffset Error vs TemperatureFull-Scale Error vs Temperature(L TC2306) T A = 25°C, V DD = OV DD = 5V , V REF = 4.096V , f SMPL = 500ksps, unless otherwise noted.TEMPERATURE (°C)–500S L E E P C U R R E N T (μA )13451070507523026 G212896–2525100125TEMPERATURE (°C)–500I N P U T L E A K A G E C U R R E N T (n A )10030040050010007000507523026 G22200800900600–2525100125TEMPERATURE (°C)–50O F F S E T E R R O R (L S B )1.52523026 G230–1.0–2550–1.5–2.02.01.00.5–0.575100125TEMPERATURE (°C)–50F U L L -S C A L E E R R O R (L S B )1.52523026 G240–1.0–2550–1.5–2.02.01.00.5–0.575100125P IN FUNCTIONSL TC2302SDO (Pin 1): Three-State Serial Data Out. SDO outputs the data from the previous conversion. SDO is shifted out serially on the falling edge of each SCK pulse. SDO is enabled by a low level on CONVST.CONVST (Pin 2): Conversion Start. A rising edge at CONVST begins a conversion. For best performance, ensure that CONVST returns low within 40ns after the conversion starts or after the conversion ends.V DD (Pin 3): 5V Supply. The range of V DD is 4.75V to 5.25V. Bypass V DD to GND with a 0.1μF ceramic capacitor and a 10μF tantalum capacitor in parallel.IN+, IN– (Pin 4, Pin 5): Positive (IN+) and Negative (IN–) Differential Analog Inputs.V REF (Pin 6): Reference Input. Connect an external refer-ence at V REF . The range of the external reference is 0.1V to V DD. Bypass to GND with a minimum 10μF tantalum capacitor in parallel with a 0.1μF ceramic capacitor. GND (Pin 7): Ground. All GND pins must be connected to a solid ground plane.SDI (Pin 8): Serial Data Input. The SDI serial bit stream confi gures the ADC and is latched on the rising edge of the fi rst 6 SCK pulses.SCK (Pin 9): Serial Data Clock. SCK synchronizes the serial data transfer. The serial data input at SDI is latched on the rising edge of SCK. The serial data output at SDO transitions on the falling edge of SCK.OV DD (Pin 10): Output Driver Supply. Bypass OV DD to GND with a 0.1μF ceramic capacitor close to the pin. The range of OV DD is 2.7V to 5.25V.Exposed Pad (Pin 11): Exposed Pad Ground. Must be soldered directly to ground plane.L TC2306SDO (Pin 1): Three-State Serial Data Out. SDO outputs the data from the previous conversion. SDO is shifted out serially on the falling edge of each SCK pulse. SDO is enabled by a low level on CONVST.CONVST (Pin 2): Conversion Start. A rising edge at CONVST begins a conversion. For best performance, ensure that CONVST returns low within 40ns after the conversion starts or after the conversion ends.V DD (Pin 3): 5V Supply. The range of V DD is 4.75V to 5.25V. Bypass V DD to GND with a 0.1μF ceramic capacitor and a 10μF tantalum capacitor in parallel.CH0, CH1 (Pin 4, Pin 5): Channel 0 and Channel 1 Analog Inputs. CH0, CH1 can be confi gured as single-ended or differential input channels. See the Analog Input Multi-plexer section.V REF (Pin 6): Reference Input. Connect an external refer-ence at V REF .The range of the external reference is 0.1V to V DD. Bypass to GND with a minimum 10μF tantalum capacitor in parallel with a 0.1μF ceramic capacitor. GND (Pin 7): Ground. All GND pins must be connected to a solid ground plane.SDI (Pin 8): Serial Data Input. The SDI serial bit stream confi gures the ADC and is latched on the rising edge of the fi rst 6 SCK pulses.SCK (Pin 9): Serial Data Clock. SCK synchronizes the serial data transfer. The serial data input at SDI is latched on the rising edge of SCK. The serial data output at SDO transitions on the falling edge of SCK.OV DD (Pin 10): Output Driver Supply. Bypass OV DD to OGND with a 0.1μF ceramic capacitor close to the pin. The range of OV DD is 2.7V to 5.5V.Exposed Pad (Pin 11): Exposed Pad Ground. Must be soldered directly to ground plane.1023026f1123026fB LOCK DIAGRAM TEST CIRCUITSTIMING DIAGRAMSVoltage Waveforms for SDO Delay Times, t dDO and t hDOVoltage Waveforms for t disLoad Circuit for t dis Waveform 1Load Circuit for t dis Waveform 2, t enSDISDO SCK CONVSTCH0 (IN +CH1 (IN –REFV OVVSCKSDOOH OLSDOWAVEFORM 1(SEE NOTE 1)SDOWAVEFORM 2(SEE NOTE 2)CONVST NOTE 1: WAVEFORM 1 IS FOR AN OUTPUT WITH INTERNAL CONDITIONS SUCH THAT THE OUTPUT IS HIGH UNLESS DISABLED BY THE OUTPUT CONTROL NOTE 2: WAVEFORM 2 IS FOR AN OUTPUT WITH INTERNAL CONDITIONS SUCH THAT THE OUTPUT IS LOW UNLESS DISABLED BY THE OUTPUT CONTROL23026 TD021223026fTIMING DIAGRAMSt WLCLK (SCK Low Time)t WHCLK (SCK High Time)t HD (Hold Time SDI After SCK ↑)t SUDI (Setup Time SDI Stable Before SCK ↑)Voltage Waveforms for t enVoltage Waveforms for SDO Rise and Fall Times t r , t fA PPLICATIONS INFORMATIONSCKSDICONVSTSDOOH OLOverviewThe L TC2302/L TC2306 are low noise, 500ksps, 1-/2-chan-nel, 12-bit successive approximation register (SAR) A/D converters. The L TC2306 includes a 2-channel analog input multiplexer (MUX) while the L TC2302 includes an input MUX that allows the polarity of the differential input to be selected. Both ADCs include an SPI-compatible se-rial port for easy data transfers and can operate in either unipolar or bipolar mode. Unipolar mode should be used for single-ended operation with the L TC2306, since single-ended input signals are always referenced to GND. The L TC2302/L TC2306 can be put into a power-down sleep mode during idle periods to save power .Conversions are initiated by a rising edge on the CONVST input. Once a conversion cycle has begun, it cannot be restarted. Between conversions, a 6-bit input word (D IN ) at the SDI input confi gures the MUX and programs vari-ous modes of operation. As the D IN bits are shifted in, data from the previous conversion is shifted out on SDO. After the 6 bits of the D IN word have been shifted in, the ADC begins acquiring the analog input in preparation for the next conversion as the rest of the data is shifted out.The acquire phase requires a minimum time of 240ns for the sample-and-hold capacitors to acquire the analog input signal.During the conversion, the internal 12-bit capacitive charge-redistribution DAC output is sequenced through a successive approximation algorithm by the SAR starting from the most signifi cant bit (MSB) to the least signifi cant bit (LSB). The sampled input is successively compared with binary weighted charges supplied by the capacitive DAC using a differential comparator . At the end of a conver-sion, the DAC output balances the analog input. The SAR contents (a 12-bit data word) that represent the sampled analog input are loaded into 12 output latches that allow the data to be shifted out.Programming the L TC2306 and L TC2302The software compatible L TC2302/L TC2306/L TC2308 fam-ily features a 6-bit D IN word to program various modes of operation. Don’t care bits (X) are ignored. The SDI data bits are loaded on the rising edge of SCK, with the S/D bit loaded on the fi rst rising edge (see Figure 6 in the Timing1323026fA PPLICATIONS INFORMATION Figure 1a. Example MUX Confi gurationsFigure 1b. Changing the MUX Assignment “On the Fly”and Control section). The input data word for the L TC2306 is defi ned as follows:S/D O/SXXUNIXS/D = SINGLE-ENDED/DIFFERENTIAL BIT O/S = ODD/SIGN BIT UNI = UNIPOLAR/BIPOLAR BIT X = DON’ T CAREFor the L TC2302, the input data word is defi ned as:XO/SXXUNIXAnalog Input MultiplexerThe analog input MUX is programmed by the S/D and O/S bits of the D IN word for the L TC2306 and the O/S bit of the D IN word for the L TC2302. Table 1 and Table 2 list MUX confi gurations for all combinations of the confi guration bits. Figure 1a shows several possible MUX confi gurations and Figure 1b shows how the MUX can be reconfi gured from one conversion to the next.Driving the Analog InputsThe analog inputs of the L TC2302/L TC2306 are easy to drive. Each of the analog inputs of the L TC2306 (CH 0 and CH1) can be used as a single-ended input relative to GND or as a differential pair . The analog inputs of theL TC2302 (IN +, IN –) are always configured as a differential pair . Regardless of the MUX confi guration, the “+” and “–” inputs are sampled at the same instant. Any unwanted signal that is common to both inputs will be reduced by the common mode rejection of the sample-and-hold cir-cuit. The inputs draw only one small current spike while2 Single-Ended1 Differential+(–)–(+) 1 Differential+(–)–(+)2nd Conversion1st Conversion+–S/D 0011O/S 0101CH0+–+CH1–++WITH RESPECT TO GNDNOTE: UNIPOLAR MODE SHOULD BE USEDFOR SINGLE-ENDED OPERATION, SINCE INPUT SIGNALS ARE ALWAYS REFERENCED TO GNDTable 1. Channel Configurationfor the L TC2306O/S 01IN ++–IN ––+Table 2. Channel Configuration for the L TC23021423026fA PPLICATIONS INFORMATION Figure 2b. Analog Input Equivalent Circuit for Large Filter CapacitancesFigure 2a. Analog Input Equivalent Circuitcharging the sample-and-hold capacitors during the acquire mode. In conversion mode, the analog inputs draw only a small leakage current. If the source impedance of the driving circuit is low, the ADC inputs can be driven directly. Otherwise, more acquisition time should be allowed for a source with higher impedance.ReferenceA low noise, stable reference is required to ensure full performance. The L T ®1790 and L T6660 are adequate for most applications. The L T6660 is available in 2.5V , 3V , 3.3V and 5V versions, and the L T1790 is available in 1.25V , 2.048V , 2.5V , 3V , 3.3V , 4.096V and 5V versions. The exceptionally low input noise allows the input range to be optimized for the application by changing the reference voltage. The V REF input must be decoupled with a 10μF capacitor in parallel with a 0.1μF capacitor , so verify that the device providing the reference voltage is stable with capacitive loads.If the voltage reference is 5V and can supply 5mA, it can be used for both V REF and V DD . V DD must be connected to a clean analog supply, and a quiet 5V reference voltage makes a convenient supply for this purpose.Input FilteringThe noise and distortion of the input amplifi er and other circuitry must be considered since they will add to the ADC noise and distortion. Therefore, noisy input circuitryshould be fi ltered prior to the analog inputs to minimize noise. A simple 1-pole RC fi lter is suffi cient for many applications.The analog inputs of the L TC2302/L TC2306 can be modeled as a 55pF capacitor (C IN ) in series with a 100Ω resistor (R ON ) as shown in Figure 2a. C IN gets switched to the selected input once during each conversion. Large fi lter RC time constants will slow the settling of the inputs. It is important that the overall RC time constants be short enough to allow the analog inputs to completely settle to 12-bit resolution within the acquisition time (t ACQ ) if DC accuracy is important.When using a fi lter with a large C FIL TER value (e.g., 1μF), the inputs do not completely settle and the capacitive input switching currents are averaged into a net DC current (I DC ). In this case, the analog input can be modeled by an equivalent resistance (R EQ = 1/(f SMPL • C IN )) in series with an ideal voltage source (V REF /2) as shown in Figure 2b. The magnitude of the DC current is then approximately I DC = (V IN – V REF /2)/R EQ , which is roughly proportional to V IN . To prevent large DC drops across the resistorR FIL TER , a filter with a small resistor and large capacitor should be chosen. When running at the minimum cycle time of 2μs, the input current equals 106μA at V IN = 5V , which amounts to a full-scale error of 0.5LSB when using a fi lter resistor (R FIL TER ) of 4.7Ω. Applications requiring lower sample rates can tolerate a larger fi lter resistor for the same amount of full-scale error .V IN23026 F02aV IN23026 F02bA PPLICATIONS INFORMATIONFigure 3a. Optional RC Input Filtering for Single-Ended Input Figure 3b. Optional RC Input Filtering for Differential Inputs Figure 4. 1kHz Sine Wave 8192 Point FFT Plot (L TC2306)Figures 3a and 3b show respective examples of input fi ltering for single-ended and differential inputs. For the single-ended case in Figure 3a, a 50Ω source resistor and a 2000pF capacitor to ground on the input will limit the input bandwidth to 1.6MHz. High quality capacitors and resistors should be used in the RC fi lter since these components can add distortion. NPO and silver mica type dielectric capacitors have excellent linearity. Carbon surface mount resistors can generate distortion from self heating and from damage that may occur during soldering. Metal fi lm surface mount resistors are much less susceptible to both problems.Dynamic PerformanceFFT (fast fourier transform) test techniques are used to test the ADC’s frequency response, distortion and noise at the rated throughput. By applying a low distortion sine wave and analyzing the digital output using an FFT algorithm, the ADC’s spectral content can be examined for frequencies outside the fundamental.Signal-to-Noise and Distortion Ratio (SINAD)The signal-to-noise and distortion ratio (SINAD) is the ratio between the RMS amplitude of the fundamental input frequency to the RMS amplitude of all other frequency components at the A/D output. The output is band-limited to frequencies from above DC and below half the sampling frequency. Figure 4 shows a typical SINAD of 72.8dB with a 500kHz sampling rate and a 1kHz input. A SNR of 73.2dB can be achieved with the L TC2302/L TC2306.Total Harmonic Distortion (THD)Total Harmonic Distortion (THD) is the ratio of the RMS sum of all harmonics of the input signal to the fundamental itself. The out-of-band harmonics alias into the frequency band between DC and half the sampling frequency(f SMPL/2). THD is expressed as:THDV V V VVN=+++2022324221log...where V1 is the RMS amplitude of the fundamental fre-quency and V2 through V N are the amplitudes of the second through Nth harmonics.40206080002050307090103040MAGNITUDE(dB)SNR = 73.2dBSINAD = 72.8dBTHD = –88.7dB1523026f。

LTC2387-18正弦信号驱动器的设计要求

LTC2387-18正弦信号驱动器的设计要求简介LTC2387-18是一款高速SAR(逐次逼近寄存器)ADC,适用于高线性度,低噪声应用。

该ADC能够以高达15Msps的速率进行采样,从而可以转换频率为几MHz的信号。

它非常适合在此频率范围内转换脉冲和连续信号。

本文将讨论对设计用于向ADC提供连续正弦信号的驱动器的需求。

噪声性能使得1MHz音调将产生超过96dBFS的SNR。

该音调的总谐波失真通常超过-100dB。

要将ADC驱动至满量程,需要8.192V pk-pk的差分输入信号。

许多传感器和信号源不会产生这么大的电压摆幅,或者无法驱动相对较低的输入阻抗的ADC。

缓冲电路最适合解决这些问题,但它们必须非常线性,并且对信号的噪声很小。

通常,缓冲电路必须向源提供阻抗,该阻抗不会过度加载,并提供电压增益。

如果整个电路要接近ADC满足的规格,运算放大器,无论是单端还是差分,必须具有非常高的性能。

缓冲电路概述如果差分输入信号可用,缓冲电路将执行三个功能。

首先,使用少量输入低通滤波来限制到达放大器的噪声频谱。

然后缓冲信号,通常每侧有一个运算放大器。

在某些情况下,缓冲器包括一些电压增益。

这样可以减轻信号源的驱动要求,但会降低信噪比,因为这种增益可以放大来自信号源的噪声。

最后,信号在传递到ADC之前再次进行低通滤波。

该功能由RC滤波器提供,进一步限制了到达ADC输入的宽带噪声。

滤波器还在滤波电容器之前提供一些串联电阻,这使放大器具有较低的无功负载阻抗。

电容用作来自ADC输入电路的采样瞬变的电荷储存器。

这减小了放大器输出端的采样电荷脉冲的大小。

但是,如果电容太大,整个网络将不会在采样时刻之间完全稳定下来。

在某些情况下,差分输入信号不可用。

然后缓冲电路必须执行从单端缓冲电路获得差分信号的附加功能。

基本缓冲电路用于驱动LTC2387-18的基本缓冲电路如下图1所示。

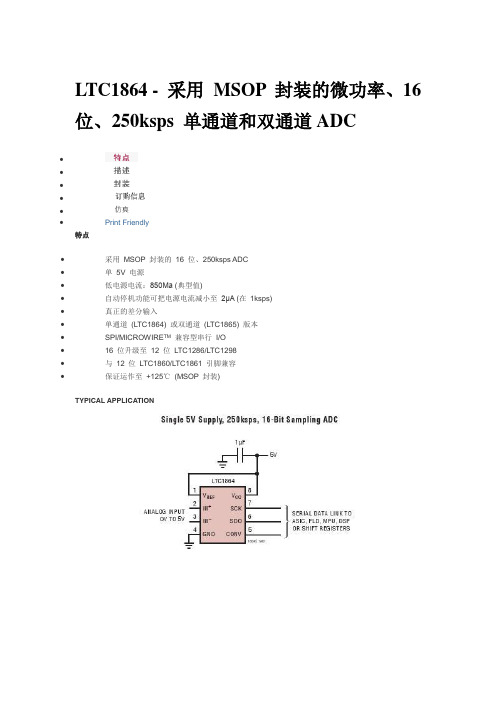

LTC1864

LTC1864 - 采用MSOP 封装的微功率、16 位、250ksps 单通道和双通道ADC••••••Print Friendly特点•采用MSOP 封装的16 位、250ksps ADC•单5V 电源•低电源电流:850Μa (典型值)•自动停机功能可把电源电流减小至2μA (在1ksps)•真正的差分输入•单通道(LTC1864) 或双通道(LTC1865) 版本•SPI/MICROWIRE TM兼容型串行I/O•16 位升级至12 位LTC1286/LTC1298•与12 位LTC1860/LTC1861 引脚兼容•保证运作至+125℃(MSOP 封装)TYPICAL APPLICATIONBACK TO TOP描述LTC®1864/LTC1865 是采用MSOP 和SO-8 封装的16 位A/D 转换器,采用单5V工作电源。

在250ksps 采样速率条件下,电源电流仅为850μA。

在较低的速度下,电源电流将减小,原因是LTC1864/LTC1865 在转换操作之间自动断电。

这些16 位开关电容器逐次逼近型ADC 包括采样及保持电路。

LTC1864 具有一个差分模拟输入和一个可调基准引脚。

LTC1865 提供了一个可利用软件来选择的双通道MUX 和一个可调基准引脚(在MSOP 封装版本上)。

三线式串行I/O、小外形MSOP 或SO-8 封装、以及极高的采样速率与功率之比使得这些ADC 非常适合于紧凑、低功率、高速系统。

这些ADC 可在比例式应用中使用,或与外部基准一起使用。

高阻抗模拟输入以及可在缩减的电压范围内(低至1V 全标度) 运作的能力使得它们在许多应用中可与信号源直接相连,从而免除了增设外部增益级的需要。

BACK TO TOP封装SO-8, MSOP-8BACK TO TOP订购信息•以PBF 结尾的器件型号表示这些是无铅型器件。

如需了解有关含铅涂层器件的信息,请与凌力尔特公司联系。

IRS2183中文资料