DSP-3DSP存储器配置及外设

DSP课后习题答案

对数据和函数的存储类别可分为:自动的(auto)、静态的(static)、寄存器的(register)、外部的(extern)。

非线性运算的方法:级数展开法、查表法、混合法DSP实现的一般方法:(1)、在通用的计算机上用软件实现。

(2)、在通用的计算机系统上加上专用的加速处理机实现(3)、在通用的单片机上实现。

(4)、在通用的可编程DSP芯片实现(5)、在专用的DSP芯片实现、(2)简述DSP应用系统的典型构成和特点答:DSP系统的典型结构其工作过程①对输入信号进行带限滤波和抽样;②进行A/D变换,将信号变换成数字比特流;③根据系统要求,DSP芯片对输入信号按照特定算法进行处理;④D/A转换,将处理后的数字样值转换为模拟信号;⑤平滑滤波,得到连续的模拟信号波形特点:接口方便编程方便稳定性好精度高可重复性好集成方便(3)简述DSP应用系统的一般设计过程DSP系统的设计流程:1. 定义系统性能指标 2. 采用高级语言进行性能模拟3. 设计实时DSP应用系统4. 借助开发工具进行软硬件调试 5. 系统集成与独立系统运行设计流程图:TMS320系列DSP芯片的特点:1.采用哈佛结构实现内部总线;2.采用流水线操作实现指令操作;3.乘法采用专用的硬件乘法器实现;4.具有高效的DSP指令哈佛结构的特点:将程序和数据存储在不同的存储空间流水线的特点:采用流水线操作,处理器可以并行处理多条指令,提高CPU工作效率DSP芯片的运算速度指标:指令周期 MAC时间 FFT执行时间 MIPS:每秒执行百万条指令 MOPS:每秒执行百万条操作 MFLOPS:每秒执行百万条浮点操作 BOPS:每秒执行十亿次操作(8)设计DSP应用系统时,如何选择合适的DSP芯片答:DSP芯片的选择要根据实际系统的需要来选择DSP芯片,已达到系统最优化的设计。

所以一般选择DSP芯片要考虑以下因素:芯片运行速度、DSP芯片的价格、DSP芯片的硬件资源、DSP芯片的运算精度、DSP芯片的开发工具、DSP芯片的功耗等因素。

存储器与通用IO端口

3.2 外部扩展接口 XINTF

▲ Zone7:Zone7是独立的地址空间,复位时,XMP/MC引脚为高电平,Zone7空间映射到0x3FC000。复位后,通过改变寄存器XINTCNF2中的MP/MC控制位,使能或屏蔽Zone7空间。如果XMP/面引脚为低电平,则Zone7不能映射到0x3FC000存储空间,而片上的ROM将映射到该存储空间。 Zone7的映射与MC/MC有关,而Zone0,Zonel,Zonc2,Zone6总是有效的存储空间,与XMP/MC状态无关。 如果用户需要建立自己的引导程序,存放在外部空间,可以使用Zone7空间进行程序的引导。引导成功后,通过软件使能内部的ROM,以便可以访问存放在ROM中的数学表。BootROM映射到Zone7空间时,Zone7空间的存储器仍然可以访问。这是因为Zone7和Zone6空间公用一个片选信号XZCS6ANDCS7。访问外部Zone7空间的地址范围是0x7C000~0x7FFFF,Zone6也使用这个地址空间。Zone7空间的使用只影响Zone6的高16K地址空间,

▲ 片内存储器操作的优点:速度快、价格低、功耗小。 ▲ 外部存储器操作的优点:可以访问更大的地址空间。

3.1 存储器

第3章 存储器与通用I/O口

第3章 存储器与通用I/O口

TMS320F2812所有存储空间采用统一寻址: ▲ 低64KB地址存储器——相当于F24x/F240x处理器的数据存储空间, 高 64KB地址存储器——相当于F24x/F240x处理器的程序存储空间,与 F24x/F240x兼容的代码只能定位在高64KB地址的存储空间运行。 ▲ XMP/MC模式为低时——顶部的32KBFlash和H0 SARAM模块可以用 来运行24x/240x兼容的代码; XMP/MC模式为高时——F2812的代码则从外部存储器接口的XINTF Zone 7空间开始执行

DSP系统设计

INT3 有 ? 效 否

有 并 效 行 自 ? 举 否

是 传 数 输 据

是 装 代 载 码 A

A

初 化 行 始 串 口 拉 XF 低

I/O 自 举 准 行 自 标 串 口 举

McB P1 S ? 否 是 有 效 数 ? 据 否 传 输 数 据 是 是 否 否 B IO 低 ? 是 有 效 数 ? 据 传 输 数 据

W =0x--A ? A 是 8位 式 模

否

-1个 以 读 取R 字 初 始 寄 器 化 存 。 8位 式 , 个 模 下 每 字 按 节 取 要 字 读 两 。 次 读 起 地 的 取 始 址 X PC 读 起 地 的 取 始 址 PC

读 段 大 取 的 小R 是

R =0? 否 读 段 标 址 取 目 地 读 段 内 并 取 的 容 放 到 标 址 置 目 地

标准串行自举 标准串行口方式McBSP1(8位模式)

B IN R T1=1 否

D R R =0x08? 是 读 一 节 下 字

检 M SP0 测 cB 自 举

D R R =0xA ? A 是 8位 式 模 读4 个 元 哑 传 代 输 码

否

标准串行自举(续) 标准串行口方式McBSP0(16位模式)

复位周期TRP

TRP = 3.125 × CRP

看门狗周期TWP

TWP = 25 × CWP

带手动复位和电压监控 TPS3808 主要特性:

复位延迟时间可设(1.25ms~10s); 小尺寸SOT23;

上电顺序连接

带手动复位和电压监控(TPS3808)

复位过程时序(tD电容预设)

带手动复位和电压监控(TPS3808)

跳 到 始 址 转 起 地 开 运 始 行

DSP原理及应用课后习题答案

简述DSP芯片的主要特点哈佛结构----将程序和数据存储在不同的存储空间中,即程序存储器和数据存储器是两个相互独立的存储器,每个存储器独立编址,独立访问。

多总线结构---保证在一个机器周期内可以多次访问程序存储空间和数据存储空间。

指令系统的流水线操作--减少指令执行时间,增强处理器的处理能力。

取址,译码,取操作和执行四个阶段。

专用的硬件乘法器--使乘法累加运算能在单个周期内完成。

特殊的DSP指令、快速的指令周期、硬件配置强。

详细描述冯诺依曼结构和哈佛结构,并比较不同?冯诺依曼结构--数据和程序共用总线和存储空间,在某一时刻,只能读写程序或者读写数据。

将指令、数据、地址存储在同一个存储器统一编址,依靠指令计数器提供的地址来区分是指令‘数据还是地址,取指令和取操作数都访问同一存储器,数据吞吐率低。

哈佛结构----将程序和数据存储在不同的存储空间中,即程序存储器和数据存储器是两个相互独立的存储器,每个存储器独立编址,独立访问。

改进的还允许在程序存储空间和数据存储空间之间相互传送数据。

DSP系统的设计过程?确定DSP系统设计的性能指标;进行算法优化与模拟;选择DSP芯片和外围芯片;进行硬件电路的设计;进行软件设计;进行软硬件综合调试。

请描述TMS320C54x的总线结构?C54X采用先进的哈佛结构并具有八组总线, 其独立的程序总线和数据总线允许同时读取指令和操作数,实现高度的并行操作。

程序总线PB传送从程序存储器来的指令代码和立即数。

3组数据总线连接各种元器件。

CB和DB总线传送从数据存储器读出的操作数,EB总线传送写入到存储器中的数据。

(1分)4组地址总线PAB\CAB\DAB\EAB传送执行指令所需的地址。

TMS320C54x片内存储器一般包括哪些种类?如何配置片内存储器?C54X片内存储器一般包括两种类型:ROM(只读存储器),RAM(随机访问存储器)。

RAM又可分为双访问DARAM和单访问SARAM。

DSP原理与应用技术-考试知识点总结

DSP原理与应用技术-考试知识点总结第一章1、DSP系统的组成:由控制处理器、DSPs、输入/输出接口、存储器、数据传输网络构成。

P2图1-1-12、TMS320系列DSPs芯片的基本特点:XXX结构、流水线操作、专用的硬件乘法器、特殊的DSP指令、快速的指令周期。

3、XXX结构:是一种将程序指令储存和数据储存分开的储存器结构。

特点:并行结构体系,是将程序和数据存储在不同的存储空间中,即程序存储器和数据存储器是两个相互独立的存储器,每个存储器独立编址,独立访问。

系统中设置了程序和数据两条总线,使数据吞吐率提高一倍。

4、TMS320系列在XXX结构之上DSPs芯片的改进:(1)允许数据存放在程序存储器中,并被算数运算指令直接使用,增强芯片灵活性(2)指令储存在高速缓冲器中,执行指令时,不需要再从存储器中读取指令,节约了一个指令周期的时间。

5、XXX结构:将指令、数据、地址存储在同一存储器中,统一编址,依靠指令计数器提供的地址来区分是指令、数据还是地址,取指令和去数据都访问同一存储器,数据吞吐率低。

6、流水线操作:TMS320F2812采用8级流水线,处理器可以并行处理2-8条指令,每条指令处于流水线的不同阶段。

解释:在4级流水线操作中。

取指令、指令译码、读操作数、执行操作可独立地处理,执行完全重叠。

在每个指令周期内,4条不同的指令都处于激活状态,每条指令处于不同的操作阶段。

7、定点DSPs芯片:定点格式工作的DSPs芯片。

浮点DSPs芯片:浮点格式工作的DSPs芯片。

(定点DSPs可以浮点运算,但是要用软件。

浮点DSPs 用硬件就可以)8、DSPs芯片的运算速度衡量标准:指令周期(执行一条指令所需时间)、MAC时间(一次乘法和加法的时间)、FFT执行时间(傅立叶运算时间)、MIPS(每秒执行百万条指令)、MOPS(每秒执行百万次操作)、MFLOPS (每秒执行百万次浮点操作)、BOPS(每秒十亿次操作)。

TMS320C54X中文

第3页

TMS320C54x DSP CPU 和 外 设

l 256 字 的 正 弦 表 l 中断矢量表 2.2 扩 展 程 序 存 储 器 ‘548 ’549 ’5410 ’5420 采 用 分 页 扩 展 的 方 式 使 可 寻 址 程 序 空 间达到 8192K 字 这一功能的实现有赖于

AG

累 加 器 A 保 护 位 39 32 比特

B

BL

累 加 器 B 低 字 15 0 比特

C

BH

累 加 器 B 高 字 31 16 比 特

D

BG

累 加 器 B 保 护 位 39 32 比特

E

T

乘法寄存器

F

TRN

传送寄存器

10-17

AR0-AR7

辅助寄存器 ARn n 0 7

18

SP

堆栈指针

19

BK

循环缓存区大小寄存器

1A

BRC

块重复计数器

1B

RSA

块重复开始地址

1C

REA

块重复结束地址

1D

PMST

状态寄存器

第4页

TMS320C54x DSP CPU 和 外 设

1E

XPC

PC 扩 展 寄 存 器

1E 1F

保留

20

BDRR0

程序空间 当地址落在这些区域内 自动对这些区域进行访问 当地

址落在这些区域以外 自动产生对外部存储器的访问

2.1 片内 ROM

片内 ROM 4K 16K 24K 28K 或 48K 字 l 引导程序 可以从串口 外部存储器 l 256 字 的 率扩展表 l 256 字 的 A 率扩展表

DSP原理及应用第二章DSP的硬件结构总结

第2 章DSP 的硬件结构DSP的硬件结构:DSP 与标准微处理器有许多共同的地方,都是由CPU、存储器、总线、外设、接口、时钟组成。

从广义上讲,可以说DSP是一种CPU。

但DSP 和一般的CPU 又有不同,DSP 有自己的一些独特的特点,比如采用哈佛结构、流水线操作、独立的硬件乘法器、独立的DMA 总线和控制器等。

Von Neuman结构与Harvard 结构:Harvard 结构:程序与数据存储空间分开,各有独立的地址总线和数据总线,取指和读数可以同时进行,从而提高速度,目前的水平已达到90 亿次浮点运算/秒( 9000MFLOPS)。

MIPS--Million Instruction Per Second算,大量重复乘法和累加。

通用计算机的乘法用软件实现,用若干个机器周期。

DSP 有硬件乘法器,用MAC 指令(取数、乘法、累加)在单周期内完成独立的DMA 总线和控制器:有一组或多组独立的DMA 总线,与CPU 的程序、数据总线并行工作,数据的传递和处理可以独立进行,DMA 内部总线与系统总线完全分开,避开了总线使用上的瓶颈。

在不影响CPU 工作的条件下,DMA 速度已达800Mbyte/s。

CPU:通用微处理器的CPU由ALU 和CU组成,其算术运算和逻辑运算通过软件来实现,如加法需要10 个机器周期,乘法是一系列的移位和加法,需要数十个机器周期。

DSP 的CPU设置硬件乘法器,可以在单周期内完成乘法和累加.移位:通用微处理器的移位,每调用一次移位指令移动1-bitDSP 可以在一个机器周期内左移或右移多个bit,可以用来对数字定标,使之放大或缩小,以保证精度和防止溢出;还可以用来作定点数和浮点数之间的转换.溢出:通用CPU 中,溢出发生后,设置溢出标志,不带符号位时回绕,带符号位时反相,带来很大的误差DSP 把移位输出的最高位(MSB )存放在一个位检测状态寄存器中,检测到MSB=1 时,就通知下一次会发生溢出,可以采取措施防止.数据地址发生器(DAG ):在通用CPU 中,数据地址的产生和数据的处理都由ALU 来完成在DSP中,设置了专门的数据地址发生器(实际上是专门的ALU ),来产生所需要的数据地址,节省公共ALU 的时间.外设(peripherals):时钟发生器(振荡器与PLL )定时器(Timer)软件可编程等待状态发生器通用I/O同步串口(SSP)与异步串口(ASP)JTAG 扫描逻辑电路(IEEE 1149.1标准便于对DSP 作片上的在线仿真和多DSP条件下的调试' C54的x 内部结构:中央处理器CPU 、内部总线控制、特殊功能寄存器、数据存储器RAM 、程序存储器ROM、I/O 功能扩展接口、串行口、、主机通信接口HPI、定时系统、中断系统。

第7章TMS320C54XDSP片内外设10

辅助寄存存器0 辅助寄存存器1 辅助寄存存器2 辅助寄存存器3 辅助寄存存器4 辅助寄存存器5 辅助寄存存器6 辅助寄存存器7 堆栈指针寄存器 循环缓冲大小寄存器 块重复计数寄存器 块重复首址寄存器 块重复尾址寄存器 处理器方式状态寄存器 扩展程序计数寄存器 保留

6

外设映射寄存器 DRR20 DRR10 DXR20 DXR10 TIM0 PRD0 TCR0 32 33 34 35 36 37 38 20 21 22 23 24 25 26 McBSP0缓冲串口数据接收寄存器2 McBSP0缓冲串口数据接收寄存器1 McBSP0缓冲串口数据发送寄存器2 McBSP0缓冲串口数据发送寄存器1 定时器0减计数寄存器 定时器0周期寄存器 定时器0控制寄存器

能被辅助寄存器算术单元ARAU修改,其主要功能是产生16位的数据 空间地址,也能用来作为通用寄存器和计数器。

l 循环缓冲寄存器(BK) 循 环缓冲寄存器(BK)被用来通过ARAU在循环寻址中确定数据循

环区的大小。

l 块循环寄存器(BRC、RSA、REA) 块循环寄存器(BRC)在块循环时确定一段代码所需循环的次数;

PLL MUL PLL 乘 数

11

PLL DIV

PLL 除 数

10-3

PLL COUNT

PLL 计 数 器

2

PLL ON/OFF

通 断 位 PLL /

1

PLL NDIV

方 式 选 择 PLL

0

PLL STATUS

状 态 位 PLL

例:

STM

#9007H, CLKMD

13

字段位

15—12

字段名称

PLL MUL

2PLL ON/OFF源自1PLL NDIV

(整理)DSP存储空间的分配问题.

在DSP的开发过程中,开发者难免会遇到DSP芯片内部存储器和片外扩展存储器的配置等问题。

本文以TMS320C54x系列DSP为例,讨论DSP存储空间的分配问题。

存储器空间'C54x系列DSP存储器分为三个独立选择的空间—程序、数据和I/O,其中程序存储器存放待执行的指令和执行中所用的系数(常数),可使用片内或片外的RAM、ROM或EPROM等来构成;数据存储器存放指令执行中产生的数据,可使用片内或片外的RAM和ROM来构成。

I/O存储器存放与映象外围接口相关的数据,也可以作为附加的数据存储空间使用。

这三个空间的寻址范围取决于DSP芯片地址线数目。

例如,'C54x系列 DSP 从'C548开始,芯片有23根地址线,具有8M字节存储空间寻址能力。

'C54x通过包含在处理器工作方式的状态寄存器(PMST)中的3个状态位,选择片内存储器作为程序空间或数据空间。

这3个状态位是:(1)MP/MC位。

MP/MC=0,则片内ROM安排到程序空间;MP/MC=1,则片内ROM不安排到程序空间。

(2)OVLY位。

OVLY=1,则片内RAM安排到程序和数据空间;OVLY=0,则片内RAM只安排到数据存储空间。

(3)DROM位。

当DROM=1,则部分片内ROM安排到数据空间;DROM=0,则片内ROM不安排到数据空间。

程序设计者可根据不同的需求,相应的配置这3个位,使系统的存储空间满足应用要求。

同时,为了扩展'C54x系列DSP的寻址空间,还增加了一个额外的存储器映像寄存器—程序计数器扩展寄存器XPC,以及6条寻址扩展程序空间的指令。

以TMS320C5410为例,它的程序空间分成128页面,每页64K字。

该64K字程序空间分为两部分:一部分是公共的32K字,另一部分是各自独立的32K字。

公共存储器为所有页面共享,每个页面独立的32K字存储器只能按指定的页面号寻址,这个页面号由XPC寄存器设定。

DSP简介

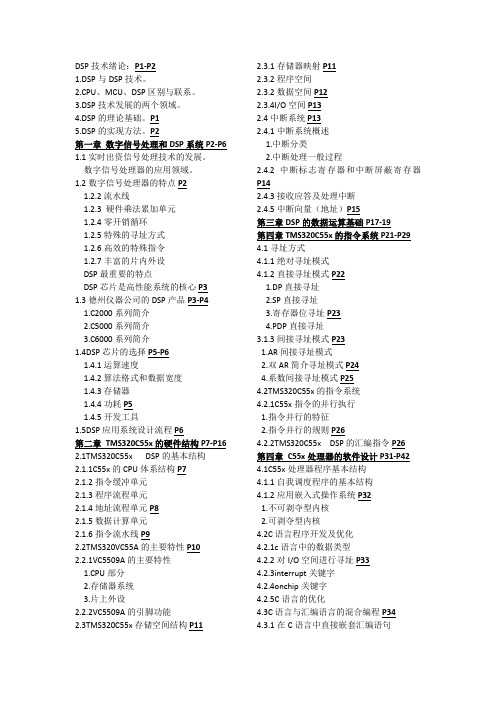

DSP技术绪论:P1-P21.DSP与DSP技术。

2.CPU、MCU、DSP区别与联系。

3.DSP技术发展的两个领域。

4.DSP的理论基础。

P15.DSP的实现方法。

P2第一章数字信号处理和DSP系统P2-P6 1.1实时出资信号处理技术的发展。

数字信号处理器的应用领域。

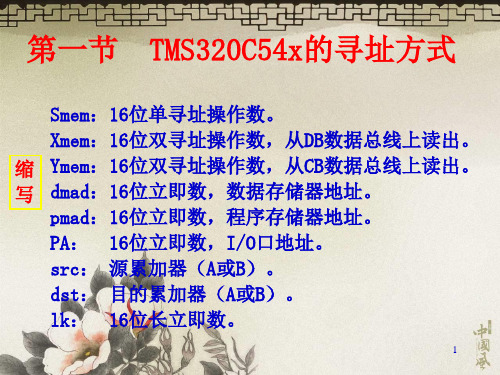

1.2数字信号处理器的特点P21.2.2流水线1.2.3 硬件乘法累加单元1.2.4零开销循环1.2.5特殊的寻址方式1.2.6高效的特殊指令1.2.7丰富的片内外设DSP最重要的特点DSP芯片是高性能系统的核心P31.3德州仪器公司的DSP产品P3-P41.C2000系列简介2.C5000系列简介3.C6000系列简介1.4DSP芯片的选择P5-P61.4.1运算速度1.4.2算法格式和数据宽度1.4.3存储器1.4.4功耗P51.4.5开发工具1.5DSP应用系统设计流程P6第二章TMS320C55x的硬件结构P7-P16 2.1TMS320C55x DSP的基本结构2.1.1C55x的CPU体系结构P72.1.2指令缓冲单元2.1.3程序流程单元2.1.4地址流程单元P82.1.5数据计算单元2.1.6指令流水线P92.2TMS320VC55A的主要特性P102.2.1VC5509A的主要特性1.CPU部分2.存储器系统3.片上外设2.2.2VC5509A的引脚功能2.3TMS320C55x存储空间结构P11 2.3.1存储器映射P112.3.2程序空间2.3.2数据空间P122.3.4I/O空间P132.4中断系统P132.4.1中断系统概述1.中断分类2.中断处理一般过程2.4.2中断标志寄存器和中断屏蔽寄存器P142.4.3接收应答及处理中断2.4.5中断向量(地址)P15第三章DSP的数据运算基础P17-19第四章TMS320C55x的指令系统P21-P29 4.1寻址方式4.1.1绝对寻址模式4.1.2直接寻址模式P221.DP直接寻址2.SP直接寻址3.寄存器位寻址P234.PDP直接寻址3.1.3间接寻址模式P231.AR间接寻址模式2.双AR简介寻址模式P244.系数间接寻址模式P254.2TMS320C55x的指令系统4.2.1C55x指令的并行执行1.指令并行的特征2.指令并行的规则P264.2.2TMS320C55x DSP的汇编指令P26第四章C55x处理器的软件设计P31-P42 4.1C55x处理器程序基本结构4.1.1自我调度程序的基本结构4.1.2应用嵌入式操作系统P321.不可剥夺型内核2.可剥夺型内核4.2C语言程序开发及优化4.2.1c语言中的数据类型4.2.2对I/O空间进行寻址P334.2.3interrupt关键字4.2.4onchip关键字4.2.5C语言的优化4.3C语言与汇编语言的混合编程P344.3.1在C语言中直接嵌套汇编语句4.3.2C语言调用汇编模块的接口1.C/C++中的寄存器规则2.函数调用规则P353.被调用函数的响应4.C/C++与汇编语言的接口P364.4公共目标文件格式——COFF4.4.1COFF文件中的段P374.4通用目标文件格式P374.4.1C/C++和汇编语言中段的分配4.4.2寄存器模式设置P381.小存储器模式2.大存储器模式3.C/C++系统堆栈4.动态内存分配P395.结构的对齐4.4.3 链接命令文件4.5汇编源程序的编辑、汇编和链接过程P39 4.5.1编辑4.5.2汇编器1.汇编器的功能2.汇编器的调用3.列表文件P404.5.3连接器1.连接器的功能2.连接器的调用3.多个文件的链接P40-P414.6C55x处理器的数字信号处理库和图像、视频处理库P414.6.1C55x的数字信号处理库4.6.2C55x的图像、视频处理库P42第五章TMS32C55Xde 片内集成外设开发及测试P43-P735.1C55x片内外设与芯片支持库简介1.时钟与定时器2.外部设备链接接口3.信号采集4.通信接口5.其他外设5.2时钟发生器P445.2.1时钟模式寄存器5.2.2工作模式P451.旁路模式2.锁定模式5.2.3CLKOUT输出5.2.4使用方法1.省点2.DSP复位3.失锁5.2.5使用方法及实例5.2.6时钟发生器的调试5.3通用定时器P465.3.1结构框图5.3.2工作原理5.3.3使用方法P471.初始化定时器2.停止/启动定时器3.DSP复位5.3.4通用定时器的应用5.3.4通用定时器的调试P485.4外部存储器接口5.4.1功能与作用5.4.2外部寄存器接口硬件连接与配置P491.异步存储器接口2.同步突发静态存储器P513.同步突发动态存储器P525.4.3外部寄存器接口的软件设置P545.5主机接口(EHPI)P555.5.1EHPI接口的非复用连接方式5.5.2EHPI接口的复用连接方式P565.5.3EHPI口的寄存器5.6多通道缓冲串口McBSP P575.6.1概述5.6.2组成框图5.6.3采样率发生器1.采样率发生器的输出时钟和桢同步信号P582.同步5.6.4多通道选择1.接收多通道选择P592.发送多通道选择5.6.5异常处理1.接收数据溢出2.同步桢同步信号错误3.发送数据重写4.发送寄存器空P605.发送帧同步脉冲错误5.6.6MCBSP寄存器1.收发通道寄存器2.时钟和帧同步寄存器(1)串口控制寄存器(2)收发控制寄存器P61(3)采样率发生寄存器(4)引脚控制寄存器3.多通道选择寄存器P62(1)通道控制寄存器(2)收发通道使能寄存器5.6.7多通道缓冲串口的应用5.6.8MCBSP串口的测试P641.DSP内部链接测试2.外部设备连接测试5.7通道输入/输出端口GPIO P655.7.1GPIO概述5.7.2上电模式设定5.7.3驱动程序开发P665.7.4通用输入/输出GPIO的测试1.输入口测试2.输出口测试5.8DMA控制器5.8.1概述5.8.2通道和端口P675.8.3HPI的配置5.8.4DMA传输配置P681.数据传输单位2.数据打包3.端口4.数据源和目的地址5.8.5DMA控制器的寄存器1.DMA全局控制寄存器P692.DMA通道控制寄存器3.源和目的参数寄存器4.起始地址寄存器P50【我标错了实际应该是P70】5.单元索引寄存器和桢索引寄存器5.8.6使用方法及实例5.9I²C总线P515.9.1I²C总线简介1. I²C总线数据传输P522.仲裁3.时钟产生和同步P534. I²C模块的终端和DMA同步事件5. I²C模块的禁止与使能5.9.2I²C寄存器5.9.3 I²C模块的使用5.10通用串行总线(USB)P545.10.1通用串行总线简介5.11.2USB的DMA控制器P551.主机-DMA模式P56B模块的中断5.10.3USB模块的寄存器1.DMA内容寄存器P572.通用端点描述寄存器3.控制端点描述寄存器P584.中断寄存器P595.11.4USB模块的应用5.11模块转换器(ADC)P605.11.1模数转换器结构和时序5.11.2模数转换器的寄存器P615.11.3使用方法及实例P625.12实时时钟(RTC)5.12.1基本结构P635.12.2内部寄存器5.12.3应用P645.13看门狗定时器(Watchdog)P655.13.1工作方式5.13.2寄存器说明5.13.3应用P665.14一步串口(UART)P665.14.1基本结构1.异步串口发送部分P672.异步串口接收部分3.波特率产生器4.异步串口的中断申请与DMA事件的产生P685.FIFO工作模式6.供电和仿真P695.14.2异步串口寄存器1.接收缓冲寄存器(URRBR)P702.发送保持寄存器(URTHR)3.分频数锁存寄存器(URDLL和URDLM)4.中断使能寄存器(URIER)5.中断标志寄存器(URIIR)6.FIFO控制寄存器(URFCR)P717.线路控制寄存器(URLCR)8.循环模式控制寄存器(URMCR)P729.线路状态寄存器(URLSR)10.供电和仿真控制寄存器(URPECR)P735.14.3异步串口的应用P73第七章TMS320C55X硬件设计实例p75-P93 7.1DSP最小系统设计7.1.1C55x的电源设计7.1.2复位电路设计P767.1.3时钟电路设计P777.1.4JTAG接口电路设计7.1.5程序加载部分1.并行外部存储器(EMIF)加载P782.标准串口加载p793.串行外设接口(SPI)加载p804.EHPI口加载程序P817.2A/D与D/A设计P827.2.1串行多路A/D设计P837.2.2高速并行A/D设计P857.2.3并行D/A设计P867.3C55X在语音系统中的应用P877.4C55x在软件无线电中的应用P89第八章TMS320C55X软件设计实例P95-P1138.1卷积算法8.1.1卷积算法8.1.2卷积算法的MATLAB实现8.1.3卷积算法的DSP实现8.2有限冲击响应滤波器的特点和结构P97 8.2.1有限冲击响应滤波器的特点和结构8.2.2MATLAB设计8.2.3DSP实现P988.3无线冲击响应滤波器(IIR)的实现8.3.1无线冲击响应滤波器的结构8.3.2无线冲击响应滤波器的MATLAB设计P998.3.3DSP实现8.4快速傅里叶变换(FFT)P1018.4.1快速傅里叶变换(FFT)算法8.4.2DSP实现8.5语音信号编码解码(G.711)P1038.5.1语音信号编码解码原理1.G.711语音编码标准2.PCM编码3.A律压扩标准8.5.语音信号编码解码的DSP实现P104 8.6数字图像的锐化8.7Viterbi译码P106 CCS集成开发环境p115-P123 S集成开发环境简介1.1CCS安装及设置(1)CCS2.0系统的安装(2)系统配置(3)系统启动1.2CCS的窗口、菜单和工具条1)CCS的窗口2)CCS的菜单P1163)CCS的工具栏1.3CCS的工程管理1)典型工程文件记录的信息2)创建和管理工程1.4调试1.5通用扩展语音GEL p117S应用举例S仿真P1204.DSP/BIOS简介P123。

DSP原理及应用第三章

15~8 7 6~0

操作码

I=0

dmad

堆栈指针SP

16位堆栈指针SP

SP+dmad

16位数据 存储器地址 16位SP+dmad 高 9位

dmad

低 7位

15

DP地址的范围是从0~511(29-1),将存储器分成 512页。 7 位 dmad 范围是从 0~127 ,每页有 128 个可以访 问的单元。 以DP为基准的直接寻址是由DP 值确定是 512 页中 的哪一页,由dmad确定是该页中的哪一个单元。 SP 可以指向存储器中的任意一个地址。 dmad 可 以指向当前页中具体的单元,从而允许访问存储器 任意基地址中的连续的128个单元

循环寻址的有效地址计算

循环缓冲区的参数主要包括:长度寄存器 (BK)、有效基地址(EFB)、尾地址(EOB)。 N>32, 则N=6。 例如:缓冲区长度 R=32 , 若 2 BK:定义了循环缓冲区的大小R。大小为R的循环缓冲 缓冲区开始的地址: xxxx xxxx xx00 0000 B 器其地址要始于最低 N位为零的地址。并且 R要满足下 缓冲区长度 N>R 装入循环缓冲长度寄存器BK中。 面的条件: 2R=32 EFB:循环缓冲器的有效基地址(EFB)就是用户选定 的辅助寄存器(ARx)的低N位置 0后所得到的值。 EOB:是通过用BK的低N位代替ARx的低N位得到。

LD

*(BUFFER),A

9

绝对寻址总结

16位地址表示形式: ① 地址符号,如:TABLE; ② 16位数值,如:89AB、1234。 特点:指令中包含一个固定的16位地址,能寻 址所有数据、程序和I/O存储空间,但 运行速度慢,需要较大的存储空间。 用途:用于对速度要求较低的场合。

DSP 第9讲 片上外设

§9.3.2 定时器操作—续

定时器中断的周期: TOUT周期=(TDDR+1)×(PRD+1) ×CLKOUT CLKOUT为CPU时钟周期, PRD为定时器周期值, TDDR为定时器分频系数。 当复位时,PRD=FFFFH,TIM=FFFFH, TDDR=0H,TSS=0 (可见复位时,定时器已经开始工作)

(4)设置PLLCOUNT位为所期望的锁定时间。

§9.4.3 软件可配置的PLL—续

注:在除以2模式和除以4模式之间的转换是不可能的。为了 转换这两种模式,时钟发生器必须首先设置为PLL模式, 然后设置回期望的除数配置的DIV模式。 例:将时钟模式从PLL×(X)转换为PLL× 1: STM #0b,CLKMD ;转换为DIV模式 TstStatu: LDM CLKMD,A AND #1b,A ;查询PLLSTATUS位 BC TstStatu,ANEQ STM #0000 0 01111101 111b,CLKMD ;转换为PLL×1模式

Soft

0

位10

Free

0

位9~6 位5

PSC

-

TRB

位4

TSS

0

位3~0

TDDR

0000

§9.3.2 定时器操作

主定时器模块:由PRD和TIM组成 预定标器模块:由TCR的TDDR和PSC位组成 定时器由CPU提供时钟 系统复位

定时器重载 定时器分频系数(4bit) 预定标计数器(4bit) 0:启动 1:停止 定时器中断送到 CPU 定时器输出引 脚(84)

VDD

晶体振荡器

NC GND

§9.4.2 硬件可配置的PLL

硬件配置的PLL:就是通过配置C54x的3个引脚CLKMD1、 CLKMD2和CLKMD3的状态,来选定时钟方式。

DSP技术及应用习题答案

《DSP技术及应用》习题答案第1章绪论1.1 DSP的概念是什么?本书说指的DSP是什么?答:DSP有两个概念。

一是数字信号处理(Digital Signal Processing),指以数字形式对信号进行采集、变换、滤波、估值、增强、压缩、识别等处理;二是数字信号处理器(Digital Signal Processor),指是一种特别适合于进行数字信号处理运算的微处理器,其主要应用是实时快速地实现各种数字信号处理算法。

本书中的DSP主要指后者,讲述数字信号处理器的应用。

1.2 什么是哈佛结构和冯•诺伊曼结构?它们有什么区别?答:(1)冯·诺伊曼(Von Neuman)结构该结构采用单存储空间,即程序指令和数据共用一个存储空间,使用单一的地址和数据总线,取指令和取操作数都是通过一条总线分时进行。

当进行高速运算时,不但不能同时进行取指令和取操作数,而且还会造成数据传输通道的瓶颈现象,其工作速度较慢。

(2)哈佛(Harvard)结构该结构采用双存储空间,程序存储器和数据存储器分开,有各自独立的程序总线和数据总线,可独立编址和独立访问,可对程序和数据进行独立传输,使取指令操作、指令执行操作、数据吞吐并行完成,大大地提高了数据处理能力和指令的执行速度,非常适合于实时的数字信号处理。

1.3 已知一个16进制数3000H,若该数分别用Q0、Q5、Q15表示,试计算该数的大小。

答:3000H=12288。

若用Q0表示,则该数就是12288;若用Q5表示,则该数就是12288*2-5=384;若用Q15表示,则该数就是12288*2-15=0.3751.4 若某一个变量用Q10表示,试计算该变量所能表示的数值范围和精度。

答:Q10能表示的数值范围是-32~31.9990234,其精度为2-101.5 若x=0.4567,试分别用Q15、Q14、Q5将该数转换为定点数。

答:Q15:x*215=int(0.4567*32768)=14965;Q14:x*214=int(0.4567*16384)=7482;Q5:x*25=int(0.4567*32)=14。

DSP芯片结构和CPU外围电路详解

第二章 DSP芯片结构和CPU外围电路

2.3通用定时器

一、组成和框图 ▪ C5509 DSP片内有两个定时器:Timer0,Timer1; ▪ 具有定时或计数功能。计数器在每个时钟周期减1,当减到0就 产生一个输出信号。该输出信号可用于中断CPU或触发DMA传输 (称为定时器事件)。 ▪ 定时器由时钟、控制寄存器、计数器和定时器事件等部分构成。

第二章 DSP芯片结构和CPU外围电路

四、定时器控制寄存器TCR

▪ IDLE_EN:省电控制使能位,0:禁止省电模式,1:允许省电模式

▪ INT/EXT:时钟源从内部切换到外部的指示标志,当时钟源从内部切换到 外部要检测此位来决定是否准备好使用外部时钟。

0:定时器没准备好使用IM:定时器错误标志,0:正常,1:错误

支持的接口有:

▪ 包括异步 SRAM、ROM、FLASH(闪速存储器) 、EPROM等,EMIF能 够提供可配置的定时参数,提供高度灵活的存储器时序。每个接口都 可以支持

▪ 程序代码访问 ▪ 32bit数据访问、16bit数据访问、8bit数据访问。

第二章 DSP芯片结构和CPU外围电路

2.1.2 TMS320C55x CPU

CPU有4个功能单元:指令缓冲单元(I单元),程序流程单元(P单元) ,地址数 据流程单元(A单元)和数据计算单元(D单元)

CPU结构示意图

第二章 DSP芯片结构和CPU外围电路

▪ A单元16位ALU的功能

能接收I单元数据,又能够和存储器、I/O空间、A单元寄存器、 D单元寄存器和P单元寄存器进行数据交换,完成算术、逻辑、 位操作、移位、测试、旋转等操作。A单元包括的寄存器有下 列4种类型:

1)数据页寄存器(Data Page Register):DPH、DP、(接口数据 页)PDP

DSP的存储空间映射、配置

.sector “vectors” 表 明 中 断 向 量表代码位于vectors段 必 须 把 vectors 段放置在片内 RAM中,用以高速响应中断 在 DSP 程 序 初 始 化 时 , 若 将 IPTR=0x001,则中断向量表 初始地址为0x80 在 CMD 文件中,在 PAGE0 中 配置一块地址从 0x80 开始 , 共128 Words,并将vectors段 配置到该区域 设 计 OVLY=1 , 将 DARAM0~3 块映射到程序空 间,实现中断向量表在 DARAM中运行

TMS320VC5416 DSP的内部存储资源

64K Words的DARAM (双访问RAM) 每8K一块,被分成8块,由低地址开始记作DARAM0 -DARAM7 在同一块内一个指令周期支持两个操作 64K Words的SARAM (单访问RAM) 每8K一块,被分成8块,由低地址开始记作SARAM0- SARAM7 在同一块内一个指令周期仅支持一个操作,但支持一个指 令周期同时对不同的块完成两个操作 16K Words的ROM 掩模ROM,只能读不能写

TMS320VC5416 DSP的存储空间配置-CMD文件结构

TMS320VC5416 DSP的存储空间分配和配置综合

OVLY=1 DROM=1

以TMS320VC5416 的中断设计为例看存储空间映射和配置 1. 中断向量地址计算方法

(1)取PMST寄存器的IPTR的值(中断向量指针,9位) (2)查DSP的中断表得到中断向量序号(5位) (3)将中断向量序号左移2位 (4)将IPTR值左移7位与(3)相加,得到中断向量地址

INT0序号为16 左移两位后为 40H

1. 硬件复位 值为0x1FF。 2. 用户可以 软件设置 3. 软件复位 该值不变化

DSP存储空间的分配问题

在DSP的开发过程中,开发者难免会遇到DSP芯片内部存储器和片外扩展存储器的配置等问题。

本文以TMS320C54x系列DSP为例,讨论DSP存储空间的分配问题。

存储器空间'C54x系列DSP存储器分为三个独立选择的空间—程序、数据和I/O,其中程序存储器存放待执行的指令和执行中所用的系数(常数),可使用片内或片外的RAM、ROM或EPROM等来构成;数据存储器存放指令执行中产生的数据,可使用片内或片外的RAM和ROM来构成。

I/O存储器存放与映象外围接口相关的数据,也可以作为附加的数据存储空间使用。

这三个空间的寻址范围取决于DSP芯片地址线数目。

例如,'C54x系列 DSP 从'C548开始,芯片有23根地址线,具有8M字节存储空间寻址能力。

'C54x通过包含在处理器工作方式的状态寄存器(PMST)中的3个状态位,选择片内存储器作为程序空间或数据空间。

这3个状态位是:(1)MP/MC位。

MP/MC=0,则片内ROM安排到程序空间;MP/MC=1,则片内ROM不安排到程序空间。

(2)OVLY位。

OVLY=1,则片内RAM安排到程序和数据空间;OVLY=0,则片内RAM只安排到数据存储空间。

(3)DROM位。

当DROM=1,则部分片内ROM安排到数据空间;DROM=0,则片内ROM不安排到数据空间。

程序设计者可根据不同的需求,相应的配置这3个位,使系统的存储空间满足应用要求。

同时,为了扩展'C54x系列DSP的寻址空间,还增加了一个额外的存储器映像寄存器—程序计数器扩展寄存器XPC,以及6条寻址扩展程序空间的指令。

以TMS320C5410为例,它的程序空间分成128页面,每页64K字。

该64K字程序空间分为两部分:一部分是公共的32K字,另一部分是各自独立的32K字。

公共存储器为所有页面共享,每个页面独立的32K字存储器只能按指定的页面号寻址,这个页面号由XPC寄存器设定。

实验1DSp;试验一

实验一DSP图像采集与传输一、实验目的通过该实验,掌握模拟图像经采集成为数字图像的方法,以及数字图像在该系统中的传输,掌握系统的资源及DSP系统各硬件资源的功能模块的作用。

1.了解PAL和NSTC视频格式。

2.掌握图像采集模块和视频解码器TVP5150A的使用3. 掌握图像显示模块和视频编码器SAA7121H的使用4. 掌握利用DM642进行图像采集与显示方法。

二、实验原理1. 数字图像经过数字化转换并可以用数字表示、处理的图像由象素点组成。

其中横向的点数称为水平分辨率,纵向的为垂直分辨率,一幅完整的图分为若干行,称为一帧图像。

每个象素根据量化精度不同其取值也不同,例如取三个色彩分量均为8位二进制数的RGB表示方法,用连续的三个8位二进制数表示一个彩色点,如(200,100,64)描述的点的红色分量为200,绿色分量100,蓝色分量64,其中每个分量的取值均为0~255表示从最暗到最亮256个等级。

静态图像可以通过连续播放产生动态效果,25帧/秒或30帧/秒的帧速可产生较平滑的动态显示效果。

2. 色彩空间色彩空间(ColorSpace),又称为色域空间,它表示的是一个图像所能够表现的色彩范围,其模型是描述使用一组值(通常使用三个、四个值或者颜色成分)表示颜色方法的抽象数学模型。

常用的色彩空间有两种,即RGB和YUV色彩空间。

其中RGB色彩空间通常为图像采集和显示设备采用,例如CCD、CMOS摄像头,CRT 监视器等。

因其色彩分量之间有较大的相关性,不适于做图像处理。

YCbCr是YUV色彩空间的使用最广泛的一种色彩编码,其中Y 表示亮度,Cb表示蓝色色差色差,Cr表示红色色差。

各色彩分量之间相关性小,适于进行处理操作,通常为计算机设备采用。

YCbCr采样格式有4:4:4(完全取样)、4:2:2(2:1水平采样,没有垂直下采样)、4:2:0( 2:1水平采样,2:1垂直下采样0、4:1:1( 4:1水平取样,没有垂直下采样)。

ch3 F28027的存储空间

扇区B(8K×16位)

扇区A(8K×16位)

当使用CSM模块该区域必须编程为 0x0000

引导至Flash的入口地址 128位的安全密码区

外设帧

外设帧是TMS320F28027的CPU定时器、Flash、中断向量、片内外设( 例 如 SCI 、 SPI 、 ADC 、 ePWM 、 eCAP 及 比 较 ) 等 寄 存 器 的 映 像 空 间 , TMS320F28027的外设帧包含3个外设空间,外设空间分类如下:

Flash & OTP 相关寄存器 FOTPWAIT OTP等待寄存器

3.4 程序的引导装载

上电或复位 芯片设置如下: PIE禁止(ENPIE=0)

VMAP=1 OBJMODE=0

AMODE=0 M0M1MAP=1

Boot ROM

从引导ROM地址0x3F FFC0处读取复位向量

跳转到InitBoot函数 启动引导流程

表3-10 引导模式选择

模式 GPIO37/TDO GPIO34/COMP2OUT

引导装载模式

3

1

2

1

1

0

0

0

EMU

x

1

0

模式获取

0

0

wait

1

0

SCI

0

0

并行I/O

x

1

仿真

1.仿真引导 2.独立引导

表3-14 独立引导模式

GPIO37 GPIO3 OTP KEY OTP BMODE

TDO

4

读0x3D 7BFE 读0x3D 7BFF

对PWL读取判断: 1.All zero: permanently secured

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

… … …

F FFFFH

0 FFFFH

1 FFFFH

XPC = 0

XPC = 1

XPC = 15

电气与信息工程学院

DSP技术及应用

程序存储空间的分页扩展

令:

• ① FB[D]——长跳转指令;

’C54x存储器及片内外 设

• 为了便于软件进行页切换,设置了6条影响XPC的专用指

• ② FBACC[D]——长跳转到累加器A或B所指定的位置;

第3讲 ’C54x存储器配置及 片内外设

电气与信息工程学院

DSP技术及应用

3.1 ’C54x的存储空间结构

’C54x存储器及片内外 设

’C54x共有192K字的存储空间,分成3个相互独立可 选择的存储空间: • 64K字(16位)的程序存储空间; • 64K字(16位)的数据存储空间; • 64K字(16位)的I/O空间。

2

① 有20或23条外部程序地址线,可寻址1M或8M存 储空间; ② 有1个额外的存储器映像寄存器—程序计数器扩 展寄存器XPC; ③ 有6条寻址扩展程序空间的指令,用于寻址扩展 程序空间。

电气与信息工程学院

DSP技术及应用

程序存储空间的分页扩展

’C54x存储器及片内外 设

’C5402共有20条外部程序地址总线,可寻址程序存储空间

OVLY=1: 0000H~007FH 0080H~3FFFH 4000H~FF7FH 2 FF80H~FFFFH OVLY=0:

0000H~FF7FH FF80H~FFFFH

保留 内部DARAM 外部存储器 中断矢量表

007FH 0080H 0080H

3FFFH

3FFFH 4000H 4000H

OVLY=1 内部SARAM OVLY=0 外部存储器 外部存储器 外部存储器 外部存储器

DROM=1 使用内部ROM F000H~FEFFH 内部ROM FF00H~FFFFH DROM=0 保留 不使用内部ROM

FEFFH FF00H

F000H~FEFFH

外部存储器

FFFFH

电气与信息工程学院

DSP技术及应用

数据存储空间

内部RAM前1K的配置:

0000H~001FH 存储器映像的CPU寄存器 0200H~005FH 存储器映像的外设寄存器 0060H~007FH 暂存器SPRAM(DP=0) DARAM(DP=1) 0080H~00FFH

DROM=1 外部存储器 内部ROM DROM=0 DROM=0 外部存储器

DROM=1 保留

FEFFH FF00H

FFFFH

DROM=1 保留 DROM=0/MC=1 微处理器模式

DROM控制的 数据存储空间

电气与信息工程学院

DSP技术及应用

3FFFH EFFFH 4000H

4000H

2

FEFFH FF00H FF7FH FF80H FFFFH

内部ROM

Ƭ ÄÚROM

F000H

外部存储器

保留 中断矢量表 (内部存储器) FF7FH FF80H FFFFH ±£ Áô 中断矢量表 (外部存储器)

EFFFH FEFFH F000H FF00H

3.1.1 程序存储空间

需的系数表。

’C54x存储器及片内外 设

• 程序存储空间用来存放要执行的指令和执行中所

• ’C5402共有20条地址线,可寻址1M字的外部程

序存储器。它的内部ROM和DARAM可通过软件映射

2

到程序空间。当存储单元映射到程序空间时,CP U可自动地按程序存储器对它们进行寻址。

2

• ③ FCALA[D]——长调用累加器A或B所指定的位置; • ④ FCALL[D]——长调用指令;

• ⑤ FRET[D]——长返回;

• ⑥ FRETE[D]——带中断使能的长返回指令。

电气与信息工程学院

DSP技术及应用

内部ROM

’C54x存储器及片内外 设

• ’C5402共有4K字的内部ROM。 • 当MP/MC=0,4K字的ROM被映射到程序空间的地址范围 为F000H-FFFFH。 • F000H-F7FFH:用户专用程序,由TI公司固化;F800H -FFFFH:TI公司定义。

OVLY=1 保留 OVLY=1 保留 007FH OVLY=0 外部存储器 OVLY=1 保留 OVLY=0 外部存储器

DSP技术及应用

程序存储空间

微处理器模式: MP/ MC=1

地址

0000H 0000H 007FH

’C54x存储器及片内外 设

程序存储空间

OVLY=1 OVLY=1 保留保留 留 保 OVLY=0 外部存储器 OVLY=1 保留 OVLY=0 外部存储器 OVLY=0 外部存储器 OVLY=1 内部DARAM OVLY=1 内部DARAM OVLY=0 外部存储器 OVLY=1 内部DARAM OVLY=0 外部存储器 OVLY=0 外部存储器

地址

0000H 007FH 0080H 3FFFH 4000H

程序存储空间

OVLY=1 保留 (0页) OVLY=0 外部存储器 OVLY=1 内部DARAM OVLY=0 外部存储器 外部存储器

地址 地址

0000H 0000H 005FH 0060H 007FH 005FH

0060H 0080H

007FH 3FFFH 0080H

• 如果程序地址生成器(PAGEN)产生的地址处于

外部存储器,CPU可自动地对外部存储器寻址。

电气与信息工程学院

DSP技术及应用

程序存储空间

微计算机模式:MP/ MC=0

0000H~007FH

0080H~3FFFH

’C54x存储器及片内外 设

地址

0000H 0000H

程序存储空间

保留

内部DARAM 外部存储器

007FH OVLY=0 外部存储器 007FH OVLY=1 内部DARAM 0080H 0080H OVLY=0 外部存储器 3FFFH OVLY=1 内部DARAM OVLY=0 外部存储器 OVLY=1 内部DARAM 4000H OVLY=0 外部存储器 外部存储器 3FFFH EFFFH 4000H F000H 外部存储器 OVLY=0内部ROM 外部存储器 FEFFH EFFFH F000H FF00H 内部ROM 保留 FF7FH FEFFH FF00H FF80H 中断矢量表 保留 (内部存储器) FFFFH FF7FH FF80H 中断矢量表 (内部存储器) FFFFH

中断矢量表 中断矢量表 (外部存储器) (外部存储器)

FF7FH

外部存储器 中断矢量表

FF7FH FF7FH FF80H FF80H

FFFFH

FFFFH FFFFH

电气与信息工程学院

DSP技术及应用

程序存储空间的分页扩展

’C54x存储器及片内外 设

• 在’C54x系列芯片中,有些芯片采用分页扩展的 方法,使程序存储空间可扩展到1M-8M。 • 如:’C5409和’C5416可扩展到8M。’C5402有20 条外部程序地址总线,其程序空间只能扩展到1M。 分页扩展技术的特点:

• ROM可以灵活地映射到程序存储空间,同时也可以部

分地映射到数据存储空间。

• 存储空间的任何一种存储器都可以驻留在片内或片外。

电气与信息工程学院

DSP技术及应用

TMS320VC5402存储器配置结构

地址

0000H 007FH 0080H 3FFFH 4000H 外部存储器 EFFFH F000H

为1M。整个程序存储空间分成16页,每页共计64K字。

0 0000H

第0页

1 0000H

第1页 低32K字 (片外) 64K字 第1页 高32K字 (片外)

F 0000H

2

… … …

F 7FFFH F 8000H

第15页 低32K字 (片外) 64K字 第15页 高32K字 (片外)

64K字

1 7FFFH 1 8000H

’C54x存储器及片内外 设

数据存储空间 数据存储空间

存储器映像寄存器 存储器映像 暂存寄存器 寄存器 暂存器 内部DARAM (16K×16位) SPRAM 内部DARAM 外部存储器 (16K×16位字) DROM=0 外部ROM 外部存储器 DROM=1 内部ROM

程序存储空间

OVLY=1 保留 (0页) OVLY=0 外部存储器 OVLY=1 内部DARAM OVLY=0 外部存储器

程序/数据 DARAM

SARAM

0

0

0

0

0

24K

24K

0

56K

64K

168K

电气与信息工程学院

DSP技术及应用

’C54x的存储空间结构

存储器分别统一编址。

’C54x存储器及片内外 设

• ’C54x所有内部和外部程序存储器及内部和外部数据

• 内部RAM总是映射到数据存储空间,但也可映射到程

2

序存储空间。

2

’C54x存储器及片内外 设

’C5402数据存储空间结构

地址

0000H 005FH 0060H 007FH 0080H 3FFFH 4000H EFFFH F000H

存储器映像寄存器 暂存器SPRAM 内部DARAM 外部存储器

数据存储空间

存储器映像 存储器映像 寄存器 寄存器 暂存器 暂存器 SPRAM SPRAM 内部DARAM 内部DARAM (16K字) (16K字) 外部存储器 DROM=1 内部ROM DROM=1 内部ROM DROM=1 内部ROM DROM=0 外部存储器 DROM=0 外部存储器 DROM=1 保留 DROM=1 保留 DROM=1 保留 DROM=0 外部存储器 外部存储器 DROM=0