SEL5823A中文资料

ADC0832芯片资料

在数控直流电流源中,ADC0832主要是用在了电流的检测,把检测到的电流值送给单片机进行相应的处理,通过1602显示出来,同时用简单的计算得出电压值。

数控的含义就是通过D/A和A/D进行相应的转换,实现用单片机进行相应的控制。

在网上搜到了一些资料,同时再参照PDF相关知识,运用别人的程序自己试着修改就可以了,这也是我运用网络学习电子类知识的小小方法。

下边的部分是在网上找到的一片不错的总结:ADC0832 是美国国家半导体公司生产的一种8 位分辨率、双通道A/D转换芯片。

由于它体积小,兼容性,性价比高而深受单片机爱好者及企业欢迎,其目前已经有很高的普及率。

学习并使用ADC0832 可使我们了解A/D转换器的原理,有助于我们单片机技术水平的提高。

ADC0832 特点· 8位分辨率;· 双通道A/D转换;· 输入输出电平与TTL/CMOS相兼容;· 5V电源供电时输入电压在0~5V之间;· 工作频率为250KHZ,转换时间为32μS;· 一般功耗仅为15mW;· 8P、14P—DIP(双列直插)、PICC 多种封装;· 商用级芯片温宽为0°C to +70°C,工业级芯片温宽为?40°C to +85°C;芯片接口说明:· CS_ 片选使能,低电平芯片使能。

· CH0 模拟输入通道0,或作为IN+/-使用。

· CH1 模拟输入通道1,或作为IN+/-使用。

· GND 芯片参考0 电位(地)。

· DI 数据信号输入,选择通道控制。

· DO 数据信号输出,转换数据输出。

· CLK 芯片时钟输入。

· Vcc/REF 电源输入及参考电压输入(复用)。

ADC0832 为8位分辨率A/D转换芯片,其最高分辨可达256级,可以适应一般的模拟量转换要求。

5821中文资料

BiMOS II 8-BIT SERIAL-INPUT,LATCHED DRIVERSAlways order by complete part number, e.g., UCN5821A .Data Sheet 26185.12E5821 AND 5822A merged combination of bipolar and MOS technology gives these devices an interface flexibility beyond the reach of standard logic buffers and power driver arrays. The UCN5821A,UCN5821LW, UCN5822A, and UCN5822LW each have an eight-bit CMOS shift register and CMOS control circuitry, eight CMOS data latches, and eight bipolar current-sinking Darlington output drivers. The UCN5821A/LW and UCN5822A/LW are identical except for rated output voltage.BiMOS II devices have much higher data-input rates than the original BiMOS circuits. With a 5 V logic supply, they will typically operate at better than 5 MHz. With a 12 V supply,significantly higher speeds are obtained. The CMOS inputs are compatible with standard CMOS and NMOS logic levels. TTL circuits may require the use of appropriate pull-up resistors. By using the serial data output, the drivers can be cascaded for interface applications requiring additional drive lines.The UCN5821/22A are furnished in a standard 16-pin plastic DIP; the UCN5821/22LW are in a 16-lead wide-body SOIC for surface-mount applications. The UCN5821A is also available for operation from -40°C to +85°C. To order, change the prefix from ‘UCN’ to ‘UCQ’.FEATURESI To 3.3 MHz Data Input Rate I CMOS, NMOS, TTL Compatible I Internal Pull-Down ResistorsI Low-Power CMOS Logic & Latches I High-Voltage Current-Sink Outputs I Automotive Capable5821 AND 58228-BIT SERIAL-INPUT,LATCHED DRIVERS115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000Copyright © 1985, 2000, Allegro MicroSystems, Inc.5821 AND 5822 8-BIT SERIAL-INPUT, LATCHED DRIVERS LimitsCharacteristic Symbol Test Conditions Min.Max.Units Output Leakage I CEX UCN5821A/LW, V OUT = 50 V—50µACurrent UCN5822A/LW, VOUT= 80 V—50µAUCN5821A/LW, V OUT = 50 V, T A = +70°C—100µAUCN5822A/LW, V OUT = 80 V, T A = +70°C—100µA Collector-Emitter V CE(SAT)I OUT = 100 mA— 1.1VSaturation Voltage IOUT= 200 mA— 1.3VI OUT = 350 mA, V DD = 7.0 V— 1.6V Input Voltage V IN(0)—0.8VV IN(1)V DD = 12 V10.5—VV DD = 5.0 V 3.5—V Input Resistance r IN V DD = 12 V50—kΩV DD = 5.0 V50—kΩSupply Current I DD(ON)One Driver ON, V DD = 12 V— 4.5mAOne Driver ON, V DD = 10 V— 3.9mAOne Driver ON, V DD = 5.0 V— 2.4mAI DD(OFF)V DD = 5.0 V, All Drivers OFF, All Inputs = 0 V— 1.6mAV DD = 12 V, All Drivers OFF, All Inputs = 0 V— 2.9mA ELECTRICAL CHARACTERISTICS at T A = +25°C, V DD = 5 V, (unless otherwise specified).5821 AND 58228-BIT SERIAL-INPUT,LATCHED DRIVERS115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000TIMING CONDITIONS(V DD = 5.0 V, T A = +25°C, Logic Levels are V DD and Ground)A.Minimum Data Active Time Before Clock Pulse(Data Set-Up Time).......................................................................75 ns B.Minimum Data Active Time After Clock Pulse(Data Hold Time)...........................................................................75 ns C.Minimum Data Pulse Width..............................................................150 ns D.Minimum Clock Pulse Width ............................................................150 ns E.Minimum Time Between Clock Activation and Strobe.......................30 ns F.Minimum Strobe Pulse Width...........................................................100 nsG.Typical Time Between Strobe Activation andOutput Transition ..........................................................................1.0 µsL = Low Logic Level H = High Logic Level X = Irrelevant P = Present State R = Previous StateDwg. No. A-12,627Serial Data present at the input is transferred to the shift register on the logic “0” to logic “1” transition of the CLOCK input pulse. On succeeding CLOCK pulses, the registers shift data information towards the SERIAL DATA OUTPUT. The SERIAL DATA must appear at the input prior to the rising edge of the CLOCK input waveform.Information present at any register is transferred to its respective latch when the STROBE is high (serial-to-parallel con-version). The latches will continue to accept new data as long as the STROBE is held high. Applications where the latches are bypassed (STROBE tied high)will require that the ENABLE input be high during serial data entry.When the ENABLE input is high, all of the output buffers are disabled (OFF)without affecting the information stored in the latches or shift register. With the ENABLE input low, the outputs are controlled by the state of the latches.CLOCKDATA INSTROBEENABLE OUT5821 AND 58228-BIT SERIAL-INPUT,LATCHED DRIVERSNOTES: 1.Lead thickness is measured at seating plane or below.2.Lead spacing tolerance is non-cumulative.3.Exact body and lead configuration at vendor’s option within limits shown.Dwg. MA-001-16A inDwg. MA-001-16A mmUCN5821A and UCN5822ADimensions in Inches (controlling dimensions)Dimensions in Millimeters(for reference only)5821 AND 58228-BIT SERIAL-INPUT,LATCHED DRIVERS115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000NOTES: 1.Lead spacing tolerance is non-cumulative.2.Exact body and lead configuration at vendor’s option within limits shown.UCN5821LW and UCN5822LWDimensions in Inches (for reference only)(controlling dimensions)5821 AND 5822 8-BIT SERIAL-INPUT, LATCHED DRIVERSThe products described here are manufactured under one or more U.S. patents or U.S. patents pending.Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.Allegro products are not authorized for use as critical components in life-support devices or systems without express written approval.The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsi-bility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.5821 AND 58228-BIT SERIAL-INPUT,LATCHED DRIVERS115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000POWERINTERFACE DRIVERSFunctionOutput Ratings*Part Number †SERIAL-INPUT LATCHED DRIVERS8-Bit (saturated drivers)-120 mA 50 V‡58958-Bit350 mA 50 V58218-Bit350 mA 80 V58228-Bit350 mA 50 V‡58418-Bit 350 mA 80 V‡58428-Bit (constant-current LED d river)75 mA 17 V62758-Bit (DMOS d rivers)250 mA 50 V65958-Bit (DMOS drivers)350 mA 50 V‡6A5958-Bit (DMOS drivers)100 mA 50 V6B59510-Bit (active pull-d owns)-25 mA 60 V5810-F an d 6809/1012-Bit (active pull-downs)-25 mA 60 V5811 an d 681116-Bit (constant-current LED driver)75 mA 17 V627620-Bit (active pull-d owns)-25 mA 60 V5812-F an d681232-Bit (active pull-d owns)-25 mA 60 V5818-F an d 681832-Bit100 mA 30 V583332-Bit (saturate d d rivers)100 mA 40 V5832PARALLEL-INPUT LATCHED DRIVERS4-Bit350 mA 50 V‡58008-Bit -25 mA 60 V58158-Bit350 mA 50 V‡58018-Bit (DMOS d rivers)100 mA 50 V6B2738-Bit (DMOS d rivers)250 mA 50 V6273SPECIAL-PURPOSE DEVICESUnipolar Stepper Motor Translator/Driver 1.25 A 50 V‡5804A ressable 8-Bit Deco der/DMOS Driver 250 mA 50 V6259Addressable 8-Bit Decoder/DMOS Driver 350 mA 50 V‡6A259A ressable 8-Bit Deco d er/DMOS Driver 100 mA 50 V6B259A ressable 28-Line Deco d er/Driver 450 mA30 V6817*Current is maximum specified test condition, voltage is maximum rating. See specification for sustaining voltage limits.Negative current is defined as coming out of (sourcing) the output.†Complete part number includes additional characters to indicate operating temperature range and package style.‡Internal transient-suppression diodes included for inductive-load protection.。

ATF-58143-TR2G中文资料

Agilent ATF-58143 Low Noise Enhancement Mode Pseudomorphic HEMT in a Surface Mount Plastic Package Data SheetDescriptionAgilent Tec hnologies’sATF-58143 is a high dynamic range, low noise E-PHEMT housed in a 4-lead SC-70 (SOT-343) surfac e mount plastic package.The combination of high gain, high linearity and low noise makes the ATF-58143 ideal as low noise amplifier for c ellular/ PCS/WCDMA base stations, wireless local loop, and other applic ations that require low noise and high linearity perfor-mance in the 450 MHz to 6 GHz frequenc y range.Features•Low noise and high linearityperformance•Enhancement Mode Technology[1]•Excellent uniformity in productspecifications•Low cost surface mount smallplastic package SOT-343 (4 leadSC-70) in Tape-and-Reel packagingoption available•Lead-free option availableSpecifications2 GHz; 3V, 30mA (Typ.)•30.5 dBm output 3rd order intercept•19 dBm output power at 1 dB•0.5 dB noise figure•16.5 dB associated gainApplications•Q1 LNA for cellular/PCS/WCDMAbase stations•Q1, Q2 LNA and Pre-driveramplifier for 3–4 GHz WLL•Other low noise and high linearityapplications at 450 MHz to 6 GHzNote:1.Enhancement mode technology requirespositive Vgs, thereby eliminating the need forthe negative gate voltage associated withconventional depletion mode devices. Surface Mount PackageSOT-343Pin Connections andPackage MarkingSOURCEDRAINGATESOURCENote:T op View. Package marking provides orientationand identification“8F” = Device Code“x” = Date code characteridentifies month of manufacture.Attention:Observe precautions forhandling electrostaticsensitive devices.ESD Machine Model (Class A)ESD Human Body Model (Class 0)Refer to Agilent Application Note A004R:Electrostatic Discharge Damage and Control.ATF-58143 Absolute Maximum Ratings [1]Absolute SymbolParameterUnitsMaximumV DS Drain-Source Voltage [2]V 5V GS Gate-Source Voltage [2]V -5 to 1V GD Gate Drain Voltage [2]V -5 to 1I DS Drain Current [2]mA 100P diss Total Power Dissipation [3]mW 500P in max.RF Input Power dBm +135]I GS Gate Source Current mA 2[5]T CH Channel Temperature °C 150T STG Storage Temperature °C -65 to 150θjcThermal Resistance [4]°C/W162Notes:1.Operation of this device above any one of these parameters may cause permanent damage.2.Assumes DC quiescent conditions.3.Source lead temperature is 25°C. Derate 6.2mW/°C for T L > 33°C.4.Thermal resistance measured using150°C Liquid Crystal Measurement method.5.The device can handle +13 dBm RF Input Power provided I GS is limited to 2 mA. I GS at P 1dB drive level is bias circuit dependent. See applications section for additional information.Product Consistency Distribution Charts [6, 7]Figure 1. Typical I-V Curves (V GS =0.1V per step)V DS (V)I D S (m A )0712345612010080604020-150-125-100-75-50-2500.30.40.50.6NF (dB)0.70.8Figure 2. NF @ 3V, 30 L = 0.9, Nominal = 0.5GAIN (dB)15161718Figure 3. Gain @ 3V, 30 mA.USL = 18.5, LSL = 15, Nominal = 16.5OIP3 (dBm)28293031323433Figure 4. OIP3 @ 3V, 30 mA.LSL = 29, Nominal = 30.5Notes:6.Distribution data sample size is 500 samples taken from 3 different wafers. Future wafers allocated to this product may have nominal values anywhere between the upper and lower limits.7.Measurements made on production test board. This circuit represents a trade-off between an optimal noise match and a realizeable match based on production test equipment. Circuit losses have been de-embedded from actual measurements.ATF-58143 Electrical SpecificationsT A = 25°C, RF parameters measured in a test circuit for a typical deviceSymbolParameter and Test ConditionUnitsMin.Typ.[2]Max.Vgs Operational Gate Voltage Vds = 3V, Ids = 30 mA V 0.40.510.75Vth Threshold Voltage Vds = 3V, Ids = 4 mA V 0.180.380.52Idss Saturated Drain Current Vds = 3V, Vgs = 0V µA —15Gm Transconductance Vds = 3V, gm = ∆Idss/∆Vgs;mmho 230410560∆Vgs = 0.75–0.7 = 0.05V Igss Gate Leakage Current Vgd = Vgs = -3V µA ——200NFNoise Figure [1]f = 2 GHz Vds = 3V, Ids = 30 mA dB —0.50.9f = 900 MHz Vds = 3V, Ids = 30 mA dB —0.3—f = 2 GHz Vds = 4V, Ids = 30 mA dB —0.5—f = 900 MHz Vds = 4V, Ids = 30 mA dB —0.3—Ga Associated Gain [1]f = 2 GHz Vds = 3V, Ids = 30 mA dB 1516.518.5f = 900 MHz Vds = 3V, Ids = 30 mA dB —23.1—f = 2 GHz Vds = 4V, Ids = 30 mA dB —17.7—f = 900 MHz Vds = 4V, Ids = 30 mA dB —22.5—OIP3Output 3rd Order f = 2 GHz Vds = 3V, Ids = 30 mA dBm 2930.5—Intercept Point [1]f = 900 MHz Vds = 3V, Ids = 30 mA dBm —28.6—f = 2 GHz Vds = 4V, Ids = 30 mA dBm —31.5—f = 900 MHz Vds = 4V, Ids = 30 mA dBm —31.0—P1dB1dB Compressed f = 2 GHz Vds = 3V, Ids = 30 mA dBm —19—Output Power [1]f = 900 MHz Vds = 3V, Ids = 30 mA dBm —18—f = 2 GHz Vds = 4V, Ids = 30 mA dBm —21—f = 900 MHzVds = 4V, Ids = 30 mAdBm—19—Notes:1.Measurements obtained using production test board described in Figure 5.2.T ypical values determined from a sample size of 500 parts from 3 wafers.Figure 5. Block diagram of 2 GHz production test board used for Noise Figure, Associated Gain,P1dB and OIP3 measurements. This circuit represents a trade-off between an optimal noise match and associated impedance matching circuit losses.RFinATF-58143 Typical Performance CurvesF m i n (d B )0.70.60.50.40.30.2Figure 10. Gain vs. Ids and Vds Tuned for Max OIP3 and Fmin at 900 MHz. Ids (mA)G A I N (d B )0701020304050602524232221201918Figure 11. OIP3 vs. Ids and Vds Tuned for Max OIP3 and Fmin at 2 GHz. Ids (mA)070102030405060Figure 12. OIP3 vs. Ids and Vds Tuned for Max OIP3 and Fmin at 900 MHz.Ids (mA)070102030405060Figure 6. Close-up of Production Test Board.C4J2C2L1C5ATF-58143SAGILENTTECHNOLOGIES C3J1G SC1R1C1: 2.7 pF Cap (0603): 1 pF Cap (0603): 1200 pF Cap (0603): 120 pF Cap (0402): 1200 pF Cap (0603): 49.9 Ohm (0603): 56 nH (0603): 0 Ohm, Jumper (0805): 0 Ohm, Jumper (0805): 0 Ohm, Jumper (0402): 0 Ohm, Jumper (0402)C2C3C4C5R1L1J1J2J3J4AATF-58143 Typical Performance Curves , continuedFigure 13. P1dB vs. Idq and Vds Tuned forMax OIP3 and Fmin at 2 GHz.[1]Idq (mA)P 1d B (d B m )07010203040506024222018161412Figure 14. P1dB vs. Idq and Vds Tuned forMax OIP3 and Fmin at 900 MHz.[1]Idq (mA)P 1d B (d B m )070102030405060232221201918171615Figure 15. Fmin vs. Frequency and Temp. Tuned for Max OIP3 and Fmin at 3V, 30 mA.FREQUENCY (GHz)F m i n (d B )06123451.51.00.5Figure 16. Gain vs. Frequency and Temp. Tuned for Max OIP3 and Fmin at 3V, 30 mA. Note:1. When plotting P1dB, the drain current was allowed to vary dependent on the RF input power.FREQUENCY (GHz)G A I N (d B )062345130252015105Figure 17. OIP3 vs. Frequency and Temp. Tuned for Max OIP3 and Fmin at 3V, 30 mA. FREQUENCY (GHz)O P I 3 (d B m )0623451353025201510Figure 18. P1dB vs. Frequency and Temp. Tuned for Max OIP3 and Fmin at 3V, 30 mA.FREQUENCY (GHz)P 1d B (d B m )062345120.019.519.018.518.017.517.016.516.011211222 GHzMag.Ang.dBMag.Ang.dBMag.Ang.Mag.Ang.dB0.10.98-17.127.2923.14168.7-40.100.01080.80.67-12.133.690.50.81-92.025.2518.31123.7-28.100.03945.70.42-46.626.680.90.75-126.421.8712.40103.4-26.120.04934.80.32-66.723.991.00.73-132.221.1811.4699.8-25.870.05133.40.31-72.323.521.50.69-153.218.388.3185.1-24.700.05829.40.25-90.821.541.90.66-165.916.74 6.8875.4-23.860.06427.40.23-103.620.302.00.65-169.316.40 6.6173.1-23.650.06626.90.22-106.020.032.50.63176.314.83 5.5161.9-22.710.07324.40.19-118.118.773.00.61160.713.51 4.7450.9-21.870.08121.10.17-133.317.693.50.61147.412.35 4.1540.4-21.100.08817.70.15-145.416.734.00.62133.811.28 3.6630.2-20.450.09513.50.13-155.715.864.50.64123.710.32 3.2820.5-19.860.1029.30.13-175.415.095.00.66112.59.41 2.9611.1-19.390.107 4.90.13166.214.405.50.68103.78.61 2.70 2.1-18.870.1140.70.14152.813.746.00.6993.07.84 2.47-7.3-18.440.120-4.40.14140.713.147.00.7177.2 6.47 2.11-24.8-17.630.131-14.60.17120.712.068.00.7458.3 5.14 1.81-43.1-17.130.139-26.10.1995.411.149.00.7839.7 3.77 1.54-60.7-16.670.147-37.00.2470.110.2210.00.8425.1 2.55 1.34-78.8-16.210.155-50.20.3452.49.3911.00.8710.2 1.25 1.16-97.1-16.040.158-64.20.4137.38.6512.00.89-3.90.19 1.02-114.0-15.720.164-78.30.4621.57.9613.00.90-20.0-1.090.88-132.2-15.860.161-93.60.52 2.57.3914.00.93-31.4-2.530.75-148.3-16.220.154-106.50.58-14.1 6.8515.00.96-43.9-4.000.63-162.8-16.730.146-118.20.66-26.0 6.3616.00.94-54.2-5.460.53-176.5-17.150.139-128.60.72-36.3 5.8517.00.96-65.1-7.140.44168.6-17.680.131-142.40.74-49.0 5.2718.00.93-79.8-8.810.36153.8-18.360.121-155.60.77-64.84.77Freq F min Γopt Γopt R n/50G a GHzdBMag.Ang.dB0.50.120.3917.7750.0425.330.90.180.3746.90.0422.261.00.200.3653.5250.0421.541.50.320.32800.0419.161.90.430.301010.0417.652.00.450.30107.70.0417.332.40.510.29125.20.0416.233.00.580.31154.4750.0514.773.90.750.35-156.950.0613.395.00.870.42-120.930.0911.925.8 1.010.50-100.830.1511.076.01.040.53-97.150.1810.93Notes:1.F min values at 2GHz and higher are based on measurements while the F mins below 2 GHz have been extrapolated. The F min values are based on a set of 16 noise figure measurements made at 16 different impedances using an ATN NP5 test system. From these measurements F min is calculated. Refer to the noise parameter application section for more information.2.S and noise parameters are measured on a microstrip line made on 0.025 inch thick alumina carrier. The input reference plane is at the end of the gate lead. The output reference plane is at the end of the drain lead. The parameters include the effect of four plated through via holes connecting source landing pads on top of the test carrier to the microstrip ground plane on the bottom side of the carrier. T wo 0.020 inch diameter via holes are placed within 0.010 inch from each source lead contact point, one via on each side of that point.Typical Noise Parameters, V DS = 3V, I DS = 30 mA Figure 19. MSG/MAG and S 21 vs. Frequency at 3V, 30 mA.FREQUENCY (GHz)M S G /M A G a n d S 21 (d B )20101554035302520151050-5-10-1511211222 GHzMag.Ang.dBMag.Ang.dBMag.Ang.Mag.Ang.dB0.10.99-16.328.1625.6169.65-41.080.0181.10.65-10.1734.620.50.83-94.525.8219.5125.68-28.950.0446.20.45-54.8327.390.90.76-133.122.5213.4104.58-27.000.0433.90.33-76.4524.7610.75-139.721.8312.3100.73-26.740.0532.00.31-80.2824.291.50.72-162.218.948.985.42-25.790.0526.90.24-95.1722.371.90.71-172.717.187.275.68-25.250.0524.80.21-104.2721.2120.70-174.916.79 6.973.47-25.090.0624.40.21-106.1820.942.50.69173.514.67 5.459.58-24.150.0621.70.18-117.3519.4130.68161.613.05 4.546.88-23.330.0719.00.16-124.8518.1940.67141.911.00 3.528.55-22.140.0814.10.13-137.3316.5750.69123.19.29 2.910.32-21.130.097.30.12-42.6515.2160.73108.97.73 2.4-7.48-20.280.10-1.30.13158.7314.0070.7696.3 6.16 2.0-23.78-19.800.10-9.70.17125.8712.9880.7982.4 4.74 1.7-39.33-19.320.11-16.90.20104.8812.0390.8271.2 3.63 1.5-55.93-18.490.12-26.70.2583.1211.06100.8560.1 2.63 1.4-73.30-17.740.13-39.30.3161.0310.19110.8747.2 1.52 1.2-90.53-17.310.14-52.20.3841.339.42120.8936.20.38 1.0-106.67-17.120.14-64.50.4422.658.75130.9126.6-0.800.9-121.58-17.090.14-75.20.49 6.288.15140.9317.2-2.010.8-135.15-17.150.14-84.20.54-7.487.57150.949.2-3.240.7-148.98-17.220.14-94.30.59-22.78 6.99160.94 1.2-4.430.6-164.25-17.360.14-106.10.64-39.22 6.46170.92-10.5-5.790.5-59.55-17.680.13-119.30.68-53.35 5.94180.9117.6-6.740.5170.70-17.940.13-127.50.69-71.735.60Freq F min Γopt Γopt R n/50G a GHzdBMag.Ang.dB0.50.140.389.70.0324.850.90.230.3644.40.0422.211.00.250.3554.00.0421.511.50.350.3278.70.0419.211.90.470.3100.70.0417.712.00.490.3105.40.0417.392.40.550.28124.00.0416.253.00.610.3153.90.0514.863.90.780.35-157.20.0713.515.00.910.42-120.80.112.055.8 1.050.49-101.20.1611.146.01.110.53-97.40.1911.14Notes:1.F min values at 2GHz and higher are based on measurements while the F mins below 2 GHz have been extrapolated. The F min values are based on a set of 16 noise figure measurements made at 16 different impedances using an ATN NP5 test system. From these measurements F min is calculated. Refer to the noise parameter application section for more information.2.S and noise parameters are measured on a microstrip line made on 0.025 inch thick alumina carrier. The input reference plane is at the end of the gate lead. The output reference plane is at the end of the drain lead. The parameters include the effect of four plated through via holes connecting source landing pads on top of the test carrier to the microstrip ground plane on the bottom side of the carrier. T wo 0.020 inch diameter via holes are placed within 0.010 inch from each source lead contact point, one via on each side of that point.Typical Noise Parameters, V DS = 4V, I DS = 30 mA Figure 20. MSG/MAG and S 21 vs. Frequency at 4V, 30 mA.FREQUENCY (GHz)M S G /M A G a n d S 21 (d B )20101554035302520151050-5-10Ordering Information Part NumberNo. of DevicesContainerATF-58143-TR130007" Reel ATF-58143-TR21000013" Reel ATF-58143-BLK 100antistatic bag ATF-58143-TR1G 30007” Reel ATF-58143-TR2G 1000013”Reel ATF-58143-BLKG100antistatic bagPackage Dimensions Outline 43 (SOT-343/SC70 4 lead)Symbol MIN. (mm)MAX. (mm)E 1.151.35D 1.852.25HE 1.80 2.40A 0.80 1.10A2 0.80 1.00A1 0.000.10b 0.250.40b1 0.550.70c 0.10 0.20L0.10 0.46Notes:1.All dimensions are in mm.2.Dimensions are inclusive of plating.3. Dimensions are exclusive of mold flash and metal blurr.4. All specifications comply to EIAJ SC70.5. Die is facing up for mold and facing down for trim/form, i.e., reverse trim/form.6. Package surface to be mirror finish.Recommended PCB Pad Layout for Agilent's SC70 4L/SOT-343 Products(Dimensions in inches/mm)Device OrientationUSER FEEDEND VIEWTOP VIEWTape Dimensions For Outline 4TFor product information and a complete list of Agilent contacts and distributors, please go to our web site./semiconductorsE-mail: SemiconductorSupport@ Data subject to change.Copyright © 2004 Agilent T echnologies, Inc.Obsoletes 5988-1922EN December 10, 20045989-1919ENTape Dimensions and Product Orientation DescriptionSymbolSize (mm)Size (inches)CavityLength A o 2.40 ± 0.100.094 ± 0.004Width B o 2.40 ± 0.100.094 ± 0.004Depth K o 1.20 ± 0.100.047 ± 0.004PitchP 4.00 ± 0.100.157 ± 0.004Bottom Hole Diameter D 1 1.00 + 0.250.039 + 0.010 PerforlationDiameter D 1.50 + 0.100.061 + 0.002Pitch P O 4.00 ± 0.100.157 ± 0.004Position E 1.75 ± 0.100.069 ± 0.004 Carrier Tape Width W 8.00 + 0.30 - 0.100.315 + 0.012Thickness t 10.254 ± 0.020.0100 ± 0.0008 Cover Tape Width C 5.40 ± 0.0100.205 + 0.004Thickness T t 0.062 ± 0.0010.0025 ± 0.0004DistanceCavity to Perforation F 3.50 ± 0.050.138 ± 0.002(Width Direction)Cavity to Perforation P 22.00 ± 0.050.079 ± 0.002(Length Direction)。

831A中文资料

ZC829, ZDC833, ZMV829, ZMDC830, ZV831 Series Device DescriptionA range of silicon varactor diodes for use in frequency control and filtering.Featuring closely controlled CV characteristics and high Q.Low reverse current ensures very low phase noise performance.Available in single or dual common cathode format in a wide rage of miniature surface mount packages.Features·Close tolerance C-V characteristics ·High tuning ratio ·Low I R (typically 200pA)·Excellent phase noise performance ·High Q·Range of miniature surface mount packagesApplications·VCXO and TCXO·Wireless communications ·Pagers ·Mobile radio*Where steeper CV slopes are required there is the 12V hyperabrupt range.ZC930, ZMV930, ZV930, ZV931 Series 830 seriesISSUE 6 - JANUARY 20021SILICON 28V HYPERABRUPT VARACTOR DIODES830 seriesISSUE 6 - JANUARY 20022PARTCapacitance (pF)V R =2V,f=1MHzMin Q V R =3V f=50MHzCapacitance RatioC 2/C 20at f=1MHzMIN.NOM.MAX.MIN.MAX.829A 7.388.29.02250 4.3 5.8829B 7.798.28.61250 4.3 5.8830A 9.010.011.0300 4.5 6.0830B 9.510.010.5300 4.5 6.0831A 13.515.016.5300 4.5 6.0831B 14.2515.015.75300 4.5 6.0832A 19.822.024.2200 5.0 6.5832B 20.922.023.1200 5.0 6.5833A 29.733.036.3200 5.0 6.5833B 31.3533.034.65200 5.0 6.5834A 42.347.051.7200 5.0 6.5834B 44.6547.049.35200 5.0 6.5835A 61.268.074.8100 5.0 6.5835B 64.668.071.4100 5.0 6.5836A 90.0100.0110.0100 5.0 6.5836B95.0100.0105.0100 5.06.5TUNING CHARACTERISTICS at Tamb = 25°CPARAMETER SYMBOLMAX UNIT Forward currentI F 200mA Power dissipation at T amb =25ЊC SOT23P tot 330mW Power dissipation at T amb =25ЊC SOD323P tot 330mW Power dissipation at T amb =25ЊC SOD523P tot250mW Operating and storage temperature range-55to +150ЊCABSOLUTE MAXIMUM RATINGSPARAMETERCONDITIONS MIN.TYP.MAX.UNIT Reverse breakdown voltage I R =10uA 25V Reverse voltage leakageV R =20V 0.220nA Temperature coefficient of capacitanceV R =3V,f =1MHz300400ppCm/ЊCELECTRICAL CHARACTERISTICS at Tamb = 25°C830 seriesTYPICAL CHARACTERISTICSISSUE 6 - JANUARY 20023830 seriesISSUE 6 - JANUARY 20024O R D E R C O D E S A N D P A R T M A R K I N GR E E L C O D ER E E L S I Z ET A P E W I D T HQ U A N T I T Y P E R R E E LT A7i n c h (180m m )8m m3000T C13i n c h (330m m )8m m 10000T A P E A N D R E E L I N F O R M A T I O NT h e o r d e r c o d e s a r e s h o w n a s T A w h i c h i s f o r 7i n c h r e e l s .F o r 13i n c h r e e l s s u b s t i t u t e T C i n p l a c e o f T A i n t h e o r d e r c o d e .ISSUE 6 - JANUARY 20025830 seriesSOT23 PACKAGE DIMENSIONSSOD323 PACKAGE DIMENSIONSZetex plcFields New Road ChaddertonOldham, OL9 8NP United KingdomTelephone (44) 161 622 4422Fax: (44) 161 622 4420Zetex GmbHStreitfeldstraße 19D-81673 München GermanyTelefon: (49) 89 45 49 49 0Fax: (49) 89 45 49 49 49Zetex Inc700 Veterans Memorial Hwy Hauppauge, NY11788USATelephone: (631) 360 2222Fax: (631) 360 8222Zetex (Asia) Ltd3701-04Metroplaza, Tower 1Hing Fong Road Kwai Fong Hong KongTelephone: (852) 26100 611Fax: (852) 24250 494These offices are supported by agents and distributors in major countries world-wide.This publication is issued to provide outline information only which (unless agreed by the Company in writing)may not be used,applied or reproduced for any purpose or form part of any order or contract or be regarded as a representation relating to the products or services concerned.The Company reserves the right to alter without notice the specification,design,price or conditions of supply of any product or service.For the latest product information,log on to©Zetex plc 2001830 series6ISSUE 6 - JANUARY 2002DIM MILLIMETRES MIN.MAX A ᎏ0.800A10.0000.100A20.6000.800b10.1600.300c 0.0800.220D 0.7000.900E 1.500 1.700E1 1.100 1.300L 0.2000.400L10.1700.230⍜1Њ4Њ10ЊSOD523 PACKAGE DIMENSIONSSOD323 PACKAGE DIMENSIONS。

ZD5232A中文资料(Cystech Electonics)中文数据手册「EasyDatasheet - 矽搜」

3.0

6.0

3.0

6.5

3.0

6.5

3.0

7.0

3.0

8.0

2.0

8.4

1.0

9.1

0.5

9.9

0.1

11

0.1

12

0.1

14

0.1

15

0.1

17

0.1

18

0.1

21

0.1

21

0.1

23

0.1

25

0.1

27

0.1

30

0.1

33

芯片中文手册,看全文,戳

规格.编号:C326SH 发布日期:2009.10.07

ZD5252A K2 24 23.52 24.48 33 5.2 600

ZD5254A K4 27 26.46 27.54 41 5.0 600

ZD5255A K5 28 27.44 28.56 44 4.5 600

ZD5256A M1 30 29.40 30.60 49 4.2 600

ZD5257A M2 33 32.34 33.66 58 3.8 700

°C

最大正向电压@ I

F=10mA ………………………………………………………........0.9V

最大功率耗散

总功率耗散@T 热阻,结到环境空气ř

L=75 °C Ptot (注1) ................................................... 500毫瓦

ZD5223A C3 2.7 2.65 2.75

30 20 1300

ZD5225A C5 3.0 2.94 3.06

30 20 1600

8205a中文资料

8205a中文资料锂电池保护板根据使用的不同IC和电压具有不同的电路和参数。

常用的保护IC是8261,DW01 +,CS213,GEM5018等。

其中,精工的8261系列具有更好的精度,当然价格也更昂贵。

后者全部在台湾制造。

国内二级市场主要使用DW01 +和CS213。

以下是带有MOS管8205A(8pin)的DW01 +的说明:锂电池保护板的正常工作流程为:当电池电压在2.5V至4.3V之间时,DW01的第一引脚和第三引脚均输出高电平(等于电源电压),第二引脚电压为0V。

此时,DW01的引脚1和3的电压将分别施加到8205A的引脚5和4。

由于8205A中的两个电子开关的G 极连接到DW01的电压,因此它们处于导通状态。

两个电子开关均处于打开状态。

此时,电池单体的负极直接连接至保护板的P-端子,并且保护板具有电压输出。

2.保护板过放电保护控制原理:当电池通过外部负载放电时,电池电压将缓慢降低,与此同时,DW01将通过R1电阻实时监控电池电压。

当电池电压降至约2.3V时,DW01将认为电池电压处于过放电电压状态,引脚1的输出电压立即断开,从而引脚1的电压变为0V,并且开关由于引脚5上没有电压,因此8205A中的电子管关闭。

此时,电池单元的B-和保护板的P-处于断开状态。

即,电池单元的放电电路被切断,并且电池单元将停止放电。

保护板处于过放电状态,并且已经维护。

保护板的P 和P-具有间接充电电压后,DW01通过B-检测到充电电压后,将立即停止过放电状态,并再次在引脚1上输出高电压以开启过放电控制8205A中的电子管。

也就是说,电池单元的B-和保护板的P-被重新连接,并且电池由充电器直接充电。

3.保护板过充保护控制原理:当电池由充电器正常充电时,随着充电时间的增加,电池的电压将越来越高。

当电池电压升至4.4V时,DW01将认为电池电压处于过充电电压状态。

然后立即断开引脚3的输出电压,以使引脚3的电压变为0V,并且由于引脚4上没有电压,因此8205A中的开关管被闭合。

TSOP58236中文资料

IR Receiver Modules for Remote Control SystemsNew TSOP582.., TSOP584.. Vishay SemiconductorsMECHANICAL DATA Pinning:1 = OUT,2 = GND,3 = V S FEATURES•Low supply current•Photo detector and preamplifier in one package •Internal filter for PCM frequency•Improved shielding against EMI•Supply voltage: 2.7 V to 5.5 V•Improved immunity against ambient light•Insensitive to supply voltage ripple and noise •Component in accordance to RoH S 2002/95/EC and WEEE 2002/96/ECDESCRIPTIONThe TSOP582.., TSOP584.. series are miniaturized receivers for infrared remote control systems. A PIN diode and a preamplifier are assembled on a lead frame, the epoxy package acts as an IR filter.The demodulated output signal can be directly decoded by a microprocessor. The TSOP582.. is compatible with all common IR remote control data formats. The TSOP584.. is optimized to suppress almost all spurious pulses from energy saving fluorescent lamps but will also suppress some data signals.This component has not been qualified according to automotive specifications.BLOCK DIAGRAM APPLICATION CIRCUIT19026PARTS TABLECARRIER FREQUENCY STANDARD APPLICATIONS (AGC2/AGC8)VERY NOISY ENVIROMENTS (AGC4) 30 kHz TSOP5823033 kHz TSOP5823336 kHz TSOP5823636.7 kHz TSOP5823738 kHz TSOP58238TSOP5843840 kHz TSOP5824056 kHz TSOP58256元器件交易网New TSOP582.., TSOP584..IR Receiver Modules for Remote Control SystemsVishay SemiconductorsNote(1)Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating condtions for extended periods may affect the device reliability.Note (1)T amb = 25 °C, unless otherwise specifiedTYPICAL CHARACTERISTICST amb = 25 °C, unless otherwise specifiedFig. 1 - Output Active LowABSOLUTE MAXIMUM RATINGS (1)PARAMETER TEST CONDITIONSYMBOLVALUE UNIT Supply voltage (pin 3)V S - 0.3 to + 6.0V Supply current (pin 3)I S 5mA Output voltage (pin 1)V O - 0.3 to 5.5V Voltage at output to supply V S - V O- 0.3 to (V S + 0.3)V Output current (pin 1)I O 5mA Junction temperature T j 100°C Storage temperature range T stg - 25 to + 85°C Operating temperature range T amb - 25 to + 85°C Power consumption T amb ≤ 85 °C P tot 10mW Soldering temperaturet ≤ 10 s, 1 mm from case T sd260°CELECTRICAL AND OPTICAL CHARACTERISTICS (1)PARAMETER TEST CONDITION SYMBOL MIN.TYP.MAX.UNIT Supply current (pin 3)E v = 0, V S = 5 V I SD 0.650.85 1.05mA E v = 40 klx, sunlightI SH 0.95mA Supply voltage V S 2.75.5V Transmission distance E v = 0, test signal see fig. 1,IR diode TSAL6200,I F = 400 mA d 40m Output voltage low (pin 1)I OSL = 0.5 mA, E e = 0.7 mW/m 2,test signal see fig. 1V OSL 100mV Minimum irradiance Pulse width tolerance:t pi - 5/f o < t po < t pi + 6/f o ,test signal see fig. 1E e min.0.30.45mW/m 2Maximum irradiance t pi - 5/f o < t po < t pi + 6/f o ,test signal see fig. 1E e max.30W/m 2DirectivityAngle of half transmission distanceϕ1/2± 45degE eV O V V 元器件交易网New TSOP582.., TSOP584..Vishay SemiconductorsIR Receiver Modules for Remote Control SystemsFig. 3 - Output FunctionFig. 4 - Output Pulse DiagramFig. 5 - Frequency Dependence of Responsivity Fig. 6 - Sensitivity in Bright AmbientFig. 7 - Sensitivity vs. Supply Voltage DisturbancesFig. 8 - Sensitivity vs. Electric Field DisturbancesE eV O V V OL0.00.20.40.60.81.01.20.70.91.11.3f/f 0 - Relati v e Fre qu ency16925E /E - R e l. R e s p o n s i v i t y e m i n.e元器件交易网New TSOP582.., TSOP584..IR Receiver Modules for Remote Control SystemsVishay SemiconductorsFig. 9 - Max. Envelope Duty Cycle vs. Burst LengthFig. 10 - Sensitivity vs. Ambient TemperatureFig. 11 - Relative Spectral Sensitivity vs. WavelengthFig. 13 - Vertical DirectivityFig. 14 - Sensitivity vs. Supply Voltage元器件交易网New TSOP582.., TSOP584..Vishay Semiconductors IR Receiver Modules forRemote Control Systems SUITABLE DATA FORMATThe TSOP582.., TSOP584.. series are designed to suppressspurious output pulses due to noise or disturbance signals.Data and disturbance signals can be distinguished by thedevices according to carrier frequency, burst length andenvelope duty cycle. The data signal should be close to theband-pass center frequency (e.g. 38 kH z) and fulfill theconditions in the table below.When a data signal is applied to the TSOP582.., TSOP584..in the presence of a disturbance signal, the sensitivity of thereceiver is reduced to insure that no spurious pulses arepresent at the output. Some examples of disturbance signalswhich are suppressed are:•DC light (e.g. from tungsten bulb or sunlight)•Continuous signals at any frequency•Strongly or weakly modulated noise from fluorescent lamps with electronic ballasts (see figure 15 or figure 16)Fig. 15 - IR Signal from Fluorescent Lampwith Low ModulationFig. 16 - IR Signal from Fluorescent Lampwith High ModulationNoteFor data formats with short bursts please see the data sheet of TSOP581..0101520Time (ms)16920IRSignal50101520Time (ms)16921IRSignal10TSOP582..TSOP584..Minimum burst length10 cycles/burst10 cycles/burstAfter each burst of lengtha minimum gap time is required of 10 to 70 cycles≥ 12 cycles10 to 35 cycles≥ 12 cyclesFor bursts greater thana minimum gap time in the data stream is needed of70 cycles> 4 x burst length35 cycles> 10 x burst lengthMaximum number of continuous short bursts/second8001300 Compatible to NEC code yes yes Compatible to RC5/RC6 code yes yes Compatible to Sony code yes no Compatible to Thomson 56 kHz code yes yes Compatible to Mitsubishi code (38 kHz, preburst 8 ms, 16 bit)yes yes Compatible to Sharp code yes yesSuppression of interference from fluorescent lamps Most common disturbancesignals are suppressedEven extreme disturbancesignals are suppressed元器件交易网New TSOP582.., TSOP584..IR Receiver Modules for Remote Control SystemsVishay SemiconductorsPACKAGE DIMENSIONSin millimeters元器件交易网元器件交易网Vishay Semiconductors IR Receiver Modules forRemote Control SystemsOZONE DEPLETING SUBSTANCES POLICY STATEMENTIt is the policy of Vishay Semiconductor GmbH to1.Meet all present and future national and international statutory requirements.2.Regularly and continuously improve the performance of our products, processes, distribution and operating systems withrespect to their impact on the health and safety of our employees and the public, as well as their impact on the environment.It is particular concern to control or eliminate releases of those substances into the atmosphere which are known as ozone depleting substances (ODSs).The Montreal Protocol (1987) and its London Amendments (1990) intend to severely restrict the use of ODSs and forbid their use within the next ten years. Various national and international initiatives are pressing for an earlier ban on these substances.Vishay Semiconductor GmbH has been able to use its policy of continuous improvements to eliminate the use of ODSs listed in the following documents.1.Annex A, B and list of transitional substances of the Montreal Protocol and the London Amendments respectively.2.Class I and II ozone depleting substances in the Clean Air Act Amendments of 1990 by the Environmental Protection Agency(EPA) in the USA.3.Council Decision 88/540/EEC and 91/690/EEC Annex A, B and C (transitional substances) respectively.Vishay Semiconductor GmbH can certify that our semiconductors are not manufactured with ozone depleting substances and do not contain such substances.We reserve the right to make changes to improve technical designand may do so without further notice.Parameters can vary in different applications. All operating parameters must be validated for each customer application by the customer. Should the buyer use Vishay Semiconductors products for any unintended or unauthorized application, the buyer shall indemnify Vishay Semiconductors against all claims, costs, damages, and expenses, arising out of, directly or indirectly, any claim of personal damage, injury or death associated with such unintended or unauthorized use.Vishay Semiconductor GmbH, P.O.B. 3535, D-74025 Heilbronn, GermanyDisclaimer Legal Disclaimer NoticeVishayAll product specifications and data are subject to change without notice.Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, “Vishay”), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.Vishay disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay’s terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay.The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay for any damages arising or resulting from such use or sale. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.Product names and markings noted herein may be trademarks of their respective owners.元器件交易网。

S-8253A中文资料

Rev.3.7_00

VDD DOP Oscillator, counter, controller

COP

− + + − + − + − + −

VC1

− + + −

95 kΩ VMP 900 kΩ

VC2

− + + −

CTLH 200 nA CTL CTLM

VSS

Remark All diodes shown in figure are parasitic diodes. Figure 1

2

Seiko Instruments Inc.

元器件交易网

BATTERY PROTECTION IC FOR 2-SERIAL OR 3-SERIAL-CELL PACK S-8253A/B Series

Rev.3.7_00

2. S-8253B Series

VDD DOP Oscillator, counter, controller

元器件交易网

Rev.3.7_00

BATTERY PROTECTION IC FOR 2-SERIAL OR 3-SERIAL-CELL PACK

S-8253A/B Series

The S-8253A/B Series are protection ICs for 2-serial or 3-serial cell lithium-ion rechargeable batteries and include high-accuracy voltage detectors and delay circuits. These ICs are suitable for protecting lithium-ion battery packs from overcharge, overdischarge and overcurrent.

5833中文资料

5833中⽂资料Designed to reduce logic supply current, chip size, and system cost, the UCN5833A/EP integrated circuits offer high-speed operation for thermal printers. These devices can also be used to drive multi-plexed LED displays or incandescent lamps within their 125 mA peak output current rating. The combination of bipolar and MOS technolo-gies gives BiMOS II smart power ICs an interface flexibility beyond the reach of standard buffers and power driver circuits.These 32-bit drivers have bipolar open-collector npn Darlington outputs, a CMOS data latch for each of the drivers, a 32-bit CMOS shift register, and CMOS control circuitry. The high-speed CMOS shift registers and latches allow operation with most microprocessor-based systems at data input rates above 3.3 MHz. Use of these drivers with TTL may require input pull-up resistors to ensure an input logic high.The UCN5833A is supplied in a 40-pin dual in-line plastic package with 0.600" (15.24 mm) row spacing. At an ambient temperature of +75°C, all outputs of the DlP-packaged device will sustain 50 mA continuously. For high-density applications, the UCN5833EP is available. This 44-lead plastic chip carrier (quad pack) is intended for surface-mounting on solder lands with 0.050" (1.27 mm) centers.CMOS serial data outputs permit cascading for applications requiring additional drive lines.FEATURESI To 3.3 MHz Data Input Rate I 30 V Minimum Output Breakdown I Darlington Current-Sink Outputs I Low-Power CMOS Logic and LatchesBiMOS II 32-BIT SERIAL-INPUT,LATCHED DRIVERAlways order by complete part number:Part Number Package UCN5833A 40-Pin DIP UCN5833EP 44-Lead PLCCData Sheet 26185.16A*58335833BiMOS II 32-BIT SERIAL-INPUT,LATCHED DRIVER115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000SERIAL DATA IN POWER STROBE OUT OUT OUT OUT OUT OUT 123456OUT7OUT 8OUT 9OUTOUT OUTOUT OUTLOGIC SUPPLY OUT OUT Dwg. No. A-13,051TYPICAL OUTPUT DRIVERSUBOUT115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000Copyright ? 1986, 1995, Allegro MicroSystems, Inc.5833BiMOS II 32-BIT SERIAL-INPUT,LATCHED DRIVERTRUTH TABLEL = Low Logic Level H = High Logic Level X = Irrelevant P = Present State R = Previous StateELECTRICAL CHARACTERISTICS at T A = +25°C, V DD = 5 V (unless otherwise noted).Limits CharacteristicSymbol Test Conditions Min.Max.Units Output Leakage Current I CEX V OUT = 30 V, T A = 70°C —10µA Collector-Emitter V CE(SAT)l OUT = 50 mA — 1.2V l OUT = 100 mA— 1.7V Input VoltageV IN(1) 3.5 5.3V V IN(0)-0.3+0.8V Input Currentl IN(1)V IN = 5.0 V — 1.0µA l IN(0)V IN = 0 V —-1.0µA Serial Output VoltageV OUT(1)I OUT = -200 µA 4.5—V V OUT(0)I OUT = 200 µA—0.3V Supply Currentl DD One output ON, l OUT = 100 mA — 1.0mA All outputs OFF—50µA Output Rise Time t r l OUT = 100 mA, 10% to 90%—500ns Output Fall Timet fl OUT = 100 mA, 90% to 10%—500nsNOTE: Positive (negative) current is defined as going into (coming out of) the specified device pin.Saturation Voltage5833BiMOS II 32-BIT SERIAL-INPUT,LATCHED DRIVER115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000TIMING CONDITIONS(V DD = 5.0 V, Logic Levels are V DD and Ground)A.Minimum Data Active Time Before Clock Pulse(Data Set-Up Time)..........................................................................75 ns B.Minimum Data Active Time After Clock Pulse(Data Hold Time).............................................................................75 ns C.Minimum Data Pulse Width ................................................................150 ns D.Minimum Clock Pulse Width...............................................................150 nsE.Minimum Time Between Clock Activation and Strobe.......................300 nsF.Minimum Strobe Pulse Width .............................................................100 nsG.Typical Time Between Strobe Activation andOutput Transition ...........................................................................500 nsDwg. No. A-12,276ASerial Data present at the input is transferred to the shift register on the logic “0” to logic “1” transition of the CLOCK input pulse. On succeeding CLOCK pulses, the registers shift data information towards the SERIAL DATA OUTPUT. The SERIAL DATA must appear at the input prior to the rising edge of the CLOCK input waveform.Information present at any register is transferred to its respective latch when the STROBE is high (serial-to-parallel conversion). The latches will continue to accept new data as long as the STROBE is held high. Applications where the latches are bypassed (STROBE tied high) will require that the OUTPUT ENABLE input be low during serial data entry.When the OUTPUT ENABLE input is low, all of the output buffers are disabled (OFF) without affecting the information stored in the latches or shift register. With the OUTPUT ENABLE input high, the outputs are controlled by the state of the latches.CLOCK DATA INSTROBE NOUTPUT ENABLEOUT5833BiMOS II 32-BIT SERIAL-INPUT,LATCHED DRIVERNOTES:1.Exact body and lead configuration at vendor’s option within limits shown.2.Lead spacing tolerance is non-cumulative.3.Lead thickness is measured at seating plane or below.UCN5833ADimensions in Inches (controlling dimensions)Dimensions in Millimeters (for reference only)123Dwg. MA-003-40 mm20421123Dwg. MA-003-40 in2045833BiMOS II 32-BIT SERIAL-INPUT,LATCHED DRIVER115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000UCN5833EPDimensions in Inches (controlling dimensions)Dimensions in Millimeters (for reference only)Dwg. MA-005-44A mm0.53340Dwg. MA-005-44A in0.021740NOTES:1.Exact body and lead configuration at vendor’s option within limits shown.2.Lead spacing tolerance is non-cumulative.5833BiMOS II 32-BITSERIAL-INPUT,LATCHED DRIVERThe products described here are manufactured under one or more U.S. patents or U.S. patents pending.Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.Allegro products are not authorized for use as critical components in life-support devices or systems without express written approval.The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsi-bility for its use; nor for any infringement of patents or other rights of third parties which may result from its use. 5833BiMOS II 32-BIT SERIAL-INPUT,LATCHED DRIVER115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000POWERINTERFACE DRIVERSFunctionOutput Ratings*Part Number ?SERIAL-INPUT LATCHED DRIVERS8-Bit (saturated drivers)-120 mA 50 V?58958-Bit 350 mA 50 V 58218-Bit 350 mA 80 V 58228-Bit 350 mA 50 V?58418-Bit 350 mA 80 V?58428-Bit (constant-current LED driver)75 mA 17 V 62758-Bit (DMOS drivers)250 mA 50 V 65958-Bit (DMOS drivers)350 mA 50 V?6A5958-Bit (DMOS drivers)100 mA 50 V 6B59510-Bit (active pull-downs)-25 mA 60 V 5810-F and 6809/1012-Bit (active pull-downs)-25 mA 60 V 5811 and 681116-Bit (constant-current LED driver)75 mA 17 V 627620-Bit (active pull-downs)-25 mA 60 V 5812-F and 681232-Bit (active pull-downs)-25 mA 60 V 5818-F and 681832-Bit100 mA 30 V 583332-Bit (saturated drivers)100 mA 40 V 5832PARALLEL-INPUT LATCHED DRIVERS4-Bit350 mA 50 V?58008-Bit -25 mA 60 V 58158-Bit350 mA 50 V?58018-Bit (DMOS drivers)100 mA 50 V 6B2738-Bit (DMOS drivers)250 mA 50 V 6273SPECIAL-PURPOSE DEVICESUnipolar Stepper Motor Translator/Driver 1.25 A 50 V?5804Addressable 8-Bit Decoder/DMOS Driver 250 mA 50 V6259Addressable 8-Bit Decoder/DMOS Driver 350 mA 50 V?6A259Addressable 8-Bit Decoder/DMOS Driver 100 mA 50 V 6B259Addressable 28-Line Decoder/Driver 450 mA30 V6817*Current is maximum specified test condition, voltage is maximum rating. See specification for sustaining voltagelimits.Negative current is defined as coming out of (sourcing) the output.Complete part number includes additional characters to indicate operating temperature range and package style. Internal transient-suppression diodes included for inductive-load protection.。

8205a中文资料

1.电池保护板的工作原理:锂电池保护板的电路和参数因IC和电压的不同而不同。

常用的保护芯片是8261,DW01 +,CS213,GEM5018等。

精工的8261系列具有更好的精度,当然也更昂贵。

后者来自台湾,国内二级市场主要使用DW01 +和CS213。

DW01 +使用MOS管8205A(8pin)给出以下说明:锂电池保护板的正常工作过程是:当电池电压在2.5V至4.3V之间时,DW01的第一和第三引脚输出高电平(等于电源电压),第二个引脚电压为0V。

此时,DW01的引脚1和引脚3的电压将分别施加到8205A的引脚5和引脚4上。

因为8205A中的两个电子开关的g极连接到DW01的电压,所以它们都处于导通状态,即两个电子开关都处于导通状态。

此时,电池单元的负极等效于与保护板的P-端子直接连通,并且保护板具有电压输出。

2.保护板的过放电保护控制原理:当电池通过外部负载放电时,电池的电压会逐渐降低,同时,电池的电压将通过R1电阻进行实时监控在DW01内部。

当电池电压降至约2.3V时,DW01会认为电池电压处于过放电电压状态,并立即断开第一引脚的输出电压,从而使第一引脚的电压变为0V,由于第5脚上没有电压,因此8205A中的开关管将闭合。

此时,电池芯的B-与保护板的P-断开。

即,当电池单元的放电电路被切断时,电池单元将停止放电。

保护板处于过放电状态,并一直保持。

在保护板的P-和P-间接施加了充电电压后,DW01在通过B-检测到充电电压后立即停止过放电,并再次在引脚1上输出高电压,从而打开了8205A中的过放电控制管。

即,电池芯的B-与保护板的P-重新连接,并且电池芯由充电器直接充电。

3.保护板过充保护控制原理:当充电器正常给电池充电时,随着充电时间的增加,电池单元的电压会越来越高。

当电池电压升至4.4V时,DW01会认为电池电压处于过充电电压状态,并立即断开第三个引脚的输出电压,从而使第三个引脚的电压变为0V,并且开关由于第四个引脚没有电压,因此8205A中的电子管关闭。

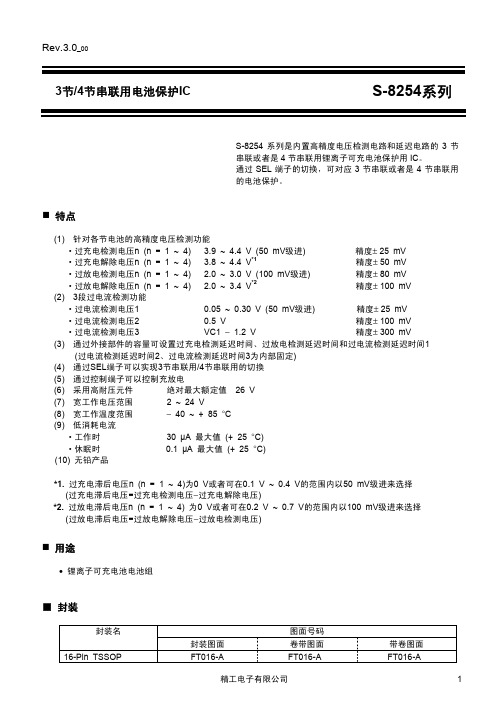

S8254中文-A

记号 VDS

(除特殊注明以外: Ta = 25 °C) 绝对最大额定值 单位 V VSS − 0.3 ∼ VSS + 26 V VSS − 0.3 ∼ VDD + 0.3

精工电子有限公司

5

3节/4节串联用电池保护IC S-8254系列 电气特性

表4 (1/2) 项目 [检测电压] 过充电检测电压n (n=1, 2, 3, 4) 过充电解除电压n (n=1, 2, 3, 4) 记号 条件 最小值 VCUn − 0.025 VCLn − 0.05 VCLn − 0.025 VDLn − 0.08 VDUn − 0.10 VDUn − 0.08 VIOV1 − 0.025 0.4 VC1 − 1.5 − 1.0 − 0.5 0.5 50 5 0.4 100 0.4 0.5 450

过放电检测电压 [VDL] 2.00 ± 0.080 V 2.00 ± 0.080 V 2.00 ± 0.080 V 2.40 ± 0.080 V 2.30 ± 0.080 V 2.40 ± 0.080 V 2.40 ± 0.080 V 2.40 ± 0.080 V 2.70 ± 0.080 V 2.40 ± 0.080 V 2.50 ± 0.080 V 2.50 ± 0.080 V

1. 产品名 S− 8254A xx FT − TB − G

3节/4节串联用电池保护IC S-8254系列

卷带规格中的IC置向*1 封装简称 FT : 16-Pin TSSOP 序列号*2 按AA ~ ZZ顺序设置 *1. *2. 请参阅带卷图。 请参阅“2. 产品名目录”。

2. 产品名目录 表1 型名/项目 S-8254AAAFT-TB-G S-8254AABFT-TB-G S-8254AAEFT-TB-G S-8254AAFFT-TB-G S-8254AAGFT-TB-G S-8254AAHFT-TB-G S-8254AAIFT-TB-G S-8254AAJFT-TB-G S-8254AAKFT-TB-G S-8254AALFT-TB-G S-8254AAMFT-TB-G S-8254AANFT-TB-G

xfl823a原理(一)

xfl823a原理(一)xfl823a原理简介xfl823a是一种智能温度控制芯片,常被应用于电子温度控制领域。

它能够监测环境温度并自动控制输出的电流或电压的大小,从而实现对设备的温度控制。

工作原理xfl823a运用焊接技术,将晶体管、电阻等元器件嵌入芯片内部。

当芯片被电源激活后,先进的电子控制技术让xfl823a开始工作。

它通过检测环境温度来实时调整输出的电流或电压的大小,从而控制设备的温度。

当芯片检测到设备温度接近预设危险温度值时,它会自动关闭电流或电压输出,以保护设备的安全运行。

特点xfl823a具有以下特点:•易于使用:通过简单的电路连接和设置,即可将xfl823a应用于不同的温度控制系统中。

•快速响应:xfl823a可在微秒级别内对温度变化做出响应,确保即时控制设备温度。

•精准控制:该芯片通过多次研究调试,可快速实现设备温度的准确控制,确保设备稳定运行。

•低功耗:由于芯片内部嵌入电阻等元件,xfl823a在工作时几乎不产生功耗,大大延长了设备寿命。

应用xfl823a可以广泛应用于各种需要温度控制的设备中,如空调、冰箱、暖气、水泵等。

同时,它还可应用于医疗、化工、冶金、环保等行业。

通过连接到不同的温度传感器,xfl823a可以实现对不同温度范围内的设备进行智能控制。

总结xfl823a作为一款智能温度控制芯片,具有快速响应、精准控制、低功耗等特点,广泛应用于各种需要温度控制的设备中。

它可以帮助设备稳定运行,延长设备寿命,是电子温度控制领域不可或缺的芯片。

安装与使用xfl823a芯片尺寸小巧,可以方便地安装在电路板上。

使用时,需要将xfl823a连接到相应的温度传感器和设备控制器,并设置相应的参数。

在连接和使用过程中,需要注意电路的极性、连接方式和参数设置,以确保设备正常运行并保护芯片免受电压、电流等因素的损害。

发展前景目前,随着全球对环境保护和能源节约意识的提高,电子温度控制技术在各个领域得到了广泛应用。

ATA5824资料

Features•Full-duplex Operation Mode without Duplex Frequency Offset to Prevent the Relay Attack against Passive Entry Go (PEG) Systems•High FSK Sensitivity: –105.5 dBm at 20 kBaud/–109 dBm at 2.4 kBaud (433.92 MHz)•High ASK Sensitivity: –111.5 dBm at 10 kBaud/–116 dBm at 2.4 kBaud (100% ASK, Carrier Level 433.92 MHz)•Low Supply Current: 10.5 mA in RX and TX Mode (3V/TX with 5 dBm/433.92 MHz)•Data Rate 1 to 20 kBaud Manchester FSK, 1 to 10 kBaud Manchester ASK•ASK/FSK Receiver Uses a Low IF Architecture with High Selectivity, Blocking and Low Intermodulation (Typical 3 dB Blocking55.5 dBC at ±750 kHz/60.5 dBC at ±1.5 MHz and 67 dBC at ±10 MHz, System I1dBCP = –30 dBm/System IIP3 = –20 dBm)•Wide Bandwidth AGC to Handle Large Outband Blockers above the System I1dBCP •226 kHz IF (Intermediate Frequency) with 30 dB Image Rejection and 220 kHz System Bandwidth to Support TPM Transmitters using ATA5756/ATA5757 Transmitters with Standard Crystals•Transmitter Uses Closed Loop FSK Modulation with Fractional-N Synthesizer with High PLL Bandwidth and an Excellent Isolation between PLL and PA•Tolerances of XTAL Compensated by Fractional-N Synthesizer with 800 Hz RF Resolution•Integrated RX/TX-Switch, Single-ended RF Input and Output •RSSI (Received Signal Strength Indicator)•Communication to Microcontroller with SPI Interface Working at 500 kBit/s Maximum •Configurable Self Polling and RX/TX Protocol Handling with FIFO-RAM Buffering of Received and Transmitted Data• 1 Push Button Input and 1 Wake-up Input are Active in Power-down Mode •Integrated XTAL Capacitors•PA Efficiency: up to 38% (433.92 MHz/10 dBm/3V)•Low In-band Sensitivity Change of Typically ±2.0 dB within ±75 kHz Center Frequency Change in the Complete Temperature and Supply Voltage Range•Fully Integrated PLL with Low Phase Noise VCO, PLL Loop Filter and full support of multi-channel operation with arbitrary Channel distance due to Fractional-N Synthesizer•Sophisticated Threshold Control and Quasi-peak Detector Circuit in the Data Slicer •433.92 MHz, 868.3 MHz and 315 MHz without External VCO and PLL Components •Efficient XTO Start-up Circuit (> –1.5 k Ω Worst Case Start Impedance)•Changing of Modulation Type ASK/FSK and Data Rate without Component Changes to Allow Different Modulation Schemes in TPM and RKE•Minimal External Circuitry Requirements for Complete System Solution•Adjustable Output Power: 0 to 10 dBm Adjusted and Stabilized with External Resistor, Programmable Output Power with 0.5dB Steps with Internal Resistor •Clock and Interrupt Generation for Microcontroller•ESD Protection at all Pins (±2.5 kV HBM, ±200V MM, ±500V FCDM)•Supply Voltage Range: 2.15V to 3.6V or 4.4V to 5.25V •Typical Power-down Current < 10 nA •Temperature Range: –40°C to +105°C •Small 7 mm ×7 mm QFN48 Package24829C–RKE–09/05ATA5823/ATA5824Applications•Automotive Keyless Entry and Passive Entry Go (Handsfree Car Access)•Tire Pressure Monitoring Systems •Remote Control Systems•Alarm and Telemetering Systems •Energy Metering •Home AutomationBenefits•No SAW Device Needed in Key Fob Designs to Meet Automotive Specifications •Low System Cost Due to Very High System Integration Level •Only One Crystal Needed in System•Less Demanding Specification for the Microcontroller Due to Handling of Power-down Mode, Delivering of Clock and Complete Handling of Receive/Transmit Protocol and Polling•Single-ended Design with High Isolation of PLL/VCO from PA and the Power Supply Allows a Loop Antenna in the Key Fob to Surround the Whole Application •Prevention against Relay Attack with Full-duplex Operation Mode•Integration of Tire Pressure Monitoring, Passive Entry and Remote Keyless Entry1.General DescriptionThe ATA5823/ATA5824 is a highly integrated UHF ASK/FSK multi-channel half-duplex and full-duplex transceiver with low power consumption supplied in a small 7 mm × 7 mm QFN48 package. The receive part is built as a fully integrated low-IF receiver, whereas direct PLL mod-ulation with the fractional-N synthesizer is used for FSK transmission and switching of the power amplifier for ASK transmission. The additional full-duplex mode makes relay attacks much more difficult, since the attacker has to receive and transmit signals on the same frequency at the same time.The device supports data rates of 1 kBaud to 20 kBaud (FSK) and 1 kBaud to 10 kBaud (ASK) in Manchester, Bi-phase and other codes in transparent mode. The ATA5824 can be used in the 433 MHz to 435 MHz band and the 867 MHz to 870 MHz band, the ATA5823 in the 313 MHz to 316 MHz band. The very high system integration level results in few numbers of external compo-nents needed.Due to its blocking and selectivity performance, together with a typical narrow-band key-fob loop antenna with 15 dB to 20 dB loss, a bulky blocking SAW is not needed in the key fob application. Additionally, the building blocks needed for a typical RKE and access control system on both sides, the base and the mobile stations, are fully integrated.Its digital control logic with self polling and protocol generation provides a fast challenge response system without using a high-performance microcontroller. Therefore, the ATA5823/ATA5824 contains a FIFO buffer RAM and can compose and receive the physical messages themselves. This provides more time for the microcontroller to carry out other func-tions such as calculating crypto algorithms, composing the logical messages and controlling other devices. Due to that, a standard 4-/8-bit microcontroller without special periphery and clocked with the delivered CLK output of about 4.5 MHz is sufficient to control the communica-tion link. This is especially valid for passive entry go and access control systems, where within less than 100 ms several communication responses with arbitration of the communication part-ner have to be handled. It is hence possible to design bi-directional RKE and passive entry go systems with a fast challenge response crypto function and prevention against relay attacks.34829C–RKE–09/05ATA5823/ATA5824Figure 1-1.System Block Diagram2.Pin ConfigurationFigure 2-1.Pinning QFN4844829C–RKE–09/05ATA5823/ATA5824Table 2-1.Pin DescriptionPin Symbol Function 1NC Not connected 2NC Not connected 3NC Not connected 4RF_IN RF input 5NC Not connected6433_N868Selects RF input/output frequency range 7NC Not connected8R_PWR Resistor to adjust output power 9PWR_H Pin to select output power 10RF_OUT RF output 11NC Not connected 12NC Not connected 13NC Not connected 14NC Not connected 15NC Not connected16AVCC Blocking of the analog voltage supply17VS2Power supply input for voltage range 4.4V to 5.6V 18VS1Power supply input for voltage range 2.15V to 3.6V 19SETPWR Internal Programmable Resistor to adjust output power 20TEST1Test input, at GND during operation 21DVCC Blocking of the digital voltage supply 22CS_POL Select polarity of pin CS23TEST2Test input, at GND during operation 24XT AL1Reference crystal 25XT AL2Reference crystal 26NC Not connected27VSINT Microcontroller interface supply voltage 28POUT Programmable output 29IRQ Interrupt request30CLK Clock output to connect a microcontroller 31SDO_TMDO Serial data out/transparent mode data out 32SDI_TMDI Serial data in/transparent mode data in 33SCK Serial clock34TEST3Test output open during operation 35CS Chip select for serial interface 36RSSI Output of the RSSI amplifier37CDEM Capacitor to adjust the lower cut-off frequency data filter 38RX_TX2Has to be connected GND39RX_TX1Switch pin to decouple LNA in TX mode (RKE mode)40PWR_ON Input to switch on the system (active high)41NCNot connected54829C–RKE–09/05ATA5823/ATA5824Figure 2-2.Block Diagram42NC Not connected43SCK_POL Polarity of the serial clock 44SCK_PHA Phase of the serial clock45N_PWR_ON Keyboard input (can also be used to switch on the system, active low)46RX_ACTIVEIndicates RX operation mode 47NC Not connected 48NC Not connectedGNDGround/Backplane (exposed die pad)Table 2-1.Pin Description (Continued)Pin Symbol Function64829C–RKE–09/05ATA5823/ATA58243.Typical Key Fob Application for Bi-directional RKEFigure 3-1.Typical Key Fob Application for Bi-directional RKE with 5 dBm TX Power, 433.92 MHzFigure 3-1 shows a typical 433.92 MHz RKE key fob application. The external components are 10 capacitors, 1 resistor, 2 inductors and a crystal. C 1 to C 3 are 68 nF voltage supply blocking capacitors. C 5 is a 10 nF supply blocking capacitor. C 6 is a 15 nF fixed capacitor used for the internal quasi-peak detector and for the high-pass frequency of the data filter. C 7 to C 11 are RF matching capacitors in the range of 1 pF to 33 pF. L 1 is a matching inductor of about 5.6 nH to 56 nH. L 2 is a feed inductor of about 120 nH. A load capacitor of 9 pF for the crystal is inte-grated. R 1 is typically 22 k Ω and sets the output power to about 5.5 dBm. The loop antenna’s quality factor is somewhat reduced by this application due to the quality factor of L 2 and the RX/TX switch. On the other hand, this lower quality factor is necessary to have a robust design with a bandwidth that is wide enough for production tolerances. Due to the single-ended and ground-referenced design, the loop antenna can be a free-form wire around the application as it is usually employed in RKE unidirectional systems. The ATA5823/ATA5824 provides sufficient isolation and robust pulling behavior of internal circuits from the supply voltage as well as an integrated VCO inductor to allow this. Since the efficiency of a loop antenna is proportional to the square of the surrounded area, it is beneficial to have a large loop around the application board with a lower quality factor to relax the tolerance specification of the RF matching components and to get a high antenna efficiency in spite of their lower quality factor.74829C–RKE–09/05ATA5823/ATA58244.Typical Car Application for Bi-directional RKEFigure 4-1.Typical Car Application for Bi-directional RKE with 10 dBm TX Power, 433.92 MHzFigure 4-1 shows a typical 433.92 MHz V CC = 4.4V to 5.25V RKE car application. The external components are 11 capacitors, 1 resistor, 4 inductors, a SAW filter and a crystal. C 1, C 3 and C 4are 68 nF voltage supply blocking capacitors. C 2 is a 2.2 µF supply blocking capacitor for the internal voltage regulator. C 5 is a 10 nF supply blocking capacitor. C 6 is a 15 nF fixed capacitor used for the internal quasi-peak detector and for the high-pass frequency of the data filter. C 7 to C 11 are RF matching capacitors in the range of 1 pF to 33 pF. L 2 to L 4 are matching inductors of about 5.6 nH to 56 nH. A load capacitor for the crystal of 9 pF is integrated. R 1 is typically 22 k Ωand sets the output power at RF OUT to about 10 dBm . Since a quarter wave or PCB antenna, which has high efficiency and wideband operation, is typically used here, it is recommended to use a SAW filter to achieve high sensitivity in case of powerful out-of-band blockers. L 1, C 10 and C 9 together form a low-pass filter, which is needed to filter out the harmonics in the transmitted signal to meet regulations.84829C–RKE–09/05ATA5823/ATA58245.Typical Key Fob Application for Full-duplex PEGFigure 5-1.Typical Key Fob Application for Full-duplex PEG, 433.92 MHzFigure 5-1 shows a typical 433.92 MHz PEG key fob application. The external components are 10 capacitors, 1 resistor, 1 inductor and a crystal. C 1 to C 3 are 68 nF voltage supply blocking capacitors. C 7 is a 10 nF supply blocking capacitor. C 4 is a 15 nF fixed capacitor used for the internal quasi-peak detector and for the high-pass frequency of the data filter. C 5, C 6, C 8 and C 9are RF matching capacitors in the range of 1 pF to 33 pF. L 2 is a feed inductor of about 120 nH. C 10 is a 10 nF capacitor which is necessary to prevent that signals couple into the pin R_PWR, causing amplitude modulation of the output power and a spurious rise of the transmitted signal. R 1 and C 10 should be placed close to the R_PWR pin. A load capacitor of 9 pF for the crystal is integrated. R 1 is typically 22 k Ω and SETPWR is programmed to get an output power of –7 dBm in full-duplex mode and 5 dBm in half-duplex mode. The quality factor of the loop antenna 1 is only reduced by the quality factor of L 2, the tolerances of C 9 and C 8 are thus important. The qual-ity factor of the loop antenna 2 is reduced to half due to the loading with the input impedance of RF_IN. With well designed loop antennas and the correct degree of overlapping, the isolation between RF_OUT and RF_IN is about 28 dB and the coupled output power from RF_OUT to RF_IN is about –35 dBm. The decoupling of two loop antennas situated close to each other is due to the effect that the magnetic flux from the part of loop antenna 1 that does not overlap and that of the overlapping part has an opposite direction. Depending on the relative position between the two antennas, a decoupling of 28 dB is achievable. Due to additional capacitive coupling between the loops the position of the components C 5, C 6 and C 8, C 9 are also important. The receive Sensitivity in full-duplex mode is reduced from –106 dBm without coupled RF-Power at RF_IN to –96 dBm with –35 dBm coupled RF power at RF_IN.94829C–RKE–09/05ATA5823/ATA58246.Typical Car Application for Full-duplex PEGFigure 6-1.Typical Car Application for Full-duplex PEG, 433.92 MHzFigure 6-1 shows a typical 433.92 MHz V CC = 4.4V to 5.25V PEG car application. The external components are 11 capacitors, 1 resistor, 3 inductors, a SAW Filter and a crystal. C 1, C 3 and C 4are 68 nF voltage supply blocking capacitors. C 2 is a 2.2 µF supply blocking capacitors for the internal voltage regulator. C5 is a 10 nF supply blocking capacitor. C 6 is a 15 nF fixed capacitor used for the internal quasi-peak detector and for the high-pass frequency of the data filter. C 7 to C 10 are RF matching capacitors in the range of 1 pF to 33 pF. L 1 is a feed inductor of about 120 nH, L 2 and L 3 are matching inductors to match the RX-antenna to the SAW and the SAW to RF_IN. A load capacitor of 9 pF for the crystal is integrated. C 11 is a 10 nF capacitor which is necessary to prevent that signals couple into the pin R_PWR, causing amplitude modulation of the output power and a spurious rise of the transmitted signal. R 1 and C 11 should be placed close to the R_PWR pin. R 1 is typically 22 k Ω and SETPWR is programmed to get an output power of 0 dBm in full-duplex mode and 5 dBm in half-duplex mode. The quality factor of the TX-loop antenna is only reduced by the quality factor of L 1, the tolerances of C 9 and C 10 are thus important. Since the 2 Antennas are located at different places the isolation between RF_OUT and RF_IN is about 45 dB and the coupled output power from RF_OUT to RF_IN is about –45 dBm. The receive Sensitivity in full-duplex mode is reduced from –106 dBm without coupled RF power at RF_IN to –102 dBm with –45 dBm coupled RF power at RF_IN. The use of SAW fil-ters in the full-duplex system is unsuitable due to the high group delay which desensitize the receiver.104829C–RKE–09/05ATA5823/ATA58247.RF Transceiver in Half-duplex ModeAccording to Figure 2-2 on page 5, the RF transceiver consists of an LNA (Low-Noise Amplifier), PA (Power Amplifier), RX/TX switch, fractional-N frequency synthesizer and the signal process-ing part with mixer, IF filter, IF amplifier with analog RSSI, FSK/ASK demodulator, data filter and data slicer.In receive mode the LNA pre-amplifies the received signal which is converted down to 226 kHz intermediate frequency (IF), filtered and amplified before it is fed into an FSK/ASK demodulator, data filter and data slicer. The RSSI (Received Signal Strength Indicator) signal and the raw dig-ital output signal of the demodulator are available at the pins RSSI and on TEST3 (open drain output). The demodulated data signal Demod_Out is fed into the digital control logic where it is evaluated and buffered as described in section “Digital Control Logic” on page 35.In transmit mode the fractional-N frequency synthesizer generates the TX frequency which is fed into the PA. In ASK mode the PA is modulated by the signal PA_Enable. In FSK mode the PA is enabled and the signal TX_DATA (FSK) modulates the fractional-N frequency synthesizer. The frequency deviation is digitally controlled and internally fixed to about ±19.5 kHz (see Table 9-1 on page 30 for exact values). The transmit data can also be buffered as described in section “Digital Control Logic” on page 35. A lock detector within the synthesizer ensures that the trans-mission will only start if the synthesizer is locked.In half-duplex mode the RX/TX switch can be used to combine the LNA input and the PA output to a single antenna with a minimum of losses. In full-duplex mode more isolation between receive and transmit antenna is needed, therefore two antennas have to be used.Transparent modes without buffering of RX and TX data are also available to allow protocols and coding schemes other than the internal supported Manchester encoding, like PWM and pulse position coding.7.1Low-IF ReceiverThe receive path consists of a fully integrated low-IF receiver. It fulfills the sensitivity, blocking, selectivity, supply voltage and supply current specification needed to manufacture an automo-tive key fob for RKE and PEG systems without the use of a SAW blocking filter (see Figure 3-1 on page 6 and Figure 5-1 on page 8). The receiver can be connected to the roof antenna in the car when using an additional blocking SAW front-end filter as shown in Figure 4-1 on page 7.At 433.92 MHz the receiver has a typical system noise figure of 6.5 dB, a system I1dBCP of –30 dBm and a system IIP3 of –20 dBm. The signal path is linear for disturbers up to the I1dBCP and there is hence no AGC or switching of the LNA needed to achieve a better blocking perfor-mance. This receiver uses an IF of about 226 kHz (see table “Electrical Characteristics” number 2.10 for exact values), the typical image rejection is 30 dB and the typical 3 dB system band-width is 220 kHz (f IF = 226 kHz ±110 kHz, f lo_IF = 116 kHz and f hi_IF = 336 kHz). The demodulator needs a signal to noise ratio of 8 dB for 20 kBaud Manchester with ±19.5 kHz fre-quency deviation in FSK mode, thus, the resulting sensitivity at 433.92 MHz is typically –105.5 dBm.Due to the low phase noise and spurious of the synthesizer in receive mode (1) together with the eighth order integrated IF filter the receiver has a better selectivity and blocking performance than more complex double superhet receivers, without using external components and without numerous spurious receiving frequencies.Note:1.–120 dBC/Hz at ±1 MHz and –72 dBC at ±f XTO at 433.92 MHz114829C–RKE–09/05 ATA5823/ATA5824A low-IF architecture is also less sensitive to second-order intermodulation (IIP2) than directconversion receivers where every pulse or amplitude modulated signal (especially the signalsfrom TDMA systems like GSM) demodulates to the receiving signal band at second-ordernon-linearities.7.2Input Matching at RF_INThe measured input impedances as well as the values of a parallel equivalent circuit of theseimpedances can be seen in Table 7-1. The highest sensitivity is achieved with power matchingof these impedances to the source impedance of 50Ω.The matching of the LNA Input to 50Ω was done with the circuit according to Figure 7-1 and withthe values of the matching elements given in Table 7-2. The reflection coefficients were always≤ –10 dB. Note that value changes of C 1 and L 1 may be necessary to compensate individualboard layout parasitics. The measured typical FSK and ASK Manchester code sensitivities witha Bit Error Rate (BER) of 10-3 are shown in Table 7-3 on page 12 and Table 7-4 on page 12.These measurements were done with multilayer inductors having quality factors according toTable 7-2, resulting in estimated matching losses of 0.8 dB at 315 MHz, 0.8 dB at 433.92 MHzand 0.7 dB at 868.3 MHz. These losses can be estimated when calculating the parallel equiva-lent resistance of the inductor with R loss = 2 × π × f × L × Q L and the matching loss with10 log(1+R In_p /R loss ).With an ideal inductor, for example, the sensitivity at 433.92 MHz/FSK/20 kBaud/±19.5 kHz/Manchester can be improved from –105.5 dBm to –106.7 dBm. The sensitivity alsodepends on the values in the registers of the control logic which examines the incoming datastream. The examination limits must be programmed in control registers 5 and 6. The measure-ments in Table 7-3 and Table 7-4 on page 12 are based on the values of registers 5 and 6according to Table 14-3 on page 60.Figure 7-1.Input Matching to 50Ω Table 7-1.Measured Input Impedances of the RF_IN Pinf RF /MHzZ In (RF_IN)R In_p //C In_p315(44-j233)Ω1278Ω//2.1 pF 433.92(32-j169)Ω925Ω//2.1 pF 868.3(21-j78)Ω311Ω//2.2 pF127.3Sensitivity versus Supply Voltage, Temperature and Frequency OffsetTo calculate the behavior of a transmission system it is important to know the reduction of thesensitivity due to several influences. The most important are frequency offset due to crystaloscillator (XTO) and crystal frequency (XTAL) errors, temperature and supply voltage depen-dency of the noise figure and IF filter bandwidth of the receiver. Figure 7-2 shows the typicalsensitivity at 433.92 MHz/FSK/20 kBaud/±19.5 kHz/Manchester versus the frequency offsetbetween transmitter and receiver at T amb = –40°C, +25°C and +105°C and supply voltageV S = V S1 = V S2 = 2.15V, 3.0V and 3.6V.Figure 7-2.Measured Sensitivity 433.92 MHz/FSK/20 kBaud/±19.5 kHz/Manchester versus Frequency Offset, Temper-ature and Supply VoltageTable 7-2.Input Matching to 50Ωf RF /MHz C 1/pF L 1/nH Q L1315 2.44765433.92 1.82767868.3 1.2 6.8 50Table 7-3.Measured Typical Sensitivity 433.92 MHz, FSK, ±19.5 kHz, Manchester, BER = 10-3RF Frequency BR_Range_01.0 kBaud BR_Range_02.4 kBaud BR_Range_15.0 kBaud BR_Range_210 kBaud BR_Range_320 kBaud315 MHz –109.5 dBm –110.0 dBm –109.0 dBm –107.5 dBm –106.5 dBm433.92 MHz –108.5 dBm –109.0 dBm –108.0 dBm –106.5 dBm –105.5 dBm868.3 MHz –105.5 dBm –106.5 dBm –105.5 dBm –103.5 dBm –103.0 dBmTable 7-4.Measured Typical Sensitivity 433.92 MHz, 100% ASK, Manchester, BER = 10-3RF Frequency BR_Range_01.0 kBaud BR_Range_02.4 kBaud BR_Range_15.0 kBaud BR_Range_210 kBaud315 MHz –117.0 dBm –117.0 dBm –114.5 dBm –112.5 dBm433.92 MHz –116.0 dBm –116.0 dBm –113.5 dBm –111.5 dBm868.3 MHz –113.0 dBm –113.0 dBm –111.5 dBm –109.0 dBm134829C–RKE–09/05 ATA5823/ATA5824As can be seen in Figure 7-2 on page 12 the supply voltage has almost no influence on the sen-sitivity. The temperature has an influence of about +1.5/–0.7 dB and a frequency offset of±85 kHz also influences by about ±1 dB. All these influences, combined with the sensitivity of atypical IC (–105.5dBm), are then within a range of –102.5 dBm and –107 dBm overtemperature,supply voltage and frequency offset. The integrated IF filter has an additional production toler-ance of ±10 kHz, hence, a frequency offset between the receiver and the transmitter of ±75 kHzcan be accepted for XTAL and XTO tolerances.Note:For the demodulator used in the ATA5823/ATA5824, the tolerable frequency offset does notchange with the data frequency, hence, the value of ±75 kHz is valid for 1 kBaud to 20 kBaud.This small sensitivity change over supply voltage, frequency offset and temperature is veryunusual in such a receiver. It is achieved by an internal, very fast and automatic frequency cor-rection in the FSK demodulator after the IF filter, which leads to a higher system margin. Thisfrequency correction tracks the input frequency very quickly, if however, the input frequencymakes a larger step (e.g., if the system changes between different communication partners), thereceiver has to be restarted. This can be done by switching back to IDLE mode and then againto RX mode. For that purpose, an automatic mode is also available. This automatic modeswitches to IDLE mode and back into RX mode every time a bit error occurs (see section “DigitalControl Logic” on page 35).7.4Frequency Accuracy of the Crystals in Bi-directional RKE/PEGThe XTO is an amplitude regulated Pierce type oscillator with integrated load capacitors. The ini-tial tolerances (due to the frequency tolerance of the XTAL, the integrated capacitors on XTAL1,XTAL2 and the XTO’s initial transconductance gm) can be compensated to a value within±0.5 ppm by measuring the CLK output frequency and tuning of f RF by programming the controlregisters 2 and 3 (see Table 12-7 on page 38 and Table 12-10 on page 39). The XTO then hasa remaining influence of less than ±2 ppm overtemperature and supply voltage due to the band-gap controlled gm of the XTO. Thus only 2.5 ppm add to the frequency stability of the usedcrystals overtemperature and aging.The needed frequency stability of the used crystals overtemperature and aging is hence±75 k H z /433.92 M H z – 2 × ±2.5 p p m = ±167.84 p p m f o r 433.92 M H z a n d±75 kHz/868.3 MHz – 2 × ±2.5 ppm = ±81.4 ppm for 868.3 MHz. Thus, the used crystals inreceiver and transmitter each need to be better than ±83.9 ppm for 433.92 MHz and ±40.7 ppmfor 868.3 MHz.7.5Frequency Accuracy of the Crystals in a Combined RKE/PEG and TPM SystemIn a tire pressure measurement system working at 433.92 MHz and using a TPM transmitterATA5757 and a transceiver ATA5824 as a receiver, the higher frequency tolerances and the tol-erance of the frequency deviation of this transmitter has to be considered.In the TPM transmitter the crystal has an frequency error overtemperature –40°C to +125°C,aging and tolerance of ±80 ppm (±34.7 kHz at 433.92 MHz). The tolerances of the XTO, thecapacitors used for FSK-Modulation and the stray capacitors, causing an additional frequencyerror of ±30 ppm (±13 kHz at 433.92 MHz). The frequency deviation of such a transmitter variesbetween ±16 kHz and ±24 kHz, since a higher frequency deviation is equivalent to an frequencyerror, this has to be considered as an additional ±24 kHz – ±19.5 kHz = ±4.5kHz frequency tol-erance. All tolerances added, these transmitters have a worst case frequency offset of±52.2 kHz.144829C–RKE–09/05ATA5823/ATA5824For the transceiver in the car a tolerance of ±75 kHz – ±52.2 kHz = ±22.8 kHz (±52.5 ppm)remains. The needed frequency stability of the used crystals overtemperature and aging is ±52.5 ppm – ±2.5 ppm = ±50 ppm. The aging of such a crystal is ±10 ppm leaving reasonable ±40 ppm for the temperature dependency of the crystal frequency in the car.Since the transceiver in the car is able to receive these TPM transmitter signals with high fre-quency offsets, the component specification in the key can be largely relaxed.This system calculation is based on worst case tolerances of all the components, this leads in practice to a system with margin.For a 315 MHz TPM system using a TPM transmitter ATA5756 and a transceiver ATA5823 as receiver the same calculation must be done, but since the RF frequency is lower, every ppm of crystal tolerances results in less frequency offset and either the system can have higher toler-ances or a higher margin there.For 868 MHz it is not possible to use the transceiver ATA5824 in a combined RKE/PEG and TPM system since all the tolerances double because of the higher RF frequency.7.6RX Supply Current versus Temperature and Supply VoltageTable 7-5 shows the typical supply current at 433.92 MHz of the transceiver in RX mode versus supply voltage and temperature with V S = V S1 = V S2. As can be seen the supply current at V S = 2.15V and T amb = –40°C is less than at V S = 3V/T amb = 25° which helps to enlarge the bat-tery lifetime within a key fob application because this is also the operation point where a lithium cell has the worst performance. The typical supply current at 315 MHz or 868.3 MHz in RX mode is about the same as for 433.92 MHz.7.7Blocking, SelectivityAs can be seen in Figure 7-3, Figure 7-4 and Figure 7-5 on page 15, the receiver can receive signals 3 dB higher than the sensitivity level in presence of large blockers of –44.5 dBm/-36.0 dBm with small frequency offsets of ±1/±10 MHz.Figure 7-3 and Figure 7-4 on page 15 shows the close-in and narrow-band blocking and Figure 7-5 on page 15 the wide-band blocking characteristic. The measurements were done with a use-ful s ignal of 433.92 MHz/FSK/20 kBaud/±19.5 kHz/Manc hester with a level of –105.5 dBm + 3 dB = –102.5 dBm which is 3 dB above the sensitivity level. The figures show by how much a continuous wave signal can be larger than –102.5 dBm until the BER is higher than10-3. The measurements were done at the 50Ω input according to Figure 7-1 on page 11. At 1 MHz, for example, the blocker can be 58 dBC higher than –102.5 dBm which is –102.5 dBm +58 dBC = –44.5 dBm. These blocking figures, together with the good intermodulation perfor-mance, avoid the additional need of a SAW filter in the key fob application.Table 7-5.Measured 433.92 MHz Receive Supply Current in FSK mode V S = V S1 = V S2 2.15V 3.0V 3.6VT amb = –40°C 8.2 mA 8.8 mA 9.2 mAT amb = 25°C 9.7 mA 10.3 mA 10.8 mAT amb = 105°C 11.2 mA 11.9 mA 12.4 mA。

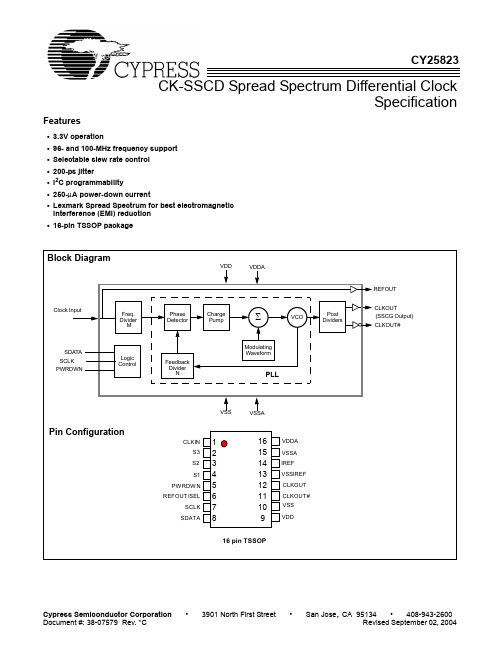

CY25823ZXCT资料