VHDL运算符重载overload

VHDL语言的基本要素(大全)

VHDL语言的基本要素一、数据对象VHDL语言的主要数据对象有信号,变量,常量。

信号—信号是电路中的物理量,对应于电路的连线、节点;信号说明全局量,用于描述中的构造体(Architecture), 实体(Intity),程序包(package)。

变量—变量是程序运算中的中间量,并不对应电路中的物理量。

变量说明局部量,用于进程语句(process), 函数(Function), 过程(procedure)。

常量—常数也不对应电路中的物理量,当常量说明全局量,在构造体(Architecture), 实体(Intity),程序包(package),进程语句(process), 函数(Function), 过程(procedure)中均可使用。

数据对象的定义格式:signal 信号名:数据类型,约束条件,表达式Variable 变量名:数据类型,约束条件:=表达式Constant 常量名:数据类型,约束条件:=表达式例如:Variable count:INTEGER RANGE 0 TO 255:=10Constant Daly:Time:=100ns信号代入和变量赋值的区别:两者形式不同,操作过程也不相同。

变量赋值符“:=”,信号的代入符“<=”。

在变量的赋值语句中,该语句一当执行,其值立即将赋予变量;而信号的代入,其语句执行后不会立即使信号发生代入,在下条语句执行时,仍使用原来的信号值,如进程语句中的敏感表的信号代入就是如此。

二、数据类型VHDL语言中的数据类型,一般而言可分为:标量类型和组合类型。

在实际使用中,也可分成予定义类型和用户定义类型。

VHDL语言是强类型的语言,主要可按如下分类和变换处理。

①标准数据类型⑴整数⑵实数(浮点数)-1.0E+38~+1.0E38 ⑶位bit(0,1)⑷位矢量⑸布尔量,“假”,“真”⑹字符(ASCⅡ)字符⑺时间⑻错误等级⑼自然数(大于等于0的整数)⑽字符串(字符矢量)②用户定义的数据类型TYPE 数据类型名{数据类型名} 数据类型定义⑴枚举类型⑵整数类型⑶实数类型⑷数组类型⑸存取类型⑹文件类型⑺记录类型⑻时间类型③用户定义子类型SUBTUPE 子类型名IS 数据类型名[范围]例:SUBTYPE digit is INTEGER RANGE 0 TO 9④数据类型转换数据类型的变换函数通常由“STD_LOGIC_1164”,“STD_LOGIC_ARITH”,“STD_LOGIC_UNSIGNED”的程序包提供例如,在STD_LOGIC_1164程序包中,TO_STD LOGIC VECTOR(A) 由BIT_VECTOR转换为STD_LOGIC_VECTORTO_BITVECTOR(A) 由STO_LOGIC_VECTOR转为BIT_VECTORTO_STDLOGIC(A) 由BIT转换为STD_LOGICTO_BIT(A) 由STD_LOGIC转换成BIT signal a: BIT_VECTOR(11 DOWNTO 0)signal b: STD_LOGIC_VECTOR(11 DOWNTO 0)a<=X”A8” 十六进制值可赋予位矢量b<=X”A8” 语法错,十六进制不能赋予.STD 矢量b<=TO_STDLOGICVECTOR(X“AF7”)b<=TO_STDLOGICVECTOR(O“5177”)八进制变换b<=TO_STDLOGICVECTCR(B“1010_1111_0111”)下表中也给出一些典型的类型变换函数三、运算符运算符的优先级如下表所示:运算符的优先级例如,并置运算符的使用:tmp_b<=b AND (en&en&en&en) y <= a & tmp_b第一个语句表示b 的4位位矢量由en 进行选择 得到一个4位位矢量输出第二个语句表示4位位矢量a 和4位位矢量b 再 次连接(并置)构成8位的位矢量y 输出 右图所示为并置运算符操作的电路示意。

(三)VHDL语言的数据类型及运算操作符090914(119)

5. 布尔量(Boolean)

一个布尔量具有两种状态,“真”或者“假”。虽然布尔量也是 二值枚举量,但它和位不同,没有数值的含义,也不能进行算术 运算。它能进行关系运算。例如,它可以在IF语句中被测试,测 试结果产生一个布尔量TRUE或者FALSE。 一个布尔量常用来表示信号的状态或者总线上的情况。如果 某个信号或者变量被定义为布尔量,那么在仿真中将自动地对其 赋值进行核查。这一类型的数据的初始值一般总为FALSE。

【例3-1-b】

PROCESS( A, B, C)

VARIABLE D:STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

D:=A; X<=B+D;

结果:X<=B+A; Y<=B+C;

D:=C;

Y<=B+D;

END PROCESS;

进程内的语句是顺序执行的, 由于D是变量,在执行 D:=A后,D=A,接着执行X<=B+D,使得在退出进程后 X=B+A 。接着执行D:=C 和 Y<=B+D ,使D=C,退出时, Y=B+C。

信号赋值语句举例: X<= y; a <= ‘1’; s1 <= s2 AFTER 10 ns;

3.1.4 信号和变量的主要区别

1) 赋值符不同 信号和变量的赋值符不同,如果一个值要赋给信号应用

代入符“<=”;而变量赋值则用赋值符“:=”。

信号和变量可以互相赋值,此时赋值符应根据左边被赋 值量的类型来确定。如果被赋值是信号应用代入符“<=”;如 果是变量,则应用赋值符“:=”。

例如: CONSTANT VCC: REAL:=5.0; CONSTANT DALY: TIME:=100 ns; CONSTANT FBUS: BIT_VECTOR:="0101";

VHDL数据类型和运算符

-(2^31-1) to +(2^31-1) -1.0E+38 to +1.0E+38 ‘0’ ‘1’ “000” true false ‘A’ “abcd” 20 us

2011/6/13

11

VHDL语言的数据类型

整数

整数范围 -(2^31-1) to +(2^31-1)

不能看作矢量, 不能单独对某一位操作

2011/6/13

22

用户定义的数据类型

TYPE 数据类型名 IS 数据类型定义;

枚举类型 数组 记录类型 文件 时间 用户自定义的整数,实数 用户自定义的子类型

2011/6/13

23

用户定义的数据类型

枚举类型

TYPE 数据类型名 IS (元素,元素…..)

Type week IS (sun,mon,tue,wed,thu,fri,sat) Type std_logic IS (‘U’, ‘X’, ‘0’, ‘1’, ‘Z’, ‘W’, ‘L’ ,‘H’, ‘-’) Type bit IS (‘0’, ‘1’)

转换为integer

31

VHDL语言的客体及其分类

常数constant、变量variable、信号量signal

VHDL语言的数据类型

标准的数据类型

用户定义的数据类型

IEEE STD 1164 标准 数据类型的转换

VHDL语言的运算操作符

逻辑、算术、关系、并置

客体的属性描述

2011/6/13

32

(信号的代入)

Signal B : Std_logic; (信号的定义)

B <= ‘Z’;

(信号的代入)

B <= A(0);

第三章VHDL语言数据类型及运算操作符

实数常量的书写方式举例

65971.333333

--十进制浮点数

8#43.6E+4#

--八进制浮点数

43.6E-4

--十进制浮点数

第三章VHDL语言数据类型及运算操作符

3、位(BIT)数据类型

位数据类型也属于枚举型,取值只能是1 或0。位数据类型的数据对象,如变量、信 号等,可以参与逻辑运算,运算结果仍是 位的数据类型。VHDL综合器用一个二进制 位表示BIT。在程序包STANDARD中定义 的源代码是:

第三章VHDL语言数据类型及运算操作符

总结:

在运行中不变,若要改变必须要改变设计, 也就是说改变常量说明,重新编译。

常量必须在程序的实体、结构体或过程的 说明区中,对其标识符类型常量值进行指 定。

定义在实体中的常量仅在实体中使用。以 此类推。

第三章VHDL语言数据类型及运算操作符

3.1.2变量(Variable)

线)信号,共有16个信号元素

第三章VHDL语言数据类型及运算操作符

以下示例定义的信号数据类型是设计者自 行定义的,这是VHDL所允许的:

TYPE FOUR IS(‘X’,‘0’,‘I’, ‘Z’);

SIGNAL S1﹕FOUR; SIGNAL S2﹕FOUR:=‘X’; SIGNAL S3﹕FOUR:=‘L’;

第三章VHDL语言数据类型及运算操作符

格式: CONSTANT 常数名:数据类型:=表达式; 例: CONSTANT VCC: REAL:=5.0; CONSTANT DALY:TIME:=100ns; CONSTANT BUS:BIT_VECTOR:=“1010 ” CONSTANT G1:BIT:= ‘ 1’; 数据类型和表达式表示的数据类型应该一致。 ‘ ’表示是位信息, 而 “ ”表示的是位矢量

运算符重载

{

rpart=rp;

ipart=ip;

}

Complex add( const Complex & com )

{

Complex temp ;

temp .rpart= com .rpart+rpart;

temp .ipart= com .ip+ipart;

return temp ;

}

2020/7/2

பைடு நூலகம்};

★单目运算符重载 :

Complex Complex:: operator {

Complex temp;

( 单) 目无参数 双目一个参数

temp.rpart=-rpart;

temp.ipart)=-ipart;

return temp;

}

Complex c=-a+b;

(a.operator-( )).operator+(b)

};

point point::operator+ (point p1)

{ point p; p.x=x+p1.x; p.y=y+p1.y; return p; }

void main()

{ point p1(10,10),p2(20,20); p1=p1+p2 ;

p1.print(); ++p1; p1.print();

}

//(╳)

运算符成员函数——调用成员函数的对象隐式成为表达式的第一个运算数 外部运算符函数——其第一个参数直接对应表达式的第一个运算数;

x1=x2+x3;

operator+(x2, x3);

2020/7/2

6 6

VHDL运算符重载overload

包集合中定义了很多重载运算符(重载函数):

一元: asb,运算:+,-,*,/,ret;,>=,<=

逻辑:not,and,or,nand,nor,xor,xnor 移位:shift_left,shift_right,rotate_left, rotate_right,sll,srl,rol,ror ★同一函数名可能在不同的包集合中定义了不同的函数,具体用哪一函数就要 将其所在的包集合在文件头声明。 例如:运算符“+”在包集合IEEE.numeric_bit,IEEE. std_logic_unsigned, IEEE. std_logic_signed中都有定义。

运算符重载重载函数指两个或两个以上的函数具有相同的函数名而操作数的数据类型有差别足以区分实际想要的函数

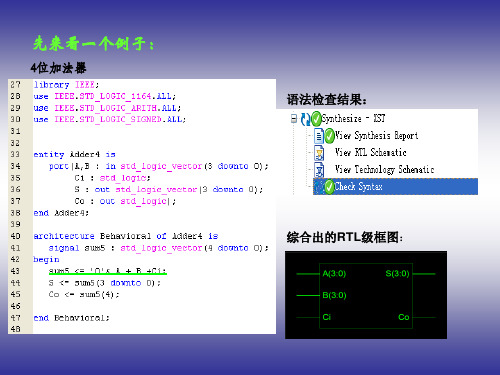

先来看一个例子:

4位加法器 语法检查结果:

综合出的RTL级框图:

关于“+”函数:

相同的函数名“+”居然 可以有不同的操作数?

从包集合中看一看函数“+” 到底是怎么回事

Std_logic_unsigned包集合中的“+”函数:

刚才的4位加法器:

std_logic类型换为bit类型

自定义重载运算符(重载函数):

在包集合中定义重载函数:

刚才的4位加法器:

声明自定义的包集合

编译通过:

该函数将bit型转换为 std_logic子类型

总结:

同名不同人,不同的人做不同的事,用 到谁时谁上;

我们是女娲,也能造自己需要的人。

谢谢大家

概念:

运算符重载(重载函数)指两个或两个以上的函数具有相同的函数

名,而操作数的数据类型有差别,足以区分实际想要的函数。 ★ 由编译器根据操作数的数据类型来判断用那一函数

EDA第4章 VHDL基础文字规则与操作符(4.3-4.4)

第4章

VHDL基础

第4章

VHDL基础

变量数值的改变是通过变量赋值来实现的,其赋 值语句的语法格式如下: 目标变量名:=表达式; 如: VARIABLE A,B:BIT_VECTOR(0 TO 7); VARIABLE X,Y: REAL; X:=1.2; Y:=100.1+X; A:=“10101011”; A(7):=‘0’;

第4章

VHDL基础

• 常量、信号、变量的使用比较

• (1) 从硬件电路系统来看,常量相当于电路中的恒定 电平,如GND或VCC接口,而变量和信号则相当于组合 电路系统中门与门间的连接及其连线上的信号值。 • (2) 从行为仿真和VHDL语句功能上看,信号和变量的 区别主要表现在接受和保持信息的方式、信息保持与 传递的区域大小上。 • (3) 从综合后所对应的硬件电路结构来看,信号一般 将对应更多的硬件结构,但在许多情况下,信号和变 量并没有什么区别。 • (4) 虽然VHDL仿真器允许变量和信号设置初始值,但 在实际应用中,VHDL综合器并不会把这些信息综合进 去。

第4章

VHDL基础

5.段名

对应数组中某一段元素,是多个下标名的组合。表达形式: 标识符(表达式 方向 表达式) 方向----To 由低到高 DOWNTO 由高到低 如:signal a, z: bit_vector(0 to 7);-- 8位位矢量 z(0 to 3)<=a(4 to 7); --以段的方式进行赋值 z(4 to 7)<=a(0 to 3); --以段的方式进行赋值

第10讲 VHDL的运算符1

本讲知识点: 算术运算符

逻辑运算符

运算符

VHale Waihona Puke DL中共有四类操作符:逻辑操作符、关系操作符、算术操作符和连接操 作符

操作符和操作数间的运算应注意: o 基本操作符间操作数是同数据类型 o 操作数的数据类型必须与操作符所要求的数据类 型一致

o

注意操作符之间的优先级

o 通常在一个表达式中有两个以上的算符时,需 要使用括号将这些运算分组,若其中的算符相同且 为AND、OR、XOR 中的一种则不需使用括号。

2、算术运算符 VHDL的算术运算符共有十几种,其中常用的有如下 几种: 操作符 功能 操作数类型 + 加法 整数 - 减法 整数 * 乘法 整数和实数 SLL等 移位 bit或布尔类型的 一维数组 (SLL SLR SLA SRA ROL ROR)

在运用算术运算符对如下的数据类型进行运算 时,应注意: (1)unsigned, signed:需打开 std_logic_arith程序包; (2)std_logic:需打开std_logic_unsigned 或std_logic_signed 程序包;

5. 移位操作符

1. 求和操作符

2. 求积操作符

*(乘)、 /(除)、 MOD(取模) 、 RED(取余)

3. 符号操作符

maxplus2不支持“MOD”、“RED”运算

“+”和“-”

4. 混合操作符

“**” “ABS”

5. 移位操作符

SLL、SRL、SLA、SRA、ROL 、ROR 移位操作符的语句格式是: 标识符 移位操作符 移位位数 ; 要求操作数的数据类型必须为1维数组,元素必须为 bit或BOOLEAN类型;操作符右边必须为整形。 逻辑左移和右移:移空的位用0填补; 逻辑左、右环移:数据内环行移动。 算术左、右移:其移空的为用最初的首位填补。

简述运算符重载的规则。

简述运算符重载的规则。

篇一:运算符重载是C/C++语言中一种强大的功能,允许程序员自定义函数的行为,以处理不同类型的数据。

运算符重载允许程序员在函数中重载算术、逻辑和位运算符,从而能够处理数组、结构体和指针等不同类型的数据。

以下是运算符重载的规则:1. 算术运算符重载算术运算符包括加号、减号、乘号和除号。

每个算术运算符都有一组默认的行为,可以通过运算符重载来自定义它们的行为。

例如,重载加号运算符可以使函数接受一个整数参数,并返回一个新的整数。

下面是一个简单的例子,演示了如何重载加号运算符:```c++struct MyStruct {int value;};MyStruct operator+(const MyStruct& other, int value) {return MyStruct(value + other.value);}int main() {MyStruct mystruct1 = { 10 };MyStruct mystruct2 = { 20 };int result = mystruct1 + mystruct2;std::cout << "result = " << result << std::endl;return 0;}```在上面的例子中,我们定义了一个名为`MyStruct`的结构体类型,其中包含一个整数类型。

然后,我们定义了一个重载加号运算符的函数,该函数接受一个整数类型的参数,并返回一个新的`MyStruct`对象。

在`main`函数中,我们定义了两个`MyStruct`对象`mystruct1`和`mystruct2`,并将它们相加,结果存储在`result`变量中。

2. 逻辑运算符重载逻辑运算符包括条件运算符和逻辑非运算符。

每个逻辑运算符都有一组默认的行为,可以通过运算符重载来自定义它们的行为。

VHDL 操作符

EDA技术实用教程

VHDL操作符

1.3 算术操作符

2. 求积操作符

* (乘)、 / (除)、 MOD (取模) 、RED (取余)

3. 符号操作符

“ + ”、“ - ”

VHDL操作符

1.3 算术操作符

4. 混合操作符

“ ** ”、“ ABS ”

【例8-22】 SIGNAL a,b : INTEGER RANGE -8 to 7 ; SIGNAL c : INTEGER RANGE 0 to 15 ; SIGNAL d : INTEGER RANGE 0 to 3 ; a <= ABS(b) ;

严格遵循在基本操作符间操作数是同数据类型的规则。 严格遵循操作数的数据类型必须与操作符所要求的数据类 型完全一致。

类型 算术操作符

操作符 + - & * / MOD REM SLL SRL SLA SRA ROL ROR ** ABS

表8-1 VHDL操作符列表

功能

操作数数据类型

加整数Βιβλιοθήκη 减整数并置

一维数组

port ( input: IN STD_LOGIC_VECTOR (2 DOWNTO 0); output: OUT BIT_VECTOR (7 DOWNTO 0));

END decoder3to8; ARCHITECTURE behave OF decoder3to8 IS BEGIN output <= "00000001" SLL CONV_INTEGER(input); --被移位部分是常数! END behave;

SIGNAL l,m,n,o,p : BOOLEAN ;

...

清华大学Overload_Operator-C++运算符重载课件

运算符重载运算符重载的方法是定义一个重载运算符的函数,在需要执行被重载的运算符时,系统就自动调用该函数,以实现相应的运算。

也就是说,运算符重载是通过定义函数实现的。

1 运算符重载为成员函数 AX++运算符重载实质上是函数的重载,重载运算符的函数一般格式如下:函数类型 operator运算符名称(形参表列){对运算符的重载处理}例如,想将“+”用于Complex(复数)的加法运算,函数的原型可以是这样的:Complex operator + (Complex & c1,Complex &c2);其中,operator是关键字,是专门用于定义重载运算符的函数的,运算符名称就是C++提供给用户的预定运算符。

注意:函数名是由operator和运算符组成。

上面的operator+就是函数名,意思是“对运算符+重载“。

只要掌握这点,这可以发现,这类函数和其他函数在形式上没有什么区别。

两个形参是Complex类对象的引用,要求实参为Complex类对象。

在定义了重载运算符后,可以说:函数operator+重载了运算符+。

在执行复数相加的表达式c1+c2时(假设c1+c2都已被定义为Complex),系统就会调用operator+函数,把c1+c2作为实参,与形参进行虚实结合。

为了说明把运算符重载后,执行表达式就是调用函数的过程,可以把两个整数相加也想象称为调用下面的函数:代码如下:int operator + (int a, int b) { return (a+b); }如果有表达式5+8,就调用此函数,将5和8作为调用函数时的形参,函数的返回值为13,这就是通过函数的方法理解运算符。

例1:运算符重载实现两个坐标点的加运算class Point {int x, y;public:Point() {}Point (int I, int j) { x=i; y=j;}v oid disp() {cout << “(“ << x <<”,”<<y<<”)”<<endl;}Point operator+ (Point &p) {return Point(x+p.x, y+p.y);}};void main() {Point p1(3,4), p2(2,9), p3;p3=p1+p2;p3.disp();}例2:运算符重载实现复数的加、减、乘、除和赋值运算。

VHDL的运算符号解析

VHDL的运算符号VHDL中主要有六类运算符号:赋值运算、逻辑运算、算术运算关系运算、连接运算、移位运算运算符号主要用于各类表达式中;运算可以分为单目运算(只有一个运算量)和双目运算(针对两个运算量);进行双目运算时,两个运算量必须类型相同;VHDL中运算没有左右优先级差别,同一表达式中进行多个运算时必须用括号表达先后差别;在同类运算中,单目运算优先;在所有运算符号中,NOT的优先级别最高;在一般运算中,优先顺序排列为:算术—关系—逻辑可以通过加括号来改变运算的优先顺序;赋值运算符<= 信号赋值:将右端值赋给左端信号;:= 变量赋值:将右端值赋给左端变量;或用于赋初始值;=> 数组内部分元素赋值;适用类型:所有数据类型;赋值号两边的数据类型原则上应该相同;逻辑运算符NOT AND OR NAND NOR XOR适用类型:STD_LOGIC STD_LOGIC_VECTORBIT BIT_VECTOR BOOLEAN逻辑运算结果为同类型逻辑量;对数组类型进行逻辑运算时,参与运算的两个数据位数必须相等,所做运算为对应位进行;算术运算:/ (除)* (乘) + (加)- (减)MOD(求模)REM(取余)**(指数) ABS(绝对值)适用类型:INTEGER REAL BIT BIT_VECTOR TIME加/减运算的结果为同类型算术量;注意:算术运算大多数只用于抽象的编程(行为设计);只有少数算术运算符能够进行综合,应尽量只使用加/减;对数组类型进行算术运算时,两边位数必须相同;关系运算:=> (大于等于)<= (小于等于)> (大于)< (小于) /= (不等于)= (等于)适用类型:等于和不等于适用于所有类型;其他运算适用于整数、实数、位、位矢量,以及枚举类型和数组类型;可比较位长度不相同的情况(从左向右逐位比较);关系运算的结果为boolean类型: false true注意:小于等于符号与信号赋值符号的写法相同,应注意使用位置和意义;连接运算:&适用类型bit bitvector character stringstd_logic std_logic_vector连接运算结果为同类型元素构成的数组;库和包集合除了实体、结构体外的第三种可编程结构Library 库编译后数据的集合,存放包集合定义、实体定义、构造体定义和配置定义,其功能相当于其他操作系统中的目录,经过说明后,设计中就可以使用库中的数据,实现共享;在前面图形输入的应用中,已多次采用库中的单元进行设计;库的使用:当使用库时,需要说明使用的库名称,同时需要说明库中包集合的名称及范围;每个实体都应独立进行库的说明;库的说明应该在实体之前;经过说明后,实体和结构体就可以自动调用库中的资源;库说明语句格式library 库名;use 库名.包集合名.范围(或项目名);例: library ieee;use ieee.std_logic_1164.all;VHDL中库的主要种类:IEEE库STD库ASIC库work库用户定义库IEEE库:含有IEEE的标准包集合“STD_LOGIC_1164”以及一些大公司提供的包集合;使用前必须说明;例:library ieee;use ieee.std_logic_1164.all; 使用标准逻辑量的定义和运算;use ieee.std_logic_unsigned.all; 无符号数算术运算的定义;use ieee.std_logic_arith.all; 使用符号数算术运算的定义;STD库:含有“STANDARD”包集合和“TEXTIO”包集合,使用前者时无需说明;ASIC库:由各公司提供,存放与逻辑门一一对应的实体,用于ASIC 设计的门级仿真,使用时需加以说明;例library altera;use altera.maxplus2.all;library lpm;use lpm.lpm_components.all;WORK库:WORK库为现行作业库,位于当前使用时设计文件的指定保存目录;WORK使用时通常无须说明;但在结构设计中进行元件的宏调用时需要说明;例:use work.all;用户定义库:由用户自定义生成,使用时需说明(指定库所在的路径);package 包集合用于罗列VHDL语言中使用的类型定义、信号定义、常数定义、元件定义、函数定义和过程定义等(类似于C语言中的include语句),方便不同模块的设计中公共定义的共享;数字电路设计中经常使用的包集合:ieee.std_logic_1164 逻辑量的定义ieee.std_logic_arith 数据转换,逻辑判断ieee.std_logic_unsigned 算术运算std.textio 文本数据输入/输出格式包集合在使用前必须采用use语句进行说明(在设计程序的最前面);包集合可以由用户自定义;包的结构与定义:(用户自定义的包集合)包集合标题+(包集合体)包集合标题:package 包集合名 is说明语句;(只有名称)end 包集合名;包集合体:package body包集合名 is说明语句;(完整定义)end 包集合名;例:(函数取自p.279 表4-38 )library ieee;use ieee.std_logic_1164.all;packge upac isconstant k: integer := 4;subtype cpu_bus is std_logic_vector(k-1downto 0); function conv_integer (x:std_logic_vector) return integer; end upac;packge body upac isfunction conv_integer (x: std_logic_vector) return integer is variable result: integer;beginresult := 0;for I in x'range loopresult :=result*2;case x(i) iswhen '0'|'L' => null;when '1'|'H' => result := result+1;when others => null;end case;end loop;return result;end conv_integer;end upac;用户自行编写的包集合将自动存放于WORK库中,使用时可采用下列语句调用use work.upac.all;configuration 配置在一个实体内可以编写多种不同的构造体,通过配置语句来进行选择;配置语句格式:configuration 配置名 of 实体名 isfor 选择的构造体名end for;end 配置名;此语句可以为设计增加更大的灵活性,可以对不同构造体进行比较。

运算符重载

sizeof (长度运算符)

(3) 重载运算符的函数不能有默认的参数,否则就改变了 运算符参数的个数。 (4) 重载的运算符必须和用户自定义类型的对象一起使用, 其参数至少应有一个是类对象(或类对象的引用)。也 就是说,参数不能全部是C++的标准类型,以防止用 户修改用于标准类型数据的运算符的性质。

operator+(Complex &c2),进行求值,得到两 个复数之和。

为了重载运算符,必须定义一个函数,并告诉编译器, 遇到这个重载运算符就调用该函数,由这个函数来完成 该运算符应该完成的操作。 这种函数称为运算符重载函数,它通常是类的成员函数 或者是友元函数。 运算符的操作数通常也应该是类的对象。 运算符被重载后,其原有的功能仍然保留,没有丧失或 改变。 通过运算符重载,扩大了C++已有运算符的作用范围, 使之能用于类对象。

void String∷display( ) { cout<<p;}l operator>(String &string1,String &string2) 函数 { if(strcmp(string1.p,string2.p)>0) return true; else return false; } int main( ) { String string1(″Hello″),string2(″Book″); cout<<(string1>string2)<<endl; }

//定义3个复数对象 //调用复数相加函数 //输出c1的值 //输出c2的值 //输出c3的值

调用方式不直观、不方便、太烦琐。

能否也和整数的加法运算一样,直接用加号“+”

第七章第三部分VHDL语言的数据类型和运算操作符号

2) 位(BIT)数据类型

位数据类型也属于枚举型,取值只 能是1或0。位数据类型的数据对象,如 变量、信号等,可以参与逻辑运算,运 算结果仍是位的数据类型。VHDL综合器 用一个二进制位表示BIT。在程序包 STANDARD中定义的源代码是:

10) 错误等级(SEVERITY_LEVEL)

在VHDL仿真器中,错误等级用来指示设计系统的工作状态, 共有四种可能的状态值:NOTE(注意)、WARNING(警告)、 ERROR(出错)、FAILURE(失败)。在仿真过程中,可输出这四种 值来提示被仿真系统当前的工作情况。其定义如下:

3.2.1、 VHDL的预定义数据类型

1) 布尔(BOOLEAN)数据类型 程序包STANDARD中定义布尔数据类型的源代码如下:

TYPE BOOLEAN IS(FALES,TRUE); 布尔数据类型实际上是一个二值枚举型数据

类型,它的取值有FALSE和TRUE两种。综合器将用 一个二进制位表示BOOLEAN型变量或信号。

3、从综合后所对应的硬件电路结构来看,信 号一般将对应更多的硬件结构,但在许多情况 下,信号和变量并没有什么区别。例如在满足 一定条件的进程中,综合后它们都能引入寄存 器。这时它们都具有能够接受赋值这一重要的 共性,而VHDL综合器并不理会它们在接受赋 值时存在的延时特性。

4、虽然VHDL仿真器允许变量和信号设置初 始值,但在实际应用中,VHDL综合器并不会 把这些信息综合进去。这是因为实际的 FPGA/CPLD芯片在上电后,并不能确保其初 始状态的取向。因此,对于时序仿真来说,设 置的初始值在综合时是没有实际意义的。

第3章 VHDL编程基础B

VHDL 编程基础

【例3.6.5】过程声明 PROCEDURE PRO1(VARIABLE A,B:INOUT REAL); PROCEDURE PRO2 (CONSTANT A1:IN INTEGER; VARIABLE B1:OUT INTEGER); PROCEDURE PRO3 (SIGNAL S1:INOUT BIT); 【例3.6.1】函数声明 FUNCTION FUNC1(A,B,C:REAL) RETURN REAL; FUNCTION “*” (A,B:INTEGER) RETURN INTEGER; --注意函数名*要用引号括住 FUNCTION AS2(SIGNAL IN1,IN2:REAL) RETURN REAL; --注意信号参量的写法 以上是三个不同的函数首,它们都放在某一程序包的说明部分。

type small is range 0 to 100;

type large is range 0 to 10000; function is_odd(num:small) return boolean;

signal b:boolean;

… b<=is_odd(a_number);

function is_odd(num:large) return boolean;

注:函数的名称可以是普通的标识符也可是运算符,是运算符时 必须加上双引号。

第3 章

VHDL 编程基础 例:函数和过程的声明(放在程序包首中) package pkg is type byte is array(7 downto 0) of bit; type nibble is array(3 downto 0) of bit;

Q8<= S1;

END ARCHITECTURE ART;

运算符重载解读

02

在重载运算符时,应明确指定 运算符的参数类型和返回类型 ,避免与其他操作符混淆。

03

在重载运算符时,应尽量使用 有意义的操作符名称,以提高 代码的可读性。

考虑性能和效率

01

02

03

运算符重载时,应考虑 性能和效率,避免对原 有代码造成不必要的性

能损失。

在重载运算符时,应尽 量减少额外的计算和内 存开销,以提高代码的

一元运算符重载

一元运算符重载是指对一元运算符进行重载,使其能够应用于一个操作数。例如,在C中,我们可以 重载一元减号运算符(-)来返回一个数的相反数。

常见的一元运算符有:+、-、~、!等。

二元运算符重载

二元运算符重载是指对二元运算符进行重载,使其能够应用于两个操作数。例如,在C中,我们可以重载加号运算符(+)来定 义两个自定义类型的相加行为。

01

提高代码可读性

运算符重载可以使代码更易读, 因为运算符的使用可以使代码更 简洁、更直观。

02

03

方便函数调用

运算符重载可以使得函数调用更 加方便,因为运算符的使用可以 减少函数调用的开销。

04

缺点分析

易造成混淆

运算符重载可能会使得代码难以理解,因为 运算符的行为可能会被改变,导致读者难以

理解代码的含义。

常见的二元运算符有:+、-、*、/、%等。

三元运算符重载

三元运算符重载是指对三元运算符进行重载,使其能够应用于三个操作数。例如,在C中,我们可以重载条件运 算符(?)来定义一个自定义类型的条件判断行为。

常见的三元运算符有:?:。

03

运算符重载的常见场景

类与类之间的运算

01

两个类对象之间的加法运算,可以表示它们之间的某种关联或 合并。

VHDL语言 第8章 VHDL结构

8.3 VHDL子程序

LIBRARY IEEE; -- 函数应用实例 USE IEEE.STD_LOGIC_1164.ALL; USE WORK.packexp.ALL ; ENTITY axamp IS PORT(dat1,dat2 : IN STD_LOGIC_VECTOR(3 DOWNTO 0); dat3,dat4 : IN STD_LOGIC_VECTOR(3 DOWNTO 0); out1,out2 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0) ); END; ARCHITECTURE bhv OF axamp IS BEGIN out1 <= max(dat1,dat2); --用在赋值语句中的并行函数调用语句 PROCESS(dat3,dat4) BEGIN out2 <= max(dat3,dat4); --顺序函数调用语句 END PROCESS; END;

86vhdl文字规则87vhdl数据类型88vhdl操作符逻辑操作符logicaloper关系操作符relonaloper算术操作符ar符号操作符signoper重载操作符overoadingoper操作数数据类型算术操作符并置一维数组整数和实数包括浮点数mod整数rem整数sll逻辑左移bit或布尔型一维数组srl逻辑右移bit或布尔型一维数组sla算术左移bit或布尔型一维数组sra算术右移bit或布尔型一维数组rol逻辑循环左移bit或布尔型一维数组ror逻辑循环右移bit或布尔型一维数组乘方整数abs取绝对值整数表82vhdl操作符列表表82vhdl操作符列表操作数数据类型关系操作符等于任何数据类型不等于任何数据类型小于枚举与整数类型及对应的一维数组大于枚举与整数类型及对应的一维数组小于等于枚举与整数类型及对应的一维数组大于等于枚举与整数类型及对应的一维数组逻辑操作符bitbooleanstdlogicnandbitbooleanstdlogicnorbitbooleanstdlogicxorbitbooleanstdlogicxnorbitbooleanstdlogic符号操作符整数88vhdl操作符运算符优先级notabsmodrem正号andornandnorxorxnor最低优先级表83vhdl操作符优先级基本逻辑电路设计举例138线译码器下面我们分别以三种方法描述一个38线译码器

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

4位加法器 语法检查结果:

综合出的RTL级框图:

关于“+”函数:

相同的函数名“+”居然 可以有不同的操作数?

从包集合中看一看函数“+” 到底是怎么回事

Std_logic_unsigned包集合中的“+”函数:

概念:

运算符重载(重载函数)指两个或两个以上的函数具有相同的函数

名,而操作数的数据类型有差别,足以区分实际想要的函数。 ★ 由编译器根据操作数的数据类型来判断用那一函数

刚才的4位加法器:

std_logic类型换为bit类型

自定义重载运算符(重载函数):

在包集合中定义重载函数:

刚才的4位加法器:

声明自定义的包集合

编译通过:

该函数将bit型转换为 std_logic子类型

总结:

同名不同人,不同的人做不同的事,用 到谁时谁上;

我们是女娲,也能造自己需要的人。

谢谢大家

作用:

运算符重载(重载函数)使得运算符(或函数)能对多种数据类型进 行操作,扩展了VHDL的功能。

好比是同名不同人,不同的人能做不同的事,用到谁时谁上

包集合中定义了很多重载运算符(重载函数):

一元: asb,运算:+,-,*,/,rem,mod

关系:=,/=,=>,<,>=,<=

逻辑:not,and,or,nand,nor,xor,xnor 移位:shift_left,shift_right,rotate_left, rotate_right,sll,srl,rol,ror ★同一函数名可能在不同的包集合中定义了不同的函数,具体用哪一函数就要 将其所在的包集合在文件头声明。 例如:运算符“+”在包集合IEEE.numeric_bit,IEEE. std_logic_unsigned, IEEE. std_logic_