第10章 DSP Builder设计深入

DSP Builder系统设计工具

DSP Builder系统设计工具DSP Builder是Altera推出的一个数字信号处理(DSP)开发工具,它在Quartus Ⅱ FPGA设计环境中集成了MathWorks的Matlab和Simulink DSP开发软件。

Altera的DSP系统体系解决方案是一项具有开创性的解决方案,它将FPGA的应用领域从多通道高性能信号处理扩展到很广泛的基于主流DSP的应用,是Altera第一款基于C代码的可编程逻辑设计流程。

在Altera基于C代码的DSP设计流程中,设计者编写在Nios Ⅱ嵌入处理器上运行的C代码。

为了优化DSP算法的实现,设计者可以使用由Matlab和Simulink工具开发的专用DSP指令。

这些专用指令通过Altera的DSP Builder和SOPC Builder工具集成到可重配置的DSP设计中。

对DSP设计者而言,与以往FPGA厂商所需的传统的基于硬件描述语言(HDL)的设计相比,这种流程会更快、更容易。

除了全新的具有软件和硬件开发优势的设计流程之外,Altera DSP系统体系解决方案还引入了先进的S tratix和Stratix Ⅱ系列FPGA开发平台。

Stratix器件是Altera第一款提供嵌入式DSP块的FPGA,其中包括能够有效完成高性能DSP功能的乘法累加器(MAC)结构。

Stratix Ⅱ FPGA能够提供比Stratix器件高四倍的DSP带宽,更适合于超高性能DSP应用。

6.1 DSP Builder安装6.1.1 软件要求使用DSP Builder创建HDL设计需要有下面的软件支持:? Matlab 6.1或6.5版本;? Simulink4.1或5.0版本;? Quartus Ⅱ 2.0以上版本;? Synplify 7.2以上版本或LeonardoSpectrum 2002c以上版本(综合工具);? ModelSim5.5以上版本(仿真工具)。

6.1.2 DSP Builder软件的安装在安装DSP Builder之前,首先安装Matlab和Simulink软件以及Quartus Ⅱ软件。

DSP Builder的功能和流程

电子131 XXX XXXXXX1、说明DSP Builder 的主要功能DSP Builder 是Altera 公司提供的一种DSP 系统设计工具,是Matlab/Simulink 设计工具和QuartusII 设计工具之间的一个桥梁,把Matlab/Simulink 中的DSP系统设计转化为HDL文件,在QuartusII 工具中实现到具体的器件中。

产生于Matlab\DSP Builder\Quartus II 流程的DSP 模块或其他功能模块可以成为单片FPGA 电路系统中的一个组成部分,担任某个局部电路的功能;通过Matlab\DSP Builder ,可以直接为Nios II 嵌入式处理器设计各类加速器,成为Nios II 系统的一个接口设备,与整个片内嵌入式系统融为一体。

DSP Builder 是一个系统级(或算法级)设计工具,它架构在多个软件工具之上,并把系统级和RTL 级两个设计领域的设计工具连接起来,最大程度地发挥了两种工具的优势。

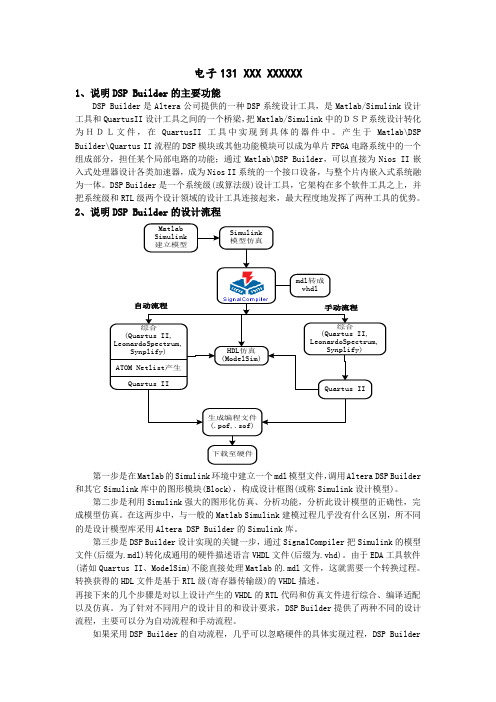

2、说明DSP Builder 的设计流程 Simulink 模型仿真综合(Quartus II,LeonardoSpectrum,Synplify)ATOM Netlist产生Quartus II HDL仿真(ModelSim)综合(Quartus II,LeonardoSpectrum,Synplify)Quartus II 生成编程文件(.pof,.sof)下载至硬件自动流程手动流程mdl转成vhdlMatlabSimulink建立模型第一步是在Matlab 的Simulink 环境中建立一个mdl 模型文件,调用Altera DSP Builder 和其它Simulink 库中的图形模块(Block),构成设计框图(或称Simulink 设计模型)。

第二步是利用Simulink 强大的图形化仿真、分析功能,分析此设计模型的正确性,完成模型仿真。

DSP Builder

1.说明DSP Builder的主要功能DSP Builder在算法友好的开发环境中帮助设计人员生成DSP设计硬件表征,从而缩短了DSP设计周期。

已有的MATLAB函数和Simulink模块可以和Altera DSP Builder模块以及Altera知识产权(IP)MegaCore功能相结合,将系统级设计实现和DSP 算法开发相链接。

DSP Builder支持系统、算法和硬件设计共享一个公共开发平台。

设计人员可以使用DSP Builder模块迅速生成Simulink系统建模硬件。

DSP Builder包括比特和周期精度的Simulink模块,涵盖了算法和存储功能等基本操作。

可以使用DSP Builder模型中的MegaCore功能实现复杂功能的集成。

Altera还提供DSP Builder高级模块集,这一Simulink库实现了时序驱动的Simulink综合。

Altera MegaCore是高级参数化IP功能,例如有限冲击响应(FIR)滤波器和快速傅立叶变换(FFT)等,经过配置能够迅速方便的达到系统性能要求。

MegaCore功能支持Altera的IP评估特性,使您在购买许可之前,便可以验证功能及其时序。

Altera IP MegaStore网站上为DSP Builder和IP评估流程提供DSP IP完整介绍DSP Builder SignalCompiler模块读取由DSP Builder和MegaCore模块构建的Simulink建模文件(.mdl),生成VHDL文件和工具命令语言(Tcl)脚本,进行综合、硬件实施和仿真。

图示为DSP Builder设计流程。

DSP Builder是一个系统级(或算法级)设计工具,它构架在多个软件工具之上,并把系统级和RTL级两个设计领域的设计工具连接起来,最大程度地发挥了两种工具的优势【10】。

DSP Builder依赖于Math Works公司的数学分析工具Matlab/Simulink,以Simulink的Blockset出现,可以在Simulink中进行图形化设计和仿真,同时又通过Signal Compiler可以把Matlab/Simulink的设计文件(.mdl)转成相应的硬件描述语言VHDL设计文件(.vhd),以及用于控制综合与编译的TCL脚本。

基于DSPBuilder数字信号处理课程设计

上海电力学院基于DSP Builder数字信号处理课程设计实验名称:AM调制FM调制及DDS信号专业:通信工程姓名:班级:学号:一、设计目的通过本次课程设计,巩固已学数字电路与逻辑设计的理论知识,掌握数字信号处理方法,引导学生从功能设计转向系统设计,掌握由现场可编程逻辑器件实现数字信号处理的方法,掌握现场可编程逻辑器件的应用设计,从而拓宽数字技术及处理的知识和设计能力,提高学生动手能力,培养学生分析问题与解决问题的能力。

二、设计内容本设计利用FPGA开发软件QuartusII,DSP BUILDER,MATLAB,设计实现各类波形信号的发生电路,如AM调制、FM调制、DDS控制等,进行引脚锁定、全编译通过后,完成FPGA器件Cyclone II的配置工作,并在Matlab Simulink中使用Scope显示仿真结果,在DE2开发板上下载并通过七段数码管,显示波形情况。

三、设计要求1.独立完成AM调制、FM调制、DDS控制电路的设计、译码显示电路的设计。

2.熟悉QuartusII,DSP BUILDER,MATLAB环境下系统开发设计流程。

3.在DE2上验证设计结果,并认真写出设计报告。

四、设计原理及步骤(一).AM 调制的设计AM 幅度调制函数信号可以用式)m 1(am dr ⋅+⋅=F F F 来表述,其中,dr F 、am F 、F 分别是被调制的载波信号,需要被调制的信号和调制后AM 的输出信号,它们都是有符号数,m 是调制度,10<<m 。

s (t )=m (t )*sin (t )其中m (t )是1或者是0,sin (t )是载波观察s (t )如果有波形输入的是1没波形是0。

基于DSP Builder 的数字的AM 系统如下图所示元器件的主要参数设定在这里省略介绍仿真如下图所示:通过matlab 转化成VHDL 语言通过Quartus2并下到板上验证,在这里需要添加几个模块一是分频器因为我们晶振频率较高反映在数码管上分辨不出所以叫频率降低,二是把8位的二进制传化成三位的十进制数,三是把十进制的数显示在数码管上;最后通过引脚分配输入端口有时钟clock 、使能端sw ,一个数字输入拨码开光,输出有四个数码管显示。

基于DSP Builder的数字滤波器设计与实现

该模 块可方便 地把 MA L BS ui T A / m l k中的设计 i n 转换为 F G P A可编译的 V D 文件 圈 H L 。

2 I滤波器 的D PB i e设计 1 阶F 6 R S ul r d

21 滤波器参数选取 .

利用 MA L B提供 的滤波器设计 的专门工 TA 具箱 F A o l D T o可以方便地设计滤波器系数 。根

(= -- ) j i1 )

B i e ̄具箱 中的模块进行简单的调用即可。值 ul r d 得注意的是 , S u dr D PB i e 中的 D P l S 模块是以算法

级 的 描 述 出现 的 ,易于用户从 系统 或 者 算 法 级 进

典 型 的直 接 I FR滤 波器 如 图 l 示 ,滤 型 I 所

(l ke 的形式出现 ,可以在 S ui 环境下进 Bo s ) c t i lk m n

1 FR 波 器 原 理 与 D PB i e I滤 S ul r d

11 I滤 波器 原 理 . FR

对于 一 个 FR 滤 波器 系统 ,它 的冲 激响应 总 I 是有 限长 的,FR 滤 波器 的数 学表 达 式可 用差 分 I

A src: il r ga b ta tFe po rmmal gt ary(P A) eie aewie sdi ii linl r csn p l a o s d be a r e a F G dvcs r dl ue dgt g a po e igapi t n y n as s ci

—弛

12 . DSP B i e ul r d

。蕴 : . 源自图 1 直 接 型 FR 滤 波器 结 构 图 I

以往 MA L T AB工 具 的使 用 往往 作为 DS P算

DSP Builder设计进阶

CtrlIn

图4-6 修改Subsystem的端口

第4章

DSP Builder设计进阶

图4-7就是更改singen子系统端口名称后subsint模型

顶层原理图的显示。 Simulink的子系统的端口的增删操作也比较简单, 可以直接在子系统的图上加入或者删除输入、输出端 口。在调用该子系统模块的上层原理图上,马上就会 更改相应的子系统模块的显示。 对于生成的子系统模块,可以将其当成一般的DSP 模块来使用,允许任意复制、删除子系统模块,或者

第4章

DSP Builder设计进阶

CtrlIn模块:(Altbus)

库:Altera DSP Builder中Bus Manipulation库 参数“Bus Type”设为“Single Bit” 参数“Bus Type”设为“Input port”

Constant模块:(Constant)

库:Simulink中Source库 参数“Constant Value”设为“512”

end mac;

architecture mac_arch of mac is

begin

Q <= (a*b);

end mac_arch;

第4章

DSP Builder设计进阶

例4-1的VHDL程序是一个12×8的MAC单元的描

述,在此把它导入到DSP Builder中。先在Simulink中建 立一个新模型,命名为vhdlmac。 在 Simulink 库 管 理 器 的 Altera DSP Builder 中 的 AltBus库中,找到SubSystemBuilder模块(图4-13),放 置在新建的vhdlmac模型窗口中。 双击vhdlmac模型窗口中的SubSystemBuilder模块, 打开SubSystem Builder对话框(见图4-14)。点击按钮,

基于DSPBuilder的DDS设计与实现.

基于DSPBuilder的DDS设计与实现DDS(DirectDigitalSynthesizer,直接数字合成器)是继直接频率合成技术和锁相环式频率合成技术之后的第三代频率合成技术,具有易于程控,相位连续,输出频率稳定度高,频率转换速度快和分辨率高等优点。

在现代电子系统及设备的频率源设计中,DDS广泛用于接收机本振、信号发生器、仪器、跳频通信系统、雷达系统等,因此有多家器件公司先后推出了多种DDS专用电路芯片,如AD7008,AD9852,AD9955等,专用DDS芯片由于采用了特定工艺,其DDS(Direct Digital Synthesizer,直接数字合成器)是继直接频率合成技术和锁相环式频率合成技术之后的第三代频率合成技术,具有易于程控,相位连续,输出频率稳定度高,频率转换速度快和分辨率高等优点。

在现代电子系统及设备的频率源设计中,DDS广泛用于接收机本振、信号发生器、仪器、跳频通信系统、雷达系统等,因此有多家器件公司先后推出了多种DDS专用电路芯片,如AD7008,AD9852,AD9955等,专用DDS芯片由于采用了特定工艺,其固定的控制方式使其在工作方式、频率控制等方面有时与实际系统的要求差距较大,并不能满足所有要求。

DDS中几乎所有部件都属于数字信号处理器件,所有可采用FPGA器件实现,利用FPGA可以较好地设计出符合用户系统需要的DDS系统,较好地解决了专用DDS灵活性差的问题。

本文应用模块化的设计方法,应用Altera公司的Cyclone器件和DSP Builder软件,设计出具有较高的频率分辨率和稳定性,能够实现频率及相位快速切换的DDS信号源。

在DDS的FPGA设计中,将Matlab仿真与FPGA设计相结合,使FPGA的波形仿真较为直观,大大缩短了DDS设计和调试时间。

1 DDS原理DDS结构见图1,由相位累加器、相位调制器、正弦ROM查找表、D/A构成。

相位累加器是整个DDS的核心,它由一个累加器和一个N位相位寄存器组成,每来一个时钟脉冲,相位寄存器以相位步长M增加,相位寄存器的输出与相位控制字相加,完成相位累加运算,其结果作为正弦查找表的地址,正弦ROM查找表内部存有一个完整周期正弦波的数字幅度信息,每个查找表地址对应正弦波中0°~360°范围的一个相位点,查找表把输入的地址信息映射成正弦波幅度信号,通过D/A输出,经低通滤波器后,即可得一纯净的正弦波。

DSPBuilder在数字信号处理中的应用_图文(精)

DSP Builder 在数字信号处理中的应用李云飞, 同晓荣(渭南师范学院计算机科学系, 陕西渭南714000摘要:目前数字信号处理(DSP 技术发展迅猛, 在电子、通信、DSP . 以往设计人员在进行DSP 系统设计时通常采用DSP 处理器或在FPG A , , 开发周期长. 本文介绍的DSP Builder 是A ltera 公司推出的一个, , 在Si m ulink 软件中完成系统集成, 然后通过, 通过综合仿真后下载到FPG A . , 这种设计流程更快、更容易.关键词:A; S OPC中图分类号:72文献标志码:A 文章编号:1009—5128(2008 02—0062—04收稿日期:2007—03—05基金项目:渭南师范学院科研基金资助项目(07YKF013作者简介:李云飞(1974— , 男, 甘肃镇原人, 渭南师范学院计算机科学系讲师.数字信号处理(DSP 技术目前广泛应用于电子信息和通信等领域. E DA 技术与FPG A 相结合的DSP 技术, 是现代电子技术发展的产物, 它有效地克服了采用DSP 处理器遇到的诸多技术瓶颈, 在许多方面显示了突出的优势, 如高速与实时性, 高可靠性, 自主知识产权化, 系统的重配置与硬件可重构性, 单片DSP 系统的可实现性以及开发技术的标准化和高效率等. 在诸如实时图像处理、3G 移动通信基站、实时工控系统、卫星导航设备等许多领域中, 基于FPG A 的DSP 解决方案有着无可比拟的优势. DSP Builder 是A ltera 公司推出的一个数字信号处理(DSP 开发工具. 它提供了QuartusII 软件和MAT LAB /Si m ulink 工具之间的接口, 通过DSP Builder 、S OPC Builder 和QuartusII 软件构筑的一套从系统算法分析到FPG A 芯片实现的完整设计平台, 使得基于FPG A 的DSP 系统设计变得比以往更快、更容易, 从而提高了设计效率.图1采用DSP Builder 的DSP 设计流程图1设计流程(1 采用DSP Builder 的DSP设计流程.在过去很长一段时间, DSP 处理器是DSP 应用系统核心器件的唯一选择. 但其硬件结构的不可改变性导致了其总线的不可改变性,而固定的数据总线宽度已成为DSP 处理器一个难以突破的瓶颈.现代大容量、高速FPG A 的出现,克服了DSP 处理器的不足. 由于FPG A 有着规整的内部逻辑块阵列和丰富的连线资源, 这些器件内部一般都内嵌有可配置的高速RA M 、P LL 、LVDS 、LVTT L 以及乘法累加器等, 有些器件甚至内嵌专用DSP 块, 所以特别适合细粒度和高并行度结构特点的数字信号处理任务. 而且其灵活的可配置特性, 2008年3月第23卷第2期渭南师范学院学报Journal of W einan Teachers UniversityM arch 2008Vol . 23No . 2使得FPG A 构成的DSP 系统非常易于修改、易于测试及硬件升级.图2DSP Builder 设计流程传统的基于FPG A 的DSP 设计通常先要通过M atlab 做系统级的算法仿真, 建立算法模型(通常使用C /C++语言或M 语言 . 然后再将系统级的算法模型通过VHDL /Verilog 语言重新描述以便进行综合、布局布线以及寄存器传输级(RT L 的仿真. 通常这一步是最费时的,需要设计人员具有非常丰富的FPG A 设计经验. 最后将设计得到的P OF 文件下载到器件中验证, 以实现最终设计. 采用这种设计流程开发人员必须一步一步地从系统级算法设计直到最终器件配置, 设计周期长、开发难度大, 行软硬件协同设计.采用A 程. ,并且为DSP 系统的软硬件分离提供了可能. 设计人员可以使用DSP Builder 和QuartusII 软件单独进行硬件设计. 使用DSP Builder 工具, 设计者可以直接将M atlab 中的算法设计转为寄存器传输级设计, 并且在Si m ulink 中自动生成RT L 测试文件. 这些文件是已经被优化的预验证RT L 输出文件, 可以直接用于QuartusII 软件进行时序仿真比较. 图1给出了A ltera DSP 设计的总体框图.由图1可以看出这种DSP 设计流程完全基于E DA 特有的自顶向下的设计流程和高速的并行算法结构. 设计人员可以从与硬件无关的系统开始, 在硬件设计的同时进行软件设计, 实现软硬件协同设计. DSP Builder 作为连接系统算法模型与实际硬件实现之间的桥梁, 使得复杂的算法模型可以迅速地在硬件上得以验证, 这是一个相互联系的过程. 设计人员可以使用DSP Builder 中的块来为Si m ulink 中的系统模型创建一个硬件, 这些块覆盖了最基本的操作, 例如运算和存储功能, 设计人员还可以使用A ltera 的I P 核来验证自己的设计. 将事先设定好的嵌入式逻辑分析仪SignalTap 和DSP 硬件系统文件一同适配并下载到FPG A 中, 然后可以在M atlab 的Si m ulink 窗口观测到通过JT AG 口, 来自SignalTap 测得的芯片中DSP 硬件模块的实时工作波形, 实现硬件仿真和调试的目的. 如有必要还可以将DSP 硬件模块通过S OPC 接口, 编辑成N i osII 嵌入式系统处理器的用户指令, 从而成为N i osII 系统的一个接口设备, 与整个片内嵌入式系统融为一体.图3DSP Builder 中设计的滤波器模型(2 DSP Builder 设计流程.・36・2008年第2期李云飞, 等:DSP Builder 在数字信号处理中的应用DSP Builder 是一个架构在多个软件之上的可把算法仿真建模与RT L 级两个设计领域连接起来的系统级设计工具. DSP Builder 以Si m ulink 中的B l ockset 形式在Si m ulink 中进行图形化设计和仿真. 通过Sig 2nal Co mp iler 把Si m ulink 的设计文件转成相应的硬件描述语言VHDL 设计文件, 以及tcl 脚本. 由于在FPG A 上设计DSP 模块的复杂性, 涉及的软件不仅仅是Si m ulink 和QuartusII . DSP Builder 针对不同情况提供了图4 F I R 滤波其仿真结果自动和手动两种设计流程. DSP Builder 设计流程如图2所示.如果采用自动流程时, 几乎可以忽略硬件的具体实现过程, 选择让DSP Builder 自动调用Qu 2artusII 等E DA 软件, 完成综合(Synthesis 、网表(AT O M Netlist 生成和QuartusII 适配, 直至在M atlab 中完成FPG A 的配置下载过程.如果采用手动流程, 设计输入外, 的E VHDL . Quar 2tusII , 也可以使用第三方工具如Synp lify Pr o 或LeonardoS pectru m. 在综合时, 可能需要对综合器进行配置或者提供综合的约束条件, 由于这个过程十分繁琐, 所以DSP Builder 的Signal Co mp iler 提供了相应的接口, 针对设计自动生成一个tcl 脚本文件与综合器相接. 综合器会综合出一个网表供下一流程使用, 主要是E D I F 网表文件或VQ M , 它们是一种参数可配置的, 并含有具体器件系列硬件特征(如逻辑宏单元LCs 、I/O单元、乘积嵌入式系统块ES B 的网表文件. QuartusII 可以利用这些AT O M 网表针对选定的具体器件进行配置, 包括布局布线、结构优化等操作, 最后产生时序仿真文件和FPG A 目标器件的编程与配置文件. 设计者可以在QuartusII 中完成对Pin 的锁定, 更改一些约束条件.图5通过DSP Builder 生成VHDL 代码・46・渭南师范学院学报第23卷(3 设计举例.使用DSP Builder 可以方便地在图形化环境中设计F I R 滤波器, 而且滤波器系数可以借助于M atlab 中的滤波器设计工具完成. 例如设计一个3阶直接I 型F I R 滤波器的模型如图3所示. h (n =(h (0 x (n +h (1 x (n -1 +h (2 x (n -2 +h (3 x (n -3 其中, h (0 =h (3 =63, h (1 =h (2 =127.由于F I R 滤波器的系数h (n 已给定, 在DSP Builder 中可以使用增益模块实现h (k 3x (n -k 的运算, 用Delay 模块来实现输入信号序列x (n 的延时. 其中Chir p 模块为一个线性调频信号发生模块, 产生0. 1Hz 到10Hz 的线性调频信号. 其仿真结果如图4所示.从仿真波形可以看出一个线性调频信号通过3阶F I R 滤波器后, 幅度发生变化, 频率越高, 幅度衰减越多. 如果仿真通过, 则可以通过如图5所示的DSP Builder 中的工具将模型自动生成代码供Quar 2tus 综合下载到FPG A 中, 完成设计.2结论DSP Builder . 利用M atlab /DSPBuilder 进行DSP 模块设计是S , Builder 设计流程的DSP 功能模块可以成为单片FPG A 电, . 如果使用Stratix 和StratixII 系列FPG A 作为开发平台, 加上各种I P 核进行设计则可以充分发挥DSP Builder 的优势. 可以预见DSP Builder 将在数字信号处理中取得广泛的应用.参考文献:[1]任爱峰, 初秀琴, 常存, 等. 基于FPG A 的嵌入式系统设计[M].西安:西安电子科技大学出版社, 2004.[2]潘松, 黄继业, 曾毓. S OPC 技术实用教程[M].北京:清华大学出版社, 2004.[3]黄智伟. FPG A 系统设计与实践[M].北京:电子工业出版社, 2005.[4]楮振勇, 齐亮, 田红心. FPG A 设计及应用(第2版 [M].西安:西安电子科技大学出版社, 2006.[5]王毅平, 张振荣. VHDL 编程与仿真[M].北京:人民邮电出版社, 2000.[责任编辑牛怀岗]Appli ca ti on of D SP Bu ilder i n D i g it a l S i gna l Processi n gL I Yun 2fei, T ONG Xiao 2r ong(Depart m ent of Computer Engineering, W einan Teachers Univeristy, W einan 714000, ChinaAbstract:The digital signal p r ocessing (DSP technol ogy has rap idly devel oped at p resent and it has widely used in electr onic, communicati on and airs pace . DSP designers usually adop te DSP p r ocess or or hardware describe language (HDL at FPG A in their design several years ago . The paper briefly intr oduces DSP Builder that is a DSP devel op t ool, which can all ow designers comp leting algorith m design inM atlab and syste m integrati on in Si m ulink, finally making HDL file used in Quartus II by Signal Comp iler bl ock . DSP designers can use the HDL file t o accomp lish their design thr ough synthesis si m ulati on and downl oad in FPG A. The design fl ow is faster and si m p ler compared with design based on HDL.Key words:signal p r ocessing; si m ulati on; DSP; FPG A; VHDL; S OPC ・56・2008年第2期李云飞, 等:DSP Builder 在数字信号处理中的应用。

基于DSP Builder数字滤波器的设计与实现毕业设计

摘要数字滤波器是现代数字信号处理系统的重要组成部分之一,具有模拟滤波器所无法替代的新特性,因此在通信、语音与图像处理、自动控制等领域有着广泛的应用,它对于降低噪声、提高信噪比及信号的频谱纯度等方面有着重要的意义。

数字滤波器根据单位脉冲响应的不同,可分为FIR(有限长脉冲响应)滤波器和IIR(无限长脉冲响应)滤波器,FIR的优点在于具有良好的相位特性,IIR的优点在于具有良好的幅频特性,可以根据不同的系统性能要求选择不同的滤波器。

目前滤波器的主要实现方法有三种,分别是:单片通用数字滤波器集成电路、采用DSP器件和FPGA(现场可编程门阵列)器件。

本文采用FPGA器件来实现滤波器的设计,在实现方法上先用MATLAB/Simulink工具箱建立滤波器模型,然后用SignalCompiler把Simulink的模型文件(后缀是.mdl)转化为硬件描述语言VHDL文件,最后利用QuartusII完成滤波器的仿真、配置、编译和下载。

本文最后用实例介绍了FIR数字滤波器和IIR数字滤波器的实现过程。

关键词:数字滤波器通信集成电路 DSP FPGAAbstractDigital filter is a digital signal processing system is one of the important component, analog filters cannot be replaced by the new characteristic, therefore in the communication, speech and image processing, automatic control and other fields have a wide range of applications, it can reduce noise, improve the signal to noise ratio and signal spectrum purity has important significance. Digital filter according to unit impulse response of different, can be divided into FIR ( finite impulse response filter ) and IIR ( infinite impulse response ) filter, FIR have the advantages of good phase characteristics, IIR have the advantages of good amplitude-frequency characteristics, according to different system performance requirements of different filter. The filter main realizing methods has three kinds, respectively is: the monolithic integrated circuit, digital filter with DSP device and FPGA ( field programmable gate array ) device. This paper uses FPGA to realize filter design, the realization method on the first MA TLAB / Simulink toolbox to establish filter model, then use SignalCompiler the Simulink model file ( the suffix is . MDL ) into the VHDL hardware description language file, finally using QuartusII complete filter simulation, configure, compile and download. Finally, examples of the FIR digital filter and IIR digital filter implementation process.Keywords: digital filter communication integrated circuit DSP FPGA目录1.绪论 (1)1.1研究背景 (1)1.2研究现状 (1)1.3本课题研究内容方法 (3)2.相关知识简介 (5)2.1 数字滤波器概述 (5)2.1.1 数字滤波器的定义 (5)2.1.2 数字滤波器的分类 (6)2.1.3 FIR和IIR数字滤波器的比较 (6)2.1.4 数字滤波器的设计要求和方法 (8)2.2 设计软件简介 (9)2.3 软件安装问题 (10)3.数字滤波器的总体设计方案 (12)3.1 FIR和IIR设计方法概述 (12)3.2 滤波器设计方法比较 (12)4. FIR设计实例 (16)4.1 FIR数字滤波器原理 (16)4.2 16阶FIR滤波器 (16)5. IIR设计实例 (27)5.1 IIR数字滤波器原理 (27)5.2 使用DSP B UILDER设计IIR滤波器 (30)5.2.1 4阶直接Ⅱ型IIR滤波器设计 (30)5.2.2 4阶级联型IIR滤波器设计 (32)6.总结 (38)参考文献 (40)致谢 (41)1.绪论1.1 研究背景当今,数字信号处理(DSP:Digtal Signal Processing)技术正飞速发展,它不但自成一门学科,更是以不同形式影响和渗透到其他学科:它与国民经济息息相关,与国防建设紧密相连;它影响或改变着我们的生产、生活方式,因此受到人们普遍的关注。

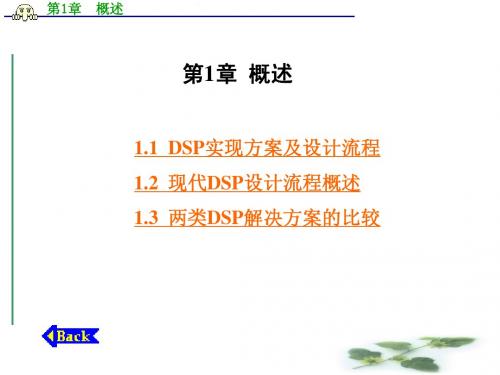

现代DSP技术课件dspbuilder设计一至四章

第1 章

概述

为了满足 DSP 技术领域中的各种需求以及顺应

DSP市场的发展,DSP应用系统的实现方式和目标器件 的品种类型、结构特点乃至开发技术本身都经历着不 断的改善和变革。 1.1.1 常用DSP应用器件及其性能特点 如前所述, DSP 作为数字信号的算法的实现方案 有多种,对于不同的应用领域、适用范围和指标要求, 可以选用不同的解决方案和 DSP 系统的实现器件。目

第1 章

概述

现代大容量、高速度的FPGA的出现,克服了上述 方案的诸多不足。在这些FPGA中,一般都内嵌有可配 置的高速 RAM 、 PLL 、 LVDS 、 LVTTL 以及硬件乘法 累加器等DSP模块。用FPGA来实现数字信号处理可以 很好地解决并行性和速度问题,而且其灵活的可配置 特性,使得FPGA构成的DSP系统非常易于修改、易于 测试及硬件升级。

第1 章

概述

1.1 DSP实现方案及设计流程

不断发展的数字信号处理(DSP,Digital Signal Processing)技术迅速地扩展到了其应用领域,如3 G移 动通信、网络会议、多媒体系统、雷达卫星系统、医 学仪器、实时图像识别与处理、联合战术无线电系统、 智能基站,以及民用电器等。所有这一切在功能实现、 性能指标与成本方面都在不断增加其要求。

第1 章

概述

在利用FPGA进行DSP系统的开发应用上,已有了

全新的设计工具和设计流程。DSP Builder就是Altera公 司推出的一个面向DSP开发的系统级工具。它是作为 MATLAB的一个Simulink工具箱(ToolBox)出现的。 MATLAB是功能强大的数学分析工具,广泛应用于科 学计算和工程计算,可以进行复杂的数字信号处理系 统的建模、参数估计、性能分析。Simulink是 MATLAB的一个组成部分,用于图形化建模仿真。

基于DSP Builder的数字调制器的设计

来 较为复 杂 , F G 而 P A不仅 具有灵 活性 和通 用 性 , 而 且使 用方便 、 件 测 试 和实 现 快 捷 。一 般来 说 , P 硬 F— G A的开发 流程为设 计 输 入 ( 用 V L 、 合 、 如 HD ) 综 仿

真 、 配 、 载 到器 件 。 由 于系 统 的 H L描 述需 要 适 下 D

究 方 向 : 电 子 技术 应 用 。 微

36 5

科

学

技

术

与

工

程

1 卷 1

式 ( ) 0 指 前 一 个 ck周 期 的 相 位 值 , 一 1 中,㈦ 1 B

2 0 N

K_l

13 1 Q . 6 AM 调 制 原 理

/ ,,△ 2 A /  ̄。只要 对 相位 的 量化 值 进 2rB 口 02 t

第 1卷 1

第2 期

21 年 1 01 月

科

学

技

术

与

工

程

⑥

Vo. 1 N . J n 2 1 11 o 2 a. 0 1

17 — 11 (0 1 20 5 —5 6 1 8 5 2 1 ) -35 0

S in e T c n lg n g n ei g ce c e h oo y a d En i e r n

真验 证 通 过 后 , 可 使 用 S nlC m ir MA — 即 i a o pl 把 g e T

L B S l k模 型设 计 文 件 ( md) 换 成 相 应 的 A /i i mu n . 1转 硬件描述 语 言 V D H L设 计 文 件 ( v d , .h ) 以及 用 于控

D S是一 种新 型 的频 率合 成 技 术 , 容 易实 现 D 很 频率 、 相位 和幅 度 的数 控调 制 。在 数 字 化 的调 制 解 调模块 中 , D D S取 代 了模 拟 的压 控 振 荡 器 , 大 量 被 使 用 。其典 型结 构如 图 1所示 。

DspBuilder中文教程2

第10章 DSP Builder 设计深入应用Matlab/DSP Builder 可以对多种类型的电子线路模块或系统进行建模、分析和硬件实现,且更擅长于一些较复杂的功能系统,及偏向于高速算法方面的模块的设计和实现,还能利用HDL Import 模块将HDL 文本设计转变成为DSP Builder 元件。

本章将给出一些DSP 及数字通信领域中实用模块的设计实例,以及基于Matlab/DSP Builder 平台的IP 核的应用。

10.1 FIR 数字滤波器设计FIR (Finite Impulse Response :有限冲激响应)滤波器在数字通信系统中,被大量用于以实现各种功能,如低通滤波、通带选择、抗混叠、抽取和内插等。

在DSP Builder 的实际应用中,FIR 滤波器是最为常用的模块之一。

DSP Builder 的FIR 滤波器设计方式有多种,作为示例,本节介绍基于模块的FIR 与基于IP 的FIR 设计方法。

10.1.1 FIR 滤波器原理对于一个FIR 滤波器系统,它的冲激响应总是有限长的,其系统函数可以记为:∑=−=Mk k k z b z H 0)( 10-1最基本的FIR 滤波器可用下式表示:∑−=−=10)()()(L i i h i n x n y 10-2其中()x n 是输入采样序列,()h n 是滤波器系数,L 是滤波器的阶数,)(n y 表示滤波器的输出序列。

也可以用卷积来表示输出序列)(n y 与)(n x 、)(n h 的关系。

)()()(n h n x n y ∗= 10-3图10-1中显示了一个典型的直接I 型3阶FIR 滤波器,其输出序列)(n y 满足下列等式:EDA 技术与VHDL366)3()3()2()2()1()1()()0()(−+−+−+=n x h n x h n x h n x h n h 10-4在这个FIR 滤波器中,总共存在3个延时结,4个乘法单元,一个4输入的加法器。

现代DSP技术课件dspbuilder设计十至十四章

第10章

编码与译码

伪随机序列广泛应用于这类加扰、解扰操作中。下

面以一类伪随机序列——m序列为例,用DSP Builder 构建一个伪随机序列发生器。 10.1.1 m序列 m序列即最长线性反馈移位寄存器序列,是一种比

较常见的伪随机序列发生器,可由线性反馈寄存器

(Linear Feedback Shift Registers,LFSR)来产生。如图 10-1所示。

对于RS码的编码器,可以用带反馈的移位寄存器来 实现,不过实现起来比较复杂。Altera为RS码提供了IP Core——RS Compiler 来简化RS编码/译码器的设计。 RS Compiler除了可在Quartus II中使用外,还可与DSP Builder配合使用(见图10-9)。

第10章

第10章

编码与译码

图10-10 选择类型为RS的编码器

第10章

编码与译码

图10-11 确定参数

第10章

编码与译码

10.3.3 使用IP Core设计RS译码器

RS Compiler这个核也可以设计RS译码器。同设计 RS编码器时一样调用RS Compiler,选择类型为 “Decoder”的译码器,见图10-12所示。 接着的参数设置与RS编码器相同,这里不再赘述。

第11章

DSP Builder设计规则

11.1 位宽设计规则

在设计中,必须根据具体情况规定输入和输出数据 口的位宽,即源端口与目标端口的数据位宽。一旦确 定了输入端的数据位宽,SignalCompiler 就会通过各中 间模块把数据位宽从源端口向目标端口传递。在一定 条件下,设计者也可以对所通过的各模块中的数据位 宽作一定的设定。例如,在第三章中介绍的调幅设计 中,Sinln和SinDelay模块的位宽是16,所以 SignalCompiler 就自动将这16位宽的数据类型赋予了中 间模块Delay。

DSP Builder设计初步资料

23

9.2 正弦信号发生器设计

2、添加波形观察模块

K 康芯科技 X

24

图9-18 Scope初始显示

9.2 正弦信号发生器设计

3、Scope参数设置

K 康芯科技 X

25

图9-19 设置Scope参数

9.2 正弦信号发生器设计

3、Scope参数设置

K 康芯科技 X

图9-20 sinout全图

26

图9-13 设置SinCtrl

18

9.2 正弦信号发生器设计

10、放置端口SinCtrl

K 康芯科技 X

图9-13 设置SinCtrl

19

9.2 正弦信号发生器设计

11、放置Product模块

K 康芯科技 X

图9-14 设置乘法单元

20

9.2 正弦信号发生器设计

12. 放置输出端口SinOut

7. 设置IncCount

K 康芯科技 X

图9-10 LUT模块

14

9.2 正弦信号发生器设计

8、放置正弦查找表(SinLUT)

K 康芯科技 X

127*sin[0:2*pi/2^6]:2*pi]) 127*sin[0:2*pi/2^8]:2*pi])

9-1 9-2

511*sin[0:2*pi/2^6]:2*pi]) + 512

5、启动仿真

K 康芯科技 X

图9-24 有符号输出波形(系统级仿真 )

30

9.2 正弦信号发生器设计

5、启动仿真

K 康芯科技 X

图9-25 无符号输出波形(系统级仿真)

31

9.2 正弦信号发生器设计

6、设计成无符号数据输出

K 康芯科技 X

使用DSP Builder设计FSK发射机的数字中频

1.数字基带信源设计

为了测试方便,我们需要在发射机中设计一个数字基带信源。它可以循环地产生基带码流,作为FSK调制器的输入信号。在这里我们采用一个长度为16位的LUT(查找表)作为数字码流的存储器件。数字码流为:

[1 0 1 0 0 0 1 1 0 0 1 1 1 0 1 0]

采用一个递增的计数器作为LUT的地址输入,随着递增的计数器的计数值的改变,LUT输出不同的数字信号(0或1)。数字信号是周期性的,每个周期长度是16位。

4)将Increment Decrement模块的输出与Bus Conversion模块的输入相连,将Bus Conversion模块的输出与LUT模块的输入相连。至此,数字基带信源模块已完成。

5)为了验证设计的正确性,可以在仿真文件中加入一个scope(示波器)模块。从SimulinkLibrary Browser中选择Simulink -> Sinks -> Scope模块,加入Simulink仿真文件中。之后将LUT模块的输出连接至Scope模块的输入即可。连接之后的仿真文件如下图5所示。

表10 Constant模块的Main选项卡中各项参数

参数名称

参数值

Constant Value

100

Bus Type

Unsigned Integer

[Number of Bits].[]

8

Rounding Mode

Truncate

Saturation Mode

Wrap

S字基带信源的仿真文件

6)点击仿真文件上方工具栏中的“Start Simulation”按钮,即可启动一次Simulink仿真。仿真结束后双击Scope模块,打开Scope模块后,可以看到仿真结果。若仿真结果显示不全,可以用鼠标右键单击波形区,在弹出的菜单中选择Autoscale,即可将所有波形显示出来。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

h9、h10、h11、h12、h13、h14、h15模块:(Delay) 库:Altera DSP Builder中IO & Bus库 参数“Bus Type”设为“Signed Integer” 参数“number of bits”设为“9”

10.1 FIR数字滤波器设计

10.1.3 使用Matlab的滤波器设计工具

10.1.4 使用FIR IP Core设计FIR滤波器

10.1 FIR数字滤波器设计

图10-27 IP Core模块库

10.1 FIR数字滤波器设计

10.1.4 使用FIR IP Core设计FIR滤波器

1、FIR滤波器核的使用

2、配置FIR滤波器器核

图10-28 设置FIR Core参数

10.1 FIR数字滤波器设计

图10-5 直接I型4阶FIR滤波器节

y4out

2、4阶FIR滤波器节设计

10.1 FIR数字滤波器设计

图10-6 直接I型4阶FIR滤波器节

10.1 FIR数字滤波器设计

2、4阶FIR滤波器节设计 Xin、hn0、hn1、hn2、hn3模块:(Altbus) 库:Altera DSP Builder中IO & Bus库 参数“Bus Type”设为“signed Integer” 参数“Node Type”设为“Input port” 参数“number of bits”设为“9”

h(0)

yout

图10-4 直接I型FIR滤波器结构

10.1 FIR数字滤波器设计

2、4阶FIR滤波器节设计

H ( z) h(1) z 1 h(2) z 2 h(3) z 3 h(4) z 4

10-6

xin

z-1 h(1)

x(n-1)

z-1 h(2)

z-1 h(3)

z-1 h(4)

4、量化

图10-23 量化后幅频、相频响应

10.1 FIR数字滤波器设计

10.1.3 使用Matlab的滤波器设计工具

4、量化

图10-24 量化后噪声分析

10.1 FIR数字滤波器设计

10.1.3 使用Matlab的滤波器设计工具

5、导出滤波器系数

图10-25 导出系数对话框

6、修改FIR滤波器模型添加参数

10.1.4 使用FIR IP Core设计FIR滤波器

图10-29 确定FIR滤波器系数

10.1 FIR数字滤波器设计

10.1.4 使用FIR IP Core设计FIR滤波器

图10-30 确定FIR工作方式

10.1 FIR数字滤波器设计

10.1.3 使用Matlab的滤波器设计工具

图10-26 16阶低通FIR滤波器

10.1 FIR数字滤波器设计

10.1.3 使用Matlab的滤波器设计工具

7、导出滤波器系数的另一种方法 把FIR滤波器模型中的h1~h16模块的参数“Constant Value (常数值)”设置为: Num(n)*(2^8) 其中Num同上文所述,是FDATool的系数导出,n用具体的数字来 代替,如h1模块用Num(1)*(2^8),h2模块用 Num(2)*(2^8)。 最后利用SingalCompiler,选定器件系列,把模型转成VHDL文 件,用QuartusII进行综合/适配,锁定管脚和下载至FPGA中,就可 以完成硬件实现了。

10.1 FIR数字滤波器设计

3、16阶FIR滤波器模型设计

图10-7 fir4tap子系统

10.1 FIR数字滤波器设计

3、16阶FIR滤波器模型设计

图10-8 fir4tap子系统内部原理图

10.1 FIR数字滤波器设计

3、16阶FIR滤波器模型设计

图10-9 16阶直接I型FIR滤波器模型

2、选择Design Filter

H ( z ) bk z k

k 1

16

10-7

H ( z ) z 1 bk z k

k 0

15

10-8

10.1 FIR数字滤波器设计

10.1.3 使用Matlab的滤波器设计工具

3、滤波器分析

图10-12 FIR滤波器的幅频响应

10.1 FIR数字滤波器设计

10-4

10.1 FIR数字滤波器设计

10.1.1 FIR滤波器原理

x(n)

z-1 h(1)

z-1 h(2)

z-1 h(3)

h(0)

图10-1 3阶FIR滤波器结构

y(n)

10.1 FIR数字滤波器设计

10.1.2 使用DSP Builder设计FIR滤波器

1.3阶常数系数FIR滤波器设计

h(n) Cq (h(0) x(n) h(1) x(n 1) h(2) x(n 2) h(3) x(n 3))

10.1 FIR数字滤波器设计

3、16阶FIR滤波器模型设计

x16模块:(Altbus) 库:Altera DSP Builder中IO & Bus库 参数“Bus Type”设为“signed Integer” 参数“Node Type”设为“Output port” 参数“number of bits”设为“9” Parallel Adder Subtractor模块:(Parallel Adder Subtractor) 库:Altera DSP Builder中Arithmetic库 参数“Add(+)Sub(-)”设为“++++” 使用“Pipeline” 参数“Clock Phaese Selectioon”设为“1” h0、h1、h2、h3、h4、h5、h6、h7、h8、

10.1.3 使用Matlab的滤波器设计工具

3、滤波器分析

图10-13 FIR滤波器的相频响应

10.1 FIR数字滤波器设计

10.1.3 使用Matlab的滤波器设计工具

3、滤波器分析

图10-14 幅频响应与相频响应比较

10.1 FIR数字滤波器设计

10.1.3 使用Matlab的滤波器设计工具

yn模块:(Altbus) 库:Altera DSP Builder中IO & Bus库 参数“Bus Type”设为“signed Integer” 参数“Node Type”设为“Output port” 参数“number of bits”设为“20”

10.1 FIR数字滤波器设计

2、4阶FIR滤波器节设计 xn4模块:(Altbus) 库:Altera DSP Builder中IO & Bus库 参数“Bus Type”设为“signed Integer” 参数“Node Type”设为“Output port” 参数“number of bits”设为“9”

4、量化

图10-20 量化参数设置

10.1 FIR数字滤波器设计

10.1.3 使用Matlab的滤波器设计工具

4、量化

图10-21 量化优化设置

10.1 FIR数字滤波器设计

10.1.3 使用Matlab的滤波器设计工具

4、量化

图10-22 量化后系数

10.1 FIR数字滤波器设计

10.1.3 使用Matlab的滤波器设计工具

滤波器转换(TransForm Filer)

设置量化参数(Set Quantization Parameters)

实现模型(Realize Model)

导入滤波器(Import Filter)

设计滤波器(Design Filter)

10.1 FIR数字滤波器设计

10.1.3 使用Matlab的滤波器设计工具

10.1 FIR数字滤波器设计

2、4阶FIR滤波器节设计 Delay、Delay1、Delay2、Delay3模块:(Delay) 库:Altera DSP Builder中Storage库 参数“Depth”设为“1” 参数“Clock Phase Selection”设为“1” Product模块:(Product) 库:Altera DSP Builder中Arithemtic库 参数“Pipeline”设为“2” 参数“Clock Phase Selection”设为“1” 不选择“

3、16阶FIR滤波器模型设计

xin模块:(Altbus) 库:Altera DSP Builder中IO & Bus库 参数“Bus Type”设为“signed Integer” 参数“Node Type”设为“Input port” 参数“number of bits”设为“9” yout模块:(Altbus) 库:Altera DSP Builder中IO & Bus库 参数“Bus Type”设为“signed Integer” 参数“Node Type”设为“Output port” 参数“number of bits”设为“20”

10.1 FIR数字滤波器设计

10.1.2 使用DSP Builder设计FIR滤波器

1.3阶常数系数FIR滤波器设计

图10-3 FIR滤波器仿真结果

10.1 FIR数字滤波器设计

2、4阶FIR滤波器节设计

xin

x(n)

z-1 h(1)

z-1 h(2)

z-1 h(k-1)

z-1 h(k)

x(n-k)

1.3阶常数系数FIR滤波器设计 Chirp Signal模块:(Chirp Signal) 库:Simulink中Sources库 参数“Initial Frequency(Hz)”设为“0.1” 参数“Target time”设为“10” 参数“Frequency at target time(Hz)”设为“1” 参数“Interpret vectors parameters as 1-D”选中 Gain模块:(Gain) 库:Simulink中Math Operations库 参数“Gain”设为“127” 参数“Multiplication”设为“Element wise(K.*u)” Scope模块:(Scope) 库:simulink中sinks库 参数“Number of Axes”为“2”