2[1].FPGA设计高级进阶破解

基于FPGA的加密解密模块设计与实现

基于FPGA的加密解密模块设计与实现随着信息技术的不断发展,数据加密已经成为了保护信息安全的重要手段。

尤其是在金融、军事等领域,数据加密已成为不可或缺的技术手段。

而加密解密的关键技术就是密码算法。

在密码算法中,对称密码算法是最常用的一种算法,然而,对称密码算法的密钥管理和密钥分发一直以来都存在着许多问题,为此,研究人员提出了一种基于FPGA的加密解密模块设计方案,可以有效解决这些问题。

FPGA是一种具有可编程性的半导体器件,它具有高度的可重构性,可以通过编程来实现特定的功能,因此被广泛应用于各种领域。

而基于FPGA的加密解密模块,采用硬件实现加密解密算法,相比采用软件实现的加密解密算法,具有更高的安全性和更快的速度。

1.加密解密模块的概述加密解密模块是实现对称密码算法的关键部分,它可以将明文转化为密文,或将密文转化为明文。

在实现加密解密模块时,需要选择合适的对称算法,并通过硬件电路来实现对称算法的加密解密操作。

常用的对称密码算法有DES、3DES、AES等。

在加密解密模块的设计中,需要对输入和输出进行格式化,并为加密解密算法提供必要的控制信号。

可以使用状态机来实现控制信号的发生,并使用计数器来计算加密解密操作的步数。

同时,在硬件电路中,需要将需要加密或解密的数据存储到寄存器中,使用多路选择器来选择需要进行加密解密的数据块,并在每一次执行加密解密操作时,更新控制信号和数据块。

2.基于FPGA的加密解密模块的设计方案基于FPGA的加密解密模块由输入接口、加密解密核心、控制器和输出接口等模块构成。

其中,输入接口用于将需要加密或解密的数据输入到加密解密核心中,控制器用于控制加密解密操作的流程,输出接口用于输出加密或解密的结果。

在加密解密核心中,可以选择采用现有的对称算法IP核,例如AES IP核、DES IP核等,也可以自己实现对称算法电路。

同时,可以采用先进的乘加器单元、查找表、寄存器等硬件电路元素来优化算法电路。

fpga设计步骤

fpga设计步骤FPGA(现场可编程门阵列)是一种可编程逻辑设备,可以通过配置文件来实现不同的功能。

FPGA设计是一个复杂的过程,涉及多个步骤。

以下是一个关于FPGA设计的详细步骤,以帮助您更好地了解FPGA设计过程。

1.确定需求:在开始FPGA设计之前,首先需要明确您的设计需求。

这包括确定所需的功能、性能要求、接口要求等。

这个步骤是非常关键的,因为它将直接影响到后续的设计和实现过程。

2.设计规划:在确定需求之后,接下来需要进行设计规划。

设计规划包括确定所需的资源(如逻辑单元、存储器、DSP等)、时钟频率、接口协议等。

这个步骤的目的是为了确保设计可以在FPGA上正确实现。

3. 设计编码:在设计规划完成之后,接下来需要进行设计编码。

设计编码是将设计规划转化为可实现的硬件描述语言(HDL)代码的过程。

常用的HDL语言包括VHDL和Verilog。

在设计编码过程中,需要根据需求使用适当的逻辑门、时序元件等。

4.仿真验证:在设计编码完成之后,需要进行仿真验证。

仿真验证是通过使用仿真工具对设计进行验证,以确保其功能和性能满足需求。

在仿真过程中,可以使用不同的输入情况和测试用例来验证设计的正确性和稳定性。

5.综合:在仿真验证通过之后,需要进行综合。

综合是将HDL代码转化为逻辑门级的网表表示。

综合工具将根据目标FPGA的资源和约束来进行综合。

综合后会生成一个网表文件,其中包含了所有的逻辑门和时序元件的连接关系。

6.物理布局:在综合完成之后,需要进行物理布局。

物理布局是将逻辑网表映射到FPGA的物理资源上的过程。

物理布局过程中需要考虑资源的分配、时钟布线、信号路由等因素。

物理布局的目标是最大程度地优化资源利用和信号延迟。

7.静态时序分析:在物理布局完成之后,需要进行静态时序分析。

静态时序分析是通过使用时序分析工具对设计进行分析,以确保时序约束得到满足。

时序约束包括时钟频率、数据路径延迟、时钟间隔等。

静态时序分析的目的是保证设计在时序约束下能够正常工作。

fpga硬件电路设计书籍

fpga硬件电路设计书籍FPGA (Field-Programmable Gate Array) 是一种可编程逻辑设备,用于实现数字电路的硬件设计。

它由逻辑门阵列、可编程连线和输入/输出引脚组成,可以根据用户的需求进行编程和重新配置。

随着FPGA技术的发展和应用越来越广泛,对于硬件电路设计方面的知识和技能也日益重要。

在本文中,我将介绍一些关于FPGA硬件电路设计的经典书籍,帮助读者更好地了解和掌握该领域的知识。

1. "FPGA原理与VHDL设计"(编著:曹志鹏)《FPGA原理与VHDL设计》是一本介绍FPGA硬件设计基础知识的经典教材。

本书从理论与实践的角度,首先详细介绍了FPGA的基本原理,包括逻辑门阵列、可编程连线和I/O引脚等。

然后,结合VHDL硬件描述语言,讲解了FPGA的编程方法和流程,以及常用的硬件设计技术和方法。

最后,通过实例和实验,让读者动手实践,加深对FPGA硬件设计的理解和应用能力。

2. "FPGA设计从入门到精通"(编著:郑宝山)《FPGA设计从入门到精通》是一本适合初学者的FPGA硬件电路设计书籍。

本书首先介绍了FPGA的基本概念和原理,包括FPGA的结构、工作原理和发展历程等。

然后,通过详细的实例和步骤,引导读者进行FPGA的环境搭建、编程工具的使用和简单电路的设计。

同时,本书还介绍了FPGA与其他硬件设备的连接和通信方式,以及FPGA在数字信号处理、通信系统和嵌入式系统中的应用。

通过逐步学习和实践,读者可以从入门到精通掌握FPGA硬件电路设计的核心技术和方法。

3. "FPGA高级设计方法与实践"(编著:张彦卓)《FPGA高级设计方法与实践》是一本面向有一定FPGA硬件设计基础的读者的进阶教材。

本书首先回顾了FPGA的基本原理和常用设计方法,然后深入讲解了FPGA高级设计的技术和方法。

其中包括时序控制、高速接口设计、时钟管理、电源管理以及设计调优等方面的内容。

fpga 设计步骤

fpga 设计步骤

FPGA(可编程逻辑门阵列)设计步骤包括以下几个主要阶段:

1. 确定需求:明确需要实现的功能和性能要求。

2. 设计规划:选择适合的FPGA平台、开发工具和开发语言。

3. 编写RTL(Register Transfer Level)代码:使用HDL(硬件描述语言)如VHDL或Verilog编写设计代码。

4. 仿真验证:使用仿真工具模拟设计的功能和性能,通过验证测试向设计中添加调整和修正。

5. 进行综合(Synthesis):将RTL代码转化为门级电路表示。

6. 进行布局布线(Place and Route):根据FPGA架构的要求

将设计映射到FPGA中。

7. 生成位流文件(Bitstream):将布局布线后的设计编译为可配置FPGA的位流文件。

8. 下载位流文件:将位流文件下载到目标FPGA设备。

9. 进行时序分析:对设计进行时序分析并验证。

如果不符合时序要求,可能需要进行时序优化。

10. 硬件验证:将设计加载到FPGA并进行功能和性能测试。

11. 调试和优化:在实际测试中发现问题,并对设计进行调试和优化。

12. 文档编写:根据项目要求编写设计文档,包括设计细节、测试方法和结果等。

需要注意的是,以上步骤可以根据具体的项目和需求进行调整和扩展。

此外,熟悉FPGA架构和相关开发工具以及编程语言是进行FPGA设计的基本要求。

FPGA学习步骤

FPGA学习步骤FPGA(Field-Programmable Gate Array)是可编程逻辑器件的一种,它具有高度可编程性和灵活性,被广泛应用于数字电路设计和嵌入式系统开发。

学习FPGA可以使我们了解数字电路的原理和设计方法,并能够利用FPGA开发和优化各种应用。

下面是一个FPGA学习的步骤,帮助你逐步了解FPGA的原理和应用。

步骤1:掌握数字电路基础知识FPGA是用于设计数字电路的器件,因此首先需要掌握数字电路的基础知识。

学习数字电路的基本逻辑门、布尔代数和组合逻辑电路等概念,理解时序电路、存储器和状态机等高级概念。

步骤2:了解FPGA的原理和架构学习FPGA的原理和架构有助于理解FPGA是如何实现数字电路的。

学习FPGA的片上资源,如查找表、触发器和运算器等,以及FPGA的内部连接结构。

还可以探索FPGA的编程方式,包括寄存器传输级综合(RTL)和硬件描述语言(HDL)等。

步骤3:学习硬件描述语言(HDL)硬件描述语言是FPGA设计的基础,通常使用的HDL是Verilog和VHDL。

学习HDL的语法和基本结构,并掌握如何使用HDL描述数字电路。

可以通过书籍、在线教程和实践项目等方式学习HDL。

步骤4:使用FPGA开发工具步骤5:完成简单的FPGA设计项目开始进行一些简单的FPGA设计项目,如实现基本的逻辑门、组合逻辑电路和时序电路等。

通过这些项目,学会如何使用HDL描述和实现数字电路,如何利用FPGA的资源和工具进行设计和优化。

步骤6:进阶学习FPGA应用进一步学习FPGA的应用,例如数字信号处理(DSP)、图像处理、通信系统和嵌入式系统等。

根据自己的兴趣和需求选择相应的应用领域,并实践相关项目。

学习如何使用FPGA实现更复杂的功能和算法,并了解相应的设计方法和技术。

步骤7:参加竞赛或项目参加FPGA设计竞赛或实际项目有助于提升自己的FPGA设计能力。

通过参赛或项目,可以锻炼自己的团队合作能力和解决问题的能力,并将学到的知识应用到实际应用中。

FPGA设计及QUARTUS_II教程

FPGA设计及QUARTUS_II教程在进行FPGA设计之前,需要先了解FPGA的基本结构和原理,掌握硬件描述语言(HDL)的基本知识。

常用的HDL语言包括VHDL和Verilog,它们用于描述数字系统的结构和行为。

在FPGA设计过程中,通常包括以下几个步骤:1.设计规划:确定需求和功能,对设计进行整体规划和分析。

2.模块设计:根据设计需求,将设计分解为多个模块并进行详细设计。

3.模块仿真:使用仿真工具对各个模块进行功能验证,确保设计的正确性。

4.综合和优化:使用综合工具将HDL代码转换为逻辑门电路,并对其进行优化。

5.布局布线:将综合后的逻辑门电路映射到FPGA芯片上,并进行布局布线操作。

6.静态时序分析:对布局布线后的设计进行静态时序分析,确保设计满足时序要求。

QUARTUS II是一款常用的FPGA设计软件,由Intel公司开发。

它提供了丰富的开发工具和资源,可用于设计、仿真、综合和验证FPGA设计。

QUARTUS II支持VHDL和Verilog等HDL语言,具有强大的综合和优化功能,并提供了直观的图形界面和丰富的调试工具。

QUARTUSII教程通常包含以下内容:1.软件安装和配置:介绍QUARTUSII软件的安装和配置过程,包括选择适合的版本、设置路径和环境变量等。

2.工程创建和管理:介绍如何创建和管理QUARTUSII工程,包括添加文件、设置工作目录和文件关系等。

4.设计流程:详细介绍FPGA设计的各个步骤和操作,包括模块设计、仿真、综合、布局布线和验证等。

5.高级特性:介绍QUARTUSII软件的高级功能和特性,包括时序分析、时钟域管理和约束等。

6.项目实例:提供一些实际的FPGA设计项目实例,让读者通过实践来掌握QUARTUSII的使用技巧和方法。

总之,FPGA设计及QUARTUSII教程是帮助读者快速入门和掌握FPGA设计和QUARTUSII软件的重要资源,通过学习和实践可以提升设计能力和项目开发效率。

FPGA典型设计方案精华汇总

FPGA典型设计方案精华汇总FPGA(现场可编程逻辑阵列)是一种可重构硬件设备,它可以根据用户的需求进行定制化的硬件设计。

FPGA在各个领域,如通信、计算机视觉、嵌入式系统等都得到了广泛的应用。

在设计FPGA时,能够选择合适的设计方案非常重要,下面是一些FPGA设计中的典型方案的精华汇总。

1.浮点加法器:浮点加法器是一种用来实现浮点数相加的重要组件。

在FPGA设计中,使用阵列乘法器和加法器可以实现浮点数相加的功能。

同时,还可以使用流水线技术提高浮点加法器的性能。

此外,还需要注意设计中的浮点数格式、舍入策略等问题。

2. 快速傅里叶变换(FFT):FFT是一种用来对离散数据进行频域分析的方法。

在FPGA设计中,可以使用蝶形运算单元(butterfly)来实现FFT。

通过并行计算和流水线技术,可以提高FFT的性能。

3.加密算法:加密算法在信息安全领域中起到非常重要的作用。

在FPGA设计中,可以使用硬件加速器来实现快速的加密算法。

同时,还需要考虑加密算法的安全性和延迟等因素。

4.VGA显示控制器:VGA显示控制器是一种用来控制显示器输出的组件。

在FPGA设计中,可以使用时序电路和状态机来实现VGA显示控制器。

通过设置合适的显示分辨率和刷新率,可以实现高质量的图像显示。

5.视频编码器:视频编码器是一种将视频信号进行压缩的组件。

在FPGA设计中,可以使用视频编码标准(如H.264)来实现视频编码器。

通过使用硬件并行计算和流水线技术,可以实现实时的视频编码。

6.数字滤波器:数字滤波器是一种用来处理数字信号的重要组件。

在FPGA设计中,可以使用FIR(有限脉冲响应)滤波器和IIR(无限脉冲响应)滤波器来实现数字滤波器。

通过优化滤波器的结构和算法,可以实现高性能和低延迟的数字信号处理。

7. 通信接口:通信接口是一种用来实现不同设备之间数据传输的组件。

在FPGA设计中,可以使用串行通信接口(如UART、SPI、I2C)和并行通信接口(如Ethernet、PCIe)来实现高速数据传输。

fpga 高位宽设计方法

fpga 高位宽设计方法

在FPGA中进行高位宽设计可以采用以下方法:

1. 流水线设计:通过设置多个流水线来拆分逻辑,这通常适用于调用IP核的情况。

2. 逻辑拆分:从设计代码的开始阶段就主动对逻辑进行拆分,特别是当面临大位宽加法器的情况。

例如,可以通过二分法流水线来拆分加法器,即将一个16bit加法器拆分为两个8bit加法器,中间插入寄存器。

3. 数据截位:对于高位宽的数据,可以通过截位的方式来处理。

具体的截位方式包括负数直接截位后+1(所有数都按绝对值取floor)、Truncate(正数取floor,负数按绝对值取ceil)和Rounding(所有数按绝对值取四舍五入)等。

以上方法仅供参考,建议咨询FPGA设计专家或查阅相关文献资料,获取更准确的信息。

fpga高级设计技巧

fpga高级设计技巧FPGA(现场可编程门阵列)的高级设计技巧包括以下几点:1. 时钟树设计:时钟树是FPGA设计中非常关键的部分,因为它决定了系统的运行速度和稳定性。

要遵循单一时钟、时钟域划分、跨时钟域信号同步处理等原则,并尽可能使用FPGA内部的PLL、DLL和MMCM等工具来产生时钟。

2. 面积与速度的平衡:面积和速度是FPGA设计的两个重要指标,它们之间需要达到平衡。

在满足设计时序要求的前提下,应尽量占用最小的芯片面积,或者在规定面积下使设计的时序余量更大、频率更高。

3. 异步设计避免:尽可能采用同步设计,因为异步设计可能导致时序问题和其他难以预料的问题。

4. 功能模块复用:如果一个设计有较大的时序余量,可以通过功能模块的复用来减少整个设计消耗的芯片面积。

5. 数据流串并转换与并行复制:如果设计的时序要求很高,无法达到设计频率,可以通过将数据流进行串并转换,并行复制多个操作模块,采取乒乓操作和串并转换的思想运行。

6. 充分理解硬件语言:深入理解硬件描述语言(如VHDL或Verilog)以及它们是如何映射到FPGA上的逻辑资源的。

这有助于更好地优化设计,使其更有效地使用FPGA的资源。

7. 代码优化:优化硬件描述语言代码以减少资源使用和提高性能。

这可能包括减少不必要的逻辑门、优化算法、使用流水线设计等。

8. 仿真和测试:在设计过程中进行充分的仿真和测试,确保设计的正确性和性能。

这可以尽早发现并修复问题,减少后期调试的时间和成本。

9. 工具的使用:利用FPGA厂商提供的EDA(电子设计自动化)工具进行设计、布局和布线。

这些工具通常包括一些高级特性,如时序分析、功耗分析、布局优化等。

10. 文档和规范编写:在设计过程中及时编写和更新文档,记录设计决策、模块接口、时序约束等重要信息。

这有助于维护设计的可读性和可维护性,方便后续的修改和扩展。

遵循这些高级技巧,可以帮助您更有效地进行FPGA设计,提高系统的性能、稳定性和可维护性。

FPGA典型设计方案精华汇总

FPGA典型设计方案精华汇总FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,可以通过编程实现各种数字逻辑电路。

它具有灵活性高、性能强、功耗低的特点,因此被广泛应用于各种领域的设计中。

下面是一些FPGA典型设计方案的精华汇总。

1.图像处理:FPGA在图像处理领域中得到广泛应用。

通过在FPGA芯片上实现图像处理算法,可以实现高速、低延迟的图像处理。

典型的图像处理方案包括图像滤波、边缘检测、图像分割等。

2.数字信号处理:FPGA在数字信号处理领域中也有很多应用。

通过在FPGA上实现数字信号处理算法,可以实现快速的实时信号处理。

典型的数字信号处理方案包括音频处理、视频处理、雷达信号处理等。

3.通信系统:FPGA在通信系统中也有重要应用。

通过在FPGA上实现通信协议、调制解调算法等,可以实现高速、高稳定性的通信系统。

典型的通信系统方案包括无线通信、光纤通信、卫星通信等。

4.自动驾驶:FPGA在自动驾驶领域中也有广泛应用。

通过在FPGA上实现图像处理算法、传感器数据融合算法等,可以实现高性能的自动驾驶系统。

典型的自动驾驶方案包括图像识别、目标跟踪、路径规划等。

5.工业控制:FPGA在工业控制领域中也有很多应用。

通过在FPGA上实现实时控制算法、数据采集算法等,可以实现高精度、高可靠性的工业控制系统。

典型的工业控制方案包括机器人控制、自动化生产线控制等。

6.教育培训:FPGA在教育培训领域中也得到广泛应用。

通过在FPGA 上进行实验和仿真,可以帮助学生理解数字电路的原理和设计方法,提高他们的实际操作能力。

基于FPGA的高性能加解密算法实现研究

基于FPGA的高性能加解密算法实现研究第一章:研究背景在当代信息技术高度发达的背景下,数据传递与保护的重要性愈加凸显。

而在传统软件实现加解密算法的方式中,由于软件本身的复杂度及其对计算机性能的依赖,安全性与效率往往难以同时得到保障。

基于此,FPGA作为硬件实现的可编程逻辑器件,可通过并行计算和快速运算等优势,提高加解密算法运算速度且更加安全可靠。

因此,对基于FPGA的高性能加解密算法的研究和探究具有重要意义。

第二章:FPGA与加解密算法2.1 FPGA概述FPGA(Field Programmable Gate Array)是一种可编程逻辑器件。

其由多个可编程逻辑单元可通过互联网络进行连接而构成。

与传统的ASIC相比,FPGA具有可编程性、灵活性、快速性和普适性等优势,因此具备广泛的应用场景。

2.2 FPGA在加解密算法中的应用相较于纯软件方式实现,FPGA中实现加解密算法可显著提高运算速度,同时保证更高的安全性。

此外,FPGA还可通过并行计算和裸机执行等方式优化加解密算法的实现。

目前,FPGA在对称加密和非对称加密算法以及哈希算法等方面已经得到了广泛的应用。

第三章:基于FPGA的高性能加解密算法实现3.1 对称加密算法实现对称加密算法是数据加密技术中的一种常见方式。

其通过同一个密钥对数据的加密和解密进行控制。

在FPGA实现对称加密算法时,可参考AES算法和DES算法进行设计。

其中,AES算法在FPGA实现中常采用32比特模式。

3.2 非对称加密算法实现与对称加密相比,非对称加密算法的设计则更为复杂。

非对称加密算法常见的是RSA算法。

其采用两个密钥,即公钥和私钥。

公钥用于对数据进行加密,而私钥则仅限于对密文进行解密。

在FPGA实现中,非对称加密算法的实现较为复杂,需要更加深入的硬件设计。

因此,FPGA中一般采用对称加密算法。

3.3 哈希算法实现哈希算法是一种能够将任意长度数据变换为固定长度摘要信息的加密算法。

【2】FPGA设计进阶篇(大工程设计)

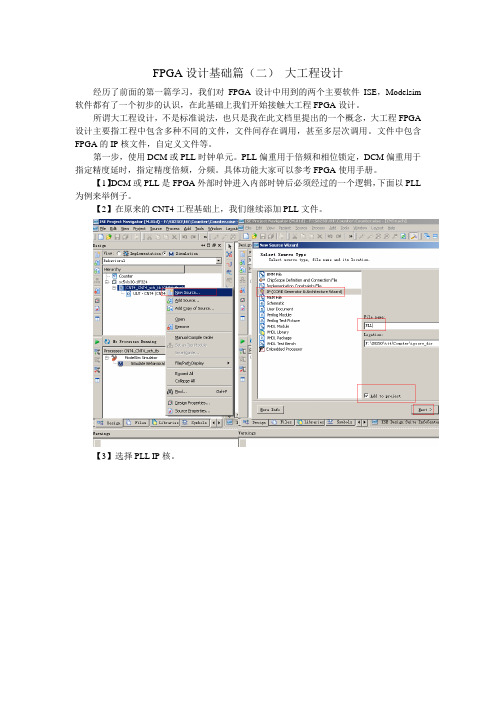

FPGA设计基础篇(二)大工程设计经历了前面的第一篇学习,我们对FPGA设计中用到的两个主要软件ISE,Modelsim 软件都有了一个初步的认识,在此基础上我们开始接触大工程FPGA设计。

所谓大工程设计,不是标准说法,也只是我在此文档里提出的一个概念,大工程FPGA 设计主要指工程中包含多种不同的文件,文件间存在调用,甚至多层次调用。

文件中包含FPGA的IP核文件,自定义文件等。

第一步,使用DCM或PLL时钟单元。

PLL偏重用于倍频和相位锁定,DCM偏重用于指定精度延时,指定精度倍频,分频。

具体功能大家可以参考FPGA使用手册。

【1】DCM或PLL是FPGA外部时钟进入内部时钟后必须经过的一个逻辑,下面以PLL 为例来举例子。

【2】在原来的CNT4工程基础上,我们继续添加PLL文件。

【3】选择PLL IP核。

【4】点击Finish 后,选择Verilog,点击OK。

等待打开PLL配置界面。

【5】配置第一面,产生三个clk输出【6】第二面设置【7】其它默认设置,点击Next,直到Finish。

【8】由于我们top层是schematic ,所以将产生的PLL ip也产生一个Schematic Symbol。

【9】点击Symbol标签,添加新器件到右边设计空白处。

【10】接下来就可以参考第一篇中添加管脚并且重新命名了,RST管脚可以连接到一起。

计数器的时钟用PLL产生的CLK400。

【11】添加新的管脚约束后可以开始Implement。

一个简单的FPGA大工程产生了。

第二步:将设计的最top层文件产生Symbol供更大的工程调用。

比如将CNT4产生一个Symbol供更大工程设计调用。

【1】创建CNT4的symbol。

为了继续使用CLK400管脚,我们将其引出,重新CreateSymbol。

【2】下面我们新建一个CNT20的project。

创建方法与第一篇中相同。

【3】新建一个CNT20.sch的设计文件,和CNT20.ucf约束文件,方法参考第一篇。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1FPGA 设计高级技巧贺光辉清华大学电子工程系hgh02@ 2目标掌握FPGA 的基本设计原则 乒乓结构、流水线设计异步时钟域的处理状态机的设计毛刺的消除掌握FPGA 设计的注意事项 从文档到设计完成从设计实例加深设计思想3提纲FPGA 的基本设计原则 FPGA 设计的注意事项 设计实例交织器数据适配器基于PCI 接口的数字电视计算机终端通信接口芯片4推荐书籍VerilogVerilog 数字系统设计教程夏宇闻北京航天航空大学出版社 硬件描述语言Verilog 刘明业等译清华大学出版社 FPGAAltera FPGA/CPLD 设计(高级篇)EDA 先锋工作室人民邮电出版社IC 设计Reuse methodology manual for system-on-a-chip designs 3rd ed. Michael Keating, Pierre Bricaud .片上系统:可重用设计方法学沈戈,等译电子工业出版社, 2004Writing testbenches :functional verification of 5推荐文章/papers/ Verilog Coding Styles For Improved Simulation Efficiency State Machine Coding Styles for Synthesis Synthesis and Scripting Techniques for Designing Multi-Asynchronous Clock DesignsSynchronous Resets? Asynchronous Resets? I am so confused!Nonblocking Assignments in Verilog Synthesis, Coding Styles That Kill!6FPGA 设计的两条思路 控制通路有限状态机的设计异步时钟域的处理数据通路关注算法到结构的映射7FPGA 设计基本原则8目标完成本单元的学习后你将会 加深FPGA 设计常用的设计思想和技巧了解为什么才用流水线设计 掌握处理异步时钟的方法 掌握状态机的设计了解毛刺消除的方法9FPGA 设计基本原则 乒乓结构和流水线设计 异步时钟的处理同步状态机的设计毛刺的消除10乒乓操作应用于数据流控制•通过“输入数据选择单元”和“输出数据选择单元”按节拍、相互配合的切换,将经过缓冲的数据流没有停顿地送到“数据流运算处理模块”进行运算与处理。

•节约缓存空间11数据通道-多级RAM 乒乓结构以定长包为单位的处理提高数据处理的并行性提高数据传输速率隔离时钟域之间的冲突66MHz, 33MHz,8MHz双口RAM 与同步器12流水线操作流水线技术几乎是最常用的提供系统工作速率的强有力手段。

它是面积换取速度思想的又一种具体体现。

13流水线操作考虑一个电路每个时钟周期执行N 个操作,工作频率为F 。

我们可以认为吞吐量为N*F ops/sec 。

Pipeline 本质上是通过增加F 来提高吞吐量,达到latency 和area 的tradeoff 。

什么决定了最高工作频率呢? 回忆static timing analysis在flip flops 之间的最大延时14流水线操作(STA ) 时序电路之间的组合电路延时决定整个电路的速度,即最大工作时钟频率,故不可太复杂。

最小时钟周期:T=Tco+Tdelay+Tsetup 最快时钟频率:F= 1/T 15解决方式(PIPELINE 技术)通过将Algorithm分为两个部分,在中间插入寄存器16流水线技术其思想是利用寄存器将一条长路径切分成几段小路径,从而达到提高工作速率的作用。

假设原路径延时为t ,加入2级流水线并且假设路径切割均匀,则路径延时可以减少到约t/3,从而系统速率可以提高到原来的3倍左右。

当然要注意的是输出同时会往后推迟3个时钟周期。

所以采用流水线技术时,要记得进行时序调整。

17流水线设计例子设计din1 + din2 + din3 + din4结果输出给dout。

din1din2din3din4dout 18PIPELINE 程序实例未用PIPELINE 技术前的程序: Always @(posedge clk)if((a+b+c) == d) ……….. 采用PIPELINE 技术后的程序: always @(posedge clk) begine <= a+b+c;if(e ==d)…………..end19FPGA 设计基本原则乒乓结构和流水线设计 异步时钟的处理同步状态机的设计毛刺的消除20多时钟系统许多系统要求在同一设计内采用多时钟,最常见的例子是两个异步微处理器之间的接口,或微处理器和异步通信通道的接口。

由于两个时钟信号之间要求一定的建立和保持时间,所以上述应用引进了附加的定时约束条件,它们会要求将某些异步信号同步化。

21多时钟系统设计如果一个系统中存在多个独立(异步)时钟,并且存在多时钟域(clock domain)之间的信号传输,那么电路会出现亚稳态。

din aclkbclkadat bdat aclkadatbclkbdat22•Sync_a2b 消除亚稳态----同步化din aclkbclk adat bdat bdat1bdat2aclkadatbclkbdat1bdat123亚稳态分析出现亚稳态的平均时间间隔常用“平均无故障时间”(MTBF ,Mean Time Between Failure )来表示。

单个触发器的MTBF 为温度、电压、辐射等因素都对MTBF 有影响24两个寄存器方案分析优点:–实现简单.–成本低.•缺点:–不能完全消除亚稳态–导致延时增加.25同步化26多时钟系统在许多应用中只将异步信号同步化还是不够的,当系统中有两个或两个以上非同源时钟的时候,数据的建立和保持时间很难得到保证,设计人员将面临复杂的时间分析问题。

可以将所有非同源时钟同步化。

这时就需要使用带使能端的D 触发器,并引入一个高频时钟来实现信号的同步化。

27同步化任意非同源时钟Q D PRN CLRNENA 3M_ENData in Data outQ D PRN CLRNENA Data in Data outQ D PRN CLRN Q D PRN CLRN20M_CLKQ D PRN CLRN Q D PRN CLRN3M_CLK 5M_CLK 5M_EN28异步多时钟系统模型aClk Logic aClk Logic bClkLogicbClk Logic Sync_a2b Sync_a2baSigaClk bClkaClk Domain bClk DomainbSig 29注意其信号命名和模块划分方法 这种信号命名和模块划分的方法有如下优点:有利于检查信号所通过的时钟域; 有利于各模块进行单独的静态时序分析;有利于在静态时序分析中快速地设定false path ;•异步信号穿越时钟域时,这些信号与异步时钟之间的相位关系数是无穷的,所以在整个系统静态时序分析时必须忽略这些信号路径。

30数据接口的同步方法输入、输出的延时(芯片间、PCB 布线、一些驱动接口元件的延时等)不可测,或者有可能变动的条件下,如何完成数据同步?最常用的缓存单元是DPRAM 和FIFO ,在输入端口使用上级时钟写数据,在输出端口使用本级时钟读数据。

31多时钟系统设计的经典案例-异步FIFO关于多时钟域数字系统设计的方法,可以参考《Synthesis and Scripting Techniques for Designing Multi-Asynchronous Clock Designs 》,Clifford E. Cummings 。

32思考当输入信号小于一个时钟周期,比如快时钟域的信号进入慢时钟域信号33时钟质量保证时钟的纯净:时钟最好不要通过任何组合电路,或者不要用组合电路产生时钟;时钟的单一:数字系统设计时,应该尽量减少时钟的数目,最好整个系统只有一个时钟。

34异步设计的注意事项小结 注意使用同步化电路来对异步信号进行同步; 采用FIFO 方式是解决问题的最好的方法,但需要注意FIFO 的深度的设定以及FIFO 门限的控制; 进行科学的模块划分和信号命名; 尽量减少握手控制信号的数目,以避免同步化造成的信号拉伸而破坏控制信号之间的相位关系; 快时钟域信号进入慢时钟域时,要注意信号丢失的避免和检测;35FPGA 设计基本原则乒乓结构和流水线设计 异步时钟的处理同步状态机的设计毛刺的消除36同步状态机的概念状态寄存器由一组触发器组成,用来记忆当前状态;所有触发器都连接在一个时钟信号上;状态的改变只在时钟沿到来时才发生,由触发器类型决定是上升沿还是下降沿; 驱动方程决定了状态机的下一个状态,驱动方程是输入信号和当前状态的组合函数;状态机的输出是由输出函数得到,它也是当前状态和输入信号的函数;目前一般都采用D 触发器进行状态机的设计。

37同步状态机的概念Moore状态机:输出仅与当前状态有关Melay状态机:输出与当前状态和输入信号都有关38Regs 译码ClkPresent_state Q(n)Next_state Q(n+1)译码DataOut Z(n)din 状态机分类Moore 机:输出仅是状态的译码39Regs 译码ClkPresent_state Q(n)Next_state Q(n+1)译码DataOutZ(n)din状态机分类Moore 机:输出仅是状态的函数Mealy 机:输出是状态和输入的函数40状态机的表示方法1方法一:状态转换表…………0000000100010000输出下一状态当前状态输入41状态机的表示方法2方法二:算法流程图方法与软件程序的流程图类似状态转换表和算法流程图都不适合复杂系统的设计42状态机的表示方法3方法三:状态转换图这是最流行的表示方法状态1状态4状态2状态3入/出入入入/出/出/出Moore 条件控制定序直接控制定序43状态机的表示方法3方法三:状态转换图这是最流行的示方法状态1状态4状态2状态3入/出入入入/出/出/出/出Mealy 条件控制定序直接控制定序44状态机的应用设计例子:设计一个二进制序列检测器,当检测到10110序列时,就输出1(一个时钟周期的脉冲)。

其他情况下输出0。

规定检测到一次之后,检测器复位到最初始的状态,重新从头检测。

如下所示:输入:01101101101100输出:0000000100000145状态转换图设计(Moore )01S0/0S1/0S2/0S3/0S4/0S5/1Reset 110011010010110s1s2s3s4s5s0问题1:如何保证状态机在初始时状态为s0?问题2:在状态机跑飞,即脱离有效状态(s0—s5)时,如何使状态机能恢复工作Sx/046状态转换图设计(Mealy)S0S1S2S3S4S5Reset 100110100101sX /0/0/0/0/0/0/0/0/0/1/0/001110s1s2s3s4s5s0/00/1s047One Hot State Machine What is One Hoteach state within the State Machine is represent by ONE BITe.g. Four State Machine : state0, state1, state2, state3 can be represented by–4 bits : 1000 0100 0010 0001 (One Hot) One Hot State Machinemainly gives us performancebut it consume more logic48Binary State MachineWhat is Binary State Machineeach state within the State Machine is encode by bits e.g. Four State Machine : state0, state1, state2, state3 can be represented by–2 bits : 00 01 10 11 (Binary)Binary State Machine–mainly consume less logic–but the performance usually is slower–can be more than one bit change from state to state •(01 -> 10) both bits changed49Gray Code State Machine What is Grey Code State Machine each state within the State Machine is encode by bitse.g. Four State Machine : state0, state1, state2, state3 can be represented by–2 bits : 00 01 11 10 (Gray Code)Gray Code State Machinemainly consume less logicbut the performance usually is slower ONLY one bit change from state to state (01 -> 11) one bit changed 50One-hot 编码(优点) 速度快:用于对下一个状态的译码和输出信号的译码所需要的组合电路很小,因此电路速度较快。