东南大学“至善”队技术报告

挑战杯历届全国特等奖、一等奖作品

国家历届挑战杯特等奖、一等奖作品第一届“挑战杯”全国大学生课外学术科技作品竞赛由清华大学于1989年承办:清华大学摘得“挑战杯”一等奖获奖名单如下:北京大学刘闯在地理信息系统中土地评价模型的建模研究清华大学陈邕涛等中华学习机CAI软件开发工具清华大学吴丹策等电脑照相及微机图像处理系统清华大学金龙文等竹草木漂白系列新工艺的研究华中理工大学吴敏等建筑方案“将居民安置在发种种的小镇中”新疆石河子医学院王惠民门脉系的内分泌学意义第二届“挑战杯”全国大学生课外学术科技作品竞赛由浙江大学于1991年承办:上海交通大学摘得“挑战杯”一等奖获奖名单如下:浙江大学微机遥感图像显示操作及处理系统郑州大学方兴未艾福利企业国防科技大学Hyperview(v1.01)系统北方交通大学铁道部及各地区财务基准收益率的测定上海交通大学光纤中自然聚焦光场的环形结构上海医科大学他莫昔芬枸橡酸新工艺的研究及其原理的讨论上海交通大学农村民居建筑调研华中理工大学微量泄漏检测仪北京航天航空大学简繁五笔汉字系统及其为通道汉卡四川成都电子科技大学通信母板自动测试系统第三届“挑战杯”全国大学生课外学术科技作品竞赛由上海交通大学于1993年承办:北京大学获得“挑战杯”一等奖获奖名单如下:北京大学基于具有更佳频率分辨率的正交子波变换及自适应VQ技术的图像压缩北京大学危机与出路.....从九二深圳股市看中国B股清华大学铁基合金薄膜中铁原子磁矩的反常增大等作品获奖东北大学超级电子档案系统吉林大学镧系离子荧光探针探测天花粉蛋白结构和分子间能量传递武汉大学信安-I型计算机网络信息保护系统浙江大学PLT陶瓷期间合金电极成型新技术四川师范大学四川西部蝶类资源调查天津财经学院建立会计逻辑学体系的构想北方交通大学多渠道多方式利用外资发展我国的铁路的探讨中国科技大学本原矩阵指数的一个猜想证明上海交通大学浦东开发区环境调查及综合防治上海医科大学Z曲线显示和分析DNA系列的直观工具南京理工大学激光全息场再现图像的离子自动检测华东理工大学化学气相淀积反应器中超细粒子形成过程研究及产物形态控制华中理工大学将城市引入农村,农村引入城市-繁忙江南水乡的僻静水上花园齐齐哈尔工学院黑龙江省甜菜糖业产品结构调整战略研究报告北京航空航天大学空中机器人系统北京航空航天大学智能化电力电容在线检测仪第四届“挑战杯”全国大学生课外学术科技作品竞赛由武汉大学于1995年承办:复旦大学摘得“挑战杯”一等奖获奖名单如下:复旦大学载能束合成新型共价氮化碳超硬材料研究河北大学BaZrXTil-03固溶体的合成,结构与物性武汉大学高性能镍/金属氢化物电池和锂离子蓄电池暨南大学物体三维形貌测试技术的研究等作品获奖北京大学物体三维形貌测试技术的研究云南大学村落文化贫困地区农村妇女生育健康服务模式——武定县中山大学《劳动法》与外来工的权益保障北京大学光WDM(波分复用)中的激光波长控制清华大学高速中西文激光打印/照排控制器北京师范大学论教师的教学效能感南京理工大学走出困境再创辉煌——重庆军工企业走上发展之路的启示北京科技大学双拇指型多指手大连理工大学大学物理实验CAI教学软件包华中理式大学新型宜人化计算机辅助设计绘图系统——开目CAD华北师范大学松树花粉的培养和它萌发时营养万分的变化吉林工业大学梁的大挠度强迫振动的非线性响应的分析的新方法苏州丝绸工学院真丝新村料的研制及产品开发北京航天航空大学遥控多用途空中飞行平台第五届“挑战杯”全国大学生课外学术科技作品竞赛由南京理工大学于1997年承办:清华大学摘得“挑战杯”一等奖获奖名单清华大学《十字路口看乡企》——中国农村乡镇企业转制问题调查报告清华大学蛋白质去折叠与折叠机制的研究清华大学基于界面设计的多层膜技术获得新型合金清华大学文本无关的说话人语音语音识别系统北京大学两家名油企业生活后勤体制变革北京大学股市中操纵市场行为及防范的法律对策北京大学 Runge—lenz矢量与升降算子武汉大学武汉市再就业工程调研报告南京理工大学小波变换中的视觉门限模型和图像的层次分割优生权编码复旦大学通用工件识别系统生成工具VisionExport南京大学水煤奖添加剂NDF上海交通大学柔体机器人(组件)云南大学边疆民族地区生态环境变迁与脱贫致富——云南省怒江傈族自治州经济开发新模式研究北京航空航天大学三翼面微型无人驾驶验证机国科学技术大学酶反应的理论研究——方法及在葡萄糖异构酶中的应用四川联合大学利用红矾母液和铬酐下脚料生产蒙囿吸收铬鞣粉剂石油大学河南西峡恐龙蛋化石层及恐龙绝灭原因初探中国政法大学青少年创造能力培养和知识产权保护教育调查报告吉林工业大学轿车车身焊装用微机控制自动螺柱焊机第六届“挑战杯”全国大学生课外学术科技作品竞赛由重庆大学于1999年承办:复旦大学获得“挑战杯”一、二等奖获奖名单北京航空航天大学鱼类运动仿生研究及其柔体舰艇模型东北大学微型足球机器人系统江苏理工大学高性能铝合金材料的应用研究复旦大学指间区纹的进化和遗传南京大学体内可降解吸收医用高分子材料及其制品大连海事大学椭圆波导中的场中国科学技术大学关于α和β环糊精与苯衍生物之间的包含驱动力及包合结构的新模型上海交通大学面向软件无线电的数字发射机(激励器部分)东南大学中文个人数字助理(ASICPDA-2000)北方交通大学大规模发展交通仿真及公交智能调度指挥平台开发重庆大学 AV-100S型双面表格自动阅读机苏州大学真丝新材料-差别化柞桑弹力真丝的研制与产品开发北京大学从法院状告新闻媒体谈起——一起名誉侵权官司引发的思考复旦大学适应环境变化,构建新型企业——上海国有外贸企业改革调查华东师范大学师范大学生专业思想状况调查哈尔滨理工大学侵华日军731部队罪证网站国立华侨大学基于可持续发展的水资源定价试探华中理工大学基于针式传感器的多功能扫描探针显微装置南京大学电动自行车综合测试仪吉林工学院轿车深冲件应用国产冷轧IF钢板研究江苏理工大学 4LGT-130型稻麦联合收割机的研制重庆大学虚拟式小波变换信号分析仪重庆医科大学手握(傻瓜)式纯水检测仪华东理工大学清洁化生产取代芳胺磺酸中国科学技术大学超支化聚(胺-酯)的合成及其光固化性能研究吉林工学院汽车内饰件粘合剂的研制同济大学茶多酚提取新工艺及其系列产品开发无锡轻工大学 UASB-CAAS系统处理高浓度有机废水的工程技术无锡轻工大学维生素在光滑球拟酵母发酵生产丙铜酸中的关键作用广西师范大学湘西洛塔植物区系及开发利用研究重庆大学心肌收缩能力的一种无伤性检测和评估方法研究山西大学 Hie Senberg 方程的换算表示复旦大学国内首家微波硫灯的研制桂林工学院 NETWARE高级编程接口及未公开的核心技术武汉交通科技大学二维条码自动识别应用技术研究西安电子科技大学高速分组无线网长沙铁道学院空调客车状态参数集中管理系统成都电子科技大学校园网上的学生管理信息系统中国科学技术大学基于中文实时语音技术的有声电子系统北京理工大学《圣林3.0》实时三维图象引擎武汉大学系列安全容错智能卡应用系统重庆邮电学院多链路中国NO.7的信令分析仪华中理工大学基于LAN/INTERNET的H.323视频会议系统西安电子科技大学自控光阀及其在防弧光领域的应用清华大学细菌基因快速鉴测仪中国地质大学(武汉)油气资源储量评价系统华东理工大学无规共聚高分子相平衡的研究武汉大学新型固相微萃取探针复旦大学智能酒气电子鼻山东工业大学弹性管束热交换器的结构、动态特性及自动控制过程仿真重庆建筑大学新型高效掺合料北京大学社区的构成清华大学走近21世纪的中国环境技术中国人民大学面对挑战,中国对外经济的立足点北京师范大学困境与出路——城镇企业下岗职工再就业状况调查北京师范大学面向21世纪发展远程教育——关于中国远程教育中若干问题的调查与思考中国政法大学中国农民法律意识现状探讨西南政法大学典权的过程分析及性质研究山西大学刚玉之路河海大学江苏省水资源可持结发展模式探讨中国药科大学我国药品价格现状分析及管理对策的研究杭州商学院论国有企业激励机制湖南财经学院买方市场:高教与经济增长—发展高教是推动经济增长的重要途径华中农业大学农业科技推广中的几点思考第七届“挑战杯”全国大学生课外学术科技作品竞赛由西安交通大学于2001年承办:复旦大学和东南大学获得“挑战杯”特等奖北京大学锆基固体电解质纳米晶薄膜材料的制备及微结构与电学性质研究清华大学结构光三维扫描仪北京航空航天大学数字立体电视其计算机成像系统南开大学发光锌纳米分子复旦大学上海越族后裔与台湾高山族的渊源华东师范大学师范生对教育类课程看法的调查报告东南大学 OSC2001微型掌上数字存储示波器东南大学南京市流动民工现状调查山东大学换热器动态仿真及智能控制系统山东大学紫外倍频晶体K2AL2B207的生长技术汕头大学 LCD生产过程的基板自动对位贴合及ITO、SPACER自动检测系统电子科技大学考虑交易费用与风险情况下移动平均交易规则的检验四川大学论对抽象行政行为的司法监督重庆大学“移民者的乐园”——三峡库区“棚户现象”调查研究与城市(镇)迁建、移民问题思考渝州大学绿色贸易壁垒及重庆之应对贵阳中医学院《针穴II》虚拟三维教学系统西安交通大学金纳米球壳微粒的空腔谐振吸收特性)西安交通大学一种适用于小C臂X光机的数字成像系统一等奖北京大学中国高龄老人健康状况和健康预期寿命研究北京航空航天大学环形翼飞机北京航空航天大学弹射座椅地面综合测试仪及其嵌入式系统北京航空航天大学多机器鱼协调及机器鱼的机动性研究北京科技大学喷丝板自动检测系统北京科技大学灵丘贫锰银矿综合利用技术研究北京理工大学哈勃常数的实验估计北京理工大学发动机润滑系统仿真软件包北京师范大学教师反馈、学生的归因模式与学生学业成绩关系的研究:一项行动研究及其对学校心理健康教育的启示中国人民大学真茵寡聚糖诱导子诱导悬浮培养红豆杉细胞的信号转导途径及其过程模型的研究天津理工学院缔合色心型X线影像板河北大学陆马峰的发育与筑巢行为的研究河北科技大学 L-抗坏血酸-2-三聚磷酸酯的合成研究华北电力大学民事举证责任倒置问题探析大连海事大学船舶运动控制试验平台大连理工大学冰柜监控管理系统大连理工大学单金属、双金属催化剂表面CO氧化反应的模拟模型大连理工大学医学层析图象三维几何重建与可视化仿真东北大学般若企业互联网络综合应用平台吉林工学院溶液法银纳米微粉的光化学制备哈尔滨理工大学地下管线定位仪东华大学中国绿色服装发展探究复旦大学转动基板的激光测温复旦大学知识产权新课题——基因专利复旦大学以企业信息化迎接B2B挑战华东师范大学 GSEEK码路天使——中西文著者号码自动生成系统上海财经大学高级管理层激励与上市公司经营绩效上海交通大学全光通信系统仿真软件上海师范大学如何在中国农村普及信息技术教育同济大学多高层建筑结构设计系统(简称MTS)东南大学均压型行波形超声波电机苏州大学真丝调拒水拒油防污多功能整理新技术研究及产品开发苏州大学非接触式高精度数字图像面积测量仪苏州大学激发型抗人CD40单克隆抗体的研制及产品开发扬州大学 Xa21基因导入水稻广亲和恢复系SWR20提高白叶枯病抗性中国药科大学脆壁克鲁维酵母菌乳糖酶的开发与应用浙江大学基于综合推理的集成化智能书法创作合肥工业大学关于安徽农村税费改革的调查和建议中国科学技术大学语音合成芯片郑州工程学院王涛河南省高校大学生创新能力现状调查与对策研究郑州工程学院袁少勇在WTO框架下:中国粮食流通体制改革研究华中师范大学我国城市社区的阶层化趋势研究武汉大学用人市场对大学毕业生质量评价的社会学分析武汉理工大学谈广义M集的演化及其在图形防伪中的应用中国地质大学(武汉) 全球古大陆再造软件开发研究国防科学技术大学 Windows变速器国防科学技术大学数字水印新技术华南农业大学车八岭保护区及其邻近地区的木兰科植物种群及其群落特征的研究中山大学中国南沙群岛海域浮游原生动物生物多样性研究中山大学珠江三角洲富裕农村主观剩余劳动力问题研究华南热带农业学院蝗虫霉菌的培养及致病性初步实验西南石油学院油藏压裂模拟设计与分析软件系统重庆大学可穿戴式计算机——Netdaily云南大学便携式高精度数字燃油流量计云南大学传统法文化的断裂与现代法治的真空——少数民族农村法治秩序建构路径选择的社区个案研究长安大学 The Problems and the Solutions on Ecological Architecture in Developing Countries西安电子科技大学单片机模糊控制软件仿真和生成平台西安理工大学 Sn02:F透明电热膜加热管兰州大学纳米微阵电极组装体系的制备和初步研究宁夏大学宁夏移民区可持续发展模式研究宁夏大学历史上固原地区人地关系的两次转型对生态建设的启示新疆大学维-汉-英三向背单词系统、电脑词典第八届“挑战杯”全国大学生课外学术科技作品竞赛由华南理工大学于2003年承办:清华大学获得“挑战杯”复旦大学获得挑战杯永久纪念碑一座一等奖获奖名单北京大学司法判决书中“双高”现象并存的另一种解释进路北京大学贫困学生怎么上大学?——中国高校学生贷款运行机制案例分析及其国际比较北京航空航天大学仿生飞翼布局飞机北京航空航天大学纳米光催化空气消毒净化器清华大学北京市流动儿童受教育状况及心理健康现状调查报告中国地质大学(北京)大学生创新精神和实践能力培养的调查研究——团体创新模式分析中国农业大学 AISCR-1-100微机控制全自动智能除雪机器人中国人民大学资本市场融资条件与产品市场竞争双重约束下的中国上市公司融资行为研究北京城市学院北京市乞丐现状调查报告天津大学桩基承台前方设挡土结构的大型码头结构河北科技师范学院杏树新害虫---JT虫生物学特性及无公害防治研究山西财经大学货币需求中的认知因素分析大连理工大学基于元胞自动机和Penna模型的生态系统模拟模型吉林大学国有经济控制力及控制方式新探吉林大学兽疫链球菌突变株产生的透明质酸的纯化及表征北华大学气动蠕动式缆索机器人哈尔滨医科大学中药复方抗心律失常药物筛选平台的建立复旦大学手晃电子显示棒上海财经大学城市轨道交通投资对周边地价变动影响的实证分析上海交通大学新型水葫芦打捞船上海交通大学基于 Inter PXA250的无线个人客户端的开发(wireless personal client)同济大学轨道交通运输组织仿真系统开发同济大学城市之桥—上海世博会人行过江“花”桥的结构概念设计同济大学四轮独立驱动燃料电池微型汽车东南大学通用手持概念仪器东南大学江苏省企业电子商务应用调查研究报告南京大学一种新型的磁力吸盘南京大学他们怎样生存——三峡移民迁前生存状况调查南京工业大学绿色紧凑的冷冻式空气干燥机南京理工大学鱼类旋涡射流推进理论及其应用南京师范大学稀土有机配合物生态转光剂的制备南京师范大学推进乡镇机构改革的对策研究——苏南、苏北若干典型乡镇机构改革的比较分析南京邮电学院基于动态路由控制的高性能IP宽带接入网关中国矿业大学花生收获机华东船舶工业学院仿生波动推进器绍兴文理学院组织的镶嵌、链接和整合——中国轻纺城地方商会个案分析浙江工业大学“AH-Assemble”汇编语言集成开发平台浙江师范大学村委会选举中乡镇政府的角色转换——以浙江省昌镇村委会选举为个案中国科学技术大学σ键超共轭作用在丙烯旋转能垒中的重要性中国科学技术大学最小超对称标准模型下的R宇称破坏机制对CERN LHC上轻子对产生过程的影响中国科学技术大学 Bcl-rambo β的发现和功能研究福建农林大学甘蔗近缘属植物斑茅的杂交利用与抗逆性评价福州大学基于评价方法属性层次的组合评价研究华侨大学三维自然纹理的反求设计与制造厦门大学从“三农”问题透视乡镇政权——以福建省枫亭镇和大济镇为例山东理工大学竹红菌甲素--一种新型抗生素的抑菌作用研究郑州工程学院大学生诚信缺失徂源及对策——转型期大学生信用行为分析湖北大学论诚信的劣变与对教育理性的质问----关于当代大学生诚信状况的分析以及对当代教育的反思华中科技大学北京、武汉高校人才培养与学生素质状况调查报告武汉大学绿色铅酸蓄电池及其生产工艺武汉化工学院水性聚酯树脂的合成及其涂料研制中国地质大学(武汉)求解动态TSP问题的新型演化算法国防科技大学新概念路标系统与无人驾驶汽车模型湖南大学 RSY-1肉类水分快速测定仪湖南大学入世过渡期:银行不良资产处置模式的比较分析与路径选择湖南师范大学传统文化与党风廉政建设湖南师范大学走向权利时代的民工权益——来自深圳民工的调查中南大学三峡移民的文化差异与文化融合——以湖南岳阳地区新市、杨林两地三峡移民为样本分析的调查报告中南大学基于等离子体聚合膜技术的压电免疫传感器的研究及其在急性白血病免疫分型中的应用广州大学岭南城市广场与公园热环境研究华南理工大学新型高分子点阵发光显示屏华南农业大学园艺植物自然分类系统及其汉拉英名称对照广东商学院 21世纪中国人口老龄化与银色产业开发四川大学通过分子复合实现聚乙烯醇的吹塑成膜西南石油学院现代试井分析技术及软件系统第三军医大学以纳米金为报告系统的病原体快速检测基因芯片第三军医大学抑制胆固醇合成对乳腺癌细胞离子跨膜流动、细胞骨架形成及细胞通讯功能影响的研究重庆工学院一个非常值得关注的“三农”问题——重庆市农村养老问题调查研究云南师范大学微波加热技术在催化化学反应中的应用长安大学环保型野生植物杀虫剂的研究西安科技大学基于虚拟仪器技术的多种机械量测试系统西安交通大学透平叶片型线设计及优化软件西安交通大学金纳米棒状微粒的吸收光谱宁夏大学数字显微镜模拟目镜及病理远程诊断系统新疆大学新疆家蚕抗菌肽基因工程产品的开发与应用第九届“挑战杯”全国大学生课外学术科技作品竞赛由复旦大学于2005年承办:复旦大学获得“挑战杯”复旦大学以总分420分的最高分夺得第九届“挑战杯”;北京大学、中国矿业大学、南京大学等20所高校捧得“优胜杯”;清华大学由于累计3次捧杯,获得“挑战杯‘永久纪念杯’”。

东南大学CPU报告

Micro-programmed CPUReportCOA Course Designcontents Purpose (2)Experiment Principle (2)Instruction Set (2)Internal Registers and Memory (3)MAR (Memory Address Register) (3)MBR (Memory Buffer Register) (4)PC (Program Counter) (4)IR (Instruction Register) (4)ACC (Accumulator) (5)MR (Multiplier Register) (5)DR (Division Register) (5)LPM_RAM_DQ (5)ALU(Arithmetic Logic Unit) (6)Micro-programmed Control Unit (6)CPU Architecture (8)Control signals in Control Memory (8)Contents of Control Memory (9)Top level circuit diagram (11)Simulation results: (12)Problem 1:Calculate the sum of all integers from 1 to 100 (12)Problem 2:Calculate300 and 275 (14)Results Analysis (14)Further Improvement (15)Reference (15)Appendix (15)1.MBR module (15)2.BR module (16)3.ALU module (17)4.IR module (18)5.PC module (19)6.MAR module (20)7.control_unit module (21)8.MR module (22)PurposeThe purpose of this project is to design a simple CPU (Central Processing Unit). This CPU has basic instruction set, and we will utilize its instruction set to generate a very simple program to verify its performance.For simplicity, we will only consider the relationship among the CPU, registers, memory and instruction set. That is to say we only need to consider the following items:Read/Write Registers, Read/Write Memory and execute the instructions.At least four parts constitute a simple CPU:the control unit, the internal registers, the ALU and instruction set,which are the main aspects of our project design and will be studied.Experiment PrincipleInstruction SetSingle-address instruction format is used in our simple CPU design. The instruction word contains two sections: the operation code (opcode),which defines the function of instructions (addition, subtraction, logic operations,etc.);the address part, in most instructions, the address part contains the memory location of the datum to be operated,we called it direct addressing.In some instructions, the address part is the operand,which is called immediate addressing.For simplicity, the size of memory is 256×16in the computer.The instruction word has 16 bits. The opcode part has 8 bits and address part has 8 bits. The instructionOPCODE[15:8]ADDRESS[7:0]Figure1 the instruction formatThe opcode of the relevant instructions are listed in Table 1. In Table 1, the notation [x] represents the contents of the location x in the memory. For example, the instruction word 00000011101110012(03B916) means that the CPU adds word at location B916in memory into the accumulator(ACC);the instruction word 00000101000001112(050716) means if the sign bit of the ACC (ACC [15]) is 0, theCPU will use the address part of the instruction as the address of next instruction, if the sign bit is 1, the CPU will increase the program counter (PC) and use its contentInternal Registers and MemoryMAR (Memory Address Register)MAR contains the memory location of the word to be read from the memory or written into the memory. Here, READ operation is denoted as the CPU reads from memory, and WRITE operation is denoted as the CPU writes to memory. In our design, MAR has 8 bits to access one of 256 addresses of the memory.In my experiment, the MAR block is as figure 2marinst6Figure 2pc[7..0]mbr[7..0] cs[31..0] clkmar_out[7..0]MBR (Memory Buffer Register)MBR contains the value to be stored in memory or the last value read from memory. MBR is connected to the address lines of the system bus. In our design, MBR has 16 bits.In my experiment, the MBR block is as figure 3mbrinst3Figure 3PC (Program Counter)PC keeps track of the instructions to be used in the program. In our design, PC has 8 bits.In my experiment, the PC block is as figure 4Figure 4IR (Instruction Register)IR contains the opcode part of an instruction. In our design, IR has 8 bits. BR (Buffer Register) BR is used as an input of ALU, it holds other operand for ALU. In our design, BR has 16 bits.In my experiment, the Instruction register is as figure 5acc_in[15..0]memory _in[15..0]cs[31..0]clkmbr_out[15..0]pcinst5mbr_in[7..0]cs[31..0]clkpc_out[7..0]irinst4mbr_in[7..0]cs[31..0]clkir_out[7..0]Figure 5ACC (Accumulator)ACC holds one operand for ALU, and generally ACC holds the calculation result of ALU. In our design, ACC has 16 bits.MR (Multiplier Register)MR is used for implementing the MPY instruction, holding the multiplier at the beginning of the instruction. When the instruction is executed, it holds part of the product.In my experiment, the MR is as figure 6Figure 6DR (Division Register)DR is used for implementing the DIV instruction, you can define it according to your division algorithm. It’s optional. Here, we ignore it.LPM_RAM_DQLPM_RAM_DQ is a RAM with separate input and output ports, it works as memory, and its size is 256×16. Although it ’s not an internal register of CPU, we need it to simulate and test the performance of CPU. All the registers are positive-edge- triggered. All the reset signals for the registers are ALU .MRinst9ACC_In[15..0]clkcs[31..0]MR[15..0]Figure 7ALU (Arithmetic Logic Unit)ALU is a calculation unit which accomplishes basic arithmetic and logic operations. In our design, some operations must be supported which are listed as follows e synchronized to the clock signal.In my experiment, the ALU block is as figure 8Figure 8Table 2 ALU operationsMicro-programmed Control UnitWe have learnt the knowledge of Micro-programmed control unit. Here, we only review some terms and basic structures. In the Micro-programmed control, the micro-program consists of some microinstructions and the micro-program is stored in control memory that generates all the control signals required to execute thealuinstbb _in[15..0]bb [31..0]clkaccis0acc[15..0] mpy high[15..0]CAR (control address Register)Instruction registerSequencing logicinstruction set correctly. The microinstruction contains some micro-operations which are executed at the same time.Microinstructions are stored in the control memory. The control address register contains the address of the next microinstructions to be read. When a microinstruction is read from the control memory, it is transferred to a control buffer register. The register connects to the control lines emanating from the control unit. Thus, reading a microinstruction from the control memory is the same as executing that microinstruction. The third element shown in the figure 9 is a sequencing unit that loads the control address register and issues a read command.Control MemoryControl Buffer RegisterFigure 9 Control UnitIn my CPU, the control address is defined as a variable, without a single part. The control unit is as figure 10.And the control memory is as figure 11.Control Signalscontrol_unitinst2Figure10lpm_rom0inst8Figure11CPU ArchitectureFigure12 Control signals in Control MemoryTable 3 Control Signalsclkf lagcs[31..0]ir_out[7..0]address_out[7..0]address[7..0]clockq[31..0]Bit in read-onlyMicro-operation Control signal name control memory(Bit of ROM)Increase CAR C0CAR←CAR+1Control addressing C1CAR←**C2Reset CARCAR←0Read RAM C3MBR←memoryC4MBR into IRopcodeIRopcode←MBR(15..8)MBR into MAR C5MAR←MBR[7..0]Increase PC C6PC←PC+1C7MBR into BRBR←MBRreset_ACC C8ACC←0C9ADDACC←ACC+BRPC into MAR C10MAR←PCC11RAM _writememory←MBRC12ACC into MBRMBR←ACCMBR into PC C14PC←MBRReset_PC C15PC←0SUB C16ACC←ACC-BRC17Shift ACC to right SHIFTRMPY(H)into MR C18MR←ACC*BR(H)C24Mpy(L)ACC←ACC*BRC25Shift ACC to left SHIFTLC26NOTACC←NOT ACCC27ORACC←ACC or BRC28ANDACC←ACC and BRContents of Control MemoryTable 4 Contents of control memoryAddress(Hex)Micro-instructions Control Signals 0(FETCH)MBR←memory,CAR←CAR+1C3,C0 000000091IRopcode←MBR15-C4,C0 000000118,CAR←CAR+12CAR←**C1 0000000210(LOAD)MAR←MBR7-0,PC←PC+1,C5,C6,C000000061CAR←CAR+111MBR←memory , CAR←CAR+1C3,C0 0000000912ACC←0,BR←MBR,CAR←CAR+1C8,C7,C00000018113ACC←ACC+BR, CAR←CAR+1C9,C0 0000020114MAR←PC, CAR←0C10,C200000404 20(STORE)MAR←MBR7-0,PC←PC+1,C5,C6,C000000061 CAR←CAR+121MBR←ACC, CAR←CAR+1C12,C00000100122memory←MBR, CAR←CAR+1C11,C00000080123MAR←PC,CAR←0C10,C20000040430(ADD)MAR←MBR7-0, PC←PC+1,C5,C6,C000000061 CAR←CAR+131MBR←memory,CAR←CAR+1C3,C0 0000000932BR←MBR, CAR←CAR+1C7,C0 0000008133ACC←ACC+BR, CAR←CAR+1C9,C0 0000020134MAR←PC, CAR←0C10,C200000404 40 (SUB)MAR←MBR7-0, PC←PC+1,C5,C6,C000000061 CAR←CAR+141MBR←memory,CAR←CAR+1C3,C0 0000000942BR←MBR, CAR←CAR+1C7,C0 0000008143ACC←ACC-BR, CAR←CAR+1C16,C00001000144MAR←PC, CAR←0C10,C20000040450(HALT)ACC←0, CAR←0 ,PC←0C8,C15,C200008104 60(AND)MAR←MBR7-0, PC←PC+1,C5,C6,C000000061 CAR←CAR+161MBR←memory,CAR←CAR+1C3,C0 0000000962BR←MBR, CAR←CAR+1C7,C0 0000008163ACC←ACC and BR,CAR←CAR+1C28,C01000000164MAR←PC,CAR←0C10,C20000040470(OR)MAR←MBR7-0,PC←PC+1,C5,C6,C000000061CAR←CAR+171MBR←memory,CAR←CAR+1C3,C0 0000000972BR←MBR, CAR←CAR+1C7,C0 0000008173ACC←ACC or BR,CAR←CAR+1C27,C00800000174MAR←PC, CAR←0C10,C200000404 80(NOT)MAR←MBR7-0,PC←PC+1,CAR←CAR+1C5,C6,C00000006181MBR←memory,CAR←CAR+1C3,C0 0000000982BR←MBR, CAR←CAR+1C7,C0 0000008183ACC←not ACC, CAR←CAR+1C26,C00400000184MAR←PC, CAR←0C10,C20000040490(SHIFTR)ACC←ACC>>1, PC←PC+1,CAR←CAR+1C17,C6,C00002004191MAR←PC, CAR←0C10,C200000404 A0(SHIFTL)ACC←ACC<<1, PC←PC+1,CAR←CAR+1C25,C6,C002000041A1MAR←PC, CAR←0C10,C200000404 B0 (MPY)MAR←MBR7-0,PC←PC+1,CAR←CAR+1C5,C6,C000000061B1MBR←memory,CAR←CAR+1BR←MBR , CAR←CAR+1C3,C0 00000009B2C7,C0 00000081 B3ACC←ACC*BR(L), CAR←CAR+1C24,C001000001B4 MR ←ACC*BR(H), CAR ←CAR+1 C18,C0 00040001 B5MAR ←PC , CAR ←0 C10,C200000404F0(JUMPEZ)(IF flag=1) PC ←PC+1, CAR ←CAR+1C6,C000000041F1 CAR ←0 ,MAR ←PC C10,C2 00000404F2(IF flag =0) PC ←MBR7-0, CAR ←CAR+1C14,C000004001F3CAR ←0 ,MAR ←PCC10,C2 00000404Top level circuit diagramlpm_rom0clk control_out[7..0]accis0 clockcs[31..0]cs[31..0]ir[7..0]inst8lpm_ram_dq0mbr[15..0] cs[11]mar[7..0]clockmemory [15..0]inst7Figure 13The detail registers or blocks are shown as follows:control_unitinst2clkf lagcs[31..0]ir_out[7..0]address_out[7..0]data[15..0] w renaddress[7..0] clockq[15..0]address[7..0] clockq[31..0]mbr[15..0] cs[31..0]clkbb [15..0]bb [31..0] clkbr[15..0]accis0acc_out[15..0] mpy high[15..0]mbr[7..0] cs[31..0]clkpc[7..0]mbr[7..0] cs[31..0]pc[7..0]mar[7..0]clkacc_out[15..0] memory [15..0]mbr[15..0] cs[31..0] clk mpy high[15..0]clkcs[31..0]mbr[15..8]ir[7..0]lpm_rom0cs[31..0] clkclk control_out[7..0]accis0 clockcs[31..0]cs[31..0]ir[7..0]inst8lpm_ram_dq0mbr[15..0]cs[11] mar[7..0] clockmemory [15..0]inst7Figure 14Simulation results:I designed several programs to test the program ,the examples are shown below:Problem 1: Calculate the sum of all integers from 1 to 1001. programming with C language:sum=0; temp=100;loop :sum=sum+temp;temp=temp-1;if temp>=0 goto loop; end2. Assume in the memory: sum is stored at location A4, temp is stored at location A3, the contents of location A0 is 0, the contents of location A1 is 1,the contents of location A2 is 10010=6416.We can translate the above C language program with the instructions listed in Table 1 into the instruction program as shown in Table 4.Table 5 Example of a program to sum from 1 to 100clkINPUT VCC clock INPUT VCC OUTPUTbr[15..0] OUTPUT pc[7..0] OUTPUT mar[7..0] OUTPUT mbr[15..0] OUTPUT control_out[7..0] OUTPUT ir[7..0] OUTPUT memory [15..0] OUTPUTcs[31..0]OUTPUT acc_out[15..0] OUTPUTacc_out[31..16]aluinst bb _in[15..0]cc [31..0] clk accis0 acc[15..0] mpy high[15..0]brinst1 mbr_in[15..0]cs[31..0]clkbr_out[15..0]control_unitinst2clkf lagcs[31..0]ir_out[7..0]address_out[7..0]mbr inst3acc_in[15..0] memory _in[15..0] cs[31..0] clk mbr_out[15..0] irinst4mbr_in[7..0]cs[31..0]clkir_out[7..0]pcinst5 mbr_in[7..0]cs[31..0] clkpc_out[7..0] marinst6 pc[7..0] mbr[7..0] cs[31..0] clkmar_out[7..0]data[15..0]w renaddress[7..0]clockq[15..0]address[7..0]clockq[31..0]M Rinst9 ACC_In[15..0]clkcs[31..0]MR[15..0]止于至善Program with C Programwith Contents of Memory (RAM) in HEXAddress Contentssum=0;LOAD i nstructionsA00002A0 STORE A40101A4temp=100;LOAD A20202A2 STORE A30301A3loop:sum=sum+temp;LOOP:LOAD A404 (so LOOP=04)02A4 ADD A30503A3 STORE A40601A4temp=temp-1;LOAD A30702A3 SUB A10804A1 STORE A30901A3if temp>=0 goto JMPGEZ LOOP0A0504loop; end HALT0B HALT…..…..A00000A10001A20064LOAD A3Temp=temp-1LOAD A4 Sum= sum +tempFinal result:5050temp<0,temp=-1Problem2: Calculate300 and275LOAD A0 AND A102A0 0AA1HALT Translate0700In the RAM, the address A0 has the content300 and the A1 has the content 275.Load A0AND A1Final result:256Results Analysis1. Problem 1:calculate the sum of all intergers from 1 to 100Through functional simulation, we get the waveform and the finalsummary is 100,which is correct. We also make the test for the functionof the instruction LOAD, STORE, ADD, SUB, JMPGEZ etc.2. Problem 2:calculate300 and 275Through functional simulation, we get the right answer,256andauthenticate the instruction AND.3. Our simple CPU has implemented the basic function required. Further Improvement1.Instruction-level parallelism and superscalar is not implemented in our CPU,which will greatly improve the efficiency.2.Some complex instructions, such as DIV, are not implemented in theinstruction set. Division can only be accomplished by shifting.3.Only direct addressing mode is realized. More modes, such as registeraddressing and indirect addressing can be designed in the future.4.There is no interrupt service provided in our simple CPU.5.In the real world,the speed of memory(RAM) is slowly than that of CPU.The ROM should share the same clock with CPU. In our simple CPU, theclock doesn’t function perfectly. Further improvement must be madeabout this.ReferenceWilliam,Stallings.“Computer Organization and Architecture, Designing for Performance”,Appendix1.MBR modulelibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity mbr isport( acc_in,memory_in:in std_logic_vector(15 downto 0);cs:in std_logic_vector(31 downto0);clk:in std_logic;mbr_out:out std_logic_vector(15 downto0));end mbr;architecture behave of mbr isbeginprocess(clk)beginif clk'event and clk='1'thenif cs(3)='1'thenmbr_out<=memory_in;-- MBR←memory elsif cs(12)='1'thenmbr_out<=acc_in;-- MBR←ACCend if;end if;end process;end behave;2.BR modulelibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity br isport( mbr_in:in std_logic_vector(15 downto0);cs:in std_logic_vector(31 downto0);clk:in std_logic;br_out:out std_logic_vector(15 downto0));end br;architecture behave of br isbeginprocess(clk)beginif clk'event and clk='1'thenif cs(7)='1'thenbr_out<=mbr_in;-- BR←MBRend if;end if;end process;end behave;3.ALU modulelibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity alu isport( br_in:in std_logic_vector(15 downto 0);cs:in std_logic_vector(31 downto0);clk:in std_logic;accis0:out std_logic;acc:out std_logic_vector(15 downto 0);mpyhigh:out std_logic_vector(15 downto0));end alu;architecture behave of alu issignal temp:std_logic_vector(15downto 0);beginaccis0<='1'when temp(15)='1'else'0';--If ACC<0,flag<=1process(clk)variable x:std_logic_vector(31 downto 0);beginif clk'event and clk='1'thenif cs(8)='1'thentemp<="0000000000000000";--resetelsif cs(9)='1'thentemp<=temp+br_in;--addelsif cs(16)='1'thentemp<=temp-br_in;--subelsif cs(17)='1'thentemp<='0'&temp(15downto 1); --shiftrelsif cs(24)='1'thenif (temp(15)xor br_in(15))='1'thenif temp(15)='1' thenx:=(0-temp)*br_in;elsex:=temp*(0-br_in);end if;x:=0-x;temp<=x(15downto 0);mpyhigh<=x(31downto 16);elseif temp(15)='1' thenx:=(0-temp)*(0-br_in);elsex:=temp*br_in;end if;temp<=x(15downto 0);mpyhigh<=x(31downto 16);end if; --mpyelsif cs(25)='1'thentemp<=temp(14downto0)&'0'; --shiftlelsif cs(28)='1'thentemp<=temp and br_in;--andelsif cs(27)='1'thentemp<=temp or br_in; --orelsif cs(26)='1'thentemp<=not br_in;--notend if;acc<=temp;end if;end process;end behave;4.IR modulelibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity ir isport( mbr_in:in std_logic_vector(7 downto 0);--mbr[15..8]cs:in std_logic_vector(31 downto0);clk:in std_logic;ir_out:out std_logic_vector(7 downto 0));end ir;architecture behave of ir isbeginprocess(clk)beginif clk'event and clk='1'thenif cs(4)='1'thenir_out<=mbr_in;end if;end if;end process;end behave;5.PC modulelibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity pc isport( mbr_in:in std_logic_vector(7 downto 0);--mbr[15..8]cs:in std_logic_vector(31 downto0);clk:in std_logic;pc_out:out std_logic_vector(7 downto0));end pc;architecture behave of pc isbeginprocess(clk)variable temp:std_logic_vector(7 downto0);beginif clk'event and clk='1'thenif cs(15)='1'thentemp:="00000000";--resetelsif cs(14)='1'thentemp:=mbr_in;elsif cs(6)='1'thentemp:=temp+1;--incrementend if;pc_out<=temp;end if;end process;end behave;6.MAR modulelibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity mar isport( pc,mbr:in std_logic_vector(7 downto 0);--mbr[7..0]cs:in std_logic_vector(31 downto0);clk:in std_logic;mar_out:out std_logic_vector(7 downto0));end mar;architecture behave of mar isbeginprocess(clk)beginif clk'event and clk='1'thenif cs(10)='1'thenmar_out<=pc;elsif cs(5)='1'thenmar_out<=mbr;end if;end if;end process;end behave;7.control_unit modulelibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity control_unit isport( clk:in std_logic;flag:in std_logic;cs:in std_logic_vector(31 downto0);ir_out:in std_logic_vector(7 downto0);address_out:out std_logic_vector(7 downto0));end control_unit;architecture behave of control_unit isbeginprocess(clk)variable address:std_logic_vector(7 downto0);beginif clk'event and clk='1' thenif cs(0)='1'thenaddress:=address+1;--increment car elsif cs(2)='1'thenaddress:="00000000";--reset carelsif cs(1)='1'then--fetchcase ir_out iswhen "00000001"=>address:="00100000";--storewhen "00000010"=>address:="00010000";--loadwhen "00000011"=>address:="00110000";--addwhen "00000100"=>address:="01000000";--subwhen "00001010"=>address:="01100000";--andwhen "00001011"=>address:="01110000";--orwhen "00001100"=>address:="10000000";--notwhen "00001101"=>address:="10010000";--shiftrwhen "00001110"=>address:="10100000";--shifrlwhen "00001000"=>address:="10110000";--mpywhen "00000101"=>--jmpgezif flag='0'thenaddress:="11110010";else address:="11110000";end if;when "00000111"=>address:="01010000";--haltwhen others=>null;end case;end if;address_out<=address;end if;end process;end behave;8.MR modulelibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_signed.all;entity MR isport(ACC_In:in std_logic_vector(15 downto 0);clk: in std_logic;cs:in std_logic_vector(31 downto0);MR: out std_logic_vector(15 downto0));end MR;architecture a of MR isbeginprocess(clk)beginif(clk'event and clk='1')thenif cs(18)='1'thenMR<=ACC_In;end if;end if;end process;end a;。

第六届北京大学生集成电路设计大赛获奖名单

三等奖获奖名单

B005

福州大学13微电队

田斌斌

王万金

钱一

B006

梧州学院橙子队

涂航辉

梁伟健

张小灵

B024

华中科技大学龙超人队

古真

孙光明

项业成

B067

武汉大学SOC队

周孝斌

汤知日

杨若婷

B084

江苏信息学院微电一队

张海洋

李敏

周转

B086

四川大学GND

林鑫

陈峰

王志

B222

中山大学Gan

李伟民

钟恒飞

施展

第六届北京大学生集成电路设计大赛获奖名单

第六届(2016)北京大学生集成电路设计大赛获奖名单如下:

华大九天企业杯

一等奖获奖名单

队伍编码

队名

队员1

队员2

队员3

B051

北京工业大学主旋律队

汪浩

张琪

邢劼思

二等奖获奖名单

M009

电子科技大学碲铋队

吕彬彬

张净植

王子晟

M066

澳门大学InPoCit队

罗自洋

黄元庆

孙凯

何彦哲

B073

武汉大学Tesla队

候伟

高杨

范波

M010

东南大学至善D队

廖一龙

施豪栋

史鹏鹏

M043

吉林大学知芯队

王仁广

胡冰妍

余芝帅

M044

北方工业大学梦之翼队

张家军

郝铁营

马亮亮

M082

西安电子科技大学坚果队

宋成

黄瀛洲

王涛

M099

上海交通大学刘奶奶买榴莲牛奶队

附四:东南大学软件学院研究生培养

附四:东南大学软件学院研究生培养情况说明一、前言东南大学软件学院是经国家教育部和原国家计委首批批准成立的“国家示范性软件学院”。

学院秉承东南大学“止于至善”的校训,坚持质量至上原则,遵循高等工程教育的内在规律,借鉴国际先进经验,建构以“基础教学提升思维水平、专业教学提升科研素养、实验教学提升应用能力、实训教学提升系统观念、外语教学提升沟通手段”为核心的高层次软件工程技术和工程管理人才培养体系,努力培养学生具有严谨的专业态度、厚实的基础知识、持久的学习能力、出色的合作精神、清晰的系统思维、丰富的技术手段、良好的管理水平、敏捷的应变能力和与时俱进的创新精神,使我们的毕业生能够体现出鲜明的特点与强劲的实力。

2007年10月,我院被江苏省教育厅、江苏省学位委员会授予“软件工程研究生联合培养示范基地”称号。

为了进一步提升我院高层次软件与IT人才的培养水平、建设瞄准国际先进水平的软件与IT人才培养基地,为我国软件与IT产业发展、增强软件与IT产业的核心竞争力多做贡献,苏州市政府与东南大学决定在苏州独墅湖高等教育区给予东南大学软件学院大力的支持,合作共建东南大学软件学院(苏州)。

东南大学软件学院所有全日制研究生的培养工作将放在苏州进行。

学院将按照全新理念、全新机制、全新模式进行办学,投入一流的师资,建立一流的实验环境,全面优化研究生培养体系,与国内外著名软件与IT企业精诚合作,努力把学院建成国内培养高层次、工程型、复合型、国际化软件与IT 人才的重要基地,为国家、地方经济的快速发展和社会进步服务。

二、招生方向东南大学软件学院(苏州)目前设有四个系:软件工程系、微电子技术系、网络工程系和数字艺术系,由东南大学软件学院、集成电路学院、计算机科学与工程学院、艺术学院和苏州研究院共同建设。

学院的培养对象为软件工程领域工程硕士研究生,目前的主要培养方向主要有软件开发技术、网络与通信、嵌入式软件技术、数字媒体技术、数字国土技术、软件项目管理、企业信息化、嵌入式系统、集成电路、网络与信息安全、影视动漫创意与制作等。

公交行业法治化建设势在必行——访东南大学法学院副教授、交通法

82019 / 06特别关注TEBIEGUANZHU问:关于公共交通行业的法治建设,从立法、执法、守法这三个方面来讲,您认为当前最为重要的工作有哪些?顾大松:在立法层面,最为重要的是尽快推动行政法规层面的《城市公共交通条例》与《农村公终于有机会采访到顾大松教授,首当其冲就问到这两年频发的针对驾驶员的危险行为及恶性事件。

顾教授认为,按照现有的“危害公共安全罪”等罪名,乘客的此类行为的定罪量刑难以做到“罪”“刑”相适应。

针对此类行为可考虑增设“妨害安全驾驶罪”:将“采用威胁、暴力方法侵犯正在驾驶公共交通工具驾驶人员的人身权、强行干扰公共交通工具正常行驶等行为”纳入其中,量刑可以参考危险驾驶罪。

公交行业法治化建设势在必行路条例》出台,这有在中央立法高度确立我国公众“出有所乘”公法权利的首倡法治意义,有利于共同构建我国城乡居民出行基本权利保障的法治体系,是交通立法践行党的十九大提出的“不断满足人民日益增长的美好生活需要”的重要体文 / 本刊编辑部现。

同时,在立法界定公共交通的范围时,不宜仅仅局限于传统定线、定时、定点、定价的公交方式,要为有些城市已经开展的多元化公交方式,如预约服务和辅助公交形式预留空间,在政府承担基本出行服务保障的基础上,依托市场—— 访东南大学法学院副教授、交通法治与发展 研究中心执行主任顾大松92019 / 06特别关注/TEBIEGUANZHU 总第114期与社会力量,推动人民群众“出行所乘”向“行有优乘”的转变。

在执法层面,重点是加强公共交通运行安全的保障。

不论是发生在重庆的公交坠江事件,还是发生在高铁上的霸座、扒车门等事件,甚至反复发生的民航乘客向发动机扔硬币事件等,均说明公共交通工具上的运行安全亟需严格执法予以保障。

一方面,有必要为现有的公交安全执法队伍赋予更多的执法权限,以树立执法权威,另一方面,也要在一定程度上肯定公交运营企业的公物管理权,甚至在某些领域确定其一定的惩戒权,使得公交运行安全既能够依托公交安全执法力量,也能依托公交企业的管理力量进行,进而推动公交运营安全的齐抓共管。

好有意义!东大录取通知书藏着手工彝绣盲盒,均来自云南省楚雄州南华县

好有意义!东大录取通知书藏着手工彝绣盲盒,均来自云南省楚雄州南华县东大录取通知书藏着手工彝绣盲盒,均来自云南省楚雄州南华县今天(7月10日),首届彝绣文化周开幕式暨“至善彝绣馆”开馆仪式在东南大学定点帮扶地-云南楚雄州南华县举行。

校长黄如带队参加了开馆仪式。

活动现场,东南大学2023年录取通知书正式亮相。

读万卷书,行万里路,展鸿鹄志。

今年东大的通知书整体采用“书”的概念,代表着历史之书、大学之书,至善之书的寓意。

通知书采用了“书函”的包装形式,选用中国传统色“天缥”,江南烟雨,天际微青,初春时节,东风解冻,蓬勃生长,代表了无限的希望与可能;“书函”封面上采用烫印的技艺,印制了东南大学校名以及校徽,校训“止于至善”以印章的形式呈现,象征着东南大学赓续千年的悠久文脉。

将录取通知“书”从“书函”中抽出,映入眼帘的是沉稳古典的“菜根绿”的颜色,来自李瑞清任两江师范学堂校长时曾提出的校训“嚼得菜根,做得大事”。

通知书封面上是烫金工艺勾画的东南大学大礼堂的线稿图案录取通知书,封底则是东大精神图腾、千年古树六朝松。

通知书里,还为今年东南大学的4000余位新生准备了一份特殊的礼物,手工绣制的“彝绣”卡套。

今天,这样的通知书也陆续发出。

东南大学本科招生办公室主任助理肖雅介绍说:“这些彝绣均来自云南省楚雄州南华县。

东南大学持续10年定点帮扶南华县,在教育、产业、医疗、基建、消费、文化等众多领域贡献了东大智慧和东大担当。

”“东南大学更是立足南华特色,因地制宜,助力南华彝绣特色产业成为富民产业。

在今年的通知书设计之初,我们考虑到做这样的结合,希望能涵养同学们的家国情怀,实现培养担当引领未来和造福人类的领军人才的目标。

希望通过这样的方式,激励东大学子不忘初心、牢记使命,在青春的赛道上奋力奔跑,将‘止于至善’的东大精神传递给更多的人,书写新时代青年的奋进与担当。

”东南大学的录取结果怎么查询目前江苏的强基和综评等已经录取完成,考生可以在所在省份考试院网站及东南大学本科招生网、东南大学本科招生官方微信公众号“录取查询”栏目进行查询。

认识实习报告

认识实习报告姓名:XXX学号:XXXXXXXX大三伊始,我们院系组织了一科电力系统的认识课程,这门课程需要实地参观,使我们对电力系统有了深刻、全面的认识。

我们不仅了解了设备生产的全过程,还对各个工厂部门和工作环境有了切身的体会。

在参观过程中,我们不断地发现问题,提出问题,气氛热烈,是我受用颇多。

首先,我们认识课程的主要内容是观看影像资料和实地参观。

在观看观看影像资料过程中,我们能够粗略的看到电气行业发展的现状和智能化的前景,这使我们为成为一名电气人而感到自豪与期待。

不仅如此,我们对火电发电厂的生产过程有了深刻的认识。

火电厂的发电过程分为5个部分:燃料系统,燃烧系统,汽水系统,电气系统,控制系统。

其中最重要的部件就是锅炉了。

但是还有一个设备也很重要,就是汽轮机。

汽轮机的图片给我的印象非常深刻。

它是以蒸汽为工质,将热能转换为机械能,为发电机发电提供机械能。

它的单机功率和运行的稳定性是衡量汽轮机的重要指标。

通过观看影像,我才了解到原来一颗小小的煤球能发挥出这么多的光与热,使我对火电厂的节能和高效利用率产生很大的兴趣。

不仅如此,我对电力系统、电网等方面也有了一个更清晰的认识,尤其是智能电网。

我国的智能电网主要是用于配电以及用户侧,在不久的将来,我们就能使用到万能遥控器、超快速的网络通道、便捷的新闻信息、全自动的家用电器以及太阳能的普及等这样现在还无法实现的高科技技术。

在不久的将来,我们都能受惠于智能的电网在医疗,吃住,教育等方面的革新。

在实地参观中,我们首先去了金智科技。

它依托于我们的东南大学,主要是研发、生产、销售发电厂、变电站的保护监控和自动装置。

但是,这座不是很恢宏的建筑中,有一群精通软件与网络信息技术的人才。

这里工作环境适宜,他们的团队协作十分和谐。

在这里,我看到了很多从来没有接触过设备,其中,印象比较深的是DCAP-4000型发电厂电气监控管理系统。

讲解的老师细心讲解了它的大致的用途和运用的技术与科技。

DNA存储技术

优点

优点

DNA存储技术作为数字存储媒介的显著优点之一是容量大。DNA分子是一种令人难以置信的密集存储介质,1 克DNA能够存储大约2拍字节,相当于大约300万张CD。

用DNA存储数据保存时间可能长达数千年。与硬盘、磁带等存储介质不同的是,DNA不需要经常维护。就读 取方式而言,DNA存储不涉及兼容问题。

原理

原理

存储模式(1张)英国的欧洲生物信息研究所研究小组利用DNA存储数据的关键是DNA碱基。DNA这种双螺旋结 构上有4个化学基团,即核碱基,它们按照特定顺序排列,组成遗传信息,指导生物体生长发育。

研究人员开发的DNA数字存储系统同样利用这4个碱基“字母”,开发定制代码,完全区别于生物体所用“语 言”。当复制一份计算机文件时,DNA数字存储系统首先把硬盘信息中的二进制数翻译成定制代码,然后借助标 准DNA合成机器制造出相应的碱基序列。这一序列并非一个长分子,而是多个重复片段,每一个片段携带一些索 引细节,明确各自在整体序列中所处位置。这样的系统虽然显得冗余,优点是即便某些片段遭损毁,数据不会丢 失。分子生物学实验室用来读取生物体DNA的标准设备可以读取信息,当即呈现在电脑屏幕上。

DNA存储技术

生物技术

01 简介

03 优点 点 06 发展历程

基本信息

DNA存储技术是一项着眼于未来的具有划时代意义存储技术,它利用人工合成的脱氧核糖核酸(DNA)作为存 储介质,具有高效、存储量大、存储时间长、易获取且免维护的优点。

简介

简介

DNA(1张)DNA存储技术即用人工合成的脱氧核糖核酸(DNA)存储文本文档、图片和声音文件等数据,随后 完整读取的技术。

应用

应用

DNA存储(1张)一些不常用却需要保存的信息,譬如政府文件、历史档案等,尤其适合用DNA存储。不过,他 们坦承,鉴于实验室合成DNA分子的成本,现阶段用它来存储信息“惊人地昂贵”,但随着技术发展,DNA存储技 术有望进入寻常百姓家。

第九届华东赛电磁组技术总结东南大学(共5篇)

第九届华东赛电磁组技术总结东南大学(共5篇)第一篇:第九届华东赛电磁组技术总结东南大学第九届华东赛赛后总结通过近四个月的努力学习和制作,我们组的作品最后在第九届全国大学生“飞思卡尔”杯华东赛区取得电磁组第十一的成绩,侥幸获得一等奖。

这四个多月的竞赛准备中,暴露了很多问题,前期不够重视,投入时间太少,以至于很多任务被推到最后一个月去解决,这也是我们止步十一名的主要原因。

而这些一定以及肯定要在下一届“飞思卡尔”比赛中去解决。

电磁组和光学组不一样,它获取赛道信息的方式比较简单,理论上仅需两个电感就可以判断出赛道的类型。

但是器获取的赛道信息也比较粗糙,不同的赛道可能拥有相同的磁场环境,这增加了误判的几率,给调试带来了难题。

下面就电磁组需要注意的几个方面谈谈自己的体会。

首先,电磁组是依靠电感来获取赛道类型的,所以不同的电感布局,我们会得到不同的赛道信息。

在本届华东赛中,增加了直角弯这种以前从未出现过的弯道。

用横排电感测试出的磁场环境和十字弯几乎没有差别,所以有必要加上竖排电感,或者倾斜的电感来加以区分直角弯和十字弯道。

我们组在准备阶段试过了几种不同的电感布局方式,发现斜着的电感可以识别直角弯,但是会干扰十字弯的判断。

建议斜着的电感在总控制量中不要占大的比重。

当然还有各种其它的布局方案,学弟学妹们可以自己尝试。

关于前瞻,前瞻对车的速度来说至关重要。

电磁组的前瞻需要利用碳杆来架设,建议其长度为45置50.前瞻不能一味的追求长度,也不能太短。

常前瞻固然可以提高反应速度,但是其不利于整个赛道路径的优化。

靠打死转弯是不行的。

电感的高度也影响着前瞻的大小,电感太高,前瞻太长,都会增加蹿道的几率。

关于蹿道,需要特别的算法来避免。

基本思想是在临界范围内,锁死电感的左右大小极性。

关于算法,传统的PID可以自己查资料,赛道的中心偏移量可以通过左边电感减去右边电感来获取,但是因为电感的衰减曲线不是线性的,其中心偏移量也不是线性的,所以单纯的一个p是不行的,我一直在探索动态p的算法,谁说其在弯道上的反应够快,但是在直到上,因为p的无线小,所以车会偏一边运动。

第六届北京大学生集成电路设计大赛获奖名单

广东工业大学巴拉拉小魔仙

杨程喻

庄楚楠

张圳彬

三等奖获奖名单

B228

中山大学ZY队

张紫莹

郑紫元

袁泽心

希格玛微电子企业杯

一等奖获奖名单

队伍编码

队名

队员1

队员2

队员3

B032

华中科技大学(8星8钻队)

刘向迪

郑凯伦

夏盛溪

二等奖获奖名单

M091

中国科学院大学梅森代表队

马松

周万兴

张闯

三等奖获奖名单

B155

新竹交大-北京工大pseudo队

郑

孔睿

张仲侯

M097

浙江大学超大所队

王武广

王喆鸿

M049

中国科学院大学-闪微队

郑岩

纪书江

时代民芯企业杯

一等奖获奖名单

队伍编码

队名

队员1

队员2

队员3

B149

南京邮电大学“邮你民芯”1队

高波

李金鑫

谭少卿

二等奖获奖名单

B122

大连理工大学脑洞大开队

刘文宇

闫晓鹏

三等奖获奖名单

第六届北京大学生集成电路设计大赛获奖名单

第六届(2016)北京大学生集成电路设计大赛获奖名单如下:

华大九天企业杯

一等奖获奖名单

队伍编码

队名

队员1

队员2

队员3

B051

北京工业大学主旋律队

汪浩

张琪

邢劼思

二等奖获奖名单

M009

电子科技大学碲铋队

吕彬彬

张净植

王子晟

M066

澳门大学InPoCit队

罗自洋

黄元庆

我感受的东南大学校园文化

我感受的东南大学校园文化2010年的九月,我怀着无比的期待和万分的欣喜之情来到南京,来到东南大学,这是我的人生的另一个起点,也是一段全新的人生的开始,一切都是那么新鲜。

占地面积3700亩的东南大学九龙湖校区无疑是南京大多数高校中的佼佼者,不仅于此,东南大学作为全国百年名校,更是以其独特的工科性质跻身国内一流大学的行列内。

带着“985”“211”的光环,东南大学在三年多的时间内也真实的让我感受到其综合实力的强大。

从平时的课程安排来看,东南大学合理的排满的各大年级的课程,使得学生能充分的学习专业知识的同时还能感受东南大学的有活力、热情的校园文化。

东南大学开设了许多人文课供大批学子选择,其中包含机械类、影视文化类、古文化欣赏类、经济以及工商管理类等,不管是在书面知识的了解还是在动手能力的seminer动手能力的提升方面,东南大学可谓是做到了极致。

与此同时,东南大学还提供了更优秀的学习资源,那就是校内文化素质修养讲座方面。

每个学年里,学校都会邀请各专业的精英人才到校内做相关方面的专题讲座。

从2010年入学以来,作为东南大学广大学子中的一员,我就已经很清楚的了解到东南大学要求我们在大学四年内至少要听完8次人文素质讲座,并且撰写八张相关讲座的听课表,并在最后撰写一篇关于东南大学人文素质讲座的论文,这样之后方可达到毕业要求。

我想这对于广大东南大学学子来说不仅是一项学习任务,也是丰富学生专业外知识的一个有效途径,在三年多的学习过程中,学校共邀请了数百知名人物做客东南大学的人文报告厅,在那里,他们带着无比的激情,挥洒着完美的英姿,向我们展示他们最擅长的领域。

这期间,我很欣然的前往人文报告厅细心聆听了他们的激情演讲,每次演讲过后,都对演讲的主题映像深刻,并从中学到了做人的道理、个人生涯的规划、东南大学悠久而详细的校园历史文化、影视戏剧的欣赏角度和方法。

我细心聆听的演讲有如下一些“中西经典文化讲座--当代国际格局的宗教背景”、“沧桑百载话东大——科学的东南与人文的东南”、“中国传统艺术系列演讲--扬剧艺术赏析会”、“中国民间剪纸艺术与吉祥图案”、“辛亥革命与近现代中国的国际发展”“至美的昆丑--中国昆曲艺术的魅力与欣赏”“钱学森先生改变和影响了我的人生轨迹---学习、弘扬、研究钱学森先生的教育思想与实践”、“感悟数学之美”“感受南京的历史与文化”等。

东南大学SEU4队技术报告

第四届“飞思卡尔”杯全国大学生智能汽车竞赛技术报告学校:东南大学队伍名称:东南大学SEU-4队参赛队员:王元哲王凯荣杰带队教师:谈英姿周怡君关于技术报告和研究论文使用授权的说明本人完全了解第四届“飞思卡尔”杯全国大学生智能汽车邀请赛关保留、使用技术报告和研究论文的规定,即:参赛作品著作权归参赛者本人,比赛组委会和飞思卡尔半导体公司可以在相关主页上收录并公开参赛作品的设计方案、技术报告以及参赛模型车的视频、图像资料,并将相关内容编纂收录在组委会出版论文集中。

参赛队员签名:带队教师签名:日期:摘要本报告我们是为参加第四届“飞思卡尔”杯全国大学生智能汽车邀请赛而撰写的技术报告在本报告中,我们详细介绍了本队的设计方案,包括机械结构的安装与调整、硬件电路的设计与制作、软件系统的开发及系统调试过程等。

本智能车系统以MC9S12XS128单片机作主控单元。

利用CMOS摄像头对道路进行检测,提取有用信息,包括前视横向偏差、小车前视方向与道路方向的斜率和道路的曲率等,通过PID方式对转向系统进行控制,同时,根据信息判断出相应的赛道类型,并分配以不同的速度给硬件电路加以控制,完成了在变负荷条件下对速度的快速稳定调节。

本报告将详细介绍智能车的机械结构安装与调整方法,硬件核心电路板及主控电路板的设计制作,摄像头工作机制、采样策略,舵机的转向控制,速度的闭环控制等。

除此之外,我们还将介绍在智能车制作过程中用到的开发工具,调试手段及智能车的技术参数。

关键词:图像处理、PID、控制策略、路径识别、速度传感器ABSTRACTThis article is the technical report written by us to participate in the fourth session of Freescale Cup National University smart race car.In this report, we detailed our design program, including the installation and adjustment of mechanics and structure, the design and production of hardware circuit,the development of software systems and the debugging of the system.The Smart car system uses Freescale MC9S12XS512 as core controller, the use of CMOS camera to detect road, extracting useful information, including the horizontal deviation of front view, the slope of the Trolley front view’s direction and the road’s direction and the curvature of the road, control steering system by way of PID, meanwhile, under the judgment of information corresponding to the traffic and to allocate different speed to phase-locked loop circuit, completion of the variable load conditions for the rapid and steady rate lock, greatly simplifying the software programming.This report will introduce the installation and adjustment method of mechanical structure of the car in detail, the core hardware circuit board and control circuit board, camera work mechanism, sampling strategy, steering control, the feedback speed control. In addition, we will introduce the development tools in the production process, debugging tools and the car's technical parameters.KEY WORD: image processing、PID、、control strategy、debugging、speed sensor目录摘要 (I)ABSTRACT (II)第一章 引 言 (1)1.1 比赛背景介绍 (1)1.2 总体设计思路 (1)1.3 文献资料综述 (2)1.4 技术报告结构 (2)第二章 机械结构安装调整 (4)2.1 整体建模 (4)2.2 技术参数 (5)2.3 舵机安装 (5)2.4 摄像头支架安装 (6)2.5 旋转编码器安装 (6)2.6 系统电路板安装 (6)2.7 前轮定位 (7)2.8 差速结构调整 (8)2.9 其他机械机构调整 (8)2.10 小结 (8)第三章 硬件电路设计 (9)3.1 核心板电路设计 (9)3.1.1 CPU资源简介 (9)3.1.2 晶振及锁相环电路 (9)3.1.3 复位电路 (9)3.1.4 CPU工作模式 (10)3.2 主控板电路设计 (10)3.2.1 视频同步分离电路 (10)3.2.2 电机驱动电路 (11)3.2.3 舵机驱动电路 (12)3.2.4 电源管理电路 (13)3.3 小结 (14)第四章 软件系统设计 (15)4.1 舵机标定 (15)4.2 图像采集及处理 (17)4.2.1 摄像头工作原理 (17)4.2.2 支架高度的确定 (18)4.2.3 视频采样 (18)4.2.4黑线中心提取跟踪算法 (20)4.2.5 直道判定算法 (21)4.3 控制策略 (22)4.3.1 PID 算法简介 (22)4.3.2 转向控制 (23)4.3.4 限速及刹车 (24)4.3.5 历史记录的使用 (24)4.4 小结 (24)第五章 开发工具与调试 (25)5.1 硬件部分调试 (25)5.2 软件部分调试 (26)5.3 小结 (26)第六章 总结 (27)参考文献 (28)附录一 电路原理图 (29)附录二 软件源程序 (29)第一章 引 言1.1 比赛背景介绍全国大学生智能汽车竞赛是教育部为了加强大学生实践、创新能力和团队精神的培养而设立的一项赛事,旨在进一步深化高等工程教育改革,培养本科生获取知识、应用知识的能力及创新意识;培养硕士生从事科学和技术研究能力;培养博士生知识和技术创新能力。

至善科技夏令营 新闻稿

“在这里,我们学到了很多,科技知识、做人做事,虽然只有短短的7天,但是这7天的每一天都是用感情筑造的。

”(张文嫣)“愿我能考上东南大学!”(王春燕)“这次的分别是为了下次更好地相遇,即使没有下一次的相遇,也但愿这7天的欢乐记忆将会是我一生中很珍贵的美好回忆,甜蜜而不忧伤,要快乐到最后一刻!”(赵元婧)“祝愿东南大学的老师们永远和我们的心连在一起,祝您快乐!再见!”(李一楠)这些来自心底的声音是孩子们在夏令营结束后,在留言板上写下的话语。

12载支教情深,2014又结硕果2003年东南大学第一次派出研究生支教团,便是来到了内蒙古准格尔旗这片土地,到今年已经先后派出了12届78位队员来到这里从事教育工作。

从最初的只负责课堂教学工作,到后来创办“东南大学希望之星班”资助学生完成学业、举办英语演讲比赛对课堂内容进行补充、组织“爱心手拉手”关爱留守儿童、医疗小分队前往准旗开展医疗工作、成立科技创新展厅带动校园科创竞赛、实现“蒲公英”圆梦游学计划、成立“诚信驿站”等促进当地教育发展的举措。

2014准格尔旗至善科技夏令营是由东南大学团委与准格尔旗团委共同主办,准格尔旗第三中学承办。

本次夏令营是东南大学与准格尔旗进一步深化合作的成果,是东南大学研究生支教团在准格尔旗长期教学形式的拓展。

夏令营以“科技创新”为主题,不仅是发挥了东南大学以理工科见长的特色,更是结合了近些年来准格尔旗当地科技教育发展的需求。

课程设置深入浅出,形式多样科技课程的设置以节能减排大赛、电路设计大赛、交通设计大赛、结构力学竞赛、智能车竞赛、机器人竞赛以及SRTP项目为基础,衍生出:节能减排、无处不在的无限电波、多才多艺的机器人、天地交而万物通、I car智能车漫谈和电子技术改变生活六个主题的科技课程,以及结构力学趣味加载组竞赛。

在前期的备课时老师们坚守的原则是:由简单到复杂、从概念到实物。

希望达到的目的是:学生能够形成自己对某一科技领域的认知;能够掌握基础概念;能够学会基础知识;能够在某一领域有自己的思考和想象。

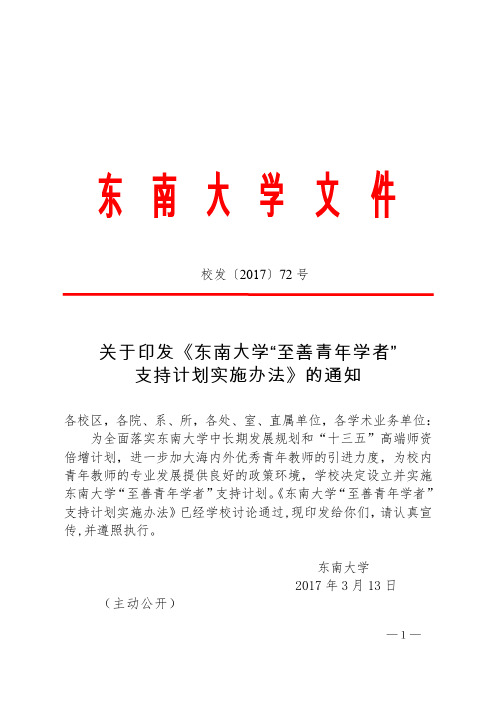

关于印发《东南大学“至善青年学者”支持计划实施办法》的通知

东南大学文件校发〔2017〕72号关于印发《东南大学“至善青年学者”支持计划实施办法》的通知各校区,各院、系、所,各处、室、直属单位,各学术业务单位:为全面落实东南大学中长期发展规划和“十三五”高端师资倍增计划,进一步加大海内外优秀青年教师的引进力度,为校内青年教师的专业发展提供良好的政策环境,学校决定设立并实施东南大学“至善青年学者”支持计划。

《东南大学“至善青年学者”支持计划实施办法》已经学校讨论通过,现印发给你们,请认真宣传,并遵照执行。

东南大学2017年3月13日(主动公开)—1—东南大学“至善青年学者”支持计划实施办法第一章总则第一条为加快东南大学世界一流大学和一流学科的建设步伐,根据东南大学中长期发展规划和“十三五”高端师资倍增计划,进一步加大海内外优秀青年教师的引进力度,为校内青年教师的专业发展提供良好的政策环境,特设立东南大学“至善青年学者”支持计划。

(以下简称“支持计划”)第二条“支持计划”着眼于培养和支持一批学术基础扎实、具有突出的创新能力和发展潜力的青年学术带头人或青年学术骨干,为学校选拔“青年长江”“青年拔尖人才”“国家自然基金优秀青年基金获得者”等高水平人才计划扩大师资储备。

通过A、B、C三个层次的支持体系,坚持培育成果与培养人才相统一。

通过“A层次”的支持,培育标志性成果,培养高层次青年才俊;通过“B层次”的支持,培育高水平成果,培养优秀青年骨干教师;通过“C层次”的支持,培育创新性成果,培养青年后备人才。

第三条“支持计划”实行聘期制,学校根据学科发展规划,在相关学科领域遴选优秀青年教师进行重点支持。

入选者冠以东南大学“至善青年学者”称号。

第四条“支持计划”是东南大学设立的专项基金,由学校财政专款拨付。

入选者在聘期内享受相应层次的待遇或经费资助。

—2—第二章基本条件第五条“支持计划”入选对象应分别具备以下基本条件:(一)东南大学“至善青年学者”(A层次)1.具有博士学位,在申报当年度的1月1日,年龄不超过35周岁。

道阻且长_行则将至——记东南大学教授温广辉

创新之路道阻且长 行则将至——记东南大学教授温广辉 李 莉 王慧娟 我们该如何认识这个世界?鱼群游弋,鸟群迁徙,萤火虫集体发光……自然界的动物在形成群体之后,仿佛能通过成员之间的“默契”与“配合”爆发出一种超越个体的智慧,进而带来整体利益的“最优解”。

20世纪90年代开始,这种内在的群体智慧逻辑被应用到人工智能领域,产生了“蚁群优化算法”“粒子群优化算法”及后来的群体智能、众包、群体计算等概念。

时光荏苒,随着人工智能技术的不断发展,2017年,中国国务院发布《新一代人工智能发展规划》。

其中,“群体智能”作为未来人工智能领域的重大研究方向21次被提及,引起广泛关注。

也是从这一年开始,我国在这一领域深耕的学者逐渐从幕后走向台前,东南大学80后教授温广辉就是其中的佼佼者。

面对“通信拓扑间歇含有生成树时多智能体系统如何实现一致性跟踪”这一难题,他的研究成果为切换通信拓扑下网络群体系统控制研究奠定了重要的理论基石,被国内外十余位院士、20余位美国电子与电气工程师协会会士(IEEE Fellow)正面引用并给予高度评价。

十多年来,温广辉共发表了150余篇《科学引文索引》(S C I)杂志论文和50余篇国际会议论文,S C I他引9800多次,出版英文学术专著2部。

自2018年开始,他更是持续被科睿唯安(Clarivate)评定为全球“高被引科学家”。

“认识世界只是科研的第一步。

”温广辉说,如何从这些现象之中得到启发,了解其中的机理,并用于改造世界,才是科研工作者真正应该追寻的大道。

为国科研,行而不辍2018年10月,科技部启动《科技创新2030“新一代人工智能”重大项目指南》。

作为未来人工智能重点发展的五大智能形态之一,“群体智能”凭借在民用和军用领域的重要应用前景,成为当年业界的热门研究方向。

彼时,温广辉早已在这一领域深耕多年。

他敏锐地意识到,自己长期专注研究的“复杂动态环境下网络群体系统理论与技术”将为今后复杂环境下无人集群的协同作业提供全新解决方案和发展框架。

第十五届至善杯东南大学大学生课外学术科技作品竞赛

第十五届“至善杯”东南大学大学生课外学术科技作品竞赛暨第十二届“挑战杯”全国大学生课外学术科技作品竞赛校内选拔作品申报书序号:编码:第十二届“挑战杯”全国大学生课外学术科技作品竞赛校级作品申报书作品名称:学校全称:申报者姓名(集体名称):类别:□自然科学类学术论文□哲学社会科学类社会调查报告和学术论文□科技发明制作A类□科技发明制作B类说明1、申报者应在认真阅读此说明各项内容后按要求详细填写。

2、申报者在填写申报作品情况时只需根据个人项目或集体项目填写A1或A2表,根据作品类别(自然科学类学术论文、哲学社会科学类社会调查报告和学术论文、科技发明制作)分别填写B1、B2或B3表。

所有申报者可根据情况填写C表。

3、表内项目填写时一律用钢笔或打印,字迹要端正、清楚,此申报书可复制。

4、序号、编码由第十二届“挑战杯”全国大学生课外学术科技作品竞赛省级竞赛组委会办公室填写。

5、学术论文、社会调查报告及所附的有关材料必须是中文(若是外文,请附中文本),请以4号楷体打印在A4纸上,附于申报书后,字数在8000字左右(文章版面尺寸14.5×22cm)。

6、作品申报书须按照要求由各高校竞赛协调机构统一寄送。

A1.申报者情况(个人项目)说明:1、必须由申报者本人按要求填写,申报者情况栏内必须填写个人作品的第一作者(承担申报作品60%以上的工作者);A2申报者情况(集体项目)说明:1、必须由申报者本人按要求填写;2、申报者代表必须是作者中学历最高者,其余作者按学历高低排列;B1.申报作品情况(自然科学类学术论文)说明:1、必须由申报者本人填写;2、本部分中的科研管理部门签章视为对申报者所填内容的确认;3、作品分类请按作品的学术方向或所涉及的主要学科领域填写;4、硕士研究生、博士研究生作品不在此列。

B2.申报作品情况(哲学社会科学类社会调查报告和学术论文)说明:1、必须由申报者本人填写;2、本部分中的管理部门签章视为对申报者所填内容的确认。

东南大学 SEU 创意组技术报告

第十届全国大学生“飞思卡尔”杯智能汽车竞赛技术报告学校:东南大学组别:创意组队伍名称: SEU参赛队员:李天助黄志亮杨天阳郑鹏曾欣带队老师:谈英姿孙琳关于技术报告和研究论文使用授权的说明本人完全了解第十届“飞思卡尔”杯全国大学生智能汽车邀请赛关保留、使用技术报告和研究论文的规定,即:参赛作品著作权归参赛者本人,比赛组委会和飞思卡尔半导体公司可以在相关主页上收录并公开参赛作品的设计方案、技术报告以及参赛模型车的视频、图像资料,并将相关内容编纂收录在组委会出版论文集中。

参赛队员签名:带队教师签名:日期:摘要: (1)第一章引言 (1)1.1 智能车竞赛概况 (5)1.2 本文研究内容 (5)1.3 整体设计思路 (5)1.4 技术概括 (6)第二章机械设计 (6)2.1 车模机械分析 (6)2.1.1转向轮 (7)2.1.2驱动轮 (7)2.1.3两翼螺旋桨 (9)2.2机械调整 (9)第三章硬件电路设计 (9)3.1 单片机系统板 (9)3.2 步进电机驱动 (11)3.3 两翼螺旋桨驱动 (11)3.4 电源供电 (12)第四章控制软件设计 (13)4.1 陀螺仪采集 (13)4.2 四元数法 (13)4.3 安全措施防护 (13)4.1 平衡控制 (14)4.1 寻向控制 (14)第五章开发及调试工具 (15)5.1 开发平台 (15)5.2 蓝牙无线调试平台 (15)5.3 USBDM 4.10.3烧写器 (16)第六章总结与展望 (17)本文针对第十届全国大学生智能车竞赛创意组赛题要求,使用飞思卡尔半导体公司生产的32位单片机MK60DN512ZVLL10作为主控制器,采用步进电机、舵机和两翼螺旋桨配合实现自行车模型的平衡与寻向。

姿态信息由MPU6050陀螺仪测得,MCU采集、计算并处理得到当前姿态信息,根据偏移角度和角加速度计算出两翼螺旋桨所加的PWM信号大小,以控制车身的平衡。

用电子罗盘测得当前航向,保证车模沿着2X2正方形的外接圆的轨迹行走,最终到达终点。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第五届全国大学生届全国大学生““飞思卡尔飞思卡尔””杯智能汽车竞赛技术报告东南大学东南大学“至善”队李垚沈赛峰马朔昕谈英姿周怡君学校:队伍名称:参赛队员:带队教师:第五届全国大学生智能汽车邀请赛技术报告关于技术报告和研究论文使用授权的说明本人完全了解第五届“飞思卡尔”杯全国大学生智能汽车邀请赛关保留、使用技术报告和研究论文的规定,即:参赛作品著作权归参赛者本人,比赛组委会和飞思卡尔半导体公司可以在相关主页上收录并公开参赛作品的设计方案、技术报告以及参赛模型车的视频、图像资料,并将相关内容编纂收录在组委会出版论文集中。

参赛队员签名:带队教师签名:日期:第3页共48页摘要本文记录了东南大学“至善”队队员在准备第五届“飞思卡尔”杯智能汽车竞赛中的工作成果和体会,并总结了方案中成功的经验和不足之处,愿与各高校代表队分享。

根据大赛规则,本智能车系统以单片MC9S12XS128单片机作主控单元,利用振荡回路感应引导线中交变电流产生的电磁波信号指出前进方向,CPU处理信息后驱动电机与舵机推动车模前进及转弯,依靠干簧管检测起跑线完成自动启停。

在运行过程中,依靠PID算法对赛道进行稳定跟踪并对车速进行控制,实现稳定快速的运行。

由于电磁组为本届竞赛新增组别,各种方案差异性较大,我们在不断尝试的过程中走了许多弯路。

但在学校的场地资金支持、两位带队老师的技术指导和各位前辈的无私帮助下,我们成功完成了小车,在此谨表达对他们的由衷感谢和尊敬。

关键词:电磁导航PID单片机应用第五届全国大学生智能汽车邀请赛技术报告AbstractThis paper concluded works and experiences of the team of perfectionists from South East University made during preparation for the fifth session of Freescale Cup National University smart race car,including both strong and weak point of the project,intended to be shared with other teams.Based on the regulations of the competition,this smart car uses one MC9S12XS128singlechip as the CPU and determine the route by signal from oscillation circuits due to electromagnetic wave from the alternating current in the guiding wire.After processing the signal,CPU drives the car by controlling motor and steer engine and stops the car by distinguishing the termination by reed switches. Throughout the race,the algorithm of PID contributes to tracing route and controlling pace.Since the group of electromagnetic-car comes on to the stage for the first time in the history of smartcar,there comes out all kinds of schemes which are quite different from each other,this team went through many branch roads.The perfectionists smartcar is finally brought to life upon the support of lab and funds from South East University,guidance from Ms.Tan and Mr.Zhou,great help from two Mr.Wang,and effort from the team.All thanks.【KEYS】Electromagnetic navigation PID Singlechip application第5页共48页目录摘要 (3)Abstract (4)目录 (5)第一章电磁环境制作 (7)1.1电磁环境介绍 (7)1.2电源设计 (7)1.3引导线选择与铺设 (8)1.4起跑线磁铁 (8)第二章整车方案设计 (10)2.1整车方案概述 (10)2.2模块方案选择 (10)2.2.1核心控制器 (10)2.2.2电机及驱动 (11)2.2.3导线检测模块 (11)2.2.4舵机 (11)2.2.6无线模块 (11)2.2.7辅助输入设备 (11)2.2.8电源模块 (11)2.2.9起跑线检测模块 (11)第三章机械结构调整 (13)3.1机械结构概述 (13)3.2舵机安装 (13)3.3探测电感的安装 (14)3.4干簧管安装 (14)3.5编码器安装 (15)3.6系统主板安装 (16)3.7前轮倾角调整 (16)3.8差速调整 (17)3.9车体全貌 (17)第四章硬件电路规划 (19)4.1电路模块综述 (19)4.2电源模块 (19)4.3检测模块 (20)4.5核心板 (22)第五章控制软件算法 (23)5.1软件流程图 (23)5.2中断使用情况 (23)5.3舵机控制 (24)5.4电机控制 (24)第六章开发调试工具 (25)第五届全国大学生智能汽车邀请赛技术报告6.1BDM/PE (25)6.2无线模块 (25)6.3Matlab (27)第七章车辆主要参数 (28)第八章总结 (29)8.1本方案的优势 (29)8.2本方案的不足 (29)致谢 (30)附录A参考文献 (31)附录B调试程序 (31)第7页共48页第一章电磁环境制作1.1电磁环境介绍在本届“飞思卡尔”杯智能车大赛中,首次加入了电磁竞赛组,其相关规定大致如下:禁止使用光学制导,跟踪对象为赛道下方沿赛道中线铺设的导线,导线中通有20kHz、50~150mA交变电流;起跑线为表面磁场强度3000~5000G直径1cm厚度1~3mm的磁铁。

可见,电磁环境主要由三部分组成:(1)提供稳定可调20±2kHz、50~150mA电流的电源;(2)坚韧、导电、发热量少的引导线;(3)起跑线磁铁。

1.2电源设计我们在王元哲前辈的指导下采用了与大赛组委会不同的电源方案,但同样实现了要求的指标。

主要原理为:由一片XS128提供PWM波,再将此方波转换为同频率的正弦波,最后功率输出。

系统原理图如图1.1,实物图如图1.2.图1.1电源原理图第五届全国大学生智能汽车邀请赛技术报告图1.2电源实物图1.3引导线选择与铺设大赛组委会提供的建议中,可供选择的有拆卸旧变压器得到漆包线或购买全新。

考虑到稳定性和成本,我们选择使用全新漆包线。

实际使用中,铺设一条总长约50米的赛道只需要数元成本,相比泡沫板赛道的价格,完全可以接受。

为了和摄像头、光电组共享赛道,漆包线可以被贴在黑线以下。

经过多次试验,我们发现先使用普通裁纸刀(刃最好略厚)先在泡沫板沿路径中心上划出5mm深的凹槽,再用指甲或铅笔将漆包线按压嵌入凹槽,再贴上黑线,就能够让漆包线得到充分保护,不会突出赛道而被车辆划伤。

特别注意的是,在漆包线引出处应将双股线拧成一股,可有效防止无意拉断。

1.4起跑线磁铁组委会明确给出了起跑线磁铁的规格,但实际购买有一定难度,主要是缺少第9页共48页方便的测试手段。

推荐在淘宝网上直接购买(4元/块,不含邮费),经实测达标。

埋设磁铁相对容易,只要用裁纸刀剥去埋放位置处的赛道表皮后,轻刮出一个对应大小的凹坑,放入磁铁后用黑胶带封住即可。

经过实际测试,磁铁的NS 极摆放顺序对检测几乎没有影响。

第五届全国大学生智能汽车邀请赛技术报告第二章整车方案设计2.1整车方案概述竞赛规则规定,智能车系统采用飞思卡尔的16位微控制器MC9S12XS128单片机作为核心控制单元用于智能车系统的控制。

在选定智能车系统采用谐振回路传感器方案后,赛车的位置信号由车体前方的谐振回路采集并放大,经XS128 MCU的I/O口处理后,用于赛车的运动控制决策,同时内部PWM模块发出PWM 波,驱动直流电机对智能车进行加速和减速控制,以及伺服电机对赛车的转向进行控制,使赛车在赛道上能够自主行驶,并以最短的时间最快的速度跑完全程。

为了对赛车的速度进行精确的控制,在智能车后轴上安装光电编码器,采集车轮转速的脉冲信号,经MCU捕获后进行PID自动规划,完成智能车速度的闭环控制。

此外,还增加了拨码盘作为输入设备,用于智能车的参数调整。

系统总体方框图如图2.1。

图1.1整车方案框图2.2模块方案选择2.2.1核心控制器我们选择MC9S12XS128芯片作为核心控制器,相对于DG128,它的性能略优但对车辆性能提升影响微乎其微,但成本也没有差距,加上之前的使用经验,选择了此芯片。

2.2.2电机及驱动按照组委会规定,我们使用了指定车模自带电机,驱动选择了双MOS管。

相比常用的33886并联,MOS管控制电流小,减少CPU发热,同时内阻小、驱动电流大,有利于快速加速和制动。

2.2.3导线检测模块为了检测20kHz交变磁场,我们使用了LC谐振回路,经由运算放大器放大整流后AD采样。

相比三极管放大电路,运算放大器优势在于放大后波形失真度低,缺点在于需要提供负电源并且有反应速率略低,但实际试验后发现影响很小。

2.2.4舵机我们使用了标准舵机。

2.2.5速度传感器我们购买了200线编码器做为速度传感器。

相对自制编码器,其计数精度高而稳定,但价格相对较高。

与别的队伍交流发现,自制编码器也可以达到很好效果。

2.2.6无线模块为了更好的调试,我们使用了无线模块对车速、舵机方向和传感器参数进行监控的无线模块,大大提高了调试效率。

2.2.7辅助输入设备为了提高调试效率及在比赛中准备多套方案可供切换,辅助的输入设备必不可少。

通常使用的有按键和拨码开关两种。

拨码开关好处在于简明易懂,不需要液晶等输出设备就可以知道当前输入状态,在实际调试中8位拨码开关很好的满足了我们的需求。