《计算机体系结构》第四次实验 Tomasulo方法实验

计算机体系结构试卷试题(答案全)

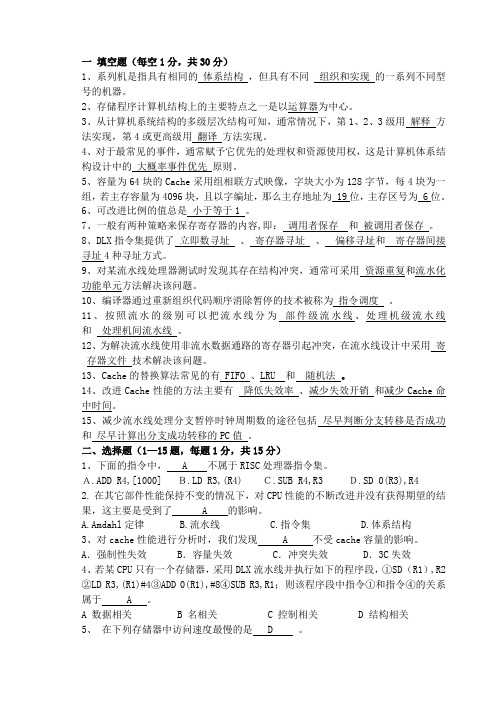

一填空题(每空1分,共30分)1、系列机是指具有相同的体系结构,但具有不同组织和实现的一系列不同型号的机器。

2、存储程序计算机结构上的主要特点之一是以运算器为中心。

3、从计算机系统结构的多级层次结构可知,通常情况下,第1、2、3级用解释方法实现,第4或更高级用翻译方法实现。

4、对于最常见的事件,通常赋予它优先的处理权和资源使用权,这是计算机体系结构设计中的大概率事件优先原则。

5、容量为64块的Cache采用组相联方式映像,字块大小为128字节,每4块为一组,若主存容量为4096块,且以字编址,那么主存地址为 19 位,主存区号为 6 位。

6、可改进比例的值总是小于等于1 。

7、一般有两种策略来保存寄存器的内容,即:调用者保存和被调用者保存。

8、DLX指令集提供了立即数寻址、寄存器寻址、偏移寻址和寄存器间接寻址4种寻址方式。

9、对某流水线处理器测试时发现其存在结构冲突,通常可采用资源重复和流水化功能单元方法解决该问题。

10、编译器通过重新组织代码顺序消除暂停的技术被称为指令调度。

11、按照流水的级别可以把流水线分为部件级流水线、处理机级流水线和处理机间流水线。

12、为解决流水线使用非流水数据通路的寄存器引起冲突,在流水线设计中采用寄存器文件技术解决该问题。

13、Cache的替换算法常见的有 FIFO 、LRU 和随机法。

14、改进Cache性能的方法主要有降低失效率、减少失效开销和减少Cache命中时间。

15、减少流水线处理分支暂停时钟周期数的途径包括尽早判断分支转移是否成功和尽早计算出分支成功转移的PC值。

二、选择题(1—15题,每题1分,共15分)1、下面的指令中, A 不属于RISC处理器指令集。

A.ADD R4,[1000] B.LD R3,(R4) C.SUB R4,R3 D.SD 0(R3),R42. 在其它部件性能保持不变的情况下,对CPU性能的不断改进并没有获得期望的结果,这主要是受到了 A 的影响。

计算机体系结构模拟试卷整理版

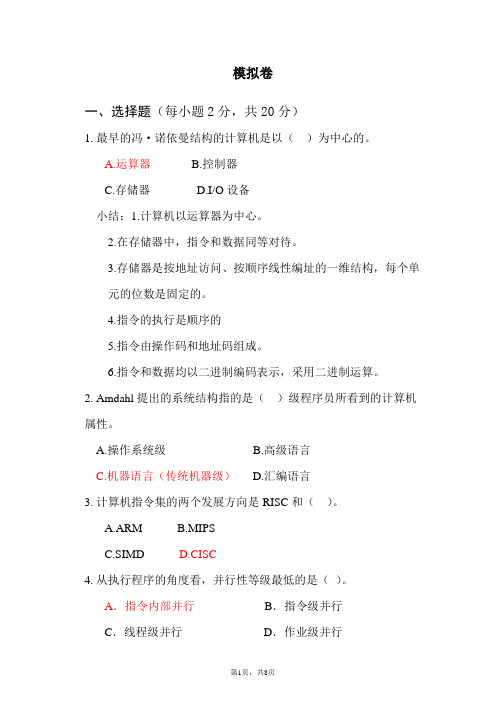

模拟卷一、选择题(每小题2分,共20分)1.最早的冯·诺依曼结构的计算机是以()为中心的。

A.运算器B.控制器C.存储器D.I/O设备小结:1.计算机以运算器为中心。

2.在存储器中,指令和数据同等对待。

3.存储器是按地址访问、按顺序线性编址的一维结构,每个单元的位数是固定的。

4.指令的执行是顺序的5.指令由操作码和地址码组成。

6.指令和数据均以二进制编码表示,采用二进制运算。

2.Amdahl提出的系统结构指的是()级程序员所看到的计算机属性。

A.操作系统级B.高级语言C.机器语言(传统机器级)D.汇编语言3.计算机指令集的两个发展方向是RISC和()。

A.ARMB.MIPSC.SIMDD.CISC4.从执行程序的角度看,并行性等级最低的是()。

A.指令内部并行B.指令级并行C.线程级并行D.作业级并行小结:指令内部并行、指令级并行、线程级并行、任务级或过程级并行、作业或程序级并行5.流水线的通过时间是指流水线中()流出结果所需的时间。

A.流水线第一段B.流水线第二段C.第一个任务D.最后一个任务小结:排空时间:最后一个任务从进入流水线到流出结果所需的时间。

6.弗林(Michael J. Flynn)对计算机的分类中,MIMD指的是()计算机。

A.单指令流单数据流B.单指令流多数据流C.多指令流单数据流D.多指令流多数据流7..因为分支指令引起的相关叫做()相关。

A.数据B.结构C.控制D.循环8.基本的MIPS整数流水线中,访存地址的计算发生在流水线的第()段。

A.1 B.2 C.3D.49.RISC执行程序的速度比CISC要快的原因是()。

A.RISC的指令系统中指令条数较少B.程序在RISC上编译生成的目标程序较短。

C.RISC的指令平均执行周期数较少。

D.RISC只允许load和store指令访存。

10.通过编译器重新安排指令的执行顺序以减少流水的停顿方法,称之为( )。

A.线性流水线B.非线性流水线C.动态调度D.静态调度二、填空题(每空2分,共30分)1.按某个时期投入市场的某种型号机器编制的程序,不加修改地就能运行于在它之前或之后投入市场的机器。

《计算机体系结构》教学大纲

《计算机体系结构》教学大纲英文名称:Computer Architecture预修课程:计算机原理、数据结构、操作系统、编译原理、高级语言总学时数:45学时,其中讲授36学时,课内实验4学时。

学分:2.5教学对象:计算机科学与技术专业本科学员开课学期:第6学期一、课程的性质、地位和任务该课程是计算机专业一门非常重要的专业基础课。

课程系统介绍进行计算机系统设计所必须了解与掌握的专业知识,重点介绍计算机体系结构的基本思想、基本概念、设计原理、设计方法与评价分析方法。

本课程内容广、概念多、系统性强、实例多,涉及计算机体系结构技术领域前沿。

本课程的任务是要使学生能够系统全面正确理解和掌握计算机体系结构技术的基本思想,并培养学生按照定量分析的方法初步设计和评价计算机系统的能力。

二、教学内容和要求(一)计算机体系结构基础内容和要求:了解计算机系统设计的基本任务;了解计算机技术发展的趋势;了解计算机性能与成本的影响因素,以及性能的评价方法,掌握计算机体系结构基本概念和定量分析方法的基本原理。

重点:计算机设计的基本任务,计算机体系结构基本概念,定量分析方法基本原理(二)计算机指令集结构设计内容和要求:从计算机系统指令集结构设计出发了解典型指令集结构的技术特点及其发展,掌握计算机系统指令集结构的设计方法以及各种设计方案的优缺点;掌握一种RISC指令集结构实例。

重点:计算机系统指令集结构设计,RISC指令集结构实例(三)流水线技术内容和要求:掌握流水线技术的基本原理及其性能评价方法;掌握RISC指令集结构流水线的基本设计方法,并能够从数据相关与控制相关两个方面分析流水线性能,掌握提高流水线性能的软硬件方法。

掌握向量处理机原理;了解基本的向量处理机结构;掌握向量处理机性能改善和评价的基本方法。

重点:流水线的基本原理与设计、分析评价方法、向量处理机原理(四)指令级并行内容和要求:掌握指令级并行的基本概念、指令的动态调度技术,理解控制相关的动态解决技术,掌握多指令流出技术的基本原理。

计算机系统结构 第四章(流水处理和ILP)

本章内容>>流水线基本概念

引 入

标量处理机

具有标量数据表示和标量指令系统的处理机称 为标量处理机。

提高指令执行速度的主要途径

提高处理机的工作主频;

采用更好的算法和设计更好的功能部件;

幻灯片 5/264

执行 △t

同济大学.电子与信息工程学院.计算机科学与工程系

本章内容>>流水线基本概念>>流水线工作原理

5 之 2

流水线基本思想

顺序执行

取指k 分析k 执行k 取指k+1 分析k+1 执行k+1 ……

n条指令的执行时间为:

优点: 控制简单,节省设备。 n T ( t取指i t分析i t执行i) 缺点: i 1 处理器执行指令的速度慢 3nt 功能部件的利用率很低

2 之 1

分类一

按流水线具有功能的多少来分,可分为: 单功能流水线 只能完成一种固定功能的 流水线。例如:Cray-1计算 机中有12条;YH-1计算机 有18条;Pentium有一条5 段定点和一条8段浮点流水 线;PentiumⅢ有两条定点 和一条浮点指令流水线。 多功能流水线 流水线的各段通过不同连 接实现不同功能。例如: Texas公司的ASC机,8段 流水线,能够实现:定点加 减法、定点乘法、浮点加法、 浮点乘法、逻辑运算、移位 操作、数据转换、向量运算 等。

本章内容>>流水线基本概念>>流水线工作原理>>流水线表示方法

2 之 1

连接图

输 入 分析器 分析k+1 t1 流水 锁存器 执行部件 执行k t2 流水 锁存器 输 出

动态调度(Cont),推断执行和ILP

Local predictor :两级预测器

• Top level :1024个10-bit 项构成,每个10-bit项对应最近10次分支 的转移方向 • Next level :由Top level所选项中的10-bit索引找到1K 项中的对应 项,每项由3-bit saturating counter 作为局部预测器

计算机体系结构 Chapter4_3.4

进行循环重叠执行需要尽快解决分支问题!

在循环展开的例子中,我们假设整数部件可以快速解决分 支问题,以便进行循环重叠执行! Loop: LD MULTD SD SUBI BNEZ F0 F4 F4 R1 R1 0 F0 0 R1 Loop R1 F2 R1 #8

计算机体系结构

Chapter4_3.14

Correlating Branch Predicator

例如: if (aa==2) aa=0; if (bb==2) bb=0; if (aa!=bb) { 翻译为DLX SUBI R3,R1,#2 BNEZ R3,L1 ADDI R1,R0,R0 L1: SUBI R3,R2,#2 BNEZ R3,L2 ADDI R2,R0,R0 L2: SUBI R3,R1,R2 BEQZ R3,L3

2-bit recent global branch history (01 = not taken then taken)

计算机体系结构 Chapter4_3.21

计算机体系结构

Chapter4_3.22

Tournament Predictors

Tournament predictors:

动态调度 (Cont), 推断执行 和ILP

计算机体系结构 Chapter4_3.1

西安邮电大学体系结构Tomasulo算法实验报告

实验4 Tomasulo算法1 实验目的(1)加深对指令级并行性及开发的理解。

(2)加深对Tomasulo算法的理解。

(3)掌握Tomasulo算法在指令流出、执行、写结果各阶段对浮点操作指令以及load和store指令进行了什么处理。

(4)掌握采用了Tomasulo算法的浮点处理部件的结构。

(5)掌握保留站的结构。

(6)给定被执行的程序片段,对于具体某个时钟周期,能够写出保留站、指令状态表以及浮点寄存器状态表内容的变化情况。

2 实验平台采用Tomasulo算法模拟器。

3 实验内容和步骤首先要掌握Tomasulo算法模拟器的使用方法(见随附的ppt)。

1)、假设浮点功能部件的延迟时间为:加减法2个时钟周期,乘法10个时钟周期,除法40个时钟周期,Load部件2个时钟周期。

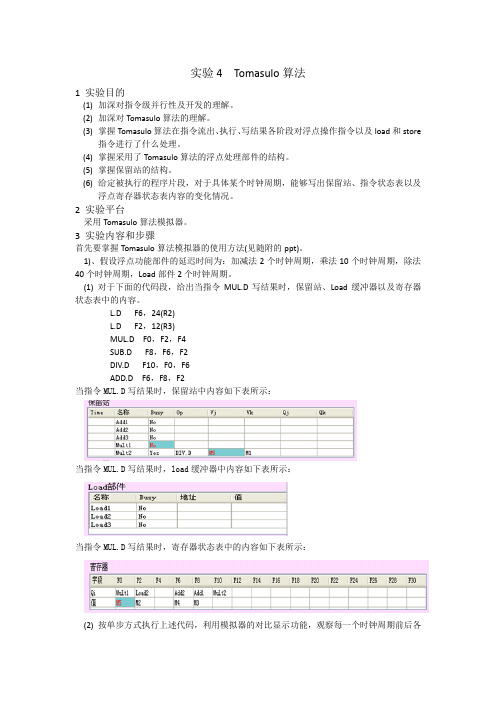

(1) 对于下面的代码段,给出当指令MUL.D写结果时,保留站、Load缓冲器以及寄存器状态表中的内容。

L.D F6,24(R2)L.D F2,12(R3)MUL.D F0,F2,F4SUB.D F8,F6,F2DIV.D F10,F0,F6ADD.D F6,F8,F2当指令MUL.D写结果时,保留站中内容如下表所示:当指令MUL.D写结果时,load缓冲器中内容如下表所示:当指令MUL.D写结果时,寄存器状态表中的内容如下表所示:(2) 按单步方式执行上述代码,利用模拟器的对比显示功能,观察每一个时钟周期前后各信息表中内容的变化情况。

观察分析:周期1:取出第一条指令L.D F6, 24(R2),地址偏移量24写入LOAD1,LOAD1名存入寄F6。

周期2:取出第二条指令L.D F2, 12(R3),地址偏移量12写入LOAD2,LOAD2名存入寄器F2,同时第一条指令开始执行,LOAD1上写入绝对地址。

周期3:取出第三条指令MUL.D F0, F2,F4,第一条指令完成,第二条指令开始执行,LOAD2上写入绝对地址。

保留站中存入待运算的操作数和操作。

《计算机体系结构》第四次实验tomasulo方法实验

《计算机体系结构》第四次实验T o m a s u l o方法实验-标准化文件发布号:(9456-EUATWK-MWUB-WUNN-INNUL-DDQTY-KIITomasulo方法实验姓名:王宇航学号:09283020Tomasul o方法实验一、实验目的:通过本实验,理解指令流水化过程中乱序执行和寄存器重命名方法。

二、实验内容:1、用dlxView模拟器或Tomasulo算法模拟器执行浮点指令程序段。

2、指出指令乱序执行和寄存器重命名过程。

三、实验环境操作系统:Windows 7 旗舰版处理器:Intel(R) Core(TM) i3 双核内存:软件:Tomasulo算法模拟器四、实验过程:1、设置Tomasulo算法模拟器参数其中Load部件的执行时间不能设置为1,至少为2,故不作修改;加/减法部件的执行时间为4个时钟周期,乘法部件的执行时间为7个时钟周期,除法部件的执行时间为15个时钟周期。

2、分析Tomasulo算法模拟器中指令乱序执行过程Tomasulo算法模拟器中默认设置的指令下图所示:执行该指令序列,重点观察指令状态的写结果一栏,便会发现执行过程中存在乱序执行现象,共有两处乱序执行,分别如下列图所示:图中显示,在第10周期时,位于指令之后的指令经过4个周期已经执行完成并已经将结果写回寄存器,而指令仍在执行中。

在第13周期时,指令经过7个周期执行完毕,才将结果写回。

此外,还可以看到,位于指令之后的指令在第11周期时就已经开始执行,而指令直至现在都未开始执行。

在第15周期时,指令经过4个周期执行完毕,先于指令写回结果;而指令仍在执行中。

在第29周期时,指令经过15个周期终于执行完毕,将结果写回寄存器。

以上分析证明,在Tomasulo算法中存在乱序执行并且不会影响执行结果的正确性。

这是因为,Tomasulo算法采用分布的保留站,冲突检测和指令执行控制是分布的。

3、分析Tomasulo算法模拟器中寄存器重命名过程在Tomasulo算法中通过寄存器重命名来消除WAR冲突,这一过程是通过保留站来完成的。

高级计算机体系结构 5 Tomasulo和动态分支预测

Computer ArchitectureLecture 5:Tomasulo Algorithm and DynamicBranch PredictionSpring 2010Super Computing Lab.Review•Instruction Level Parallelism (ILP) in SW or HW•Loop level parallelism is the easiest one to see/exploit •SW parallelism dependencies defined for program, hazards if HW cannot resolve•SW dependencies/compiler sophistication determine if compiler can unroll loops–Memory dependencies hardest to determine•HW exploiting ILP–Works when cannot know dependence at run time–Code for one machine runs well on another•Key idea of Scoreboard: Allow instructions behind stall to proceed (Decode => Issue instr & read operands)–Enables out-of-order execution => out-of-order completion–ID stage checked both for structural & data dependenciesReview: Three Parts of Scoreboard1.Instruction status: which of 4 steps the instruction is in2. Functional unit status: indicates the state of the functional unit (FU) & 9 fields for each functional unitBusy: indicates whether the unit is busy or notOp: operation to perform in the unit (e.g., + or -)Fi: destination registerFj, Fk : source-register numbersQj, Qk : functional units producing source registers Fj, FkRj, Rk: flags indicating when Fj, Fk are ready3. Register result status: Indicates which functional unit will write each register, if one exists. Blank when no pending instructions will write that registerReview: Scoreboard Example Cycle 3 Instruction status Read Execution WriteInstruction j k Issue operands c omplete ResultLD F634+R2123LD F245+R3MULTD F0F2F4SUBD F8F6F2DIVD F10F0F6ADDDF6F8F2Functional unit status dest S1S2FU for j FU for k Fj?Fk?Time Name Busy Op Fi Fj Fk Qj Qk Rj RkInteger Yes Load F6R2YesMult1NoMult2NoAdd NoDivide NoRegister result statusClock F0F2F4F6F8F10F12...F30 3FU Integer• Issue MULT? No, stall on structural hazardReview: Scoreboard Example Cycle 9 Instruction status Read Execution WriteInstruction j k Issue operands c omplete ResultLD F634+R21234LD F245+R35678MULTD F0F2F469SUBD F8F6F279DIVD F10F0F68ADDDF6F8F2Functional unit status dest S1S2FU for j FU for k Fj?Fk?Time Name Busy Op Fi Fj Fk Qj Qk Rj RkInteger No10Mult1Yes Mult F0F2F4Yes Yes Mult2No2Add Yes Sub F8F6F2Yes YesDivide Yes Div F10F0F6Mult1No YesRegister result statusClock F0F2F4F6F8F10F12...F30 9FU Mult1Add Divide• Read operands for MULT & SUBD & Issue ADDD?Review: Scoreboard Example Cycle 17 Instruction status Read Execution WriteInstruction j k Issue operands c omplete ResultLD F634+R21234LD F245+R35678MULTD F0F2F469SUBD F8F6F2791112DIVD F10F0F68ADDDF6F8F2131416Functional unit status dest S1S2FU for j FU for k Fj?Fk?Time Name Busy Op Fi Fj Fk Qj Qk Rj RkInteger No2Mult1Yes Mult F0F2F4Yes YesMult2NoAdd Yes Add F6F8F2Yes YesDivide Yes Div F10F0F6Mult1No Yes Register result statusClock F0F2F4F6F8F10F12...F3017FU Mult1Add Divide• Write result of ADDD? No, WAR hazardReview: Scoreboard Example Cycle 62 Instruction status Read Execution WriteInstruction j k Issue operands c omplete ResultLD F634+R21234LD F245+R35678MULTD F0F2F4691920SUBD F8F6F2791112DIVD F10F0F68216162ADDDF6F8F213141622Functional unit status dest S1S2FU for j FU for k Fj?Fk?Time Name Busy Op Fi Fj Fk Qj Qk Rj RkInteger NoMult1NoMult2NoAdd No0Divide NoRegister result statusClock F0F2F4F6F8F10F12...F3062FU•In-order issue; out-of-order execute & commitReview: Scoreboard Summary•Limitations of 6600 scoreboard–No forwarding (First write register then read it)–Limited to instructions in basic block(small window)–Number of functional units (structural hazards)–Wait for WAR hazards–Prevent WAW hazardsAnother Dynamic Algorithm:Tomasulo Algorithm•For IBM 360/91•Goal: High Performance without special compilers •Differences between IBM 360 & CDC 6600 ISA –IBM has only 2 register specifiers/instr vs. 3 in CDC 6600–IBM has 4 FP registers vs. 8 in CDC 6600•Why Study => lead to Alpha 21264, HP 8000, MIPS 10000, Pentium II, PowerPC 604Tomasulo Algorithm vs. Scoreboard•Control & buffers distributed with Function Units (FU) vs. centralized in scoreboard;–FU buffers called, reservation stations, have pending operands•Registers in instructions replaced by values or pointers to reservation stations(RS); called register renaming ;–avoids WAR, WAW hazards–More reservation stations than registers, so can do optimizations compilerscannot•Results to FU from RS, not through registers, over Common Data Bus that broadcasts results to all FUs•Load and Store units treated as FUs with RSs as well•Integer instructions can go past branches, allowingFP ops beyond basic block in FP queueFP adders Add1 Add2 Add3FP multipliers Mult1 Mult2From MemFP RegistersTo MemFP Op QueueLoad BuffersStore BuffersLoad1 Load2 Load3 Load4 Load5 Load6Tomasulo OrganizationCommon data bus (CDB)FP AdderReservation StationsFP multiplierReservation StationsReservation Station ComponentsOp: Operation to perform in the unit (e.g., + or -)Vj, Vk: Value of Source operands–Store buffers has V field, result to be storedQj, Qk: Reservation stations producing source registers (value to be written)–Note: No ready flags as in Scoreboard; Qj,Qk=0 => ready–Store buffers only have Qi for RS producing resultBusy: Indicates reservation station or FU is busyRegister result status: Indicates which functional unit will write each register, if one exists. Blank when no pending instructions that will write that register.Three Stages of Tomasulo Algorithm 1. Issue: Get instruction from FP Op QueueIf reservation station free (no structural hazard),control issues instr & sends operands (renames registers)2. Execution: Operate on operands (EX)When both operands ready then execute;if not ready, watch Common Data Bus for result3. Write result: Finish execution (WB)Write on Common Data Bus to all awaiting units;mark reservation station available•Normal data bus: data + destination (go to bus)•Common data bus: data + source (come from bus)–64 bits of data + 4 bits of Functional Unit source address–Write if matches expected Functional Unit (produces result)–Does the broadcastInstruction status Execution WriteInstruction j k Issue complete Result Busy AddressLD F634+R2Load1NoLD F245+R3Load2NoMULTD F0F2F4Load3NoSUBD F8F6F2DIVD F10F0F6ADDD F6F8F2Reservation Stations S1S2RS for j RS for kTime Name Busy Op Vj Vk Qj Qk0Add1No0Add2No0Add3No0Mult1No0Mult2NoRegister result statusClock F0F2F4F6F8F10F12...F30 0FUInstruction status Execution WriteInstruction j k Issue complete Result Busy AddressLD F634+R21Load1Yes34+R2LD F245+R3Load2NoMULTD F0F2F4Load3NoSUBD F8F6F2DIVD F10F0F6ADDD F6F8F2Reservation Stations S1S2RS for j RS for kTime Name Busy Op Vj Vk Qj Qk0Add1No0Add2NoAdd3No0Mult1No0Mult2NoRegister result statusClock F0F2F4F6F8F10F12...F30 1FU Load1Instruction status Execution WriteInstruction j k Issue complete Result Busy AddressLD F634+R21Load1Yes34+R2LD F245+R32Load2Yes45+R3 F0F2F4Load3NoMULTDSUBD F8F6F2DIVDF10F0F6ADDD F6F8F2Reservation Stations S1S2RS for j RS for kTimeNameBusy Op Vj Vk Qj Qk0Add1No0Add2NoAdd3No0Mult1No0Mult2NoRegister result statusClock F0F2F4F6F8F10F12...F30 2FU Load2Load1Note: Unlike 6600, can have multiple loads outstandingInstruction status Execution WriteInstruction j k Issue complete Result Busy AddressLD F634+R213Load1Yes34+R2LD F245+R32Load2Yes45+R3 F0F2F43Load3NoMULTDSUBD F8F6F2DIVDF10F0F6ADDD F6F8F2Reservation Stations S1S2RS for j RS for kTimeNameBusy Op Vj Vk Qj Qk0Add1No0Add2NoAdd3No0Mult1Yes MULTD R(F4)Load20Mult2NoRegister result statusClock F0F2F4F6F8F10F12...F30 3FU Mult1Load2Load1•Note: registers names are removed (renamed in Reservation Stations); MULT issued vs. scoreboard •Load1 completing; what is waiting for Load1?Instruction status Execution WriteInstruction j k Issue complete Result Busy AddressLD F634+R2134Load1NoLD F245+R324Load2Yes45+R3MULTD F0F2F43Load3NoSUBD F8F6F24DIVD F10F0F6ADDDF6F8F2Reservation Stations S1S2RS for j RS for kTime Name Busy Op Vj Vk Qj Qk0Add1Yes SUBD M(34+R2)Load20Add2NoAdd3No0Mult1Yes MULTD R(F4)Load20Mult2NoRegister result statusClock F0F2F4F6F8F10F12...F30 4FU Mult1Load2M(34+R2)Add1• Load2 completing; what is waiting for it?Instruction status Execution WriteInstruction j k Issue complete Result Busy AddressLD F634+R2134Load1NoLD F245+R3245Load2NoF0F2F43Load3NoMULTDSUBD F8F6F24DIVDF10F0F65ADDD F6F8F2Reservation Stations S1S2RS for j RS for kTimeNameBusy Op Vj Vk Qj Qk2Add1Yes SUBD M(34+R2)M(45+R3)0Add2NoAdd3No10Mult1Yes MULTD M(45+R3)R(F4)0Mult2Yes DIVD M(34+R2)Mult1Register result statusClock F0F2F4F6F8F10F12...F30 5FU Mult1M(45+R3)M(34+R2)Add1Mult2Instruction status Execution WriteInstruction j k Issue complete Result Busy AddressLD F634+R2134Load1NoLD F245+R3245Load2NoF0F2F43Load3NoMULTDSUBD F8F6F24DIVDF10F0F65ADDD F6F8F26Reservation Stations S1S2RS for j RS for kTimeNameBusy Op Vj Vk Qj Qk1Add1Yes SUBD M(34+R2)M(45+R3)0Add2Yes ADDD M(45+R3)Add1Add3No9Mult1Yes MULTD M(45+R3)R(F4)0Mult2Yes DIVD M(34+R2)Mult1Register result statusClock F0F2F4F6F8F10F12...F30 6FU Mult1M(45+R3)Add2Add1Mult2• Issue ADDD here vs. scoreboard?Instruction status Execution WriteInstruction j k Issue complete Result Busy AddressLD F634+R2134Load1NoLD F245+R3245Load2NoF0F2F43Load3NoMULTDSUBD F8F6F247DIVDF10F0F65ADDD F6F8F26Reservation Stations S1S2RS for j RS for kTimeNameBusy Op Vj Vk Qj Qk0Add1Yes SUBD M(34+R2)M(45+R3)0Add2Yes ADDD M(45+R3)Add1Add3No8Mult1Yes MULTD M(45+R3)R(F4)0Mult2Yes DIVD M(34+R2)Mult1Register result statusClock F0F2F4F6F8F10F12...F30 7FU Mult1M(45+R3)Add2Add1Mult2• Add1 completing; what is waiting for it?Instruction status Execution WriteInstruction j k Issue complete Result Busy AddressLD F634+R2134Load1NoLD F245+R3245Load2NoF0F2F43Load3NoMULTDSUBD F8F6F2478DIVDF10F0F65ADDD F6F8F26Reservation Stations S1S2RS for j RS for kTimeNameBusy Op Vj Vk Qj Qk0Add1No2Add2Yes ADDDM()-M()M(45+R3)0Add3No7Mult1Yes MULTD M(45+R3)R(F4)0Mult2Yes DIVD M(34+R2)Mult1Register result statusClock F0F2F4F6F8F10F12...F30 8FU Mult1M(45+R3)Add2M()-M()Mult2Instruction status Execution WriteInstruction j k Issue complete Result Busy AddressLD F634+R2134Load1NoLD F245+R3245Load2NoF0F2F43Load3NoMULTDSUBD F8F6F2478DIVDF10F0F65ADDD F6F8F26Reservation Stations S1S2RS for j RS for kTimeNameBusy Op Vj Vk Qj Qk0Add1No1Add2Yes ADDDM()-M()M(45+R3)0Add3No6Mult1Yes MULTD M(45+R3)R(F4)0Mult2Yes DIVD M(34+R2)Mult1Register result statusClock F0F2F4F6F8F10F12...F30 9FU Mult1M(45+R3)Add2M()-M()Mult2Instruction status Execution WriteInstruction j k Issue complete Result Busy AddressLD F634+R2134Load1NoLD F245+R3245Load2NoF0F2F43Load3NoMULTDSUBD F8F6F2478DIVDF10F0F65ADDD F6F8F2610Reservation Stations S1S2RS for j RS for kTimeNameBusy Op Vj Vk Qj Qk0Add1No0Add2Yes ADDDM()?()M(45+R3)0Add3No5Mult1Yes MULTD M(45+R3)R(F4)0Mult2Yes DIVD M(34+R2)Mult1Register result statusClock F0F2F4F6F8F10F12...F30 10FU Mult1M(45+R3)Add2M()?()Mult2• Add2 completing; what is waiting for it?Instruction status Execution WriteInstruction j k Issue complete Result Busy AddressLD F634+R2134Load1NoLD F245+R3245Load2NoF0F2F43Load3NoMULTDSUBD F8F6F2478DIVDF10F0F65ADDD F6F8F261011Reservation Stations S1S2RS for j RS for kTimeNameBusy Op Vj Vk Qj Qk0Add1No0Add2No0Add3No4Mult1Yes MULTD M(45+R3)R(F4)0Mult2Yes DIVD M(34+R2)Mult1Register result statusClock F0F2F4F6F8F10F12...F30 11FU Mult1M(45+R3)(M-M)+M()M()?()Mult2• Write result of ADDD here vs. scoreboard?Instruction status Execution WriteInstruction j k Issue complete Result Busy AddressLD F634+R2134Load1NoLD F245+R3245Load2NoF0F2F43Load3NoMULTDSUBD F8F6F2467DIVDF10F0F65ADDD F6F8F261011Reservation Stations S1S2RS for j RS for kTimeNameBusy Op Vj Vk Qj Qk0Add1No0Add2No0Add3No3Mult1Yes MULTD M(45+R3)R(F4)0Mult2Yes DIVD M(34+R2)Mult1Register result statusClock F0F2F4F6F8F10F12...F30 12FU Mult1M(45+R3)(M-M)+M()M()?()Mult2•Note: all quick instructions complete alreadyInstruction status Execution WriteInstruction j k Issue complete Result Busy AddressLD F634+R2134Load1NoLD F245+R3245Load2NoF0F2F43Load3NoMULTDSUBD F8F6F2478DIVDF10F0F65ADDD F6F8F261011Reservation Stations S1S2RS for j RS for kTimeNameBusy Op Vj Vk Qj Qk0Add1No0Add2NoAdd3No2Mult1Yes MULTD M(45+R3)R(F4)0Mult2Yes DIVD M(34+R2)Mult1Register result statusClock F0F2F4F6F8F10F12...F30 13FU Mult1M(45+R3)(M?)+M()M()?()Mult2Instruction status Execution WriteInstruction j k Issue complete Result Busy AddressLD F634+R2134Load1NoLD F245+R3245Load2NoF0F2F43Load3NoMULTDSUBD F8F6F2478DIVDF10F0F65ADDD F6F8F261011Reservation Stations S1S2RS for j RS for kTimeNameBusy Op Vj Vk Qj Qk0Add1No0Add2No0Add3No1Mult1Yes MULTD M(45+R3)R(F4)0Mult2Yes DIVD M(34+R2)Mult1Register result statusClock F0F2F4F6F8F10F12...F30 14FU Mult1M(45+R3)(M?)+M()M()?()Mult2Instruction status Execution WriteInstruction j k Issue complete Result Busy AddressLD F634+R2134Load1NoLD F245+R3245Load2NoF0F2F4315Load3NoMULTDSUBD F8F6F2478DIVDF10F0F65ADDD F6F8F261011Reservation Stations S1S2RS for j RS for kTimeNameBusy Op Vj Vk Qj Qk0Add1No0Add2NoAdd3No0Mult1Yes MULTD M(45+R3)R(F4)0Mult2Yes DIVD M(34+R2)Mult1Register result statusClock F0F2F4F6F8F10F12...F30 15FU Mult1M(45+R3)(M?)+M()M()?()Mult2• Mult1 completing; what is waiting for it?Instruction status Execution WriteInstruction j k Issue complete Result Busy AddressLD F634+R2134Load1NoLD F245+R3245Load2NoF0F2F431516Load3NoMULTDSUBD F8F6F2478DIVDF10F0F65ADDD F6F8F261011Reservation Stations S1S2RS for j RS for kTimeNameBusy Op Vj Vk Qj Qk0Add1No0Add2NoAdd3No0Mult1No40Mult2Yes DIVD M*F4M(34+R2)Register result statusClock F0F2F4F6F8F10F12...F30 16FU M*F4M(45+R3)(M?)+M()M()?()Mult2•Note: Just waiting for divideInstruction status Execution WriteInstruction j k Issue complete Result Busy AddressLD F634+R2134Load1NoLD F245+R3245Load2NoF0F2F431516Load3NoMULTDSUBD F8F6F2478DIVDF10F0F65ADDD F6F8F261011Reservation Stations S1S2RS for j RS for kTimeNameBusy Op Vj Vk Qj Qk0Add1No0Add2NoAdd3No0Mult1No1Mult2Yes DIVD M*F4M(34+R2)Register result statusClock F0F2F4F6F8F10F12...F30 55FU M*F4M(45+R3)(M?)+M()M()?()Mult2Instruction status Execution WriteInstruction j k Issue complete Result Busy AddressLD F634+R2134Load1NoLD F245+R3245Load2NoF0F2F431516Load3NoMULTDSUBD F8F6F2478DIVDF10F0F6556ADDD F6F8F261011Reservation Stations S1S2RS for j RS for kTimeNameBusy Op Vj Vk Qj Qk0Add1No0Add2NoAdd3No0Mult1No0Mult2Yes DIVD M*F4M(34+R2)Register result statusClock F0F2F4F6F8F10F12...F30 56FU M*F4M(45+R3)(M?)+M()M()?()Mult2• Mult 2 completing; what is waiting for it?Instruction status Execution WriteInstruction j k Issue complete Result Busy AddressLD F634+R2134Load1NoLD F245+R3245Load2NoF0F2F431516Load3NoMULTDSUBD F8F6F2478DIVDF10F0F655657ADDD F6F8F261011Reservation Stations S1S2RS for j RS for kTimeNameBusy Op Vj Vk Qj Qk0Add1No0Add2NoAdd3No0Mult1No0Mult2NoRegister result statusClock F0F2F4F6F8F10F12...F30 57FU M*F4M(45+R3)(M?)+M()M()?()M*F4/M •Again, in-oder issue,out-of-order execution, completionCompare to Scoreboard Cycle 62 Instruction status Read Execution WriteInstruction j k Issue operands c omplete ResultLD F634+R21234LD F245+R35678MULTD F0F2F4691920SUBD F8F6F2791112DIVD F10F0F68216162ADDDF6F8F213141622Functional unit status dest S1S2FU for j FU for k Fj?Fk?Time Name Busy Op Fi Fj Fk Qj Qk Rj Rk Integer NoMult1NoMult2NoAdd No0Divide NoRegister result statusClock F0F2F4F6F8F10F12...F30 62FU•Why takes longer on Scoreboard/6600?Tomasulo v. Scoreboard(IBM 360/91 v. CDC 6600)Pipelined Functional Units Multiple Functional Units(6 load, 3 store, 3 +, 2 x/) (1 load/store, 1 + , 2 x, 1 ) window size: 14 instructions 5 instructionsNo issue on structural hazard same WAR: renaming avoids stall completionWAW: renaming avoids stall completion Broadcast results from FU Write/read registers Control: reservation stations central scoreboardTomasulo Drawbacks•Complexity–delays of 360/91, MIPS 10000, IBM 620?•Many associative stores (CDB) at high speed •Performance limited by Common Data Bus –Multiple CDBs => more FU logic for parallel assoc storesTomasulo Loop ExampleLoop: LD F0 0 R1MULTD F4 F0 F2SD F4 0 R1SUBI R1 R1 #8BNEZ R1 Loop•Assume Multiply takes 4 clocks•Assume first load takes 8 clocks (cache miss?), second load takes 4 clocks (hit)•To be clear, will show clocks for SUBI, BNEZ •Reality, integer instructions aheadInstruction status ExecutionWriteInstruction j k iteration Issue complete Result Busy AddressLD F00R11Load1NoMULTD F4F0F21Load2NoSD F40R11Load3No QiLD F00R12Store1NoMULTD F4F0F22Store2NoSD F40R12Store3NoReservation Stations S1S2RS for j RS for kTime Name Busy Op Vj Vk Qj Qk Code:0Add1No LD F00R10Add2No MULTD F4F0F20Add3No SD F40R10Mult1No SUBI R1R1#80Mult2No BNEZ R1Loop Register result statusClock R1F0F2F4F6F8F10F12...F30 080QiInstruction status ExecutionWriteInstruction j k iteration Issue complete Result Busy AddressLD F00R111Load1Yes80MULTD F4F0F21Load2NoSD F40R11Load3No QiLD F00R12Store1NoMULTD F4F0F22Store2NoSD F40R12Store3NoReservation Stations S1S2RS for j RS for kTime Name Busy Op Vj Vk Qj Qk Code:0Add1No LD F00R10Add2No MULTD F4F0F20Add3No SD F40R10Mult1No SUBI R1R1#80Mult2No BNEZ R1Loop Register result statusClock R1F0F2F4F6F8F10F12...F30 180Qi Load1Instruction status ExecutionWriteInstruction j k iteration Issue complete Result Busy AddressLD F00R111Load1Yes80MULTD F4F0F212Load2NoSD F40R11Load3No QiLD F00R12Store1NoMULTD F4F0F22Store2NoSD F40R12Store3NoReservation Stations S1S2RS for j RS for kTime Name Busy Op Vj Vk Qj Qk Code:0Add1No LD F00R10Add2No MULTD F4F0F20Add3No SD F40R10Mult1Yes MULTD R(F2)Load1SUBI R1R1#80Mult2No BNEZ R1Loop Register result statusClock R1F0F2F4F6F8F10F12...F30 280Qi Load1Mult1Instruction status ExecutionWriteInstruction j k iteration Issue complete Result Busy AddressLD F00R111Load1Yes80MULTD F4F0F212Load2NoSD F40R113Load3No QiLD F00R12Store1Yes80Mult1 MULTD F4F0F22Store2NoSD F40R12Store3NoReservation Stations S1S2RS for j RS for kTime Name Busy Op Vj Vk Qj Qk Code:0Add1No LD F00R10Add2No MULTD F4F0F20Add3No SD F40R10Mult1Yes MULTD R(F2)Load1SUBI R1R1#80Mult2No BNEZ R1Loop Register result statusClock R1F0F2F4F6F8F10F12...F30 380Qi Load1Mult1Instruction status ExecutionWriteInstruction j k iteration Issue complete Result Busy AddressLD F00R111Load1Yes80MULTD F4F0F212Load2NoSD F40R113Load3No QiLD F00R12Store1Yes80Mult1 MULTD F4F0F22Store2NoSD F40R12Store3NoReservation Stations S1S2RS for j RS for kTime Name Busy Op Vj Vk Qj Qk Code:0Add1No LD F00R10Add2No MULTD F4F0F20Add3No SD F40R10Mult1Yes MULTD R(F2)Load1SUBI R1R1#80Mult2No BNEZ R1Loop Register result statusClock R1F0F2F4F6F8F10F12...F30 472Qi Load1Mult1Instruction status ExecutionWriteInstruction j k iteration Issue complete Result Busy AddressLD F00R111Load1Yes80MULTD F4F0F212Load2NoSD F40R113Load3No QiLD F00R12Store1Yes80Mult1 MULTD F4F0F22Store2NoSD F40R12Store3NoReservation Stations S1S2RS for j RS for kTime Name Busy Op Vj Vk Qj Qk Code:0Add1No LD F00R10Add2No MULTD F4F0F20Add3No SD F40R10Mult1Yes MULTD R(F2)Load1SUBI R1R1#80Mult2No BNEZ R1Loop Register result statusClock R1F0F2F4F6F8F10F12...F30 572Qi Load1Mult1Instruction status ExecutionWriteInstruction j k iteration Issue complete Result Busy AddressLD F00R111Load1Yes80MULTD F4F0F212Load2Yes72SD F40R113Load3No QiLD F00R126Store1Yes80Mult1 MULTD F4F0F22Store2NoSD F40R12Store3NoReservation Stations S1S2RS for j RS for kTime Name Busy Op Vj Vk Qj Qk Code:0Add1No LD F00R10Add2No MULTD F4F0F20Add3No SD F40R10Mult1Yes MULTD R(F2)Load1SUBI R1R1#80Mult2No BNEZ R1Loop Register result statusClock R1F0F2F4F6F8F10F12...F30 672Qi Load2Mult1Instruction status ExecutionWriteInstruction j k iteration Issue complete Result Busy AddressLD F00R111Load1Yes80MULTD F4F0F212Load2Yes72SD F40R113Load3No QiLD F00R126Store1Yes80Mult1 MULTD F4F0F227Store2NoSD F40R12Store3NoReservation Stations S1S2RS for j RS for kTime Name Busy Op Vj Vk Qj Qk Code:0Add1No LD F00R10Add2No MULTD F4F0F20Add3No SD F40R10Mult1Yes MULTD R(F2)Load1SUBI R1R1#80Mult2Yes MULTD R(F2)Load2BNEZ R1Loop Register result statusClock R1F0F2F4F6F8F10F12...F30 772Qi Load2Mult2WriteInstruction status ExecutionInstruction j k iteration Issue complete Result BusyAddressLD F00R111Load1Yes80 F4F0F212Load2Yes72MULTDSD F40R113Load3No QiLD F00R126Store1Yes80Mult1 F4F0F227Store2Yes72Mult2 MULTDSD F40R128Store3NoReservation Stations S1S2RS for j RS for kTime NameBusy Op Vj Vk Qj Qk Code:0Add1No LD F00R1F4F0F2 0Add2No MULTD0Add3No SD F40R10Mult1Yes MULTD R(F2)Load1SUBIR1R1#80Mult2Yes MULTD R(F2)Load2BNEZ R1Loop Register result statusClock R1F0F2F4F6F8F10F12...F30 872Qi Load2Mult2Instruction status ExecutionWriteInstruction j k iteration Issue complete Result Busy AddressLD F00R1119Load1Yes80MULTD F4F0F212Load2Yes72SD F40R113Load3No QiLD F00R126Store1Yes80Mult1 MULTD F4F0F227Store2Yes72Mult2SD F40R128Store3NoReservation Stations S1S2RS for j RS for kTime Name Busy Op Vj Vk Qj Qk Code:0Add1No LD F00R10Add2No MULTD F4F0F20Add3No SD F40R10Mult1Yes MULTD R(F2)Load1SUBI R1R1#80Mult2Yes MULTD R(F2)Load2BNEZ R1Loop Register result statusClock R1F0F2F4F6F8F10F12...F30 964Qi Load2Mult2WriteInstruction status ExecutionInstruction j k iteration Issue complete Result BusyAddressLD F00R111910Load1NoF4F0F212Load2Yes72MULTDSD F40R113Load3No QiLD F00R12610Store1Yes80Mult1 F4F0F227Store2Yes72Mult2 MULTDSD F40R128Store3NoReservation Stations S1S2RS for j RS for kTime NameBusy Op Vj Vk Qj Qk Code:0Add1No LD F00R1F4F0F2 0Add2No MULTD0Add3No SD F40R14Mult1Yes MULTD M(80)R(F2)SUBIR1R1#80Mult2Yes MULTD R(F2)Load2BNEZ R1Loop Register result statusClock R1F0F2F4F6F8F10F12...F30 1064Qi Load2Mult2Instruction status ExecutionWriteInstruction j k iteration Issue complete Result Busy AddressLD F00R111910Load1NoMULTD F4F0F212Load2NoSD F40R113Load3Yes64QiLD F00R1261011Store1Yes80Mult1 MULTD F4F0F227Store2Yes72Mult2SD F40R128Store3NoReservation Stations S1S2RS for j RS for kTime Name Busy Op Vj Vk Qj Qk Code:0Add1No LD F00R10Add2No MULTD F4F0F20Add3No SD F40R13Mult1Yes MULTD M(80)R(F2)SUBI R1R1#84Mult2Yes MULTD M(72)R(F2)BNEZ R1Loop Register result statusClock R1F0F2F4F6F8F10F12...F30 1164Qi Load3Mult2Instruction status ExecutionWriteInstruction j k iteration Issue complete Result Busy AddressLD F00R111910Load1NoMULTD F4F0F212Load2NoSD F40R113Load3Yes64QiLD F00R1261011Store1Yes80Mult1 MULTD F4F0F227Store2Yes72Mult2SD F40R128Store3NoReservation Stations S1S2RS for j RS for kTime Name Busy Op Vj Vk Qj Qk Code:0Add1No LD F00R10Add2No MULTD F4F0F20Add3No SD F40R12Mult1Yes MULTD M(80)R(F2)SUBI R1R1#83Mult2Yes MULTD M(72)R(F2)BNEZ R1Loop Register result statusClock R1F0F2F4F6F8F10F12...F30 1264Qi Load3Mult2。

level 4

level 4Level 4内容:计算机科学是一门广泛而深奥的学科,涵盖了许多不同的主题。

以下是一些与计算机科学相关的内容,以及对它们的简要介绍。

1. 数据结构与算法:数据结构是组织和存储数据的方式,而算法是用于解决问题的一系列指令。

学习数据结构和算法可以帮助我们更有效地处理和操作数据,从而提高程序的效率。

2. 编程语言:编程语言是用于编写计算机程序的工具。

不同的编程语言有不同的语法和规则,可以用于不同的应用。

一些常见的编程语言是Java、Python、C++等。

3. 软件工程:软件工程是研究如何开发高质量软件的学科。

它包括从需求分析、设计到测试和维护的整个软件开发过程。

软件工程还研究如何管理和组织软件项目,以确保项目的成功。

4. 数据库:数据库是用于存储和管理数据的系统。

它可以用于存储大量的结构化数据,并提供数据的查询和操作功能。

数据库管理系统(DBMS)是用于管理数据库的软件工具,常见的DBMS有MySQL、Oracle等。

5. 计算机网络:计算机网络是连接计算机和其他设备的通信系统。

它包括局域网、广域网和互联网等,是实现计算机之间通信和共享资源的基础。

6. 人工智能:人工智能是研究如何使计算机具备智能的学科。

它涉及机器学习、自然语言处理、图像识别等技术,旨在开发出能够模仿人类智能行为的计算机系统。

7. 计算机图形学:计算机图形学是研究如何生成和处理图像和动画的学科。

它涵盖了三维建模、渲染、虚拟现实等领域,广泛应用于游戏开发、电影制作等行业。

8. 操作系统:操作系统是管理计算机硬件和软件资源的系统。

它提供了一组基本的功能,如进程管理、文件管理和内存管理,使得计算机可以有效地运行应用程序。

9. 计算机安全:计算机安全是保护计算机系统和数据免受未经授权访问、损坏或泄露的学科。

它包括网络安全、密码学等领域,旨在确保计算机系统的可靠和安全。

10. 软件测试:软件测试是验证和评估软件功能和质量的过程。

计算机体系结构报告

中南大学计算机体系结构实验报告学生姓名郁博文指导教师雷向东学院信息科学与工程学院专业班级信安1302班学号 ********** 完成时间 2015年11月4日实验 1 对指令操作码进行霍夫曼编码一、实验目的了解和掌握指令编码的基本要求和基本原理二、实验要求使用编程工具编写一个程序,对一组指令进行霍夫曼编码,并输出最后的编码结果以及对指令码的长度进行评价。

与扩展操作码和等长编码进行比较。

问题描述以及问题分析:我们举例说明此问题,例如:有一组指令的操作码共分七类,它们出现概率如下表所示:P1 P2 P3 P4 P5 P6 P70.45 0.30 0.15 0.05 0.03 0.01 0.01对此组指令进行 HUFFMAN 编码正如下图所示:三、实验内容因为各字符在信息中出现的频率是不同的,若根据字符出现的不同频率分配给不同长度的编码:频繁出现的字符分配给较短的编码,不常出现的字符分配给较长的编码,且这种编码还具有“前缀特性”,那么这样的编码电文总长会最短,发送效率会最高,占用的空间会最少。

而哈弗曼编码就是这样一种编码,字符出现的频率与该程序中对应的权重。

首先将建立哈弗曼树,将权重最小的放在二叉树的最低端,将权重最大的放置在离根结点最近的位置,这样就可以使权重大的结点的编码较短,权重小的结点的编码较长。

实际上是建立一个表格,中间有结点的权重,父亲和孩子的信息。

建立好哈弗曼树之后,要使得哈弗曼的左子树的编码为0,右子树的编码为1。

可以通过这个来确定字符的哈弗曼编码。

四、实验原理构造 HUFFMAN 树所要做的工作:1、先对各指令操作码的出现概率进行排序,构造一个有序链表。

2、再取出两个最小的概率节点相加,生成一个生的节点加入到链表中,同时从两表中删除此两个节点。

3、在对链表进行排序,链表是否只有一个节点,是则 HUFFAN 树构造完毕,否则继续做 2 的操作。

为此设计一个工作链表(链表的元素时类,此类的功能相当结构。

计算机方法论-chapter 4 计算学科中的三个学科形态

第二次飞跃是从精神到物质,从认识到实践的飞跃。这 次飞跃的实质对技术学科(计算学科就是一门技术学科) 而言,其实就是要在理论的指导下,以抽象的成果为工 具来完成各种设计工作。

9

三个学科形态的内在联系

N(x)=0(零函数),

Ui(n)(x1,x2,…,xn)=xi,1≤i≤n(投影函数) 上述3个函数的任意组合。

从递归论中,我们知道这3个函数属于初始递归函数

任何原始递归函数都是从这3个初始递归函数经有限次的复 合、递归和极小化操作得到的。

从可计算理论可知,每一个原始递归函数都是图灵机可计算

号“(”开头且以“)”结尾的符号串,为一公式。

问:Y是否为一形式语言?

答:不是。 因为,根据形成规则,无法对不是以符号“(”开头

且以“)”结尾的符号串进行判定。例如,(a+b)c。

19

例4:形式语言语法示例

语言Z定义为:

初始符号集:{a,b,c,d,e,(,),,,,}。 形成规则:上述符号组成的有限符号串中,凡以符

波斯特系统(字符串处理 算 机 等 实 现 技

语言的基础);

术;

λ-演算(函数式语言的基 数 字 电 子 计 算

础)等计算模型

机产品

12

BACK

ห้องสมุดไป่ตู้

1、自然语言与形式语言

人类的语言(文字)是人类最普遍使用的符号系统。其最基 本、最普遍的形式是自然语言符号系统

歧义性; 不够严格和不够统一的语法结构。

31

冯·诺依曼型计算机的组织结构

存储器

计算机体系结构-量化研究方法笔记2

计算机体系结构-量化研究方法笔记2一、概述在计算机科学领域,计算机体系结构是一个重要的研究方向。

量化研究方法可以帮助我们更好地理解和分析计算机体系结构的复杂性,从而为优化和改进计算机系统提供支持。

本文将就计算机体系结构的量化研究方法进行笔记整理,并对相关内容进行深入探讨。

二、量化研究方法的基本概念1. 量化研究方法的定义量化研究方法是一种通过定量数据和分析技术来研究问题和现象的方法。

在计算机体系结构领域,量化研究方法可以帮助我们收集和分析系统性能数据、硬件指标、指令级别的执行统计等信息,从而更好地了解计算机系统的特性和性能表现。

2. 量化研究方法的优势量化研究方法可以提供客观、可验证的数据和结论,有利于科学研究的的严谨性和可靠性。

通过量化分析,我们可以深入挖掘计算机体系结构的内在规律和特点,为系统设计和优化提供有效的依据。

三、量化研究方法在计算机体系结构中的应用1. 性能评估与优化在计算机体系结构研究中,性能评估与优化是一个重要的课题。

量化研究方法可以帮助我们通过实验数据和分析来评估系统的性能,找到系统瓶颈并进行相应的优化。

通过量化分析,我们可以发现系统运行过程中的性能瓶颈,提出优化方案并验证其有效性。

2. 硬件设计与验证在计算机体系结构的硬件设计与验证中,量化研究方法同样具有重要作用。

通过收集和分析硬件指标、延迟统计、能耗数据等信息,我们可以对硬件设计方案进行量化评估,验证设计的可行性和性能表现。

3. 架构模拟与分析在计算机体系结构的研究中,架构模拟与分析也是一个重要的方向。

量化研究方法可以为架构模拟和分析提供数据支持,帮助我们对系统进行深入分析、研究和验证,从而发现系统的特性和行为规律。

四、量化研究方法在实际工作中的挑战与应对1. 数据收集的难点在实际工作中,数据收集往往是一个比较困难的环节。

不同的计算机系统、应用场景、工作负载等因素都会对数据收集产生影响,因此如何有效地进行数据收集是一个需要仔细考虑和处理的问题。

《计算机系统结构》课程教学大纲

《计算机系统结构》课程教学大纲英文课程名称: Computer Architecture 课程编号:授课语言:中文学分:3课内学时:51 课程性质:专业课先修课程:计算机组成原理考试/考查:考试是否全英/双语课程:否一、课程定位和基本要求1.课程定位本课程是计算机专业和软件工程专业的一门重要专业课。

其目的是提高学生从总体结构、系统分析这一层次来研究和分析计算机系统的能力,帮助学生建立整机的概念;使学生掌握计算机系统结构的概念、原理、结构以及设计和分析方法,并对计算机系统结构的发展历史和现状有所了解。

2.课程教学目标课程教学目标1:掌握计算机系统结构相关的基本概念和计算机系统的设计方法,掌握定量分析的基本方法以及计算机系统的性能评测技术。

掌握计算机系统结构中并行性的发展。

课程教学目标2:理解指令集结构的分类及指令系统设计中应考虑的各种因素,掌握计算机指令系统的设计方法,掌握指令操作码的优化编码。

课程教学目标3:掌握流水线的基本概念、分类以及性能分析,掌握基本MIPS流水线的实现,掌握流水线中的各种冲突及其解决方法。

课程教学目标4:掌握向量处理机的基本概念、结构和性能评价方法。

课程教学目标5:掌握指令级并行的概念及其硬件开发方法,掌握Tomasulo算法以及动态分支预测技术。

课程教学目标6:掌握指令级并行开发的软件方法,包括基本指令调度、循环展开、全局指令调度(踪迹调度和超块调度)、静态多指令流出、显式并行指令计算;掌握开发循环级并行的方法,如软流水。

课程教学目标7:掌握多级存储层次,掌握Cache的组成及性能分析,掌握改进Cache 性能的方法;课程教学目标8:掌握磁盘冗余阵列RAID以及通道的工作原理和性能分析;课程教学目标9:掌握互连函数、互连网络的参数和性能指标,掌握静态互连网络和动态互连网络。

课程教学目标10:掌握多处理机系统的两种存储结构模型, 掌握实现多Cache一致性的监听法和目录法。

Tomasulo算法实验报告

Tomasulo算法实验报告一、实验目的本次实验的主要目的是深入理解和研究 Tomasulo 算法的工作原理及其在处理器指令执行中的性能优化作用。

通过实际的实验操作和数据分析,观察 Tomasulo 算法在解决指令相关和资源冲突方面的表现,为进一步优化处理器性能提供理论依据和实践经验。

二、实验环境本次实验在模拟的处理器环境中进行,使用了专门设计的软件工具来模拟 Tomasulo 算法的运行。

该工具提供了详细的指令集、寄存器、功能单元和存储结构等模型,能够准确地反映 Tomasulo 算法在实际处理器中的执行情况。

三、实验原理Tomasulo 算法是一种用于动态调度指令的算法,旨在解决指令执行过程中的数据相关和资源冲突问题。

其核心思想是通过寄存器重命名和保留站的使用,实现指令的乱序执行,从而提高处理器的性能。

在 Tomasulo 算法中,寄存器被重命名为逻辑寄存器,指令在执行前会先将操作数从寄存器中读取到保留站中。

保留站不仅存储操作数,还负责监控功能单元的可用性,并在功能单元空闲时将指令发送执行。

同时,通过公共数据总线(CDB)来广播结果,使等待该结果的指令能够及时获取并继续执行。

四、实验步骤1、初始化处理器模型:设置寄存器、保留站、功能单元和存储的初始状态。

2、加载指令序列:将待执行的指令序列加载到指令队列中。

3、指令发射:按照顺序从指令队列中取出指令,检查操作数是否准备好,如果准备好则将指令发送到相应的保留站。

4、执行指令:当保留站中的指令所需要的功能单元空闲且操作数准备好时,指令开始执行。

5、结果广播:指令执行完成后,通过 CDB 将结果广播到所有等待该结果的保留站和寄存器。

6、指令完成:当指令的结果写回寄存器后,指令完成。

五、实验结果及分析1、性能提升通过实验观察,Tomasulo 算法在指令级并行性方面表现出色。

与传统的顺序执行方式相比,乱序执行能够有效地减少指令的等待时间,提高处理器的吞吐量。

《软件体系结构》实验指导书解读

前言软件体系结构课程是计算机科学与技术本科专业的一门重要的专业课.通过本课程的学习,使学生在已有的计算机软硬件基础知识、程序设计知识、数据库和网络通信知识的基础上系统掌握面向对象系统分析与设计的基本方法和技术,并具有针对特定环境下的应用问题进行信息系统开发(包括系统分析,设计与实现)的能力。

通过学习本课程学生可以理解和掌握软件体系结构的分析和设计方法,掌握面向对象系统分析和设计的建模标准UML语言,能够利用Rational Rose(或Microsoft Viso)软件以某一信息系统为例进行系统分析和设计。

本课程主要介绍系统原理的基本概念、系统开发过程RUP、对面向对象分析和面向对象设计的方法、对面向对象分析和设计的建模标准UML等内容。

通过本课程的学习,学生掌握的知识、内容及掌握的程度要求为:1. 使学生理解面向对象的信息系统的开发过程、系统分析和设计的原则和方法;2. 使学生掌握UML语言的基础知识,以及UML在面向对象的软件系统分析和设计中的应用,并能使用UML工具建立系统模型;3. 使学生掌握在UML系统模型下应用高级语言建立应用系统的方法;4. 通过案例教学和实验,提高学生在应用面向对象技术开发软件方面的动手能力和解决问题的能力,并鼓励创新。

本实验所要求的建模工具为Rational Rose 2003。

目录实验一用例图及进度安排 (3)实验二活动图 (8)实验三状态图 (16)实验四类 (23)实验五类的关系 (29)实验六交互图 (33)实验七对象图和包 (42)实验八组件图和配置图 (44)实验九正向工程 (51)实验一用例图及进度安排一、实验目的1.熟悉用例图的基本功能和使用方法。

2.掌握如何使用建模工具绘制用例图方法。

3.学习使用Microsoft Project对题目进行进度安排。

二、实验器材1.计算机一台。

2.Rational Rose 工具软件。

三、实验内容根据实例,如“图书馆管理系统”开发进度,在完成对系统的需求建模,得到用例模型后,应针对每个用例进行业务分析,说明其具体的业务流程,现系统分析部指派您完成该项任务。

计算机操作系统第四版汤小丹课后答案完整版之欧阳物创编

第一章时间:2021.02.07 命题人:欧阳物1.设计现代OS的主要目标是什么?答:(1)有效性(2)便利性(3)可扩充性(4)开放性2. OS的作用可表示在哪几个方面?答:( 1)OS 作为用户与计算机硬件系统之间的接口(2))OS作为计算机系统资源的管理者(3))OS实现了对计算机资源的笼统3.为什么说OS实现了对计算机资源的笼统?答:OS首先在裸机上笼盖一层I/O设备管理软件,实现了对计算机硬件操纵的第一条理抽象;在第一层软件上再笼盖文件管理软件,实现了对硬件资源操纵的第二条理笼统。

OS 通过在计算机硬件上装置多层系统软件,增强了系统功能,隐藏了对硬件操纵的细节,由它们共同实现了对计算机资源的笼统。

4.试说明推动多道批处理系统形成和成长的主要动力是什么?答:主要动力来源于四个方面的社会需求与技术成长:(1)不竭提高计算机资源的利用率;(2)便利用户;(3)器件的不竭更新换代;(4)计算机体系结构的不竭成长。

5.何谓脱机I/O和联机I/O?答:脱机I/O是指事先将装有用户法度和数据的纸带或卡片装入纸带输入机或卡片机,在外围机的控制下,把纸带或卡片上的数据或法度输入到磁带上。

该方法下的输入输出由外围机控制完成,是在脱离主机的情况下进行的。

而联机 I/O方法是指法度和数据的输入输出都是在主机的直接控制下进行的。

6.试说明推动分时系统形成和成长的主要动力是什么?答:推动分时系统形成和成长的主要动力是更好地满足用户的需要。

主要表示在:CPU的分时使用缩短了作业的平均周转时间;人机交互能力使用户能直接控制自己的作业;主机的共享使多用户能同时使用同一台计算机,自力地处理自己的作业。

7.实现分时系统的关键问题是什么?应如何解决?答:关键问题是当用户在自己的终端上键入命令时,系统应能及时接收并及时处理该命令,在用户能接受的时延内将结果前往给用户。

解决办法:针对及时接收问题,可以在系统中设置多路卡,使主机能同时接收用户从各个终端上输入的数据;为每个终端配置缓冲区,暂存用户键入的命令或数据。

2022年湖南科技职业学院计算机应用技术专业《计算机系统结构》科目期末试卷B(有答案)

2022年湖南科技职业学院计算机应用技术专业《计算机系统结构》科目期末试卷B(有答案)一、选择题1、开发并行的途径有(),资源重复和资源共享。

A.多计算机系统B.多道分时C.分布式处理系统D.时间重叠2、除了分布处理、MPP和机群系统外,并行处理计算机按其基本结构特征可分为流水线计算机,阵列处理机,多处理机和()四种不同的结构。

A.计算机网络B.控制流计算机C.机群系统D.数据流计算机3、在操作系统机器级,一般用()程序()作业控制语句。

A.汇编程序,翻译B.汇编程序,解释C.机器语言,解释D.机器语言,翻译4、非线性流水线是指( )A.一次运算中使用流水线中的多个功能段B.一次运算中要多次使用流水线中的某些功能段C.流水线中某些功能段在各次运算中的作用不同D.流水线的各个功能段在各种运算中有不同的组合5、在计算机系统设计中,比较好的方法是( )A.从上向下设计B.从下向上设计C.从两头向中间设计D.从中间开始向上、向下设计6、对系统程序员不透明的应当是()A.CACHE 存储器B.系列机各档不同的数据通路宽度C.指令缓冲寄存器D.虚拟存储器7、计算机系统的层次结构按照由高到低的顺序分别为()。

A.高级语言机器级,汇编语言机器级,传统机器语言机器级,微程序机器级B.高级语言机器级,应用语言机器级,汇编语言机器级,微程序机器级C.应用语言机器级,传统机器语言机器级,汇编语言机器级,操作系统机器级D.应用语言机器级,操作系统机器级,微程序机器级,传统机器语言机器级8、在流水机器中,全局性相关是指( )。

A.先写后读相关B.先读后写相关C.指令相关D.由转移指令引起的相关9、高级语言程序经()的()成汇编语言程序。

A.编译程序,翻译B.汇编程序,翻译C.汇编程序,解释D.编译程序,解释10、设16个处理器编号分别为0,1,2,...,15用Cube,互联函数时,第10号处理机与第()号处理机相联。

A.11B.8C.14D.2二、判断题11、单功能流水线只能完成一种固定功能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Tomasulo方法实验姓名:王宇航学号:09283020

Tomasulo方法实验

一、实验目的:

通过本实验,理解指令流水化过程中乱序执行和寄存器重命名方法。

二、实验内容:

1、用dlxView模拟器或Tomasulo算法模拟器执行浮点指令程序段。

2、指出指令乱序执行和寄存器重命名过程。

三、实验环境

操作系统:Windows 7 旗舰版

处理器:Intel(R) Core(TM) i3 双核

内存:2.00GB

软件:Tomasulo算法模拟器

四、实验过程:

1、设置Tomasulo算法模拟器参数

其中Load部件的执行时间不能

设置为1,至少为2,故不作修改;

加/减法部件的执行时间为4个时钟

周期,乘法部件的执行时间为7个

时钟周期,除法部件的执行时间为

15个时钟周期。

2、分析Tomasulo算法模拟器中指令乱序执行过程

Tomasulo算法模拟器中默认设置的指令下图所示:

执行该指令序列,重点观察指令状态的写结果一栏,便会发现执行过程中存在乱序执行现象,共有两处乱序执行,分别如下列图所示:

图中显示,在第10周期时,位于MULT.D指令之后的SUB.D指令经过4个周期已经执行完成并已经将结果写回寄存器,而MULT.D指令仍在执行中。

在第13周期时,MULT.D指令经过7个周期执行完毕,才将结果写回。

此外,还可以看到,位于DIV.D指令之后的ADD.D指令在第11周期时就已经开始执行,而DIV.D指令直至现在都未开始执行。

在第15周期时,ADD.D指令经过4个周期执行完毕,先于DIV.D指令写回结果;而DIV.D 指令仍在执行中。

在第29周期时,DIV.D指令经过15个周期终于执行完毕,将结果写回寄存器。

以上分析证明,在Tomasulo算法中存在乱序执行并且不会影响执行结果的正确性。

这是因为,Tomasulo算法采用分布的保留站,冲突检测和指令执行控制是分布的。

3、分析Tomasulo算法模拟器中寄存器重命名过程

在Tomasulo算法中通过寄存器重命名来消除WAR冲突,这一过程是通过保留站来完成的。

当指令流出到保留站时,若其操作数已经就绪,则将该指令中相应的寄存器号换为该数据本身;若其操作数还未计算出来,则将该指令中相应的寄存器号重命名为将产生这个操作数的保留站的标识,从而使得该指令与此寄存器不再有关系,后面指令对此寄存器的写入操作也不可能对该指令造成WAR冲突了。

(1)将指令中相应的寄存器号换为数据本身

执行Tomasulo算法模拟器中默认设置的指令序列,容易看出最后一条指令ADD.D和前一条指令DIV.D之间存在一个WAR冲突,即DIV.D指令要读寄存器F8中的值,ADD.D要写寄存器F8中的值,由于乱序执行,ADD.D指令会先于DIV.D指令完成;但是执行结果却不会发生错误,是因为Tomasulo算法通过寄存器重命名将这一冲突消除了。

可以看到在第5周期时,DIV.D指令流出到保留站中,此时F8中的值已经由前面的L.D 指令得出,为M1,但是模拟器并没有将相应的寄存器号R[F8]写入Vk字段中,而是将其换为了F8中数据本身M1,从而使得该指令与寄存器F8不再有关联,无论后面指令怎样改写F8也都不会影响该指令的正确执行了。

此外,由于前面的MULT.D指令还未得出F2的值,故DIV.D指令将寄存器F2重命名为MULT.D指令的保留站标识Mult1,写入Qj字段中。

如下图所示:

在这个周期中,ADD.D指令已经执行完毕,并且已经将寄存器F8中的值由M1改写成了M5,但此时DIV.D指令仍在正确执行着,并没有发生任何错误,并且经过15个执行周期可以正确完成执行过程,第15周期如下图所示:

由此说明了将指令中相应的寄存器号换为数据本身这一寄存器重命名的方法成功地消除了WAR冲突。

(2)将指令中相应的寄存器号重命名为将产生该操作数的保留站的标识

对Tomasulo算法模拟器中默认设置的指令进行重排,将第一条L.D指令后移两个位置,重排后的指令如下图所示:

可以看到,在该指令序列中,最后一条指令ADD.D和前一条指令DIV.D之间仍然存在一个WAR冲突。

执行该指令序列,观察执行过程。

可以发现在第5周期时,DIV.D指令流出到保留站中,而此时前面的L.D指令还未得出F8的值,但是模拟器并没有将相应的寄存器号R[F8]写入Vk字段中,而是将其换为了L.D指令的保留站标识Load2写入了Qk中,从而使得该指令与寄存器F8不再有关联,无论后面指令怎样改写F8也都不会影响该指令的正确执行了,如下图所示:

对寄存器F2的处理和前一种情况的相同。

在第6周期时,保留站Load2完成计算,得出F8的值M2,就会通过CBD将F8的值直接传送到DIV.D指令的保留站Mult2的Vk字段中,如下图所示:

在第12周期时,MULT.D指令得出F2的值后也会通过CDB将其直接送到DIV.D指令的保留站中,DIV.D指令便可以开始执行了。

(3)分析WAW冲突的消除方法

寄存器重命名方法不仅可以消除WAR冲突,还可以配合使用对目标寄存器的预约方法消除WAW冲突。

这一方法的思想是,在一条指令流出到保留站时,将结果寄存器的Qi字段设置为该指令的保留站标识,表示结果寄存器将要接收该指令的结果,这样其实相当于提前完成了写操作。

由于指令是按程序顺序流出的,当出现多条指令写同一个结果寄存器时,最后留下的预约结果必定是最后一条指令的,因此能够消除WAW冲突。

为了演示消除WAW冲突的过程,改写上述指令的最后一条指令,将目标寄存器由F8改为F12,如下图所示:

在该指令序列中,DIV.D指令和最后的ADD.D指令之间存在WAW冲突,即DIV.D指令要写寄存器F12,ADD.D指令也要写寄存器F12,由于乱序执行,ADD.D指令会先于DIV.D指令完成,写结果至寄存器F12。

若没有任何防范措施,当DIV.D指令完成后又会写其执行结果至寄存器F12,修改刚才的ADD.D指令的执行结果,导致结果错误。

但Tomasulo算法通过寄存器重命名和对目标寄存器的预约方法将这一冲突消除了。

执行修改后的指令序列,观察执行过程。

可以看到,在第5周期时,DIV.D指令流出到保留站中,同时将寄存器F12的Qi字段中设为DIV.D指令保留站的标识Mult2,完成预约工作。

如下图所示:

在第6周期时,ADD.D指令流出到保留站中,同时将寄存器F12的Qi字段中改写为该指令保留站的标识Add2,这样就表示寄存器F12最后接收的是ADD.D指令的执行结果,即使DIV.D指令在ADD.D指令之后执行完,也无法再改写寄存器F12了,从而保证了F12中结果的正确性。

如下图所示:

为了验证这一方法的有效性,可以看一下第16周期和第28周期。

在第16周期,ADD.D 指令先于DIV.D指令完成执行过程,将结果写入寄存器F12中,值为M5;在第29周期,DIV.D 指令也完成执行过程,但是再也无法写寄存器F12了,F12中的值仍然为ADD.D指令的执行结果M5,如下图所示:

第16周期

第28周期

由此说明寄存器重命名和对目标寄存器的预约方法成功地消除了WAW冲突。

五、实验总结:

本次实验主要是借助Tomasulo算法模拟器理解指令流水化过程中乱序执行和寄存器重命名方法。

通过在Tomasulo算法模拟器执行存在WAR冲突或者WAW冲突的浮点指令程序段,分析其中的乱序执行现象和寄存器重命名过程,我理解了Tomasulo算法消除WAR冲突和WAW冲突的方法,理解并掌握了寄存器重命名的原理及过程。