免费的74HC573中文资料

74HC573

型号:74HC573D

尺寸:12mm(长)*8mm(宽)

12mm(长)*11mm(宽)

8D数据锁存器和373一样

注:74HC573参数

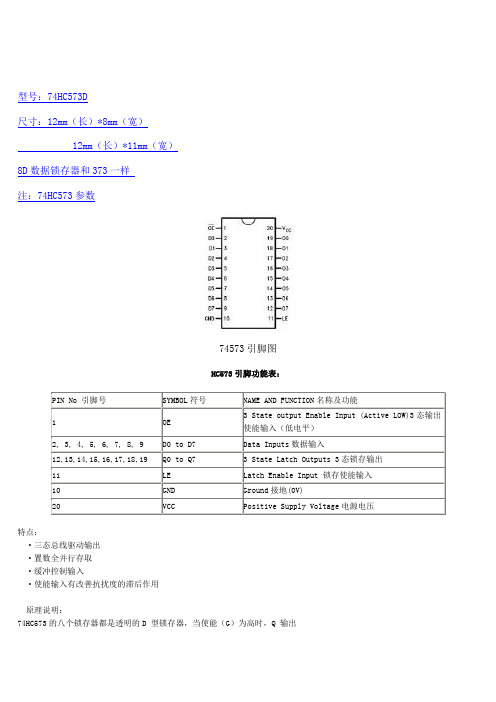

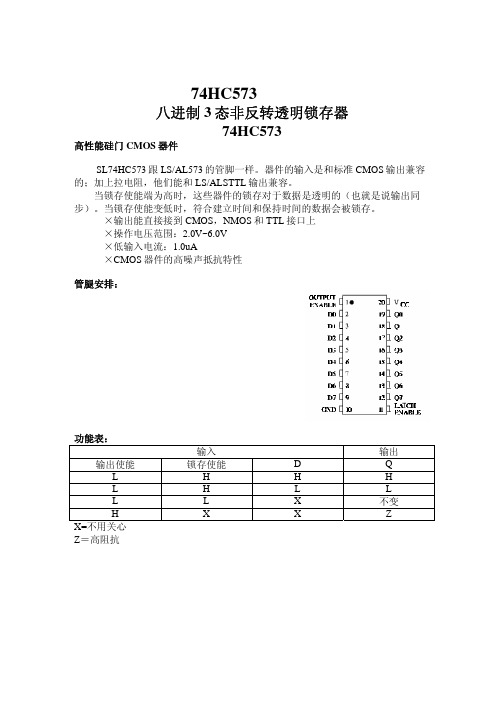

74573引脚图

HC573引脚功能表:

特点:

·三态总线驱动输出

·置数全并行存取

·缓冲控制输入

·使能输入有改善抗扰度的滞后作用

原理说明:

74HC573的八个锁存器都是透明的D 型锁存器,当使能(G)为高时,Q 输出

将随数据(D)输入而变。

当使能为低时,输出将锁存在已建立的数据电平上。

输出控制不影响锁存器的内部工作,即老数据可以保持,甚至当输出被关闭时,

新的数据也可以置入。

这种电路可以驱动大电容或低阻抗负载,可以直接与系统总线接口并驱动总线,而不需要外接口。

特别适用于缓冲寄存器,I/O 通道,双向总线驱动器和工作寄存器。

真值表:

ABSOLUTE MAXIMUM RATINGS绝对最大额定值:

RECOMMENDED OPERATING CONDITIONS建议操作条件:

DC SPECIFICATIONS直流电气规格:

应用电路图:点击图片查看大图。

74HC573中文资料

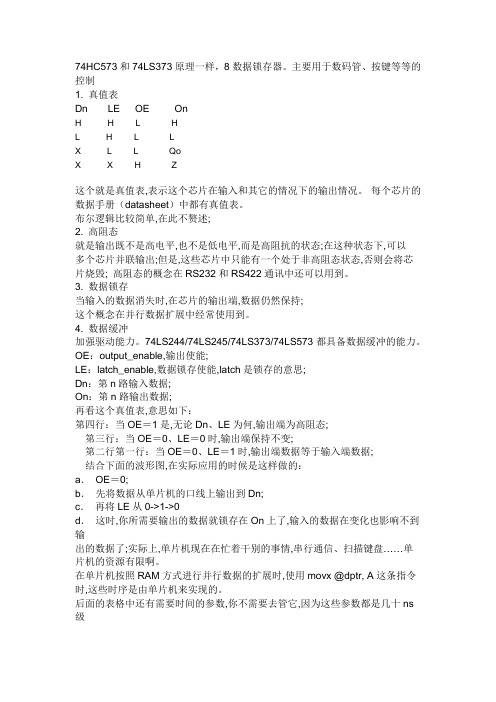

74HC573和74LS373原理一样,8数据锁存器。

主要用于数码管、按键等等的控制1. 真值表Dn LE OE OnH H L HL H L LX L L QoX X H Z这个就是真值表,表示这个芯片在输入和其它的情况下的输出情况。

每个芯片的数据手册(datasheet)中都有真值表。

布尔逻辑比较简单,在此不赘述;2. 高阻态就是输出既不是高电平,也不是低电平,而是高阻抗的状态;在这种状态下,可以多个芯片并联输出;但是,这些芯片中只能有一个处于非高阻态状态,否则会将芯片烧毁; 高阻态的概念在RS232和RS422通讯中还可以用到。

3. 数据锁存当输入的数据消失时,在芯片的输出端,数据仍然保持;这个概念在并行数据扩展中经常使用到。

4. 数据缓冲加强驱动能力。

74LS244/74LS245/74LS373/74LS573都具备数据缓冲的能力。

OE:output_enable,输出使能;LE:latch_enable,数据锁存使能,latch是锁存的意思;Dn:第n路输入数据;On:第n路输出数据;再看这个真值表,意思如下:第四行:当OE=1是,无论Dn、LE为何,输出端为高阻态;第三行:当OE=0、LE=0时,输出端保持不变;第二行第一行:当OE=0、LE=1时,输出端数据等于输入端数据;结合下面的波形图,在实际应用的时候是这样做的:a.OE=0;b.先将数据从单片机的口线上输出到Dn;c.再将LE从0->1->0d.这时,你所需要输出的数据就锁存在On上了,输入的数据在变化也影响不到输出的数据了;实际上,单片机现在在忙着干别的事情,串行通信、扫描键盘……单片机的资源有限啊。

在单片机按照RAM方式进行并行数据的扩展时,使用movx @dptr, A这条指令时,这些时序是由单片机来实现的。

后面的表格中还有需要时间的参数,你不需要去管它,因为这些参数都是几十ns级别的,对于单片机在12M下的每个指令周期最小是1us的情况下,完全可以实现;如果是你自己来实现这个逻辑,类似的指令如下:mov P0,A ;将数据输出到并行数据端口clr LEsetb LEclr LE ;上面三条指令完成LE的波形从0->1->0的变化74ls573跟74LS373逻辑上完全一样,只不过是管脚定义不一样,数据输入和输出端。

74HC573数据手册

© NXP B.V. 2012. All rights reserved.

2 of 21

NXP Semiconductors

74HC573; 74HCT573

Octal D-type transparent latch; 3-state

D0

D1

D2

D3

Q0 19 Q1 18 Q2 17 3-STATE Q3 16 OUTPUTS Q4 15 Q5 14 Q6 13 Q7 12

mna809

74HC_HCT573

Product data sheet

All information provided in this document is subject to legal disclaimers.

3 of 21

NXP Semiconductors

74HC573; 74HCT573

Octal D-type transparent latch; 3-state

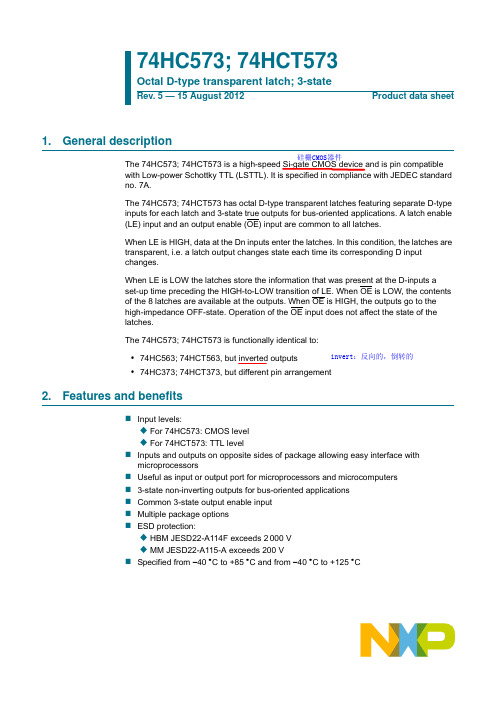

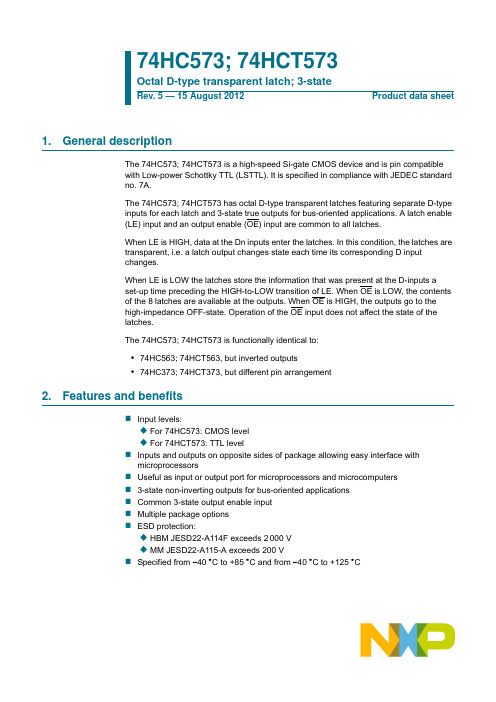

5. Pinning information

5.1 Pinning

OE 1 D0 2 D1 3 D2 4 D3 5 D4 6 D5 7 D6 8 D7 9 GND 10

(1) The die substrate is attached to this pad using conductive die attach material. It can not be used as supply pin or input

Fig 6. Pin configuration DHVQFN20

Useful as input or output port for microprocessors and microcomputers 3-state non-inverting outputs for bus-oriented applications Common 3-state output enable input Multiple package options ESD protection:

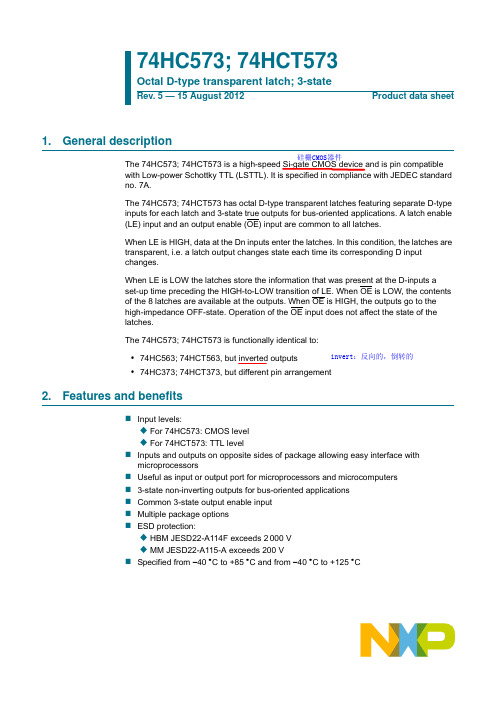

74HC573数据手册

2. Features and benefits

Input levels: For 74HC573: CMOS level For 74HCT573: TTL level

Inputs and outputs on opposite sides of package allowing easy interface with microprocessors

data input

10

ground (0 V)

11

latch enable input (active HIGH)

19, 18, 17, 16, 15, 14, 13, 12 3-state latch output

20

supply voltage

74HC_HCT573

Product data sheet

Q0 19 Q1 18 Q2 17 3-STATE Q3 16 OUTPUTS Q4 15 Q5 14 Q6 13 Q7 12

mna809

74HC_HCT573

Product data sheet

All information provided in this document is subject to legal disclaimers.

5.2 Pin description

Table 2. Symbol OE D[0:7] GND LE Q[0:7] VCC

Pin description

Pin

Description

1

3-state output enable input (active LOW)

2, 3, 4, 5, 6, 7, 8, 9

HBM JESD22-A114F exceeds 2 000 V MM JESD22-A115-A exceeds 200 V Specified from 40 C to +85 C and from 40 C to +125 C

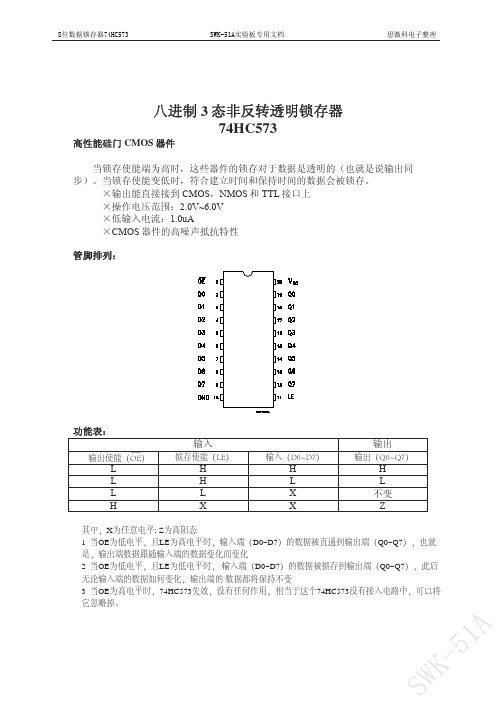

74hc573完整中文资料

74hc573中文资料参数-74hc573引脚图-功能原理-74hC573的作用-应用电路-74hC563-54hC57高性能硅门CMOS器件SL74HC573跟LS/AL573的管脚一样。

器件的输入是和标准CMOS输出兼容的;加上拉电阻,他们能和LS/ALSTTL输出兼容。

当锁存使能端为高时,这些器件的锁存对于数据是透明的(也就是说输出同步)。

当锁存使能变低时,符合建立时间和保持时间的数据会被锁存。

×输出能直接接到CMOS,NMOS和TTL接口上×操作电压范围:~×低输入电流:×CMOS器件的高噪声抵抗特性·三态总线驱动输出·置数全并行存取·缓冲控制输入·使能输入有改善抗扰度的滞后作用原理说明:M54HC563/74HC563/M54HC573/74HC573的八个锁存器都是透明的D 型锁存器,当使能(G)为高时,Q 输出将随数据(D)输入而变。

当使能为低时,输出将锁存在已建立的数据电平上。

输出控制不影响锁存器的内部工作,即老数据可以保持,甚至当输出被关闭时,新的数据也可以置入。

这种电路可以驱动大电容或低阻抗负载,可以直接与系统总线接口并驱动总线,而不需要外接口。

特别适用于缓冲寄存器,I/O 通道,双向总线驱动器和工作寄存器。

HC563引脚功能表:HC573引脚功能表:图1 HC573引脚图图2 HC573 国际电工委员会逻辑符号图3 HC563引脚图图4 HC563 国际电工委员会逻辑符号图5 HC563 逻辑图图6 HC573 逻辑图图7 输入输出等效电路真值表:ABSOLUTE MAXIMUM RATINGS绝对最大额定值:Top Operating Temperature: M54HC Series M74HC Series 操作温度:M54HC 系列M74HC系列-55 to +125 -40 to +85℃tr,tf Input Rise and Fall Time输入上升和下降时间VCC = 2V0 to 1000ns VCC =0 to 500VCC = 6V0 to 400VOHHigh Level Output Voltage输出高电平电压 VI = VIH or VILIO=-20μ 4.54.44 Level Output Voltage输出低电平电压VI = VIH or VILIO=20 μLeakage Current输入漏电流=VCC or GND--±±1±1μAIOZState Output Off State Current关断状态3态输出电流=VIH or VIL VO =VCC or GND--±±±10μAICCQuiescent Supply Current静态电源电流=VCC or GND--4-40-80μA应用电路图:点击图片查看大图图8。

74HC573及上拉电阻

TTL电路的输入端是遵循TTL标准的,其需要的输入电流很小,74HC573的输入电流在电源电压为6V,输入电压为6V的情况下,其所需要的驱动电流仅仅为0.1uA。

你给的图是说明74HC573的输出驱动能力,573的每个输出引脚都有20mA的灌入电流,因此可以直接驱动LED,而扇出电流可以达到35mA.芯片有一个极限功耗,根据封装不同其功耗也不同,所以在设计驱动的时候,在任一时间要保证芯片的功耗不要超过此参数。

比如:573的每个引脚可能灌入20mA的电流,8个引脚,总电流是160mA,乘以工作电压5V,其值为800mW,这样就超出了芯片的极限,芯片容易损坏或者寿命缩短。

另外上拉电阻的问题。

是否需要上拉电阻,对于TTL电路输入端来说并不是关键,加与不加是要看你的单片机IO口的属性。

如果单片机的输出端口是推挽输出的,那么这个上拉电阻根本没有必要,但如果单片机的IO口是开漏输出或者是内部弱上拉输出的,那这个时候就需要接一个上拉电阻。

上拉电阻的大小一般参照后级电路所需要驱动电流的5~10倍来选取,可大不可小,一般现在用10K或者4K7的比较多,但如果对功耗要求比较严格,这个电阻就需要去计算,阻值太大那么容易受干扰,太小功耗不能满足,这需要去权衡.经过试验证明:以前在开发板上(比如天祥的板子)就是利用74HC573来驱动数码管的,该板是这样的,通过位选来导通哪个数码管并通过段选来使被选中的那个数码管显示什么数字。

这里面具体接法是:数码管是共阴极的,它的公共端(如数码管的3、8脚)接到位选的74HC573的输出端Q0,Q1,Q2,Q3,Q4,Q5,Q6,Q7,其中的一个如Q0(当然这里说的是一个数码管的接法,多个就接Q1,Q2,Q3,Q4一直可以接到Q7,共可以接8个数码管)对应573的管脚号是19,18,17,16,15,14,13,12。

数码管的a,b,c,d,e,f,g,h段分别接到另外一个74HC573的输出Q0,Q1,Q2,Q3,Q4,Q5,Q6,Q7,对应573的管脚号是19,18,17,16,15,14,13,12。

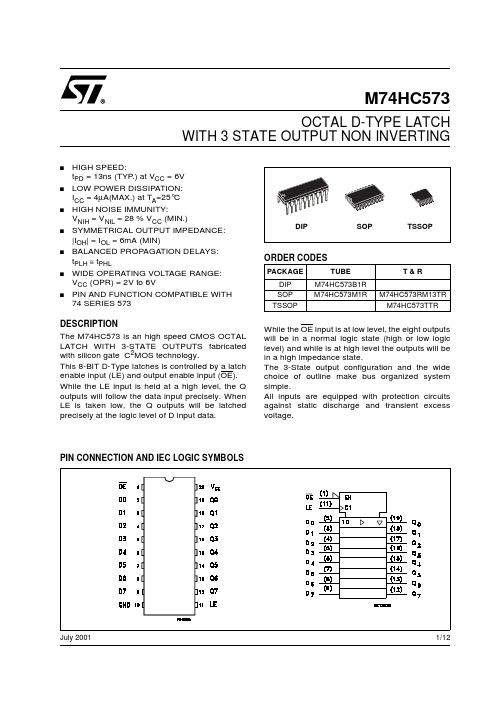

M74HC573M1R中文资料

1/12July 2001sHIGH SPEED:t PD = 13ns (TYP .) at V CC = 6V sLOW POWER DISSIPATION:I CC = 4µA(MAX.) at T A =25°C sHIGH NOISE IMMUNITY:V NIH = V NIL = 28 % V CC (MIN.)sSYMMETRICAL OUTPUT IMPEDANCE:|I OH | = I OL = 6mA (MIN)sBALANCED PROPAGATION DELAYS:t PLH ≅ t PHLsWIDE OPERATING VOLTAGE RANGE:V CC (OPR) = 2V to 6VsPIN AND FUNCTION COMPATIBLE WITH 74 SERIES 573DESCRIPTIONThe M74HC573 is an high speed CMOS OCTAL LATCH WITH 3-STATE OUTPUTS fabricated with silicon gate C 2MOS technology.This 8-BIT D-Type latches is controlled by a latch enable input (LE) and output enable input (OE).While the LE input is held at a high level, the Q outputs will follow the data input precisely. When LE is taken low, the Q outputs will be latched precisely at the logic level of D input data.While the OE input is at low level, the eight outputs will be in a normal logic state (high or low logic level) and while is at high level the outputs will be in a high impedance state.The 3-State output configuration and the wide choice of outline make bus organized system simple.All inputs are equipped with protection circuits against static discharge and transient excess voltage.M74HC573OCTAL D-TYPE LATCHWITH 3 STATE OUTPUT NON INVERTINGPIN CONNECTION AND IEC LOGIC SYMBOLSORDER CODESPACKAGE TUBE T & RDIP M74HC573B1R SOP M74HC573M1RM74HC573RM13TR TSSOPM74HC573TTRM74HC5732/12INPUT AND OUTPUT EQUIVALENT CIRCUITPIN DESCRIPTIONTRUTH TABLEX: Don’t CareZ: High Impedance(*): Q Outputs are latched at the time when the LE input is taken low logic level.LOGIC DIAGRAMPIN No SYMBOL NAME AND FUNCTION 1OE 3 State Output Enable Input (Active LOW)2, 3, 4, 5, 6, 7, 8, 9D0 to D7Data Inputs12, 13, 14, 15, 16, 17, 18, 19Q0 to Q73 State Latch Outputs11LE Latch Enable Input 10GND Ground (0V)20V CCPositive Supply VoltageINPUTSOUTPUTSOE LE D QH X X ZL L X NO CHANGE (*)L H L L LHHHM74HC5733/12ABSOLUTE MAXIMUM RATINGSAbsolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied(*) 500mW at 65 °C; derate to 300mW by 10mW/°C from 65°C to 85°CRECOMMENDED OPERATING CONDITIONSSymbol ParameterValue Unit V CC Supply Voltage -0.5 to +7V V I DC Input Voltage -0.5 to V CC + 0.5V V O DC Output Voltage -0.5 to V CC + 0.5V I IK DC Input Diode Current ± 20mA I OK DC Output Diode Current ± 20mA I O DC Output Current ± 35mA I CC or I GND DC V CC or Ground Current± 70mA P D Power Dissipation 500(*)mW T stg Storage Temperature -65 to +150°C T LLead Temperature (10 sec)300°CSymbol ParameterValue Unit V CC Supply Voltage 2 to 6V V I Input Voltage 0 to V CC V V O Output Voltage 0 to V CC V T op Operating Temperature -55 to 125°C t r , t fInput Rise and Fall TimeV CC = 2.0V 0 to 1000ns V CC = 4.5V 0 to 500ns V CC = 6.0V0 to 400nsM74HC5734/12DC SPECIFICATIONSSymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.V IHHigh Level Input Voltage2.0 1.5 1.5 1.5V 4.53.15 3.15 3.156.04.24.24.2V ILLow Level Input Voltage2.00.50.50.5V4.5 1.35 1.35 1.356.0 1.81.81.8V OHHigh Level Output Voltage2.0I O =-20 µA 1.9 2.0 1.9 1.9V4.5I O =-20 µA 4.4 4.5 4.4 4.46.0I O =-20 µA5.96.0 5.9 5.94.5I O =-6.0 mA 4.18 4.31 4.13 4.106.0I O =-7.8 mA 5.685.8 5.635.60V OLLow Level Output Voltage2.0I O =20 µA 0.00.10.10.1V 4.5I O =20 µA 0.00.10.10.16.0I O =20 µA 0.00.10.10.14.5I O =6.0 mA 0.170.260.330.406.0I O =7.8 mA 0.180.260.330.40I I Input Leakage Current6.0V I = V CC or GND ± 0.1± 1± 1µA I OZHigh Impedance Output Leakage Current6.0V I = V IH or V IL V O = V CC or GND ± 0.5± 5± 10µA I CCQuiescent Supply Current6.0V I = V CC or GND44080µAM74HC5735/12AC ELECTRICAL CHARACTERISTICS (C L = 50 pF, Input t r = t f = 6ns)SymbolParameterTest ConditionValue UnitV CC (V)C L (pF)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.t TLH t THL Output TransitionTime 2.05025607590ns 4.571215186.06101315t PLH t PHL Propagation DelayTime(LE - Q)2.05050115145175ns4.5152329356.0132025302.015060155195235ns4.5203139476.017263340t PLH t PHL Propagation DelayTime(D - Q)2.05042110140165ns4.5142228336.0121924282.015057150190225ns4.5193038456.016263238t PZL t PZH High ImpedanceOutput Enable Time2.050R L = 1 K Ω55140175210ns4.5172835426.0142430362.0150R L = 1 K Ω66180225270ns4.5223645546.019313846t PLZ t PHZ High ImpedanceOutput Disable Time 2.050R L = 1 K Ω40125155190ns4.5172531386.015212632t W(L) t W(H)Minimum Pulse Width2.050407595110ns4.581519226.07131619t sMinimum Set-up Time2.05016506575ns4.551013156.0391113t hMinimum Hold Time2.050555ns4.55556.0555M74HC5736/12CAPACITIVE CHARACTERISTICS1) C PD is defined as the value of the IC’s internal equivalent capacitance which is calculated from the operating current consumption without load. (Refer to Test Circuit). Average operating current can be obtained by the following equation. I CC(opr) = C PD x V CC x f IN + I CC /8 (per Flip Flop) and the C PD when n pcs of Flip Flop operate, can be gained by the following equation: C PD(TOTAL) = 33 + 18 x n (pF)TEST CIRCUITC L = 50pF/150pF or equivalent (includes jig and probe capacitance)R 1 = 1K Ω or equivalentR T = Z OUT of pulse generator (typically 50Ω)SymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.C IN Input Capacitance 5101010pF C OUT OutputCapacitance10pF C PDPower Dissipation Capacitance (note 1)51pF TESTSWITCH t PLH , t PHL Open t PZL , t PLZ V CC t PZH , t PHZGNDM74HC5737/12WAVEFORM 1: LE TO Qn PROPAGATION DELAYS, LE MINIMUM PULSE WIDTH, Dn TO LE SETUP AND HOLD TIMES (f=1MHz; 50% duty cycle)WAVEFORM 2: OUTPUT ENABLE AND DISABLE TIMES(f=1MHz; 50% duty cycle)M74HC5738/12WAVEFORM 3: PROPAGATION DELAY TIMES(f=1MHz; 50% duty cycle)M74HC573Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.© The ST logo is a registered trademark of STMicroelectronics© 2000 STMicroelectronics - Printed in Italy - All Rights ReservedSTMicroelectronics GROUP OF COMPANIESAustralia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - MoroccoSingapore - Spain - Sweden - Switzerland - United Kingdom© 12/12。

锁存器74hc573的使用

74HC573锁存器用法

发表于3年前(2011-02-24 14:13) 阅读(3787) | 评论(0)1人收藏此

文章, 我要收藏

赞0

74HC573锁存器

锁存器介绍

如果单片机的总线接口只作一种用途,不需要接锁存器;如果单片机的总线接口要作两种用途,就要用两个锁存器。

例如:一个口要控制两个LED,对第一个LED 送数据时,“打开”第一个锁存器而“锁住”第二个锁存器,使第二个LED 上的数据不变。

对第二个LED 送数据时,“打开”第二个锁存器而“锁住”第一个锁存器,使第一个LED 上的数据不变。

如果单片机的一个口要做三种用途,则可用三个锁存器,操作过程相似。

然而在实际应用中,我们并不这样做,只用一个锁存器就可以了,并用一根I/O 口线作为对锁存器的控制之用(接74373 的LE,而OE可恒接地)。

所以,就这一种用法而言,可以把锁存器视为单片机的I/O 口的扩展器。

更多信息请看/view/629932.htm?fr=ala0_1_1

74hc573 引脚图

1脚是输出使能

11脚是锁存使能

D是输入

Q是输出

H是高电平,L是低

/OE是1脚LE是11脚

/OE 接低电平,使芯片内部数据保持器输出端与芯片8位输出端之间连通。

LE 端的作用是通过高低电平控制8位输入与内部数据保持器输入端的连通与断开。

当LE = 0 时,P0端口的8位数据线与74HC573内部数据保持器的输入端断开。

当LE = 1 时,P0端口的8位数据线与74HC573内部数据保持器的输入端连通。

74hc573中文资料_数据手册_参数

PACKAGE OUTLINES See "74HC/HCT!HCU!HCMOS Logic Package Outlines".

7 December 1990

万联芯城

万联芯城 电子元器件物料全国供应,专业提 供电子元器件原装现货产品,1 片起订,价格优势明显,电子元 器件采购网万联芯城目前为长电科技,顺络电子,先科 ST 等多 家知名原厂的指定授权代理商,专为客户提供电子元器件配单业 务,提交物料清单即可当天报价当天发货,点击进入万联芯城。

1990年12月 2飞利浦半导体产品SPECI FI CATION八进制D型透明锁存器;三态 74HC / 74HC573特征 ?74hc573相反的输入和输出包装的两侧容易与微处理器接口 ?用作输入或 输出端口微处理器/微计算机 ?3态非反74HC573相输出总线应用 ?共用3态输出使能输 入 ?在功能上与“563”和“373” ?输出能力:总线驱动程序 ?74hc573我 CC 类别:MSI 一般描述 74HC / HCT573是高速的硅栅CMOS器件和引脚兼容低功耗肖特基 TTL(LSTTL).他们在中指定符合JEDEC标准NO. 7A. 74HC / HCT573是八进制D型透 明闩锁特色每个锁存器都有独立的D型输入和面向公共汽车的三态输出应用.一个锁存 使能(LE)输入和一个输出使能(OE)74HC573输入是常见的到所有的锁存器. “573”由8个D型组成透明锁存器与三态真74hc573实输74HC573出.当LE为高时,数据 在 D N 输入进入锁存器. 在这条件锁存器是透明的,即锁存输出将改变状态每次都有 相应的D输入变化.当LE为低电平时,锁存器存储信息出现在 D - 74HC573输入一个设 定时间 LE的高到低转换.当OE为低时,74hc573内容为输出端有8个锁存器.当OE为高电 平时,74HC573输出将转至高阻抗关闭状态. OE输入的操作没有影响锁存器的状态. “573”与功能相同 “563”和“373”,74hc573但“563”却有倒相输出和“373”有一 个不同的引脚排列.快速参考数据 GND = 0 V; T AMB = 25℃; T R = T F = 6NS笔记 1. C PD 用于确定动态功耗(P D ,单位为μW): P D = C PD ×V CC2 ×F I +Σ(C L ×V CC2 ×F O )其中: F I =以MHZ为单位的输入频率; F O =以MHZ为单位的输出频率 Σ(C L ×V CC2 ×F O )=输出之和 C L 74HC573=输出负载电容,单位PF; V CC = V 中的电源电压 2.对于HC,条件是V I = GND到V CC ; 对于HCT,条件是V I = GND到V CC - 1.5 V订购信息看到 “74HC / HCT / HCU / HCMOS逻辑封装信息” .74HC573符号 参数条件典型单元 H

74hc573原理

74hc573原理74HC573是一种常用的集成电路芯片,属于高速CMOS逻辑系列。

它是一种8位透明锁存器,可以实现数据的存储和传输功能。

本文将介绍74HC573的原理和应用。

我们来了解一下74HC573的基本结构。

它由8个锁存器单元组成,每个单元都具有一个数据输入端(D)、一个时钟输入端(CK)和一个数据输出端(Q)。

这些单元可以独立地将数据存储在内部存储器中,并在时钟脉冲到达时将数据传输到输出端。

除此之外,74HC573还具有一个输出使能端( OE ),通过控制该端口的高低电平,可以使输出端的数据有效或者无效。

接下来,我们来看一下74HC573的工作原理。

当时钟输入端接收到一个信号时,数据输入端的数据会被存储在内部存储器中。

存储的数据可以通过数据输出端输出。

当输出使能端为高电平时,数据输出端的数据有效;当输出使能端为低电平时,数据输出端的数据无效。

通过控制输出使能端的状态,我们可以实现数据的读取和屏蔽操作。

那么,74HC573的应用有哪些呢?它广泛应用于数字电路中,特别是在数据存储和传输方面。

例如,在微处理器系统中,我们可以使用74HC573将数据从外部设备传输到微处理器中,或者将数据从微处理器传输到外部设备中。

它还可以用于存储数据,以便在需要时进行读取。

除了数据存储和传输外,74HC573还可以用于地址译码。

通过将地址线连接到74HC573的数据输入端,我们可以根据地址信号的不同将数据传输到不同的输出端。

这在存储器和外设的选择和控制中起着重要作用。

74HC573还可以用于时序控制。

通过控制时钟输入端和输出使能端的状态,我们可以实现对数据传输的控制。

例如,可以根据特定的时序要求将数据传输到其他模块,并在需要时将其输出。

总结一下,74HC573是一种功能强大的集成电路芯片,可以实现数据的存储和传输功能。

它广泛应用于数字电路中,特别是在数据存储、传输、地址译码和时序控制等方面。

通过灵活的控制和应用,我们可以实现不同的功能需求。

74hc573完整中文资料培训讲学

74h c573完整中文资料74hc573中文资料参数-74hc573引脚图-功能原理-74hC573的作用-应用电路-74hC563-54hC57高性能硅门 CMOS器件SL74HC573跟 LS/AL573的管脚一样。

器件的输入是和标准CMOS输出兼容的;加上拉电阻,他们能和 LS/ALSTTL输出兼容。

当锁存使能端为高时,这些器件的锁存对于数据是透明的(也就是说输出同步)。

当锁存使能变低时,符合建立时间和保持时间的数据会被锁存。

×输出能直接接到CMOS,NMOS和 TTL接口上×操作电压范围:2.0V~6.0V×低输入电流:1.0uA×CMOS器件的高噪声抵抗特性·三态总线驱动输出·置数全并行存取·缓冲控制输入·使能输入有改善抗扰度的滞后作用原理说明:M54HC563/74HC563/M54HC573/74HC573的八个锁存器都是透明的D 型锁存器,当使能(G)为高时,Q 输出将随数据(D)输入而变。

当使能为低时,输出将锁存在已建立的数据电平上。

输出控制不影响锁存器的内部工作,即老数据可以保持,甚至当输出被关闭时,新的数据也可以置入。

这种电路可以驱动大电容或低阻抗负载,可以直接与系统总线接口并驱动总线,而不需要外接口。

特别适用于缓冲寄存器,I/O 通道,双向总线驱动器和工作寄存器。

HC563引脚功能表:HC573引脚功能表:1OE 3 State output Enable Input (Active LOW)3态输出使能输入(低电平)2, 3, 4, 5, 6, 7, 8, 9D0 to D7Data Inputs数据输入12,13,14,15,16,17,18,19Q0 to Q7 3 State Latch Outputs 3态锁存输出11LE Latch Enable Input 锁存使能输入10GND Ground接地(0V)20VCC Positive Supply Voltage电源电压图1 HC573引脚图图2 HC573 国际电工委员会逻辑符号图3 HC563引脚图图4 HC563 国际电工委员会逻辑符号图5 HC563 逻辑图图6 HC573 逻辑图图7 输入输出等效电路真值表:INPUTS 输入Outputs输出OE LE D Q (HC573) Q (HC563) H X X Z ZL L X NO CHANGE *NO CHANGE * L H L L HL H H H L ABSOLUTE MAXIMUM RATINGS绝对最大额定值:Symbol 符号Parameter 参数Value 数值Unit 单位VCC Supply Voltage电源电压-0.5 to +7VVI DC Input Voltage 直流输入电压-0.5 to VCC + 0.5VVO DC Output Voltage直流输出电压-0.5 to VCC + 0.5VIIK DC Input Diode Current直流输入二极管电流± 20mA IOK DC Output Diode Current直流输出二极管电流± 20mA IO DC Output Source Sink Current Per Output Pin± 35mA ICC or IGND DC VCC or Ground Current± 70mA PD Power Dissipation功耗500 (*)mW Tstg Storage Temperature贮藏温度-65 to +150℃TL Lead Temperature 焊接温度 (10 sec)300℃RECOMMENDED OPERATING CONDITIONS建议操作条件:Symbol 符号Parameter 参数Value 数值Unit单位VCC Supply Voltage电源电压 2 to 6V VI Input Voltage输入电压0 to VCC V VO Output Voltage输出电压0 to VCC VTop Operating Temperature: M54HC Series M74HC Series操作温度: M54HC系列M74HC系列-55 to +125 -40 to +85℃tr,tf Input Rise and Fall Time输入上升和下降时间VCC =2V0 to 1000ns VCC=4.5V0 to 500VCC =6V0 to 400VOHHigh Level Output Voltage输出高电平电压2.0 VI = VIH or VILIO=-20 μA1.92.0-1.9 -1.9 -V4.54.44.54.44.4---6.05.96.05.95.9-4.5IO=-6.0 mA4.184.314.134.10-6.0IO=-7.8 mA5.685.85.635.60-VOLLow Level Output Voltage输出低电平电压2.0 VI = VIH or VILIO=20 μA-0.0 0.1 -0.1-0.1V4.5-0.00.1 0.10.16.0-0.00.10.10.14.5IO= 6.0mA-0.170.260.330.406.0IO= 7.8mA-0.180.260.330.40IIInput Leakage Current输入漏电流6.0VI=VCC or GND--±0.1-±1±1μA IOZState Output Off State Current关断状态3态输出电流6.0VI =VIH or VIL VO =VCC or GND--±0.5-±5.0-±10μAICCQuiescent Supply Current静态电源电流6.0VI =VCC or GND--4-40-80μA应用电路图:点击图片查看大图图8。

74HC573锁存器

74HC573锁存器编程时,先将使能端置1,此时输出数据和输入数据一致;为了将输出的数据锁定,防止误操作,可将使能端清0,此时,输出端保持原有值,不再变化。

(1,使能置1;2,数据输入到锁存器输入端(输出=输入);3,使能置0(输出恒定=先前输入);(达到锁存功能))74HC系列的数字集成电路,当5V供电时,输出高电平接近5V,带负载后,能输出4.95V左右。

从你图上看,这里需要573输出高电平段码,138输出位码,进行动态显示。

但是图上有错,为了LED安全使用,在573的输出端与7LED连接之间,应串联300Ω电阻。

附加:锁存器的作用锁存器(Latch)是一种对脉冲电平敏感的存储单元电路,它们可以在特定输入脉冲电平作用下改变状态。

锁存,就是把信号暂存以维持某种电平状态。

锁存器的最主要作用是缓存,其次完成高速的控制其与慢速的外设的不同步问题,再其次是解决驱动的问题,最后是解决一个I/O 口既能输出也能输入的问题。

74HC37374HC37374hc373中文资料:373为三态输出的八D 透明锁存器,共有54/74S373 和54/74LS373 两种线路结构型式,其主要电器特性的典型值如下(不同厂家具体值有差别):型号tPd PD54S373/74S373 7ns 525mW54LS373/74LS373 17ns 120mW373 的输出端O0~O7 可直接与总线相连。

当三态允许控制端OE 为低电平时,O0~O7 为正常逻辑状态,可用来驱动负载或总线。

当OE 为高电平时,O0~O7 呈高阻态,即不驱动总线,也不为总线的负载,但锁存器内部的逻辑操作不受影响。

当锁存允许端LE 为高电平时,O 随数据D 而变。

当LE 为低电平时,O 被锁存在已建立的数据电平。

当LE 端施密特触发器的输入滞后作用,使交流和直流噪声抗扰度被改善400mV。

74HC573中文资料

6.0

VIN=VCC 或者 GND

6.0

高阻抗态下的输出 6.0

VIN=VIH 或者 VIL,

VOUT=VCC 或者 GND

VIN=VCC 或者 GND

6.0

IOUT=0uA

3.15 3.15 3.15 4.2 4.2 4.2 0.5 0.5 0.5 V 1.35 1.35 1.35 1.8 1.8 1.8 1.9 1.9 1.9 V 4.4 4.4 4.4 5.9 5.9 5.9

6.0

VIN=VIH 或者 VIL,

2.0

|IOUT|≤20uA

4.5

6.0Biblioteka VIN=VIH 或者 VIL,

|IOUT|≤6.0mA

4.5

|IOUT|≤7.8mA

6.0

VIN=VIH 或者 VIL,

2.0

|IOUT|≤20uA

4.5

6.0

VIN=VIH 或者 VIL,

|IOUT|≤6.0mA

4.5

|IOUT|≤7.8mA

×输出能直接接到 CMOS,NMOS 和 TTL 接口上 ×操作电压范围:2.0V~6.0V ×低输入电流:1.0uA ×CMOS 器件的高噪声抵抗特性

管腿安排:

功能表:

输入

输出使能

锁存使能

D

L

H

H

L

H

L

L

L

X

H

X

X

X=不用关心

Z=高阻抗

输出 Q H L

不变 Z

http://www.elecfans.com

符号

参数

VCC

条件限制

单

V 25℃~ ≤85 ≤125 位

74HC573最新数据手册

Fig 5.

Pin configuration DIP20, SO20, SSOP20 and TSSOP20

Fig 6.

Pin configuration DHVQFN20

5.2 Pin description

Table 2. Symbol OE D[0:7] GND LE Q[0:7] VCC Pin description Pin 1 2, 3, 4, 5, 6, 7, 8, 9 10 11 20 Description 3-state output enable input (active LOW) data input ground (0 V) latch enable input (active HIGH) supply voltage

• 74HC563; 74HCT563, but inverted outputs • 74HC373; 74HCT373, but different pin arrangement

2. Features and benefits

Input levels: For 74HC573: CMOS level For 74HCT573: TTL level Inputs and outputs on opposite sides of package allowing easy interface with microprocessors Useful as input or output port for microprocessors and microcomputers 3-state non-inverting outputs for bus-oriented applications Common 3-state output enable input Multiple package options ESD protection: HBM JESD22-A114F exceeds 2 000 V MM JESD22-A115-A exceeds 200 V Specified from 40 C to +85 C and from 40 C to +125 C

74HC573数据手册

䘏䕥˖

SWK-51A

8位数据锁存器74HC573 6:.$ᇎ傼ᶯу⭘᮷ẓ ᙍᗞ、⭥ᆀᮤ⨶

SWK-51A来自⬉ᑇ䕧 9ˈ

ܹ⬉य़ _,287_İX$

9,/ ᳔Ԣ 9287 9 㗙 9&&

9

⬉य़䕧 9ˈ

䰤ࠊᴵӊ

ć̚ˉ

ć

İ

ć

İ

ć

᳔ؐ㣗ೈ˖

ヺো

খ᭄

ؐ

ऩԡ

9&&

'& կ⬉⬉य़˄খ㗗 *1'˅

9,1

'& 䕧ܹ⬉य़˄খ㗗 *1'˅

a

9

a9&&

9

9287 ,,1 ,287 ,&& 3'

'& 䕧ߎ⬉य़˄খ㗗 *1'˅ ↣ϔϾ 3,1ⱘ '& 䕧ܹ⬉⌕ ↣ϔϾ 3,1 ⱘ'& 䕧ߎ⬉⌕ '& կ⬉⬉⌕ˈ9&& *1' П䯈 㞾✊⦃๗ϟˈ3',3 62,& ᇕ㺙ϟⱘ

ℹ˅DŽᔧ䫕ᄬՓ㛑বԢᯊˈヺড়ᓎゟᯊ䯈ֱᣕᯊ䯈ⱘ᭄Ӯ㹿䫕ᄬDŽ

h䕧ߎ㛑Ⳉࠄ &026ˈ1026 77/ ষϞ

h᪡⬉य़㣗ೈ˖9a9

hԢ䕧ܹ⬉⌕˖X$

h&026 ఼ӊⱘ催ాໄᢉᡫ⡍ᗻ

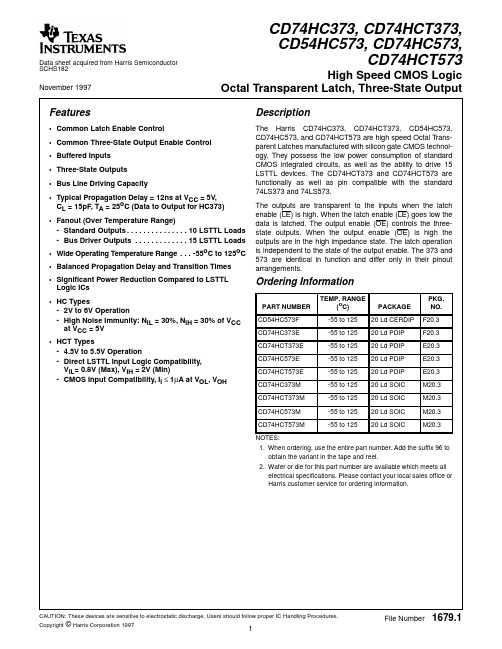

CD74HCT573中文资料

For VO < -0.5V or VO > VCC + 0.5V . . . . . . . . . . . . . . . . . . . .±20mA DC Drain Current, per Output, IO

• HC Types - 2V to 6V Operation - High Noise Immunity: NIL = 30%, NIH = 30% of VCC at VCC = 5V

• HCT Types - 4.5V to 5.5V Operation - Direct LSTTL Input Logic Compatibility, VIL= 0.8V (Max), VIH = 2V (Min) - CMOS Input Compatibility, Il ≤ 1µA at VOL, VOH

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures.

Copyright © Harris Corporation 1997

For -0.5V < VO < VCC + 0.5V. . . . . . . . . . . . . . . . . . . . . . . . . .±35mA DC Output Source or Sink Current per Output Pin, IO

74hc573完整中文资料

74hc573中文资料参数-74hc573引脚图-功能原理-74hC573的作用-应用电路-74hC563-54hC57高性能硅门CMOS器件SL74HC573跟LS/AL573的管脚一样。

器件的输入是和标准CMOS输出兼容的;加上拉电阻,他们能和LS/ALSTTL输出兼容。

当锁存使能端为高时,这些器件的锁存对于数据是透明的(也就是说输出同步)。

当锁存使能变低时,符合建立时间和保持时间的数据会被锁存。

×输出能直接接到CMOS,NMOS和TTL接口上×操作电压范围:2.0V~6.0V×低输入电流:1.0uA×CMOS器件的高噪声抵抗特性·三态总线驱动输出·置数全并行存取·缓冲控制输入·使能输入有改善抗扰度的滞后作用原理说明:M54HC563/74HC563/M54HC573/74HC573的八个锁存器都是透明的D 型锁存器,当使能(G)为高时,Q 输出将随数据(D)输入而变。

当使能为低时,输出将锁存在已建立的数据电平上。

输出控制不影响锁存器的内部工作,即老数据可以保持,甚至当输出被关闭时,新的数据也可以置入。

这种电路可以驱动大电容或低阻抗负载,可以直接与系统总线接口并驱动总线,而不需要外接口。

特别适用于缓冲寄存器,I/O 通道,双向总线驱动器和工作寄存器。

HC563引脚功能表:HC573引脚功能表:图1 HC573引脚图图2 HC573 国际电工委员会逻辑符号图3 HC563引脚图图4 HC563 国际电工委员会逻辑符号图5 HC563 逻辑图图6 HC573 逻辑图图7 输入输出等效电路真值表:ABSOLUTE MAXIMUM RATINGS绝对最大额定值:Top Operating Temperature: M54HC Series M74HC Series 操作温度:M54HC系列M74HC系列-55 to +125 -40 to +85℃tr,tf Input Rise and Fall Time输入上升和下降时间VCC =2V0 to 1000ns VCC=4.5V0 to 500VCC =6V0 to 400VOHHigh Level Output Voltage输出高电平电压2.0 VI = VIH or VILIO=-20 μA1.92.0-1.9 -1.9 -V4.54.44.54.44.4---6.05.96.05.95.9-4.5IO=-6.0mA4.184.314.134.10-6.0IO=-7.8 mA5.685.85.635.60-VOLLow Level Output Voltage输出低电平电压2.0 VI = VIH or VILIO=20μA-0.0 0.1 -0.1-0.1V4.5-0.00.1 0.10.16.0-0.00.10.10.14.5IO=6.0mA-0.170.260.330.406.0IO=7.8mA-0.180.260.330.40IIInput Leakage Current输入漏电流6.0VI =VCC or GND--±0.1-±1±1μA IOZState Output Off State Current关断状态3态输出电流6.0VI =VIH or VIL VO =VCC or GND--±0.5-±5.0-±10μAICCQuiescent Supply Current静态电源电流6.0VI =VCC or GND--4-40-80μA应用电路图:点击图片查看大图图8。

74hc573中文资料参数

74hc573中文资料参数

特点:

·三态总线驱动输出

·置数全并行存取

·缓冲控制输入

·使能输入有改善抗扰度的滞后作用

原理说明:

M54HC563/74HC563/M54HC573/74HC573的八个锁存器都是透明的D 型锁存器,当使能(G)为高时,Q 输出

将随数据(D)输入而变。

当使能为低时,输出将锁存在已建立的数据电平上。

输出控制不影响锁存器的内部工作,即老数据可以保持,甚至当输出被关闭时,

新的数据也可以置入。

这种电路可以驱动大电容或低阻抗负载,可以直接与系统总线接口并驱动总线,而不需要外接口。

特别适用于缓冲寄存器,I/O 通道,双向总线驱动器和工作寄存器。

HC563

HC573

图1 HC573引脚图图2 HC573 国际电工委员会逻辑符号

图3 HC563引脚图图4 HC563 国际电工委员会逻辑符号

图5 HC563 逻辑图

图6 HC573 逻辑图

图7 输入输出等效电路

真值表:

应用电路图:点击图片查看大图

图8

图9。

74HC573及上拉电阻

TTL电路的输入端是遵循TTL标准的,其需要的输入电流很小,74HC573的输入电流在电源电压为6V,输入电压为6V的情况下,其所需要的驱动电流仅仅为0.1uA。

你给的图是说明74HC573的输出驱动能力,573的每个输出引脚都有20mA的灌入电流,因此可以直接驱动LED,而扇出电流可以达到35mA.芯片有一个极限功耗,根据封装不同其功耗也不同,所以在设计驱动的时候,在任一时间要保证芯片的功耗不要超过此参数。

比如:573的每个引脚可能灌入20mA的电流,8个引脚,总电流是160mA,乘以工作电压5V,其值为800mW,这样就超出了芯片的极限,芯片容易损坏或者寿命缩短。

另外上拉电阻的问题。

是否需要上拉电阻,对于TTL电路输入端来说并不是关键,加与不加是要看你的单片机IO口的属性。

如果单片机的输出端口是推挽输出的,那么这个上拉电阻根本没有必要,但如果单片机的IO口是开漏输出或者是内部弱上拉输出的,那这个时候就需要接一个上拉电阻。

上拉电阻的大小一般参照后级电路所需要驱动电流的5~10倍来选取,可大不可小,一般现在用10K或者4K7的比较多,但如果对功耗要求比较严格,这个电阻就需要去计算,阻值太大那么容易受干扰,太小功耗不能满足,这需要去权衡.经过试验证明:以前在开发板上(比如天祥的板子)就是利用74HC573来驱动数码管的,该板是这样的,通过位选来导通哪个数码管并通过段选来使被选中的那个数码管显示什么数字。

这里面具体接法是:数码管是共阴极的,它的公共端(如数码管的3、8脚)接到位选的74HC573的输出端Q0,Q1,Q2,Q3,Q4,Q5,Q6,Q7,其中的一个如Q0(当然这里说的是一个数码管的接法,多个就接Q1,Q2,Q3,Q4一直可以接到Q7,共可以接8个数码管)对应573的管脚号是19,18,17,16,15,14,13,12。

数码管的a,b,c,d,e,f,g,h段分别接到另外一个74HC573的输出Q0,Q1,Q2,Q3,Q4,Q5,Q6,Q7,对应573的管脚号是19,18,17,16,15,14,13,12。