基于FPGA的视频图像采集系统的设计

基于FPGA的视频信号采集系统的硬件设计

2 系统 功 能

本系统所要完成的工作, 是在 F G P A的逻辑控制下, 对从 C D摄像头输人 的兼容视频模拟信号进行模 C 数转换并采集有效信号, 将有效数字视频信号放人缓冲区中进行缓冲, 等待后端视频处理部分 的数据请求, 从而将数据传输给后续部分进行下一步的处理. 由于后续部分需处理的数据比较多, 运算 比较复杂, 工作压 力很 大, 因此本系统需要分担一部分后续数据处理的工作, 以缓解其压力. 方法是采集有效的数字视频数据

蚓像 提取 图 2 系 统 框 图

视频前端芯片 S A 11 C D摄像头输出的标准模拟视频信号进行采样量化, A 7 对 C 1 输出的数 字信号经 FG P A进行提 取等 处理后 存入 S A 中供后 续视 频处 理 ( 视频 信号 压缩 、 RM 如 编码 等 ) 使用 b. 1 32 视 频 的模 / . 数转 换 视频信号的 A D转换有两种实现方法: / 一种是 由软件实现, 另一种是采用专用 图像 A D转换芯片实 / 现. 本设计 中视 频 A D转换 电路选用 的是专 用视 频 A D采 集芯 片 S A 11 / / A 7 . I

s A l1 A 7 1 芯片是由荷兰 P i s h i 公司生产的视频前端处理器, l p 其内部集成了强大的图像色度和亮度处理 功能, 能完成从标准模拟视频信号到数字视频信号的转换, 并且将非常复杂的视频 A D转换 电路集成到了 / 块芯片内, 使得外 围电路大大简化. 同时该器件可通过 P C总线很方便地与其他芯片如 F G 、 S 等芯片 P ADP

图 l 当前典型图形采集卡硬件框图

本设计所提 出的基于 F G P A的视频信号采集系统设计方案正是基于图 1 建立的, 其优势在于使用 了 FG P A作为 视频 采集 卡 的核 心控 制处 理 部分 , 以充分 利用 F G 可 P A所具 有 的可 编程 、 控制 逻辑 实 现方式 灵 活 的特 点 , 设计 出的视频采 集 系统 具有 很强 的通 用性 、 活性 和 实用性 【. 使 灵 2 】

基于FPGA的视频的采集、处理和显示

基于FPGA的视频的采集、处理和显示

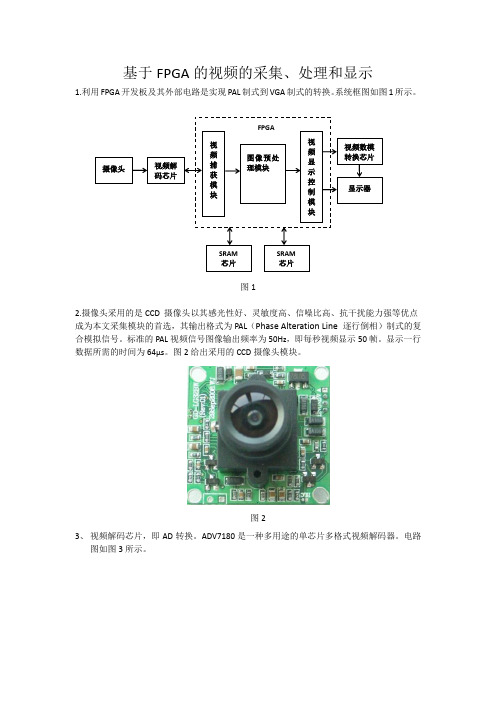

1.利用FPGA开发板及其外部电路是实现PAL制式到VGA制式的转换。

系统框图如图1所示。

图1

2.摄像头采用的是CCD 摄像头以其感光性好、灵敏度高、信噪比高、抗干扰能力强等优点成为本文采集模块的首选,其输出格式为PAL(Phase Alteration Line 逐行倒相)制式的复合模拟信号。

标准的PAL视频信号图像输出频率为50Hz,即每秒视频显示50帧。

显示一行数据所需的时间为64μs。

图2给出采用的CCD摄像头模块。

图2

3、视频解码芯片,即AD转换。

ADV7180是一种多用途的单芯片多格式视频解码器。

电路

图如图3所示。

图3

4. 视频采集模块电路板如图4所示。

图4

5. 系统采用VGA显示器作为视频图像的输出媒介,其显示数据为RGB三色的模拟视频数据,而FPGA处理完成的视频图像数据为数字信号,视频数模转换芯片,采用AD公司的ADV7123作为视频数模转换芯片。

ADV7123是一款单芯片、三通道、低功耗高速数模转换器,内置三个高速、10位、带互补输出的视频数模转换器、一个标准TTL输入接口以及一个高阻抗、模拟输出电流源。

如图5所示。

图5

6.结果图如图6所示。

图6 既是采用本文的系统实现的7.作品整体结构图。

基于FPGA的多路图像采集系统的软件设计

ue o r AA7 1 H vd od c d r n woF GA oahe e tea q iio ssfu S 1 3 ie e o esa d t P t c iv h c ust n,soa e n ipa ft h n e ma e i trg ,a d dsly o woc a n li g ,

fl sre .I fr e e l e h ac d o f u ain o wo F GA,a d te F mnb s c n g rt n, te I U6 6 ul cen t ut rrai s te c sa e c n g rt ft P — h z i o n h C o iu o f u ai i o h T 5

( 安 工 业 大 学 计 算机 科 学 与 工程 学 院 , 西 西 安 7 0 3 ) 西 陕 10 2

摘 要 :分 析 了 现 有 的 视 频 采 集 方 案 的 研 究现 状 。 对如 何 采 用 C D 摄 像 头采 集 多通 道 、 C 高分 辨 率 、 高质 量 的 图像 以及

基 于 F G 的 嵌 入 式 图 像 采 集 系统 的 实 现 方 法做 了研 究 。 与传 统 图像 采 集 系统 相 比 . 系统 主要 利 用 四 片视 频 解码 PA 该

关键 词 : A 7 l H;F G I U 6 ;图像 采 集 S A l3 P A; T 5 5

,

文 章 编 号 :17 — 2 6 2 1 )3 14 0 6 4 6 3 (0 号 :I 99 , 1 ’ P

文献标识码 : A

The s fwa e de i n o u t- ha ne m a e a q sto s s e b s d o FPGA o t r sg fm lic n li g c uiii n y t m a e n

基于FPGA和USB3.0的高速视频图像采集处理系统设计

摘要随着机器视觉的广泛应用,以及工业4.0和“中国制造2025”的提出,在数字图像的采集、传输、处理等领域也提出了越来越高的要求。

传统的基于ISA接口、PCI接口、串行和并行等接口的图像采集卡已经不能满足人们对于高分辨率、实时性的图像采集的需求了。

一种基于FPGA和USB3.0高速接口,进行实时高速图像采集传输的研究越来越成为国内外在高速图像采集研究领域的一个新的热点。

针对高速传输和实时传输这两点要求,通过采用FPGA作为核心控制芯片与USB3.0高速接口协调工作的架构,实现高帧率、高分辨率、实时性的高速图像的采集和传输,并由上位机进行可视化操作和数据的保存。

整体系统采用先硬件后软件的设计方式进行设计,并对系统各模块进行了测试和仿真验证。

通过在FPGA 内部实现滤波和边缘检测等图像预处理操作,验证了FPGA独特的并行数据处理方式在信号及图像处理方面的巨大优势。

在系统硬件设计部分,采用OV5640传感器作为采集前端,选用Altera的Cyclone IV E系列FPGA作为系统控制芯片,由DDR2存储芯片进行数据缓存,采用Cypress公司的USB3.0集成型USB3.0芯片作为数据高速接口,完成了各模块的电路设计和采集卡PCB实物制作。

系统软件设计,主要分为FPGA逻辑程序部分、USB3.0固件程序部分和上位机应用软件部分。

通过在FPGA上搭建“软核”的方式,由Qsys系统完成OV5640的配置和初始化工作。

由GPIF II接口完成FPGA和FX3之间的数据通路。

通过编写状态机完成Slave FIFO的时序控制,在Eclipse中完成USB3.0固件程序的设计和开发。

上位机采用VS2013软件通过MFC方式设计,从而完成整体图像采集数据通路,并在上位机中显示和保存。

整体设计实现预期要求,各模块功能正常,USB3.0传输速度稳定在320MB/s,通过上位机保存至PC机硬盘的图像分辨率大小为1920*1080,与传感器寄存器设置一致,采集卡图像采集帧率为30fps,滤波及边缘检测预处理符合要求,采集系统具有实际应用价值和研究意义。

基于FPGA的图像采集模块设计

口可兼 容 +5V, 常 工 作 时 功 耗 为 0 4 W , 闲 时 功 耗 为 正 . 空 o 0 。 钟 丢失 、 源 电 压 降 低 都 会 引起 芯 片 的 自动 复 . 7W 时 电 位, 因此 要 保 证 供 电系 统 的 稳 定 可靠 性 。

足 够 的 IE以及 RAM 单 元 , 在 其 内 部 实 现 像 预 处 理 为

行 同步信号 , 只有 在行 场 同步 信号 同时有效 时 , 且 才是 有

且 用 DS P的 IC总 线 来 配 置 其 内部 的 各 个 寄存 器 。这 里 把 S AA7 1 H 相 应 的 信 号 R 1 RTS 13 TS 、 0分 别 配 置 成 场 、

* 基 金 项 目: 东省 自然 科 学 基 金 ( o 62 69 。 广 N . 0 9 6 )

提 供 了保 障 , 且 具 有 足 够 的 I( 引 脚 使 其 方 便 与 其 他 设 并 /)

备 相 接 。本 文 将 详 细 描 述 F GA如 何 对 S P AA7 1 H 解 码 13 后 的 图 像 数 据 信 号 及 一 些 控 制 信 号 进 行 采 集 , 得 到 一 幅 并 完 整 的 图像 供后 续 系 统 进 行 处 理 。也 就 是 说 , 何 编 写 出 如 F GA程 序 来 控 制 各 个 信 号 , 而 采 集 图 像 。 最 后 , P 从 在 Qu ru IMo eSm 等 软 件 上 验 证 了 系 统 中一 些 重 要 的 at sI、 d l i 信 号 , 到 了较 为满 意 的效 果 。 达

出 8位 “ ’ VP 总线 , 标 准 的 I 为 TU6 6 YUV 5、 4:2: 2格 式 。 S AA7 1 H 的模 拟 与 数 字 部 分 均采 用 +3 3V, 字 Io接 13 . 数 /

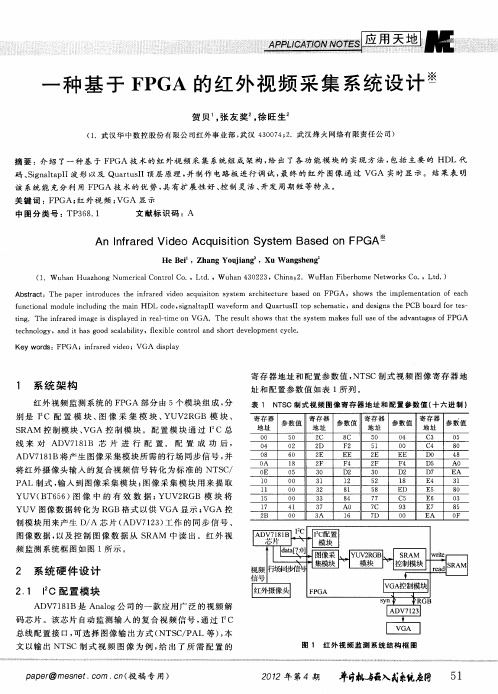

一种基于FPGA的红外视频采集系统设计

f n t n l d l n l d n h i u ci a mo u e i cu i g t e man HDL c d , i n l p 1wa e o m n a t sIt p s h ma i ,a d d s n h CB b a d f rt s o o e s at I g a v f r a d Qu r u I o c e t c n e i st e P o r o e — g

线 来 对 ADV7 8 B 芯 片 进 行 配 置 。 配 置 成 功 后 , 11

址 和 配 置 参 数值 如 表 1所 列 。

表 1 N S T C制 式 视 频 图像 寄 存 器 地 址 和 配 置 参数 值 ( 六进 制 ) 十

寄存 器 参 数值 寄 存 器 参 数 值 寄 存 器 参 数 值 寄 存 器 参 数 值

码 、i a a I 波 形 以及 Q atsI 层 原 理 , 制 作 电路 板 进 行 调 试 , 终 的 红 外 图像 通 过 VG 实 时 显 示 。结 果 表 明 S n l pI g t u r I顶 u 并 最 A

该 系统 能 充 分 利 用 F GA 技 术 的优 势 , 有 扩 展 性 好 、 制 灵 活 、 P 具 控 开发 周 期 短 等 特 点 。 关 键 词 :F GA; 外 视 频 ; P 红 VGA 显 示

( . W u a u z o g Nu rc lC n r l . 1 h n H a h n me ia o t o Co ,Lt . d ,W u a 3 2 3,Chn ; .W u n Fi e h me Ne wo k . h n40 2 ia 2 Ha b r o t r sCo ,L d ) t .

基于FPGA的图像处理系统设计与实现

基于FPGA的图像处理系统设计与实现图像处理是计算机视觉领域中的重要技术之一,可以对图像进行增强、滤波、分割、识别等操作,广泛应用于医学图像处理、工业检测、安防监控等领域。

而FPGA(Field Programmable Gate Array)可编程门阵列,则是一种自由可编程的数字电路,具有并行处理能力和灵活性。

本文将介绍基于FPGA的图像处理系统的设计与实现。

一、系统设计流程1. 系统需求分析:首先需要明确图像处理系统的具体需求,例如实时性、处理的图像类型、处理的算法等。

根据需求,选择合适的FPGA芯片和外设。

2. 图像采集与预处理:使用图像传感器或摄像头采集图像数据,然后对图像进行预处理,如去噪、增强、颜色空间转换等,从而提高后续处理的准确性和效果。

3. 图像处理算法设计与优化:根据具体的图像处理需求,选择适合的图像处理算法,并对算法进行优化,以提高处理速度和效率。

常用的图像处理算法包括滤波、边缘检测、图像分割等。

4. FPGA硬件设计:基于选定的FPGA芯片,设计硬件电路,包括图像存储、图像处理模块、通信接口等。

通过使用硬件描述语言(如Verilog、VHDL)进行功能模块设计,并进行仿真和验证。

5. 系统集成与编程:将设计好的硬件电路与软件进行集成,包括FPGA程序编写、软件驱动开发、系统调试等。

确保系统的稳定运行和功能实现。

6. 系统测试与优化:对整个系统进行完整的测试和验证,包括功能性测试、性能测试、稳定性测试等。

根据测试结果,对系统进行优化,提高系统的性能和可靠性。

二、关键技术及挑战1. FPGA芯片选择:不同的FPGA芯片具有不同的资源和性能特点,需要根据系统需求选择合适的芯片。

一方面需要考虑芯片的处理能力和资源利用率,以满足图像处理算法的实时性和效果。

另一方面,还需要考虑芯片的功耗和成本,以便在实际应用中具有可行性。

2. 图像处理算法优化:在FPGA上实现图像处理算法需要考虑到算法的计算复杂度和存储开销。

基于FPGA的视频图像采集与显示系统设计

YANG Qi n。ZHOU Yu n - f e i +,HU Yo n g - b i n g

( S c h o o l o f Me c h a n i c a l S c i e n c e a n d En g i n e e r i n g,H u a z h o n g Un i v e r s i t y o f S c i e n c e a n d Te c h n o l o g y ,W u h a n 4 3 0 0 7 4 ,C h i n a )

Ab s t r a c t :As CC D c a me r a a n a l o g s i g n a l d a t a i s e n o r mo u s a n d F PGA’ S p a r a l l e l p r o c e s s i n g c a p a b i l i t y i s p o we r f u l ,A p r o j e c t i s

2 0 1 3年 6月

计算机 工程 与设计

C OMPUTE R E NGI NE ERI NG AND DES I GN

J u n - 2 0 1 3

V0 1 . 3 4 NO . 6

第3 4卷

第 6期

基于FPGA技术的视频信息采集系统的设计与实现的开题报告

基于FPGA技术的视频信息采集系统的设计与实现的开题报告一、选题背景随着科技的不断发展,数字信号的处理已经成为当今社会的一个重要方向。

视频信息是其中不可或缺的一部分,它被广泛应用于监控、视频会议、互联网直播等领域。

而基于FPGA(Field Programmable Gate Array)技术的视频信息采集系统是一个非常有前景和实用价值的研究方向。

FPGA具有硬件可重构和并行处理等优点,能够高效处理大规模的数据,因此被广泛应用于视频采集和处理领域。

二、选题目的本项目旨在设计和实现一个基于FPGA技术的视频信息采集系统,能够高效地采集、传输和处理视频信号,并提供简单易用的界面。

具体实现目标如下:1. 设计一个视频信号采集板卡,能够快速采集高清视频信号,并通过高速接口传输到FPGA。

2. 设计一个视频信号处理模块,能够对采集到的视频信号进行色彩空间转换、图像增强等操作。

3. 利用高速存储器实现视频数据的暂存和传输,并设计一套简单易用的界面,在界面上实现视频的播放和保存等操作。

三、研究内容本项目主要涉及以下内容:1. FPGA基础知识:了解FPGA的基本原理、编程语言和开发软件。

2. 视频信号采集:设计和实现一个视频信号采集板卡,能够快速采集高清视频信号,并通过高速接口传输到FPGA。

3. 视频信号处理:设计一个视频信号处理模块,能够对采集到的视频信号进行色彩空间转换、图像增强等操作。

4. 高速存储器设计:利用高速存储器实现视频数据的暂存和传输。

5. 界面设计:设计一套简单易用的界面,在界面上实现视频的播放和保存等操作。

四、研究方法本项目采用以下研究方法:1. 文献查阅法:通过查阅相关的专业书籍、学术论文和网络资料,掌握FPGA技术的基本原理和应用。

2. 实验研究法:通过设计和实现一个视频信息采集系统,验证所学理论知识的正确性和实用性。

3. 数据分析法:通过对实验结果的数据分析,总结经验和发现问题,进一步完善和优化系统的性能。

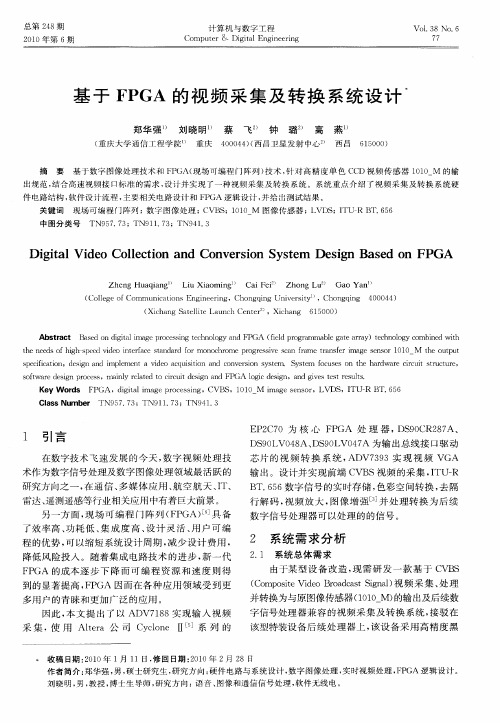

基于FPGA的视频采集及转换系统设计

Ab t a t B sd o ii l ma ep o e sn e h oo y a d F GA ( il r g a s r c a e n d gt g r c s i g t c n lg n P ai f d p o rmma l g t r a )tc n lg o i e t e b e ae a r y e h oo y c mbn d wi h t e n e so ih s e d v d o i tra e sa d r o n c r me p o rs ie s a r me ta s e m g e s r 1 1 M he o t t h e d f g - p e i e n ef c t n a d fr mo o h o r g e s c n fa r n fr i h v a esn o 0 0 t u pu

一

Cls mb r TN9 7 7 a s Nu e 5 . 3;TN9 l 7 :TN9 1 3 1_3 4 .

1 引 言

在数字技 术 飞速 发 展 的今 天 , 数字 视 频 处 理技

E 2 7 P C 0为 核 心 F GA 处 理 器 , S 0 R2 7 P D 9 C 8 A、

雷达、 遥测遥感 等行业 相关应用 中有着 巨大前景 。

输 出 。设 计并 实 现前端 C S视 频 的采 集 ,T R VB I U— B 6 6 字信 号 的实 时存 储 , T. 5 数 色彩 空 间转换 , 隔 去 行解 码 , 视频 放 大 , 像增 强 _ 并 处 理转 换 为 后 续 图 3 ] 数字 信号 处理 器 可 以处 理 的 的信号 。

D g I 4 A、 S 0 4 A 为输 出总线接 口驱 动 s 0 8 D 9 I V0 V0 7 芯 片的 视 频 转 换 系 统 , V7 9 AD 3 3实 现 视 频 VG A

基于FPGA的视频编码系统设计与实现

基于FPGA的视频编码系统设计与实现基于FPGA的视频编码系统设计与实现摘要:随着数字视频的快速发展,视频编码成为了计算机视觉领域的重要研究方向。

本文主要介绍了基于FPGA的视频编码系统的设计与实现过程。

首先,简要回顾了视频编码的基本原理和常用算法。

然后,详细讨论了FPGA作为硬件加速平台的优势,并介绍了FPGA平台上常用的视频编码算法。

接着,详细描述了视频编码系统的硬件架构设计,包括编码器和解码器的模块划分以及模块之间的通信和数据传输。

最后,进行了实验验证并进行了性能分析,结果表明,基于FPGA的视频编码系统在实时性和编码效率方面均具有较好的性能。

关键词:FPGA、视频编码、编码器、解码器、硬件架构1. 引言随着互联网技术的飞速发展和宽带网络的普及,视频数据的传输和处理需求日益增加。

视频编码作为一种将原始视频信号转换为压缩格式的技术,已经成为了现代多媒体应用中不可或缺的环节。

在视频编码中,编码器将原始视频转换为压缩的码流,而解码器将压缩的码流解码为可视的视频图像。

目前,H.264、H.265等压缩标准已经成为了主流视频编码标准。

2. 视频编码原理和算法视频编码的核心思想是利用视频序列中的时空冗余性进行压缩。

在时域上,视频序列中的相邻帧之间存在大量的冗余信息,可以通过运动估计和运动补偿来减少冗余。

在空域上,同一帧中相邻像素之间也存在冗余,可以通过空间预测编码来提高压缩效率。

常用的视频编码算法主要包括运动估计、变换编码和熵编码等。

3. FPGA在视频编码中的应用优势FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,具有高度灵活性和可编程性。

与传统的视频编码器相比,基于FPGA的视频编码系统具有以下优势:(1)硬件加速平台:FPGA可以提供并行计算和硬件加速的能力,能够显著提高视频编码的处理速度和性能;(2)可嵌入性:FPGA可以嵌入到视频采集设备、摄像头等设备中,具有较小的体积和功耗;(3)可定制性:FPGA可以根据不同的视频编码需求进行定制开发,提供更灵活的编码方案。

基于FPGA的视频采集输出系统的实现的开题报告

基于FPGA的视频采集输出系统的实现的开题报告1. 项目背景和意义随着数字视频技术的发展和普及,视频采集、处理和输出系统已成为各种应用场景中的重要环节,比如视频监控系统、直播平台、游戏录制等。

FPGA作为可重构硬件的代表,具有高度的灵活性和可定制性,因此在视频领域得到了广泛的应用。

本项目旨在基于FPGA开发一个视频采集输出系统,实现实时高清视频的采集、处理和输出,为各种应用场景提供高效、灵活的解决方案。

2. 项目内容和技术路线本项目的主要内容包括视频采集模块、视频处理模块、视频输出模块等。

其中,视频采集模块使用FPGA硬件来读取外部视频信号,并将其转换为数字信号,以方便后续处理。

视频处理模块则包括图像增强、边缘检测、滤波等基本功能,以及特定应用领域的定制功能,比如目标检测、场景识别等。

视频输出模块则负责将处理后的视频信号输出到显示设备上,包括HDMI、VGA、DVI等接口。

技术路线如下:(1)使用FPGA实现视频采集模块,借助VGA或HDMI接口来读取外部视频信号。

(2)基于视频采集模块开发视频处理模块,包括图像处理功能、定制应用功能等。

(3)设计视频输出模块,支持多种输出接口,能够自动选择最优接口。

(4)利用DSP等硬件加速技术,提高视频处理和输出的效率和质量。

(5)通过调试和性能优化,实现较为稳定和高效的视频采集输出系统。

3. 预期成果和应用前景本项目的预期成果包括以下几个方面:(1)基于FPGA的视频采集模块,支持不同分辨率、帧率的视频信号读取。

(2)完整的视频处理模块,包括基本功能和定制应用功能。

(3)支持多种输出接口的视频输出模块,能够自动选择最优输出方式。

(4)经过性能优化和调试的完整视频采集输出系统,具有较高的效率和稳定性。

本项目的应用前景广阔,可以应用于各种视频采集、处理和输出场景,比如:(1)视频监控系统:通过FPGA实现高效的视频采集和处理,能够实现实时的视频监控功能。

(2)直播平台:通过FPGA实现高清视频采集和输出,提高直播质量和用户体验。

采用FPGA实现视频和图像处理设计

Al r 公 司 Bin J et ta e r .J nz a

视频和图像处理发展趋势

到 了 大 量 应 用 。H .6 将 可 能 取 代 广 播 24

另 一快 速发 展的 领域 是视 频智 能 。

以视 频和 图像处 理为核心 的HDT 电视 应用 中的 MP G2 V E ,以及视 频监控 相机 已经具 有摇摄 、俯仰 、变 焦、全景 和 数字 影 院 等 创新 技 术 的进 展 非 常 迅 系统 的MP G at 2 E 4 P r 和用于视 频会议 等 拍摄功能 ,这些功 能逐步 由系统 智能 速 ,其推 动力量在 于 图像采集 和显示 分 的 H.6 。在应 用这些新 压缩方 案的同 实现 而不需 要人为干 预 。移 动探测技 术 23 辨 率 、高级 压缩方法 以及视频 智能的跨 时 , 2 4 N P G 2 0 标 准仍然 在不 能够 更高效 的利用硬 盘存储 ,它只捕 获 H.6  ̄ E 0 0 J 越 式发展 。 在过去 几年 中 ,分辨率 的发展最 为

表 1不 同终端设备的 分辨率

3 D医疗 成像压缩 多分量 变换 。附件 1 6 0

随 着分辨率 和压缩 比的提 高 ,不但

将包括 J I 议 ,远 程浏 览使 用 J E 要提 高性能 ,还需要非 常灵活 的体 系结 P P协 P G 2 0 压缩 的医疗 影像 。 00

终端设备

的例子 包括缩放 、去 隔行 、滤波和 颜色 断攀 升 ,使得这 些解决 方案只有 在大批 基 础 ,产 品从 推 出以 来 已 经发 售 了多

空 间转 换等 。

量 消费类 应用 中才 具有 较好 的 经济性 。 年 。而且 ,F GA设计很 容易从一 个工 P

视频图像实时采集和显示系统的FPGA设计

视频 图像实时采集和显示系统 的F G P A设计

The FPGA des gn o ealtm e deo m age t i fr -i vi i s da a acqui ii s t on and di spl y ys em a s t

集 成 电路 ,采 用硬 连 线逻 辑实 现数 据 处理 和 运算 , 具 有 集成 度高 、速 度 快 、性能 稳 定 、开发 周 期短 、

便 于 改进升 级 等一 系 列优 点 ,还 能实 现视 频 采集 、

图像 显 示 的外 围逻 辑 控 制 ,在 视 频 采 集 和 图像 处

理 方 面 具 有 独 特 优 势 。使 用 F GA 实现 该 类任 务 P

l

正 、闪 烁 避免 、连 续 调 整 滤 光 尺 寸 、平 滑 的 数 字

变 焦 、快速 自动 曝 光模 式 和 不工 作 时缺 陷修 正 等 ,

可 以通过 两线 串行接 口对其 进 行配置 。

然 后叙 述 了各 功 能模 块 和 接 口 电路 的设 计 方 法 和 过程 ,重 点 介 绍 了 F GA应 用 系支 持 S 18 HX1 2 V) XGA格 式 输 出 ; 嵌 入 的 可 编程 图像 处 理 器 提 供 的功 能 包括 色 彩 恢 复 和 修 补 、 自动 曝 光 、 白 平 衡 、镜 头 阴 影 修 正 、 增 加 清 晰 度 、可 编 程 灰 度 修 正 、黑 暗 电平 失 调 修

0 引 言

视 频信 息采集 为视频 图像处理 、传 输 、显示等 提供提 供原始 的数 字图像数 据 ,视 频采 集系统 的性 能是影 响视频 图像 系统性 能 的关 键 因素之一 f 1 】 。随 着人 们 对 视 频 图 像 质量 的要 求 越 来 越 高 ,对 视 频 采 集 系统 的性 能 要 求 也 将 越 来 越 高 口。 目前 视 频 ] 采 集 系统 常 用 的 处 理 器 包括 通 用 处 理 器 、D P和 S

基于FPGA的视频图像采集系统

嵌 入 式技 术 墨

基于 F G P A的视频 图像采集系统

黄颠 挺 ,王 少 荣

( 中科技 大 学 电力安 全与高效 湖 北省 重 点实验 室 , 湖北 武 汉 4 0 7 华 3 0 4) [ 摘要] 介 绍 了一种基于 F G P A和 A M视 频采集 系统进行设计的新 方法。 该 系统 采用摄像 头芯片 L 6 7 R M9 2 、低 端 F GA器件和 A M嵌入 式系统实现 了高速连续的视频 采集 。 系统具有设计结构 清晰 、使 用灵活和性 P R

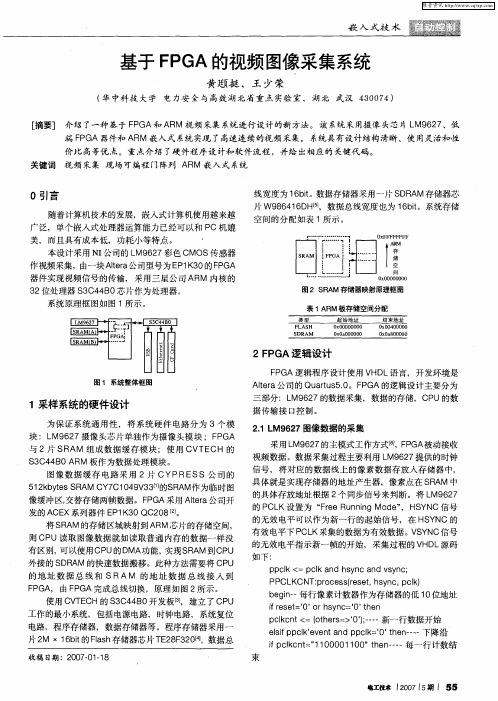

图 1 系统整体框图

Atr 公司的 Qu r s .。F G l a e at 50 P A的逻辑设计主要分为 u

1采样系统的硬件设计

U的数 一存 空一 M9 2 三部分:L 6 7的数据采集,数据 的存储,CP 删储问 蝴

据传输接 口控 制。

为保证系统通用性,将 系统 硬件 电路分为 3个模

如下:

p l <: p k a d h y c a s n pck cl n s n nd v y c;

将S A R M的存储区域映射到 A M芯片的存储空间, R 则 C U读取图像数据就如读取普通 内存 的数据一样没 P

有区别, 可以使用 C U的D A功能, P M 实现S A R M到C U P 外接的S R M的快速数据搬移 。此种方法需要将 C U DA P 的地 址 数据 总 线 和 SRAM 的地 址 数据 总 线接 入 到 F G , 由F G P A P A完成总线切换,原理如 图 2 所示。 使用 C T C V E H的 S C 4 0开发板【 3 4B ,建立 了 C U P 工作的最小系统,包括 电源电路,时钟电路,系统复位

基于FPGA的视频图像处理系统的研究与设计

1 引 言

FG P A具 有结 构 灵 活 、 用性 强 、 于 维 护 和 通 便

( L ) 1 2个 IO管 脚 。 D L ,8 /

芯片 驱 动 单 元 采 用 F G P A专 用 X 1 V 1的 C8 O P A , 系统更稳 定 , 大 。 R M 使 更强 视频 处理 单元采 用 A I 司的 A V 19 具 D公 D 77 ,

关键词: P A; F G 视频 处理 ; 号发 生 ; 频编码 芯 片 ;IO 信 视 FF

中 图分 类号 :N 4 T 95

文献标识 码 :A

Re e r h a d De in o d o I g r c sig s a c n sg fVi e ma eP o e sn

8 4计 数 时输 出一 个 t m信 号 , 其 作 为垂 直 行 6 e r 将 计数器 的 使 能 信 号 , 垂 直 行 计 数 器 开 始 计 数 。 使 图 2为 同步时序部 分波形 图 。

I . 一行消隐一. 1 .

V y  ̄ I .. J s n . .__ .. .. .

识情 况如 下 : 1 )场 同 步 开 槽 脉 冲 期 间 :A = V C, = C B

GND;

3 原 理 设计

图 1 系统 框 图。 为

2 前后 均衡 脉冲期 间 : =V C, V C; ) A C B: C

视频

显 示 时序

竺一

3 行 同步期 间 : ) A=G D, N B=V C; C

图 1 系统 框 图

号, 设置 输 入 不 同 组 合 可 以 产 生 不 同 的 同 步 信 号 , 而 清 晰 地 看 出不 同 的 同 步 信 号 对 电 视 图 从 像 的影 响 。

基于FPGA的数字图像采集存储系统的设计

文 章 编 号 :0 2 8 9 2 0) 6 0 3 — 3 1 0 — 6 2(01 0 — 0 2 0

基于 F GA的数字 图像采集 P 存储 系统的设计 串

刘 攀 , 红亮 , 王 孟令 军

・ 设・ 实 计 用

( 中北 大 学 仪 器科 学 与 动 态测 试教 育部 重 点 实验 室 ; 电子 测 试技 术 国 家重 点 实验 室 , 西 太原 0 0 51 山 30 )

E e t n a ue n e h oo y a u n 0 0 5 ,C ia lcr i Me rme t T c n l ,T i a 3 0 1 h n ) oc s g y

【 bta t ad aei pe ett nb sd o P A i pooe o r l etecn g rtn o MO m g esr cusi A s c 】A hrw r m lm nao ae n F G s rp sd t e i h of ua o fC S i aesno,aq it n r i az i i io

【 摘 要 】本 系统 主 要 利 用 F G 实 现 了对 C S图像 传 感 器 的 配 置 及 图像 采 集 , 采 集 到 的 数 字 图像 实 时存 储 到 Fah存 储 器 PA MO 将 l s

基于FPGA的视频采集系统设计

Ab st r a c t The p a p e r a i ms t o s t u d y t h e r e a l i z a t i o n o f FPGA- ba s e d v i d e o c a pt ur e s y s t e m. I t u s e s Ve r i l o g h a r dwa r e d e s c r i pt i o n 1 a n g u a g e t o d e s i g n a n d v e r i f y t h e mo d u l e s o f t h e s y s t e m ,i n c l u d i n g I C b u s s y s t e m c o n f i g u r a t i o n mo d u l e ,I TU

a l — t i me d i s pl a y a s we l 1 . Th e s y s t e m a l s o pr o v i de s a mor e f l e x i b l e a n d e f f i c i e n t p o s s i b i l i t y f o r v i d e o c o l l e c t i o n b a s e d o n FPGA. Th e s y s t e m h a s t h e a d v a n t a g e s o f s ma l l s i z e,h i g h e f f i c i e n c y,l o w c O S t ,a n d c a n b e wi d e l y us e d i n v i d e o p r o c e s s i n g s ys t e ms ,s e c u r i t y mo n i t o r i n g s y s t e ms a n d

基于FPGA的图像采集系统设计与实现

基于FPGA的图像采集系统设计与实现1、引言视频图像采集是视频信号处理系统的前端部分,正在向高速、高分辨率、高集成化、高可靠性方向发展。

图像采集系统在当今工业、军事、医学各个领域都有着极其广泛的应用,如使用在远程监控、安防、远程抄表、可视电话、工业控制、图像模式识别、医疗器械等各个领域都有着广泛的应用[1]。

本文介绍了一种基于 FPGA的图像采集系统,用户可以根据需要对FPGA 内部的逻辑模块和I/O模块重新配置,以实现系统的重构[1][2];而且采用这种设计方案 ,便于及时地发现设计中的错误,能够有效地缩短研发时间,提高工作效率。

2、系统的总体框架和工作原理整个系统主要分为四个模块:视频解码模块、视频编码模块、存储器模块和FPGA核心控制模块,系统总体框架如图1所示。

其中FPGA实现的主要功能有:视频编解码器件的初始化,视频图像的采集存储以及将采集的图像数据通过视频编码芯片送到监视器上显示。

系统的工作原理为:系统上电后,FPGA通过FLASH中的程序对完成视频解码和编码芯片的初始化配置;在接到视频AD转换的中断信号后,FPGA将转换的数字图像数据传送到SRAM保存;一帧图像转换结束后FPGA再将SRAM中的数字图像传递给视频编码芯片以便在监视器上显示,同时开始控制下一帧图像的采集。

3、硬件电路设计3.1 AD和DA转换模块本系统采用的视频编解码芯片是ADV7181和ADV7177,下面分别介绍AD 和DA转换器件的硬件电路设计。

3.1.1 AD转换模块ADV7181系统是AD公司推出的一款视频解码芯片[3],它具有如下特点:I2C总线接口,6通道模拟视频输入,支持NTSC、PAL、SECAM视频制式,支持多种模拟输入格式和多种数字输出格式。

本系统中选用其中的通道1作为PAL制CVBS视频输入,数据输出可根据需要采用8位或16位的格式输出。

ADV7181与FPGA的接口电路如图2所示。

系统上电后通过FPGA的I2C模块完成对ADV7181的初始化配置,其中ADC_SCLK、ADC_SDATA分别为I2C总线的时钟线和数据线。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

0引言视频图像采集系统是多媒体信息处理、视频监控等系统的前端子系统,是实际视频处理系统中必须考虑的部分。

随着图像的数字化处理在军事、科研、工业、农业和医疗等领域得到广泛应用,许多用于图像采集和处理的芯片也相继推出,处理功能越来越强大,使用也越来越方便[1-2]。

数字视频日益成为一种广泛应用的媒体,视频技术的产品开发也颇具前景,而嵌入式视频采集系统的实现方法正是其中的关键技术[3]。

对于嵌入式视频采集系统,选择不同的视频编解码器或处理器,其系统构成和实现方法也有所不同。

目前国内利用CCD 摄像头采集视频图像一般采用CCD 摄像头+视频解码芯片(如ADV7181B )+FPGA/CPLD/EPLD+DSP 的模式实现[4-6],其中视频信号解码芯片用来对信号进行AD 转换,FPGA/CPLD/EPLD 用于对视频采样进行控制,DSP 对采集的数据进行处理。

本文设计了一种利用Altera 公司的FPGA CycloneII EP2C35和AD 公司的视频解码芯片ADV7181B 的嵌入式视频采集系统。

CycloneII EP2C35用于对视频采样进行控制,ADV7181B 用于对输入视频信号进行AD 转换。

1视频采集系统基本构成图1为视频图像采集的系统框图,主要分为以下几部分:I 2C 总线配置、ITU656解码、帧存储器(SDRAM )设计和VGA 显示模块。

I 2C 总线配置模块根据系统的需求配置芯片的内部寄存器,使芯片能够正确的将摄像头采集到的模拟视频信号转换为数字图像并对数字图像进行处理(如摄像头的PAL 或者NTSC 制式就是通过I 2C 总线来配置)。

VGA 显示模块是将SDRAM 中的视频数据通过VGA 显示器显示出来。

收稿日期:2007-09-02E-mail :zhcf45@作者简介:祝长锋(1984-),男,江西波阳人,硕士研究生,研究方向为嵌入式计算及系统;肖铁军(1963-),男,教授,研究方向为嵌入式计算及系统。

基于FPGA 的视频图像采集系统的设计祝长锋,肖铁军(江苏大学计算机科学与通信工程学院,江苏镇江212013)摘要:分析了各种视频采集方案的研究现状。

对如何采用CCD 摄像头采集高分辨率、高质量的图像以及基于FPGA 的嵌入式视频图像采集系统的实现方法进行了研究。

采用了以摄像头+解码芯片模式为采集方案,针对视频解码芯片ADV7181B ,实现了I 2C 总线配置、ITU656解码、VGA 显示模块的设计。

设计的视频采集控制器已经在Altera 公司的CycloneII 系列FPGA (EP2C35)上实现。

结果显示本设计具有速度高、成本低、易于集成等优点。

关键词:CCD 摄像头;现场可编程门阵列;视频解码芯片;视频采集;实时处理中图法分类号:TP274+.2文献标识码:A文章编号:1000-7024(2008)17-4404-04Design of video capture system based on FPGAZHU Chang-feng,XIAO Tie-jun(School of Computer Science and Telecommunications Engineering,Jiangsu University,Zhenjiang 212013,China )Abstract :The research of the method of kinds of video capture is analyzed.The method that how to capture high resolution and high quality image and how to implement embedded video capture system based on FPGA is researched.The project of video capture is adopted by the mode of camera and decoding chip.The decode of ITU656and the display of VGA modules is implemented on the video-decoding chip ADV7181B.This video capture control is achieved on the EP2C35in Cyclone II series of Altera International Ltd.The result shows that the system is highlighted for its high processing speed,low cost and easy integration.Key words :CCD camera;FPGA;ADV7181B;video capture;real-time processing2008年9月计算机工程与设计Sept.2008第29卷第17期Vol.29No.17Computer Engineering and Design图1系统基本结构SCLKSDATAI视频解码芯片ADV7181B 为AD 公司的一款可编程芯片,支持多种格式的模拟视频信号输入,包括各种制式的CVBS 信号、S-Video 和YPrPb 分量,可以自动检测NTSC 、PAL 、SEC-AM 及其兼容的各种标准模拟基带电视信号,包括PAL-B/G/H/I/D 、PAL-M/N 、PAL-combination N 、NTSC-M 、NTSC-J 、SEC-AM 50Hz/60Hz 、NTSC4.43和PAL60等。

ADV7181的数字输出为16位或8位的与CCIR656标准兼容的YCrCb 4:2:2视频数据,还包括垂直同步VS 、水平同步HS 及场同步等信号。

2I 2C 总线配置为了对总线上的设备进行控制,必须制定一个特定的协议(I 2C 总线协议)。

首先,I 2C 控制器建立一个数据传输的开始条件:SCLK 保持为高,SDATA 从高到低转变。

外围设备监控SDATA 和SCLK ,等待开始条件和正确的传输地址。

开始条件到达以后,紧接着送出一个8位的设备地址,所有的外围设备响应开始条件并转换下一个8位寄存器地址(7位地址和1位读写信号)。

外围设备认出传送地址后作出响应,在第9个时钟脉冲把数据线变为低电平;其它所有的设备都退出总线,使总线处于空闲状态,开始将8位的数据写入寄存器或者从寄存器读出,R/W 读写位决定了数据的方向。

当SCLK 为高,SDATA 从低到高转变时,表示一次传输完成,等待下一次传输开始。

图2为I 2C 传输的时序。

I 2C 总线用来配置ADV7181B 解码芯片,写入各寄存器的值,使芯片能够完成特定的功能。

各寄存器值通过I 2C 控制器写入,由于I 2C 只用来写寄存器,因此编写的I 2C 控制器只需要实现写数据的功能即可,并不需要写一个完整的I 2C 控制器。

I 2C 控制器每次传输24位数据,前8位是从设备地址SLA VE_ADDR ,接下来8位是从设备的寄存器地址SUB_ADDR ,最后8位是数据,I 2C 控制器使用33个I 2C 时钟周期完成1次24位数据传输。

第1个时钟周期初始化控制器,第2、3周期启动传输,第4-30个周期传输数据(其中包含24位数据和3个ACK ),最后3个周期用以停止传输。

控制器中使用了一个6位计数器SD_COUNTER 对传输周期计数。

配置数据存储在查找表LUT_DATA 中,LUT_DATA 数据为16位,包括了ADV7181B 的寄存器地址和寄存器数据,共对40个寄存器的内容作配置,配置时逐个写入寄存器的值,寄存器索引代码为LUT_INDEX 。

每个寄存器的配置分为3步,用图3所示的状态机来实现,mSetup_ST 表示当前进行到了哪一步,第一步准备数据,将8位的从设备地址与LUT_DATA 合并为24位数据mI2C_DATA ,并将mI2C_GO 置1,启动I 2C 传输,第5步检测传输结束信号,如果检测到传输结束(mI2C_END=1),但ACK 信号不正常,返回第1步,重新发送数据,如果检测到传输结束且ACK 信号正常,则进入第3步,将寄存器索引LUT_INDEX 加1,准备下一个数据的传输。

3ITU656解码摄像头采集到的视频数据经解码芯片进行AD 转换后得到8位的4:2:2视频数据流。

ITU656解码模块根据ITU656标准将4:2:2的数据流解码成ITU656标准视频流。

ITU656并行接口除了传输4:2:2的YCbCr 视频流外,还有行、场同步所用的控制信号。

PAL 制式的图像一帧有625行,每秒扫描25帧;NTSC 制式为一帧525行,每秒扫描30帧。

每行数据由1728字节的数据块组成。

其中,PAL 制式23~311行是偶数场视频数据,312~552行是奇数场视频数据,其余为垂直控制信号。

NTSC 制式20~264行是偶数场视频数据,283~525行是奇数场视频数据,其余为垂直控制信号。

图4为ITU656每行的数据结构。

每行数据包含水平控制信号和YCbCr 视频数据信号。

视频数据字是以27兆字/秒的速率传送的,其顺序是:Cb ,Y ,Cr ,Y ,Cb ,Y ,Cr ,…其中,Cb ,Y ,Cr 这3个字指的是同址的亮度和色差信号取样,后面的Y 字对应于下一个亮度取样。

每行开始的288字节为行控制信号,开始的4字节为EAV 信号(有效视频结束),紧接着280个固定填充数据,最后是4字节的SAV 信号(有效视频起始)。

SA V 和EA V 信号有3字节的前导:FF 、FF 、00;最后1字节XY 表示该行位于整个数据帧的位置及如何区分SAV 、EAV 。

在每个时钟的上升沿读取从解码芯片传来的8位数据。

当检测到一行数据的开始标志FF 0000XY 时,检测到SAV 信号或EA V 信号,提取H 、F 、V 信号。

然后发出开始命令,同时开启行列计数器,开始对接下来的图像数据进行解码,根据每个8位数据自身带的信息,判断该数据为Y ,Cr 还是Cb ,从而得到Y ,Cr ,Cb 各分量的值。

解码流程如图5所示。

图2I图4ITU656每行的数据结构行控制信号EAVSAV视频数据信号F F 0000X Y 80108108010…F F0000X Y C Y YY C r b Cb Cr…428041440图5视频解码流程YN提取Y 、Cb 、Cr提取H 、F 、V信号检测SAV 或EAVPAL制式的视频信号分辨率为864×625,其中有效视频数据为720×576像素。