2501-2-00-01-00-00-07-0中文资料

牧场物语金手指

1600蛋黄酱S型1700蛋黄酱M型1800蛋黄酱L型1900蛋黄酱G型

1A00蛋黄酱P型1B00蛋黄酱X型::

1C00牛乳S型1D00牛乳M型1E00牛乳L型1F00牛乳G型

2000牛乳P型2100牛乳X型

2200 S奶酪2300 M奶酪2400 L奶酪2500 G奶酪2600 P奶

◆优的强求:

时间:水(三)am10.00-pm5.00

地点:艾莲家

条件:主角和艾利未婚

选择:选“玩”,大家友好度增加;选“不玩”,大家友好度降低

◆艾利和优的姐弟情:

时间:水(三)am9.00-pm1.00

地点:艾莲家

条件:主角和艾利未婚

内容:优生病了,艾利让主角带他去医院,艾利好感增加,艾莲、优、多特友好度增加

草0401三色花

0501羊毛S型羊毛0601羊毛M型羊毛0701羊毛L型羊毛

0801羊毛G型羊毛

0901羊毛P型羊毛0A01羊毛X型羊毛

0B01 S型羊毛球0C01 M型羊毛球0D01 L型羊毛球0E01 G

型羊毛球

0F01 P型羊毛球1001 X型羊毛球

1101废矿石1201铜1301银1401金1501秘银1601奥

7F00生鱼片8000煮鱼8100寿司拼盘8200披萨8300 ??

8400咖喱?? 8500天妇罗

8600 ??? 8700 ??? 8800天妇罗面8900乾烧意面8A00 ??

面8B00曲奇(应该是饼乾吧)

8C00巧克力曲奇8D00天妇罗8E00冰淇淋8F00蛋糕

9000巧克力蛋糕

9100消闲茶(轻松茶) 9200土司9300法国土司9400布丁

4001 cd1 4101 cd2 4201 cd3 4301 cd4 4401 cd5 4501

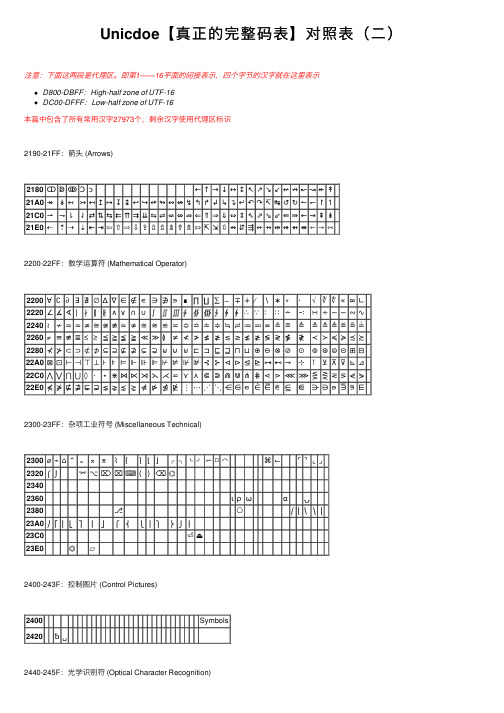

Unicdoe【真正的完整码表】对照表(二)

2C80-2CFF:古埃及语 (Coptic)

2C80 2CA0 2CC0 2CE0

Bohairic

2D00-2D2F:格鲁吉亚语补充 (Georgian Supplement)

2D00 2D20

Georgian ⴰⴱⴲⴳⴴⴵⴶⴷⴸⴹⴺⴻⴼⴽⴾⴿ

2D30-2D7F:提非纳文 (Tifinagh)

2D20

⧎⧏⧐⧑⧒⧓⧔⧕ ⧫

⧺⧻

2A00-2AFF:追加数学运算符 (Supplemental Mathematical Operator)

2A00 ⨀ ⨁ ⨂ 2A20

⨌⨍ ⨎ ⨏ ⨐ ⨑ ⨒ ⨓ ⨔ ⨕ ⨖ ⨗ ⨘ ⨙ ⨚ ⨛ ⨜ ⨯

2A40

2A60

⩽⩾⩿

2A80 ⪀ ⪁ ⪂ ⪃ ⪄ ⪅ ⪆ ⪇ ⪈ ⪉ ⪊ ⪋ ⪌ ⪍ ⪎ ⪏ ⪐ ⪑ ⪒ ⪓ ⪔ ⪕ ⪖ ⪗ ⪘ ⪙ ⪚ ⪛ ⪜ ⪝ ⪞ ⪟

23C0

⏎⏏

23E0

⏣⏥

⌘⌙ ⌜⌝ ⌞⌟

⍺⍽ ⎛⎜⎝ ⎞⎟

2400-243F:控制图片 (Control Pictures)

2400 2420 ␢ ␣

Symbols

2440-245F:光学识别符 (Optical Character Recognition)

2440

2460-24FF:封闭式字母数字 (Enclosed Alphanumerics)

2300-23FF:杂项工业符号 (Miscellaneous Technical)

2300 ⌀ ⌁ ⌂ ⌃ ⌄ ⌅ ⌆ ⌇ ⌈ ⌉ ⌊ ⌋ ⌌ ⌍ ⌎ ⌏ ⌐ ⌑ ⌒

2320 ⌠ ⌡

⌤⌥⌦⌧⌨⟨ ⟩ ⌫⌬

2340

2360

⍳⍴ ⍵

DC2952A Demo Manual

1Rev. 0DESCRIPTIONLT3093–20V, 200mA, Ultralow Noise, Ultrahigh PSRRNegative Linear RegulatorDemo circuit DC2952A features the LT ®3093, an ultralow noise, ultrahigh power supply rejection ratio (PSRR) negative low dropout (LDO) regulator . DC2952A oper-ates over an input range of –3.8V to –20V, and can deliver up to 200mA output current. It features ultralow noise (0.8µVRMS from 10Hz to 100kHz) and very high PSRR (73dB at 1MHz).The EN/UVLO of LT3093 is bidirectional and can be switched with either a positive or a negative voltage. LT3093 also offers programmable current limit function-ality by connecting a resistor from ILIM to GND. The VIOC tracking function controls an up-stream switching con-verter to maintain a constant voltage across the regulator and hence minimize power dissipation. The power good feedback (PGFB) pin is used to set a programmable power good threshold, and activates the fast start-up circuitry. ToAll registered trademarks and trademarks are the property of their respective owners.PERFORMANCE SUMMARYuse the power good function, connect an external voltage source at VEXT . If power good and fast start-up functional-ity are not needed, tie PGFB to IN.Built-in protection includes internal current limit with fold-back and thermal limit with hysteresis.The LT3093 datasheet gives a complete description of the part, operation and applications information. The datasheet must be read in conjunction with this Demo Manual for demonstration circuit DC2952A. The LT3093 is assembled in 12-lead MSOP and 3mm x 3mm DFN packages with an exposed pad on the bottom-side of the IC. Proper board layout is essential for maximum thermal performance.Design files for this circuit board are available .Specifications are at T A = 25°CPARAMETERCONDITIONSMIN TYPMAX UNITSInput Voltage Range (V IN )I OUT = 100mA, V OUT = –3.3V –20–3.8V Input Voltage Range (V IN )I OUT = 190mA, V OUT = –3.3V –13*–3.8V Output Voltage (V OUT )V IN = –5V, I OUT = 190mA –3.39–3.32–3.25V Shutdown Input Current (I IN )V EN = 0V, V IN = –5V3µA*The maximum input voltage for 100mA load current is set by a 60°C temperature rise of LT3093 on the demo circuit. Higher input voltage can berealized if larger copper area or forced-air cooling is applied. The output current is also limited by the input and output voltage differential; please refer to the datasheet for details.2Rev. 0QUICK START PROCEDUREDemonstration circuit DC2952A is easy to set up to evalu-ate the performance of the LT3093EDD. Refer to Figure 1 for proper measurement equipment setup and follow the procedure below:1. Connect a load between the V OUT and GND terminals.2. With power off, connect the input power supply to the V IN and GND terminals.3. Apply –3.8V across V IN to GND. The output voltage should be –3.32V ±3% (–3.39V to –3.25V)4. Vary V IN from –3.8V to –20V and vary the load from 0mA to 200mA.Note: The current limit may drop at high input-output differential voltage. Please refer to the datasheet for details. Make sure the power dissipation is below the thermal limit. 5. Apply a power source at VEXT . The PG pin voltage should be approximately equal to VEXT . 6. Refer to Application Notes AN70 and AN159 for mea-suring output noise and PSRR.Figure 1. Test procedure setup drawing for DC2952A*The maximum output current will be limited by internal current limit based on the input and output voltage differential. Please refer to the datasheet.3Rev. 0PCB LAYOUTPCB LAYOUT1. Best PSRR Performance: PCB Layout for Input T race For applications utilizing the LT3093 for post-regulating switching converters, placing a capacitor directly at the LT3093 input results in AC current (at the switching fre-quency) flowing near the LT3093. Without careful atten-tion to PCB layout, this relatively high frequency switch-ing current generates an electromagnetic field (EMF) that couples to the LT3093 output, thereby degrading its effective PSRR. While highly dependent on the PCB, the switching pre-regulator , and the input capacitor size among other factors, the PSRR degradation can easily be 30dB at 1MHz. This degradation is present even if the LT3093 is de-soldered from the board, because it effec-tively degrades the PSRR of the PC board itself. While negligible for conventional low PSRR LDOs, the LT3093’s ultrahigh PSRR requires careful attention to higher order parasitics in order to realize the full performance offered by the regulator .The LT3093 demo board alleviates this degradation in PSRR by using a specialized layout technique. In Figure 2, the input trace (V IN ) is highlighted in red, and in Figure 3 the return path (GND) is also highlighted together with input capacitor C1. Normally when an AC voltage is applied to the input of the board, AC current flows along this path, thus generating EMF . This EMF couples to output capacitor C2 and the related traces, making the PSRR appear worse than it actually is. With the input trace directly above the return path, the EMFs are in opposite directions, and consequently cancel each other out. Make sure these traces exactly overlap each other to maximize the cancellation effect and thus provide the maximum PSRR offered by the regulator .2. Best AC Performance: PCB Layout for Output Capacitors C2For ultrahigh PSRR performance, the LT3093 bandwidth is quite high (~1MHz), making it very close to the output capacitor’s self-resonance frequency (~1.6MHz). There-fore, it is very important to avoid adding extra imped-ance (ESL & ESR) outside the feedback loop. To that end, minimize the effects of PCB trace and solder inductance by Kelvin connecting OUTS and SET pin capacitor GND directly to output capacitors (C2) terminals using split capacitor techniques. With only small AC current flowing through these connections, the impact of solder joint/PCB trace inductance on stability is eliminated. While the LT3093 is robust enough not to oscillate if the recom-mended layout is not followed, phase/gain margin and stability will degrade.Figure 2. Bottom Layer of DC2952AFigure 3. Layer 3 of DC2952A4Rev. 0PARTS LISTITEM QTY REFERENCE PART DESCRIPTIONMANUFACTURER/PART NUMBERRequired Circuit Components11CIN CAP , ALUM, 22µF, 35V, 5X5.4MM SUN ELECTRONIC INDUSTRIES CORP , 35CE22BSS 23C1,C2,C4CAP , X7R, 4.7µF, 25V, 10% 1206MURATA, GRM31CR71E475KA88L 31R1RES, CHIP , 200k, 1/10W, 5% 0603VISHAY, CRCW0603200KJNEA 41R2RES, CHIP , 100k, 1/10W, 1% 0603VISHAY, CRCW0603100KFKEA 51R3RES, CHIP , 33.2k, 1/10W, 1% 0603VISHAY, CRCW060333K2FKEA 61R5RES, CHIP , 453k, 1/10W, 1% 0603VISHAY, CRCW0603453KFKEA 71R6RES, CHIP , 49.9k, 1/10W, 1% 0603VISHAY, CRCW060349K9FKEA 81R7RES., CHIP , 9.76K, 1/10W, 1% 0603VISHAY, CRCW06039K76FKEA 91U1IC, LT3093EDD, 12DFN ANALOG DEVICES, LT3093EDD#PBFAdditional Demo Board Circuit Components10C3, C5 (OPT)CAP , OPTION, 120620R4 (OPT)RES, OPTION, 0603Hardware: For Demo Board Only18E1 TO E8TESTPOINT , TURRET , 0.094" pbf MILL-MAX, 2501-2-00-80-00-00-07-022J1, J2CONN, BNC, 5 PINS CONNEX, 11240434MH1 TO MH4STAND-OFF , NYLON 6.4mmWURTH ELEKTRONIK, 702931000PCB LAYOUT3093 F03Figure 4. C2 and C SET connections for best performanceFigure 5. Split Pads for Output Capacitors on Top Layer of DC2952ASCHEMATIC DIAGRAM5Rev. 06Rev. 0ANALOG DEVICES, INC. 201906/19ESD CautionESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.Legal Terms and ConditionsBy using the evaluation board discussed herein (together with any tools, components documentation or support materials, the “Evaluation Board”), you are agreeing to be bound by the terms and conditions set forth below (“Agreement”) unless you have purchased the Evaluation Board, in which case the Analog Devices Standard Terms and Conditions of Sale shall govern. Do not use the Evaluation Board until you have read and agreed to the Agreement. Your use of the Evaluation Board shall signify your acceptance of the Agreement. This Agreement is made by and between you (“Customer”) and Analog Devices, Inc. (“ADI”), with its principal place of business at One Technology Way, Norwood, MA 02062, USA. Subject to the terms and conditions of the Agreement, ADI hereby grants to Customer a free, limited, personal, temporary, non-exclusive, non-sublicensable, non-transferable license to use the Evaluation Board FOR EVALUATION PURPOSES ONL Y. Customer understands and agrees that the Evaluation Board is provided for the sole and exclusive purpose referenced above, and agrees not to use the Evaluation Board for any other purpose. Furthermore, the license granted is expressly made subject to the following additional limitations: Customer shall not (i) rent, lease, display, sell, transfer , assign, sublicense, or distribute the Evaluation Board; and (ii) permit any Third Party to access the Evaluation Board. As used herein, the term “Third Party” includes any entity other than ADI, Customer , their employees, affiliates and in-house consultants. The Evaluation Board is NOT sold to Customer; all rights not expressly granted herein, including ownership of the Evaluation Board, are reserved by ADI. CONFIDENTIALITY. This Agreement and the Evaluation Board shall all be considered the confidential and proprietary information of ADI. Customer may not disclose or transfer any portion of the Evaluation Board to any other party for any reason. Upon discontinuation of use of the Evaluation Board or termination of this Agreement, Customer agrees to promptly return the Evaluation Board to ADI. ADDITIONAL RESTRICTIONS. Customer may not disassemble, decompile or reverse engineer chips on the Evaluation Board. Customer shall inform ADI of any occurred damages or any modifications or alterations it makes to the Evaluation Board, including but not limited to soldering or any other activity that affects the material content of the Evaluation Board. Modifications to the Evaluation Board must comply with applicable law, including but not limited to the RoHS Directive. TERMINATION. ADI may terminate this Agreement at any time upon giving written notice to Customer . Customer agrees to return to ADI the Evaluation Board at that time. LIMITATION OF LIABILITY. THE EVALUATION BOARD PROVIDED HEREUNDER IS PROVIDED “AS IS” AND ADI MAKES NO WARRANTIES OR REPRESENTATIONS OF ANY KIND WITH RESPECT TO IT . ADI SPECIFICALL Y DISCLAIMS ANY REPRESENTATIONS, ENDORSEMENTS, GUARANTEES, OR WARRANTIES, EXPRESS OR IMPLIED, RELATED TO THE EVALUATION BOARD INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, TITLE, FITNESS FOR A PARTICULAR PURPOSE OR NONINFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS. IN NO EVENT WILL ADI AND ITS LICENSORS BE LIABLE FOR ANY INCIDENTAL, SPECIAL, INDIRECT , OR CONSEQUENTIAL DAMAGES RESUL TING FROM CUSTOMER’S POSSESSION OR USE OF THE EVALUATION BOARD, INCLUDING BUT NOT LIMITED TO LOST PROFITS, DELAY COSTS, LABOR COSTS OR LOSS OF GOODWILL. ADI’S TOTAL LIABILITY FROM ANY AND ALL CAUSES SHALL BE LIMITED TO THE AMOUNT OF ONE HUNDRED US DOLLARS ($100.00). EXPORT . Customer agrees that it will not directly or indirectly export the Evaluation Board to another country, and that it will comply with all applicable United States federal laws and regulations relating to exports. GOVERNING LAW . This Agreement shall be governed by and construed in accordance with the substantive laws of the Commonwealth of Massachusetts (excluding conflict of law rules). Any legal action regarding this Agreement will be heard in the state or federal courts having jurisdiction in Suffolk County, Massachusetts, and Customer hereby submits to the personal jurisdiction and venue of such courts. The United Nations Convention on Contracts for the International Sale of Goods shall not apply to this Agreement and is expressly disclaimed.。

数学六年级下册第34课时《鸽巢问题-例2》课件

课堂小结 通过这节课的学习, 你有什么收获?

鸽巢问题的一般规律,可以用假设 法,列式计算

a÷n=b……c(c≠0), 至少数=b+1。

没有余数:至少数=b

作业:

(1)把17支铅笔放进4个文具盒里,至少 有一个文具盒里放几支?

(2)幼儿园里有80个小朋友,各种玩具共 有330件。把这些玩具分给小朋友,是否 有人会得到5件或5件以上的玩具?

把两种颜色看成两个抽屉,正方体的6个 面看成分放的物体,至少3个面要涂上相同的 颜色。

6÷2=3(个)

(教材P71 练习十三第4题)

4.把红、蓝、黄三种颜色的筷子各 3根混在一起。如果让你闭上眼睛, 每次最少拿出几根才能保证一定有 2根同色的筷子?如果要保证有2双 不同色的筷子呢?(指一双筷子为 其中一种颜色,另一双筷子为另一 种颜色。)

13÷12=1(人)……1(人) 1+1=2(人)

(教材P71 练习十三2) 2.张叔叔参加飞镖比赛,投了5镖,

成绩是41环。张叔叔至少有一镖不低于9 环。为什么?

41÷5=8(环)……1(环) 8+1=9(环)

(教材P71 练习十三第3题)

3.给一个正方体木块的6个面分别涂上蓝、黄两种颜 色。不论怎么涂至少有3个面涂的颜色相同。为什么?

人教版六年级数学下册

数学广角—鸽巢问题

第 2 课时

知识回顾:

把n+1个物体放进n个抽屉,能得到 什么结论?

尝试探究:

例2 : 把7本书放在3个抽屉里,不管怎么放,

总有一个抽屉里至少放进3本书。为什么?

例2 : 把7本书放在3个抽屉里,不管怎么放, 总有一个抽屉里至少放进3本书。为什么?

自主探究: 用自己喜欢的、能理解的方法进行说理。

台达 vfd-v变频器说明书

第五章功能•參數說明00系統參數機種識別出廠設定值工廠設定設定範圍依機種顯示額定電流顯示出廠設定值工廠設定設定範圍依機種顯示230V系列功率[馬力] 0.75[1]1.5[2]2.2[3]3.7[5]5.5[7.5]7.5[10]11[15]15[20]18.5[25]22[30]30[40]37[50]45[60]55[75]75[100]機種代碼 4 6 8 10 12141618202224 26 28 3032定轉矩額定電流5 7.5 11 17 253349657590120 146 182 220300變轉矩額定電流6.3 9.4 13.8 21.331.341.361.381.393.8113150 183 228 275375最高載波頻率15kHz 10kHz6kHz460V系列功率[馬力] 0.75[1]1.5[2]2.2[3]3.7[5]5.5[7.5]7.5[10]11[15]15[20]18.5[25]22[30]30[40]37[50]45[60]55[75]75[100]機種代碼 5 7 09 11 13151719212325 27 29 3133定轉矩額定電流3 4.2 6 8.5 13182432384560 73 91 110150變轉矩額定電流3.8 5.3 7.5 10.616.322.5304047.556.375 91.3 113.8138188最高載波頻率 15kHz 10kHz6kHz00-00參數決定驅動器容量,在出廠時已設定於本參數內。

同時,可讀取參數(00-01)的電流值是否為該機種的額定電流。

參數00-00對應參數00-01電流的顯示值。

出廠設定為定轉矩額定,若需使用變轉矩額定請設定參數00-12。

參數重置設定出廠設定值0設定內容10 參數重置(基底頻率為60Hz)9參數重置(基底頻率為50Hz)位元設定Bit 0 1 參數不可讀20 1 Bit11頻率、轉矩命令不可改(僅限於PU05) 21 2 Bit21數位操作器(PU05)不能運作(Run)22 4位元設定的輸入方法:本系列有些功能的參數設定是採用位元設定法來設定參數,此法的優點是設定一個數值可重覆組合多項功能,但設定時需先將二進位的編碼自行轉換成十進位數值後再輸入此參數。

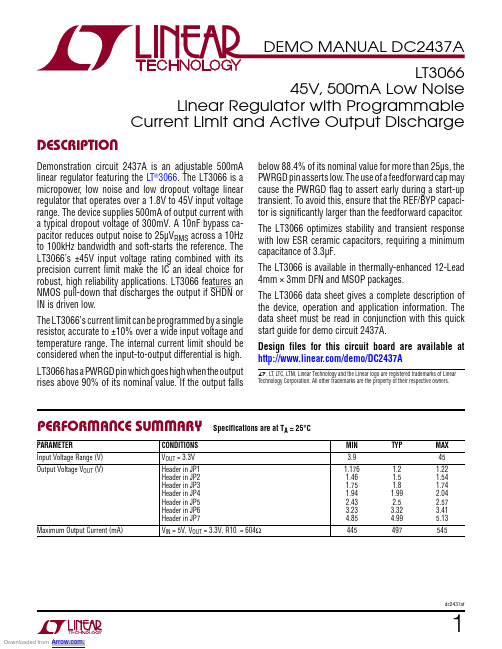

DC2535A 应用手册

1Rev. 0DESCRIPTIONLT8653SDual Channel 2A, 42V, Synchronous Step-DownSilent Switcher with 6.2μA Quiescent CurrentDemonstration circuit 2535A is a 42V, dual channel, 2A synchronous step-down regulator featuring the L T ®8653S . The LT8653S is a compact, high efficiency, high speed syn-chronous monolithic step-down switching regulator which features the second generation Silent Switcher ® technology that minimizes EMI and reduces PCB layout sensitivity. The demo board is designed for two outputs: 5V and 3.3V from a 5.5V to 42V input. Each output can source up to 2A continuous current at the same time. The wide input range allows a variety of input sources, such as automo-tive batteries and industrial supplies. The integrated power switches and other necessary circuitry reduce the external component count and simplify design. Selectable spread spectrum mode of operation can further improve EMI/EMC performance. Ultralow quiescent current in Burst Mode ® operation achieves high efficiency at very light loads.The DC2535A demo board is 3" by 3" in size and has four layers with 2oz copper on the outer layers and 1oz cop-per on the inner layers. The DC2535A operates at 2MHz switching frequency by default to minimize solution size. The LT8653S is assembled in a small thermally enhanced 4mm × 3mm LQFN package. The IC temperature rises about 50°C when both channels operate at full load, 2A each, with the default switching frequency of 2MHz.The jumper JP2 on the demo board determines the con-figuration of the SYNC pin of the LT8653S. By default, the SYNC pin on the demo board is grounded for lowAll registered trademarks and trademarks are the property of their respective owners.PERFORMANCE SUMMARYripple Burst Mode operation. Moving JP2 to FCM W/SSM enables the spread spectrum mode of operation by tying the SYNC pin to VCC pin. To synchronize to an external clock, move JP2 to FCM W/O SSM OR SYNC position and apply the external clock on the SYNC turret.The jumpers JP3 and JP4 on the demo board determine the configuration of the output voltage select bit pins D0 and D1. On the DC2535A, the D0 and D1 pins are by default floating. This combination connects internal feed-back resistor divider between the FB1/FB2 pins and the error amplifier which means that FB1 and FB2 pins are regulated to 5V and 3.3V respectively. On the DC2535A, FB1/FB2 pins are by default connected through 0Ω resis-tors to the output nodes. Refer to the LT8653S data sheet for more information on the D0 and D1 pin settings.The demo board has an EMI filter installed. The EMI per-formance of the demo board (with EMI filter) is shown in Figure 1 and Figure 2. The black lines in Figure 2 are CISPR 25 class 5 limits. To achieve EMI/EMC performance as shown in Figure 2, the input EMI filter is required and the input voltage should be applied at VEMI terminal.The LT8653S data sheet gives a complete description of the part, operation and application information. The data sheet must be read in conjunction with this manual for demo circuit 2535A.Design files for this circuit board are available .Specifications are at T A = 25°CSYMBOL PARAMETER CONDITIONSMIN TYPMAX UNITSV IN Input Supply Range 5.542V V OUT1Output1 Voltage4.855.2V I OUT1Maximum Output1 Current 2A V OUT2Output2 Voltage3.168 3.33.432V I OUT2Maximum Output2 Current 2A f SW Switching Frequency 1.852 2.15MHz EFEEfficiency at DCV IN = 12V, I OUT1 = 1A, I OUT2 = 1A93.1%Figure 2. Radiated EMI Performance (CISPR 25 Radiated Emission Test with Class 5 Peak Limits)2Rev. 03Rev. 0QUICK START PROCEDUREFigure 3. Proper Measurement Equipment SetupFigure 4. Measure Output RippleDemonstration circuit 2535A is easy to set up to evalu-ate the performance of the LT8653S. Refer to Figure 3 for proper measurement equipment setup and follow the procedure below:NOTE: When measuring the input or output voltage rip-ple, care must be taken to avoid long ground lead on the oscilloscope probe. Measure the output voltage ripple by touching the probe tip directly across the VOUT and GND terminals. See Figure 4 for the proper measurement technique.1. Check that JP3 and JP4 are placed on the FLOAT position.2. Check that JP2 are placed on BURST position.3. With power off, connect the input power supply to VEMI and GND. If the EMI/EMC performance is not important, connect the input power supply to VIN and GND.4. With power off, connect the loads from VOUT1 to GND, and VOUT2 to GND.5. Turn on the power at the input.NOTE: make sure that the input voltage never exceeds 42V.6. Check for proper output voltages: V OUT1 = 5V, V OUT2 = 3.3V. NOTE: If there is no output, temporarily disconnect the load to make sure that the load is not set too high.7. Once the proper output voltages are established, adjust the load within the operating ranges and observe the output voltage regulation, ripple voltage, efficiency and other parameters.8. An external clock can be added to the SYNC terminal when SYNC function is used (JP2 on the FCM W/O SSM OR SYNC position). Please make sure that R12 resistor should be chosen to set the LT8653S switching frequency equal to or below the lowest synchronization frequency. JP2 can also set the LT8653S in spread spectrum mode (JP2 on the FCM W/SSM position).OUTPARTS LISTITEM QTY REFERENCE PART DESCRIPTION MANUFACTURER/PART NUMBERRequired Circuit Components11C2CAP., 4.7µF, X7R, 50V, 10%, 1206MURATA, GRM31CR71H475KA12L24C5, C9, C17, C23CAP., 1µF, X7R, 10V, 10%, 0603MURATA, GRM188R71A105KA61D32C6, C12CAP., 10µF, X5R, 10V, 10%, 0603TDK, C1608X5R1A106K080AC41C10CAP., 47µF, X5R, 10V, 10%, 1210MURATA, GRM32ER61A476KE20K51C11CAP., 100µF, X5R, 10V, 20%, 1210MURATA, GRM32ER61A107ME20L62C15, C16CAP., 10nF, X7R, 25V, 10%, 0603MURATA, GRM188R71E103KA01D72L1, L2INDUCTOR, 2.2µH, XFL4020COILCRAFT, XFL4020-222ME81R1RES., 1M, 1/10W, 1%, 0603VISHAY, CRCW06031M00FKEA94R4, R5, R13, R14RES., 0Ω, 1/10W, 0603VISHAY, CRCW06030000Z0EA102R10, R11RES., 100k, 1/10W, 1%, 0603VISHAY, CRCW0603100KFKEA111R12RES., 15k, 1/10W, 1%, 0603VISHAY, CRCW060315K0FKEA121U1I.C., STEP-DOWN SWITCHER, LQFN ANALOG DEVICES, LT8653SEV#PBF Additional Demo Board Circuit Components11C1CAP., ALUM, 22µF, 63V, 20%SUN ELECT., 63CE22BS20C7, C8CAP., OPTION, 060332C3, C4 (OPT)CAP., 0.1µF, X7R, 50V, 10%, 0402MURATA, GRM155R71H104KE14J40C13, C14, C21, C22 (OPT)CAP., OPTION, 060353C18, C25, C26CAP., 1µF, X5R, 50V, 10% 0603MURATA, GRM188R61H105KAALD62C19, C20CAP., 10µF, X7R, 50V, 10% 1210MURATA, GRM32ER71H106KA12L71FB1CHIP BEAD, 0805TDK, MPZ2012S101A81L3INDUCTOR, 220nH VISHAY, IHLP1616ABERR22M0191R2RES., 0Ω, 1/10W, 0603VISHAY, CRCW06030000Z0EA100R3, R6, R7, R8, R9 (OPT)RES, OPTION, 0603Hardware: For Demo Board Only116E1-E16TESTPOINT, TURRET, 0.094"MILL-MAX, 2501-2-00-80-00-00-07-0 21JP1HEADER 3 PIN 0.079 SINGLE ROW WURTH ELEKTRONIK, 6200031112133JP2, JP3, JP4HEADER 3 PIN 0.079 DOUBLE ROW WURTH ELEKTRONIK, 6200062112144xJP1, xJP2, xJP3, xJP4SHUNT, 0.079" CENTER WURTH ELEKTRONIK, 6080021342154MH1-MH4STAND-OFF, NYLON, 9.5mm WURTH ELEKTRONIK, 7029330004Rev. 05Rev. 0Information furnished by Analog Devices is believed to be accurate and reliable. However , no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.SCHEMATIC DIAGRAM1. A L L R E S I S T O R S A R E 0603. A L L C A P A C I T O R S A R E 0603.N O T E : U N L E S S O T H E R W I S E S P E C I F I E DS Y N CG N DP G 2V C CP G 1V O U T 23.3V / 2AV I N5.3V - 42VE NJ P 3D 0V E M I 5.3V - 42VC L K O U TV B I A SS S 1V O U T 15V / 2AG N S S 2G N D6Rev. 0ANALOG DEVICES, INC. 201912/19ESD CautionESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.Legal Terms and ConditionsBy using the evaluation board discussed herein (together with any tools, components documentation or support materials, the “Evaluation Board”), you are agreeing to be bound by the terms and conditions set forth below (“Agreement”) unless you have purchased the Evaluation Board, in which case the Analog Devices Standard Terms and Conditions of Sale shall govern. Do not use the Evaluation Board until you have read and agreed to the Agreement. Your use of the Evaluation Board shall signify your acceptance of the Agreement. This Agreement is made by and between you (“Customer”) and Analog Devices, Inc. (“ADI”), with its principal place of business at One Technology Way, Norwood, MA 02062, USA. Subject to the terms and conditions of the Agreement, ADI hereby grants to Customer a free, limited, personal, temporary, non-exclusive, non-sublicensable, non-transferable license to use the Evaluation Board FOR EVALUATION PURPOSES ONL Y. Customer understands and agrees that the Evaluation Board is provided for the sole and exclusive purpose referenced above, and agrees not to use the Evaluation Board for any other purpose. Furthermore, the license granted is expressly made subject to the following additional limitations: Customer shall not (i) rent, lease, display, sell, transfer , assign, sublicense, or distribute the Evaluation Board; and (ii) permit any Third Party to access the Evaluation Board. As used herein, the term “Third Party” includes any entity other than ADI, Customer , their employees, affiliates and in-house consultants. The Evaluation Board is NOT sold to Customer; all rights not expressly granted herein, including ownership of the Evaluation Board, are reserved by ADI. CONFIDENTIALITY. This Agreement and the Evaluation Board shall all be considered the confidential and proprietary information of ADI. Customer may not disclose or transfer any portion of the Evaluation Board to any other party for any reason. Upon discontinuation of use of the Evaluation Board or termination of this Agreement, Customer agrees to promptly return the Evaluation Board to ADI. ADDITIONAL RESTRICTIONS. Customer may not disassemble, decompile or reverse engineer chips on the Evaluation Board. Customer shall inform ADI of any occurred damages or any modifications or alterations it makes to the Evaluation Board, including but not limited to soldering or any other activity that affects the material content of the Evaluation Board. Modifications to the Evaluation Board must comply with applicable law, including but not limited to the RoHS Directive. TERMINATION. ADI may terminate this Agreement at any time upon giving written notice to Customer . Customer agrees to return to ADI the Evaluation Board at that time. LIMITATION OF LIABILITY. THE EVALUATION BOARD PROVIDED HEREUNDER IS PROVIDED “AS IS” AND ADI MAKES NO WARRANTIES OR REPRESENTATIONS OF ANY KIND WITH RESPECT TO IT . ADI SPECIFICALL Y DISCLAIMS ANY REPRESENTATIONS, ENDORSEMENTS, GUARANTEES, OR WARRANTIES, EXPRESS OR IMPLIED, RELATED TO THE EVALUATION BOARD INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, TITLE, FITNESS FOR A PARTICULAR PURPOSE OR NONINFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS. IN NO EVENT WILL ADI AND ITS LICENSORS BE LIABLE FOR ANY INCIDENTAL, SPECIAL, INDIRECT , OR CONSEQUENTIAL DAMAGES RESUL TING FROM CUSTOMER’S POSSESSION OR USE OF THE EVALUATION BOARD, INCLUDING BUT NOT LIMITED TO LOST PROFITS, DELAY COSTS, LABOR COSTS OR LOSS OF GOODWILL. ADI’S TOTAL LIABILITY FROM ANY AND ALL CAUSES SHALL BE LIMITED TO THE AMOUNT OF ONE HUNDRED US DOLLARS ($100.00). EXPORT . Customer agrees that it will not directly or indirectly export the Evaluation Board to another country, and that it will comply with all applicable United States federal laws and regulations relating to exports. GOVERNING LAW . This Agreement shall be governed by and construed in accordance with the substantive laws of the Commonwealth of Massachusetts (excluding conflict of law rules). Any legal action regarding this Agreement will be heard in the state or federal courts having jurisdiction in Suffolk County, Massachusetts, and Customer hereby submits to the personal jurisdiction and venue of such courts. The United Nations Convention on Contracts for the International Sale of Goods shall not apply to this Agreement and is expressly disclaimed.。

DC2358A 手册说明书

DESCRIPTION Isolated μModule DC/DC Converterwith LDO RegulatorThe Demo Circuit 2358A is a 2kV AC isolated flyback μModule® DC/DC converter with LDO post regulator featur-ing the LTM8068. The demo circuit is designed for a 5.6V flyback output and a 5V post regulator output from a 4.5V to 40V input. The current capability of the 5.6V flyback output varies with input voltage from about 200mA at 4.5V IN to about 460mA at 40V IN. The current capability of the 5V LDO output is limited by either the current capabil-ity of V OUT1 minus V OUT1 loading or the 300mA current limit on the LDO post regulator itself. Figure 1 shows the maximum output current on V OUT1 when V OUT2 is notloaded, and V OUT2 when V OUT1 is unloaded. V OUT2 is the LDO post regulator from V OUT1.L, L T, L TC, L TM, Linear Technology, the Linear logo and µModule are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners. The two-stage converter provides an isolated flyback output as well as a low-noise LDO output. Figure 2 shows the output noise spectrum on the flyback output and Figure 3 shows the output noise spectrum on the LDO output. The LTM8068 data sheet gives complete description of the device, operation and application information. The data sheet must be read in conjunction with this quick start guide for demo circuit 2358A.Design files for this circuit board are available at /demo/DC2358ABOARD PHOTO1dc2358af2dc2358afPERFORMANCE SUMMARYPARAMETER CONDITIONSMINTYPMAX UNITSMinimum Input Voltage 4.5V Maximum Input Voltage 40V Output Voltage V OUT1 V IN = 4.5V to 40V 5.3 5.6 5.9V Output Voltage V OUT2V IN = 4.5V to 40V4.855 5.15V Voltage Ripple V OUT1V IN = 12V, I OUT1 = 200mA, I OUT2 = 0mA 25mV Voltage Ripple V OUT2V IN = 12V, I OUT1 = 0mA, I OUT2 = 200mA1mVDemo circuit 2358A is easy to set up to evaluate the per-formance of the LTM8068. Refer to Figure 4 for proper measurement equipment setup and follow the procedure below:NOTE: When measuring the input or output voltage ripple, care must be taken to avoid a long ground lead on the oscilloscope probe. Measure the input or output voltage ripple by touching the probe tip directly across the V IN and GND or V OUT and V OUTN terminals. See Figure 5 for proper scope probe technique.1. With power off, connect the input power supply to V IN and GND.2. Turn on the power at the input.NOTE. Make sure that the input voltage does notexceed 40V.3. Check for the proper output voltages. (For OUT1, check the voltage between V OUT1 and V OUTN . For OUT2, check the voltage between V OUT2 and V OUTN .) NOTE: If there is no output, temporarily disconnect the load to make sure that the load is not set too high.4. Once the proper output voltages are established, adjust the load within the operating range and observe the output voltage regulation, ripple voltage, efficiency and other parameters.QUICK START PROCEDURESpecifications are at T A = 25°CFigure 1. Maximum Output Current vs V IN : 5.6V OUT1 Flyback Output with V OUT2 Unloaded; 5V OUT2 LDO output with V OUT1 UnloadedFigure 2. V OUT1 Output Noise Spectrum with I OUT1 at 200mA and V IN at 12V (V OUT2 Has No Extra Load)Figure 3. V OUT2 Output Noise Spectrum with I OUT2 at 200mA and V IN at 12V (V OUT1 Has No Extra Load)V IN (V)M A X I M U M L O A D C U R R E N T (m A )5001003004002000dc2358 F01FREQUENCY (MHz)I N T E N S I T Y (d B m )0–80–40–20–60–1002.5 4.51.53.5dc2358 F025.02.0 4.01.03.00.5FREQUENCY (MHz)I N T E N S I T Y (d B m )–80–40–20–60–1002.5 4.51.53.5dc2358 F035.02.0 4.01.03.00.5QUICK START PROCEDUREFigure 4. DC2358A Proper Equipment SetupINPUT OR OUTPUT CAPACITORFigure 5. Measuring Input or Output Ripple3dc2358afPARTS LISTITEM QTY REFERENCE PART DESCRIPTION MANUFACTURER/PART NUMBERRequired Circuit Components11CIN1CAP., ALUM, 22µF, 50V, 6.6x6.6mm NICHICON, UUD1H220MCL1GS21C1CAP., CER., 10µF, X7R, 50V, 10%, 1210MURATA, GRM32ER71H106KA12L32C2, C3CAP., CER., 4.7µF, X5R, 10V, 10%, 0603MURATA, GRM188R61A475KE15D41C4CAP., CER., 47µF, X5R, 10V, 10%, 1206MURATA, GRM31CR61A476KE15L51C5CAP., CER., 22µF, X5R, 6.3V, 20%, 0805MURATA, GRM21BR60J226ME39L61C8CAP., CER., 0.01µF, X7R, 25V, 10%, 0603MURATA, GRM188R71E103KA01D71C10CAP., CER., 10pF, NP0, 50V, 5%, 0603MURATA, GRM1885C1H100JA01D81R1RES, 200k, 1/10W, 1%, 0603VISHAY, CRCW0603200KFKEA91R2RES, 95.3k, 1/10W, 1%, 0603VISHAY, CRCW060395K3FKEA101R3RES, 7.32k, 1/10W, 1%, 0603VISHAY, CRCW06037K32FKEA111R4RES, 604Ω, 1/8W, 1%, 0805VISHAY, CRCW0805604RFKEA121R5RES, 162k, 1/10W, 1%, 0603VISHAY, CRCW0603162KFKEA131U1I.C., LTM8068EY#PBF 9 × 11.25 × 4.92 BGA LINEAR TECH., LTM8068EY#PBFAdditional Demo Board Circuit Components10C6 (OPT)CAP., 1210 (OPT)20C7 (OPT)CAP., 0805 (OPT)30C9 (OPT)CAP., 1808 (OPT)40L1 (OPT)IND., 10µH, XFL3012 (OPT)Hardware: For Demo Board Only16E1-E6TESTPOINT, TURRET, 0.094" pbf MILL-MAX, 2501-2-00-80-00-00-07-021E7TEST POINT, TURRET, 0.064" MTH HOLE MILL-MAX, 2308-2-00-80-00-00-07-034MH1-MH4STAND-OFF, NYLON 0.375" SNAP ON KEYSTONE, 88324dc2358af5dc2358afI nformation furnished by Linear Technology Corporation is believed to be accurate and reliable. However , no responsibility is assumed for its use. Linear Technology Corporation makes no representa-tion that the interconnection of its circuits as described herein will not infringe on existing patent rights.SCHEMATIC DIAGRAM6dc2358afLinear Technology Corporation1630 McCarthy Blvd., Milpitas, CA 95035-7417(408) 432-1900 ● FAX : (408) 434-0507 ● www.linear .com© LINEAR TECHNOLOGY CORPORA TION 2016LT 0216 • PRINTED IN USADEMONSTRATION BOARD IMPORTANT NOTICELinear Technology Corporation (LTC) provides the enclosed product(s) under the following AS IS conditions:This demonstration board (DEMO BOARD) kit being sold or provided by Linear Technology is intended for use for ENGINEERING DEVELOPMENT OR EVALUATION PURPOSES ONLY and is not provided by LTC for commercial use. As such, the DEMO BOARD herein may not be complete in terms of required design-, marketing-, and/or manufacturing-related protective considerations, including but not limited to product safety measures typically found in finished commercial goods. As a prototype, this product does not fall within the scope of the European Union directive on electromagnetic compatibility and therefore may or may not meet the technical requirements of the directive, or other regulations.If this evaluation kit does not meet the specifications recited in the DEMO BOARD manual the kit may be returned within 30 days from the date of delivery for a full refund. THE FOREGOING WARRANTY IS THE EXCLUSIVE WARRANTY MADE BY THE SELLER TO BUYER AND IS IN LIEU OF ALL OTHER WARRANTIES, EXPRESSED, IMPLIED, OR STATUTORY, INCLUDING ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR ANY PARTICULAR PURPOSE. EXCEPT TO THE EXTENT OF THIS INDEMNITY, NEITHER PARTY SHALL BE LIABLE TO THE OTHER FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES.The user assumes all responsibility and liability for proper and safe handling of the goods. Further, the user releases LTC from all claims arising from the handling or use of the goods. Due to the open construction of the product, it is the user’s responsibility to take any and all appropriate precautions with regard to electrostatic discharge. Also be aware that the products herein may not be regulatory compliant or agency certified (FCC, UL, CE, etc.).No License is granted under any patent right or other intellectual property whatsoever. LTC assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or any other intellectual property rights of any kind.LTC currently services a variety of customers for products around the world, and therefore this transaction is not exclusive .Please read the DEMO BOARD manual prior to handling the product . Persons handling this product must have electronics training and observe good laboratory practice standards. Common sense is encouraged .This notice contains important safety information about temperatures and voltages. For further safety concerns, please contact a LTC application engineer.Mailing Address:Linear Technology 1630 McCarthy pitas, CA 95035Copyright © 2004, Linear Technology Corporation。

Solid State Broadband High Power Amplifier 1191 -

Solid State Broadband High Power Amplifier2500 – 6000 MHz / 100 WattsThe BBM5K8CKT (SKU 1191) is a 2500 to 6000 MHz amplifier which is guaranteed to deliver 100W minimum output power and related RF performance under all specified temperature and environmental conditions. Typical power output is 125W and other typical performance parameters are also listed as a guide for consideration, but not guaranteed. This amplifier is suitable for broadband mobile jamming and band specific high power linear applications in the S and C frequency bands. This compact module utilizes the latest high power RF GaN transistors and also features built in control and monitoring, with protection functions to ensure high availability.▪ Solid-state Class AB linear design ▪ Instantaneous ultra broadband▪ Suitable for CW, AM, and FM (Consult factory for other modulation types) ▪ Small and lightweight▪ 50 ohm input/output impedance ▪ High reliability and ruggedness▪ Built-in control, monitoring and protection circuits ▪ RS485 serial interface for monitoring and control******************************DC , Over Temperature and Environmental Conditions, as specified. Min Typ Max Operating frequency BW MHz 2500 6000 Peak output power P SAT W CW input signal 100 125Gain, small signal G SS dB Measured with VNA in swept frequency mode at -20dBmCW. Input power calibrated / measured at the amplifier input port. Variable attenuator set to nominal attenuation.55 6065 Gain flatness small signal ΔG SS dB Test conditions the same as G SS ±5 Gain adjustment range G ADJ dB Test conditions the same as G SS 15 Gain adjustment step size G STEP dB Test conditions the same as G SS 0.5 Maximum input powerwithout damageP IN, Max dBm CW input signal for unlimited duration.20 Input return loss IRL dB Measured with VNA in swept frequency mode at -20dBm and 0dBm CW. Input power calibrated / measured at theamplifier input port. Variable attenuator set to nominal attenuation.-10 Noise figure NF dB Variable attenuator set to nominal attenuation.20 2nd harmonics 2nddBc Variable attenuator set to nominal attenuation. CW signal source at an output power of 100W.-10 3rd harmonics 3rddBc Variable attenuator set to nominal attenuation. CW signal source at an output power of 100W.-20Spurious Spur dBc Variable attenuator set to nominal attenuation. CW signal source of 0dBm at the input to the amplifier. Input power is calibrated / measured at the amplifier input port.Spurious defined as any non-harmonic amplifier output.Spurious measured in a 1kHz resolution bandwidth,10kHz video bandwidth. Specifications apply at offsets of greater than or equal to +/- 10kHz from the RF carrier. Maximum measurement frequency is 6.5GHz.-60Operating voltage V DC V Note: Output power capabilities and gain will vary withvoltage.26 2832 Current consumption I DC A Variable attenuator set to nominal attenuation.Measurement at an output power of 100W with a CW source.22Stock No. 1191D.S. Rev. 1.32 / 12-18-201319812500 – 6000 MHz / 100 WattsPA enable / Disable time T ON/OFF uSec Variable attenuator set to nominal attenuation.Measurement with 0dBm CW signal presented to theinput of the amplifier. Rise and fall times of amplifieroutput envelope recorded. Rise and fall times at 10% /90% of the output power in linear scale. PA Enable /Disable signal set to 10kHz repetition rate and 50% dutycycle.1PA PROTECTION / RUGGEDNESSThe PA includes protection circuits for:•Over temperature•Over voltage•Reverse polarity•Over currentIn addition to protection circuits, the PA will withstand full reflection at the RF output port at any angle for up to 1 minute at P3dB. ENVIRONMENTAL SPECIFICATIONSOperating Case Temperature T C-40 +85 °C Storage Temperature T STG-40 +85 °C Relative Humidity (non-condensing) RH 95 % Altitude (MIL-STD-810F Method 500.4) ALT 30,000 Feet Vibration/ShockMIL-STD-810F Method 514.5/516.5 – Proc 1VI/SH AirborneMECHANICAL SPECIFICATIONSDimensions 8.0 x 6.5 x 1.0 Inch Max Weight 3.5 lb. MaxRF ConnectorsInput: Type-SMA, Female Output: Type-TNC, FemaleDC Interface Connector Hybrid – D-Sub 17-Pin, Male (17W2) Cooling External Heatsink Required (not supplied)2500 – 6000 MHz / 100 Watts DC INTERFACE CONNECTORA1 GND Ground ReturnA2 VDD Supply Voltage: +26.0 – 32.0V DC, 28.0V DC Nominal1 RS485 (-) Serial Communication Bus2 Temperature Reporting Analog Output Voltage @ 10 mV/°C with a 500 mV offset (i.e. 0.75V = 25°C)3 Address 1 Hardware Address 14 Address 3 Hardware Address 35 Attenuator Setting Voltage input in the range of 0.5 – 3.0V DC, 0.5V DC corresponds with minimum attenuation, 3.0V DC is maximum attenuation. Leave pin open or grounded to utilize RS-485 interface. (See RS-485 details below)6 PA Enable 0/3.3V logic levels:Power Amplifier disable is a TTL Logic Low (0V).(Internally Pulled-High 3.3V)Leave pin open or pulled high to utilize RS-485 interface.(See RS-485 details below)7 Alarm Amplifier Alarm indicator: Normally TTL LowA logic High indicates a fault condition, 0/3.3V Logic Levels8 RS485 (+) Serial Communication Bus9 Current Reporting Analog output voltage range of 1V/10 A (i.e. 1.5V = 15A)10 Address 0 Hardware Address 0 – Least significant bit11 Address 2 Hardware Address 212 Address 4 Hardware Address 4 – Most significant bit13 Not Used No Connection14 Not Used No Connection15 Reset Hardware resetLogic 0 to reset PA and clear latched faultsPh. 1 (310) 412-8100 Fax. 1 (310) 412-9232 Stock No. 1191D.S. Rev. 1.32 / 12-18-20132500 – 6000 MHz / 100 WattsRS-485 User InterfaceThe following settings are used for serial communications:• Baud rate: 115,200 • Start bits: 1 • Data bits: 8 • Stop bits: 1 • Parity: None• Handshake: NoneFrame and Message StructuresFrame structureThe serial link will be asynchronous, and follows a typical RS485 frame structure. The frame structure is defined in the figure below.Each frame is 10 bits in length and will begin with a start bit, followed by 8 data bits and finally a single stop bit.Message structureFigure 1: Serial interface frame structureFigure 2: Serial interface message structure316 W. Florence Ave. Inglewood, CA 90301 Ph. 1 (310) 412-8100 Fax. 1 (310) 412-9232Stock No. 1191D.S. Rev. 1.32 / 12-18-20132500 – 6000 MHz / 100 Watts Master AddressA7 A6 A5 A4 A3 A2 A1 A0X X X X X X X XMaster Address is not evaluatedSlave AddressA7 A6 A5 A4 A3 A2 A1 A00 0 0 16 8 4 2 132 Slave addresses are possible (If no address lines are strapped on hardware, unit defaults to address 0)LenLen contains the number of bytes that follow, from Status to Checksum.StatusMaster should load this with zero.Slave will echo back status of the command after it is evaluated.Possible Slave responses:Value Description0x00h Message received and decoded successfully0x13h Checksum error0x2Bh Command not availableThere are 7 supported RS-485 commands, detailed below.2500 – 6000 MHz / 100 WattsNullThe null command responds with message status. It is used for a basic test of the communications link.Command frame value (hex) 0x00Length frame value (hex) 0x03Command data noneSlave response Echo with status setExample:[8/30 17:58:15.3]SEND: 00 00 03 00 00 03 ......[8/30 17:58:15.4]RECV: 00 00 03 00 00 03 .......Soft resetPerforms a restart of the system.Command frame value (hex) 0x04Length frame value (hex) 0x03Command data NoneSlave response Echo with status setExample:[8/30 18:09:39.0]SEND: 00 00 03 00 04 07 ......[8/30 18:09:39.1]RECV: 00 00 03 00 00 03 .......Set power up conditionSets the state of the amplifier bias on application of DC or reset.Command frame value (hex) 0x05Length frame value (hex) 0x03Command data 2 bytes:0x0001 sets power up condition to biasenabled.0x0000 sets power up condition to biasdisabled.Slave response Echo with status set2500 – 6000 MHz / 100 Watts Example:[8/30 18:13:08.5]SEND: 00 00 05 00 05 00 01 01 ........[8/30 18:13:12.3]RECV: 00 00 03 00 05 06 .......DisableDisables amplifier bias.Command frame value (hex) 0x06Length frame value (hex) 0x03Command data NoneSlave response Echo with status setExample:[8/30 18:14:36.7]SEND: 00 00 03 00 06 05 ......[8/30 18:14:36.8]RECV: 00 00 03 00 06 05 .......EnableEnables amplifier bias.Command frame value (hex) 0x07Length frame value (hex) 0x03Command data NoneSlave response Echo with status setExample:[8/30 18:15:35.4]SEND: 00 00 03 00 07 04 ......[8/30 18:15:35.5]RECV: 00 00 03 00 07 04 .......Set input attenuationSets the attenuation level.Notes:•The RS-485 attenuation value overrides voltage control on pin 5.•The value of the attenuation can only be increased from the factory value.•The gain of the amplifier is also a function of temperature compensation.•Variations in gain versus temperature are expected, independent of the user attenuation setting.2500 – 6000 MHz / 100 Watts Command frame value (hex) 0x11Length frame value (hex) 0x05Command data 2 bytes. The first byte is 0 and the secondbyte is the mixed number attenuationvalue.D7 D6 D5 D4 D3 D2 D1 D00 0 16 8 4 2 1 . 1/2Examples:30dB is 0x00 0x3C8.5dB is 0x00 0x11Slave response Echo with status setExample for setting 8.5dB user attenuation:[9/4 15:45:49.9]SEND: 00 00 05 00 11 08 05 19 ........[9/4 15:45:49.9]RECV: 00 00 03 00 11 12 .......Get statusReturns current status of amplifierCommand frame value (hex) 0x02Length frame value (hex) 0x03Command data NoneSlave response Input Current (2 bytes)Input Voltage (2 bytes)Temperature (2 bytes)Attenuator Setting (2 bytes)Alarm Register (2 bytes)Example:[8/30 17:59:39.5]SEND: 00 00 03 00 02 01 ......[8/30 17:59:39.5]RECV: 00 00 0D 00 02 00 0A 0A ........0008: C4 00 19 00 11 00 00 C3 ...2500 – 6000 MHz / 100 WattsALARM REGISTER15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0Temperature Alarm > 85 C Current Alarm > 25 A Voltage Alarm > 34 V Sequencer AlarmLatched Alarm Current > 29 A Latched Alarm Voltage or Temperature >36 V and/or>90 C00Notes on Alarms• Any alarm condition will pull the Alarm line high (Pin 7)• For Latched Current Alarm, the input power is attenuated by approximately 15 dB. • For Latched Voltage or Temperature, the unit will disable.• A Software or Hardware reset is required to clear Latched Alarm.Voltage 16 bit signed, 1/100th of a Volt +327.67 / -327.66 V Current16 bit unsigned in 1/100th of an Amp0 ~ 65535 in hundredths of an AmpTemperature 16 bit signed inwhole degrees+32767 / -32766 degrees CentigradeStock No. 1191D.S. Rev. 1.32 / 12-18-2013。

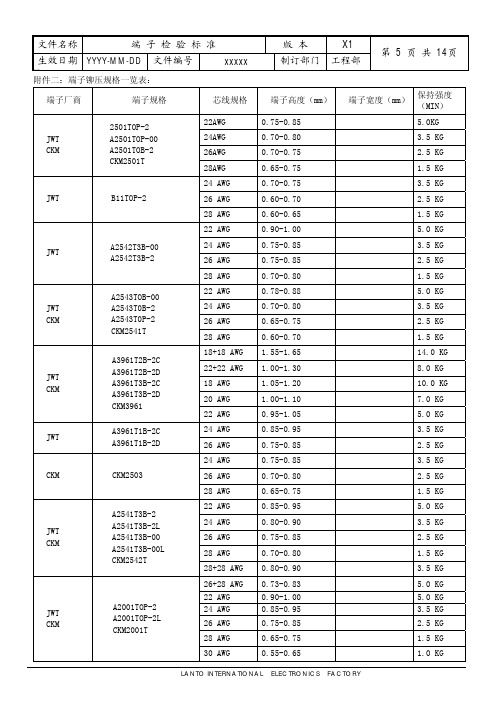

端子铆压规格表

附件二:端子铆压规格一览表:端子厂商端子规格 芯线规格 端子高度(mm)端子宽度(mm)保持强度 (MIN) 22AWG 0.75-0.85 5.0KG 24AWG 0.70-0.80 3.5 KG 26AWG 0.70-0.75 2.5 KG JWT CKM2501TOP-2 A2501TOP-00 A2501TOB-2 CKM2501T28AWG 0.65-0.75 1.5 KG 24 AWG0.70-0.75 3.5 KG 26 AWG 0.60-0.70 2.5 KG JWT B11TOP-2 28 AWG 0.60-0.65 1.5 KG 22 AWG0.90-1.00 5.0 KG 24 AWG 0.75-0.85 3.5 KG 26 AWG 0.75-0.85 2.5 KG JWTA2542T3B-00 A2542T3B-228 AWG0.70-0.80 1.5 KG 22 AWG 0.78-0.88 5.0 KG 24 AWG 0.70-0.80 3.5 KG 26 AWG 0.65-0.75 2.5 KG JWT CKMA2543TOB-00 A2543T0B-2 A2543T0P-2 CKM2541T 28 AWG 0.60-0.70 1.5 KG 18+18 AWG 1.55-1.65 14.0 KG 22+22 AWG 1.00-1.30 8.0 KG 18 AWG 1.05-1.20 10.0 KG 20 AWG 1.00-1.10 7.0 KG JWT CKMA3961T2B-2C A3961T2B-2D A3961T3B-2C A3961T3B-2D CKM3961 22 AWG 0.95-1.05 5.0 KG 24 AWG 0.85-0.95 3.5 KG JWTA3961T1B-2C A3961T1B-2D26 AWG 0.75-0.85 2.5 KG 24 AWG0.75-0.85 3.5 KG 26 AWG 0.70-0.80 2.5 KG CKM CKM2503 28 AWG0.65-0.75 1.5 KG 22 AWG 0.85-0.95 5.0 KG 24 AWG 0.80-0.90 3.5 KG 26 AWG 0.75-0.85 2.5 KG 28 AWG 0.70-0.80 1.5 KG JWT CKMA2541T3B-2 A2541T3B-2L A2541T3B-00 A2541T3B-00L CKM2542T28+28 AWG 0.80-0.90 3.5 KG 26+28 AWG 0.73-0.83 5.0 KG 22 AWG 0.90-1.00 5.0 KG 24 AWG 0.85-0.95 3.5 KG 26 AWG 0.75-0.85 2.5 KG 28 AWG 0.65-0.75 1.5 KG JWT CKMA2001TOP-2 A2001TOP-2L CKM2001T端子厂商 端子规格 芯线规格 端子高度(mm)端子宽度(mm)保持强度 (MIN) 26AWG 0.70-0.80 2.5KG JWTA2541T3P-0028AWG 0.65-0.75 1.5KG 24AWG0.85-0.95 3.5KG 26AWG 0.75-0.85 2.5 KG 28AWG 0.65-0.75 1.5 KG JWT CKM CKM2003T A2002TOP30AWG 0.60-0.70 1.0 KG 18+18AWG 1.30-1.40 14 KG 16AWG1.30-1.40 14 KG 18AWG 1.20-1.30 12 KG 20AWG 1.00-1.20 7.0 KG 22AWG 0.90-1.10 5.0 KG JWT CKMC5081T2B-2 C5081TOB-2 CKM508224AWG 0.85-0.95 3.5KG 18+18 AWG 1.50-2.00 14KG 18 AWG1.20-1.40 12KG 20 AWG 1.10-1.30 7.0KG 22 AWG 1.00-1.10 5.0KG JWT CKM C5082TOP-2 CKM508124 AWG0.90-1.10 3.5KG 16 AWG 1.30-1.50 14KG JWT CKM C5082T2B-2 CKM5081 18AWG 1.20-1.40 12KG 20 AWG0.95-1.15 7.0KG 22AWG 0.85-0.95 5.0KG 24 AWG 0.80-0.90 3.5KG JWT CKMA2544TOP-2 A2544TOB-2 CKM2544T 26 AWG0.75-0.85 2.5KG CKM 2506-TA 24 AWG 0.80-0.90 3.5KG CKM 2506-TB 22 AWG 0.85-0.95 5.0KG CKM CKM2002-TV 28 AWG 0.70-0.80 1.5KG CKM CKM2004T 28 AWG 0.65-0.75 1.5KG CKMCKM2542T 28+28 AWG 0.80-0.90 3.5KG 22 AWG 0.80-0.90 5.0KG 18 AWG 1.00-1.20 12KG JWTA2505TOP-2 C4202T2B-2 C4202T2P-216 AWG 1.20-1.50 14KG 24+24 AWG0.90-1.20 6.0KG 26+26 AWG 0.85-0.95 5.0KG 22 AWG 0.90-1.00 5.0KG 24AWG 0.85-0.95 3.5KG 26AWG 0.80-0.90 2.5KG JWT CKM A2547TOP-2 CKM2543T端子厂商 端子规格 芯线规格 端子高度(mm)端子宽度(mm)保持强度 (MIN) JWT CKM A1251TOP-2 CKM1251T 28 AWG 0.50-0.60 1.5KG 26AWG 0.55-0.65 2.5KG 28AWG 0.50-0.62 1.5KG JWT A2003TOB-00 A2003TOB-2 A2003TOB-0D 30AWG 0.50-0.60 1.0KG 24AWG 0.70-0.80 3.5KG JWTA2005TOP-0028AWG 0.55-0.65 1.5KG 18AWG1.20-1.40 12KG 26AWG 0.70-0.802.5KG CKM CKM2005-T 28AWG0.50-0.60 1.5KG 26AWG 0.70-0.80 2.5KG 28AWG 0.65-0.75 1.5KG JWT CKMA2005TOB-2 A2005TOB-00 CKM2004T30AWG 0.60-0.70 1.0KG 18+18AWG1.50-2.00 14KG 18AWG 1.00-1.30 12KG 20AWG 0.90-1.00 7.0KG 22AWG 0.85-0.95 5.0KG JWT CKMA3963TOB-2 A3963TOP-2 CKM396224AWG 0.80-0.90 3.5KG 14 AWG1.30-1.70 15KG 16 AWG 1.20-1.50 14KG JWT CKM A3963T2B-2 A3963T2P-218 AWG 1.00-1.30 12KG 16AWG1.20-1.40 14KG 18AWG 1.00-1.20 12KG 20AWG 0.90-1.10 7.0KG JWT CKM C4202TOP-2 C4202TOB-2 CKM4201 22AWG 0.80-1.005.0KG 260901T 24AWG 0.89±0.05 1.45±0.05 3.5KG JFE260902T28AWG 0.63±0.05 1.45±0.05 1.8KG 24AWG0.75-0.80 3.5KG 26AWG 0.68-0.75 2.5KG JST SHE-001T-P0.6 28AWG 0.65-0.70 1.5KG 24AWG0.70-0.80 3.5KG 26AWG 0.65-0.75 2.5KG 28AWG 0.65-0.72 1.5KG JST SPH-002T-P0.5S30AWG 0.60-0.65 1.0KG C5082TOB-2 18AWG 1.25-1.35 12KG C5082TOB-2 18+22AWG 1.45-1.55 12KG JWT端子厂商 端子规格 芯线规格 端子高度(mm)端子宽度(mm)保持强度 (MIN) 18AWG 1.10-1.20 10KG JWT B1811TOP-2 28AWG 0.95-1.05 1.5KG JWT A1561TOP-2 22AWG 1.00-1.10 5.0KG JWT A1561T0B-222AWG 0.80-0.90 5.0KG JWT A3961T2B-2C 18AWG 1.05-1.20 10KG 24AWG 0.75-0.85 3.5KG JWT 2006TOP-2 28AWG 0.65-0.75 1.5KG CKM 2543T 28+28AWG 0.80-0.90 3.5KG CKM 2503T 28+26AWG 0.80-0.90 3.5KG CKM 5081T 22+20AWG 1.35-1.45 12KG CKM 1561T 22AWG 1.00-1.10 5.0KG CKM 2542T 20AWG 0.95-1.00 7.0KG CKM 2004T 28AWG 0.65-0.75 1.5KG 26AWG 0.58-0.65 2.5KG 华通 50079-8000 28AWG 0.57-0.65 1.5KG CKM 20020301 26AWG 0.60-0.70 2.5KG JWT A1251T0P-2 28AWG 0.50-0.60 1.5KG CKM CKM3962T 18AWG 1.00-1.3012KG CKM CKM15010301 28AWG 0.65-0.72 1.1±0.05 1.5KG CKMCKM2002-TV28AWG 0.70-0.80 1.5KG 16AWG1.20-1.50 14KG 18AWG 1.10-1.20 9.0KG 20AWG 1.00-1.10 7.0KG JWT CKMC4202T0P-2 C4202T0B-2 CKM4201 22AWG0.90-1.00 5.0KG JWT C4202T2B-2 16AWG 1.20-1.50 14KG JWT C4202T2P-2 18AWG 1.00-1.20 12KG CKM 3963T 22AWG 0.85-0.95 5.0KG CKM2503T 22AWG 0.80-0.90 5.0KG 28AWG 0.60-0.70 1.5KG 2580T22AWG 0.75-0.85 5.0KG 28AWG 0.55-0.65 1.5KG 2015T 22AWG 0.70-0.80 5.0KG 4256TP3 16AWG 1.30-1.50 14KG ALEX 51T 22AWG 0.75-0.85 5.0KG 08-50-0114 22AWG 0.75-0.85 5.0KG 08-50-0114 26AWG 0.70-0.80 2.5KG MOLEX端子厂商 端子规格 芯线规格 端子高度(mm)端子宽度(mm) 保持强度 (MIN) 胡连 604180-2 编织线 1.65-1.802.50-3.2010KG翔辉 SH-995 18AWG 一分钟吊重9.1KG 不脱落为合格 MOLEX 39-00-0065 22AWG 0.85-0.95 5.0KG MOLEX39-00-0067 22AWG 0.85-0.95 5.0KG 104505-03 22AWG 0.90-1.00 5.0KG 35085-1 18AWG 1.25-1.35 12KG 770601-218AWG 0.70-0.80 12KG 104503-3 22AWG 0.85-0.95 5.0KG 170362-1 22AWG 0.95-1.05 5.0KG 104480-4 22AWG 0.85-0.95 5.0KG 2-36152-1 18AWG 2.70-3.00 12KG 1757778-3 28AWG 0.75-0.85 1.5KG 170204-1 22AWG 0.85-0.95 5.0KG 170360-118AWG 1.05-1.15 12KG 170262 22AWG 0.95-1.05 5.0KG 104505-B22AWG 0.85-0.95 5.0KG 350570-1 18AWG 1.20-1.50 12KG 104504-322AWG 0.85-0.95 5.0KG 2-520403-2 22AWG 0.85-0.95 5.0KG 66105-3 24AWG 0.75-0.85 3.5KG 66424-7 28AWG 0.75-0.85 1.8KG 61116-4 20+20AWG 1.55-1.65 12KG 50011-8000 28AWG 0.52-0.62 1.5KG 640271-1 18AWG 2.00-2.10 10KG 22AWG 1.10-1.30 5.0KG 63475-2 22+22AWG 1.40-1.50 8.0KG 61070-1 22AWG 1.10-1.20 5.0KG 71180-BS-1 18AWG 1.35-1.45 10KG 55675-1 22AWG 2.50-3.00 5.0KG AMP602207-218AWG 1.50-2.0010KG 24AWG 0.75-0.85 1.50-1.60 3.5KG JAEIL-G-C2-SA-10000 28AWG 0.65-0.75 1.50-1.60 1.5KG 75653-00522AWG 0.90-1.00 5.0KG 47445-00 22AWG 0.90-1.00 5.0KG 22AWG 0.90-1.00 5.0KG DUPONT47217-000端子厂商 端子规格 芯线规格 端子高度(mm)端子宽度(mm) 保持强度 (MIN)FDFV-187(5) 18AWG 1.10-1.20 10KGRNBS1-3.7 18AWG 2.35-2.45 12KG KSTRNB-1-5 22AWG 2.00-2.50 5.0KGTDP 8810T 22AWG 0.80-0.90 5.0KGT-UBAC11-BN-5S-D-V01 28AWG 0.73-0.83 1.5KGT-UBAC10-BN-5S-D-V01 24AWG 0.93-1.13 3.5KGT-UBAC14-BN-5S-D-V01 20AWG 1.00-1.25 7.0KG30AWG 0.75-0.85 1.0KG28AWG 0.80-0.90 1.5KG26AWG 0.88-0.98 2.5KG24AWG 0.95-1.30 3.5KG22AWG 0.98-1.50 5.0KG V3.5(公﹑母)20AWG 1.00-1.60 7.0KGT-UAC10-10200 24AWG 0.93-1.13 3.5KGT-UAC10-20200 28AWG 0.73-0.83 1.5KG28AWG 0.65-0.75 1.5KG Φ0.76圆形端子30AWG 0.55-0.65 1.0KG24AWG 0.75-0.85 3.5KG26AWG 0.72-0.82 2.5KG Φ1.0圆形端子28AWG 0.70-0.80 1.5KGRVS2-3.7 18AWG 2.50-3.50 10KG24AWG 0.83-0.95 3.5KG TA1BA000E28AWG 0.73-0.83 1.5KG24AWG 0.83-0.95 3.5KG26AWG 0.78-0.90 2.5KG TAB1000E28AWG 0.73-0.83 1.5KGWST139601BS-2 18AWG 0.90-1.03 10KG14AWG 3.50-4.50 15KG16AWG 3.00-4.00 14KG FDFD2-25018AWG 3.00-4.00 10KG STM2131BS 接地线 1.15±0.05 2.05±0.05 10KGPACKARD:12040993 接地线 1.15±0.05 2.05±0.05 10KGE7EB-14487-AA 20AWG 1.25±0.05 7.0KG FDD1-250 18AWG 3.00-4.00 10KG CUSTIMER CONSIGN 22AWG 0.85-0.95 5.0KGMPNY1-156(公) 18AWG 1.60-1.70 12KG FRD1-156(母) 18AWG 1.85-1.95 12KG 世聚 T202P00T00 24AWG 0.70-0.80 3.5KG端子厂商端子规格芯线规格 端子高度(mm)端子宽度(mm)保持强度 (MIN) 28AWG0.65-0.75 1.5KG 26AWG 0.70-0.80 2.5KG 24AWG 0.75-0.85 3.5KG 08-05-011322AWG 0.80-0.90 5.0KG 22AWG0.80-0.90 5.0KG 20AWG 0.85-0.95 7.0KG 08-50-010618AWG1.00-1.30 12KG 43030-0003 22AWG 0.85-0.95 5.0KG 02-09-2103 18AWG 1.30-1.80 12KG AS-N-345 18AWG2.00-2.50 12KG 08-65-0804 26+28AWG 0.80-0.90 5.0KG 20+20AWG 1.60-1.80 12KG02-08-123420AWG 1.45-1.65 7.0KG 20+20AWG 1.75-1.95 12KG 02-08-1201 20AWG 1.35-1.55 7.0KG 43030-0001 20AWG 1.10-1.20 7.0KG 22-01-104228+26AWG 0.85-0.95 3.5KG 43030-0007 22AWG 0.90-1.00 5.0KG 43030-0001 20AWG 1.00-1.10 7.0KG 50079-8000 28AWG 0.55-0.60 1.5KG 26AWG 0.65-0.75 2.5KG 50390-8051 28AWG 0.60-0.70 1.5KG 39-00-0061 18+18AWG 1.40-1.50 14KG 02-06-2101 20AWG 0.90-1.10 7.0KG 02-06-1101 20AWG 0.85-0.95 7.0KG 28AWG 0.70-0.80 1.5KG 16-02-0082 24AWG 0.85-0.95 3.5KG 16-02-0119 26AWG 0.70-0.80 2.5KG 26AWG 0.80-0.85 2.5KG 16-02-111928AWG 0.75-0.80 1.5KG 18AWG0.95-1.05 12KG 20AWG 0.90-1.00 7.0KG 08-70-010622AWG 0.85-0.95 5.0KG 18AWG 1.20-1.50 12KG 20AWG 1.00-1.30 7.0KG 22AWG 0.90-1.10 5.0KG MOLEX08-07-103124AWG0.85-0.953.5KG端子厂商端子规格芯线规格 端子高度 (mm) 端子宽度(mm)保持强度 (MIN)TWP-0.35(22AWG)0.85±0.05 1.80+0.1/-0.2 6.0KG 12064971TWP-0.5(20AWG)0.95±0.05 1.80+0.1/-0.2 8.0KG TWP-0.35(22AWG) 1.10±0.05 1.65+0.1/-0.2 5.5KG 15326268 TWP-0.5(20AWG) 1.15±0.05 1.65+0.1/-0.2 8.0KG 12034046 TWP-0.8(18AWG) 1.35±0.05 2.45+0.1/-0.2 10KG 12047581 TWP-0.8(18AWG) 1.30±0.05 2.50+0.1/-0.2 10KG TWP-1.0(16AWG)1.55±0.05 3.05+0.1/-0.2 14KG 12020116TWP-2.0(14AWG) 2.50±0.05 3.45+0.1/-0.2 15KG 15304722 TWP-0.35(22AWG) 1.10±0.05 1.65+0.1/-0.2 5.5KG TWP-1.0(16AWG) 1.40±0.05 2.10+0.1/-0.2 14KG 15304723 TWP-0.8(18AWG) 1.25±0.05 2.05+0.1/-0.2 10KG 12059894 TWP-0.35(22AWG) 1.10±0.05 2.05+0.1/-0.2 6.0KG 12077628 TWP-0.35(22AWG) 1.10±0.05 2.05+0.1/-0.2 5.5KG TWP-0.8(18AWG) 1.30±0.05 2.50+0.1/-0.2 10KG 12045773 TWP-1.0(16AWG) 1.40±0.05 2.50+0.1/-0.2 14KG 12052172 TWP-3.0(12AWG) 2.15±0.05 3.97+0.1/-0.2 32KG TWP-1.0(16AWG) 1.50±0.05 3.00+0.1/-0.2 14KG PACKARD12066214 TWP-2.0(14AWG) 1.65±0.05 3.00+0.1/-0.2 15KG 8100-3258 AVS-5.0(10AWG) 2.50±0.05 5.25±0.05 36KG 8100-0797AVS-5.0(10AWG) 2.50±0.05 5.25±0.05 36KG 8100-0453 AVS-5.0(10AWG) 2.50±0.05 5.25±0.05 36KG 8100-0467 TAV-0.5(20AWG) 1.55±0.05 2.75±0.05 7.0KG SUMITOMO 8100-1427TAV-0.5(20AWG) 1.25±0.051.80±0.057.0KG7116-4143-024MM 2CROSS LINKED POLY ALKENE 2.25±0.05 3.97-4.15 36KGYAZAKI7116-4140-02 16AWG CROSS LINKED POLYETHEL 1.55±0.05 2.58-2.77 10KG 21T-6502-PB22AWG 0.92-1.02 5.0KG 51T-1202 24AWG 0.85-0.95 3.5KG ALEX端子厂商端子规格 芯线规格 端子高度(mm)端子宽度(mm) 保持强度(MIN)39-00-0038 18AWG 1.10-1.20 12KG 39-00-0053 18AWG 1.10-1.20 12KG 39-00-0059 18AWG 1.00-1.20 12KG 39-00-008316AWG 1.20-1.4014KG 39-00-0061 18AWG 1.06-1.66 10KG 39-00-0038 24AWG 0.85-0.953.5KG 39-00-0040 24AWG 0.85-0.95 3.5KG 39-00-0087 28AWG 0.75-0.85 1.5KG 39-00-0038 24+24AWG 0.90-1.20 6.0KG MOLEX39-00-008318+18AWG 1.55-1.60 14KG ITT CANNONMDS-S-TS 28AWG 0.40-0.50 1.5KG 16AWG 1.35-1.45 14KG 4201T18+18AWG 1.35-1.45 8.0KG 5081T 18+22AWG 1.70-1.80 12KG 28AWG 0.65-0.75 1.5KG CKM2505T 30AWG 0.60-0.70 1.0KG SVH-21T-P1.1 18AWG 1.00-1.30 10KG JSTSYM-001P-P0.6 24AWG 1.00-1.10 3.5KG 24AWG 0.80-0.90 5.0KG 26AWG 0.70-0.80 3.0KG 5-66507-7 6-66505-228AWG 0.60-0.70 2.0KG 42374-2 20AWG 1.50-1.60 7.0KG 60967-1 20AWG 1.13-1.23 7.0KG 170147-1 22AWG 1.15-1.25 5.0KG AMP350689-122AWG 0.90-1.00 5.0KG 24AWG 0.70-0.80 3.5KG CKM20010301 28AWG 0.60-0.70 1.5KG A1500-TP 28AWG 0.55-0.65 1.5KG A1501TOP-228AWG 0.55-0.65 1.5KG A1252-TP-(B) 28AWG 0.55-0.65 1.5KG A1252TOP-2 28AWG 0.55-0.65 1.5KG A2001TOP 28AWG 0.60-0.70 1.5KG A2004-TP 28AWG 0.60-0.70 1.5KG JWT CKMHR其他端子类型:芯线规格 拉力(MIN) 芯线规格 拉力(MIN) 芯线规格 拉力(MIN) 横卷线 4.5KG 22AWG 5.0KG 32AWG 0.8KG编织线 10KG 26AWG 2.5KG 10AWG 36.4KG14AWG 15KG 28AWG 1.5KG 12AWG 31.9KG16AWG 14KG 30AWG 1.0KG 20AWG 7.0KG18AWG 12KG 24+24AWG 6.0KG 26+26AWG 5.0KG。

金手指代码收集查询

金手指代码收集查询(按游戏首字母查询)代码(A区)热血格斗04C2-02-FFFF 血不减05B2-01-1D 最高等级05BE-01-1D 同伴最高等级0605-02-FDFD 快手招式0609-02-FFFF 快脚招式0401-02-0404 虎头降临04C4-32-0000 一击必杀0613-01-08 合体无限(锁定合体游标的位置)0614-01-00 敌人别想合体(右侧)061A-01-00 敌人的L是1(右侧)0619-01-08 我方L是L9(左侧)代码(B区)蝙蝠侠无限血00B7-04-0008无敌00CC-01-B0生命00BE-02-0009蝙蝠侠304C8-01-15闪烁无敌0142-01-FFFF等级/分数/血蝙蝠侠20479-01-11 无敌代码(C区)三目童子无敌0074-01-1B赤色要塞无敌金手指0052-02-FF赤影战士06F0-01-10 1P血0662-01-14 1P武器数量0680-01-XX 1P武器威力(00-等级1 04-等级2 08-等级3)06B2-01-XX 1P武器种类(00-刀锋 03-铁钩)赤影忍者全屏攻击轻松通关金手指06C1-03-19008E注意!!!!!!!!!!!!当与到如下情况是请按DELETE关闭金手指。

否则主角会掉下去火之鸟(无敌/定时/无限血/穿墙)超级宝宝00BA-01-11闪烁无敌彩虹魔法金手指:0022:63 (人数)0024:0b (速度+双彩虹+隐身)0509:01-08 (魔法,开启后立即关掉,BOSS战时开启无效) 057a:0f (魔法持续时间)0052:01-06 (选关) 07 (公开关卡,泡泡龙关)赤影战士金手指:06f0:10 (HP)06b2:00 (刀) 03 (矛)0680:0c (武器最强)0662:14 (手里剑 or 雷)06a1:0e (蓄力超杀,开启后立即关闭)代码(D区)西游记1代0109-03-FFFF 无限金钱代码(F区)斧王(战斧)0091-01-14 血0093-01-14 能量007D-01-11 无敌(受攻击后)代码(G区)古巴战士0028-01-63生命04C2-01-FF 坦克0600-01-81 Weapon0600:00-04 (子弹) 05,06 (?子弹)0600:0a (超级雷,用B键发出)0600:20-24 (子弹+超级雷)0600:80-85 (坦克子弹,己方无敌,但不能下水) 0680:20 (隐身)代码(H区)魂斗罗3(魂斗罗4)#1 0091-01-09 1P人数#1 0093-01-09 1P炸弹数#1 0315-01-0C 1P隐身无敌#1 0312-01-01 1P枪型01-S 04-L#2 0090-01-01 选关#2 00B9-01-16 一直闪震#2 030E-01-0B 屏幕间随意走魂斗罗7_超级战魂#1 00A0-01-02 不死#2 00C4-01-02 透明无敌魂斗罗X_Super Contra X (Unl)#1 00B7-01-02 人数#2 005A-01-01 不死#1 008E-01-01 透明火炮无敌0180-01-05荒野大镖客0078-01-04速度0079-01-04射程0049-01-01通缉令火之鸟060A-03-999 时间0411-02-99 兽面0030-02-99 生命(无限续关)0416-03-000055 无限隐身,穿墙(向日葵的效果)0413-03-5575 小兵定身(哨子的效果)0415-03-0044 撞怪无敌(主角和小兵相遇时小兵死,BOSS无效)0412-03-9900 无限血0416-03-440055 无限隐身+撞怪无敌过关时一定要把隐身关了,否则主角不会拼图,站在那里不动金手指开的越少越好代码(I区)代码(J区)代码(K区)空中魂斗罗(Virtuanes)001C-01-XX 1P人数0012-01-XX 1P武器(00-白弹 01-旋转月牙 02-激光 03-旋转椭圆)0088-01-XX 1P速度设置(00-慢 08-快)SD快打006C-02-999 经验科纳米 KONAMI 世界07de:03 (弹药数量)07df:01 (钥匙)07b1:0f (全道具)07b2:ff (全角色副武器)07ca:00-07 (换人)0040:07 (隐身时间)07db:03 (兵蜂登陆)07dc:03 (战斗机登陆)07d0-07d7:0e (HP不减+不死)第3个门开,忘改了... ...代码(L区)龙之忍者029B-01-0A 血0204-01-63 时间代码(M区)魔界村0647-01-00猫和老鼠3命数0046-01-20红心004A-01-FF猫和老鼠命数04A2-01-09红心04A3-01-09代码(N区)鸟人战士008B-01-40定身无敌0088-01-01绝技(SELECT使用的那个)无限能源战士2(力量刀锋2);Power Blade 2 (U)#1 0055-01-03 POW#1 049A-01-12 血#1 00A0-01-12 ENERGY#1 009D-01-99 L数#1 009E-01-99 E数#1 009F-01-99 人数#2 0054-01-10 发镖时POW仍满格#2 0095-01-05 时间(前两位) #2 009C-01-06 AREA(选小关) #2 05B8-01-14 透明#2 054A-01-80 跳得高代码(O区)代码(P区)代码(Q区)代码(R区)忍者龙剑传无敌1代:0095-01-092代:0068-01-2F3代:无敌00AD-01-0A时间00C7-01-09忍者龙剑传2 (中)0068:20 (隐身)00ae:30 (忍)007d:00-04 (手里剑)忍者龙剑传3 (中)00ad:04 (隐身)00cd:63 (忍)009f:00-04 (手里剑)04ee,04ef:80 (,手里剑发出后开启,过关后先关掉,后期BOSS战前也要先关闭) 00a9:01 (刀)忍者龟2人数无限006A-02-99忍者神龟3006A-01-09 :人数无限人间兵器无敌06F8-01-02代码(S区)沙罗曼蛇2无敌0074-01-05SD快打006C-02-999 经验双截龙2 (U)0432:0a (人数)0422:04,08-0b (选关)双截龙3045d:64 (HP)06df:63 (双截棍数量)06e0:63 (2P双截棍数量)06e1:63 (手里剑数量)06e2:63 (铁爪数量)0074:00-03 (换人) 04-0f (?)SD 快打 (中)006d:04 (快速升级)0034:00-02 (换人,建议不要换成哈格) 003e:09 (人数)0030:** ()松鼠大战I#2 005E-01-11 1P闪烁无敌#2 005F-01-11 2P闪烁无敌#1 05B6-01-82 1P人数不减#1 05E6-01-82 2P人数不减#2 0560-01-01 1P跳起飘浮#2 0561-01-01 2P跳起飘浮#2 0031-01-07 选关00,01,02,03,04……松鼠大战II#2 00D8-01-0A 1P闪烁无敌#2 00D9-01-0A 2P闪烁无敌#2 0072-01-02 选关00,01,02,03,04……沙罗曼蛇 2#1 0056-01-63 生命数#1 0506-01-FF 透明无敌双接龙3045D-01-FF角色1血不减06DF-01-FF双截棍不减04DA-01-FF角色3血不减06E1-01-FF角色3飞标不减代码(T区)踢王无敌 00D2-01-28MP 00EC-01-69EXP 00F0-01-69人数 030E-01-0AHP 06B9-01-B0HPMAX 06BB-01-B0物品 06BE-02-FFFF烟山90坦克#1 0045-01-02 基地是可修复钢墙02 基地是不可修复钢墙00#1 0100-01-02 敌人被定时#1 0051-01-64 P1生命#1 0052-01-64 P2生命#2 00A8-01-60 P1加俩星后(推铁)#2 00A9-01-60 P2加俩星后(推铁)#2 0089-01-10 P1防弹罩(无敌)#2 008A-01-10 P2防弹罩(无敌)#2 007F-01-1C 敌方坦克随机增加#2 0086-01-40 Power位置横向X#2 0087-01-D0 Power位置纵向Y#2 0088-01-06 Power类型 00帽01定时02锹03星04炸弹05坦克06枪07船#1 0178-01-A0 P1推草#1 0179-01-A0 P2推草#1 0101-01-63 P1加枪后(推铁/打不死)#1 0102-01-63 P2加枪后(推铁/打不死)#1 0170-01-FF P1加船后(过河/打不死)#1 0171-01-FF P2加船后(过河/打不死)脱狱043a:64 (人数)0047:00-05 (选关)0715:00-02 (手持物变为,00 枪 01 刀 02 手雷)0438:ca (全能力)0438:da (全能力+手持枪) ea (全能力+手持刀) fa (全能力+手雷) 代码(U区)代码(V区)代码(W区)代码(X区)雪山兄弟0369-01-07 Player 1 攻击上升036A-01-07 Player 2 攻击上升雪人兄弟#1 0369-01-07 1P攻击上升(红蓝黄瓶)#1 036A-01-07 2P攻击上升(红蓝黄瓶)#1 0076-01-0A 1P人数#1 0077-01-0A 2P人数#1 03D2-01-01 1P无敌#1 03D3-01-01 1P无敌雪人兄弟0369:07 (1P全能力+不死)036a:07 (2P全能力+不死)037e:20 (无敌)037f:20 (2P无敌)03d4-03d9:e0 (敌全灭,对BOSS依然见效)0073:00-31 (选关)008a:01 (寿)雪人兄弟#1 0369-01-07 1P全能不死(红蓝黄瓶,快腿大镖快镖) #1 036A-01-07 2P全能不死(红蓝黄瓶,快腿大镖快镖) #1 0076-01-0A 1P人数#1 0077-01-0A 2P人数#1 03D2-01-01 1P隐身无敌#1 03D3-01-01 2P隐身无敌#2 037E-01-20 1P大头无敌(绿瓶)#2 037F-01-20 2P大头无敌(绿瓶)#2 0073-01-28 选关00-09,0A-13,14-1D,1E-27,28-31#2 0082-01-01 摇奖机01(1P加楼),02(2P加楼)#2 03D4-01-E0 敌1(Boss)直接灭#2 03D5-01-E0 敌2(Boss2)直接灭#2 03D6-01-E0 敌3直接灭#2 03D7-01-E0 敌4直接灭#2 03D8-01-E0 敌5直接灭#2 03D9-01-E0 敌6直接灭#2 008A-01-01 祝&寿#2 007F-01-3B 时间西游记010c:05 (如意棒)0113:01 (不死)0117:00-03 (宝种类改变)0118:63 (宝数量)雪人兄弟0369:07 (1P全能力+不死)036a:07 (2P全能力+不死)037e:20 (无敌)的金手指应换算成另一种形式0369-01-07036a-01-07037e-01-20代码(Y区)原人0482-01-05 闪烁无敌烟山90坦克#1 0045-01-02 基地是可修复钢墙02 基地是不可修复钢墙00 #1 0100-01-02 敌人被定时#1 0051-01-64 P1生命#1 0052-01-64 P2生命#2 00A8-01-60 P1加俩星后(推铁)#2 00A9-01-60 P2加俩星后(推铁)#2 0089-01-10 P1防弹罩(无敌)#2 008A-01-10 P2防弹罩(无敌)#2 007F-01-1C 敌方坦克随机增加#2 0086-01-40 Power位置横向X#2 0087-01-D0 Power位置纵向Y#2 0088-01-06 Power类型 00帽01定时02锹03星04炸弹05坦克06枪07船#1 0178-01-A0 P1推草#1 0179-01-A0 P2推草#1 0101-01-63 P1加枪后(推铁/打不死)#1 0102-01-63 P2加枪后(推铁/打不死)#1 0170-01-FF P1加船后(过河/打不死)#1 0171-01-FF P2加船后(过河/打不死)影子传说Legend of Kage, The (U)#1 002B-01-09 人数#1 0041-01-02 LV#1 0046-01-60 20(分身,隐身)60(分身,隐身,八向剑)#2 0046-01-80 金刚咒,数值改为20或者60来关掉。

DC1846A Demo Manual

1dc1846afDESCRIPTIONUltralow Noise and SpuriousFractional-N SynthesizerDemonstration circuit 1846A features the L TC ®6947, an Ultralow Noise and Spurious Fractional-N Synthesizer.DC1846A provides 50Ω SMA connectors for the reference frequency (REF+) and the two single-ended RF outputs (RF+ and RF–).L , L T , L TC, L TM, Linear Technology and the Linear logo are registered trademarks and FracNWizard is a trademark of Linear Technology Corporation. All other trademarks are the property of their respective owners.A DC590 USB serial controller board is used for SPI com-munication with the LTC6947, controlled by the supplied FracNWizard™ software.Design files for this circuit board are available at/demoFigure 1. DC1846A Connections2dc1846afDEMO MANUAL DC1846A QUICK START PROCEDUREThe DC1846A is easy to set up to evaluate the performance of the LTC6947. Follow the procedure below.The DC590 and FracNWizard application are required to control the DC1846A through a personal computer (PC).DC590 ConfigurationPlace the DC590 jumpers in the following positions (refer to Figure 2):JP4: EE – Must be in the EN position.JP5: ISO – ON must be selected.JP5: SW – ON must be selected.JP6: VCCIO – 3.3V must be selected. This sets the SPI port to 3.3V operation.Connect the DC590 to one of your computer’s USB ports with the included USB cable.FracNWizard InstallationThe FracNWizard software is used to communicate with the LTC6947 synthesizer. It uses the DC590 to translate between USB and SPI-compatible serial communica-tions formats. It also includes advanced PLL design and simulation capabilities. The following are the FracNWizard system requirements:• Windows Operating System: Windows XP, Windows 2003 Server, Windows Vista, Windows 7• Microsoft .NET 3.5 SP1 or later • Windows Installer 3.1 or later • Linear Technology’s DC590 hardwareFigure 2. DC590 Jumper and Connector Locations3dc1846afDEMO MANUAL DC1846AQUICK START PROCEDUREDownload the FracNWizard setup file at: /FracNWizardRun the FracNWizard setup file and follow the instructions given on the screen. The setup file will verify and/or install Microsoft .NET and install the FracNWizard. Refer to the Help menu for software operation.DC1846A Configuration1. Connect a 100MHz reference frequency source (at J2) and signal analyzers to RF+ and/or RF– (at J6 and/or J7) using the SMA connectors (see Figure 1 and the Typical DC1846A Requirements and Characteristics table).Be sure to terminate any unused RF output with 50Ω, or poor spurious performance may result.2. Choose the MUTE jumper setting:JP1: GND/3.3V - MUTE position. Select GND to mute the RF output, 3.3V to unmute.3. Connect the GND, 3.3V, 5V banana jacks and the V+VCO turret to a power supply and apply power (see Figure 1 and the Typical DC1846A Requirements and Characteristics table).4. Connect the DC590 to the DC1846A with the provided ribbon cable.5. Run the FracNWizard application.6. In FracNWizard, click File -> Load Settings and point to the “LTC6947_100MHz.fracnset” file.The red LED on the DC1846A should turn on indicating that the loop is locked at 2415MHz.Figure 3. FracNWizard Screenshot4dc1846afDEMO MANUAL DC1846A QUICK START PROCEDUREDC1846A RECONFIGURATIONT roubleshootingIf the red LED does not illuminate, follow the instructions below:1. Verify that you are able to communicate with the DC1846A. The bottom status line in FracNWizard should read “LTC6947” and “Comm Enabled”. Refer to FracNWizard’s T roubleshoot and Help if not.2. Verify that the3.3V, 5V and V+VCO have the correct voltages on them and that the reference frequency is applied to the REF+ SMA input.If the red LED is on but you cannot detect an RF output, make sure the DC1846A jumper JP1 is at the 3.3V position. Run Help -> T roubleshoot in FracNWizard if the problem is not resolved.The DC1846A is flexible and allows the use of a variety of VCOs and the choice to employ either an active or pas-sive loop filter. The following covers the hardware recon-figuration of the DC1846A. Refer to FracNWizard’s Help and the LTC6947 data sheet to better understand how to change programmed parameters on the DC1846A.Installing Different Tunable DevicesThe DC1846A permits the use of different tunable oscil-lators, such as VCOs and VCXOs. There are two different oscillator footprints on the board: U3, which accommodates the popular 0.5 × 0.5 in. package, and U4, which accom-modates another common 14mm × 9 mm package with four or six pins. An external connectorized VCO can alsodrive the LTC6947 through J5. Table 1 gives options to customize the DC1846’s VCOs. When using an active loop filter, an additional pole is required in the loop filter to limit the op amp’s noise contribution to the VCO phase noise.Selecting Loop Filter TypeThe DC1846A can use either an active or a passive loop filter, depending upon the application. Some VCO tuning voltage ranges are greater than the LTC6947 charge pump voltage range (refer to the LTC6947 data sheet). In such cases, an active loop filter using an op amp can deliver the required tuning voltage. Table 2 summarizes these options. FracNWizard helps determine the component values listed in this table.Table 1. Oscillator OptionsTUNABLE DEVICE SELECTION COMPONENTSRESISTOR FOR ADDITIONAL POLECAPACITOR FOR ADDITIONAL POLEPOWERENABLE PIN OR REMARKSU3*C26 ≅ 100pF, depopulate R2_F3, C25 and C28*R2_F2 = 0Ω for passiveloop filter*R2_F2 = 75Ω for active loop filter C3_F2 = Open for passive loop filter*Pick C3_F2 such that1/(2π × R2_F2 × C3_F2) ≅ 15 × the loop bandwidth in Hz for active loop filterDetermined by U3device power supply specification, up to 24V applied to V+VCO turret U4C28 ≅ 100pF, depopulate R2_F2, C25 and C26R2_F3 = 0Ω for passiveloop filter R2_F3 ≅ 75Ω for active loop filter C3_F3 = Open for passive loop filterPick C3_F3 such that1/(2π × R2_F3 × C3_F3) ≅ 15 × the loop bandwidth in Hz for active loop filter Determined by U4device power supply specification, up to 24V applied to V+VCXO turret Use EN turret to control pin 2 of U4 if needed ExternalC25 ≅ 100pF, R15 = 0Ω Ohms, depopulate R13, C26 and C28---Selection components are for an active loop filter. Connect the external VCO output to J5. Use CPGAIN to tune the external device.*These are the default installation options. For the DC1846A-A, U3 is populated with CVCO55CC-2328-2536 from Crystek5dc1846afDEMO MANUAL DC1846ATYPICAL DC1846A REQUIREMENTS AND CHARACTERISTICSDC1846A RECONFIGURATIONTable 2. Loop Filter OptionsLOOP FIL TER TYPESELECTION RESISTORSRZ FROMFRACNWIZARDCI FROMFRACNWIZARD CP FROMFRACNWIZARD POWER CPINV BOX, SYSTEM TAB IN FRACNWIZARD PassiveR14 and R16 = 0Ω, depopulate R13 and R15RZ_P CI1_P in parallel with CI2_P CP_PNoneUncheckedActive R13 (except when using an external VCO) and R15 = 0Ω, depopulate R14 and R16RZ_A CI1_A in parallel with CI2_ACP_ADetermined by the maximum allowed tune voltage of the populated VCO (U3 or U4), up to 24V applied to V+OA turretCheckedPARAMETER INPUT OR OUTPUT PHYSICAL LOCATION DETAILS3.3V Power SupplyInput J9 and J10 banana jacks Low noise and spur-free 3.3V, 103mA**5V Charge Pump Power Supply Input J11 and J12 banana jacks Low noise and spur-free 5V, 22mA**5V VCO Power Supply Input V+VCO turret Low noise and spur-free 5V, 30mA**REF+, Reference Frequency Input J2 SMA connectorLow noise 100MHz**, 6 to 10dBm into 50Ω, see NoteRF+ and RF–T wo Outputs J6 and J7 SMA connectors***2328 to 2536MHz** in 190.7Hz** steps, 0dBm Loop Bandwidth–Set by loop filter component values30.7kHz****These values are for the “DC1846A_100MHz.fracnset” file and included VCO.***Any unused RF output must be terminated with 50Ω, or poor spurious performance may result.Note: A low noise 100MHz reference frequency, such as the Wenzel 501-04516D OCXO, is recommended. If using a different frequency, make sure to update the Fref and R_DIV boxes under the System tab in FracNWizard so that Fpfd is still 50MHz. For example, if a 250MHz clock is used, Fref should be changed to 250MHz and R_DIV to 5. Ref BST and FIL T under the System tab in FracNWizard might need to be changed if the reference frequency and/or power is different than what is recommended in the table above. More information can be found in the LTC6947 data sheet.DEMO MANUAL DC1846APARTS LISTITEM QTY REFERENCE PART DESCRIPTION MANUFACTURER/PART NUMBER 10CI1_A, C3_F2, C3_F3, CP_A, C14CAP, 0603OPT26CI1_P, C5, C12, C13, C18, C31CAP, 0603 1.0µF 10% 10V X7R TAIYO YUDEN, LMK107B7105KA-T 30CI2_P, CI2_A CAP, 1206OPT41CP_P CAP, 0603 47nF 10% 50V X7R AVX 06035C473KAT2A53C1, C19, C33CAP, 7361 47µF 10% 35V, 7361AVX TAJV476K035RNJ63C2, C21, C35CAP, 0805 0.1µF 10% 50V X7R AVX 08055C104KAT2A72C3, C16CAP, 7343 330µF 10% 10V TANT AVX TPME337K010R003589C4, C6, C11, C30, C36, C39, C41, C43, C44CAP, 0402 0.1µF 10% 10V X7R TAIYO YUDEN, LMK105B7104KV-F 91C7CAP, 7343 47µF 10% 20V TANT AVX TAJD476K020RNJ102C8, C15CAP, 0402 1µF 10% 16V X5R TDK C1005X5R1C105K114C17, C23, C34, C45CAP, 0402 0.01µF 10% 16V X7R AVX 0402YC103KAT2A121C2_F1CAP, 0603 33nF 10% 50V X7R AVX 06035C333KAT2A130C25, C28CAP, 0402OPT144C26, C29, C37, C38CAP, 0402 100pF 10% 16V NPO AVX 0402YA101KAT2A151D1LED, RED PANASONIC LN1251CTR1610E3, E6, E11-E18TURRET MILL-MAX 2501-2-00-80-00-00-07-0 171JP1HEADER, 3-PIN 2mm SAMTEC TMM-103-02-L-S184J2, J5, J6, J7CONN, SMA 50Ω EDGE-LAUNCH E.F. JOHNSON, 142-0701-851190J3, J4CONN, SMA 50Ω Straight OPT204J9, J10, J11, J12JACK, BANANA KEYSTONE 575-4211J13HEADER, 7 DUAL PIN, 2mm MOLEX 87831-1420220L1IND, 0402OPT232L2, L3IND, 0402 68nH 5%COILCRAFT 0402HPH-68NXJLW241L1_F1RES, 0805, 0Ω JUMPER VISHAY CRCW08050000Z0EA250L1_F2, L1_F3IND, 0805OPT262R1_F1, RZ_P RES, 0603 21Ω 1% 1/10W VISHAY CRCW060321R0FKED275R1, R2, R11, R20, R26RES, 0402 4.99kΩ 1% 1/16W VISHAY CRCW04024K99FKED281R4RES, 0402 330Ω 1% 1/16W NIC NRC04F3300TRF291R5RES, 0402 51.1Ω 1% 1/10W VISHAY CRCW040251R1FKED304R7, R8, R18, R19RES, 0402 200kΩ 1% 1/16W VISHAY CRCW0402200KFKED314R9, R14, R16, R2_F2RES, 0603 0Ω JUMPER VISHAY CRCW06030000Z0EA323R12, R21, R22RES, 0402 100Ω 5% 1/16W VISHAY CRCW0402101RJKED330R13, R15, R2_F3, RZ_A, R31RES, 0603OPT340R23, R24RES, 0402OPT355R25, R27, R28, R29, R30RES, 0402 0Ω JUMPER VISHAY CRCW04020000Z0EA361U1IC, QFN28IUFD-4X5LINEAR TECH. LTC6947IUFD371U2IC, LOW NOISE AMP, SO8LINEAR TECH. LT1678IS8#PBF381U3IC, VCO CRYSTEK, CVCO55CC-2328-2536390U4IC, CRYSTAL OSCILLATOR OPT402U5, U10IC, DUAL BUFFER, SC70FAIRCHILD SEMI NC7WZ17P6X411U8I.C., Serial EEPROM, TSSOP8MICROCHIP, 24LC025-I /ST421U11IC, DUAL TRANSCEIVER, SOT363NXP 74LVC1T45GW431SHUNT ON JP1 (2&3)SHUNT, 2mm CTRS SAMTEC 2SN-BK-G6dc1846afDEMO MANUAL DC1846A SCHEMATIC DIAGRAM7DEMO MANUAL DC1846ASCHEMATIC DIAGRAMNote: The buffers shown on sheet 2 of 2 of the schematic are used to protect the LTC6947 when connected to the DC590 before the LTC6947 is powered up. There is no need for such circuitry if the SPI bus is not powered before powering up the LTC6947. The EEPROM is for identification and is not neededto program the LTC6947.8dc1846af9dc1846afDEMO MANUAL DC1846AInformation furnished by Linear Technology Corporation is believed to be accurate and reliable. However, no responsibility is assumed for its use. Linear Technology Corporation makes no representa-tion that the interconnection of its circuits as described herein will not infringe on existing patent rights.LAYOUT TOP LAYER10dc1846afDEMO MANUAL DC1846ALinear Technology Corporation1630 McCarthy Blvd., Milpitas, CA 95035-7417(408) 432-1900 ● FAX : (408) 434-0507 ● www.linear .comLINEAR TECHNOLOGY CORPORA TION 2014LT 0514 • PRINTED IN USADEMONSTRATION BOARD IMPORTANT NOTICELinear Technology Corporation (L TC) provides the enclosed product(s) under the following AS IS conditions:This demonstration board (DEMO BOARD) kit being sold or provided by Linear Technology is intended for use for ENGINEERING DEVELOPMENT OR EVALUATION PURPOSES ONL Y and is not provided by L TC for commercial use. As such, the DEMO BOARD herein may not be complete in terms of required design-, marketing-, and/or manufacturing-related protective considerations, including but not limited to product safety measures typically found in finished commercial goods. As a prototype, this product does not fall within the scope of the European Union directive on electromagnetic compatibility and therefore may or may not meet the technical requirements of the directive, or other regulations.If this evaluation kit does not meet the specifications recited in the DEMO BOARD manual the kit may be returned within 30 days from the date of delivery for a full refund. THE FOREGOING WARRANTY IS THE EXCLUSIVE WARRANTY MADE BY THE SELLER TO BUYER AND IS IN LIEU OF ALL OTHER WARRANTIES, EXPRESSED, IMPLIED, OR STATUTORY, INCLUDING ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR ANY PARTICULAR PURPOSE. EXCEPT TO THE EXTENT OF THIS INDEMNITY, NEITHER PARTY SHALL BE LIABLE TO THE OTHER FOR ANY INDIRECT , SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES.The user assumes all responsibility and liability for proper and safe handling of the goods. Further , the user releases L TC from all claims arising from the handling or use of the goods. Due to the open construction of the product, it is the user’s responsibility to take any and all appropriate precautions with regard to electrostatic discharge. Also be aware that the products herein may not be regulatory compliant or agency certified (FCC, UL, CE, etc.).No License is granted under any patent right or other intellectual property whatsoever. L TC assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or any other intellectual property rights of any kind.L TC currently services a variety of customers for products around the world, and therefore this transaction is not exclusive .Please read the DEMO BOARD manual prior to handling the product . Persons handling this product must have electronics training and observe good laboratory practice standards. Common sense is encouraged .This notice contains important safety information about temperatures and voltages. For further safety concerns, please contact a L TC applica-tion engineer .Mailing Address:Linear Technology 1630 McCarthy pitas, CA 95035Copyright © 2004, Linear Technology Corporation。

LT3935 36V, 4A同步降压LED驱动器说明书