verilog-Chapter1

verilog语言参考目录说明

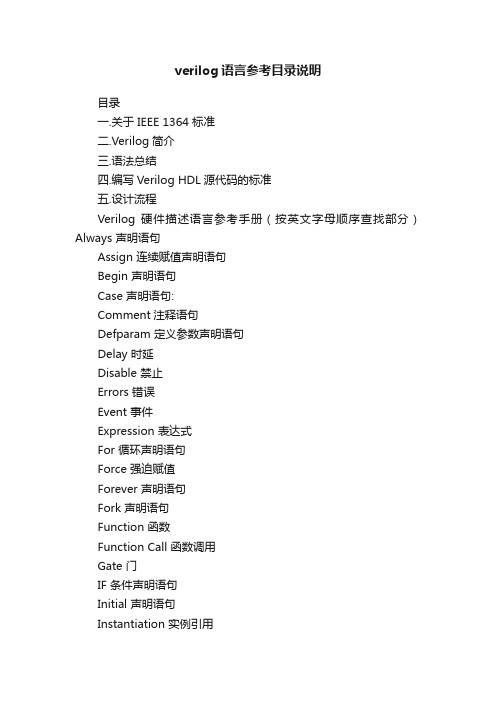

verilog语言参考目录说明目录一.关于 IEEE 1364 标准二.Verilog简介三.语法总结四.编写Verilog HDL源代码的标准五.设计流程Verilog 硬件描述语言参考手册(按英文字母顺序查找部分)Always 声明语句Assign 连续赋值声明语句Begin 声明语句Case 声明语句:Comment注释语句Defparam 定义参数声明语句Delay 时延Disable 禁止Errors 错误Event 事件Expression 表达式For 循环声明语句Force 强迫赋值Forever 声明语句Fork 声明语句Function 函数Function Call 函数调用Gate 门IF 条件声明语句Initial 声明语句Instantiation 实例引用Module 模块定义Name 名字Hierarchical Names 分级名字Upwards Name Referencing 向上索引名Net 线路连接Number 数Operators 运算符Parameter 参数PATHPULSE$ 路径脉冲参数Port 端口Procedural Assignment 过程赋值语句Procedural Continuous Assignment 过程连续赋值语句Programming Language Interface 编程语言接口Register 寄存器Repeat 重复执行语句Reserved Words 关键词Specify 指定的块延时Specparam 延时参数Statement 声明语句Strength 强度String 字符串Task 任务Task Enable 任务的启动Timing control 定时控制User Defined Primitive 用户自定义原语While 条件循环语句Compiler Directives 编译器指示Standard Compiler Directives 标准的编译器指示Non-Standard Compiler Directives 非标准编译器指示系统任务和函数 System task and function标准的系统任务和函数$display, $monitor, $strobe, $write 等$fopen 和$fclose$readmemb 和 $readmemh$timeformat[(Units,Precision,Suffix,MinFieldWidth)]; $printtimescale$stop$finish$time,$stime,和 $realtime$realtobits 和 $bitstoreal$rtoi 和 $itor随机数产生函数1)$random2)$dist_chi_square3)$dist_erlang4)$dist_exponential5)$dist_normal6)$dist_poisson7)$dist_t8)$dist_uniform指定块内的定时检查系统任务Specify Block Timing Checks1)$hold2)$nochange3)$period4)$recovery5)$setup6)$setuphold7)$skew8)$width记录数值变化的系统任务 Value Change Dump Tasks1)$dumpfile2)$dumpvars3)$dumpoff;4)$dumpon;5)$dumpall;6)$dumplimit( FileSize);7) $dumpflush;非标准的系统任务和函数$countdrivers$list$input$scope and $showscopes$key, $nokey, $log and $nolog$reset[$reset_count$reset_value$save(“FileName”);$incsave(“FileName”);$restart(“FileName”);$showvars[( NetOrRegister,...)];$getpattern( MemoryElement);$sreadmemb (Memory, StartAddr, FinishAddr, String, ...); $sreadmemh (Memory, StartAddr, FinishAddr, String, ...); $scale(DelayName); {Returns realtime}常用系统任务和函数的详细使用说明$display 和 $write$fopen and $fclose$monitor 等$readmemb 和 $readmemh$strobe$timeformat随机模型 Stochastic Modelling$q_initialize$q_add$q_remove$q_full$q_exam定时检查 Timing Checks$hold$nochange$period$recovery$setup$setuphold$skew$width记录数值变化的系统任务 Value Change Dump Tasks $dumpfile $dumpvars$dumpoff;$dumpon;$dumpall;$dumplimit$dumpflush;Command Line Options 命令行的可选项。

verilog教程

verilog教程Verilog是一种硬件描述语言(HDL),用于描述数字系统的行为和结构。

它是一种流行的HDL,广泛用于硬件设计和验证领域。

本教程将介绍Verilog的基本概念和语法,以帮助初学者入门。

一、Verilog的基本概念1.1 什么是VerilogVerilog是一种描述数字系统的语言,它可以用来描述硬件电路、验证设计的正确性以及进行电路仿真。

1.2 Verilog的应用领域Verilog广泛应用于硬件设计和验证领域,包括用于开发ASIC(应用特定集成电路)、FPGA(现场可编程门阵列)以及其他数字系统的设计。

1.3 Verilog的版本Verilog有多个版本,包括Verilog-1995、Verilog-2001以及最新的Verilog-2005、这些版本之间有一些语法和功能上的差异。

二、Verilog的语法结构2.1模块和端口在Verilog中,所有的电路描述都是由模块(module)组成的。

模块是电路的基本组成单元,可以看作是一个黑盒子,它接受一些输入,产生一些输出。

2.2信号声明在Verilog中,我们需要声明所有的输入和输出信号。

可以使用`input`和`output`关键字来声明这些信号。

2.3电路实现Verilog允许使用多种语句和结构来描述电路的行为和结构。

这些语句包括顺序语句、条件语句、循环语句以及层次结构。

2.4实例化模块在一个模块中,我们可以实例化其他的模块。

这样可以将一个大的电路拆分成多个小的模块,方便编写和测试。

三、Verilog的仿真和验证3.1静态验证Verilog语言本身提供了很多语法和语义层面的验证功能,对于语法和类型错误会有相应的提示。

3.2激励设计在进行电路验证时,我们需要为输入信号提供激励。

Verilog提供了一种称为`testbench`的特殊模块,用于生成输入信号并将其应用到待验证的电路中。

3.3波形仿真在Verilog中,我们可以使用仿真器来模拟电路的行为,并生成波形图来验证电路是否按预期工作。

Verilog的讲义52页PPT

0

0x

9

9.40ns

9

01

10

10.00ns 10

11

19

19.40ns 19

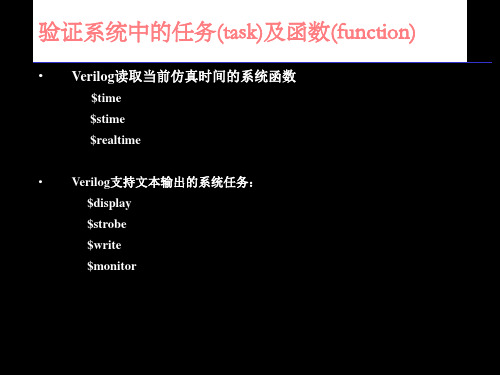

显示信号值 — $display

• $display输出参数列表中信号的当前值。 语法:$display([“ format_specifiers”,] <argument_ list>)

• $display输出时自动换行。

%m %t

hex octal decimal binary ASCII string strength module time

转义符

\t \n \\

\" \< 1-3 digit octal number> %0d

tab 换行 反斜杠 双引号 上述的ASCII表示 无前导0的十进制数

显示信号值—$write和$strobe

9.53ns

initial

10

01

begin

10 10.00ns 10

11

$display("time realtime20stime19\.t53ns

20

in1 \t o1 ");

10

$timeformat(-9, 2, "ns", 10);

$monitor("%d %t %d \t %b \t %b", $time, $realtime,

• $write与$display相同,不同的是不会自动换行。

$write($time, “%b \t %h \t %d \t %o \t”, sig1, sig2, sig3, sig4);

• $strobe与$display相同,不同的是在仿真时间前进之前的信号值。 而$display和$write立即显示信号值。也就是说$strobe显示稳定状态 信号值,而$display和$write可以显示信号的中间状态值。

Verilog HDL简明教程中文版

中文版Verilog HDL简明教程Verilog HDL是一种硬件描述语言,用于从算法级、门级到开关级的多种抽象设计层次的数字系统建模。

被建模的数字系统对象的复杂性可以介于简单的门和完整的电子数字系统之间。

数字系统能够按层次描述,并可在相同描述中显式地进行时序建模。

Verilog HDL 语言具有下述描述能力:设计的行为特性、设计的数据流特性、设计的结构组成以及包含响应监控和设计验证方面的时延和波形产生机制。

所有这些都使用同一种建模语言。

此外,Verilog HDL语言提供了编程语言接口PLI,通过该接口可以在模拟、验证期间从设计外部访问设计,包括模拟的具体控制和运行。

Verilog HDL语言不仅定义了语法,而且对每个语法结构都定义了清晰的模拟、仿真语义。

因此,用这种语言编写的模型能够使用Verilog仿真器进行验证。

语言从C编程语言中继承了多种操作符和结构。

Verilog HDL提供了扩展的建模能力,其中许多扩展最初很难理解。

但是,Verilog HDL语言的核心子集非常易于学习和使用,这对大多数建模应用来说已经足够。

当然,完整的硬件描述语言足以对从最复杂的芯片到完整的电子系统进行描述。

第1章简介Verilog HDL是一种硬件描述语言,用于从算法级、门级到开关级的多种抽象设计层次的数字系统建模。

被建模的数字系统对象的复杂性可以介于简单的门和完整的电子数字系统之间。

数字系统能够按层次描述,并可在相同描述中显式地进行时序建模。

Verilog HDL 语言具有下述描述能力:设计的行为特性、设计的数据流特性、设计的结构组成以及包含响应监控和设计验证方面的时延和波形产生机制。

所有这些都使用同一种建模语言。

此外,Verilog HDL语言提供了编程语言接口,通过该接口可以在模拟、验证期间从设计外部访问设计,包括模拟的具体控制和运行。

Verilog HDL语言不仅定义了语法,而且对每个语法结构都定义了清晰的模拟、仿真语义。

verilog教程

verilog教程当您开始学习Verilog时,以下是一些重要的基础知识和概念。

1. Verilog是一种硬件描述语言(HDL),用于描述和设计数字电路。

它可以用于模拟、合成和验证电路。

2. Verilog使用模块化的设计风格。

每个设计都由一个或多个模块组成,每个模块有自己的输入和输出。

3. 使用`module`关键字定义一个模块,并在其后给出模块的名称。

```verilogmodule my_module;// 模块主体endmodule```4. 模块内部包含用`input`和`output`声明的端口,用于与其他模块进行通信。

```verilogmodule my_module(input wire a,input wire b,output wire c);// 模块主体endmodule```5. `wire`关键字用于声明连接不同模块的导线。

可以将导线看作是用于传输数字信号的线。

6. 在模块主体中,可以使用`assign`关键字创建逻辑连接。

逻辑连接使用`=`运算符连接输入和输出。

```verilogmodule my_module(input wire a,input wire b,output wire c);assign c = a & b;endmodule```7. 除了逻辑连接外,可以在模块内部使用`always`块创建组合和时序逻辑。

```verilogmodule my_module(input wire a,input wire b,output wire c);reg d;always @(a or b)d = a | b;assign c = d;endmodule```8. Verilog还支持使用`if-else`语句,`case`语句和循环结构等常见的编程结构。

9. 为了模拟和验证设计,可以使用Verilog仿真工具,如ModelSim、VCS等。

第四章 Verilog基本语法(一)PPT教学课件

2020/12/11

玉溪师范学院

参数

➢ 参数是一个常量。用parameter定义一个标识符来代表 一个常量。参数经常用于定义时延和变量的宽度。

格式: parameter param1 = const_expr1,

param2 = const_expr2,

…,

paramN = const_exprN;

assign #XOR_DELAY S=A^B;

assign #AND_DELAY C=A&B;

endmodule

19

TOP HA

2020/12/11

玉溪师范学院

参数值的模块引用

module TOP3(NewA,NewB,NewS,NewC); input NewA, NewB; output NewS,NewC; HA #(5,2) Ha1 (NewA, NewB, NewS, NewC);ut

selb

26

2020/12/11

玉溪师范学院

reg型

寄存器是数据存储单元的抽象 reg型数据常用来表示always块内的指定信号,常代表触

发器 reg型数据用initial或者always块中指定信号 reg型数据的缺省值是x。可以被赋正值或者负值。当它作

为一个表达式中的操作数时候,作为无符号数。 reg数据类型定义格式为

2.0 ; -0.1等

科学记数法,例如:

235.1e2 等于23510.0

234_12e2

等于2341200.0

实数小数通过四舍五入被隐式地转换为最相近的整数。例如:

42.446, 42.45 转换为整数42

92.5, 92.699 转换为整数93

-5.62 转换为整数-6

verilog基本语法、模块写法

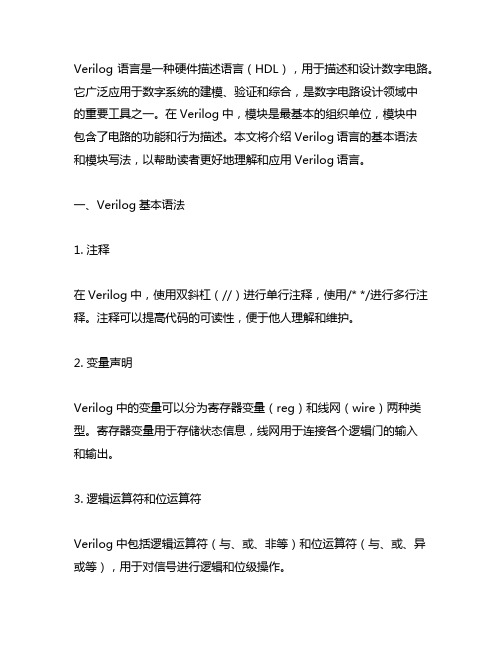

Verilog语言是一种硬件描述语言(HDL),用于描述和设计数字电路。

它广泛应用于数字系统的建模、验证和综合,是数字电路设计领域中的重要工具之一。

在Verilog中,模块是最基本的组织单位,模块中包含了电路的功能和行为描述。

本文将介绍Verilog语言的基本语法和模块写法,以帮助读者更好地理解和应用Verilog语言。

一、Verilog基本语法1. 注释在Verilog中,使用双斜杠(//)进行单行注释,使用/* */进行多行注释。

注释可以提高代码的可读性,便于他人理解和维护。

2. 变量声明Verilog中的变量可以分为寄存器变量(reg)和线网(wire)两种类型。

寄存器变量用于存储状态信息,线网用于连接各个逻辑门的输入和输出。

3. 逻辑运算符和位运算符Verilog中包括逻辑运算符(与、或、非等)和位运算符(与、或、异或等),用于对信号进行逻辑和位级操作。

4. 控制语句Verilog支持if-else语句、case语句等控制语句,用于根据不同条件执行不同的操作。

5. 模拟时钟在Verilog中,时钟是电路中的重要部分,通常使用时钟信号来同步各个元件的动作。

时钟可以通过周期性方波信号来模拟,使用$period 函数可以定义时钟的周期。

6. 仿真指令Verilog提供了多种仿真指令,用于初始化信号、设置仿真时间、输出波形图等操作,有助于仿真和调试电路。

二、模块写法1. 模块定义在Verilog中,一个模块包含了一组功能相关的硬件描述,可以看作是一个小型电路的抽象。

模块通过module关键字进行定义,其中包括模块名、输入输出端口声明等信息。

```verilogmodule adder(input wire [3:0] a,input wire [3:0] b,output reg [4:0] c);// 模块内部逻辑描述endmodule```2. 端口声明模块的端口包括输入端口(input)和输出端口(output),可以通过wire和reg进行声明。

verilog(1)

Z or z

High Impedance

0、1代表常见的布尔状态或者电平的状态 X常用于仿真中表示发生冲突或者错误,也可用于表示“don’t care” Z代表电路中的高阻状态 0、1、Z状态存在于真实的电路当中

9

常量

整数型:

8’b0100_1011

实数:1.34,1.3e2(130) 字符串:“FourValue”

基于名字

7

语法规范与注释

标志符由数字、字母、符号($)和下划线构成,但

是必须以字母或者下划线作为首字符 标志符区分大小写 语句遵循自由格式,可以每一条语句占用一行或者 多条语句共用一行 基本语句以“;”结束 注释有两种形式“//”和“/* */”

//单行注释 /* 多行注释 可以单行也可以跨行 */

有关Verilog的 全部权利都移交 OVI Cadence购买 Verilog版权 Verilog XL 诞生 1980 s

,

1990

Verilog IEEE1364-2001 标准发布

1987 1989 Synopsys公 司支持 Verilog输入

4

Verilog is a HDL

软件编程语言最终被转换为机器指令,可以在一台

– ABEL、ISPS、VHDL、Verilog、SystemC、SystemVerilog ……

3

Verilog语言的发展历史

“Verilog”= “Verification” + “Logic”

Verilog IEEE1364-2005 标准发布 使用模拟和数字 的Verilog 标准 发布 1995 1999 Verilog IEEE1364-1995 标准发布 Verilog HDL 公开发表 2001 2005 并入 SystemVerilog 标准IEEE 1800 2009

Verilog入门教程笔记

将编码后的信号还原成原始信号,常用于数据解压缩和控制信号生成。例如, 将3个输入信号译码成8个输出信号的3-8译码器。

多路选择器设计实例

多路选择器(Multiplexer)

根据选择信号从多个输入信号中选择一个输出,常用于数据选择和路由。例如,2选1 多路选择器、4选1多路选择器等。

明确CPU需要实现哪些指令集,具备哪些功能,以及达到什么样的性 能指标。

选择合适的架构

根据需求和性能指标,选择适合的CPU架构,如RISC或CISC。

设计指令集

根据所选架构,设计相应的指令集,包括指令格式、操作码、寻址方 式等。

规划寄存器组

设计寄存器组,包括通用寄存器、特殊功能寄存器等,以满足指令执 行和数据存储的需求。

03

组合逻辑电路设计

基本门电路实现方法

01

02

03

04

05

与门(AND Gate)或门(OR Gate) 非门(NOT Gate)与非门(NAND 或非门(NOR

Ga…

Gat…

实现逻辑与操作,当所有输 入为高电平时输出高电平。

实现逻辑或操作,当任一输 入为高电平时输出高电平。

实现逻辑非操作,将输入信 号取反后输出。

实现二进制数的减法运算,可 以通过加法器和取反器来实现。

实现二进制数的乘法运算,通 常采用逐位相乘再相加的方式 实现。

实现二进制数的除法运算,通 常采用逐位相除再减去的方式 实现,也可以使用更高效的算 法如SRT除法算法等。

04

时序逻辑电路设计

触发器类型及特点介绍

RS触发器

具有置0、置1和保持功能,是基 本存储单元。

数字电路的设计。

发展历程

verilog基础一

2013-6-13

8

一 Verilog HDL 语言架构

� 模块 � 时延 � 描述方式

2013-6-13

9

描述方法

� � � � 数据流描述方法 行为描述方法 结构化描述方法 混合设计描述方法

2013-6-13

10

数据流描述方法

� assign [delay] LHS_net = RHS_expression; � LHS_net 必须是线网变量 � 多个assign之间0时刻并行执行 � 连续赋值 � 抽象层次较低 如 …… assign #1 abar = ~A; assign #1 bbar = ~B; assign #2 z[0] = ~(abar & bbar & en); assign #2 z[1] = ~(abar ) ……

2013-6-13 15

结构化描述方法

�内置门级原语 �内置开关级原语 �内置用户定义的原语 �模块实例

2013-6-13

16

结构化描述方法

一位全加器结构

a b cin cout

, b, cin,cout , sum); module FA(a FA(a, cin,cout, ; input a,b,cin a,b,cin; ; output cout,sum cout,sum; // HDL modeling of 1 bit // full adder functionality assign { count,sum } = a+b+cin; {count,sum count,sum} endmodule

25

注释

� //到本行结束 � /* 可以扩展至多行 */ Wire [0:3] abus; //地址总线

verilog语法基础

verilog语法基础Verilog语法基础Verilog是一种硬件描述语言(HDL),用于描述数字电路和系统。

它是一种基于事件的语言,能够描述电路的结构和行为。

本文将介绍Verilog语法的基础知识,包括模块、端口、信号、赋值和运算等。

一、模块(Module)在Verilog中,模块是描述电路的基本单元。

一个模块可以包含多个端口和信号,并定义了电路的功能和结构。

模块的定义使用关键字module,后跟模块的名称和端口列表。

二、端口(Port)Verilog中的端口是模块与外部环境进行通信的接口。

端口可以是输入端口、输出端口或双向端口。

输入端口用于接收外部信号,输出端口用于输出信号至外部,而双向端口则可同时进行输入和输出。

端口的定义使用关键字input、output或inout,后跟端口的类型和名称。

三、信号(Signal)Verilog中的信号用于在模块内部传递和存储数据。

信号可以是寄存器类型或线网类型。

寄存器类型信号用于存储数据,线网类型信号用于传递数据。

信号的定义使用关键字reg或wire,后跟信号的宽度和名称。

四、赋值(Assignment)在Verilog中,使用赋值语句将值分配给信号或变量。

赋值语句可以是阻塞式赋值或非阻塞式赋值。

阻塞式赋值使用等号(=)将右侧的值赋给左侧的信号,而非阻塞式赋值使用双等号(<=)进行赋值。

赋值语句的左侧可以是信号或变量,右侧可以是常数、信号、变量或表达式。

五、运算(Operator)Verilog中支持多种运算,包括算术运算、逻辑运算、位运算和比较运算等。

算术运算包括加法、减法、乘法和除法等;逻辑运算包括与、或、非和异或等;位运算包括位与、位或、位非和位异或等;比较运算包括等于、不等于、大于、小于等。

运算符可以用于常数、信号、变量或表达式之间的运算。

六、条件语句(Conditional Statement)Verilog中的条件语句用于根据条件选择执行不同的操作。

verilog核心语法

verilog核心语法Verilog是一种硬件描述语言(HDL),用于描述数字电路和系统的行为和结构。

下面我将从多个角度来介绍Verilog的核心语法。

1. 模块声明:Verilog中,模块是描述数字电路的基本单元。

模块声明的语法如下:module 模块名(输入端口声明, 输出端口声明, 内部信号声明);// 模块内部逻辑描述。

endmodule.其中,输入端口声明和输出端口声明指定了模块的接口,内部信号声明定义了模块内部使用的信号。

2. 数据类型:Verilog支持多种数据类型,包括位(bit)、向量(vector)、整数(integer)、实数(real)等。

可以使用`reg`关键字声明寄存器类型,使用`wire`关键字声明线网类型。

例如:reg [7:0] a; // 8位寄存器。

wire [3:0] b; // 4位线网。

integer c; // 整数类型。

real d; // 实数类型。

3. 运算符:Verilog支持常见的运算符,包括算术运算符(+、-、、/、%)、逻辑运算符(&&、||、!)、位运算符(&、|、^、~)等。

此外,还有条件运算符(?:)和赋值运算符(=、<=、>=、+=、-=等)。

4. 语句:Verilog中常用的语句有:过程语句(always),用于描述组合逻辑和时序逻辑。

常见的过程语句有`always @()`和`always @(posedge clk)`,分别表示组合逻辑和时钟上升沿触发的时序逻辑。

条件语句(if-else):用于根据条件执行不同的语句块。

语法如下:if (条件)。

// 条件为真时执行的语句块。

else.// 条件为假时执行的语句块。

循环语句(for、while):用于重复执行一段代码块。

语法如下:for (初始化; 条件; 更新)。

// 循环体。

while (条件)。

// 循环体。

分支语句(case):根据表达式的值选择执行不同的语句块。

Verilog 01

SOC与ESDA设计技术 与 设计技术

半导体工艺技术的不断进步,使芯片集成度越来越高。近几年工艺上可 以实现一亿个晶体管(100M)的集成规模,如此大规模的集成电路,实际 上已经可以把一个完整的电子系统集成到一个芯片上,因而称之为片上 系统SOC。因此要求软件公司提供系统级的设计工具,也就是要将EDA 发展成ESDA(Electronic System Design Automatic)。 新开发的工具应具备协同开发的功能,也传达了最先进的设计理念。如: Synopsys公司的CoCentric System Studio,Mentor的Seamless CVE系统。

模拟电路 Analog

集成电路芯片及下游产品

芯片制造流程

1.Design .

2.Photo mask production .

芯片制造流程

4. Sawing the Ingot .

纯度: 纯度:0.99999999999

3. Silicon Crystal Growing .

5. Wafer Polishing .

参考类

IEEE Std 1364-2001,IEEE Standard Verilog® Hardware , ® Description Language; ; IEEE Std 1364.1™-2002,IEEE Standard for Verilog® Register ™ , ® Transfer Level Synthesis Verilog HDL design liberary

Intel Pentium 4

IC设计技术的发展过程

手工设计阶段 CAD设计技术 设计技术 EDA设计技术 设计技术 SOC与ESDA设计技术 与 设计技术 EDA工具的软、硬件平台及配置 工具的软、 工具的软 电子CAD技术的范畴与功能 电子 技术的范畴与功能

verilog语法(一)Verilog基础知识

verilog语法(⼀)Verilog基础知识本节主要讲解了 Verilog 的基础知识,包括 7 个⼩节,下⾯我们分别给⼤家介绍这 7 个⼩节的内容。

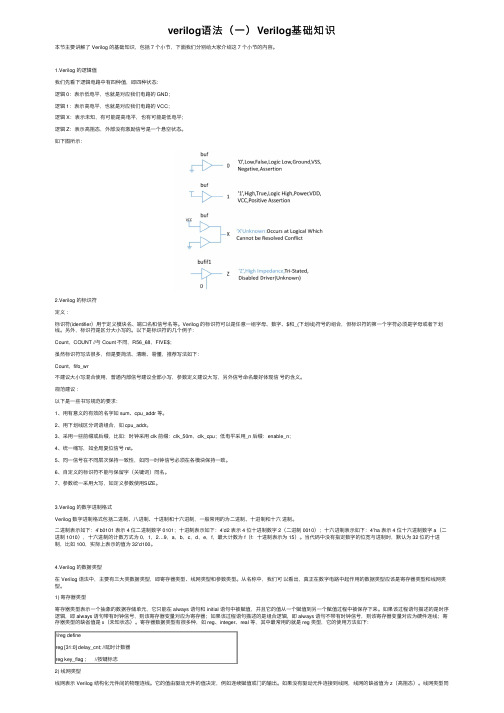

1.Verilog 的逻辑值我们先看下逻辑电路中有四种值,即四种状态:逻辑 0:表⽰低电平,也就是对应我们电路的 GND;逻辑 1:表⽰⾼电平,也就是对应我们电路的 VCC;逻辑 X:表⽰未知,有可能是⾼电平,也有可能是低电平;逻辑 Z:表⽰⾼阻态,外部没有激励信号是⼀个悬空状态。

如下图所⽰:2.Verilog 的标识符定义:标识符(identifier)⽤于定义模块名、端⼝名和信号名等。

Verilog 的标识符可以是任意⼀组字母、数字、$和_(下划线)符号的组合,但标识符的第⼀个字符必须是字母或者下划线。

另外,标识符是区分⼤⼩写的。

以下是标识符的⼏个例⼦:Count,COUNT //与 Count 不同,R56_68,FIVE$;虽然标识符写法很多,但是要简洁、清晰、易懂,推荐写法如下:Count,fifo_wr不建议⼤⼩写混合使⽤,普通内部信号建议全部⼩写,参数定义建议⼤写,另外信号命名最好体现信号的含义。

规范建议:以下是⼀些书写规范的要求:1、⽤有意义的有效的名字如 sum、cpu_addr 等。

2、⽤下划线区分词语组合,如 cpu_addr。

3、采⽤⼀些前缀或后缀,⽐如:时钟采⽤ clk 前缀:clk_50m,clk_cpu;低电平采⽤_n 后缀:enable_n;4、统⼀缩写,如全局复位信号 rst。

5、同⼀信号在不同层次保持⼀致性,如同⼀时钟信号必须在各模块保持⼀致。

6、⾃定义的标识符不能与保留字(关键词)同名。

7、参数统⼀采⽤⼤写,如定义参数使⽤SIZE。

3.Verilog 的数字进制格式Verilog 数字进制格式包括⼆进制、⼋进制、⼗进制和⼗六进制,⼀般常⽤的为⼆进制、⼗进制和⼗六进制。

⼆进制表⽰如下:4’b0101 表⽰ 4 位⼆进制数字 0101;⼗进制表⽰如下:4’d2 表⽰ 4 位⼗进制数字 2(⼆进制 0010);⼗六进制表⽰如下:4’ha 表⽰ 4 位⼗六进制数字 a(⼆进制 1010),⼗六进制的计数⽅式为 0,1,2…9,a,b,c,d,e,f,最⼤计数为 f(f:⼗进制表⽰为 15)。

verilog教程

verilog教程Verilog是一种硬件描述语言(HDL),用于设计和描述数字电路。

它是一种事件驱动的语言,可以用来描述时序逻辑和组合逻辑。

Verilog可以用于设计和验证各种数字电路,从简单的门电路到复杂的处理器和系统。

Verilog的语法和结构与C语言相似,它由模块、端口、信号和行为描述组成。

Verilog中的模块是模块化设计的基本单元,可以将模块集成到更大的设计中。

模块可以具有输入端口、输出端口和内部信号。

输入和输出端口用于与其他模块进行通信,而内部信号用于在模块内部传递和保存数据。

Verilog的行为描述方式包括并行块和顺序块。

并行块表示同时执行的代码,而顺序块表示按顺序执行的代码。

Verilog中的并行块使用关键字"always @(posedge clock)"来表示,其中的代码只在时钟上升沿触发时执行。

顺序块使用关键字"always @(*)"来表示,其中的代码在输入信号变化时立即执行。

在Verilog中,可以使用各种逻辑运算符,如AND、OR、NOT和XOR,来实现组合逻辑。

此外,还可以使用各种触发器和寄存器类型,如D触发器和JK触发器,来实现时序逻辑。

通过将组合逻辑和时序逻辑结合起来,可以实现复杂的数字电路。

Verilog的仿真可以使用各种工具,如ModelSim和Vivado,来验证设计的正确性。

仿真可以通过将输入信号施加到设计中,然后观察输出信号的变化来进行。

如果输出信号与预期的结果一致,那么设计就是正确的。

在Verilog中,还可以使用分层设计的概念来实现模块的结构化和组织。

通过使用层次化模块,可以将设计划分为更小的模块,并将它们组合在一起以实现更大的系统。

尽管Verilog的学习曲线可能有点陡峭,但它是数字电路设计中最常用和最强大的工具之一。

通过掌握Verilog,您可以实现自己的数字电路设计,并进行验证和测试。

总之,Verilog是一种用于设计和描述数字电路的硬件描述语言。

verilog第一~第六讲PPT

西安电子科技大学

雷达信号处理国防科技重点实验室

1.1

门级结构描述

一个逻辑网络是由许多逻辑门和开关所组成,因此用逻辑门的模型 来描述逻辑网络是最直观的。Verilog HDL提供了一些门类型的关键 字,可以用于门级结构建模。

1.1.1 与非门、或门和反向器等及其说明语法

西安电子科技大学 雷达信号处理国防科技重点实验室

2.1

加法器

在数字信号处理的快速运算电路中常常用到多位数字 量的加法运算,这时需要用到并行加法器。并行加法器比串 行加法器快得多,电路结构也不太复杂。

用Verilog HDL 来描述加法器是相当容易的,只需要把运 算表达式写出就可以了。

module add_4( X, Y, sum, C); input [3 : 0] X, Y; output [3: 0] sum; output C; assign {C, Sum } = X + Y; endmodule

1) flop f1op_d( d1, clk, clrb, q, qn); 2) flop flop_d (.clock(clk),.q(q),.clear(clrb),.qb(qn),.data(d1));

显而易见,通过Verilog HDL模块的调用,可以构成任 何复杂结构的电路。这种以结构方式所建立的硬件模型不仅 是可以仿真的,也是可综合的,这就是以门级为基础的结构 描述建模的基本思路。

综合工具能自 动把以上源代码综 合成一个八位比较 器

雷达信号处理国防科技重点实验室

2.4 多路器

多路器是一 个多输入、单输 出的组合逻辑电 路,在数字系统 中有着广泛的应 用。它可以根据 地址码的不同, 从多个输入数据 中选取一个,让 其输出到公共的 输出端。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Digital Design Flow

Verilog Digital System Design Copyright Z. Navabi, 2006

January 2006

2

Digital System Design Automation with Verilog

As the size and complexity of digital systems increase, more computer aided design (CAD) tools are introduced into the hardware design process. Early simulation and primitive hardware generation tools have given way to sophisticated design entry, verification, high-level synthesis, formal verification, and automatic hardware generation and device programming tools. Growth of design automation tools is largely due to hardware description languages (HDLs) and design methodologies that are based on these languages. Based on HDLs, new digital system CAD tools have been developed and are now widely used by hardware designers. One of the most widely used HDLs is the Verilog HDL. Because of its wide acceptance in digital design industry, Verilog has become a must-know for design engineers and students in computerhardware-related fields.

Formal Verification

Pass / Fail Report Property Coverage Counter Examples

Compilation and Synthesis

Analysis Synthesis Routing and placement

C++ Classes, Language Representation

Formal Verification

Pass / Fail Report Property Coverage Counter Examples

FPLD Design Flow

Verilog Digital System Design Copyright Z. Navabi, 2006

January 2006

Y=a&d&w w=a&b|c

Timing Analysis

Presynthesis Verification

1.6 ns

FPLD Design Flow (Continued)

January 2006

2 ns

Verilog Digital System Design Copyright Z. Navabi, 2006

Testbench in Verilog

module testbench (); generate data; process data; endmodule

Behavioral Simulation

Assertion Verification

Violation Report; Time of Violation; Monitor Coverage

January 2006

1010...

Verilog Digital System Design Copyright Z. Navabi, 2006

4

Digital Design Flow

Design Entry Phase

Design Entry in Verilog

module design (. . .); assign . . . always . . . compi (. . .) endmodule Comp1 U1 (. . .); Comp2 U2 (. . .); ... Compn Un (. . .); always (posedge clk) begin . . . end if (…) bus = w; else . . .

Digital System Design Automation with Verilog

1.1 Digital Design Flow 1.1.1 Design entry 1.1.2 Testbench in Verilog 1.1.3 Design validation 1.1.4 Compilation and synthesis 1.1.5 Postsynthesis simulation 1.1.6 Timing analysis 1.1.7 Hardware generation 1.2 Verilog HDL 1.2.1 Verilog evolution 1.2.2 Verilog attributes 1.2.3 The verilog language 1.3 Summary

Verilog Digital System Design Copyright Z. Navabi, 2006 3

January 2006

Digital Design Flow

Design Entry in Verilog

module design (. . .); assign . . . always . . . compi (. . .) endmodule Comp1 U1 (. . .); Comp2 U2 (. . .); ... Compn Un (. . .); always (posedge clk) begin . . . end if (…) bus = w; else . . .

Y=a&d&w w=a&b|c

Timing Analysis

Synthesis Process

FPLD Design Flow (Continued)

January 2006

2 ns

1.6 ns

Verilog Digital System Design Copyright Z. Navabi, 2006

January 2006

Verilog Digital System Design Copyright Z. Navabi, 2006

6

Digital Design Flow

Behavioral Simulation Assertion Verification

Violation Report; Time of Violation; Monitor Coverage

10

Digital Design Flow

Testbench in Verilog

module testbench (); generate data; process data; endmodule

Timing Analysis

2 ns

1.6 ns

Post-synthesis Simulation

9

Digital Design Flow

Synthesis process: Translating the design into actual hardware of a target device (FPLD, ASIC or custom IC)

January 2006

Verilog Digital System Design Copyright Z. Navabi, 2006

5

Digital Design Flow

Digital Design Flow begins with specification of the design at various levels of abstraction. Design entry phase: Specification of design as a mixture of behavioral Verilog code, instantiation of Verilog modules, and bus and wire assignments

Testbench in Verilog

module testbench (); generate data; process data; endmodule

Behavioral Simulation

Assertion Verification

Violation Report; Time of Violation; Monitor Coverage

Postsynthesis Verification

Device Programming

ASIC Netlist

EDIF or other netlists

Custom IC Layout

1010...

FPLD Design Flow (Continued)

January 2006 Verilog Digital System Design Copyright Z. Navabi, 2006 11

Verilog Digital System Design Copyright Z. Navabi, 2006