MRF9085S中文资料

WM8805中文资料

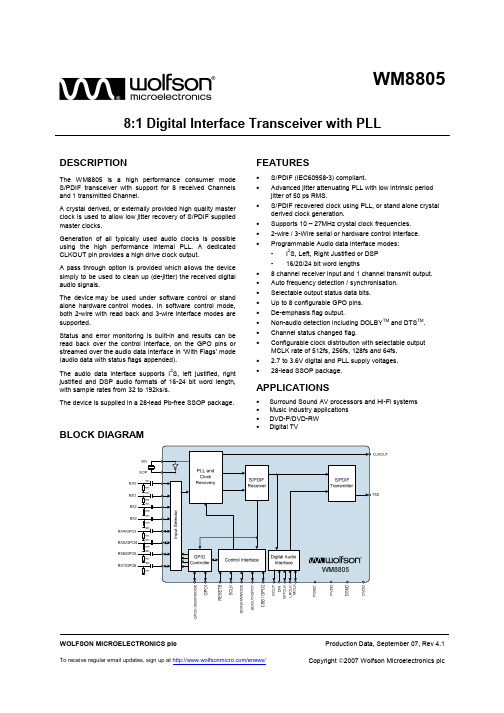

wWM88058:1 Digital Interface Transceiver with PLLWOLFSON MICROELECTRONICS plcProduction Data, September 07, Rev 4.1 DESCRIPTIONThe WM8805 is a high performance consumer mode S/PDIF transceiver with support for 8 received Channels and 1 transmitted Channel.A crystal derived, or externally provided high quality master clock is used to allow low jitter recovery of S/PDIF supplied master clocks.Generation of all typically used audio clocks is possible using the high performance internal PLL. A dedicated CLKOUT pin provides a high drive clock output.A pass through option is provided which allows the device simply to be used to clean up (de-jitter) the received digital audio signals.The device may be used under software control or stand alone hardware control modes. In software control mode, both 2-wire with read back and 3-wire interface modes aresupported.Status and error monitoring is built-in and results can be read back over the control interface, on the GPO pins or streamed over the audio data interface in ‘With Flags’ mode (audio data with status flags appended).The audio data interface supports I 2S, left justified, right justified and DSP audio formats of 16-24 bit word length, with sample rates from 32 to 192ks/s.The device is supplied in a 28-lead Pb-free SSOP package.BLOCK DIAGRAMFEATURES• S/PDIF (IEC60958-3) compliant.• Advanced jitter attenuating PLL with low intrinsic period jitter of 50 ps RMS.• S/PDIF recovered clock using PLL, or stand alone crystal derived clock generation.• Supports 10 – 27MHz crystal clock frequencies. • 2-wire / 3-Wire serial or hardware control interface. •Programmable Audio data interface modes: - I 2S, Left, Right Justified or DSP - 16/20/24 bit word lengths• 8 channel receiver input and 1 channel transmit output. • Auto frequency detection / synchronisation. •Selectable output status data bits.• Up to 8 configurable GPO pins. • De-emphasis flag output.• Non-audio detection including DOLBY TM and DTS TM . • Channel status changed flag.•Configurable clock distribution with selectable output MCLK rate of 512fs, 256fs, 128fs and 64fs. • 2.7 to 3.6V digital and PLL supply voltages. • 28-lead SSOP package. APPLICATIONS• Surround Sound AV processors and Hi-Fi systems • Music industry applications • DVD-P/DVD-RW• Digital TVWM8805Production DataTABLE OF CONTENTS DESCRIPTION (1)BLOCK DIAGRAM (1)FEATURES (1)APPLICATIONS (1)TABLE OF CONTENTS (2)PIN CONFIGURATION (3)ORDERING INFORMATION (3)PIN DESCRIPTION (4)ABSOLUTE MAXIMUM RATINGS (5)RECOMMENDED OPERATING CONDITIONS (6)SUPPLY CURRENT (6)ELECTRICAL CHARACTERISTICS (6)MASTER CLOCK TIMING (7)DIGITAL AUDIO INTERFACE – MASTER MODE (7)DIGITAL AUDIO INTERFACE – SLAVE MODE (8)CONTROL INTERFACE – 3-WIRE MODE (9)CONTROL INTERFACE – 2-WIRE MODE (10)DEVICE DESCRIPTION (11)INTRODUCTION (11)POWER UP CONFIGURATION (12)HARDWARE CONTROL MODE (18)DIGITAL ROUTING CONTROL (20)MASTER CLOCK AND PHASE LOCKED LOOP (21)SOFTWARE MODE INTERNAL CLOCKING (21)HARDWARE MODE INTERNAL CLOCKING (30)S/PDIF TRANSMITTER (31)S/PDIF RECEIVER (34)GENERAL PURPOSE OUTPUT (GPO) CONFIGURATION (44)DIGITAL AUDIO INTERFACE (45)AUDIO DATA FORMATS (46)REGISTER MAP (53)APPLICATIONS INFORMATION (63)RECOMMENDED EXTERNAL COMPONENTS (63)PACKAGE DIMENSIONS (64)IMPORTANT NOTICE (65)ADDRESS: (65)w PD Rev 4.1 September 07Production Data WM8805wPD Rev 4.1 September 07PIN CONFIGURATION( Top View )ORDERING INFORMATIONDEVICE TEMPERATURERANGE PACKAGE MOISTURESENSITIVITY LEVELPEAK SOLDERING TEMPERATUREWM8805GEDS -25 to +85oC 28-lead SSOP (Pb-free) MSL1 260o C WM8805GEDS/R -25 to +85o C28-lead SSOP (Pb-free, tape and reel)MSL1260o CNote:Reel quantity = 2,000WM8805Production DatawPD Rev 4.1 September 07PIN DESCRIPTIONPIN NAME Type DESCRIPTION1 DVDD Supply Digital core supply2 RX1 Digital In S/PDIF receive channel 13 RX0 Digital In S/PDIF receive channel 04 SCLKDigital In/Out Control interface clock / TRANS_ERR flag in hardware control mode. See note 2.5 GPO0 / SWIFMODEDigital In/Out General purpose digital output or selected functionality at hardware reset. See note 2.6 GPO1 Digital Out General purpose digital output7 SDIN / HWMODE Digital Input Control interface data input and hardware/software mode select at hardware reset. See note 2.8 SDOUT / GPO7 Digital In/Out Control interface data output / NON_AUDIO flag in hardware control mode / GPO in 2-wire software control mode. See note 2.9 CSB / GPO2 Digital In/Out Chip select / UNLOCK flag in hardware control mode / GPO in 2-wire software control mode. See note 2. 10 RESETB Digital Input System reset (active low) 11 PVDD Supply PLL core supply12 PGND Supply PLL ground 13CLKOUTDigital OutHigh drive clock output at 64fs, 128fs, 256fs and 512fs14 XOP Digital Output Crystal output 15 XIN Digital Input Crystal input 16 DOUT Digital Out Audio interface data output 17 DIN Digital In Audio interface data input 18 BCLK Digital In/Out Audio interface bit clock19 LRCLK Digital In/Out Audio interface left/right word clock 20 MCLK Digital In/Out Master clock input or output 21 TX0 Digital Out S/PDIF transmit22 RX7 / GPO6 Digital In/Out S/PDIF receive channel 7 or general purpose digital output 23 RX6 / GPO5 Digital In/Out S/PDIF receive channel 6 or general purpose digital output 24 RX5 / GPO4 Digital In/Out S/PDIF receive channel 5 or general purpose digital output 25 RX4 / GPO3Digital In/Out S/PDIF receive channel 4 or general purpose digital output 26 RX3 Digital In S/PDIF receive channel 3 27 RX2Digital InS/PDIF receive channel 228 DGND Supply Digital groundNotes : 1. Digital input pins have Schmitt trigger input buffers.2.Refer to Table 6 Device Configuration at Power up or Hardware ResetProduction Data WM8805wPD Rev 4.1 September 07ABSOLUTE MAXIMUM RATINGSAbsolute Maximum Ratings are stress ratings only. Permanent damage to the device may be caused by continuously operating at or beyond these limits. Device functional operating limits and guaranteed performance specifications are given under ElectricalCharacteristics at the test conditions specified.ESD Sensitive Device. This device is manufactured on a CMOS process. It is therefore generically susceptible to damage from excessive static voltages. Proper ESD precautions must be taken during handling and storage of this device.Wolfson tests its package types according to IPC/JEDEC J-STD-020B for Moisture Sensitivity to determine acceptable storage conditions prior to surface mount assembly. These levels are:MSL1 = unlimited floor life at <30°C / 85% Relative Humidity. Not normally stored in moisture barrier bag. MSL2 = out of bag storage for 1 year at <30°C / 60% Relative Humidity. Supplied in moisture barrier bag. MSL3 = out of bag storage for 168 hours at <30°C / 60% Relative Humidity. Supplied in moisture barrier bag. The Moisture Sensitivity Level for each package type is specified in Ordering Information. CONDITIONMIN MAX Digital core and I/O buffer supply voltage -0.3V +5V PLL supply voltage -0.3V +5V Voltage range digital inputs DGND -0.3VDVDD +0.3VMaster Clock Frequency 37MHz Operating temperature range, T A -25°C +85°C Storage temperature -65°C +150°CNote : 1. PLL and digital supplies must always be within 0.3V of each other. 2.PLL and digital grounds must always be within 0.3V of each other.WM8805Production DatawPD Rev 4.1 September 07RECOMMENDED OPERATING CONDITIONSPARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNIT Digital supply range DVDD 2.7 3.6 V GroundDGND 0 V PLL supply range PVDD 2.7 3.6 VGround PGND0 VNote : 1. PLL and digital supplies must always be within 0.3V of each other. 2.PLL and digital grounds must always be within 0.3V of each other.SUPPLY CURRENTPARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNIT Digital supply current I DVDD DVDD =3.3V 14.9 mA PLL supply current I PVDDPVDD = 3.3V 1.7 mAPower consumption DVDD/PVDD = 3.3V 54.8 mW Standby Power consumption DVDD/PVDD = 3.3V Device powered down0.11 mWELECTRICAL CHARACTERISTICSTest ConditionsPVDD = 3.3V, DVDD = 3.3V, PGND = 0V, DGND = 0V, T A = +25o C, fs = 48kHz, MCLK = 256fs unless stated. PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNIT Jitter Characteristics Intrinsic Period JitterJ i50 psDigital Logic Levels (CMOS Levels) Input LOW level V IL 0.3 x DVDD V Input HIGH level V IH 0.7 x DVDD V Output LOW V OL 0.1 x DVDD V Output HIGHV OH0.9 x DVDD VI source 25 mACLOCKOUT buffer drive capabilityI sinkCMOS 20pF load 25 mA S/PDIF Receiver Characteristics Input Resistance23 k ΩProduction DataWM8805wPD Rev 4.1 September 07MASTER CLOCK TIMINGFigure 1 Master Clock Timing RequirementsTest ConditionsPVDD = 3.3V, DVDD = 3.3V, PGND = 0V, DGND = 0V, T A = +25o C, fs = 48kHz, MCLK = 256fs unless stated.PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNIT System Clock Timing Information – Slave Mode MCLK System clock cycle time t MCLKY27nsMCLK System clock pulse width high t MCLKH 11 ns MCLK System clock pulse width low t MLCKL 11 ns MCLK Duty cycle40:60 60:40 %Table 1 Slave Mode MCLK Timing RequirementsDIGITAL AUDIO INTERFACE – MASTER MODEFigure 2 Digital Audio Data Timing – Master ModeTest ConditionsPVDD = 3.3V, DVDD = 3.3V, PGND = 0V, DGND = 0V, T A = +25o C, fs = 48kHz, MCLK = 256fs unless stated.PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNIT Audio Data Input Timing InformationLRCLK propagation delay from BCLK falling edget DL 0 10 ns DOUT propagation delay from BCLK falling edget DDA 0 10 ns DIN setup time to BCLK rising edget DST 10 ns DIN hold time from BCLK rising edget DHT10 nsTable 2 Digital Audio Data Timing – Master ModeWM8805Production DatawPD Rev 4.1 September 07DIGITAL AUDIO INTERFACE – SLAVE MODEFigure 3 Digital Audio Data Timing – Slave ModeTest ConditionsPVDD = 3.3V, DVDD = 3.3V, PGND = 0V, DGND = 0V, T A = +25o C, fs = 48kHz, MCLK = 256fs unless stated.PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNIT Audio Data Input Timing InformationBCLK cycle time t BCY 50 ns BCLK pulse width high t BCH 20 ns BCLK pulse width low t BCL 20 ns LRCLK set-up time to BCLK rising edget LRSU 10 ns LRCLK hold time from BCLK rising edge t LRH 10 ns DIN set-up time to BCLK rising edget DS 10 ns DIN hold time from BCLK rising edget DH 10 ns DOUT propagation delay from BCLK falling edget DD0 10 nsTable 3 Digital Audio Data Timing – Slave ModeProduction DataWM8805wPD Rev 4.1 September 07CONTROL INTERFACE – 3-WIRE MODEFigure 4 Control Interface Timing – 3-Wire Serial Control ModeTest ConditionsPVDD = 3.3V, DVDD = 3.3V, PGND = 0V, DGND = 0V, T A = +25o C, fs = 48kHz, MCLK = 256fs unless stated. PARAMETER SYMBOL MIN TYP MAX UNITProgram Register Input Information SCLK rising edge to CSB rising edge t SCS 60 ns SCLK cycle time t SCY 80 nsSCLK duty cycle40/60 60/40 %SDIN to SCLK set-up timet DSU 20 ns SDIN hold time from SCLK rising edget DHO 20 ns SDOUT propagation delay from SCLK rising edge t DL 5 ns CSB pulse width hight CSH 20 ns CSB rising/falling to SCLK rising t CSS 20 ns SCLK glitch suppressiont ps 2 8 nsTable 4 Control Interface Timing – 3-Wire Serial Control ModeWM8805Production DatawPD Rev 4.1 September 07CONTROL INTERFACE – 2-WIRE MODEFigure 5 Control Interface Timing – 2-Wire Serial Control ModeTest ConditionsPVDD = 3.3V, DVDD = 3.3V, PGND = 0V, DGND = 0V, T A = +25o C, fs = 48kHz, MCLK = 256fs unless stated. PARAMETER SYMBOL MIN TYP MAX UNITProgram Register Input Information SCLK cycle time t SCY 2500 nsSCLK duty cycle 40/60 60/40 %SCLK frequency400 kHz Hold Time (Start Condition) t STHO 600 ns Setup Time (Start Condition) t STSU 600 ns Data Setup Time t DSU 100 nsSDIN, SCLK Rise Time 300 nsSDIN, SCLK Fall Time 300 nsSetup Time (Stop Condition) t STOP 600 ns Data Hold Time t DHO 900 ns SCLK glitch suppressiont ps 2 8 nsTable 5 Control Interface Timing – 2-Wire Serial Control ModeDEVICE DESCRIPTIONINTRODUCTIONFEATURES•IEC-60958-3 compatible with 32 to 192k frames/s support.AES-3 data frames.• Supports•Support for reception and transmission of S/PDIF data.•Clock synthesis PLL with reference clock input and low jitter output.•Supports input reference clock frequencies from 10MHz to 27MHz.•Dedicated high drive clock output pin.•Register controlled channel status bit configuration.•Register read-back of recovered channel status bits and error flags.•Detection of non-audio data, sample rate and de-emphasis.•Programmable GPOs for error flags and frame status flags.The WM8805 is an IEC-60958 compatible S/PDIF transceiver with support for up to eight receivedS/PDIF data streams and one transmitted S/PDIF data stream.The receiver performs data and clock recovery, and transmits recovered data from the chip eitherthrough the digital audio interface or, alternatively, the device can loop the received S/PDIF databack out through the S/PDIF transmitter producing a de-jittered S/PDIF transmit data stream. Therecovered clock may be routed to a high drive output pin for external use. If there is no S/PDIF inputdata stream the PLL can be configured to output all standard MCLK frequencies or it can beconfigured to maintain the frequency of the last received S/PDIF data stream.The transmitter generates S/PDIF frames where audio data may be sourced from the S/PDIFreceiver or the digital audio interface. Timing for the S/PDIF transmitter interface can be sourcedfrom the internally derived MCLK in loop through mode or it can be taken from an external source.S/PDIF FORMATS/PDIF is a serial, bi-phase-mark encoded data stream. An S/PDIF frame consists of two sub-frames. Each sub-frame is made up of:•Preamble – a synchronization pattern used to identify the start of a 192-frame block or sub-frame•4-bit Auxiliary Data (AUX) – ordered LSB to MSB•20-bit Audio Data (24-bit when combined with AUX) – ordered LSB to MSB•Validity Bit – a 1 indicates invalid data in the associated sub-frame•User Bit – over 192-frames, this forms a User Data Block•Channel Bit – over 192-frames, this forms a Channel Status Block•Parity Bit – used to maintain even parity over the sub-frame (not including the preamble)An S/PDIF Block consists of 192 frames. Channel and user blocks are incorporated within the 192-frame S/PDIF Block. For Consumer mode only the first 40-frames are used to make up the Channeland User blocks. Figure 6 illustrates the S/PDIF format. The WM8805 does not support transmissionof user channel data. Received user channel data may be accessed via GPO pins.w PD Rev 4.1 September 07wPD Rev 4.1 September 07Figure 6 S/PDIF FormatPOWER UP CONFIGURATIONThe operating mode of the WM8805 is dependent upon the state of SDIN, SCLK, SDOUT, CSB and GPO0 when the device is powered up or a hardware reset occurs. Table 6 summarises the configuration options.HW RESET = 0HW RESET = 1SWMODE HWMODE SWMODE HWMODESDIN HWMODE / SWMODE SelectSDINN/ASCLKN/A AIF_MS SCLKGPO(TRANS_ERR)2-wire 3-wire SDOUTN/A AIF_CONF[0]GPO SDOUT GPO(NON_AUDIO)2-wire 3-wire2-wire 3-wireCSBDevice AddressN/ATXSRCGPO CSB GPO(UNLOCK)P I NGPO02-wire/3-wireMode SelectAIF_CONF[1] GPOGPO(GEN_FLAG)Note: AIF_CONF[1:0] configures the audio interface when the device operates in hardware mode. Refer to Table 16 for description of modes.Table 6 Device Configuration at Power up or Hardware ResetwPD Rev 4.1 September 07When the device powers up, all power up configuration pins are configured as inputs for a minimum of 9.4us and a maximum of 25.6us following the release of the external reset. The times are based on 27MHz and 10MHz crystal clock frequencies respectively. This enables the pins to be sampled and the device to be configured before the pins are released to their selected operating conditions. Figure 7 illustrates how SDIN is sampled.Figure 7 Pin Sampling On Power Up or Hardware ResetIf the device is powered up in Software control mode, all functions of the device are powered down by default and must be powered up individually by writing to the relevant bits of the PWRDN register (Table 7). In Hardware Control Mode, all functions of the device are powered up by default. REGISTER ADDRESSBITLABELDEFAULTDESCRIPTION0 PLLPD1 PLL Powerdown0 = PLL enabled 1 = PLL disabled 1 SPDIFRXPD 1S/PDIF Receiver Powerdown 0 = S/PDIF receiver enabled 1 = S/PDIF receiver disabled 2 SPDIFTXPD1S/PDIF Transmitter Powerdown0 = S/PDIF transmitter enabled 1 = S/PDIF transmitter disabled3 OSCPD0 Oscillator Power Down0 = Power Up 1 = Power Down 4 AIFPD0 Digital Audio Interface PowerDown0 = Power Up 1= Power Down R30 PWRDN 1Eh5 TRIOP0 Tri-state all Outputs0 = Outputs not tri-stated 1 = Outputs tri-statedTable 7 Power Down RegisterCONTROL INTERFACE OPERATIONControl of the WM8805 is implemented in either hardware control mode or software control mode.The method of control is determined by sampling the state of the SDIN/HWMODE pin at power up orat a hardware reset. If SDIN/HWMODE is low during power up the device is configured in hardwarecontrol mode, otherwise the device is configured in software control mode.SDIN/HWMODEmode0 Hardwaremode1 SoftwareTable 8 Hardware or Software Mode SelectSoftware control is achieved using a 3-wire (3-wire write, 4-wire read) or a 2-wire serial interface.The serial interface format is configured by sampling the state of the GPO0/SWIFMODE pin onpower up or at a hardware reset. If the GPO0/SWIFMODE pin is low the interface is configured in 2-wire mode, otherwise the interface is configured in 3-wire SPI compatible mode.GPO0/SWIFMODEinterface0 2-wireinterface1 3-wireTable 9 Software Mode Control Interface Select3-WIRE (SPI COMPATIBLE) SERIAL CONTROL MODE – REGISTER WRITESDIN is used for the program data, SCLK is used to clock in the program data and CSB is used tolatch in the program data. SDIN is sampled on the rising edge of SCLK. The 3-wire interface writeprotocol is shown in Figure 8.Figure 8 3-Wire Serial Interface Register Write Protocol•W is a control bit indicating a read or write operation. 0 =write operation, 1 = read operation•REGA[6:0] is the register Address.•DIN[7:0] is the data to be written to the register being addressed.•CSB is edge sensitive – the data is latched on the rising edge of CSB.w PD Rev 4.1 September 073-WIRE SERIAL CONTROL MODE REGISTER READ-BACKNot all registers can be read. Only the device ID (registers R0, R1 and R2) and the status registers can be read. These status registers are labelled as “read only” in the Register Map section.The read-only status registers can be read back via the SDOUT pin. The registers can be read by one of two methods, selected by the CONT register bit and the ‘W’ control bit. The oscillator must be powered up before 3-wire control interface read-back is possible.When CONT =1 and ‘W’=0, a single read-only register can be read back by writing to any other register or to a dummy register. The register to be read is determined by the READMUX[2:0] bits. When a write to the device is performed, the device will respond by returning the status byte of the register selected by the READMUX register bits. The data is returned on the SDOUT pin. This 3-wire interface read-back method using a write access is shown in Figure 9.REGISTER ADDRESS BIT LABEL DEFAULT DESCRIPTION2:0 READMUX[2:0] 000 Status Register SelectDetermines which status registeris to be read back:000 = Interrupt Status Register001 = Channel Status Register 1010 = Channel Status Register 2011 = Channel Status Register 3100 = Channel Status Register 4101 = Channel Status Register 5110 = S/PDIF Status RegisterR29SPDRX11Dh3 CONT 0 Continuous Read Enable0 = Continuous read-back modedisabled1 = Continuous read-back modeenabledTable 10 Read-back Control RegisterThe SDOUT pin is tri-state unless CSB is held low; therefore CSB must be held low for the durationof the read.Figure 9 3-Wire Control Interface Read-Back Method 1The second method of reading the read only status registers is If CONT=0 and ‘W’=1. Using thismethod the user can read back directly from a register by reading the register address. The devicewill respond with the contents of the register. The protocol for this read-back method is shown inFigure 10.w PD Rev 4.1 September 07wPD Rev 4.1 September 07Figure 10 3-Wire Control Interface Read-Back Method 22-WIRE SERIAL CONTROL WITH READ-BACK MODEThe WM8805 supports software control via a 2-wire serial bus. Many devices can be controlled by the same bus and each device has a unique 7-bit address (see Table 11).The controller indicates the start of data transfer with a high to low transition on SDIN while SCLK remains high. This indicates that a device address, DEVA(7:1), and data, REG(6:0), will follow. All devices on the 2-wire bus will shift in the next eight bits on SDIN (7-bit address DEVA(7:1), + read/write ‘W’ bit, MSB first). If the device address received matches the address of the WM8805, the WM8805 responds by driving SDIN low on the next clock pulse (ACK). This is a device acknowledgement of an address match. If the address does not match that of the WM8805, the device returns to the idle condition and waits for a new start condition and valid address.Once the WM8805 has acknowledged a matching address, the controller sends the first byte of control data, which is the WM8805 register address (REGA[6:0]). The WM8805 then acknowledges reception of the control data byte by pulling SDIN low for one clock pulse (another ACK). The controller then sends the second byte of control data (DIN[7:0], i.e. the eight bits of register data to be written), and the WM8805 acknowledges again by pulling SDIN low (another ACK).The transfer of data is complete when there is a low to high transition on SDIN while SCLK is high. After receiving a complete address and data sequence the WM8805 returns to the idle state and waits for another start condition. If a start or stop condition is detected out of sequence at any pointduring data transfer (i.e. SDIN changes while SCLK is high), the device returns to the idle condition.Figure 11 2-Wire Serial Control Interface WriteMultiple consecutive register writes can be performed in 2-wire control mode by setting the CONT bit high. This method allows the entire register map to be defined in a one continuous write operation.wPD Rev 4.1 September 07Figure 12 2-Wire Serial Control Interface Multi-WriteThe WM8805 has two possible device addresses, which can be selected using the CSB pin during hardware reset.CSB STATEDEVICE ADDRESS IN2-WIRE MODEADDRESS (X=R/W BIT)X=0 X= 1 Low0111010x0x7A0x75High 0111011x 0x76 0x77Table 11 2-Wire Interface Address Selection2-WIRE SERIAL CONTROL MODE -REGISTER READ-BACKThe WM8805 allows read-back of certain registers in 2-wire mode. The protocol is similar to thatused to write to the device. The controller will issue the device address followed by a write bit, the register index will then be passed to the WM8805. At this point the controller will issue a repeated start condition and resend the device address along with a read bit. The WM8805 will acknowledge this and the WM8805 will become a slave transmitter. The WM8805 will transmit the data from the indexed register on SDIN MSB first. When the controller receives the data it will not acknowledge receipt of the data indicating that it will resume master transmitter control of SDIN. The controller willthen issue a stop command completing the read cycle. Figure 13 illustrates the read protocol.Figure 13 2-Wire Serial Control Interface Read (CONT=0)2-WIRE SERIAL CONTROL MODE – CONTINUOUS READ-BACKAs in 3-wire mode, there are two methods of reading back data: continuous and non-continuous read-back. Continuous read-back is selected by setting CONT to 1. In continuous read-back mode, the device will return the indexed register first followed by consecutive registers in increasing index order until the controller does not acknowledge the data then issues a stop sequence. This is shownin Figure 14Figure 14 2-Wire Serial Interface Continuous Read-Back (CONT=1)wPD Rev 4.1 September 07SOFTWARE REGISTER RESETWriting to register 0000000 will reset the WM8805. This will reset all register bits to their default values. Note that the WM8805 is powered down by default so writing to this register will power down the device.DEVICE ID AND REVISION IDENTIFICATIONRegisters 0,1 and 2 can be read to identify the device ID and IC revision number. Refer to Table 12 for details.REGISTER ADDRESS BIT LABEL DEFAULTDESCRIPTIONRESET N/A Writing to this register will apply a reset to the device. R00RST/DEVID100h7:0DEVID1[7:0] 00000101 Reading from this register will returnthe second part of the device ID00000101 = 0x05 R01 DEVID2 01h (read only) 7:0DEVID2[7:0] 10001000 Reading from this register will returnthe first part of the device ID10001000 = 0x88 R02 DEVREV 02h3:0 DEVREV [3:0]N/AReading from this register will return the device revision. 0x1 = revision 1Table 12 Software Reset Register and Device IDHARDWARE CONTROL MODEThe WM8805 can be operated in either software or hardware control modes. The method of control is determined by sampling the state of the SDIN pin during power up or hard reset. If SDIN is LOW during power up or hardware reset, the WM8805 will be switched into hardware control mode.PIN 0 1SDINHardware Control ModeSoftware Control ModeTable 13 Hardware / Software Mode ConfigurationIn hardware control mode the user has limited control over the configuration of the device. Most of the features will assume default values but some can be configured using external pins. When the device is configured in hardware control mode, all functions of the device are powered up.The clock and data recovery module with the WM8805 will require a 12 MHz crystal derived master clock as the default values for this module cannot be altered in Hardware Control mode.MASTER / SLAVE MODE SELECTIONThe WM8805 can be configured in either master or slave mode In software control mode this is set by writing to AIF_MS in the AIFRX register. In hardware control mode this is controlled by sampling the SCLK pin on power up or hardware reset. PIN(HARDWARE MODE)REGISTER (SOFTWARE MODE) 0 1SCLKAIF_MSSlave Mode Master ModeTable 14 Master / Slave Mode Configuration in Hardware ModeDIGITAL ROUTING CONTROLSee page 20 for a full description of the signal routing options available in the WM8805. In Software control mode the values set in registers TXSRC and RXINSEL determine the S/PDIF Rx data source and destination. In hardware control mode the device can receive data only from RX0 but can set the value of TXSRC directly using the CSB pin. This determines the S/PDIF transmitter data sourcePIN (HARDWARE MODE)REGISTER(SOFTWAREMODE)0 1CSB TXSRC S/PDIFRxAIFRxTable 15 S/PDIF Transmitter Digital Routing Control ConfigurationAUDIO INTERFACE CONTROLIn software control mode the audio data word length and audio data format can be set independently for the receiver and transmitter sides of the interface. However, in hardware control mode both sides of the interface are combined and the configuration is set using SDOUT and GPO0 pins as described in Table 6 and Table 16. Note that AIF_CONF[1:0] configures the audio interface when the device operates in hardware mode.GPO0 / AIFCONF[1]SDOUT /AIFCONF[0]DESCRIPTION0 0 16-bitI2S0 1 24-bitI2S1 0 24-bit Left Justified With Flags1 1 16-bitRightJustifiedTable 16 Digital Audio Interface Control in Hardware Control ModeSTATUS INFORMATIONIn hardware control mode the WM8805 outputs a selection of status flags for the user. Table 17describes the flags which are available and the output pins on which they are available.PIN STATUSFLAGSCLK TRANS_ERRSDOUT NON_AUDIOCSB UNLOCKGPO0 GEN_FLAGTable 17 Hardware Control Mode Status Flag ConfigurationA full description of the status flags is given in Table 45.w PD Rev 4.1 September 07。

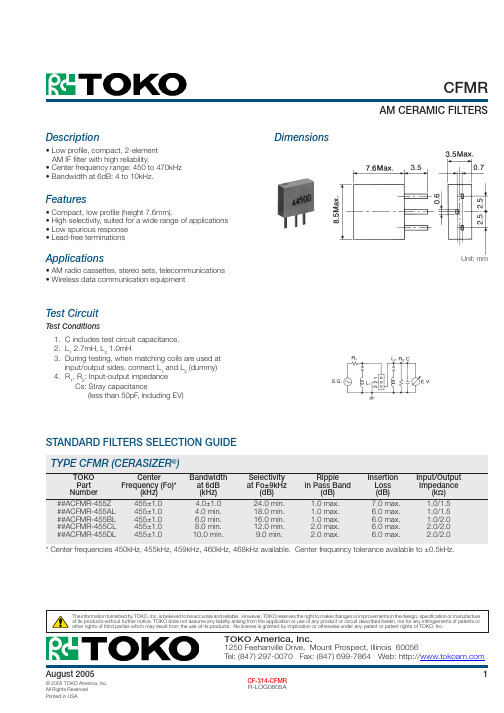

CFMR中文资料

* Center frequencies 450kHz, 455kHz, 459kHz, 460kHz, 468kHz available. Center frequency tolerance available to ±0.5kHz.

The information furnished by TOKO, Inc. is believed to be accurate and reliable. However, TOKO reserves the right to make changes or improvements in the design, specification or manufacture of its products without further notice. TOKO does not assume any liability arising from the application or use of any product or circuit described herein, nor for any infringements of patents or other rights of third parties which may result from the use of its products. No license is granted by implication or otherwise under any patent or patent rights of TOKO, Inc.

© 2005 TOKO America, Inc. All Rights Reserved Printed in USA

CF-314-CFMR R SELECTION GUIDE TYPE CFMR (CERASIZER®)

瑞丰瑞丰W40QI35DS -DF-J-Y型号产品说明书

1-8th Floor, Building #1,10th Industrial Zone, Tian Liao Community, Gong Ming Area, Guang Ming栋一至八楼Web/网址:Features 特征PLCC-2 Package.垂直型表贴封装 Extremely wide viewing angle.发光角度大Suitable for all SMT assembly and solder process.适用于所有的SMT 组装和焊接工艺 Available on tape and reel.适用于载带及卷轴 Moisture sensitivity level: 3.防潮等级:3 Package:4000pcs/reel.包装:4000颗/卷RoHS compliant.RoHS 认证Description 描述The White LED which was fabricated using a blue chip and phosphors 白光LED 由芯片激发荧光粉后,混光形成。

Applications 应用Optical indicator.光学指示 Indoor display.室内显示Landscape lighting,lamp belt. 景观照明,灯带等 General use.其他适合的应用Package DimensionNOTES:1.All dimensions units are millimeters. (所有尺寸标注单位为毫米)2.All dimensions tolerances are 0.2mm unless otherwise noted. (除特别标注外,所有尺寸允许公差为±0.2毫米)Electrical / Optical Characteristics at Ts=25°C 电性与光学特性4.The above luminous flux measurement allowance tolerance ±10%. 上述光通量的测试允许公差为±10%.5. Care is to be taken that power dissipation does not exceed the absolute maximum rating of the product. 使用功率不能超过规定的最大值。

徕卡S2中文说明书

imported or sold in the People’s Republic of China

徠卡 S2

订货编号 10 801

徠卡 S2-P

订货编号 10 802

部件名称

Part Name

有毒有害物质和元素

Toxic and Hazardous Substances and Elements

铅 汞 镉 六价铬 多溴联苯 多溴二苯醚

㉂動及固定設定項目 ...................................................29 直接設定色溫 ...............................................................29 透過測量手動設定 .......................................................29 ISO感光度 ........................................................................30 影像㊕性(對比、銳利度、色彩飽和度) ........................31 影像色彩空間..................................................................31 儲存相片資料/記憶卡管理 ................................................31

ca-if1051s 参数

ca-if1051s 参数

CA-IF1051S是一种电子元件,通常被用于电子设备中。

它可能

被用作接口芯片,用于连接不同类型的设备或系统,比如连接传感

器或执行器到控制器或处理器。

这种元件可能有多种参数,包括电

压范围、工作温度范围、通信协议、引脚配置等。

通常这些参数会

在元件的数据手册或规格表中详细描述。

在选择和使用CA-IF1051S 时,需要仔细阅读相关的规格表,以确保它符合特定应用的要求。

此外,CA-IF1051S可能还有一些特定的功能和特性,比如低功耗、高速传输、抗干扰能力等。

这些特性也需要在选择元件时考虑到。

另外,还需要注意元件的封装类型和引脚布局,以确保它可以

方便地集成到设计中。

除了硬件参数和特性外,还需要考虑到软件驱动程序和支持,

以确保CA-IF1051S可以在目标系统中正常工作。

有时厂商会提供相

应的驱动程序和示例代码,这些信息也需要在选择元件时进行考虑。

总的来说,选择和使用CA-IF1051S需要综合考虑其硬件参数、

特性、软件支持等多个方面的因素,以确保它能够满足特定应用的

要求,并且能够方便地集成到目标系统中。

ADS8555SPM;ADS8555SPMR;中文规格书,Datasheet资料

BUSY/INTRANGE/XCLKHW/SWREF/WRRESETENSTBYCSRD/DB[15:0]WORD/BYTEPAR/SERFSCH_A0CONVST_AAGNDREFC_AREF_IOAGNDCH_A1AGNDCH_B0CONVST_BAGNDREFC_BCH_B1AGNDCH_C0CONVST_CAGNDREFC_CCH_C1AGNDADS8555 SBAS531B–DECEMBER2010–REVISED FEBRUARY201116-Bit,Six-Channel,Simultaneous SamplingANALOG-TO-DIGITAL CONVERTERCheck for Samples:ADS8555FEATURES DESCRIPTION•Six SAR ADCs Grouped in Three Pairs The ADS8555contains six low-power,16-bit,successive approximation register(SAR)-based •Maximum Data Rate Per Channel with Internalanalog-to-digital converters(ADCs)with true bipolar Clock and Reference:inputs.Each channel contains a sample-and-hold 630kSPS(Parallel)or450kSPS(Serial)circuit that allows simultaneous high-speed •Maximum Data Rate Per Channel with External multi-channel signal acquisition.Clock and Reference:The ADS8555supports data rates of up to630kSPS 800kSPS(Parallel)or500kSPS(Serial)in parallel interface mode or up to450kSPS if the •Pin-Selectable or Programmable Input Voltageserial interface is used.The bus width of the parallel Ranges:Up to±12V interface can be set to eight or16bits.In serial•Excellent AC Performance:mode,up to three output channels can be activated.91.5dB SNR,–94dB THDThe ADS8555is specified over the extended •Programmable and Buffered Internal industrial temperature range of–40°C to+125°C and Reference:0.5V to2.5V and0.5V to3.0V is available in an LQFP-64package.•Comprehensive Power-Down Modes:Deep Power-Down(Standby Mode)Auto-Nap Power-Down•Selectable Parallel or Serial Interface•Operating Temperature Range:–40°C to+125°C•LQFP-64PackageAPPLICATIONS•Power Quality Measurement•Protection Relays•Multi-Axis Motor Control•Programmable Logic Controllers•Industrial Data AcquisitionPlease be aware that an important notice concerning availability,standard warranty,and use in critical applications of TexasInstruments semiconductor products and disclaimers thereto appears at the end of this data sheet.All trademarks are the property of their respective owners.ADS8555SBAS531B–DECEMBER2010–REVISED This integrated circuit can be damaged by ESD.Texas Instruments recommends that all integrated circuits be handled with appropriate precautions.Failure to observe proper handling and installation procedures can cause damage.ESD damage can range from subtle performance degradation to complete device failure.Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.PACKAGE/ORDERING INFORMATIONFor the most current package and ordering information,see the Package Option Addendum at the end of this document,or visit the device product folder at .ABSOLUTE MAXIMUM RATINGS(1)Over operating free-air temperature range,unless otherwise noted.ADS8555UNIT Supply voltage,HVDD to AGND–0.3to+18VSupply voltage,HVSS to AGND–18to+0.3VSupply voltage,AVDD to AGND–0.3to+6VSupply voltage,BVDD to BGND–0.3to+6V Analog input voltage HVSS–0.3to HVDD+0.3V Reference input voltage with respect to AGND AGND–0.3to AVDD+0.3VDigital input voltage with respect to BGND BGND–0.3to BVDD+0.3V Ground voltage difference AGND to BGND±0.3VInput current to all pins except supply–10to+10mA Maximum virtual junction temperature,T J+150°C Human body model(HBM)±2000V JEDEC standard22,test method A114-C.01,all pinsESD ratingsCharged device model(CDM)±500V JEDEC standard22,test method C101,all pins(1)Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device.These are stress ratingsonly and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied.Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.THERMAL INFORMATIONADS8555THERMAL METRIC(1)PM UNITS64PINSθJA Junction-to-ambient thermal resistance48θJCtop Junction-to-case(top)thermal resistance16θJB Junction-to-board thermal resistance N/A°C/WψJT Junction-to-top characterization parameter N/AψJB Junction-to-board characterization parameter N/AθJCbot Junction-to-case(bottom)thermal resistance N/A(1)For more information about traditional and new thermal metrics,see the IC Package Thermal Metrics application report,SPRA953A.ADS8555 SBAS531B–DECEMBER2010–REVISED FEBRUARY2011RECOMMENDED OPERATING CONDITIONSMIN TYP MAX UNIT Supply voltage,AVDD to AGND 4.55 5.5VLow-voltage levels 2.7 3.0 3.6V Supply voltage,BVDD to BGND5V logic levels 4.55 5.5VInput range=±2×V REF2×V REF16.5VInput supply voltage,HVDD to AGNDInput range=±4×V REF4×V REF16.5VInput range=±2×V REF–16.5–2×V REF VInput supply voltage,HVSS to AGNDInput range=±4×V REF–16.5–4×V REF V Reference input voltage(V REF)0.5 2.5 3.0VInput range=±2×V REF–2×V REF2×V REF V Analog inputs(also see the Analog Inputs section)Input range=±4×V–4×V REF4×V REF VREFOperating ambient temperature range,T A–40+125°C ELECTRICAL CHARACTERISTICSOver recommended operating free-air temperature range of–40°C to+125°C,AVDD=4.5V to5.5V,BVDD=2.7V to5.5V, HVDD=10V to15V,HVSS=–15V to–10V,V REF=2.5V(internal),and f DATA=maximum,unless otherwise noted.ADS8555PARAMETER CONDITIONS MIN TYP(1)MAX UNITDC ACCURACYResolution16BitsNo missing codes16BitsAt T A=–40°C to+85°C–3±1.53LSB Integral linearity error INLAt T A=–40°C to+125°C–4±1.54LSBAt T A=–40°C to+85°C–1±0.75 1.5LSB Differential linearity error DNLAt T A=–40°C to+125°C–1±0.752LSB Offset error–4.0±0.8 4.0mV Offset error drift±3.5μV/°C Gain error Referenced to voltage at REFIO–0.75±0.250.75%FSR Gain error drift Referenced to voltage at REFIO±6ppm/°C Power-supply rejection ratio PSRR At output code FFFFh,related to AVDD60dB SAMPLING DYNAMICSAcquisition time t ACQ280ns Conversion time per ADC t CONV 1.26μs18.5t CCLK Internal conversion clock period t CCLK68.0nsParallel interface,internal clock and reference630kSPS Throughput rate f DATASerial interface,internal clock and reference450kSPSAC ACCURACYAt f IN=10kHz,T A=–40°C to+85°C9091.5dB Signal-to-noise ratio SNRAt f IN=10kHz,T A=–40°C to+125°C8991.5dBAt f IN=10kHz,T A=–40°C to+85°C8789.5dB Signal-to-noise ratio+distortion SINADAt f IN=10kHz,T A=–40°C to+125°C86.589.5dBAt f IN=10kHz,T A=–40°C to+85°C–94–90dB Total harmonic distortion(2)THDAt f IN=10kHz,T A=–40°C to+125°C–94–89.5At f IN=10kHz,T A=–40°C to+85°C9095dB Spurious-free dynamic range SFDRAt f IN=10kHz,T A=–40°C to+125°C89.595dB Channel-to-channel isolation At f IN=10kHz100dBInput Range=±4×V REF48MHz–3dB small-signal bandwidthInput Range=±2×V REF24MHz(1)All values are at T A=+25°C.(2)Calculated on the first nine harmonics of the input frequency.ADS8555SBAS531B–DECEMBER2010–REVISED ELECTRICAL CHARACTERISTICS(continued)Over recommended operating free-air temperature range of–40°C to+125°C,AVDD=4.5V to5.5V,BVDD=2.7V to5.5V, HVDD=10V to15V,HVSS=–15V to–10V,V REF=2.5V(internal),and f DATA=maximum,unless otherwise noted.ADS8555PARAMETER CONDITIONS MIN TYP(1)MAX UNIT ANALOG INPUTRANGE pin/RANGE bit=0–4×V REF4×V REF V Bipolar full-scale range CHXXRANGE pin/RANGE bit=1–2×V REF2×V REF VInput range=±4×V REF10pF Input capacitanceInput range=±2×V REF20pF Input leakage current No ongoing conversion±1μA Aperture delay5ns Aperture delay matching Common CONVST for all channels250ps Aperture jitter50ps EXTERNAL CLOCK INPUT(XCLK)External clock frequency f XCLK An external reference must be used for f XCLK>f CCLK11820MHz External clock duty cycle4555% REFERENCE VOLTAGE OUTPUT(REF OUT)2.5V operation,REFDAC=0x3FF 2.485 2.5 2.515V2.5V operation,REFDAC=0x3FF at+25°C 2.496 2.5 2.504V Reference voltage V REF3.0V operation,REFDAC=0x3FF 2.985 3.0 3.015V3.0V operation,REFDAC=0x3FF at+25°C 2.995 3.0 3.005V Reference voltage drift dV REF/dT±10ppm/°C Power-supply rejection ratio PSRR73dB Output current I REFOUT DC current–22mA Short-circuit current(3)I REFSC50mA Turn-on settling time t REFON10msAt CREF_x pins 4.710μF External load capacitanceAt REFIO pins100470nF Tuning range REFDAC Internal reference output voltage range0.2×V REF V REF V REFDAC resolution10Bits REFDAC differential nonlinearity DNL DAC–1±0.11LSB REFDAC integral nonlinearity INL DAC–2±0.12LSB REFDAC offset error V OSDAC V REF=0.5V(DAC=0x0CC)–4±0.654LSB REFERENCE VOLTAGE INPUT(REF IN)Reference input voltage V REFIN0.5 2.5 3.025VInput resistance100MΩInput capacitance5pF Reference input current1μA SERIAL CLOCK INPUT(SCLK)Serial clock input frequency f SCLK0.136MHz Serial clock period t SCLK0.027810μs Serial clock duty cycle4060% DIGITAL INPUTS(4)Logic family CMOS with Schmitt-TriggerHigh-level input voltage0.7×BVDD BVDD+0.3VLow-level input voltage BGND–0.30.3×BVDD VInput current V I=BVDD to BGND–50+50nA Input capacitance5pF(3)Reference output current is not limited internally.(4)Specified by design.ADS8555 SBAS531B–DECEMBER2010–REVISED FEBRUARY2011ELECTRICAL CHARACTERISTICS(continued)Over recommended operating free-air temperature range of–40°C to+125°C,AVDD=4.5V to5.5V,BVDD=2.7V to5.5V, HVDD=10V to15V,HVSS=–15V to–10V,V REF=2.5V(internal),and f DATA=maximum,unless otherwise noted.ADS8555PARAMETER CONDITIONS MIN TYP(1)MAX UNIT DIGITAL OUTPUTS(5)Logic family CMOSHigh-level output voltage I OH=100μA BVDD–0.6BVDD VLow-level output voltage I OH=–100μA BGND BGND+0.4VHigh-impedance-state output current–5050nA Output capacitance5pF Load capacitance30pF POWER-SUPPLY REQUIREMENTSAnalog supply voltage AVDD 4.5 5.0 5.5V Buffer I/O supply voltage BVDD 2.7 3.0 5.5VInput positive supply voltage HVDD 5.010.016.5VInput negative supply voltage HVSS–16.5–10.0–5.0Vf DATA=maximum30.036.0mAf DATA=250kSPS(auto-NAP mode)14.016.5mA Analog supply current(6)IAVDD Auto-NAP mode,no ongoing conversion,4.0 6.0mAinternal conversion clockPower-down mode0.150.0μAf DATA=maximum0.9 2.0mAf DATA=250kSPS(auto-NAP mode)0.5 1.5mA Buffer I/O supply current(7)IBVDD Auto-NAP mode,no ongoing conversion,0.110.0μAinternal conversion clockPower-down mode0.110.0μAf DATA=maximum 3.0 3.5mAf DATA=250kSPS(auto-NAP mode) 1.6 2.0mA Input positive supply current(8)IHVDD Auto-NAP mode,no ongoing conversion,0.20.3μAinternal conversion clockPower-down mode0.110.0μAf DATA=maximum 3.6 4.0mAf DATA=250kSPS(auto-NAP mode) 1.8 2.2mA Input negative supply current(9)IHVSS Auto-NAP mode,no ongoing conversion,0.20.25μAinternal conversion clockPower-down mode0.110.0μAf DATA=maximum251.7298.5mWf DATA=250kSPS(auto-NAP mode)122.5150.0mW Power dissipation(10)Auto-NAP mode,no ongoing conversion,26.038.3mWinternal conversion clockPower-down mode 3.8580.0μW(5)Specified by design.(6)At AVDD=5V.(7)At BVDD=3V,parallel mode,load capacitance=6pF/pin.(8)At HVDD=15V.(9)At HVSS=–15V.(10)At AVDD=5V,BVDD=3V,HVDD=15V,and HVSS=–15V.48474645444342414039383736353433CH_C1AVDD AVDD CH_C0AGND AGND CH_B1AVDD AVDD CH_B0AGND AGND CH_A1AVDD AVDD CH_A012345678910111213141516DB14/REFBUF ENDB13/SDIDB12DB11DB10/SDO_C DB9/SDO_B DB8/SDO_ABGND BVDDDB7/HB /DC EN EN DB6/SCLK DB5/DCIN_A DB4/DCIN_B DB3/DCIN_C DB2/SEL_C DB1/SEL_B D B 15D B 0/SE L _AR E F /W RE N B U S Y /I N TH W /S WC S F S/P A R /S E RR DA V D DC O N V S T _CA G N DC O N V S T _BR E F C _CC O N V S T _AA G N DS T B YR E F C _BA G N DA G N DA V D DR E F C _AR A N G E /X C L KA G N DR E S E TA G N DW O R D /B Y T ER E F I OH V S SA V D DH V D DA G N DA G N D6463626160595857565554171819202122232425262753525150492829303132ADS8555SBAS531B –DECEMBER 2010–REVISED FEBRUARY 2011EQUIVALENT INPUT CIRCUITSPIN CONFIGURATIONPM PACKAGE LQFP-64(TOP VIEW)ADS8555 SBAS531B–DECEMBER2010–REVISED FEBRUARY2011PIN DESCRIPTIONSDESCRIPTIONNAME PIN#TYPE(1)PARALLEL INTERFACE(PAR/SER=0)SERIAL INTERFACE(PAR/SER=1)Hardware mode(HW/SW=0):Reference buffers enable input.When low,all reference buffers are enabled(mandatory ifinternal reference is used).When high,all reference buffers DB14/REFBUF EN1DIO/DI Data bit14input/output are disabled.Software mode(HW/SW=1):Connect to BGND or BVDD.The reference buffers are controlled by bit C24(REFBUF)incontrol register(CR).Hardware mode(HW/SW=0):Connect to BGND DB13/SDI2DIO/DI Data bit13input/outputSoftware mode(HW/SW=1):Serial data input DB123DIO Data bit12input/output Connect to BGNDDB114DIO Data bit11input/output Connect to BGNDWhen SEL_C=1,data output for channel C DB10/SDO_C5DIO/DO Data bit10input/outputWhen SEL_C=0,this pin should be tied to BGNDWhen SEL_B=1,data output for channel BWhen SEL_B=0,this pin should be tied to BGND DB9/SDO_B6DIO/DO Data bit9input/outputWhen SEL_C=0,data from channel C1are also availableon this outputData output for channel AWhen SEL_C=0,data from channel C0are also available DB8/SDO_A7DIO/DO Data bit8input/output on this outputWhen SEL_C=0and SEL_B=0,SDO_A acts as the singledata output for all channelsBGND8P Buffer I/O ground,connect to digital ground planeBuffer I/O supply,connect to digital supply(2.7V to5.5V).Decouple with a1μF ceramic capacitor or a BVDD9Pcombination of100nF and10μF ceramic capacitors to BGND.Word mode(WORD/BYTE=0):Data bit7input/outputDaisy-chain enable input.Byte mode(WORD/BYTE=1):DB7/HB EN/DC EN10DIO/DI/DI When high,DB[5:3]serve as daisy-chain inputs DCIN[A:C].High byte enable input.If daisy-chain mode is not used,connect to BGND.When high,the high byte is output first onDB[15:8].When low,the low byte is output first onDB[15:8].Word mode(WORD/BYTE=0):Data bit6input/outputDB6/SCLK11DIO/DI Serial interface clock input(36MHz max)Byte mode(WORD/BYTE=1):Connect to BGND or BVDDWord mode(WORD/BYTE=0):Data bit5input/output When DCEN =1,daisy-chain data input for channel ADB5/DCIN_A12DIO/DIWhen DC EN=0,connect to BGNDByte mode(WORD/BYTE=1):Connect to BGND or BVDDWord mode(WORD/BYTE=0):When SEL_B=1and DC EN=1,daisy-chain data input forData bit4input/outputDB4/DCIN_B13DIO/DI channel BByte mode(WORD/BYTE=1):When DCEN =0,connect to BGNDConnect to BGND or BVDDWord mode(WORD/BYTE=0):When SEL_C=1and DC EN=1,daisy-chain data input forData bit3input/outputDB3/DCIN_C14DIO/DI channel CByte mode(WORD/BYTE=1):When DCEN =0,connect to BGNDConnect to BGND or BVDDWord mode(WORD/BYTE=0):Data bit2input/output Select SDO_C input.DB2/SEL_C15DIO/DIWhen high,SDO_C is active.When low,SDO_C is disabled.Byte mode(WORD/BYTE=1):Connect to BGND or BVDDWord mode(WORD/BYTE=0):Data bit1input/output Select SDO_B input.DB1/SEL_B16DIO/DIWhen high,SDO_B is active.When low,SDO_B is disabled.Byte mode(WORD/BYTE=1):Connect to BGND or BVDD(1)AI=analog input;AIO=analog input/output;DI=digital input;DO=digital output;DIO=digital input/output;and P=power supply.ADS8555SBAS531B–DECEMBER2010–REVISED PIN DESCRIPTIONS(continued)DESCRIPTIONNAME PIN#TYPE(1)PARALLEL INTERFACE(PAR/SER=0)SERIAL INTERFACE(PAR/SER=1)Word mode(WORD/BYTE=0):Select SDO_A input.Data bit0(LSB)input/outputDB0/SEL_A17DIO/DI When high,SDO_A is active.When low,SDO_A is disabled.Byte mode(WORD/BYTE=1):Should always be high.Connect to BGND or BVDDWhen CR bit C21=0(BUSY/INT),converter busy status output.Transitions high when a conversion has beenstarted and remains high during the entire process.Transitions low when the conversion data of all six channelsare latched to the output register and remains low thereafter.In sequential mode(SEQ=1in the CR),the BUSY output transitions high when a conversion has been started BUSY/INT18DOand goes low for a single conversion clock cycle(t CCLK)whenever a channel pair conversion is completed.When bit C21=1(BUSY/INT in CR),interrupt output.This bit transitions high after a conversion has beencompleted and goes low with the first read data access.The polarity of BUSY/INT output can be changed using bit C20(BUSY L/H)in the control register.Chip select input.Frame synchronization.CS/FS19DI/DI When low,the parallel interface is enabled.WhenThe falling edge of FS controls the frame transfer.high,the interface is disabled.Read data input.RD20DI When low,the parallel data output is enabled.Connect to BGNDWhen high,the data output is disabled.Hardware mode(HW/SW=0):Conversion start of channel pair C.The rising edge of this signal initiates simultaneous conversion of analog signals at inputs CH_C[1:0].CONVST_C21DISoftware mode(HW/SW=1):Conversion start of channel pair C in sequential mode(CR bit C23=1)only;connect to BGND or BVDD otherwiseHardware mode(HW/SW=0):Conversion start of channel pair B.The rising edge of this signal initiates simultaneous conversion of analog signals at inputs CH_B[1:0].CONVST_B22DISoftware mode(HW/SW=1):Conversion start of channel pair B in sequential mode(CR bit C23=1)only;connect to BGND or BVDD otherwiseHardware mode(HW/SW=0):Conversion start of channel pair A.The rising edge of this signal initiates simultaneous conversion of analog signals at inputs CH_A[1:0].CONVST_A23DISoftware mode(HW/SW=1):Conversion start of all selected channels except in sequential mode(CR bit C23=1):Conversion start of channel pair A onlyStandby mode input.When low,the entire device is powered down(including the internal clock and reference).STBY24DIWhen high,the device operates in normal mode.25,32,37,38,Analog ground,connect to analog ground plane43,44,AGND P Pin25may have a dedicated ground if the difference between its potential and AGND is always kept within 49,52,±300mV.53,55,57,5926,34,Analog power supply(4.5V to5.5V).Decouple each pin with a100nF ceramic capacitor to e an 35,40,additional10μF capacitor to AGND close to the device but without compromising the placement of the smaller AVDD41,46,Pcapacitor.Pin26may have a dedicated power supply if the difference between its potential and AVDD is always 47,50,kept within±300mV.60Hardware mode(HW/SW=0):Input voltage range select input.When low,the analog input range is±4V REF.When high,the analog input range is±2V REF.RANGE/XCLK27DI/DIOSoftware mode(HW/SW=1):External conversion clock input,if CR bit C11(CLKSEL)is set high or internalconversion clock output,if CR bit C10(CLKOUT_EN)is set high.If not used,connect to BVDD or BGND.Reset input,active high.Aborts any ongoing conversions.Resets the internal control register to0x000003FF.The RESET28DIRESET pulse should be at least50ns long.Output mode selection input.When low,data are transferred in word mode usingDB[15:0].When high,data are transferred in byteWORD/BYTE29DI Connect to BGNDmode using DB[15:8]with the byte order controlledby HB EN pin while two accesses are required for acomplete16-bit transfer.Negative supply voltage for the analog inputs(–16.5V to–5V).HVSS30P Decouple with a100nF ceramic capacitor to AGND placed next to the device and a10μF capacitor to AGND closeto the device but without compromising the placement of the smaller capacitor.Positive supply voltage for the analog inputs(5V to16.5V).Decouple with a100nF ceramic capacitor to AGND HVDD31P placed next to the device and a10μF capacitor to AGND close to the device but without compromising theplacement of the smaller capacitor.Analog input of channel A0.The input voltage range is controlled by RANGE pin in hardware mode or CR bit C26 CH_A033AI(RANGE_A)in software mode.Analog input of channel A1.The input voltage range is controlled by RANGE pin in hardware mode or CR bit C26 CH_A136AI(RANGE_A)in software mode.ADS8555 SBAS531B–DECEMBER2010–REVISED FEBRUARY2011PIN DESCRIPTIONS(continued)DESCRIPTIONNAME PIN#TYPE(1)PARALLEL INTERFACE(PAR/SER=0)SERIAL INTERFACE(PAR/SER=1)Analog input of channel B0.The input voltage range is controlled by RANGE pin in hardware mode or CR bit C27 CH_B039AI(RANGE_B)in software mode.Analog input of channel B1.The input voltage range is controlled by RANGE pin in hardware mode or CR bit C27 CH_B142AI(RANGE_B)in software mode.Analog input of channel C0.The input voltage range is controlled by RANGE pin in hardware mode or CR bit C28 CH_C045AI(RANGE_C)in software mode.Analog input of channel C1.The input voltage range is controlled by RANGE pin in hardware mode or CR bit C28 CH_C148AI(RANGE_C)in software mode.Reference voltage input/output(0.5V to3.025V).The internal reference is enabled via REF EN/WR pin in hardware mode or CR bit C25(REF EN)in software mode.REFIO51AIOThe output value is controlled by the internal DAC(CR bits C[9:0]).Connect a470nF ceramic decouplingcapacitor between this pin and pin52.Decoupling capacitor for reference of channels A.REFC_A54AIConnect a10μF ceramic decoupling capacitor between this pin and pin53.Decoupling capacitor for reference of channels B.REFC_B56AIConnect a10μF ceramic decoupling capacitor between this pin and pin55.Decoupling capacitor for reference of channels C.REFC_C58AIConnect a10μF ceramic decoupling capacitor between this pin and pin57.Interface mode selection input.PAR/SER61DIWhen low,the parallel interface is selected.When high,the serial interface is enabled.Mode selection input.HW/SW62DI When low,the hardware mode is selected and part works according to the settings of external pins.When high,the software mode is selected in which the device is configured by writing into the control register.Hardware mode(HW/SW=0):Hardware mode(HW/SW=0):Internal reference enable input.Internal reference enable input.When high,the internal reference is enabled(the When high,the internal reference is enabled(the referencereference buffers are to be enabled).When low,buffers are to be enabled).When low,the internal referencethe internal reference is disabled and an external is disabled and an external reference should be applied at REF EN/WR63DI reference is applied at REFIO.REFIO.Software mode(HW/SW=1):Write input.The parallel data input is enabled,when CS and Software mode(HW/SW=1):Connect to BGND or BVDD.WR are low.The internal reference is enabled by The internal reference is enabled by CR bit C25(REF EN).the CR bit C25(REF EN).DB1564DIO Data bit15(MSB)input/output Connect to BGNDADS8555SBAS531B–DECEMBER2010–REVISED TIMING CHARACTERISTICSFigure1.Serial Operation Timing Diagram(All Three SDOs Active)SERIAL INTERFACE TIMING REQUIREMENTS(1)Over recommended operating free-air temperature range at–40°C to+125°C,AVDD=5V,and BVDD=2.7V to5.5V,unless otherwise noted.ADS8555PARAMETER MIN MAX UNITt ACQ Acquisition time280nst CONV Conversion time 1.26µst1CONVST_x low time20nst2BUSY low to FS low time0nst3Bus access finished to next conversion start time40nst D1CONVST_x high to BUSY high delay520nst D2FS low to SDO_x active delay512nst D3SCLK rising edge to new data valid delay15nst D4FS high to SDO_x3-state delay10nst H1Input data to SCLK falling edge hold time5nst H2Output data to SCLK rising edge hold time5nst S1Input data to SCLK falling edge setup time3nst S3CONVST_x high to XCLK falling or rising edge setup time6nst SCLK Serial clock period0.027810μs(1)All input signals are specified with t R=t F=1.5ns(10%to90%of BVDD)and timed from a voltage level of(V IL+V IH)/2.分销商库存信息:TIADS8555SPM ADS8555SPMR。

MRF9080LR3;中文规格书,Datasheet资料

Document Number: MRF9080 Rev. 8, 10/2008

MRF9080LR3

920 - 960 MHz, 75 W, 26 V LATERAL N - CHANNEL

Part

Description

Part Number

C1 C2 C3 C4, C5, C9, C10, C12, C13 C6, C16, C17 C7, C18 C8, C11 C14 C15 R1, R2, R3 Raw PCB Material

4.7 pF Chip Capacitor 2.7 pF Chip Capacitor 1.5 pF Chip Capacitor 5.6 pF Chip Capacitors 22 pF Chip Capacitors 10 μF, 35 V Tantalum Chip Capacitors 10 pF Chip Capacitors 0.8 pF Chip Capacitor 8.2 pF Chip Capacitor 1.0 kΩ, 1/8 W Chip Resistors 30 mil Glass Teflon®, εr = 2.55

Derate above 25°C Storage Temperature Range Case Operating Temperature Operating Junction Temperature Table 2. Thermal Characteristics

Characteristic Thermal Resistance, Junction to Case Table 3. ESD Protection Characteristics

MRF101BN和MRF101AN RF 设备数据手册说明书

MRF101BN MRF101ANMRF101AN MRF101BN1RF Power LDMOS TransistorsHigh Ruggedness N--ChannelEnhancement--Mode Lateral MOSFETsThese devices are designed for use in VHF/UHF communications,VHF TV broadcast and aerospaceapplications as well as industrial,scientific and medical applications.The devices are exceptionally rugged and exhibit high performance up to 250MHz.Typical Performance:V DD =50VdcFrequency (MHz)Signal TypeP out (W)G ps (dB)ηD (%)13.56CW 130CW 27.179.627CW 130CW 24.081.540.68(1)CW 120CW 23.881.550CW 115CW 23.079.581.36CW 130CW 23.280.887.5–108CW 110CW 21.377.1136–174(2,3)CW104CW 21.276.5230(4)Pulse(100μsec,20%Duty Cycle)115Peak21.176.7Load Mismatch/RuggednessFrequency (MHz)Signal TypeVSWR P in (W)Test Voltage Result 40.68CW>65:1at all Phase Angles 0.64Peak (3dB Overdrive)50No Device Degradation 230Pulse(100μsec,20%Duty Cycle)>65:1at all Phase Angles1.8Peak (3dB Overdrive)50No Device Degradation1.Measured in 40.68MHz reference circuit (page 5).2.Measured in 136–174MHz VHF broadband reference circuit (page3.The values shown are the center band performance numbers across the indicated frequency range.4.Measured in 230MHz fixture (page 13).Features ∙Mirror pinout versions (A and B)to simplify use in a push--pull,two--up configuration∙Characterized from 30to 50V ∙Suitable for linear application∙Integrated ESD protection with greater negative gate--source voltage range for improved Class C operation∙Included in NXP product longevity program with assured supply for a minimum of 15years after launchTypical Applications∙Industrial,scientific,medical (ISM)–Laser generation –Plasma etching –Particle accelerators–MRI and other medical applications–Industrial heating,welding and drying systems∙Radio and VHF TV broadcast ∙HF and VHF communications ∙Switch mode power supplies Document Number:MRF101ANRev.0,11/2018Technical Data1.8–250MHz,100W CW,50VWIDEBANDRF POWER LDMOS TRANSISTORSMRF101AN MRF101BNTO--220--3LMRF101BNTO--220--3LMRF101ANGSDDS GNote:Exposed backside of the packageand tab also serves as a source terminal for the transistor.BacksideSS2RF Device Data NXP SemiconductorsMRF101AN MRF101BN Table 1.Maximum RatingsRatingSymbol Value Unit Drain--Source Voltage V DSS –0.5,+133Vdc Gate--Source Voltage V GS –6.0,+10Vdc Operating VoltageV DD 50Vdc Storage Temperature Range T stg –65to +150︒C Case Operating Temperature Range T C –40to +150︒C Operating Junction Temperature Range (1,2)T J –40to +175︒C Total Device Dissipation @T C =25︒C Derate above 25︒CP D1820.91W W/︒CTable 2.Thermal CharacteristicsCharacteristicSymbol Value (2,3)Unit Thermal Resistance,Junction to CaseCW:Case Temperature 77︒C,150W CW,50Vdc,I DQ =100mA,40.68MHz R θJC 1.1︒C/W Thermal Impedance,Junction to CasePulse:Case Temperature 73︒C,113W Peak,100μsec Pulse Width,20%Duty Cycle,50Vdc,I DQ =100mA,230MHzZ θJC0.37︒C/WTable 3.ESD Protection CharacteristicsTest MethodologyClass Human Body Model (per JS--001--2017)1B,passes 1000V Charge Device Model (per JS--002--2014)C3,passes 1200VTable 4.Electrical Characteristics (T A =25︒C unless otherwise noted)CharacteristicSymbolMinTypMaxUnitOff CharacteristicsGate--Source Leakage Current (V GS =5Vdc,V DS =0Vdc)I GSS ——1μAdc Drain--Source Breakdown Voltage (V GS =0Vdc,I D =50mAdc)V (BR)DSS 133——Vdc Zero Gate Voltage Drain Leakage Current (V DS =100Vdc,V GS =0Vdc)I DSS——10μAdcOn CharacteristicsGate Threshold Voltage(V DS =10Vdc,I D =290μAdc)V GS(th) 1.7 2.2 2.7Vdc Gate Quiescent Voltage(V DS =50Vdc,I D =100mAdc)V GS(Q)— 2.5—Vdc Drain--Source On--Voltage (V GS =10Vdc,I D =1Adc)V DS(on)—0.45—Vdc Forward Transconductance (V DS =10Vdc,I D =8.8Adc)g fs—7.1—S1.Continuous use at maximum temperature will affect MTTF.2.MTTF calculator available at /RF/calculators .3.Refer to AN1955,Thermal Measurement Methodology of RF Power Amplifiers.Go to /RF and search for AN1955.(continued)MRF101AN MRF101BN3RF Device DataNXP SemiconductorsTable 4.Electrical Characteristics (T A =25︒C unless otherwise noted)(continued)CharacteristicSymbolMinTypMaxUnitDynamic CharacteristicsReverse Transfer Capacitance(V DS =50Vdc ±30mV(rms)ac @1MHz,V GS =0Vdc)C rss —0.96—pF Output Capacitance(V DS =50Vdc ±30mV(rms)ac @1MHz,V GS =0Vdc)C oss —43.4—pF Input Capacitance(V DS =50Vdc,V GS =0Vdc ±30mV(rms)ac @1MHz)C iss—149—pFTypical Performance —230MHz (In NXP 230MHz Fixture,50ohm system)V DD =50Vdc,I DQ =100mA,P in =0.9W,f =230MHz,100μsec Pulse Width,20%Duty Cycle Common--Source Amplifier Output Power P out —115—W Power Gain G ps —21.1—dB Drain EfficiencyηD—76.7—%Table 5.Load Mismatch/Ruggedness (In NXP 230MHz Fixture,50ohm system)I DQ =100mAFrequency (MHz)Signal TypeVSWR P in (W)Test Voltage,V DDResult230Pulse(100μsec,20%Duty Cycle)>65:1at all Phase Angles1.8Peak (3dB Overdrive)50No Device DegradationTable 6.Ordering InformationDeviceShipping InformationPackageMRF101AN MPQ =250devices (50devices per tube,5tubes per box)TO--220--3L (Pin 1:Gate,Pin 2:Source,Pin 3:Drain)MRF101BNTO--220--3L (Pin 1:Drain,Pin 2:Source,Pin 3:Gate)4RF Device Data NXP SemiconductorsMRF101AN MRF101BNTYPICAL CHARACTERISTICS1100V DS,DRAIN--SOURCE VOLTAGE(VOLTS)Figure1.Capacitance versus Drain--Source Voltage C,CAPACITANCE(pF)1010000.1MRF101AN MRF101BN5RF Device DataNXP Semiconductors40.68MHz COMPACT REFERENCE CIRCUIT (MRF101AN)—0.7"⨯2.0"(1.8cm ⨯5.0cm)Table 7.40.68MHz Performance (In NXP Reference Circuit,50ohm system)V DD =50Vdc,I DQ =100mA,P in =0.50W,CWFrequency (MHz)P out (W)G ps (dB)ηD (%)40.6812023.881.56RF Device Data NXP SemiconductorsMRF101AN MRF101BN 40.68MHz COMPACT REFERENCE CIRCUIT (MRF101AN)—0.7"⨯2.0"(1.8cm ⨯5.0cm)Figure 2.MRF101AN Compact Reference Circuit Component Layout and Assembly Example —40.68MHzFigure 3.MRF101AN Compact Reference CircuitBoardaaa--032274Table 8.MRF101AN Compact Reference Circuit Component Designations and Values —40.68MHzPartDescriptionPart NumberManufacturer B1Short RF Bead 2743019447Fair-Rite C1,C582pF Chip Capacitor GQM2195C2E820GB12D Murata C2,C4200pF Chip Capacitor GQM2195C2A201GB12D Murata C333pF Chip Capacitor GQM2195C2E330GB12D Murata C6,C7,C8,C9,C101000pF Chip Capacitor GRM2165C2A102JA01D Murata C111μF Chip Capacitor GJ821BR71H105KA12L Murata C12,C1310nF Chip Capacitor GRM21BR72A103KA01B Murata C141μF Chip Capacitor C3216X7R2A105K160AA TDK L1150nH Chip Inductor 0805WL151JT ATC L217.5nH,4Turn Inductor GA3095-ACL Coilcraft L3160nH Square Air Core Inductor 2222SQ-161JEC Coilcraft L4110nH Square Air Core Inductor 2222SQ-111JEB Coilcraft Q1RF Power LDMOS Transistor MRF101ANNXP R175Ω,1/4W Chip Resistor SG73P2ATTD75R0F KOA Speer PCBFR40.09",εr =4.8,2oz.CopperD113958MTLMRF101AN MRF101BN7RF Device DataNXP SemiconductorsTYPICAL CHARACTERISTICS —40.68MHz COMPACT REFERENCE CIRCUIT (MRF101AN)V GS ,GATE--SOURCE VOLTAGE (VOLTS)8060P o u t ,O U T P U T P O W E R (W A T T S )40 3.52.51.51100120014020Figure 4.CW Output Power versus Gate--SourceVoltage at a Constant Input PowerP in ,INPUT POWER (WATTS)8060P o u t ,O U T P U T P O W E R (W A T T S )40010012001402040.68101121f (MHz)P1dB (W)P3dB (W)Figure 5.CW Output Power versus Input PowerP out ,OUTPUT POWER (WATTS)Figure 6.Power Gain and Drain Efficiencyversus CW Output PowerG p s ,P O W E R G A I N (d B )ηD ,D R A I N E F F I C I E N C Y (%)25242802090705030302223262729806040201004060801001201400.5230.10.20.30.40.50.60.721201008RF Device Data NXP SemiconductorsMRF101AN MRF101BN40.68MHz COMPACT REFERENCE CIRCUIT(MRF101AN)fMHzZ sourceΩZ loadΩ40.6824.0+j12.614.2–j2.5Z source=Testcircuit impedance as measured fromgate to ground.Z load=Test circuit impedance as measuredfromdrain toground.Figure7.Series Equivalent Source and Load Impedance—40.68MHzZ source Z load50Ω50ΩMRF101AN MRF101BN9RF Device DataNXP Semiconductors136–174MHz COMPACT VHF BROADBAND REFERENCE CIRCUIT (MRF101AN)—0.7"⨯2.0"(1.8cm ⨯5.0cm)Table 9.136–174MHz VHF Broadband Performance (In NXP Reference Circuit,50ohm system)V DD =50Vdc,I DQ =100mA,P in =0.79W,CWFrequency (MHz)P out (W)G ps (dB)ηD (%)13511721.780.015510421.276.517510721.375.4136–174MHz COMPACT VHF BROADBAND REFERENCE CIRCUIT(MRF101AN)—0.7"⨯2.0"(1.8cm⨯5.0cm)Figure8.MRF101AN Compact Reference Circuit Component Layout and Assembly Example—136–174MHzFigure9.MRF101AN Compact Reference Circuit BoardTable10.MRF101AN Compact VHF Broadband Reference Circuit Component Designations and Values—136–174MHz Part Description Part Number ManufacturerB1Short RF Bead2743019447Fair-RiteC139pF Chip Capacitor GQM2195C2E390GB12D MurataC2,C5,C6,C7,C8,C12510pF Chip Capacitor GRM2165C2A511JA01D MurataC368pF Chip Capacitor GQM2195C2E680GB12D MurataC427pF Chip Capacitor GQM2195C2E270GB12D MurataC910pF Chip Capacitor GQM2195C2E100FB12D MurataC111μF Chip Capacitor GJ821BR71H105KA12L MurataC1310nF Chip Capacitor GRM21BR72A103KA01B MurataC141μF Chip Capacitor C3216X7R2A105K160AA TDKL122nH Chip Inductor0805WL220JT ATCL212nH Chip Inductor0805WL120JT ATCL3,L4,L668nH Air Core Inductor1812SMS-68NJLC CoilcraftL512nH,3Turn Inductor GA3094-ALC CoilcraftQ1RF Power LDMOS Transistor MRF101AN NXPR175Ω,1/4W Chip Resistor SG73P2ATTD75R0F KOA SpeerPCB FR40.09",εr=4.8,2oz.Copper D113958MTLTYPICAL CHARACTERISTICS —136–174MHzCOMPACT VHF BROADBAND REFERENCE CIRCUIT (MRF101AN)20150f,FREQUENCY (MHz)26259085807565130120ηD ,D R A I N E F F I C I E N C Y (%)G p s ,P O W E R G A I N (d B )242322211715516016517070110P o u t ,O U T P U T P O W E R (W A T T S )14514017513519100180P in,INPUT POWER (WATTS)0P o u t ,O U T P U T P O W E R (W A T T S )806040200.40.61201000.20.8140 1.027202422807570G p s ,P O W E R G A I N (d B )20406026858025232110012014065605550ηD ,D R A I N E F F I C I E N C Y (%)Figure 10.Power Gain,Drain Efficiency and CW Output Power versus Frequency at a Constant Input PowerFigure 11.CW Output Power versus Input Power and FrequencyP out ,OUTPUT POWER (WATTS)Figure 12.Power Gain and Drain Efficiency versusCW Output Power and Frequency191817454035136–174MHz COMPACT VHF BROADBAND REFERENCE CIRCUIT(MRF101AN)f MHz Z sourceΩZ loadΩ135 6.8+j10.29.5+j5.2145 6.2+j10.29.9+j5.9155 5.3+j10.810.2+j6.2165 4.4+j11.910.0+j5.9175 3.9+j13.48.8+j5.0Z source=Test circuit impedance as measured fromgate to ground.Z load=Test circuit impedance as measured fromdrain to ground.Figure13.Series Equivalent Source and Load Impedance—136–174MHzZ source Z load50Ω50Ω230MHz FIXTURE(MRF101AN)—4.0"⨯5.0"(10.2cm⨯12.7cm)aaa--031939Figure14.MRF101AN Fixture Component Layout—230MHzTable11.MRF101AN Fixture Component Designations and Values—230MHzPart Description Part Number Manufacturer B1Long Ferrite Bead2743021447Fair-RiteC1,C2,C1018pF Chip Capacitor ATC100B180JT500XT ATCC343pF Chip Capacitor ATC100B430JT500XT ATCC4,C131000pF Chip Capacitor ATC800B102JT50XT ATCC50.1μF Chip Capacitor GRM319R72A104KA01D MurataC610nF Chip Capacitor C1210C103J5GACTU KemetC7 2.2μF Chip Capacitor C3225X7R1H225K TDKC847μF,16V Tantalum Capacitor T491D476K016AT KemetC951pF Chip Capacitor ATC100B510JT500XT ATCC1116pF Chip Capacitor ATC100B160JT500XT ATCC12470pF Chip Capacitor ATC800B471JW50XT ATCC140.1μF Chip Capacitor C1812104K1RACTU KemetC15 2.2μF Chip Capacitor C3225X7R2A225K TDKC16 2.2μF Chip Capacitor HMK432B7225KM-T Taiyo YudenC17220μF,100V Electrolytic Capacitor MCGPR100V227M16X26MulticompL139nH Chip Inductor1812SMS-39NJLC CoilcraftL246nH Chip Inductor1010VS-46NME CoilcraftL317.5nH,4Turn Inductor GA3095-ALC CoilcraftR1470Ω,1/4W Chip Resistor CRCW1206470RFKEA VishayPCB Rogers AD255C,0.030",εr=2.55,2oz.Copper D113651MTLTYPICAL CHARACTERISTICS —230MHz FIXTURE,T C =25_C (MRF101AN)0V GS ,GATE--SOURCE VOLTAGE (VOLTS)Figure 15.Output Power versus Gate--SourceVoltage at a Constant Input PowerP o u t ,O U T P U T P O W E R (W A T T S )P E A K755025 1.52 2.531251000.51P in ,INPUT POWER (dBm)PEAK 514943P o u t ,O U T P U T P O W E R (d B m )P E A K4733302127245318230110128f (MHz)P1dB (W)P3dB (W)Figure 16.Output Power versus Input PowerP out ,OUTPUT POWER(WATTS)PEAKFigure 17.Power Gain and Drain Efficiency versus Output Power and Quiescent CurrentG p s ,P O W E R G A I N (d B )ηD ,D R A I N E F F I C I E N C Y (%)3300806040203301080706050403020P out ,OUTPUT POWER (WATTS)PEAKFigure 18.Power Gain and Drain Efficiencyversus Output PowerG p s ,P O W E R G A I N (d B )ηD ,D R A I N E F F I C I E N C Y (%)0P out ,OUTPUT POWER (WATTS)PEAKFigure 19.Power Gain versus Output Powerand Drain--Source Voltage20G p s ,P O W E R G A I N (d B )16145075100182522150451001251503003002441393715230MHz FIXTURE (MRF101AN)f MHz Z sourceΩZ load Ω2302.1+j5.95.5+j3.2Z source =Test circuitimpedance as measured fromgate to ground.Z load=Test circuit impedance asmeasured from drain toground.Figure 20.Series Equivalent Source and Load Impedance —230MHzZ source Z load50Ω50ΩPACKAGE DIMENSIONSPRODUCT DOCUMENTATION,SOFTWARE AND TOOLS Refer to the following resources to aid your design process.Application Notes∙AN1955:Thermal Measurement Methodology of RF Power AmplifiersEngineering Bulletins∙EB212:Using Data Sheet Impedances for RF LDMOS DevicesSoftware∙Electromigration MTTF Calculator∙RF High Power Model∙.s2p FileDevelopment Tools∙Printed Circuit BoardsTo Download Resources Specific to a Given Part Number:1.Go to /RF2.Search by part number3.Click part number link4.Choose the desired resource from the drop down menuREVISION HISTORYThe following table summarizes revisions to this document.Revision Date Description 0Nov.2018∙Initial release of data sheetRF Device DataNXP Semiconductors How to Reach Us:Home Page: Web Support:/support Information in this document is provided solely to enable system and software implementers to use NXP products.There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document.NXP reserves the right to make changes without further notice to any products herein.NXP makes no warranty,representation,or guarantee regarding the suitability of its products for any particular purpose,nor does NXP assume any liability arising out of the application or use of any product or circuit,and specifically disclaims any and all liability,including without limitation consequential or incidental damages.“Typical”parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications,and actual performance may vary over time.All operating parameters,including “typicals,”must be validated for each customer application by customer’s technical experts.NXP does not convey any license under its patent rights nor the rights of others.NXP sells products pursuant to standard terms and conditions of sale,which can be found at the following address:/SalesTermsandConditions .NXP and the NXP logo are trademarks of NXP B.V.All other product or service names are the property of their respective owners.E 2018NXP B.V.MRF101BN MRF101AN。

DVSA2805S中文资料

VPT Inc.2801 Commerce StreetBlacksburg, VA 24060Sales Info: (425) 337-2482 FAX: (603) 297-1160WEB: E-mail: mbosmann@DescriptionThe DVSA series of hybrid DC to DC conve r ters is able to operate at the full military (-55 °C to +125 °C) temperature range with no power derating. Unique to the DVSA series is a PATENTED magnetic feedback circuit that is fault tolerant and radiation immune. Operating at a nominal fixed frequ ency of 450kHz the regulated, isolated units utilize well controlled undervoltage lock out circuitry to eliminate slow start-up problems.Block DiagramDVSA2800S SeriesSpecificationsAbsolute Maximum RatingsInput Voltage (Continuous) 50 Vdc Input Voltage (Transient) 80 V (1sec) Output Power 16 Watts Power Dissipation, Full Load, T CASE = +125°C 2.5 Watts Junction Temperature rise to case +10°C Storage Temperature-65°C to +150°C Lead Solder Temperature for 10 seconds 270°C Weight15 gramsTcase = -55°C to +125°C, Vin = +28V ±5%, Full Load unless otherwise specifiedDVSA283R3S DVSA2805SDVSA2812SParameterConditions-55°C ≤TC ≤125°C,VIN = 28 VDC ±5%, Full LoadUnless otherwise specifiedMin Typ MaxMin Typ MaxMin Typ MaxUnitsStaticINPUTVoltage15 28 50 15 28 50 15 28 50 V Current 3Inhibited No Load3.5 40 5 60 3.5 40 5 60 3.5 40 5 60 mA mA Ripple Current Full Load, 20Hz to 10MHz 15 30 15 30 15 30 mA P-P Inhibit Pin Input 0 1.5 0 1.5 0 1.5 V Inhibit Pin Open Circuit Voltage 9.0 11.0 13.0 9.0 11.0 13.0 9.0 11.0 13.0 V UVLO Turn On 11.5 15.0 11.5 15.0 11.5 15.0 V UVLO Turn Off 11.0 14.5 11.0 14.5 11.0 14.5 V OUTPUTVoltage V OUTV OUTTcase = 25°C -55°C ≤ Tcase ≤ +125°C 3.27 3.20 3.30 3.30 3.33 3.40 4.95 4.85 5.00 5.00 5.05 5.15 11.88 11.64 12.0 12.0 12.12 12.36 V V Power 0 4 0 5 0 6 W Current V OUT0 1.21 0 1.0 0 0.50 A Ripple Voltage V OUT Full Load, 20Hz to 10MHz 10 30 10 30 15 40 mV p-p Line Regulation V OUT Vin = 15V to 50V 10 20 10 20 10 20 mV Load Regulation V OUT No Load to Full Load 20 40 20 40 20 40 mV EFFICIENCY64 68 68 72 73 77 % LOAD FAULT POWER DISSIPATIONOverload Short Circuit 3.0 2.5 3.0 2.5 3.0 2.5 W W CAPACITIVE LOAD 1000 1000 500 µF SWITCHING FREQUENCY400 450 525 400 450 525 400 450 525 kHz ISOLATION 500Vdc100 100 100 M Ω THERMAL RESISTANCE Case to Ambient (θCA) 28 28 28 °C/W MTBFMIL-HDBK-217F, AIF @ Tc = 55°C 457 457 457 kHrs DynamicLOAD STEPOutput Transient Recovery 2 V OUT Half Load to Full Load200 200 400 400200 200 400 400300 200 500 400mV PK µSec LINE STEPOutput Transient Recovery 2 V OUT V IN = 15V to 50V 200 200 400 400 200 200 400 400300 200 500 400mV PK µSecTURN ON DelayOvershoot 2V OUTV IN = 0V to 28V10 015 3310 015 5010 015 120mSec mV PKNOTES: 1. Dependent on output voltage. 2. Time for output voltage to settle within 1% of its nominal value 3. Derate linearly to 0 at 135°C.DVSA2800S SeriesSpecificationsAbsolute Maximum RatingsInput Voltage (Continuous) 50 Vdc Input Voltage (Transient) 80 V (1sec) Output Power 16 Watts Power Dissipation, Full, TCASE = +125°C 2.5 Watts Junction Temperature rise to case +10°C Storage Temperature-65°C to +150°C Lead Solder Temperature for 10 seconds 270°C Weight15 gramsTcase = -55°C to +125°C, Vin = +28V ±5%, Full Load unless otherwise specifiedDVSA2815SParameterConditions-55°C ≤TC ≤125°C,VIN = 28 VDC ±5%, Full LoadUnless otherwise specifiedMin Typ Max UnitsStaticINPUTVoltage15 28 50 V Current 3Inhibited No Load3.5 40 5 60 mA mA Ripple Current Full Load, 20Hz to 10MHz 15 30 mA P-P Inhibit Pin Input 0 1.5 V Inhibit Pin Open Circuit Voltage 9.0 11.0 13.0 V UVLO Turn On 11.5 15.0 V UVLO Turn Off 11.0 14.5 V OUTPUTVoltage V OUTV OUTTcase = 25°C -55°C ≤ Tcase ≤ +125°C 14.85 14.55 15.00 15.00 15.15 15.45 V V Power 0 6 W Current V OUT0 0.4 A Ripple Voltage V OUT Full Load, 20Hz to 10MHz 15 40 mV P-P Line Regulation V OUT Vin = 15V to 50V 10 20 mV Load Regulation V OUT No Load to Full Load 20 40 mV EFFICIENCY74 78 % LOAD FAULT POWER DISSIPATIONOverload Short Circuit 3.0 2.5 W W CAPACITIVE LOAD 500 µF SWITCHING FREQUENCY 400 450 525 kHz ISOLATION100 M Ω THERMAL RESISTANCE Case to Ambient (θCA) 28 °C/W MTBFMIL-HDBK-217F, AIF @ Tc = 55°C 457 kHrs DynamicLOAD STEPOutput Transient Recovery2 V OUT Half Load to Full Load300 200 500 400 mV PK µSecLINE STEPOutput Transient Recovery2 V OUT V IN = 15V to 50V 300 200 500 400 mV PK µSecTURN ON DelayOvershoot2V OUTV IN = 0V to 28V10 015 150mSec mV PKNOTES: 1. Dependent on output voltage. 2. Time for output voltage to settle within 1% of its nominal value. 3. Derate linearly to 0 at 135°C.DVSA2800S Without EMI filterFigure 1DVSA2800S With EMI filterFigure 2DVSA2800S SeriesOrdering InformationExample Part Number: DVSA2805DR/ESDVSA 28 05 S R /ESProduct Series Nominal Input Voltage Output Voltage No. Outputs Rad Hard Opt. Screening DVSA 28 28 Volts 03R3 3.3 Volts S Single None Std. None Standard05 5 Volts R 100kRad /ES Extended12 12 Volts /HB HB Screening15 15 VoltsLast Revised 6/26/00。

RP08-4805SA中文资料

31.80 25.54

Bottom View

16 15 14 13 9 10 11 12 16 14

Bottom View 9 11

17.80 31.80

20.32 23.40 25.40

15.20 20.30

10.20

0.25 x 0.50 Rectangular Pin

10.90

Pin Pitch Tolerance ±0.35 mm

Maximum Capacitive Load

RP08-xx33SA RP08-xx05SA RP08-xx12SA RP08-xx15SA RP08-xx05DA RP08-xx12DA RP08-xx15DA PO 34 August 2002 3300µF 1600µF 350µF 240µF ±1000µF ±160µF ±100µF

50mVp-p Single Output ±0.2% max. Dual Output ±0.2% max. Single Output ±2% max. Dual Output ±1% max. ±0.02%/°C Continuous CMOS, TTL 4.8V min, or Open 0.4V max. or Short 300kHz, typ. 1600VDC 109 Ω 300pF max. -25°C to +71°C -55°C to +125°C Free-air Convection Five-sided Shield Nickel-Coated Copper with Non-Conductive Base 31.8 x 20.3 x 10.2 mm 7.189 x 105 Hours

Input Voltage Range 12V types nominal 24V types nominal 48V types nominal 9-18V 18-36V 36-75V Pi Type ±2% ±2%

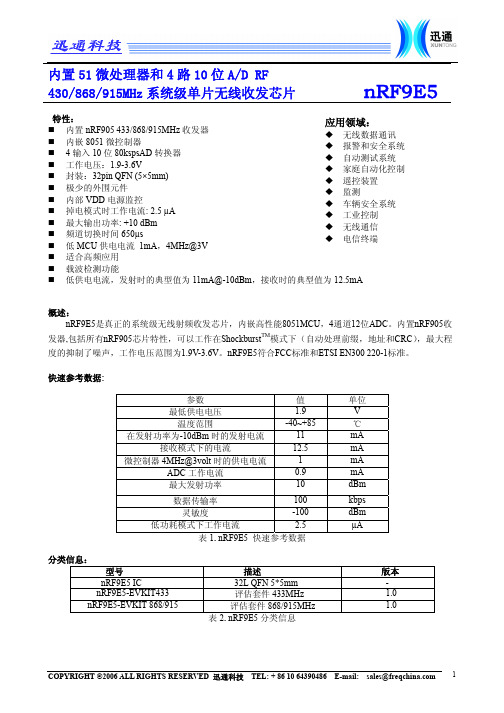

NRF9E5中文资料

nRF9E5 以 SPI 接口控制为特点。SPI 的 3 根数据线(MISO,SCK 和 MOSI)具有多种复用功能。SPI 硬件不产生片选择信号。设计人员可以通过 GPIO 来设置一个或多个外部 SPI 的片选。EECSN 引脚是通用 I/O 接口,它在这里作为导入 EEPROM 的片选端。

接收模式下的电流 微控制器 4MHz@3volt 时的供电电流

ADC 工作电流 最大发射功率

值 1.9 -40~+85 11 12.5 1 0.9 10

数据传输率

100

灵敏度

-100

低功耗模式下工作电流

2.5

表 1. nRF9E5 快速参考数据

分类信息: 型号

nRF9E5 IC nRF9E5-EVKIT433 nRF9E5-EVKIT 868/915

COPYRIGHT ©2006 ALL RIGHTS RESERVED 迅通科技 TEL: + 86 10 64390486 E-mail: sales@ 3

11.7 RF-配置寄存器内容 11.8 ADC 配置寄存器内容 11.9 ADC 数据寄存器内容 11.10 状态寄存器内容 12. 无线收发器子系统时序 12.1 转换时间 12.2 ShockBurst TX 时序 12.3 ShockBurst RX 时序 12.4 前导码 12.5 空中传输时间

内置 51 微处理器和 4 路 10 位 A/D RF 430/868/915MHz 系统级单片无线收发芯片

nRF9E5

MRF5S9080NR1;中文规格书,Datasheet资料