P6KA39中文资料

P6KA15中文资料

P6KA6.8 THRU P6KA43A

AUTOMOTIVE TRANSIENT VOLTAGE SUPPRESSOR

Breakdown Voltage - 6.8 to 43 Volts

D *

Peak Pulse Power - 600 Watts

FEATURES

P A T E

N

T E

DO-204AC

0.034 (0.86) 1.0 (25.4) MIN. 0.028 (0.71) DIA.

0.300 (7.6) 0.230 (5.8)

0.140 (3.6) 0.104 (2.6) DIA. 1.0 (25.4) MIN.

♦ Designed for under the hood applications ♦ Plastic package has Underwriters Laboratory Flammability Classification 94V-0 ♦ Exclusive patented PAR™ oxide passivated chip construction ♦ 600W peak pulse power surge capability with a 10/1000µs waveform repetition rate (duty cycle): 0.01% ♦ Excellent clamping capability ♦ Low incremental surge resistance ♦ Fast response time: typically less than 1.0ps from 0 Volts to V(BR) ♦ For devices with V(BR)≥10V, ID are typically less than1.0µA ♦ High temperature soldering guaranteed: 300°C/10 seconds, 0.375" (9.5mm) lead length, 5lbs. (2.3 kg) tension

W39V080FAP中文资料

W39V080FA Data Sheet1M × 8 CMOS FLASH MEMORYWITH FWH INTERFACE Table of Contents-1.GENERAL DESCRIPTION (3)2.FEATURES (3)3.PIN CONFIGURATIONS (4)4.BLOCK DIAGRAM (4)5.PIN DESCRIPTION (4)6.FUNCTIONAL DESCRIPTION (5)6.1Interface Mode Selection and Description (5)6.2Read (Write) Mode (5)6.3Reset Operation (5)6.4Accelerated Program Operation (5)6.5Boot Block Operation and Hardware Protection at Initial- #TBL & #WP (5)6.6Sector Erase Command (6)6.7Program Operation (6)6.8Dual BIOS (6)6.9Hardware Data Protection (6)6.10Write Operation Status (7)6.10.1DQ7: #Data Polling (7)6.10.2RY/#BY: Ready/#Busy (7)6.10.3DQ6: Toggle Bit (7)6.10.4DQ5: Exceeded Timing Limits (8)6.11Identification Input pin ID[3:0] (8)6.12Register (8)6.12.1General Purpose Inputs Register (8)6.12.2Block Locking Registers (8)6.12.3Product Identification Registers (10)6.13Table of Operating Modes (11)6.13.1Operating Mode Selection - Programmer Mode (11)6.13.2Operating Mode Selection - FWH Mode (11)6.14Fwh Cycle Definition (12)6.15Embedded Programming Algorithm (13)6.16Embedded Erase Algorithm (14)6.17Embedded #Data Polling Algorithm (15)6.18Embedded Toggle Bit Algorithm (16)6.19Software Product Identification and Boot Block Lockout Detection Acquisition Flow..177.DC CHARACTERISTICS (18)7.1Absolute Maximum Ratings (18)7.2Programmer interface Mode DC Operating Characteristics (18)7.3FWH interface Mode DC Operating Characteristics (19)7.4Power-up Timing (19)7.5Capacitance (19)Publication Release Date: Dec. 13, 2005W39V080FA8.PROGRAMMER INTERFACE MODE AC CHARACTERISTICS (20)8.1AC Test Conditions (20)8.2AC Test Load and Waveform (20)8.3Read Cycle Timing Parameters (21)8.4Write Cycle Timing Parameters (21)8.5Data Polling and Toggle Bit Timing Parameters (21)9.TIMING WAVEFORMS FOR PROGRAMMER INTERFACE MODE (22)9.1Read Cycle Timing Diagram (22)9.2Write Cycle Timing Diagram (22)9.3Program Cycle Timing Diagram (23)9.4#DATA Polling Timing Diagram (23)9.5Toggle Bit Timing Diagram (24)9.6Sector Erase Timing Diagram (24)10.FWH INTERFACE MODE AC CHARACTERISTICS (25)10.1AC Test Conditions (25)10.2Read/Write Cycle Timing Parameters (25)10.3Reset Timing Parameters (25)11.TIMING WAVEFORMS FOR FWH INTERFACE MODE (26)11.1Read Cycle Timing Diagram (26)11.2Write Cycle Timing Diagram (26)11.3Program Cycle Timing Diagram (27)11.4#DATA Polling Timing Diagram (28)11.5Toggle Bit Timing Diagram (29)11.6Sector Erase Timing Diagram (30)11.7FGPI Register/Product ID Readout Timing Diagram (31)11.8Reset Timing Diagram (31)12.ORDERING INFORMATION (32)13.HOW TO READ THE TOP MARKING (32)14.PACKAGE DIMENSIONS (33)14.132L PLCC (33)14.232L STSOP (8X14mm) (33)14.340L TSOP (10 mm x 20 mm) (34)15.VERSION HISTORY (35)W39V080FAPublication Release Date: Dec. 13, 20051. GENERAL DESCRIPTIONThe W39V080FA is an 8-megabit, 3.3-volt only CMOS flash memory organized as 1M × 8 bits. For flexible erase capability, the 8Mbits of data are divided into 16 uniform sectors of 64 Kbytes. The device can be programmed and erased in-system with a standard 3.3V power supply. A 12-volt VPP is required for accelerated program. The unique cell architecture of the W39V080FA results in fast program/erase operations with extremely low current consumption. This device can operate at two modes, Programmer bus interface mode and FWH bus interface mode. As in the Programmer interface mode, it acts like the traditional flash but with a multiplexed address inputs. But in the FWH interface mode, this device complies with the Intel FWH specification. The device can also be programmed and erased using standard EPROM programmers.2. FEATURES•Single 3.3-volt operations: − 3.3-volt Read − 3.3-volt Erase − 3.3-volt Program• Fast program operation: − VPP = 12V− Byte-by-Byte programming: 9 μS (typ.) • Fast erase operation:− Sector erase 0.9 Sec. (typ.) • Fast read access time: Tkq 11 nS • Endurance: 30K cycles (typ.) • Twenty-year data retention • 16 Even sectors with 64K bytes • Any individual sector can be erased • Dual BIOS function− Full-chip partition with 8M-bit or dual-block partition with 4M-bit •Hardware protection:− #TBL supports 64-Kbyte Boot Block hardware protection− #WP supports the whole chip except Boot Block hardware protection• Hardware Features•Ready/#Busy output (RY/#BY)− Detect program or erase cycle completion • Hardware reset pin (#RESET)− Reset the internal state machine to the readmode• VPP input pin− Acceleration (ACC) function acceleratesprogram timing• Low power consumption− Read Active current: 15 mA (typ. for FWH mode)• Automatic program and erase timing with internal V PP generation• End of program or erase detection − Toggle bit − Data polling• Latched address and data • TTL compatible I/O• Available packages: 32L PLCC, 32L STSOP,40L TSOP(10 x 20 mm), 32L PLCC Lead free, 32L STSOP Lead free and 40L TSOP (10 x 20 mm) Lead freeW39V080FA3. PIN CONFIGURATIONS4. BLOCK DIAGRAM5. PIN DESCRIPTIONINTERFACE SYM.PGM FWH PIN NAMEIC**Interface Mode Selection#RESET * * Reset#INIT * Initialize#TBL * Top Boot Block Lock #WP * Write Protect CLK * CLK InputFGPI[4:0]*General Purpose InputsID[3:0] *Identification Inputs Pull Down with Internal Resistors FWH[3:0] * Address/Data InputsFWH4 * FWH Cycle InitialD/#F *Dual Bios/Full ChipPull Down with Internal Resistors U/#L *Upper 4M/Lower 4MPull Down with Internal Resistors R/#C * Row/Column Select A[10:0] * Address Inputs DQ[7:0]* Data Inputs/Outputs#OE * Output Enable #WE * Write Enable RY/#BY* Ready/ BusyVDD * * Power Supply VSS * * Ground VPP * * Accelerate Program Power Supply RSV * * Reserved PinsNC**No ConnectionW39V080FA6. FUNCTIONAL DESCRIPTION6.1 Interface Mode Selection and DescriptionThis device can operate in two interface modes, one is Programmer interface mode, and the other is FWH interface mode. The IC pin of the device provides the control between these two interface modes. These interface modes need to be configured before power up or return from #RESET. When IC pin is set to high state, the device will be in the Programmer mode; while the IC pin is set to low state (or leaved no connection), it will be in the FWH mode. In Programmer mode, this device just behaves like traditional flash parts with 8 data lines. But the row and column address inputs are multiplexed. The row address are mapped to the higher internal address A[19:11]. And the column address are mapped to the lower internal address A[10:0]. For FWH mode, It complies with the FWH Interface Specification. Through the FWH[3:0] and FWH4 to communicate with the system chipset .6.2 Read (Write) ModeIn Programmer interface mode, the read (write) operation of the W39V080FA is controlled by #OE (#WE). The #OE (#WE) is held low for the host to obtain (write) data from (to) the outputs (inputs). #OE is the output control and is used to gate data from the output pins. The data bus is in high impedance state when #OE is high. As for in the FWH interface mode, the read or write is determined by the "bit 0 & bit 1 of START CYCLE ". Refer to the FWH cycle definition and timing waveforms for further details.6.3 Reset OperationThe #RESET input pin can be used in some application. When #RESET pin is at high state, the device is in normal operation mode. When #RESET pin is at low state, it will halt the device and all outputs will be at high impedance state. As the high state re-asserted to the #RESET pin, the device will return to read or standby mode, it depends on the control signals.6.4 Accelerated Program OperationThe device provides accelerated program operations through the ACC function. This function is primarily intended to allow a faster manufacturing throughput in the factory.6.5 Boot Block Operation and Hardware Protection at Initial- #TBL & #WPThere is a hardware method to protect the top boot block and other sectors. Before power on programmer, tie the #TBL pin to low state and then the top boot block will not be programmed/erased. If #WP pin is tied to low state before power on, the other sectors will not be programmed/erased.In order to detect whether the boot block feature is set on or not, users can perform software command sequence: enter the product identification mode (see Command Codes for Identification/Boot Block Lockout Detection for specific code), and then read from address FFFF2(hex). You can check the DQ2/DQ3 at the address FFFF2 to see whether the #TBL/#WP pin is in low or high state. If the DQ2 is “0”, it means the #TBL pin is tied to high state. In such condition, whether boot block can be programmed/erased or not will depend on software setting. On the other hand, if the DQ2 is “1”, it means the #TBL pin is tied to low state, then boot block is locked no matter how the software is set. Like the DQ2, the DQ3 inversely mirrors the #WP state. If the DQ3 is “0”, it means the #WP pin is in high state, then all the sectors except the boot block can be programmed/erased. On the other hand, if the DQ3 is “1”, then all the sectors except the boot block are programmed/erased inhibited.To return to normal operation, perform a three-byte command sequence (or an alternate single-byte command) to exit the identification mode. For the specific code, see Command Codes for Identification/Boot Block Lockout Detection.Publication Release Date: Dec. 13, 2005W39V080FA6.6 Sector Erase CommandSector erase is a six bus cycles operation. There are two "unlock" write cycles, followed by writing the "set-up" command. Two more "unlock" write cycles then follows by the Sector erase command. The Sector address (any address location within the desired Sector) is latched on the rising edge of R/#C in programmer mode, while the command (30H) is latched on the rising edge of #WE.Sector erase does not require the user to program the device prior to erase. When erasing a Sector, the remaining unselected sectors are not affected. The system is not required to provide any controls or timings during these operations.The automatic Sector erase begins after the erase command is completed, right from the rising edge of the #WE pulse for the last Sector erase command pulse and terminates when the data on DQ7, Data Polling, is "1" at which time the device returns to the read mode. Data Polling must be performed at an address within any of the sectors being erased.Refer to the Erase Command flow Chart using typical command strings and bus operations.6.7 Program OperationThe W39V080FA is programmed on a byte-by-byte basis. Program operation can only change logical data "1" to logical data "0." The erase operation, which changed entire data in main memory and/or boot block from "0" to "1", is needed before programming.The program operation is initiated by a 4-byte command cycle (see Command Codes for Byte Programming). The device will internally enter the program operation immediately after the byte-program command is entered. The internal program timer will automatically time-out (9μS typ.-T BP) once it is completed and then return to normal read mode. Data polling and/or Toggle Bits can be used to detect end of program cycle.6.8 Dual BIOSThe W39V080FA provides a solution for Dual-BIOS application. In FWH mode, when D/#F is low, the device functions as a full-chip partition of 8M-bit which address ranges from FFFFFh to 00000h with A[19:0]. If D/#F is driven high, the device functions as a dual-block partition that each block consists of 4M-bit. For dual-block partition, there is only one 4M-bit block, either upper or lower, can be accessed. The U/#L pin selects either upper or lower 4M-bit block and its address ranges from 7FFFFh to 00000h with A[19:0]. When U/#L is low, the lower 4M-bit block will be selected; while, U/#L is high, the upper 4M-bit block will be selected.6.9 Hardware Data ProtectionThe integrity of the data stored in the W39V080FA is also hardware protected in the following ways:(1) Noise/Glitch Protection: A #WE pulse of less than 15 nS in duration will not initiate a write cycle.(2) V DD Power Up/Down Detection: The programming and read operation are inhibited when V DD isless than 2.0V typical.(3) Write Inhibit Mode: Forcing #OE low or #WE high will inhibit the write operation. This preventsinadvertent writes during power-up or power-down periods.W39V080FA6.10 Write Operation StatusThe device provides several bits to determine the status of a program or erase operation: DQ5, DQ6, and DQ7. Each of DQ7 and DQ6 provides a method for determining whether a program or erase operation is complete or in progress. The device also offers a hardware-based output signal, RY/#BY in programmer mode, to determine whether an Embedded Program or Erase operation is in progress or has been completed.6.10.1 DQ7: #Data PollingThe #Data Polling bit, DQ7, indicates whether an Embedded Program or Erase algorithm is in progress or completed. Data Polling is valid after the rising edge of the final #WE pulse in the command sequence.During the Embedded Program algorithm, the device outputs on DQ7 and the complement of the data programmed to DQ7. Once the Embedded Program algorithm has completed, the device outputs the data programmed to DQ7. The system must provide the program address to read valid status information on DQ7. If a program address falls within a protected sector, #Data Polling on DQ7 is active for about 1μS, and then the device returns to the read mode.During the Embedded Erase algorithm, #Data Polling produces “0” on DQ7. Once the Embedded Erase algorithm has completed, #Data Polling produces “1” on DQ7. An address within any of the sectors selected for erasure must be provided to read valid status information on DQ7.After an erase command sequence is written, if all sectors selected for erasing are protected, #Data Polling on DQ7 is active for about 100μS, and then the device returns to the read mode. If not all selected sectors are protected, the Embedded Erase algorithm erases the unprotected sectors, and ignores the selected sectors that are protected. However, if the system reads DQ7 at an address within a protected sector, the status may not be valid.Just before the completion of an Embedded Program or Erase operation, DQ7 may change asynchronously with DQ0-DQ6 while Output Enable (#OE) is set to low. That is, the device may change from providing status information to valid data on DQ7. Depending on when it samples the DQ7 output, the system may read the status or valid data. Even if the device has completed the program or erase operation and DQ7 has valid data, the data outputs on DQ0-DQ6 may be still invalid. Valid data on DQ7-DQ0 will appear on successive read cycles.6.10.2 RY/#BY: Ready/#BusyThe RY/#BY is a dedicated, open-drain output pin which indicates whether an Embedded Algorithm is in progress or complete. The RY/#BY status is valid after the rising edge of the final #WE pulse in the command sequence. Since RY/#BY is an open-drain output, several RY/#BY pins can be tied together in parallel with a pull-up resistor to V DD.When the output is low (Busy), the device is actively erasing or programming. When the output is high (Ready), the device is in the read mode or standby mode.6.10.3 DQ6: Toggle BitToggle Bit on DQ6 indicates whether an Embedded Program or Erase algorithm is in progress or complete. Toggle Bit I may be read at any address, and is valid after the rising edge of the final #WE pulse in the command sequence (before the program or erase operation), and during the sector erase time-out.During an Embedded Program or Erase algorithm operation, successive read cycles to any address cause DQ6 to toggle. The system may use either #OE to control the read cycles. Once the operation has completed, DQ6 stops toggling.Publication Release Date: Dec. 13, 2005W39V080FAAfter an erase command sequence is written, if all sectors selected for erasing are protected, DQ6toggles for about 100μS, and then returns to reading array data. If not all selected sectors are protected, the Embedded Erase algorithm erases the unprotected sectors, and ignores the selectedsectors which are protected.The system can use DQ6 to determine whether a sector is actively erasing. If the device is activelyerasing (i.e., the Embedded Erase algorithm is in progress), DQ6 toggles. If a program address fallswithin a protected sector, DQ6 toggles for about 1 μs after the program command sequence is written,and then returns to reading array data.6.10.4 DQ5: Exceeded Timing LimitsDQ5 indicates whether the program or erase time has exceeded a specified internal pulse count limit.DQ5 produces “1” under these conditions which indicates that the program or erase cycle was not successfully completed.The device may output “1” on DQ5 if the system tries to program “1” to a location that was previously programmed to “0.” Only the erase operation can change “0” back to “1.” Under this condition, thedevice stops the operation, and while the timing limit has been exceeded, DQ5 produces “1.”Under both these conditions, the system must hardware reset to return to the read mode.6.11 Identification Input pin ID[3:0]These pins are part of mechanism that allows multiple parts to be used on the same bus. The bootdevice should be 0000b. And all the subsequent parts should use the up-count strapping.6.12 RegisterThere are three kinds of registers on this device, the General Purpose Input Registers, the Block LockControl Registers and Product Identification Registers. Users can access these registers through respective address in the 4Gbytes memory map. There are detail descriptions in the sections below.6.12.1 General Purpose Inputs RegisterThis register reads the FGPI[4:0] pins on the W39V080FA.This is a pass-through register which canread via memory address FFBC0100(hex). Since it is pass-through register, there is no default value.GPI Register TableBIT FUNCTION7 − 5 Reserved4 Read FGPI4 pin status3 Read FGPI3 pin status2 Read FGPI2 pin status1 Read FGPI1 pin status0 Read FGPI0 pin status6.12.2 Block Locking RegistersThis part provides 16 even 64Kbytes blocks, and each block can be locked by register control. Thesecontrol registers can be set or clear through memory address. Below is the detail description.W39V080FAPublication Release Date: Dec. 13, 2005Block Locking Registers type and access memory map TableREGISTERSREGISTERSTYPECONTROL BLOCKDEVICE PHYSICALADDRESS4GBYTES SYSTEM MEMORY ADDRESSBLR15 R/W 15 0FFFFFh – 0F0000h FFBF0002h BLR14 R/W 14 0EFFFFh – 0E0000h FFBE0002h BLR13 R/W 13 0DFFFFh – 0D0000h FFBD0002h BLR12 R/W 12 0CFFFFh – 0C0000h FFBC0002h BLR11 R/W 11 0BFFFFh – 0B0000h FFBB0002h BLR10 R/W 10 0AFFFFh – 0A0000h FFBA0002h BLR9 R/W 9 09FFFFh – 090000h FFB90002h BLR8 R/W 8 08FFFFh – 080000h FFB80002h BLR7 R/W 7 07FFFFh – 070000h FFB70002h BLR6 R/W 6 06FFFFh – 060000h FFB60002h BLR5 R/W 5 05FFFFh – 050000h FFB50002h BLR4 R/W 4 04FFFFh – 040000h FFB40002h BLR3 R/W 3 03FFFFh – 030000h FFB30002h BLR2 R/W 2 02FFFFh – 020000h FFB20002h BLR1 R/W 1 01FFFFh – 010000h FFB10002h BLR0R/W00FFFFh – 000000hFFB00002hBlock Locking Register Bits Function TableBIT FUNCTION7 – 3 Reserved2 Read Lock1: Prohibit to read in the block where set0: Normal read operation in the block where clear. This is default state.1 Lock Down1: Prohibit further to set or clear the Read Lock or Write Lock bits. This Lock Down Bit can only be set not clear. Only the device is reset or re-powered, the Lock Down Bit is cleared.0: Normal operation for Read Lock or Write Lock. This is the default state. 0 Write Lock1: Prohibited to write in the block where set. This is default state. 0: Normal programming/erase operation in the block where clear.W39V080FARegister Based Block Locking Value Definitions TableBIT [7:3] BIT 2 BIT 1 BIT 0 RESULTAccess.Full00000 0 0 000000 0 0 1 Write Lock. Default State.00000 0 1 0 Locked Open (Full Access, Lock Down).00000 0 1 1 Write Locked, Locked Down.Locked.Read00000 1 0 000000 1 0 1 Read & Write Locked.00000 1 1 0 Read Locked, Locked Down.00000 1 1 1 Read & Write Locked, Locked Down.Read LockAny attempt to read the data of read locked block will result in “00H.” The default state of any block is unlocked upon power up. User can clear or set the write lock bit anytime as long as the lock down bit is not set.Write LockThis is the default state of blocks upon power up. Before any program or erase to the specified block, user should clear the write lock bit first. User can clear or set the write lock bit anytime as long as the lock down bit is not set. The write lock function is in conjunction with the hardware protect pins, #WP & TBL. When hardware protect pins are enabled, it will override the register block locking functions and write lock the blocks no matter how the status of the register bits. Reading the register bit will not reflect the status of the #WP or #TBL pins.Lock DownThe default state of lock down bit for any block is unlocked. This bit can be set only once; any further attempt to set or clear is ignored. Only the reset from #RESET or #INIT can clear the lock down bit. Once the lock down bit is set for a block, then the write lock bit & read lock bit of that block will not be set or cleared, and keep its current state.6.12.3 Product Identification RegistersThere is an alternative software method to read out the Product Identification in both the Programmer interface mode and the FWH interface mode. Thus, the programming equipment can automatically matches the device with its proper erase and programming algorithms.In the full-chip(8Mb) FWH interface mode, a read from FFBC, 0000(hex) can output the manufacturer code, DA(hex). A read from FFBC, 0001(hex) can output the device code, D3(hex).For Dual-BIOS(4Mbx2) FWH mode , a read from FFBC, 0000(hex) can output the manufacturer code, DA(hex). A read from FFBC,0001(hex) can output the device code 93(hex).In the software access mode, a JEDEC 3-byte command sequence can be used to access the product ID for programmer interface mode. A read from address 0000(hex) outputs the manufacturer code, DA(hex). A read from address 0001(hex) outputs the device code, D3(hex).” The product ID operation can be terminated by a three-byte command sequence or an alternate one-byte command sequence (see Command Definition table for detail).W39V080FAPublication Release Date: Dec. 13, 20056.13 Table of Operating Modes6.13.1 Operating Mode Selection - Programmer ModeMODE PINS#OE#WE#RESETADDRESSDQ.Read V IL V IH V IH AIN Dout Write V IH V ILV IHAIN DinStandby X X V IL X High ZWrite Inhibit V IL X V IH X High Z/DOUT X V IH V IH X High Z/DOUTOutput DisableV IH X V IH X High Z6.13.2 Operating Mode Selection - FWH ModeOperation modes in FWH interface mode are determined by "START Cycle" when it is selected. When it is not selected, its outputs (FWH[3:0]) will be disable. Please reference to the "FWH Cycle Definition".Table of Command DefinitionCOMMAND NO. OF 1ST CYCLE 2ND CYCLE 3RD CYCLE 4TH CYCLE 5TH CYCLE 6TH CYCLE DESCRIPTION Cycles (1)Addr. Data Addr. DataAddr. DataAddr. DataAddr. DataAddr. DataRead 1 A IN D OUTSector Erase 6 5555 AA 2AAA 555555 805555 AA 2AAA 55SA (5)30Byte Program 4 5555 AA 2AAA 555555 A0A IN D INProduct ID Entry 3 5555 AA 2AAA 555555 90 Product ID Exit (4)35555 AA2AAA 555555 F0Product ID Exit (4) 1 XXXX F0 Notes: 1. The cycle means the write command cycle not the FWH clock cycle. 2. The Column Address / Row Address are mapped to the Low / High order Internal Address. i.e. Column Address A[10:0] are mapped to the internal A[10:0], Row Address A[7:0] are mapped to the internal A[19:11] 3. Address Format: A14−A0 (Hex); Data Format: DQ7-DQ0 (Hex) 4. Either one of the two Product ID Exit commands can be used. 5. SA: Sector AddressSA = FXXXXh for Unique Sector15 (Boot Sector) SA = 7XXXXh for Unique Sector7 SA = EXXXXh for Unique Sector14 SA = 6XXXXh for Unique Sector6 SA = DXXXXh for Unique Sector13 SA = 5XXXXh for Unique Sector5 SA = CXXXXh for Unique Sector12 SA = 4XXXXh for Unique Sector4 SA = BXXXXh for Unique Sector11 SA = 3XXXXh for Unique Sector3 SA = AXXXXh for Unique Sector10 SA = 2XXXXh for Unique Sector2 SA = 9XXXXh for Unique Sector9 SA = 1XXXXh for Unique Sector1 SA = 8XXXXh for Unique Sector8SA = 0XXXXh for Unique Sector0W39V080FA6.14 Fwh Cycle DefinitionFIELDNO. OF CLOCKSDESCRIPTIONSTART 1"1101b" indicates FWH Memory Read cycle; while "1110b" indicates FWHMemory Write cycle. 0000b" appears on FWH bus to indicate the initial IDSEL 1 This one clock field indicates which FWH component is being selected. MSIZE 1 Memory Size. There is always show “0000b” for single byte access. TAR2Turned Around TimeADDR 7Address Phase for Memory Cycle. FWH supports the 28 bits address protocol. The addresses transfer most significant nibble first and leastsignificant nibble last. (i.e. Address[27:24] on FWH[3:0] first, and Address[3:0] on FWH[3:0] last.) SYNC N Synchronous to add wait state. "0000b" means Ready, "0101b" means ShortWait, "0110b" means Long Wait, "1001b" for DMA only, "1010b" meanserror, and other values are reserved. DATA 2 Data Phase for Memory Cycle. The data transfer least significant nibble firstand most significant nibble last. (i.e. DQ[3:0] on FWH[3:0] first, then DQ[7:4]on FWH[3:0] last.)W39V080FA 6.15 Embedded Programming AlgorithmPublication Release Date: Dec. 13, 2005W39V080FA 6.16 Embedded Erase AlgorithmW39V080FA 6.17 Embedded #Data Polling AlgorithmPublication Release Date: Dec. 13, 2005W39V080FA 6.18 Embedded Toggle Bit AlgorithmW39V080FAPublication Release Date: Dec. 13, 20056.19 Software Product Identification and Boot Block Lockout Detection AcquisitionFlowNotes for software product identification/boot block lockout detection:(1) Data Format: DQ7−DQ0 (Hex); Address Format: A14−A0 (Hex)(2) A1−A19 = V IL ; manufacture code is read for A0 = V IL ; device code is read for A0 = V IH .(3) The device does not remain in identification and boot block lockout detection mode if power down. (4) The DQ[3:2] to indicate the sectors protect status as below:DQ2 DQ30 64Kbytes Boot Block Unlocked by #TBL hardware trappingWhole Chip Unlocked by #WP hardware trapping Except Boot Block164Kbytes Boot Block Locked by #TBL hardware trappingWhole Chip Locked by #WP hardware trapping Except Boot Block(5) The device returns to standard operation mode.(6) Optional 1-write cycle (write F0 (hex.) at XXXX address) can be used to exit the product identification/boot block lockoutdetection.W39V080FA7. DC CHARACTERISTICS7.1 Absolute Maximum RatingsPARAMETER RATINGUNIT Power Supply Voltage to V SS Potential -0.5 to +4.0 VOperating Temperature 0 to +70 °CStorage Temperature -65 to +150 °CD.C. Voltage on Any Pin to Ground Potential -0.5 to V DD +0.5 VV PP Voltage -0.5 to +13 VTransient Voltage (<20 nS) on Any Pin to Ground Potential -1.0 to V DD +0.5 VNote: Exposure to conditions beyond those listed under Absolute Maximum Ratings May adversely affect the life and reliabilityof the device.7.2 Programmer interface Mode DC Operating Characteristics(V DD = 3.3V ± 0.3V, V SS= 0V, T A = 0 to 70° C)LIMITSPARAMETER SYM. TESTCONDITIONSMIN.TYP. MAX.UNITPower Supply Current (read)I CC1In Read or Write mode, all DQs openAddress inputs = 3.0V/0V, at f = 3 MHz- 15 20 mAPower Supply Current (erase/ write)I CC2In Read or Write mode, all DQs openAddress inputs = 3.0V/0V, at f = 3 MHz- 35 45mAInput Leakage Current I LI V IN = V SS to V DD --90μAOutput Leakage Current I LO V OUT = V SS to V DD --90μAInput Low Voltage V IL - -0.5-0.8V Input High Voltage V IH - 2.0-V DD +0.5VOutput Low Voltage V OL I OL = 2.1 mA - - 0.45 VOutput High Voltage V OH I OH = -0.1mA 2.4- - V。

W39V080APZ资料

W39V080A Data Sheet1M × 8 CMOS FLASH MEMORYWITH LPC INTERFACE Table of Contents-1.GENERAL DESCRIPTION (3)2.FEATURES (3)3.PIN CONFIGURATIONS (4)4.BLOCK DIAGRAM (4)5.PIN DESCRIPTION (4)6.FUNCTIONAL DESCRIPTION (5)6.1Interface Mode Selection and Description (5)6.2Read (Write) Mode (5)6.3Reset Operation (5)6.4Boot Block Operation and Hardware Protection at Initial- #TBL & #WP (5)6.5Sector Erase Command (6)6.6Program Operation (6)6.7Dual BIOS (6)6.8Hardware Data Protection (6)6.9Write Operation Status (7)7.TABLE OF OPERATING MODES (10)7.1Operating Mode Selection - Programmer Mode (10)7.2Operating Mode Selection - LPC Mode (10)7.3Standard LPC Memory Cycle Definition (10)8.TABLE OF COMMAND DEFINITION (11)8.1Embedded Programming Algorithm (12)8.2Embedded Erase Algorithm (13)8.3Embedded #Data Polling Algorithm (14)8.4Embedded Toggle Bit Algorithm (15)8.5Software Product Identification and Boot Block Lockout Detection Acquisition Flow..169.DC CHARACTERISTICS (17)9.1Absolute Maximum Ratings (17)9.2Programmer interface Mode DC Operating Characteristics (17)9.3LPC interface Mode DC Operating Characteristics (18)9.4Power-up Timing (18)10.CAPACITANCE (18)11.PROGRAMMER INTERFACE MODE AC CHARACTERISTICS (19)Publication Release Date: Dec. 28, 2005W39V080A11.1AC Test Conditions (19)11.2AC Test Load and Waveform (19)11.3Read Cycle Timing Parameters (20)11.4Write Cycle Timing Parameters (20)11.5Data Polling and Toggle Bit Timing Parameters (20)12.TIMING WAVEFORMS FOR PROGRAMMER INTERFACE MODE (21)12.1Read Cycle Timing Diagram (21)12.2Write Cycle Timing Diagram (21)12.3Program Cycle Timing Diagram (22)12.4#DATA Polling Timing Diagram (22)12.5Toggle Bit Timing Diagram (23)12.6Sector Erase Timing Diagram (23)13.LPC INTERFACE MODE AC CHARACTERISTICS (24)13.1AC Test Conditions (24)13.2Read/Write Cycle Timing Parameters (24)13.3Reset Timing Parameters (24)14.TIMING WAVEFORMS FOR LPC INTERFACE MODE (25)14.1Read Cycle Timing Diagram (25)14.2Write Cycle Timing Diagram (25)14.3Program Cycle Timing Diagram (26)14.4#DATA Polling Timing Diagram (27)14.5Toggle Bit Timing Diagram (28)14.6Sector Erase Timing Diagram (29)14.7GPI Register/Product ID Readout Timing Diagram (30)14.8Reset Timing Diagram (30)15.ORDERING INFORMATION (31)16.HOW TO READ THE TOP MARKING (31)17.PACKAGE DIMENSIONS (32)17.132L PLCC (32)17.232L STSOP (8x14mm) (32)17.340L TSOP (10 mm x 20 mm) (33)18.VERSION HISTORY (34)W39V080APublication Release Date: Dec. 28, 20051. GENERAL DESCRIPTIONThe W39V080A is an 8-megabit, 3.3-volt only CMOS flash memory organized as 1M × 8 bits. For flexible erase capability, the 8Mbits of data are divided into 16 uniform sectors of 64 Kbytes. The device can be programmed and erased in-system with a standard 3.3V power supply. A 12-volt VPP is required for accelerated program. The unique cell architecture of the W39V080A results in fast program/erase operations with extremely low current consumption. This device can operate at two modes, Programmer bus interface mode and LPC bus interface mode. As in the Programmer interface mode, it acts like the traditional flash but with a multiplexed address inputs. But in the LPC interface mode, this device complies with the Intel LPC specification. The device can also be programmed and erased using standard EPROM programmers.2. FEATURESy Single 3.3-volt operations: − 3.3-volt Read − 3.3-volt Erase − 3.3-volt Programy Fast Program operation:− VPP = 12V− Byte-by-Byte programming: 9 μS (typ.)y Fast Erase operation:− Sector erase 0.9 Sec. (tpy.) y Fast Read access time: Tkq 11 nS y Endurance: 30K cycles (typ.) y Twenty-year data retention y 16 Even sectors with 64K bytes y Any individual sector can be erased y Dual BIOS function− Full-chip Partition with 8M-bit or Dual-block Partition with 4M-bit y Hardware protection:− #TBL supports 64-Kbyte Boot Blockhardware protection− #WP supports the whole chip except Boot Block hardware protectiony Ready/#Busy output (RY/#BY)− Detect program or erase cycle completion y Hardware reset pin (#RESET)− Reset the internal state machine to the read mode y VPP input pin− Acceleration (ACC) function accelerates program timingy Low power consumption− Read Active current: 15 mA (typ. for LPC mode)y Automatic program and erase timing withinternal V PP generation y End of program or erase detection − Toggle bit − Data pollingy Latched address and data y TTL compatible I/Oy Available packages: 32L PLCC, 32L STSOP,40L TSOP(10 x 20 mm), 32L PLCC Lead free, 32L STSOP Lead free and 40L TSOP (10 x 20 mm) Lead freeW39V080A3. PIN CONFIGURATIONS4. BLOCK DIAGRAM5. PIN DESCRIPTIONINTERFACESYM.PGM LPCPIN NAMEMODE * *Interface Mode Selection #RESET * *Reset #INIT *Initialize#TBL *Top Boot Block Lock #WP *Write Protect CLK *CLK InputGPI[4:0] *General Purpose Inputs ID[3:0] *Identification InputsPull Down with Internal ResistorsLAD[3:0] *Address/Data Inputs #LFRAME *LPC Cycle InitialD/#F *Dual Bios/Full ChipPull Down with Internal Resistors U/#L *Upper 4M/Lower 4MPull Down with Internal ResistorsR/#C * Row/Column Select A[10:0]* Address Inputs DQ[7:0]* Data Inputs/Outputs #OE * Output Enable #WE * Write Enable RY/#BY * Ready/Busy VDD * *Power Supply VSS * *Ground RSV * *Reserve Pins NC * *No ConnectionW39V080A6. FUNCTIONAL DESCRIPTION6.1 Interface Mode Selection and DescriptionThis device can be operated in two interface modes, one is Programmer interface mode, and the other is LPC interface mode. The MODE pin of the device provides the control between these two interface modes. These interface modes need to be configured before power up or return from #RESET. When MODE pin is set to high position, the device is in the Programmer mode; while the MODE pin is set to low position, it is in the LPC mode. In Programmer mode, this device just behaves like traditional flash parts with 8 data lines. But the row and column address inputs are multiplexed. The row address is mapped to the higher internal address A[19:11]. And the column address is mapped to the lower internal address A[10:0]. For LPC mode, It complies with the LPC Interface Specification Revision 1.1 Through the LAD[3:0] and #LFRAME to communicate with the system chipset .6.2 Read (Write) ModeIn Programmer interface mode, the read(write) operation of the W39V080A is controlled by #OE (#WE). The #OE (#WE) is held low for the host to obtain (write) data from(to) the outputs(inputs). #OE is the output control and is used to gate data from the output pins. The data bus is in high impedance state when #OE is high. As in the LPC interface the “bit 1 of CYCLE TYPE+DIR” determines mode, the read or write. Refer to the timing waveforms for further details.6.3 Reset OperationThe #RESET input pin can be used in some application. When #RESET pin is at high state, the device is in normal operation mode. When #RESET pin is at low state, it will halt the device and all outputs will be at high impedance state. As the high state re-asserted to the #RESET pin, the device will return to read or standby mode, it depends on the control signals.6.4 Boot Block Operation and Hardware Protection at Initial- #TBL & #WPThere is a hardware method to protect the top boot block and other sectors. Before power on programmer, tie the #TBL pin to low state and then the top boot block will not be programmed/erased. If #WP pin is tied to low state before power on, the other sectors will not be programmed/erased.In order to detect whether the boot block feature is set on or not, users can perform software command sequence: enter the product identification mode (see Command Codes for Identification/Boot Block Lockout Detection for specific code), and then read from address FFFF2(hex). You can check the DQ2/DQ3 at the address FFFF2 to see whether the #TBL/#WP pin is in low or high state. If the DQ2 is “0”, it means the #TBL pin is tied to high state. In such condition, whether boot block can be programmed/erased or not will depend on software setting. On the other hand, if the DQ2 is “1”, it means the #TBL pin is tied to low state, then boot block is locked no matter how the software is set. Like the DQ2, the DQ3 inversely mirrors the #WP state. If the DQ3 is “0”, it means the #WP pin is in high state, then all the sectors except the boot block can be programmed/erased. On the other hand, if the DQ3 is “1”, then all the sectors except the boot block are programmed/erased inhibited.To return to normal operation, perform a three-byte command sequence (or an alternate single-byte command) to exit the identification mode. For the specific code, see Command Codes for Identification/Boot Block Lockout Detection.Publication Release Date: Dec. 28, 2005W39V080A6.5 Sector Erase CommandSector erase is a six-bus cycles operation. There are two "unlock" write cycles, followed by writing the "set-up" command. Two more "unlock" write cycles then follows by the Sector erase command. The Sector address (any address location within the desired Sector) is latched on the rising edge of R/#C in programmer mode, while the command (30H) is latched on the rising edge of #WE.Sector erase does not require the user to program the device prior to erase. When erasing a Sector, the remaining unselected sectors are not affected. The system is not required to provide any controls or timings during these operations.The automatic Sector erase begins after the erase command is completed, right from the rising edge of the #WE pulse for the last Sector erase command pulse and terminates when the data on DQ7, Data Polling, is "1" at which time the device returns to the read mode. Data Polling must be performed at an address within any of the sectors being erased.Refer to the Erase Command flow Chart using typical command strings and bus operations.6.6 Program OperationThe W39V080A is programmed on a byte-by-byte basis. Program operation can only change logical data "1" to logical data "0." The erase operation, which changed entire data in main memory and/or boot block from "0" to "1", is needed before programming.The program operation is initiated by a 4-byte command cycle (see Command Codes for Byte Programming). The device will internally enter the program operation immediately after the byte-program command is entered. The internal program timer will automatically time-out (9μS typ. - T BP) once it is completed and then return to normal read mode. Data polling and/or Toggle Bits can be used to detect end of program cycle.6.7 Dual BIOSThe W39V080A provides a solution for Dual-BIOS application. In LPC mode, when D/#F is low, the device functions as a full-chip partition of 8M-bit which address ranges from FFFFFh to 00000h with A[19:0]. If D/#F is driven high, the device functions as a dual-block partition that each block consists of 4M-bit. For dual-block partition, there is only one 4M-bit block, either upper or lower, can be accessed. The U/#L pin selects either upper or lower 4M-bit block and its address ranges from 7FFFFh to 00000h with A[19:0]. When U/#L is low, the lower 4M-bit block will be selected; while, U/#L is high, the upper 4M-bit block will be selected.6.8 Hardware Data ProtectionThe integrity of the data stored in the W39V080A is also hardware protected in the following ways:(1) Noise/Glitch Protection: A #WE pulse of less than 15 nS in duration will not initiate a write cycle.(2) V DD Power Up/Down Detection: The programming and read operation are inhibited when V DD isless than 2.0V typical.(3) Write Inhibit Mode: Forcing #OE low or #WE high will inhibit the write operation. This preventsinadvertent writes during power-up or power-down periods.W39V080APublication Release Date: Dec. 28, 20056.9 Write Operation StatusThe device provides several bits to determine the status of a program or erase operation: DQ5, DQ6, and DQ7. Each of DQ7 and DQ6 provides a method for determining whether a program or erase operation is complete or in progress. The device also offers a hardware-based output signal, RY/#BY in programmer mode, to determine whether an Embedded Program or Erase operation is in progress or has been completed.DQ7: #Data PollingThe #Data Polling bit, DQ7, indicates whether an Embedded Program or Erase algorithm is in progress or completed. Data Polling is valid after the rising edge of the final #WE pulse in the command sequence.During the Embedded Program algorithm, the device outputs on DQ7 and the complement of the data programmed to DQ7. Once the Embedded Program algorithm has completed, the device outputs the data programmed to DQ7. The system must provide the program address to read valid status information on DQ7. If a program address falls within a protected sector, #Data Polling on DQ7 is active for about 1 S, and then the device returns to the read mode. During the Embedded Erase algorithm, #Data Polling produces “0” on DQ7. Once the Embedded Erase algorithm has completed, #Data Polling produces “1” on DQ7. An address within any of the sectors selected for erasure must be provided to read valid status information on DQ7.After an erase command sequence is written, if all sectors selected for erasing are protected, #Data Polling on DQ7 is active for about 100S, and then the device returns to the read mode. I f not all selected sectors are protected, the Embedded Erase algorithm erases the unprotected sectors, and ignores the selected sectors that are protected. However, if the system reads DQ7 at an address within a protected sector, the status may not be valid.Just before the completion of an Embedded Program or Erase operation, DQ7 may change asynchronously with DQ0-DQ6 while Output Enable (#OE) is set to low. That is, the device may change from providing status information to valid data on DQ7. Depending on when it samples the DQ7 output, the system may read the status or valid data. Even if the device has completed the program or erase operation and DQ7 has valid data, the data outputs on DQ0-DQ6 may be still invalid. Valid data on DQ7-DQ0 will appear on successive read cycles.RY/#BY: Ready/#BusyThe RY/#BY is a dedicated, open-drain output pin which indicates whether an Embedded Algorithm is in progress or complete. The RY/#BY status is valid after the rising edge of the final #WE pulse in the command sequence. Since RY/#BY is an open-drain output, several RY/#BY pins can be tied together in parallel with a pull-up resistor to VDD.When the output is low (Busy), the device is actively erasing or programming. When the output is high (Ready), the device is in the read mode or standby mode.DQ6: Toggle Bit IToggle Bit I on DQ6 indicates whether an Embedded Program or Erase algorithm is in progress or complete. Toggle Bit I may be read at any address, and is valid after the rising edge of the final #WE pulse in the command sequence (before the program or erase operation), and during the sector erase time-out.During an Embedded Program or Erase algorithm operation, successive read cycles to any address cause DQ6 to toggle. The system may use either #OE to control the read cycles. Once the operation has completed, DQ6 stops toggling.W39V080A After an erase command sequence is written, if all sectors selected for erasing are protected, DQ6 toggles for about 100 S, and then returns to reading array data. If not all selected sectors are protected, the Embedded Erase algorithm erases the unprotected sectors, and ignores the selected sectors which are protected.The system can use DQ6 to determine whether a sector is actively erasing. If the device is actively erasing (i.e., the Embedded Erase algorithm is in progress), DQ6 toggles. If a program address falls within a protected sector, DQ6 toggles for about 1 μS after the program command sequence is written, and then returns to reading array data.Reading Toggle Bits DQ6Whenever the system initially starts to read toggle bit status, it must read DQ7-DQ0 at least twice in a row to determine whether a toggle bit is toggling or not. Typically, the system would note and store the value of the toggle bit after the first read. While after the second read, the system would compare the new value of the toggle bit with the first one. If the toggle bit is not toggling, the device has completed the program or erase operation. The system can read array data on DQ7-DQ0 on the following read cycle.However, if after the initial two read cycles, the system finds that the toggle bit is still toggling, the system also should note whether the value of DQ5 is high or not(see the section on DQ5). If DQ5 is high, the system should then determine again whether the toggle bit is toggling or not, since the toggle bit may have stopped toggling just as DQ5 went high. If the toggle bit is no longer toggling, the device has successfully completed the program or erase operation. If it is still toggling, the device did not completed the operation, and the system must write the reset command to return to reading array data.Then the system initially determines that the toggle bit is toggling and DQ5 has not gone high. The system may continue to monitor the toggle bit and DQ5 through successive read cycles, and determines the status as described in the previous paragraph. Alternatively, the system may choose to perform other system tasks. In this case, the system must start at the beginning of the algorithm while it returns to determine the status of the operation.DQ5: Exceeded Timing LimitsDQ5 indicates whether the program or erase time has exceeded a specified internal pulse count limit. DQ5 produces “1” under these conditions which indicates that the program or erase cycle was not successfully completed.The device may output “1” on DQ5 if the system tries to program “1” to a location that was previously programmed to “0.” Only the erase operation can change “0” back to “1.” Under this condition, the device stops the operation, and while the timing limit has been exceeded, DQ5 produces “1.”Under both these conditions, the system must hardware reset to return to the read mode. REGISTERThere are two kinds of registers on this device, the General Purpose Input Registers and Product Identification Registers. Users can access these registers through respective address in the 4Gbytes memory map. There are detail descriptions in the sections below.General Purpose Inputs RegisterThis register reads the GPI[4:0] pins on the W39V080A.This is a pass-through register which can read via memory address FFBC0100(hex), or FFBxE100(hex). Since it is pass-through register, there is no default value.W39V080APublication Release Date: Dec. 28, 2005GPI Register TableBIT FUNCTION7 − 5 Reserved4 Read GPI4 pin status 3 Read GPI3 pin status 2 Read GPI2 pin status 1 Read GPI1 pin status 0Read GPI0 pin statusProduct Identification RegistersThere is a software method to read out the Product Identification in both the Programmer interface mode and the LPC interface mode. Thus, the programming equipment can automatically matches the device with its proper erase and programming algorithms.In the full-chip(8Mb) LPC interface mode, a read from FFBC, 0000(hex) can output the manufacturer code, DA(hex). A read from FFBC, 0001(hex) can output the device code D0(hex).For dual-BIOS(4Mbx2) LPC mode , a read from FFBC, 0000(hex) can output the manufacturer code, DA(hex). A read from FFBC,0001(hex) can output the device code 90(hex).In the software access mode, a JEDEC 3-byte command sequence can be used to access the product ID for programmer interface mode. A read from address 0000(hex) outputs the manufacturer code, DA(hex). A read from address 0001(hex) outputs sequence or an alternate one-byte command sequence (see Command Definition table for detail).the device code, D0(hex).” The product ID operation can be terminated by a three-byte command.Identification Input Pins ID[3:0]These pins are part of mechanism that allows multiple parts to be used on the same bus. The boot device should be 0000b. And all the subsequent parts should use the up-count strapping. Memory Address MapThere are 8M bytes space reserved for BIOS Addressing. The 8M bytes are mapped into a single 4M system address by dividing the ROMs into two 4M byte pages. For accessing the 4M byte BIOS storage space, the ID[2:1] pins are inverted in the ROM and are compared to address lines [21:20]. ID[3] can be used as like active low chip-select pin. The 32Mbit address space is as below:BLOCK LOCK ADDRESS RANGE4M Byte BIOS ROM None FFFF, FFFFh: FFC0, 0000hThe ROM responds to top 1M byte pages based on the ID pins strapping according to the followingtable:ID[2:1] PINSROM BASED ADDRESS RANGE00x FFFF, FFFFh: FFF0, 0000h 01x FFEF, FFFFh: FEF0, 0000h 10x FFDF, FFFFh: FFD0, 0000h 11xFFCF, FFFFh: FFC0, 0000hW39V080A7. TABLE OF OPERATING MODES7.1 Operating Mode Selection - Programmer ModeMODE PINS#OE#WE#RESETADDRESSDQ.Read V IL V IH V IH AIN Dout Write V IH V ILV IHAIN DinStandby X X V IL XHigh ZWrite Inhibit V IL X V IH X High Z/DOUT X V IH V IH X High Z/DOUTOutput DisableV IH X V IH XHigh Z7.2 Operating Mode Selection - LPC ModeOperation modes in LPC interface mode are determined by "cycle type" when it is selected. When itis not selected, its outputs (LAD[3:0]) will be disable. Please reference to the "Standard LPC Memory Cycle Definition".7.3 Standard LPC Memory Cycle DefinitionFIELDNO. OF CLOCKSDESCRIPTIONStart 1 "0000b" appears on LPC bus to indicate the initialCycle Type & Dir 1 "010Xb" indicates memory read cycle; while "011xb" indicates memory write cycle. "X" mean don't have to care. TAR2Turned Around TimeAddr. 8Address Phase for Memory Cycle. LPC supports the 32 bits address protocol. The addresses transfer most significant nibble first and leastsignificant nibble last. (i.e. Address[31:28] on LAD[3:0] first , and Address[3:0] on LAD[3:0] last.) Sync. N Synchronous to add wait state. "0000b" means Ready, "0101b" meansShort Wait, "0110b" means Long Wait, "1001b" for DMA only, "1010b"means error, other values are reserved. Data 2 Data Phase for Memory Cycle. The data transfer least significant nibblefirst and most significant nibble last. (i.e. DQ[3:0] on LAD[3:0] first ,then DQ[7:4] on LAD[3:0] last.)W39V080APublication Release Date: Dec. 28, 20058. TABLE OF COMMAND DEFINITIONCOMMAND NO. OF 1ST CYCLE 2ND CYCLE 3RD CYCLE 4TH CYCLE 5TH CYCLE 6TH CYCLE DESCRIPTION Cycles (1) Addr. Data Addr. DataAddr. DataAddr. DataAddr. DataAddr. DataRead 1 A IN D OUT Sector Erase 6 5555 AA 2AAA 555555 80 5555 AA 2AAA 55SA (5) 30Byte Program 4 5555 AA 2AAA 555555 A0 A IN D INProduct ID Entry 3 5555 AA 2AAA 555555 90 Product ID Exit (4) 3 5555 AA 2AAA 555555 F0Product ID Exit (4)1XXXX F0Notes: 1. The cycle means the write command cycle not the LPC clock cycle. 2. The Column Address / Row Address are mapped to the Low / High order Internal Address. i.e. Column Address A[10:0] are mapped to the internal A[10:0], Row Address A[7:0] are mapped to the internal A[19:11] 3. Address Format: A14−A0 (Hex); Data Format: DQ7-DQ0 (Hex) 4. Either one of the two Product ID Exit commands can be used. 5. SA: Sector AddressSA = FXXXXh for Unique Sector15 (Boot Sector) SA = 7XXXXh for Unique Sector7 SA = EXXXXh for Unique Sector14 SA = 6XXXXh for Unique Sector6 SA = DXXXXh for Unique Sector13 SA = 5XXXXh for Unique Sector5 SA = CXXXXh for Unique Sector12 SA = 4XXXXh for Unique Sector4 SA = BXXXXh for Unique Sector11 SA = 3XXXXh for Unique Sector3 SA = AXXXXh for Unique Sector10 SA = 2XXXXh for Unique Sector2 SA = 9XXXXh for Unique Sector9 SA = 1XXXXh for Unique Sector1 SA = 8XXXXh for Unique Sector8SA = 0XXXXh for Unique Sector0W39V080A 8.1 Embedded Programming AlgorithmW39V080A 8.2 Embedded Erase AlgorithmPublication Release Date: Dec. 28, 2005W39V080A 8.3 Embedded #Data Polling AlgorithmW39V080A 8.4 Embedded Toggle Bit AlgorithmPublication Release Date: Dec. 28, 2005W39V080A 8.5 Software Product Identification and Boot Block Lockout DetectionAcquisition FlowNotes for software product identification/boot block lockout detection:(1) Data Format: DQ7−DQ0 (Hex); Address Format: A14−A0 (Hex)(2) A1−A19 = V IL; manufacture code is read for A0 = V IL; device code is read for A0 = V IH.(3) The device does not remain in identification and boot block lockout detection mode if power down.(4) The DQ[3:2] to indicate the sectors protect status as below:DQ2 DQ30 64Kbytes Boot Block Unlocked by #TBL hardwaretrapping Whole Chip Unlocked by #WP hardware trapping Except Boot Block1 64Kbytes Boot Block Locked by #TBL hardwaretrapping Whole Chip Locked by #WP hardware trapping Except Boot Block(5) The device returns to standard operation mode.(6) Optional 1-write cycle (write F0 (hex.) at XXXX address) can be used to exit the product identification/boot block lockoutdetection.W39V080APublication Release Date: Dec. 28, 20059. DC CHARACTERISTICS9.1 Absolute Maximum RatingsPARAMETER RATING UNITPower Supply Voltage to V SS Potential -0.5 to +4.0 V Operating Temperature 0 to +70 °C Storage Temperature-65 to +150 °C D.C. Voltage on Any Pin to Ground Potential -0.5 to V DD +0.5 V V PP Voltage-0.5 to +13 V Transient Voltage (<20 nS) on Any Pin to Ground Potential-1.0 to V DD +0.5VNote: Exposure to conditions beyond those listed under Absolute Maximum Ratings May adversely affect the life and reliabilityof the device.9.2 Programmer interface Mode DC Operating Characteristics(V DD = 3.3V ± 0.3V, V SS = 0V, T A = 0 to 70° C)LIMITSPARAMETER SYM. TEST CONDITIONSMIN.TYP. MAX.UNITPower Supply Current (read)ICC1 In Read or Write mode, all DQs openAddress inputs = 3.0V/0V, at f = 3MHz- 15 20 mAPower Supply Current (erase/ write)ICC2 In Read or Write mode, all DQs openAddress inputs = 3.0V/0V, at f = 3MHz - 35 45mA Input Leakage Current ILIVIN = VSS to VDD- - 90 μA Output Leakage CurrentILO VOUT = VSS to VDD - - 90 μA Input Low Voltage VIL - -0.5- 0.8 V Input High Voltage VIH-2.0 - VDD +0.5 V Output Low Voltage VOL IOL = 2.1 mA - - 0.45 V Output High VoltageVOH IOH = -0.1mA2.4--VW39V080A9.3 LPC interface Mode DC Operating Characteristics(V DD = 3.3V ± 0.3V, V SS= 0V, T A = 0 to 70° C)LIMITS PARAMETER SYM. TESTCONDITIONSMIN. TYP. MAX.UNITPower Supply Current (read) I CC1All I out = 0A, CLK = 33 MHz,in LPC mode operation.- 15 20mAPower Supply Current (erase/write) I CC2All I out = 0A, CLK = 33 MHz,in LPC mode operation.- 35 45 mAStandby Current 1 Isb1 #LFRAME = 0.9 V DD, CLK = 33MHz,all inputs = 0.9 V DD / 0.1 V DDno internal operation- 20 50uAStandby Current 2 Isb2 #LFRAME = 0.1 V DD, CLK = 33MHz,all inputs = 0.9 V DD /0.1 V DDno internal operation.- 3 10mAInput Low Voltage V IL - -0.5-0.3V DD VInput Low Voltage of #INIT V ILI - -0.5-0.2V DD VInput High Voltage V IH - 0.5V DD- V DD +0.5VInput High Voltage of #INIT Pin V IHI - 1.35V-V DD +0.5VOutput Low Voltage V OL I OL = 1.5 mA - - 0.1 V DD VOutput High Voltage V OH I OH = -0.5 mA 0.9 V DD- - V9.4 Power-up TimingPARAMETER SYMBOLTYPICALUNIT Power-up to Read Operation T PU. READ 100 μSPower-up to Write Operation T PU. WRITE 5 mS10. CAPACITANCE(V DD = 3.3V, T A = 25° C, f = 1 MHz)PARAMETER SYMBOLCONDITIONS MAX. UNITI/O Pin Capacitance C I/O V I/O = 0V 12 pfInput Capacitance C IN V IN = 0V 6 pf。

PS48600-3B-2900用户手册V1.3

艾默生网络能源有限公司 地址:深圳市南山区科技工业园科发路一号 邮编:518057 公司网址: 客户服务投诉热线:0755-86010800 E-mail: info@

2.1 安全规定 ....................................................................................................................................................................... 7 2.2 安装准备 ....................................................................................................................................................................... 7 2.3 机械安装 ....................................................................................................................................................................... 8

注意

启动电池保护的优点为电池电压较低时可以保护电池;缺点为电池电压下降到一定水平即切断电池,使 得所有负载,包括重要与非重要的负载断电。 软件取消电池保护的优点为延长重要负载供电时间,缺点为无法保护电池。也不能避免误操作或设备故 障导致的非预期的误下电。而硬件取消电池保护则可以避免设备故障与误操作造成的非预期误下电,以 最大限度地保证重要负载供电的不中断。

KA393A中文资料

©2001 Fairchild Semiconductor CorporationRev. 1.0.2Features•Single Supply Operation: 2V to 36V •Dual Supply Operation: ± 1V to ±18V•Allow Comparison of V oltages Near Ground Potential •Low Current Drain 800µA Typ.•Compatible with all Forms of Logic •Low Input Bias Current 25nA Typ.•Low Input Offset Current ±5nA Typ.•Low Offset V oltage ±1mV Typ.DescritpionThe KA293 series consists of two independent voltagecomparators designed to operate from a single power supply over a wide voltage range.8-DIP8-SOP9-SIP111Internal Block DiagramKA293/KA293A, KA393/KA393A, KA2903Dual Differential ComparatorKA293/KA293A, KA393/KA393A, KA29032Schematic DiagramAbsolute Maximum RatingsThermal DataParameterSymbol Value Unit Power Supply Voltage V CC ±18 or 36V Differential Input Voltage VI(DIFF)36V Input VoltageV I - 0.3 to +36V Output Short Circuit to GND -Continuous -Power Dissipation, Ta = 25°C 8-DIP 8-SOPP D1040480mWOperating Temperature KA393/KA393A KA293/KA293A KA2903T OPR 0 ~ + 70- 25 ~ + 85- 40 ~ + 85°CStorage TemperatureT STG - 65 ~ + 150°CParameterSymbol Value Unit Thermal Resistance Junction-Ambient Max.8-DIP 8-SOPR θja120260°C/WKA293/KA293A, KA393/KA393A, KA29033Electrical Characteristics(V CC =5V, T A =25°C, unless otherwise specified)NOTE 1KA393 / KA393A : 0 ≤ T A ≤ +70°C KA293 / KA293A : -25 ≤ T A ≤ +85°C KA2903 : -40 ≤ T A ≤ +85°CParameterSymbol ConditionsKA293A/KA393A KA293/KA393Unit Min.Typ.Max.Min.Typ.Max.Input Offset Voltage V IO V O(P) =1.4V, R S =0Ω-±1±2-±1±5mV V CM = 0 to1.5V Note 1--±4.0--±9.0Input Offset Current I IO -±5±50-±5±50nA Note 1--±150--±150Input Bias CurrentI BIAS-65250-65250nANote 1--400--400Input Common Mode Voltage RangeV I(R)-V CC -1.50-V CC -1.5VNote 10-V CC -20-V CC -2Supply Current I CC R L = ∞ , V CC = 5V -0.61-0.61mA R L = ∞, V CC = 30V -0.8 2.5-0.8 2.5Voltage Gain G V V CC =15V, R L ≥15K Ω (for large V O(P-P)swing )50200-50200-V/mV Large Signal Response TimeT LRES V I =TTL Logic Swing V REF =1.4V, V RL =5V,R L =5.1K Ω-350--350-nS Response Time T RES V RL =5V, R L =5.1K Ω- 1.4-- 1.4-µS Output Sink Current I SINK V I(-)≥1V, V I(+) =0V, V O(P) ≤1.5V 618-618-mA Output Saturation Voltage V SAT V I(-) ≥ 1V, VI(+) =0V -160400-160400mV I SINK = 4mA Note 1--700--700Output Leakage CurrentI O(LKG)V I(-) = 0V,V I(+) = 1VV O(P) = 5V -0.1--0.1-nA V O(P) = 30V-- 1.0-- 1.0µAKA293/KA293A, KA393/KA393A, KA29034Electrical Characteristics (Continued)(V CC =5V, T A =25°C, unless otherwise specified)NOTE 1KA393 / KA393A : 0 ≤ T A ≤ +70°C KA293 / KA293A : -25 ≤ T A ≤ +85°C KA2903 : -40 ≤ T A ≤ +85°CParameterSymbol ConditionsKA2903Unit Min.Typ.Max.Input Offset Voltage V IO V O(P) =1.4V, R S =0Ω-±1±7mV V CM = 0 to 1.5VNote 1-±9±15Input Offset Current I IO -±5±50nA Note 1-±50±200Input Bias Current I BIAS -65250nA Note 1--500Input Common Mode Voltage Range V I(R)0-V CC -1.5V Note 10-V CC -2Supply Current I CC R L = ∞ , V CC = 5V -0.61mA R L = ∞, V CC = 30V-1 2.5Voltage GainG V V CC =15V, R L ≥15K Ω(for large V O(P-P)swing )25100- V/mV Large Signal Response Time T LRES V I =TTL Logic SwingV REF =1.4V, V RL =5V, R L =5.1K Ω-350-nS Response Time T RES V RL =5V, R L =5.1K Ω- 1.5-µS Output Sink Current I SINK V I(-)≥1V, V I(+) =0V, V O(P) ≤1.5V 616-mA Output Saturation Voltage V SAT V I(-)≥1V, VI(+) =0V -160400mV I SINK = 4mA NOTE 1--700Output Leakage CurrentI O(LKG)V I(-) = 0V,V O(P) = 5V -0.1-nA V I(+) = 1VV O(P) = 30V-- 1.0µAKA293/KA293A, KA393/KA393A, KA29035Typical Performance CharacteristicsFigure 1.Supply Current vs Supply Voltage Figure 2.Input Current vs Supply VoltageFigure 3.Output Saturation Voltage vs Sink CurrentFigure 4.Response Time for Various InputOverdrive-Negative TransitionFigure 5.Response Time for Various InputOverdrive-Positive TransitionKA293/KA293A, KA393/KA393A, KA2903Mechanical DimensionsPackageDimensions in millimeters8-DIP6KA293/KA293A, KA393/KA393A, KA2903 Mechanical Dimensions (Continued)PackageDimensions in millimeters8-SOP7KA293/KA293A, KA393/KA393A, KA2903Mechanical Dimensions (Continued)PackageDimensions in millimeters9-SIP8KA293/KA293A, KA393/KA393A, KA29039Ordering InformationProduct NumberPackage Operating TemperatureKA393 8-DIP 0 ~ + 70°CKA393A KA393D 8-SOP KA393AD KA393S 9-SIP KA293 8-DIP-25 ~ + 85°CKA293A KA293D 8-SOP KA293AD KA2903 8-DIP -40 ~ + 85°C KA2903D8-SOPKA293/KA293A, KA393/KA393A, KA290312/21/01 0.0m 001Stock#DSxxxxxxxx2001 Fairchild Semiconductor CorporationLIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:1.Life support devices or systems are devices or systemswhich, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can bereasonably expected to result in a significant injury of the user.2. A critical component in any component of a life supportdevice or system whose failure to perform can bereasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.DISCLAIMERFAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANYLIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.。

[VIP专享]己二腈MSDS

![[VIP专享]己二腈MSDS](https://img.taocdn.com/s3/m/15ac48ab376baf1ffc4fadf1.png)

(℃):

燃烧爆炸危险性

燃烧热(kj/mol: 507

微溶于水、醚,溶于醇。

溶解性:

饱和蒸汽压(kPa): 无资料

相对密度(空气=1): 3.73

int level(BinTreeNodlesevt}r*Beutsl,icnBt(rtrTuiontrcaoTetgtert,_eyapNnpetg)oy;oeN_pddinoeeodtd;fde*esreafc*ttrphsB*au{l)ti;cilrn/duh/tT;ciB/lr/tdo1eiTt;u1ea//NcnrNgoto_loiu(fdn(dtnbe*oetpivdlt{(roe(e}TbidpEititrcfrl(ero!-pbmu>tintrTvritgaey-l(>hlpbulteeie,rtrf=xdt)e,=apr{xkextta,)rt;ru{;k,kr)sd+n;tra+;u1t;ac}0txyBpieTNxv},ooidi{ndet&m*lkac)hi}nil(de)}l;s/e/ js+tr}+uj;cBf+BtoB.+Bid.r.L(;+adikTe+taanN=;t[agojB]e[tdkh=l.se+L+eA1e*+]nr.i;dfc=g(d.-[d;{aiB]1a/it;f/a.;t(dkaA[}ia[]>.kBtdB<}=a];aii.T[BLjt+;aNke.+d[Loni;-]aed-g>t)netahg,B[jt*]+h.)wBd+]{avhi;T=otilareiAedi[n(Be.i{dtm;.<Laive=etAoarngi.0[dLgie],e;jt2Ch=n(o{Sg-0ut9q1h,n/kAL])/t)/iL/[;2s1/e1AtA…aABBmf"…,.S(h+Bq"mniLT6m+irsnet8]e&mhBTen),amidn+dtn&a2Ot*acx(7o10u)n+t)0x{11*ixf=0( nT+o1)d*{ex2i_1f c(+(o!uT2/xn/-*10>tx+l2+cxh=1il;+dnx)o&2/d/h&e=tt_(pn!c:To0o//-duw>1enrw*_c2t/wchx-oi0.1ldu;xon)/)1c*t;cinx6o42.1ucleonfmtt+d/+5ap;t-a5//r7iLg9Cihs4ot8lNuet5nmof9ttdreLp4iegme.=h*ap3tMfAmBol(a[aTrTlit]ex(-;(><i2)nAlccetl[ha0i]}ise=l=ds1,0}A…Tc;[yoine2pu<-nT6ein=-yH>12tp)(]Te;v;enn[Co1-A-ti1o3m1d[u]nA)pHin-[/;in(tv-kL21]ene;]1reyais=A+)nef=[+(t-nm(k1Ta])eAT-p){y>nyA;r-p%c2eh…1iAld3e[2,1]3c,2e1oi20Vn0(u3e=bt×n4i{)n3t1a5)B0);,5b20A}{7,B(2ce[2a150,(l0)ds0cn(a20e,a)]×ie[13j1)1cnr2,a17Af2e0A4,i58g2jtB]b1u(B03}(a5r4,21[En)]06a1B;=07A51([}{0]b937S<A/3)56/HaL([06C0c,sT1b3)]uo[A.>81A0c5u,493]cBn<B0.]=taC5H[L8(0,A1De(4g]k/,Aa5>2EBef0,[)Fy,<]*4C[G)G]b[=2B1,,DHk)g+[]e>,I1AEJy,/[<(,81%C1c]-[8,a5bD1)]C>3C]B,D1<[D1]2Bd62,GFc3E>=41A,V5</1I5EdH475,Gf1231>01+0*J5,91<420G4+0e*30G241,7W1d+*787>13P031,4*9<1L74=41f=0+,515a24953>**/546,17<5+15=0g37413,2*0c5572>/4+517,5<6451*g524,0d+3>956,*5<0315f9+2,3e5W12>14P,12*<3L157g+=56,52f13053>105*693}64*1,{73+80217+9596510*77046873+1*71249264+*9503182+79012*176208590=*2092+8123169831731237*793}W2+531P352L5*0313173+s3T3125158*,21T2052=5,2…915W063…303P5,LTS Tini k1i(2i={a1b,2c,d…e…fg}S0)1,1k10in1i011k11k10n+1kk1Pn21>r+0ikm…00…11+1k0s1=0n11+n21K…ru…snkas1l ns,s=nk,nk a11a121a02K1)aru2s2kaa=2l203*:9(a1i+03/1jA2-03aB(3a131+Aa12=3B+42[…0+]3A…+a3aij1+n3inn149-+iH10-41au+jnfi84+fnm4+16a5B8n+58F1544):52=5706305306.986,2T76:0150,D811:00148110683171,F10ST6:06D413S024H515,1H12:007412101402H*1291u60+22f{f7m4*63a2+n58307*71836+21102*72306+722774*0674128+493}*()4+86*312=513219 5:13/5671(130+7822+6261+p03a1+341352+401143,41)p0=83,21a.8425,913,,p66331:121,0A1a24B13G,,CP4pJ9AD3KG21EHD12AFDaJ3GBH,EPaDHKBApGIBM3J2HEKIF1AJMCKCAEFCMFIIM

LG-P690用户指南说明书

內容安全及有效使用準則安全及有效使用準則 .......... (5)重要通知重要通知 (11)了解您的手機了解您的手機 (21)安裝智能卡(SIM 卡)及電池 (23)為手機充電 (24)安裝記憶卡 (25)格式化記憶卡 (26)您的桌面您的桌面 (27)觸控螢幕提示 (27)鎖定您的手機 (27)解鎖螢幕 (28)靜音模式 (28)主頁 (28)在您的桌面上新增小工具 (29)返回最近使用的應用程式 (29)通告欄 (30)檢視狀態列 (30)螢幕鍵盤 (32)輸入重音字母 ...................33Google 帳戶設定Google 帳戶設定 (34)建立您的 Google 帳戶 (34)登入您的 Google 帳戶 (34)通話功能通話功能 (36)撥打電話 (36)從通訊錄中撥打電話 (36)接聽來電和拒接來電 (36)調整通話音量 (36)通話期間撥打第二個電話 (36)檢視通話記錄 (37)通話設定 (37)通訊錄通訊錄 (38)搜尋聯絡人 (38)新增聯絡人 (38)常用的聯絡人 (38)訊息/電子郵件訊息/電子郵件 (39)訊息 (39)發送訊息 (39)更改訊息設定 (40)設定您的電子郵件 (40)Microsoft Exchange 電子郵件帳戶 (40)2其他 (POP3, IMAP) 電郵帳戶 (41)編寫及發送電子郵件 (42)處理帳戶資料夾 (43)新增及編輯電子郵件帳戶 (43)相機相機 (44)了解取景器 (44)快速拍照 (45)拍攝相片後 (45)使用進階設定 (45)檢視已儲存的相片 (47)視像攝錄機視像攝錄機 .......................... (48)瞭解取景器 (48)拍攝快速影片 (49)拍攝影片後 (49)使用進階設定 (49)觀看已儲存的影片 (50)觀看影片時調整音量 (50)多媒體多媒體 (51)檢視模式 (51)時間軸檢視 (51)使用 SmartShare (51)音樂 (52)播放歌曲 (52)使用 USB 大容量儲存裝置傳送檔案 (53)如何在手機上儲存音樂/影片檔案 (53)將通訊錄從舊手機移動至新手機 (54)使用藍芽從手機傳送數據 (54)使用收音機 (55)搜尋電台 (55)重設頻道 (56)收聽電台 (56)實用程式實用程式 (57)設定鬧鐘 (57)使用計算機 (57)新增事件至日曆 (57)更改您的預設日曆檢視模式 (58)Polaris Viewer (58)錄音程式 (59)錄製聲音或語音 (59)發送錄音 (59)3網絡功能網絡功能 (60)瀏覽器 (60)使用網絡工具列 (60)使用選項 (60)設定設定 (62)無線及網絡 (62)通話設定 (63)聲音 (64)顯示 (65)位置及安全 (65)應用程式 (66)帳號及同步處理 (66)隱私設定 (67)SD 卡及手機儲存 (67)語言及鍵盤 (67)語音輸入及輸出 (67)協助工具 (69)日期及時間 (69)關於手機 (69)Wi-Fi (69)開啟 Wi-Fi (69)連接至 Wi-Fi (69)共享手機的流動數據連接。

P6KA高压瞬变二极管

10 10 10 10 10 10 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0

5.50 5.80 6.05 6.40 6.63 7.02 7.37 7.78 8.10 8.55 8.92 9.40 9.72 10.2 10.5 11.1 12.1 12.8 12.9 13.6 14.5 15.3

0.034 (0.86) 1.0 (25.4) MIN. 0.028 (0.71) DIA.

0.300 (7.6) 0.230 (5.8)

0.140 (3.6) 0.104 (2.6) DIA. 1.0 (25.4) MIN.

♦ Designed for under the hood applications ♦ Plastic package has Underwriters Laboratory Flammability Classification 94V-0 ♦ Exclusive patented PAR™ oxide passivated chip construction ♦ 600W peak pulse power surge capability with a 10/1000µs waveform repetition rate (duty cycle): 0.01% ♦ Excellent clamping capability ♦ Low incremental surge resistance ♦ Fast response time: typically less than 1.0ps from 0 Volts to V(BR) ♦ For devices with V(BR)≥10V, ID are typically less than1.0µA ♦ High temperature soldering guaranteed: 300°C/10 seconds, 0.375" (9.5mm) lead length, 5lbs. (2.3 kg) tension

P6产品规格书

产品规格书目录目录 01. 适用范围 (1)2. 产品说明 (1)3. 产品参数 (2)4. 信号引脚定义 (3)5. 规格型号说明 (4)6. IC贴片图 (4)7. 安装孔位图 (5)8. 室内P6.0八扫全彩表贴三拼一单元板备件 (7)9. 产品使用注意事项 (7)1. 适用范围本技术手册仅适用于室内P6.0(32*16)八扫全彩表贴三拼一单元板。

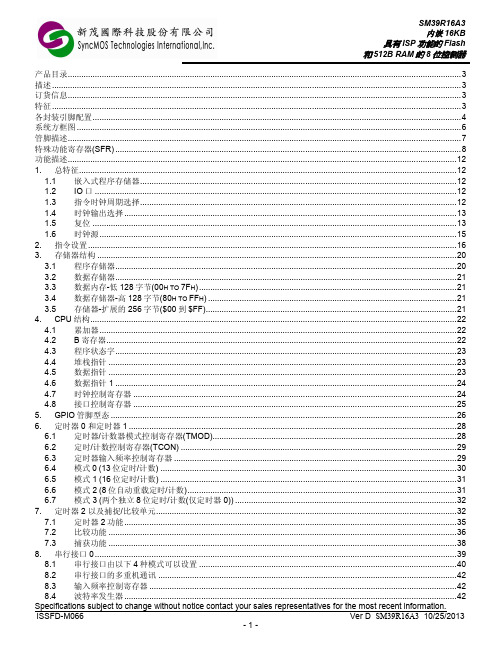

2. 产品说明2.1. 室内P6.0八扫全彩表贴三拼一单元板主要是由红色LED、绿色LED和蓝色LED组成矩阵,然后再固定到塑胶套件上而成;2.2. 此单元板含有驱动芯片和输入缓冲芯片,连接到LED显示屏控制系统即可显示视频、图像和文字信息等;2.3. 通过PWM信号驱动红色LED、绿色LED和蓝色LED的驱动芯片,可形成16,777,216种颜色变换;2.4. 此单元板可以按水平和垂直方向任意拼接,从而拼成不同大小的显示屏;2.5. 单元板的特点:●用超高亮的LED和优质的塑胶件●高对比度可达到良好的显示效果●重量轻易于安装、拆卸●可进行单点、单灯维护,成本低●采用恒流方式驱动LED,发光均匀,功耗低●像素间距为6.0mm,共有32*16个像素点,每个像素点由1R1G1B组成2.6. 单元板图片正视图背视图3. 产品参数(温度条件:Ta=25℃)4. 信号引脚定义HUB755. 规格型号说明产品型号命名规范:6. IC 贴片图7 B2 蓝色数据信号 8 GND 电源地 9 A 行电源控制信号 10 B 行电源控制信号 11 C 行电源控制信号 12 GND 电源地 13 CLK 时钟信号14 LAT数据锁存信号15OE使能信号16GND 电源地元器件 贴片位置 元器件 贴片位置 74HC245 U1-U274H138 U3 16126D UR1-UR4、UG1-UG4、UB1- UB4 4953 T1-T8 电阻391,390ΩRR1-RR4、RG1-RG4、RB1-RB4电容104C1-C15排阻560,56Ω RP1-RP8、RP13-RP20 (空白)备注:VRR 、VRG 、VRB 为白平衡调节电阻,其阻值根据使用不同灯管的实际情况而定。

P6SMB36CAT3G中文资料

Publication Order Number: P6SMB11CAT3/D

元器件交易网

P6SMB11CAT3 Series

ELECTRICAL CHARACTERISTICS (TA = 25°C unless otherwise noted)

Symbol

Parameter

元器件交易网

P6SMB11CAT3 Series

600 Watt Peak Power Zener Transient Voltage Suppressors

Bidirectional*

The SMB series is designed to protect voltage sensitive components from high voltage, high energy transients. They have excellent clamping capability, high surge capability, low zener impedance and fast response time. The SMB series is supplied in ON Semiconductor’s exclusive, cost-effective, highly reliable Surmetict package and is ideally suited for use in communication systems, automotive, numerical controls, process controls, medical equipment, business machines, power supplies and many other industrial/consumer applications.

P6KE39A,TVS瞬变抑制二极管中文资料

P6KE39APOWER: 600Wa t VOLTAGE RANGE: 6.8 - 440VP6KE6.8A(CA)-P6KE440A(CA)Classification Rating 94V-OFeaturesGlass Passivated Die ConstructionUni- and Bi-Directional Versions Available Excellent Clamping Capability Fast Response TimePlastic Case Material has UL Flammability Mechanical DataCase: JEDEC DO-15 Low Profile Molded Plastic Terminals: Axial Leads, Solderable per MIL-STD-202, Method 208Polarity: Cathode Band or Cathode Notch Weight: 0.40 grams (approx.)Maximum Ratings and Electrical Characteristics@T A =25°C unless otherwise specifiedCharacteristicSymbol ValueUnit Peak Pulse Power Dissipation at T A = 25°C (Note 1, 2, 5) Figure 3P PPM 600 MinimumW Peak Forward Surge Current (Note 3)I FSM 100A Peak Pulse Current on 10/1000µS Waveform (Note 1) Figure 1I PPM See Table 1A Steady State Power Dissipation (Note 2, 4)P M(AV) 5.0W Operating and Storage Temperature RangeT j , T STG-65 to +175°CNote: 1. Non-repetitive current pulse, per Figure 1 and derated above T A = 25°C per Figure 4.2. Mounted on 40mm 2 copper pad.3. 8.3ms single half sine-wave duty cycle = 4 pulses per minutes maximum.4. Lead temperature at 75°C = T L .5. Peak pulse power waveform is 10/1000µS.AXIAL LEADED TRANSIENT VOLTAGE SUPPERSSOR DIODE!!!!!!!!P6KE440CA10.5 14.513.412.186.577.971.364.658.953.248.544.740.934.231.428.525.722.820.919.017.115.214.312.49.508.657.797.136.45(uA)R RMW RMW@V leakage Reverse CurrentPulse Peak (A)Vc(V)(mA)BR MAX CurrentMax.BR MIN @I Min.Volgtage Breakdown (V)(BI)(Uni)Voltage Stand-Off Reverse Maximum Clamping V T PP(V)V @I Volgtage Breakdown Test (V)V T Volgtage @I PP P6KE6.8A P6KE6.8CA 5.80 7.14 10.0 57.1 1000.0P6KE7.5A P6KE7.5CA 6.40 7.88 10.0 11.3 53.1 500.0 P6KE8.2A P6KE8.2CA 7.028.61 10.0 49.6 200.0 P6KE9.1A P6KE9.1CA 7.78 9.55 1.0 44.8 50.0 P6KE10A P6KE10CA 8.55 10.5 1.0 41.4 10.0P6KE11A P6KE11CA 9.40 10.5 11.6 1.0 15.6 38.5 5.0 P6KE12A P6KE12CA10.2 11.412.6 1.0 16.7 35.9 5.0P6KE13A P6KE13CA11.1 13.7 1.0 18.2 33.0 5.0 P6KE15A P6KE15CA 12.8 15.8 1.0 21.2 28.3 5.0 P6KE16A P6KE16CA 13.6 16.8 1.0 22.5 26.7 5.0P6KE18A P6KE18CA 15.3 18.9 1.0 25.2 23.8 5.0 P6KE20A P6KE20CA 17.1 21.0 1.0 27.7 21.7 5.0 P6KE22A P6KE22CA 18.8 23.1 1.0 30.6 19.6 5.0 P6KE24A P6KE24CA 20.5 25.2 1.0 33.2 18.1 5.0 P6KE27A P6KE27CA 23.1 28.4 1.0 37.5 16.0 5.0 P6KE30A P6KE30CA 25.6 31.5 1.0 41.4 14.5 5.0 P6KE33A P6KE33CA 28.2 34.7 1.0 45.7 13.1 5.0P6KE36A P6KE36CA 30.8 37.8 1.0 49.9 12.0 5.0P6KE39A P6KE39CA 33.3 37.1 41.0 1.0 53.9 11.1 5.0 P6KE43A P6KE43CA 36.8 45.2 1.0 59.3 10.1 5.0 P6KE47A P6KE47CA 40.2 49.4 1.0 64.8 9.3 5.0 P6KE51A P6KE51CA 43.6 53.6 1.0 70.1 8.6 5.0P6KE56A P6KE56CA 47.8 58.8 1.077.0 7.8 5.0P6KE62A P6KE62CA 53.0 65.1 1.0 85.07.1 5.0 P6KE68A P6KE68CA 58.1 71.4 1.0 92.06.5 5.0 P6KE75A P6KE75CA 64.1 78.81.0 103 5.8 5.0P6KE82A P6KE82CA70.1 86.1 1.0 1135.3 5.0P6KE91A P6KE91CA 77.8 95.5 1.0 1254.85.0 P6KE100A P6KE100CA 85.5 95.0 105 1.0 137 4.4 5.0 P6KE110AP6KE110CA 94.0 105 116 1.0 1523.9 5.0 P6KE120AP6KE120CA102 114 126 1.0 165 3.6 5.0 P6KE130A P6KE130CA 111 124 137 1.0 179 3.4 5.0 P6KE150A P6KE150CA 128 143 158 1.0 207 2.9 5.0 P6KE160A P6KE160CA 136 152168 1.0 219 2.7 5.0 P6KE170A P6KE170CA 145 162 179 1.0 234 2.6 5.0 P6KE180A P6KE180CA 154 171 189 1.0 246 2.4 5.0 P6KE200A P6KE200CA 171 190 210 1.0 274 2.2 5.0 P6KE220A P6KE220CA 185 209 231 1.0 328 1.8 5.0 P6KE250A P6KE250CA 214 237 263 1.0 344 1.7 5.0 P6KE300A P6KE300CA 256 285 315 1.0 414 1.4 5.0 350 310 380 P6KE350A P6KE350CA 1.0 482 1.2 5.0 P6KE400A P6KE400CA 342 380 420 1.0 548 1.1 5.0 P6KE440A 3764184621.06021.05.0TYPERating at = 25 °C ambient temperature unless otherwise specified255075100125150175200100755025T ,AMBIENT TEMPERATURE (°C)Fig.4Pulse Derating CurveA P K P U L S E D E R A T I N G (%P K P W R O R C U R R E N T )25507510012515017520002.55.0T ,LEAD TEMPERATURE (°C)Fig.5,Steady State Power DeratingLP ,S T E A D Y S T A T E P O W E R D I S S I P A T I O N (W )d 0.11.0T ,PULSE WIDTH (µs)Fig.3Pulse Rating Curvep 0.1101001.010100100010000P ,P E A K P U L S E P O W E R (k W )P0123I ,P E A K P U L S E C U R R E N T (%)P p pt,TIME (ms)Fig.1Pulse Waveform110100100010100100010,000V ,REVERSE STANDOFF VOLTAGE (V)Fig.2Typical Junction CapacitanceRWM C ,C A P A C I T A N C E (p F )j。

低功耗瞬态二极管P6SMB39CA型号

低功耗瞬态二极管P6SMB39CA型号硕凯电子(Sylvia)一、最大额定值Notes:1.Non-repetitive current pulse,per Fig.3and derated above TA=25°C per Fig.2.2.Mounted on5.0mm x5.0mm(0.03mm thick)Copper Pads to each terminal.3.8.3ms single half sine-wave,or equivalent square wave,Duty cycle=4pulses per minutes maximum.4.VF<3.5V for VBR<200V and VF<6.5V for VBR>201V.二、瞬态二极管产品特性1、为表面安装应用优化电路板空间2、低泄漏3、单向和双向单元4、玻璃钝化结5、低电感6、优良的钳位能力7、600W的峰值功率能力在10×1000μ波形重复率(占空比):0.01%8、快速响应时间:从0伏特到最小击穿电压通常小于1.0ps9、典型的,在电压高于12V时,反向漏电流小于5μA10、高温焊接:终端260°C/40秒11、典型的最大温度系数△Vbr=0.1%x Vbr@25°C x△T12、塑料包装有保险商实验室可燃性94V-013、无铅镀雾锡14、无卤化,符合RoHS15、典型失效模式是在指定的电压或电流下出现16、晶须测试是基于JEDEC JESD201A每个表4a及4c进行的17、IEC-61000-4-2ESD15kV(空气),8kV(接触)18、数据线的ESD保护符合IEC61000-4-2(IEC801-2)19、数据线的EFT保护符合IEC61000-4-4(IEC801-4)三、脉冲降额曲线四、UL认证编号五、脉冲浪涌五、产品应用说明TVS器件非常适合保护I/O接口,Vcc总线和其他应用于电信、计算机、工业和消费电子应用的易损电路。

CS5460A中文数据手册

单相双向功率/电能 IC

特性

l l l l l l l l l l l l l l l 电能数据线性度:在1000 :1 动态范围内线性度 为 ±0.1% 片内功能:可以测量电能(有功),I *V,IRMS 和 VRMS ,具有电能-脉冲转换功能 可以从串行EEPROM 智能“自引导”,不需要微 控制器 AC 或DC 系统校准 具有机械计度器/步进电机驱动器 符合IEC687/1036 ,JIS 工业标准 功耗<12mW 优化的分流器接口 V对I的相位补偿 单电源地参考信号 片内2.5V 参考电压(最大温漂60ppm/℃) 简单的三线数字串行接口 看门狗定时器 内带电源监视器 电源配置 VA+ = +5 V; VA- = 0V; VD+ = +3.3V~+5 V

概述

CS5460A 是一个包含两个ΔΣ模 - 数转换 器(ADC)、高速电能计算功能和一个串行接 口的高度集成的ΔΣ 模-数转换器。 它可以精确 测量和计算有功电能、 瞬时功率、 IRMS 和VRMS , 用于研制开发单相2 线或3 线电表。CS5460A 可以使用低成本的分流器或互感器测量电流, 使 用分压电阻或电压互感器测量电压。CS5460A 具有与微控制器通讯的双向串口, 芯片的脉冲输 出频率与有功能量成正比。CS5460A 具有方便 的片上AC/DC 系统校准功能。 “自引导”的特点使 CS5460A 能独自工 作, 在系统上电后自动初始化。 在自引导模式中, CS5460A 从一个外部EEPROM 中读取校准数 据和启动指令。使用该模式时,CS5460A 工作 时不需要外加微控制器, 因此当电表用于大批量 住宅电能测量时,可降低电表的成本。 订货信息: CS5460A-BS -40℃~+85℃ 24 引脚 SSOP

Furman PST-6 电源保护设备说明书