EM6352YSC4B1.6中文资料

EM9636BBD产品说明书

EM9636B/BD产品说明书图1声明:此说明书归北京中泰研创科技有限公司所有。

未经本公司授权,任何公司及个人不得以盈利目的进行复制、抄袭、翻译或传播。

订购产品前,请详细了解产品性能是否符合用户需求。

说明书描述了产品的基本功能,若客户有特殊要求需要增加其他功能,请与本公司工程师联系。

说明书的内容力求准确、可靠。

本公司对侵权使用说明书所造成的后果不承担任何法律责任。

安全使用常识:•使用前请务必仔细阅读产品说明书。

•禁止带电插拔,以免瞬间冲击电压过大烧毁敏感元器件。

•避免频繁开机,以免对产品造成损坏。

目录第一章产品介绍 (3)1.1 概述 (3)1.2 特点 (3)1.3 一般特性 (5)第二章安装说明 (6)2.1 初始检查 (6)2.2 跳线分布图 (6)2.3 跳线设置 (6)2.3.1 模拟输入量程跳线说明 (7)2.3.2 模拟输入单端/差分方式跳线说明 (7)2.3.3 模拟输入电压/电流方式跳线说明 (7)2.3.4 模拟输出跳线说明 (8)2.3.5 模拟输出上电状态跳线说明 (8)2.3.6 加载默认网络设置跳线说明 (8)2.3.7 写保护跳线说明 (9)2.4 设备的安装 (9)2.4.1 使用网络接口时硬件安装 (9)2.4.2 使用网络接口时软件安装 (9)2.4.3 使用USB接口时硬件安装 (10)2.4.4 使用USB接口时软件安装 (10)2.4.5 设置更改模块参数设置 (10)第三章连接与测试 (13)3.1 管脚分布图 (13)3.1.1管脚功能定义说明 (13)3.2 模拟输入连接 (14)3.2.1 模拟信号种类 (14)3.2.2 单端模拟输入连接 (15)3.2.3 差分模拟输入连接 (15)3.3 模拟输出连接 (17)3.3.1 电压模拟输出连接 (17)3.3.2 电流模拟输出连接 (17)3.4 计数器输入连接 (18)3.5 数字量输入连接及注意事项 (18)3.6 数字量输出的连接 (19)3.7 编码器输入的连接 (20)3.8 PWM输出的连接 (21)3.9 SD卡的连接 (21)3.10 外触发与外时钟的连接 (21)3.11 测试 (21)3.8.1 模拟输入功能测试 (23)3.8.2 模拟输出功能测试 (24)3.8.3 计数器功能测试 (25)3.8.4 频率输入功能测试 (26)3.8.5 数字量输入功能测试 (27)3.8.6 数字量输出功能测试 (29)第四章原理说明 (31)4.1数据采集触发方式详解 (31)4.1.1采样时钟 (32)4.1.2采样方式 (32)4.1.3 触发信号 (32)4.1.4 边沿触发 (32)4.1.5 电平触发 (33)4.2 指示灯功能详解 (35)4.2.1 红灯,电源指示灯 (35)4.2.2 绿灯,采集指示灯 (35)4.2.3 黄灯,离线采集指示灯 (35)4.3 PWM脉冲生成 (36)第五章结构说明 (36)5.1结构图(尺寸图) (36)附录:....................................................................................................................................................... 错误!未定义书签。

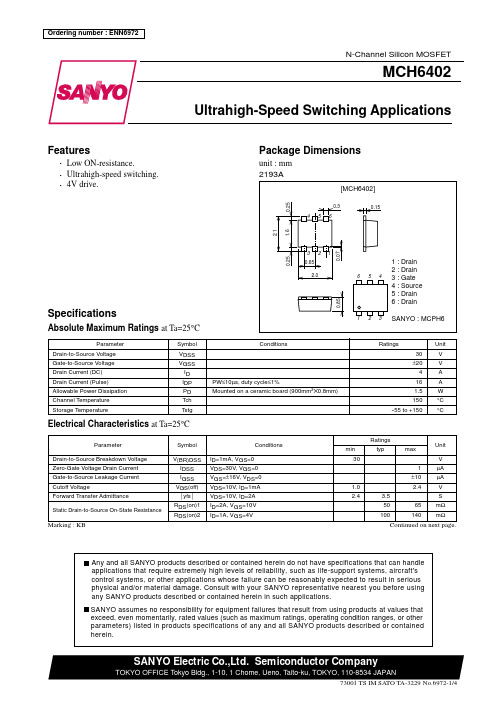

MCH6402资料

4V

2.5

Drain Current, ID -- A

8V

Drain Current, ID -- A

10V

2.0

VGS=3V

1.5

1.0

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1.0 0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0

Drain-to-Source Voltage, VDS -- V

Parameter Drain-to-Source Voltage Gate-to-Source Voltage Drain Current (DC) Drain Current (Pulse) Allowable Power Dissipation Channel Temperature Storage Temperature Symbol VDSS VGSS ID IDP PD Tch Tstg PW≤10µs, duty cycle≤1% Mounted on a ceramic board (900mm2!0.8mm) Conditions

Marking : KB

Continued on next page.

Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications. SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

EMVY6R3ADA470ME55G中文资料(Nippon Chemi-Con)中文数据手册「EasyDatasheet - 矽搜」

请参考“产品代码指南(表面贴装型)”

◆标记

D55 to JA0 EX) 6.3V100µF

7hY

100 6.3V

KE0 to MN0

EX) 16V1,000µF

0V MVY

1000 16V

(1/2)

芯片中文手册,看全文,戳

表面安装铝电解电容器

1.8

95 EMVY6R3ADA330ME55G

47 E55

1.8

95 EMVY6R3ADA470ME55G

100 F55

1.0

140 EMVY6R3ADA101MF55G

220 F55

1.0

140 EMVY6R3ADA221MF55G

330 F80

0.34

280 EMVY6R3ADA331MF80G

≦The initial specified value

≦The initial specified value

Shelf Life

The following specificationsshall be satisfied when the capacitorsare restored to 20℃ after exposing them for 1,000 hoursat 105℃ without

Lower Z MVE

◆技术指标

Items

特点

Category Temperature Range

-55 to +105℃ (6.3 to 63V dc ) -40 to +105℃ (80 & 100V dc )

Rated Voltage Range 6.3 to 100V dc

启扬科技 QY-6351S 英特尔

QY-6351SIntel®Celeron® ULV Processor CPU Board with LAN & VGA & AUDIO中文使用手册杭州启扬智能科技有限公司杭州山水人家诗家谷5幢1单元1楼电话:*************传真:*************网址: 前言感谢您购买杭州启扬智能科技有限公司QY-6351S主板,该主板内置有一个Intel ULV EBGA series CPU ,采用VIA CLE266+VT8235 芯片组设计。

板载128MB 内存, 提供一个DDR SO-DIMM 插槽,支持DDR266/200 (PC2100/1600) 内存,最大容量达384MB 。

采用AC97 音频芯片,支持AC97 音频解码和兼容AC97 2.1, 提供1 个板载10BaseT/100Base TX 网卡,支持扩展的USB2.0(Universal Serial Bus Specification Revision 2.0),USB2.0 提供比USB1.1 更高的带宽。

该主板集成了一整套的I/O 端口,包括一个MINI IDE 接口,一个CF 插槽, 一个PC104 接口,键盘和鼠标输入端口,四个串行端口,一个并行端口,一个TTL/LCD 端口、一个Digital IO 端口、一个FIR 红外端口和两个USB 端口。

该主板采用AT 结构, 规格为115mm x 165mm,8 层印刷电路板。

目录序章版权宣告、配件清单与注意事项 (1)0.1 版权宣告 (1)0.2 配件清单................................................................ .. (1)0.3 安装前注意事项....................................................... .. (1)第一章规格简介 (3)1.1 规格简介 (3)第二章安装与设置指南 (5)2.1 主板位图和背板I/O 图.............................................. . (5)2.2 跳线说明............................................................... .. (6)2.2.1 如何辨认跳线的1 脚位置 (6)2.2.2 JP1: 清除CMOS 跳线 (6)2.2.3 F_PANEL/J19 面板插针.......................................... .. (6)2.3 接口说明 (7)2.3.1 AT ---电源接口.................................................. . (7)2.3.2 FAN1 ---CPU 风扇接口 (7)2.3.3 J18 ---KB/MS 扩展接口................................... ...... (8)2.3.4 IR1 ---红外接口................................................. . (8)2.3.5 DIO --- Digital IO 接口........................................ (8)2.3.6 CN3 ---LCD 背光接口............................................. (9)2.3.7 CN2 --- TTL/LCD 接口 (9)2.3.8 COM1/COM3 ---COM 接口........................ (10)2.3.9 JP3/JP4/JP5 --- COM2 RS232/RS422/RS485 跳线......... .. (10)2.3.10 CN6 ---并行接口............................................... . (11)2.3.11 JP7 ---音频接口 (11)2.3.12 CD_IN --- CD-IN 接口 (12)2.4 外部设备的安装 (12)第三章驱动程序安装........................................... (13)3.1 前言 (13)3.2 驱动程序目录一览表 (13)3.3 驱动程序安装 (13)3.3.1 VIA 4IN1 驱动的安装 (13)3.3.2 显卡驱动的安装.................................................. . (18)3.3.3 VIA USB2.0 驱动的安装........................................ . (18)3.3.4 声卡驱动的安装 (19)3.3.5 REALTEK 8100BL 网卡驱动安装 (19)3.4 其它软件安装........................................................ .. (19)序章版权宣告、配件清单与注意事项0.1 版权宣告本手册受到国际著作法以及相关法律的保护,本公司将保留所有的权利,未经本公司书面同意,不得擅自重制、改编、传送本手册的内容与相关数据,否则将进行民事或刑事诉讼。

EM6322FP8CT-85S中文资料(Emerging Memory)中文数据手册「EasyDatasheet - 矽搜」

推荐直流工作条件

1)

参数 电源电压 地面 输入高电压

输入低电压

符号

VCC VSS VIH VIL

Min 2.7 0 2.2 -0.2 3)

Typ

Max

Unit

3.3

3.6

V

0

0

V

-

VCC + 0.2 2)

V

-

0.6

V

1. TA = -40到85 oC,另有说明

2. 过冲:V

符号

VIN , V OUT VCC PD TA

* 强调超过"绝对最大额定值"可能会造成永久性损坏设备.功能 操作应仅限于推荐工作条件.暴露在绝对最大额定值条件下长时间可能会影响其可靠性.

EM641FV8FS系列

低功耗,512Kx8 SRAM

额定值

-0.2 to Vcc+0.3(Max.4.0V) -0.2 to 4.0V 1.0 -40到85

芯片中文手册,看全文,戳

合并存储器与逻辑解决方案公司

文档标题

512K×8位 超 低 功 耗 和 低 电 压 全 CMOS静 态 RAM

修订记录 版本号 0.0 0.1

历史

初稿草案

第2'草案

加入无铅部件号

EM641FV8FS系列 低功耗,512Kx8 SRAM

草案日期 5月25日,2003 2004年2月13日,

Unit

V V W oC

功能说明

CS

OE

WE

H

X

X

L

H

H

L

L

H

L

X

L

注:X表示不关心. (必须是高或低状态)

WEBs 应用手册说明书

WEBs 应用手册关于霍尼韦尔霍尼韦尔是一家《财富》全球500 强的高科技企业。

我们的高科技解决方案涵盖航空、汽车、楼宇、住宅和工业控制技术,特性材料,以及物联网。

我们致力于将物理世界和数字世界深度融合,利用先进的云计算、数据分析和工业物联网技术解决最为棘手的经济和社会挑战。

在中国,霍尼韦尔长期以创新来推动增长,贯彻“东方服务于东方”和“东方服务于全球”的战略。

霍尼韦尔始创于1885 年,在华历史可以追溯到1935 年,在上海开设了第一个经销机构。

目前,霍尼韦尔四大业务集团均已落户中国,上海是霍尼韦尔亚太区总部,在华员工人数约11,000 人。

同时,霍尼韦尔在中国的30 多个城市拥有50 多家独资公司和合资企业,其中包括20 多家工厂,旨在共同打造万物互联、更智能、更安全和更可持续发展的世界。

欲了解更多公司信息,请访问霍尼韦尔中国网站www. ,或关注霍尼韦尔官方微博和官方微信。

霍尼韦尔霍尼韦尔智能建筑科技集团我们在全球拥有23,000 多名员工。

我们的产品、软件和技术已在全球超过1,000 万栋建筑中使用。

我们的技术确保商业楼宇业主和用户的设施安全、节能、具有可持续性与高生产力。

霍尼韦尔智能建筑科技集团深耕中国40 多年来,参与了30 多个城市的150 多条地铁的建设,为500 多座机场的智慧和安全保驾护航,为600 多家酒店提供智能管理系统,为1000多家医院提供了数字化解决方案。

目录第一部分 (4)霍尼韦尔智慧楼宇系统架构示意图 (4)霍尼韦尔智慧能源管理解决方案 (6)WEBs N4管理软件 (9)霍尼韦尔智慧触控屏 (13)第二部分 (17)系统控制器 WEB 8000 系列 (17)系统控制器 WEB 8000 VAV 专用系列 (21)边缘数据管理器 (24)增强型可编程通用控制器 (27)可编程通用控制器 (30)可编程通用控制器扩展模块 (33)BACnet 可编程通用 / VAV 控制器 (36)Lonworks 可编程通用 / VAV 控制器 (39)VAV 控制器 (43)BACnet 通用控制器 (46)Sylk TM I/O 扩展模块 (49)MVCweb 控制器 (52)UB系列独立控制器 (55)第三部分 (59)房间温控单元 (59)变风量末端墙装模块 (63)WTS3/6 系列温控器 (65)WTS8/9 系列温控器 (69)WS9 系列墙装模块 (73)建筑网络适配器 (76)智能电表 (78)4Ethernet / LANBACnet MS/TP Modbus RTU LonworksKNXSylk BusLightingModbus TCP BACnet IPBACnet IPAlarm Console clientWEB 8000 Web ControllerWEBStation Supervisor智慧触控屏Sylk I/O ModuleLonworks Spyder边缘数据管理器Spyder Universal ControllerPUC BACnet MS/TP Controller霍尼韦尔智慧楼宇系统架构示意图系统示意图仅用于显示设备在系统中的层次关系以及支持的通讯协议具体配置细节请结合实际项目情况,联系霍尼韦尔技术工程师进行架构设计5ElectricitySubmeterBACnet IPBACnet IPHTTPs , BACnet IP , oBIX , SNMP , …WEBs Enterprise Security WEBs Energy AnalyticsHAQ61增强型 BACnet IP ControllerFCU Wall ModuleVAV Controller EM Bus I/O ModuleSylk Bus Wall Module增强型 BACnet IP ControllerEM Bus6霍尼韦尔智慧能源管理解决方案智能高效,机器自学习功能准确分析,快速发现能耗异常功能全面,基于能耗大数据采集、趋势分析、评估诊断和流程控制的闭环管理功能数据准确,具有180多年计量仪表生产、安装与服务的专业知识灵活易用,云平台或本地部署灵活配置和迁移,操作简便扩展性好通过能源可见性、积极应对能耗异常和提高管理人员参与度,用户可以:★ 避免能耗异常波动★ 确保节能投资的投资回报率(ROI)符合预期★ 提高管理效率和降低运营成本研究显示,更多的企业为合规地实现节省成本、提高效率,越来越关注能源管理系统。

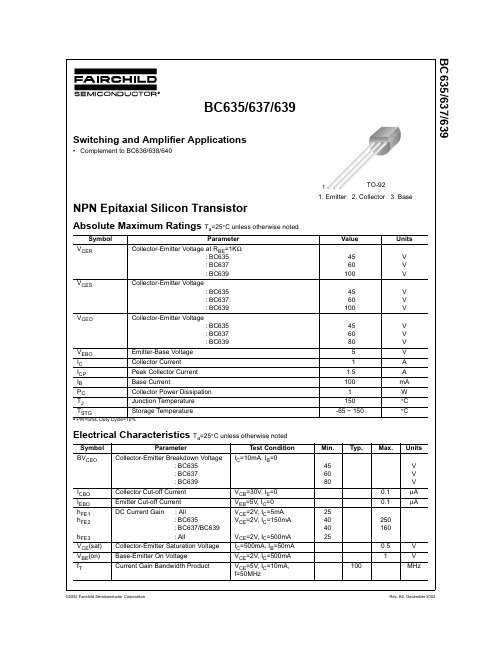

BC635中文资料

BC635/637/639NPN Epitaxial Silicon TransistorAbsolute Maximum Ratings T a =25°C unless otherwise noted• PW=5ms, Duty Cycle=10%Electrical Characteristics T a =25°C unless otherwise notedSymbol ParameterValue Units V CERCollector-Emitter Voltage at R BE =1K Ω: BC635 : BC637: BC639 45 60100V V V V CESCollector-Emitter Voltage: BC635: BC637: BC639 45 60100V V V V CEOCollector-Emitter Voltage: BC635: BC637: BC639 45 60 80V V V V EBO Emitter-Base Voltage 5V I C Collector Current 1A I CP Peak Collector Current 1.5A I B Base Current100mA P C Collector Power Dissipation 1W T J Junction Temperature 150°C T STGStorage Temperature-65 ~ 150°CSymbol ParameterTest Condition Min.Typ.Max.Units BV CEOCollector-Emitter Breakdown Voltage: BC635: BC637: BC639I C =10mA, I B =0456080V V V I CBO Collector Cut-off Current V CB =30V, I E =00.1µA I EBO Emitter Cut-off CurrentV EB =5V, I C =00.1µAh FE1h FE2h FE3DC Current Gain : All: BC635: BC637/BC639: All V CE =2V, I C =5mA V CE =2V, I C =150mA V CE =2V, I C =500mA 25404025250160V CE (sat)Collector-Emitter Saturation Voltage I C =500mA, I B =50mA 0.5V V BE (on)Base-Emitter On Voltage V CE =2V, I C =500mA 1V f TCurrent Gain Bandwidth ProductV CE =5V, I C =10mA, f=50MHz100MHzBC635/637/639Switching and Amplifier Applications•Complement to BC636/638/6401. Emitter2. Collector3. BaseTO-921BC635/637/639BC635/637/639TRADEMARKSThe following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.DISCLAIMERFAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN;NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.As used herein:1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body,or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.PRODUCT STATUS DEFINITIONS Definition of TermsDatasheet Identification Product Status DefinitionAdvance InformationFormative or In Design This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.PreliminaryFirst ProductionThis datasheet contains preliminary data, andsupplementary data will be published at a later date.Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design.No Identification Needed Full ProductionThis datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design.Obsolete Not In ProductionThis datasheet contains specifications on a product that has been discontinued by Fairchild semiconductor.The datasheet is printed for reference information only.FACT™FACT Quiet series™FAST ®FASTr™FRFET™GlobalOptoisolator™GTO™HiSeC™I 2C™ImpliedDisconnect™ISOPLANAR™LittleFET™MicroFET™MicroPak™MICROWIRE™MSX™MSXPro™OCX™OCXPro™OPTOLOGIC ®OPTOPLANAR™PACMAN™POP™Power247™PowerTrench ®QFET™QS™QT Optoelectronics™Quiet Series™RapidConfigure™RapidConnect™SILENT SWITCHER ®SMART START™SPM™Stealth™SuperSOT™-3SuperSOT™-6SuperSOT™-8SyncFET™TinyLogic™TruTranslation™UHC™UltraFET ®VCX™ACEx™ActiveArray™Bottomless™CoolFET™CROSSVOLT ™DOME™EcoSPARK™E 2CMOS™EnSigna™Across the board. Around the world.™The Power Franchise™Programmable Active Droop™。

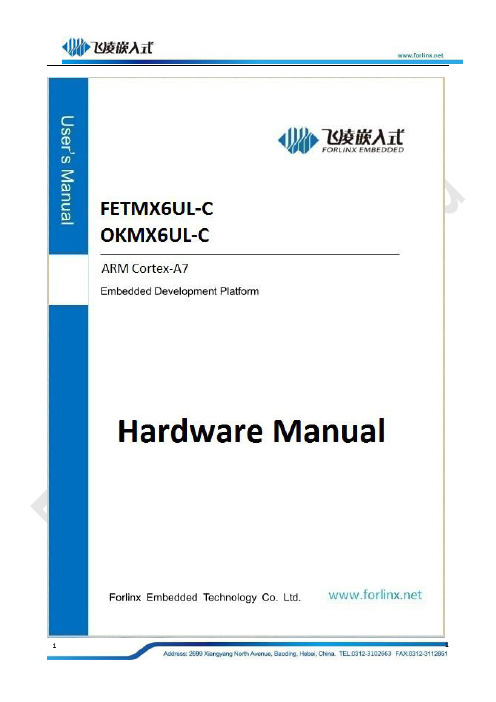

i.MX6UL产品说明书

Product Features1.NXP i.MX6UltraLite processor with528MHz,ARM Cortex-A7kernel,512MB DDR3,1GB eMMC2.Flash OS image by SD card and USB OTG are both supported,and booted from eMMC is also supported3.Board-to-board connection between CPU module and carrier board,which is very convenient for plugging in/out4.Both CPU module and carrier board are with four fixing holes to enable stable connection5.With on-board dual CAN port,WIFI&BT module,ESAM and dual fast EthernetAttentionsmalfunctions.Please do not modify the product by yourself or use fittings unauthorized by us.Otherwise, the damage caused by that will be on your part and not included in guarantee terms.Any questions please feel free to contact Forlinx Technical Service Department..Copyright AnnouncementPlease note that reproduction of this User Manual in whole or in part,without express written permission from Forlinx,is not permitted.Updating RecordTechnical Support and Innovation1.Technical Support1.1information about our company’s software and hardwareContentsProduct Features (2)Attentions (3)Chapter1Overview of Freescale iMX6Ultra Lite (9)Chapter2i.MX6UL CPU Module Introduction (12)2.1CPU Module Overview (12)2.2FETMX6UL CPU Module Dimension (13)2.2CPU Module Features (13)2.3Power Supply Mode (14)2.4Working Environment (14)2.5CPU Module Interface (14)2.6CPU Module Pin Definition (15)2.6.1CPU module schematic (15)2.6.2CPU Module FETMX6UL-C Pin Definition (16)2.7CPU Module Design (21)Chapter3i.MX6UR Development Platform Overview (23)3.1Overview of single board computer i.MX6UR (23)3.2Carrier Board Dimension (24)3.3Base board resource: (24)3.4i.MX6UR Base Board Introduction (25)3.4.1Base Board Power (25)3.4.2Power Switch (25)3.4.3Reset Key (25)3.4.4Boot Configuration (26)3.4.5Serial Port(Debug Port) (27)3.4.6General Serial Port (28)3.4.7CAN (28)3.4.8SD Card Slot (28)3.4.9SDIO Port (29)3.4.10RTC Battery (29)3.4.11WIFI/Bluetooth (30)3.4.12Digital Camera Interface (30)3.4.13ESAM Interface (31)3.4.14RED (31)3.4.15Audio (31)3.4.16Dual Hundred Ethernet Ports (33)3.4.17USB Host (33)3.4.18JTAG Debug Port (34)3.4.19RCD Connector (35)3.4.20USB OTG (36)3.4.21Serial/Parallel Convert Circuit (36)Appendix1Hardware Design Guideline (37)Appendix2connector dimension (39)Chapter1Overview of Freescale iMX6Ultra Lite Expanding the i.MX6series,the i.MX6UltraLite is a high performance,ultra-efficient processor family featuring an advanced implementation of a single ARM®Cortex®-A7core,which operates at speeds up to528MHz.The i.MX6UltraLite applications processor includes an integrated power management module that reduces the complexity of external power supply and simplifies power sequencing.Each processor in this family provides various memory interfaces,including16-bit LPDDR2,DDR3,DDR3L, raw and managed NAND flash,NOR flash,eMMC,Quad SPI and a wide range of other interfaces for connecting peripherals such as WLAN,Bluetooth™,GPS,displays and camera sensors.Freescale i.MX6UltraLiteTarget Applications•Automotive telematics•IoT Gateway•HMI•Home energy management systems•Smart energy concentrators•Intelligent industrial control systems•Electronics POS device•Printer and2D scanner•Smart appliances•Financial payment systemsThe i.MX6UltraLite applications processor includes an integrated power management module that reduces the complexity of external power supply and simplifies power sequencing.Each processor in this family provides various memory interfaces,including16-bit LPDDR2,DDR3,DDR3L,raw and managed NAND flash,NOR flash,eMMC,Quad SPI and a wide range of other interfaces for connecting peripherals such as WLAN,Bluetooth®,GPS,displays and camera sensors.The i.MX6UltraLite is supported by discrete component power circuitry.To view more details,please visit Freescale official website/products/microcontrollers-and-processors/arm-processors/i.mx-applications-proces sors-based-on-arm-cores/i.mx-6-processors/i.mx6qp/i.mx-6ultralite-processor-low-power-secure-arm-co rtex-a7-core:i.MX6UL?uc=true&lang_cd=enChapter2i.MX6UL CPU Module Introduction 2.1CPU Module OverviewNAND Flash versionEMMC Version2.2FETMX6UL CPU Module DimensionDimension:40mm x50mm,tolerance±0.15mmCraftwork:thickness:1.15mm,6-layer PCBConnectors:2x0.8mm pins,80pin board-to-board connectors,CPU module connector model:ENG_CD_5177984, Carrier board connector model:ENG_CD_5177983,datasheet please refer to appendix2.2CPU Module FeaturesUnitUART Each up to5.0MbpseCSPI Full duplex enhanced sync.Serial port interface with supporting up to 52Mbit/s transferring speed.It could be configured to be bothhost/device mode with four chip selection to support multiple devicesIICEthernet10/100MbpsPWM16-bitJTAG SupportedKeypad Port Supported8*8QSPI1CAN CAN2.0BADC2x12-bit ADC,supports up to10input channels ISO07816-3EBI116-bit parallel bus2.6CPU Module Pin Definition2.6.1CPU module schematic2.6.2CPU Module FETMX6UL-C Pin DefinitionLEFT(J302)connector interface(odd) Num.Ball Signal GPIO Vol Spec.FunctionL_1G13UART5_RXD gpio1.IO[31] 3.3V UART5receiving IIC2_SDAL_3F17UART5_TXD gpio1.IO[30] 3.3V UART5sending IIC2_SCLL_5G16UART4_RXD gpio1.IO[29] 3.3V UART4receiving IIC1_SDAL_7G17UART4_TXD gpio1.IO[28] 3.3V UART4sending IIC1_SCLL_9H15UART3_CTS gpio1.IO[26] 3.3V UART3clear to send CAN1_TXL_11G14UART3_RTS gpio1.IO[27] 3.3V UART3request to send CAN1_RXL_13H16UART3_RXD gpio1.IO[25] 3.3V UART3receiving UART3_RXDL_15H17UART3_TXD gpio1.IO[24] 3.3V UART3sending UART3_TXDL_17-GND GNDL_19J15UART2_CTS gpio1.IO[22] 3.3V UART2clear sending CAN2_TXL_21H14UART2_RTS gpio1.IO[23] 3.3V UART2request to send CAN2_RXL_23J16UART2_RXD gpio1.IO[21] 3.3V UART2receiving UART2_RXDL_25J17UART2_TXD gpio1.IO[20] 3.3V UART2sending UART2_TXDL_27K15UART1_CTS gpio1.IO[18] 3.3V UART1(debug port)clearUART1_CTSsendingL_29J14UART1_RTS gpio1.IO[19] 3.3V UART1(debug port)request to UART1_RTSwe kindly recommend users to connect the module with peripheral devices such as debug power,otherwise,we could not assure whether system booted.Chapter3i.MX6UR Development Platform Overview3.1Overview of single board computer i.MX6UR3.2Carrier Board Dimension3.4.3Reset KeySW2on right bottom corner of base board is the reset key.3.4.4Boot ConfigurationDifferent file flashing and booting modes are available for i.MX6UR,.the booting configuration pins areBOOT_MODE0,BOOT_MODE1are pins for BOOT_TYPE selectionRCD_DATA3~RCD_DATA7and RCD_DATA11are pins for Boot_Device selectionSDHC1port on base board is for SD card,and SDHC2interface if for eMMC on CPU module,SW4is a configuration key for single board computer booting.Below modes are available1.Flash OS image via SD card:On(up)1,4Off(down)2,3,5,6,7,82.Flash OS image via USB OTG:key1off,others are all to off,3.Boot from eMMC:On:1,4,5,8Off:2,3,6,73.Boot from NAND Flash:on:1,3Off:2,4,5,6,7,83.4.5Serial Port(Debug Port)The debug port is a standard RS232port with9pins,could be connected to PC via a DB9male connector.If without serial port on PC,it could be connected via USB-to-RS232cable.The UART1is a debug port with5-wire and3.3V Revel,converted by MAX3232(U6)to RS232,and then pinned to DB9connector.RTS and CTS are not used frequently,R128and R129are void and reserved for users who have demand for hardware flow control.Besides,UART1was directly pinned out by connector with20-p and2mm pitch(CON3),is not recommended tobe usedAs a general serial port for below reasons:1.R87have to be removed to avoid effect of U62.Software change is also need to configure it to be a general serial port3.4.6General Serial PortBoth UART2and UART3are5-wired serial port with3.3V Revel,and are pinned out by CON4and CON5.They could be used matched with Forlinx module,to convert3.3V Revel to RS232and RS485.3.4.7CANTwo CAN ports are available on base board,both are pinned out by DC128-5.0green terminal and numbered asCON7and CON8.Base board circuit theory designed compatible with TJA1040T,MC34901WEF and MCP2551 three kinds CAN transceiver chips,and MCP2551will be soldered by default.As the MCP2551output RX is5V,it my effect the CPU module3.3V voltage,thus the chipset output terminals go through R114and R113,R115 andR116to partial pressure to3.3V,then input to CAN1_RX and CAN2_RX of the CPU.3.4.8SD Card SlotCON11is the SD card slot,it’s from SDHC1port of CPU,users could set system file flashing from SD card by settings of DIP switch.This port is available for SD card,SDHC card and SDXC(UHS-A)card.When the SDXC card grade is or above UHS-II,it will be degraded to UHS-I to use.Because new data pins(compared with USB3.0)are added begin from UHS-II.3.4.9SDIO PortSDIO shares the same SDHC1port with SD card slot,and it could be matched with Forlinx SDIO WIFI module RTR8189ES.This port was pinned out by a20-pin2mm pitch(CON29)connector3.4.10RTC BatteryThe CPU is with RTC and it also supports external RTC.We selected to use external RTC considering CPU RTC power consumption.The battery model is CR12203.4.11WIFI/BluetoothThe WIFI&BT coexistence model is RR-UM02WBS-8723BU-V1.2,IEEE802.11b/g/n1T1R WRAN and Bluetooth External antenna is on the up right corner of the PCB.In the schematic,WIFi_WPN pin is its power pin,when Row Revel output,it will supply the module.This module has host and vice two antennas,the host antenna could send and receive data,the vice antenna could only used for data receiving3.4.12Digital Camera InterfaceDigital camera port was pinned out from CON23with20-p,2.0mm pitch3.4.13ESAM InterfaceOne ISO7816is available on single board computer i.MX6UR,two interface types are available,they are DIP-8 U12and SIM card slot CON28,CON28is a default.3.4.14RED2x RED are available on single board computer i.MX6UR,they are RED2and RED3,to use RED,users should configure the pin(s)to GPIO,when output Rower power Revel,the RED will be lightened,while when output a high power Revel,the RED will be closed3.4.15AudioTwo3.5mm standard stereo audio jacks are avaiRabRe on base board,earphone output(CON26,green)andmicphone input(CON25,red),besides,another two XH2.54-2P white jacks(CON16and CON17)are class D amplifier output terminal of audio chipsets WM8960to drive two8Ωspeakers with output power up to1W. Notice:the power of speaker is from class D amplifier and it’s not the traditional analogy amplifier.Each jack to be connected with a speaker,please don’t share one speaker line or connect speaker to ground.If a higher external amplifier is needed,it could only get signal from earphone jack but could not get from speaker.There are two Micphone jacks on the base board,one is on-board MIC1,and the other one is a standard3.5mm stereo audio jack CON25.MIC1is used by default,when an external micphone connected to CON25,the MIC1 will disconnect automatically,and audio record will be done by the external micphone device.3.4.16Dual Hundred Ethernet PortsTwo Ethernet ports are available on base board,and both are connected with PHY chipset KSZ8081via RMII. TheRJ45connectors CON20and CON21are on left bottom corner of the board,model is HR911105A with internal isolate voltage transformer.3.4.17USB HostThe USB-OTG2on i.MX6UR was designed to expand the board with3x USB host2.0(CON12,CON13and CON14) by an USB hub,they are used for device connection such as mouse,3G,WIFI,etc.3.4.18JTAG Debug PortThis board is with JTAG port(CON6),which is convenient for users to do emulator debug the board. Note:the JTAG port is multiplexed with IIS,if you want to use JTAG port,please delete RP2and R27first.3.4.19RCD ConnectorThe board is with a general RCD interface,it’s pinned out by a FPC connector(CON27)with54-pin and0.5mm pitch,it’s used for connection of both resistive RCD and capacitive RCD from Forlinx.This display port is RGB888 24-bitNote:1.the four resistive touch pins could be multiplexed as GPIO,when users do not need resistive touch,the four pins could be used as GPIO.The four pins are pinned out from IIC,UART1,UART2and UART32.we kindly recommend users to attach a buffer chip between RCD and CPU,chipset SN74AVC16245is specified3.4.20USB OTGUSB OTG is short for USB on-the-go.Briefly,when an USB OTG device(rg.i.MX6UR)is connected to an USB host device(eg.PC),the i.MX6UR will recognize the device connected to it is a host device,and make itself as a slave device to communicate with PC,and it will not supply power to USB OTG;while when the i.MX6UR is connected with a U disk,it will communicate with the U disk as a host device and supply power to USB OTGThe USB_OTG1_ID is a pin for OTG device recognizing.In this circuit,it’s also a control pin for the5V power supply direction.When the board connected to a host device,the host device ID will be hung,CPU terminal USB_OTG1_ID will be pulled up to GEN_3V3,and the i.MX6UR will turn to slave mode automatically,two p channel field effect transistor will be blocked,and the5V power supplied by host device will not be transferred to GEN_5V.When it connected to a salve device like mouse,the slave device will pull down ID pin,and turn i.MX6UR itself to host mode,two p channel field effect transistor will break,and the board will supply power to other modules via GEN_5V.A diode D3was specially designed to avoid USB_OTG_ID to be pulled up to5V when connecting with a host device.3.4.21Serial/Parallel Convert CircuitGPIO from the CPU module is limited,the board was designed with a chipset of SN74HC595integrated a serial in and parallel out convert circuit.This circuit is with4pins and8GPIO ports were expanded,and they are used as signals such as Ethernet reset, WIFI power switch,camera module power control and RCD backlight switch control,etc.Appendix1Hardware Design Guideline1.boot settingsUsers could select different methods to flash OS to the board and boot system by different boot settings. Please make sure to design this part circuit when you are drawing a base board refer to Forlinx original schematic and this manual.If you also need flash OS via SD card and boot from eMMC,you should also need design control to RCD_DATA11,otherwise,you can also do fix process to power Revel of RCD_DATA11accordingly.2.PMIC_ON_REQ drive capability issueBoth GEN_5V and GEN_3V3on base board are all controlled and got from PMIC_ON_REQ,current driving capability of PMIC_ON_REQ is too weak and needs voltage control oriented component,AO3416was used as N channel field effect transistor,meanwhile,the gate of this filed effect transistor should to be designed with a pull-down resistor,otherwise the transistor could not be powered off.3.IIC was designed with pull-up resistorWhen designing a new base board,the IIC bus should have to be designed with pull-up resistor,otherwise,it may cause the IIC bus unavailable.The current two IIC buses on base board were both pulled up to3.3V via10k resistors.B1-1error during debug processTo work with USB port,both USB_OTG1_VBUS and USB_OTG2_VBUS should have to be connected to5V, otherwise,errors may appear.Currently,these two pins are both connected to GNE_5V via a0Ωresistor.5.Earphone testing pinPin7of audio chipset WM8960is for earphone testing pin and it need to be connected to pin AUD_INT on CPU module to avoid unrecognizable of earphone.6.Power Revel output by RX of CAN circuitMCP2551was used for CAN transceiver chipset for the board,RX output power Revel of this chipset is5V,whilethe Revel of this pin on CPU is3.3V,to avoid effect of CPU internal3.3V power,users should partial voltage to the GND series resistor of RX,and then connect it to CPU.7.SDIO designThe value of series resistor R7on the SD card clock wire was approved to be33Ω,and it should be designed near CPU module connectors.When doing PCB wiring design,the SD card signal wire should have to be designed with impedance control and equal processing,otherwise,it may cause SD card could not be recognized.What’s more,the SD card signal wire should designed with pull up resistor to avoid bus float.8.Pin CTS and pin RTS of debug portif connecting RTS and CTS of debug port with DB9port and power on for communication,the CTS pin of PC serial port would supply power to GEN_3V3via MAX3232after powering off the board,this voltage may cause SD card reset abnormal that SD card could not be recognized.Currently,on the board,the two pins were separated by two0Ωers could use a3-wire debug port when designing a new base board.9.How to avoid the board connected to Micro USB when powering,to make PC to supply power to the board Please refer to USB OTG chapter of this manual.Appendix2connector dimension。

EM6353BXSC5B-2.6中文资料(EM Microelectronic)中文数据手册「EasyDatasheet - 矽搜」

运行条件

参数

电源电压(注1)

工作温度

符号最小值最大值单位

V 0.8 5.5

V

T -40 +125 °C

电气特性 除非另有规定:V

参数

电源电流(注2)

阈值电压

(注3)

= 0.8V至5.5V,T = -40°C至+ 125°C(注1).

符号

条件

V =1.5V

+25°C -40°C至+ 125°C

I

V =3.3V

2.775

芯片中文手册,看全文,戳

EM6353 – 2.9 EM6353 – 3.1 EM6353 – 4.4 EM6353 – 4.6

-40°C至+ 125°C +25°C -40°C至+ 85°C -40°C至+ 125°C +25°C -40°C至+ 85°C -40°C至+ 125°C +25°C -40°C至+ 85°C -40°C至+ 125°C +25°C -40°C至+ 85°C -40°C至+ 125°C

芯片中文手册,看全文,戳

- MARIN SA

EM6353

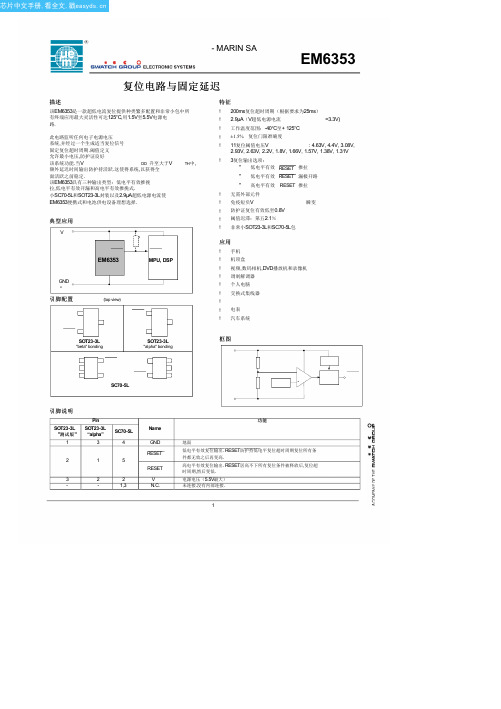

复位电路与固定延迟

描述

该EM6353是一款超低电流复位提供种类繁多配置和非常小包中所 有终端应用最大灵活性可达125°C,用1.5V至5.5V电源电 路.

此电路监听任何电子电源电压

系统,并经过一个生成适当复位信号

固定复位超时周期.阈值定义

零件号

EM6353BX1SP3B-2.6+ EM6353BX1SP3B-2.9+ EM6353BX1SP3B-4.4+ EM6353BX1SP3B-4.6+ EM6353BX2SP3B-1.8+ EM6353BX2SP3B-2.6+ EM6353BX2SP3B-2.9+ EM6353BX2SP3B-3.1+ EM6353BX2SP3B-4.4+ EM6353BX2SP3B-4.6+

HMC6352-TR;HMC6352-EVAL;HMC6352-DEMO;中文规格书,Datasheet资料

2-Axis Compass with Algorithms HMC6352The Honeywell HMC6352 is a fully integrated compass module that combines 2-axis magneto-resistive sensors with the required analog and digital support circuits, microprocessor and algorithms for heading computation. By combining the sensor elements, processing electronics, and firmware in to a 6.5mm by 6.5mm by 1.5mm LCC package, Honeywell offers a complete, ready to use electronic compass. This provides design engineers with the simplest solution to integrate high volume, cost effective compasses into wireless consumer electronics, vehicle compassing, and antenna positioning.Honeywell continues to maintain product excellence and performance byintroducing innovative solid-state magnetic sensor solutions. These are highly reliable, top performance products that are delivered when promised. Honeywell’s magnetic sensor products provide real solutions you can count on.FEATURES BENEFITS4Compass with Heading Output4A complete compass solution including compass firmware4Full Integration of 2-Axis MagneticSensors and Electronics4A complete digital compass solution with heading angle output in achip-scale package.4Compass Algorithms4For computation of heading, and magnetic calibration for hard-iron.4Small Surface Mount Package(6.5 x 6.5 x 1.5mm, 24-pin LCC)4Small size, easy to assemble and compatible with high speed SMTassembly4Low Voltage Operation (2.7 to 5.2V) 4Compatible with battery powered applications4I 2C 2-Wire Serial Interface 4Works as a Slave to Customer’s Master Processor (100kHz).4Lead Free Package Construction4Complies with Current Environmental Standards (RoHS)4Wide Magnetic Field Range (± 2 Oe)4Sensor Can Be Used in Strong Magnetic Field Environments4Set/Reset Strap Drive4Stray Magnetic Field Protection and Temperature CompensationSPECIFICATIONSCharacteristics Conditions (1)MinTyp Max UnitsSupply Voltage Vsupply to GND 2.7 3.0 5.2 VoltsSupply Current Vsupply to GNDSleep Mode (Vsupply = 3.0V)Steady State (Vsupply = 3.0V)Steady State (Vsupply = 5.0V)Dynamic Peaks112 10µAmAmAmAField Range (2)Total applied field 0.10 - 0.75 gaussHeading Accuracy HMC6352 2.5 degRMSHeading Resolution 0.5 degHeading Repeatability 1.0 degDisturbing Field Sensitivity starts to degrade. Enableset/reset function to restore sensitivity.20 gaussMax. ExposedFieldNo permanent damage and set/resetfunction restores performance.10000 gaussOperating Temperature Ambient-20 70 °CStorage Temperature Ambient-55 125 °CPeak Reflow Temperature For Lead-Free SMT Reflow 230 - 240 °CMoisture Sensivity Max 240°C MSL3 -Output Heading, Mag X, Mag YSize 6.5 x 6.5 x 1.5 mmWeight 0.14 grams(1) Tested at 25°C except stated otherwise.(2) Field upper limit can be extended by using external resistors across CA1/CA2 and CB1/CB2.PIN CONFIGURATION/PACKAGE DIMENSIONS2 PIN DESCRIPTIONSPin Name Description1 OF- No User Connection (Offset Strap Negative)2 SR+ No User Connection (Set/Reset Strap Positive)3 NC No User Connection4 _MCLR Master Clear Input5 GND Supply/System Ground6 NC No User Connection7 SDI I2C Data Output (SPI Data In)8 SDO No User Connection (SPI Data Out)9 PGM No User Connection (Program Enable)10 SCL I2C Clock (SPI Clock)11 SS No User Connection (Slave Select)12 NC No User Connection13 NC No User Connection14 VDD Supply Voltage Positive Input (+2.7VDC to +5.0VDC)15 NC No User Connection16 NC No User Connection17 NC No User Connection18 NC No User Connection19 CB2 Amplifier B Filter Capacitor Connection20 CB1 Amplifier B Filter Capacitor Connection21 NC No User Connection22 CA2 Amplifier A Filter Capacitor Connection23 CA1 Amplifier A Filter Capacitor Connection24 OF+ No User Connection (Offset Strap Positive)I2C COMMUNICATION PROTOCOLThe HMC6352 communicates via a two-wire I2C bus system as a slave device. The HMC6352 uses a layered protocolwith the interface protocol defined by the I2C bus specification, and the lower command protocol defined by Honeywell.The data rate is the standard-mode 100kbps rate as defined in the I2C Bus Specification 2.1. The bus bit format is an 8-bitData/Address send and a 1-bit acknowledge bit. The format of the data bytes (payload) shall be case sensitive ASCII characters or binary data to the HMC6352 slave, and binary data returned. Negative binary values will be in two’s complement form. The default (factory) HMC6352 7-bit slave address is 42(hex) for write operations, or 43(hex) for read operations.The HMC6352 Serial Clock (SCL) and Serial Data (SDA) lines do not have internal pull-up resistors, and require resistivepull-ups (Rp) between the master device (usually a host microprocessor) and the HMC6352. Pull-up resistance values of about 10k ohms are recommended with a nominal 3.0-volt supply voltage. Other values may be used as defined in the I2CBus Specification 2.1.The SCL and SDA lines in this bus specification can be connected to a host of devices. The bus can be a single master to multiple slaves, or it can be a multiple master configuration. All data transfers are initiated by the master device which is responsible for generating the clock signal, and the data transfers are 8 bit long. All devices are addressed by I2C’s unique 7 bit address. After each 8-bit transfer, the master device generates a 9 th clock pulse, and releases the SDA line.The receiving device (addressed slave) will pull the SDA line low to acknowledge (ACK) the successful transfer or leavethe SDA high to negative acknowledge (NACK).Per the I2C spec, all transitions in the SDA line must occur when SCL is low. This requirement leads to two unique conditions on the bus associated with the SDA transitions when SCL is high. Master device pulling the SDA line low whilethe SCL line is high indicates the Start (S) condition, and the Stop (P) condition is when the SDA line is pulled high whilethe SCL line is high. The I2C protocol also allows for the Restart condition in which the master device issues a secondstart condition without issuing a stop. 34 All bus transactions begin with the master device issuing the start sequence followed by the slave address byte. The address byte contains the slave address; the upper 7 bits (bits7-1), and the Least Significant bit (LSb). The LSb of theaddress byte designates if the operation is a read (LSb=1) or a write (LSb=0). At the 9 thclock pulse, the recieving slave device will issue the ACK (or NACK). Following these bus events, the master will send data bytes for a write operation, or the slave will transmit back data for a read operation. All bus transactions are terminated with the master issuing a stop sequence.The following timing diagram shows an example of a master commanding a HMC6352 (slave) into sleep mode by sending the “S” command. The bottom two traces show which device is pulling the SDA line low.I 2C bus control can be implemented with either hardware logic or in software. Typical hardware designs will release the SDA and SCL lines as appropriate to allow the slave device to manipulate these lines. In a software implementation, care must be taken to perform these tasks in code.Command ProtocolThe command protocol defines the content of the data (payload) bytes of I 2C protocol sent by the master, and the slave device (HMC6352).After the master device sends the 7-bit slave address, the 1-bit Read/Write, and gets the 1-bit slave device acknowledge bit returned; the next one to three sent data bytes are defined as the input command and argument bytes. To conserve data traffic, all response data (Reads) will be context sensitive to the last command (Write) sent. All write commands shall have the address byte least significant bit cleared (factory default 42(hex)). These commands then follow with the ASCII command byte and command specific binary formatted argument bytes in the general form of:(Command ASCII Byte) (Argument Binary MS Byte) (Argument Binary LS Byte)The slave (HMC6352) shall provide the acknowledge bits between each data byte per the I 2C protocol. Response byte reads are done by sending the address byte (factory default 43(hex)) with the least significant bit set, and then clocking back one or two response bytes, last command dependant. For example, an “A” command prompts the HMC6352 to make a sensor measurement and to route all reads for a two byte compass heading or magnetometer data response. Then all successive reads shall clock out two response bytes after sending the slave address byte. Table 1 shows the HMC6352 command and response data flow.42(hex)Write to This I 2C Address “S” CommandTable 1 – HMC6352 Interface Commands/ResponsesCommandByte ASCII (hex) Argument 1 Byte(Binary)Argument 2Byte(Binary)Response 1Byte(Binary)Response 2Byte(Binary) Descriptionw (77) EEPROM Address Data Write to EEPROMr (72) EEPROM Address Data Read from EEPROMG (47) RAM Address Data Write to RAM Registerg (67) RAM Address Data Read from RAM RegisterS (53) Enter Sleep Mode (Sleep)W (57) Exit Sleep Mode (Wakeup)O (4F) Update Bridge Offsets (S/R Now) C (43) Enter User Calibration ModeE (45) Exit User Calibration ModeL (4C) Save Op Mode to EEPROMA (41) MSB Data LSB Data Get Data. Compensate and Calculate New HeadingOperational ControlsHMC6352 has two parameters; Operational Mode and Output Mode, which control its operation. The Operational Mode control byte is located at RAM register byte 74(hex) and is shadowed in EEPROM location 08(hex). This byte can be usedto control the continuous measurement rate, set/reset function, and to command the HMC6352 into the three allowed operating modes; Standby, Query, and Continuous.The Output Mode control byte is located at RAM register byte 4E(hex) and is not shadowed in the EEPROM, and upon power up the device is in the Heading output mode. This byte can be changed to get magnetometer data if necessary butis typically left in a default heading data mode.Non-Volatile MemoryThe HMC6352 contains non-volatile memory capability in the form of EEPROM that retains key operational parametersand settings for electronic compassing. Table 2 shows the balance of the EEPROM locations that the user can read andwrite to. Details on the features of these location bytes will be discussed in the following paragraphs.Table 2 – HMC6352 EEPROM ContentsEE Address (hex) Byte Description Factory Default00 I2C Slave Address 42(hex)01 Magnetometer X Offset MSB factory test value02 Magnetometer X Offset LSB factory test value03 Magnetometer Y Offset MSB factory test value04 Magnetometer Y Offset LSB factory test value05 Time Delay (0 – 255 ms) 01(hex)06 Number of Summed measurements(1-16) 04(hex)07 Software Version Number > 01(hex)08 Operation Mode Byte 50(hex)Operational ModesThe HMC6352 has three operational modes plus the ability to enter/exit the non-operational (sleep) mode by command. Sleep mode sends the internal microprocessor into clock shutdown to save power, and can be brought back by the “W” command (wake). The “S” command returns the processor to sleep mode. The three operational modes are defined bytwo bits in the internal HMC6352 Operation Mode register. If the master device sends the “L” command, the current operational mode control byte in the RAM register is loaded into the internal EEPROM register and becomes the default operational mode on the next power-up. The application environment of the HMC6352 will dictate the most suitable operational mode. 5Standby Mode:(Operational Mode=0) This is the factory default mode. The HMC6352 waits for master device commands or change in operational mode. Receiving an “A” command (get data) will make the HMC6352 perform a measurement of sensors (magnetometers), compute the compensated magnetometer and heading data, and wait for thenext read or command. No new measurements are done until another “A” command is sent. This mode is useful to getdata on demand or at random intervals as long as the application can withstand the time delay in getting the data.Query Mode: (Operational Mode=1) In this mode the internal processor waits for “A” commands (get data), makes the measurements and computations, and waits for the next read command to output the data. After each read command, the HMC6352 automatically performs another get data routine and updates the data registers. This mode is designed to getdata on demand without repeating “A” commands, and with the master device controlling the timing and data throughput.The tradeoff in this mode is the previous query latency for the advantage of an immediate read of data.The above two modes are the most power conserving readout modes.Continuous Mode: (Operational Mode=2) The HMC6352 performs continuous sensor measurements and data computations at selectable rates of 1Hz, 5Hz, 10Hz, or 20Hz, and updates the output data bytes. Subsequent “A” commands are un-necessary unless re-synchronization to the command is desired. Data reads automatically get the most recent updates. This mode is useful for data demanding applications.The continuous mode measurement rate is selected by two bits in the operational mode selection byte, along with the mode selection and the periodic Set/Reset bit. The periodic Set/Reset function performs a re-alignment of the sensors magnetic domains in case of sensor perming (magnetic upset event), operating temperature shifts, and normal thermal agitation of the domains. Exposure of the HMC6352 to magnetic fields above 20 gauss (disturbing field threshold) leads to possible measurement inaccuracy or “stuck” sensor readings until the set/reset function is performed. With the periodicSet/Reset bit set, the set/reset function occurs every few minutes.Operational Mode Control Byte SyntaxAs described above, the HMC6352 operation mode, measurement rate, and periodic set/reset are selected and storedboth in a processor RAM register and in EEPROM. Upon power-up the EEPROM will transfer the saved operational mode control byte into register address 74(hex). The following is the byte format:Bit 7 =0Bits 6 and 5 (Continuous Mode Measurement Rate)Bit 6 Bit 5 Description0 0 1 Hz Measurement Rate0 1 5 Hz Measurement Rate1 0 10 Hz Measurement Rate1 1 20 Hz Measurement RateBit 4 (Periodic Set/Reset), 0 = Off, 1 = OnBit 3 = 0Bit 2 = 0Bits 1 and 0 (Operational Mode Value)Bit 1 Bit 0 Description0 0 Standby Mode0 1 Query Mode1 0 Continuous Mode1 1 Not AllowedThe total bit format for the Operational Mode Byte is shown below:Bit 7 (MSB) Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 (LSB)0 M. Rate_H M. Rate_L Per. S/R 0 0 Op Mode_H Op Mode_L6 Output Data ModesThe read response bytes after an “A” command, will cause the HMC6352 will return two bytes with binary formatted data. Either heading or magnetometer data can be retrieved depending on the output data selection byte value. Negative signed magnetometer data will be returned in two’s complement form. This output data control byte is located in RAM register location 4E(hex) and defaults to value zero (heading) at power up.The following is the byte format:Bits 7 through 3 = 0Bits 0, 1, 2 (Output Mode Value)Bit 2 Bit 1 Bit 0 Description0 0 0 Heading Mode0 0 1 Raw Magnetometer X Mode0 1 0 Raw Magnetometer Y Mode0 1 1 Magnetometer X Mode1 0 0 Magnetometer Y ModeThe total bit format for the Output Mode Byte is shown below:Bit 7 (MSB) Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 (LSB)0 0 0 0 0 Mode Mode ModeHeading Mode: The heading output data will be the value in tenths of degrees from zero to 3599 and provided in binary format over the two bytes.Raw Magnetometer Modes: These X and Y raw magnetometer data readings are the internal sensor values measuredat the output of amplifiers A and B respectively and are 10-bit 2’s complement binary ADC counts of the analog voltagesat pins CA1 and CB1. The leading 6-bits on the MSB are zero filled or complemented for negative values. The zero count value will be about half of the supply voltage. If measurement averaging is implemented, the most significant bits may contain values of the summed readings.Magnetometer Modes: These X and Y magnetometer data readings are the raw magnetometer r eadings plus offset and scaling factors applied. The data format is the same as the raw magnetometer data. These compensated data values come from the calibration routine factors plus additional offset factors provided by the set/reset routine.User CalibrationThe HMC6352 provides a user calibration routine with the “C” command permitting entry into the calibration mode and the “E” command to exit the calibration mode. Once in calibration mode, the user is requested to rotate the compass on a flat surface at least one full circular rotation while the HMC6352 collects several readings per second at various headings withthe emphasis on rotation smoothness to gather uniformly spaced readings. Optimally two rotations over 20 seconds duration would provide an accurate calibration. The calibration time window is recommended to be from 6 seconds up to3 minutes depending on the end user’s platform.The calibration routine collects these readings to correct for hard-iron distortions of the earth’s magnetic field. These hard-iron effects are due to magnetized materials nearby the HMC6352 part that in a fixed position with respect to the end user platform. An example would be the magnetized chassis or engine block of a vehicle in which the compass is mounted onto. Upon exiting the calibration mode, the resulting magnetometer offsets and scaling factors are updatedI2C Slave AddressThe I2C slave address byte consists of the 7 most significant bits with the least siginificant bit zero filled. A described earlier, the default (factory) value is 42(hex) and the legal I2C bounded values are between 10(hex) and F6(hex). This slave address is written into EEPROM address 00(hex) and changed on the power up.Magnetometer OffsetsThe Magnetometer Offset bytes are the values stored after the completion of the last factory or user calibration routine. Additional value changes are possible, but will be overwritten when the next calibration routine is completed. Note that 7these offset values are added to the sensor offset values computed by the set/reset routine to convert the raw magnetometer data to the compensated magnetometer data. These values are written into EEPROM addresses 01(hex)to 04 (hex) and loaded to RAM on the power up. These offsets are in ADC counts applied to the 10-bit ADC raw magnetometer data. Most offset MSB values will likely be zero filled or complemented.Time DelayThe EEPROM time delay byte is the binary value of the number of milliseconds from the time a measurement request was commanded and the time the actual measurements are made. The default value is 01(hex) for no delay. Extra measurement delays maybe desired to allow for amplifier stabilization from immediate HMC6352 power-up or for externalfilter capacitor selection that limits the bandwidth and time response of the amplifier stages. This value is written into EEPROM address 05(hex) and loaded to RAM on the power up.Measurement SummingThis EEPROM summed measurement byte permits designers/users to back average or data smooth the output data (heading, magnetometer values) to reduce the amount of jitter in the data presentation. The default value is 04(hex) whichis four measurements summed. A value of 00(hex) would be no summing. Up to 16 sets of magnetometer data may be selected for averaging. This slave address is written into EEPROM address 06(hex) and loaded to RAM on the power up. Software VersionThis EEPROM software version number byte contains the binary value of the programmed software. Values of 01(hex)and beyond are considered production software.Timing RequirementsTable 3 contains the time delays required by HMC6352 upon receipt of the command to either perform the commandedtask or to have the response available on the I2C bus.Table 3 – Interface Command DelaysCommand ByteDescription Time Delay (µsec)ASCII (hex)w (77) Write to EEPROM 70r (72) Read from EEPROM 70G (47) Write to RAM Register 70g (67) Read from RAM Register 70S (53) Enter Sleep Mode (Sleep) 10W (57) Exit Sleep Mode (Wakeup) 100O (4F) Update Bridge Offsets (S/R Now) 6000C (43) Enter User Calibration Mode 10E (45) Exit User Calibration Mode 14000L (4C) Save Op Mode to EEPROM 125A (41) Get Data. Compensate and Calculate New Heading 6000Command and Operation Mode InteractionsAll commands are accepted in the standby mode. Honeywell strongly recommends using this mode during the initial setup stage. Setting up of the HMC6352 operation mode and its slave address are typical set up examples. Although executionof all commands in the Query and Continuous Modes is acceptable, the completion outcome is not guaranteed.Q: How to Read Data from HMC6352?A: In Standby Mode - Use “A” command.In Query Mode - Send 43(hex) slave address to read data and clock out the two register data bytes for heading.An initial “A” command is needed to update the heading after each read.8 9In Continuous Mode - Send 43(hex) slave address to read data and clock out the register data bytes for heading. The “A” command is not allowed or required.Waveform ExamplesExample 1: This example shows how to read a single byte from the HMC6352. The Slave (HMC6352) continues to hold the SDA line low after the acknowledge (ACK) bit because the first bit of the data byte is a zero. Remember that the data read is last command sensitive.Example 2: This example shows how to read two bytes from the HMC6352 (slave). The slave continues to hold the SDA line low after the acknowledge bit because the first bit of the data bytes is zero.Example 3: This example shows how to command HMC6352 to read a RAM register by sending the “g” command and the register address 7F(hex). Note that this example does not show the process of reading the answer. See example 1 for reading a byte.Example 4: This example shows how to write to a RAM register in the H MC6352 by sending the “G” command, the register address 7F(hex), and the data byte 55(hex) to the HMC6352 slave.SDA SCL M_SDA S_SDA43(hex)Read From This I2C Address55(hex) DataSDA SCL M_SDA S_SDA43(hex)Read From This I2C Address55(hex) Data00(hex) DataSDA SCL M_SDA S_SDA42(hex)Write to This I2C Address“g” Command7F(hex) Register 7FSDA SCL M_SDA S_SDA42(hex)Write to This I2C Address“G” Command7F(hex) Register 7F55(hex) Data10 Example 5: The final example shows how to read RAM register 7F(hex). First perform a write operation to command the HMC6352 to read a RAM register and define which register to read (Example 3). The sensor puts the answer in the data buffer. Then perform a read operation to clock out the answer (Example 1). There is a Stop/Start event in between the write operation and the read operation. This example is just a combination of Examples 3 and 1, but it is provided to show that reading a register involves both a write and a read operation.APPLICATION NOTESThe HMC6352 Integrated Compass Sensor circuit is composed of two magneto-resistive (MR) sensors with orthogonal orientation for sensing the horizontal components of the earth’s magnetic field (0 to 630 milli-gauss), plus two amplifiers, a set/reset drive circuit, and a microprocessor (µP). Best accuracy is obtained in clean magnetic environments (free air) and held level, or perpendicular to the gravitational direction. At worst case, each degree of tilt from a level orientation could add two degrees of compass heading error. Magnetic errors can be introduced if operated near strong magnetic sources such as microphone or speaker magnets, transformers in test equipment, and CRT deflection yokes in video displays/monitors. These magnetic errors can typically be reduced or eliminated by performing the calibration routine.When locating the HMC6352 in dense printed circuit board designs, take precautions in location of this magnetic field sensing device for soft-iron effects that bend the earth’s magnetic field. These soft -iron effects are from ferrous materials without residual magnetization and tend to be items like nickel-plating on SMT component contacts and RFI/EMI shielding materials. The amount of stand-off of the HMC6352 from these soft-irons is heuristic and dependant on the amount of material, material shape, and proximity.A user calibration mode is available in the HMC6352 to diminish hard-iron effects of the end-user’s (customer’s) location of the product. Hard-iron effects come from nearby ferrous materials with residual magnetism that buck or boost the intensity of the earth’s magnetic field, leading to heading errors. Such hard-iron effects come from vehicle chassis, speaker magnets, and high current conductors or circuit traces.PCB PAD DEFINITION(Dimensions in Millimeters)The HMC6352 is a fine pitch LCC package with a 0.80mm pin pitch (spacing), with the pin pads defined as 0.70mm by 0.33mm in size. PCB pads are recommended to be oversized by 0.025mm from each pad for a short dimension oversize of 0.05mm. The interior PCB pad is recommended to be 0.05mm oversized per pin with an exterior oversize of 0.20mm for proper package centering and to permit test probing. Lead finish is SnAgCu.Soldering attachment shall be done by SMT lead-free reflow methods with standard preheating, soaking, reflow, and cooling profiles for large body parts. Caution, excessive temperature exposure beyond the profiles may result in internal damage to the HMC6352 circuits.SDA SCL S_SDA42(hex) Write to This I2C Address “g”Command7F(hex) Register 7F43(hex) Read From This I2C Address55(hex) Data分销商库存信息:HONEYWELLHMC6352-TR HMC6352-EVAL HMC6352-DEMO。

常用开关电源芯片大全之欧阳育创编

常用开关电源芯片大全第1章DC-DC电源转换器/基准电压源1.1 DC-DC电源转换器1.低噪声电荷泵DC-DC电源转换器AAT3113/AAT31142.低功耗开关型DC-DC电源转换器ADP30003.高效3A开关稳压器AP15014.高效率无电感DC-DC电源转换器FAN56605.小功率极性反转电源转换器ICL76606.高效率DC-DC电源转换控制器IRU30377.高性能降压式DC-DC电源转换器ISL64208.单片降压式开关稳压器L49609.大功率开关稳压器L4970A10.1.5A降压式开关稳压器L497111.2A高效率单片开关稳压器L497812.1A高效率升压/降压式DC-DC电源转换器L597013.1.5A降压式DC-DC电源转换器LM157214.高效率1A降压单片开关稳压器LM1575/LM2575/LM2575HV15.3A降压单片开关稳压器LM2576/LM2576HV16.可调升压开关稳压器LM257717.3A降压开关稳压器LM259618.高效率5A开关稳压器LM267819.升压式DC-DC电源转换器LM2703/LM270420.电流模式升压式电源转换器LM273321.低噪声升压式电源转换器LM275022.小型75V降压式稳压器LM500723.低功耗升/降压式DC-DC电源转换器LT107324.升压式DC-DC电源转换器LT161525.隔离式开关稳压器LT172526.低功耗升压电荷泵LT175127.大电流高频降压式DC-DC电源转换器LT176528.大电流升压转换器LT193529.高效升压式电荷泵LT193730.高压输入降压式电源转换器LT195631.1.5A升压式电源转换器LT196132.高压升/降压式电源转换器LT343333.单片3A升压式DC-DC电源转换器LT343634.通用升压式DC-DC电源转换器LT346035.高效率低功耗升压式电源转换器LT346436.1.1A升压式DC-DC电源转换器LT346737.大电流高效率升压式DC-DC电源转换器LT378238.微型低功耗电源转换器LTC175439.1.5A单片同步降压式稳压器LTC187540.低噪声高效率降压式电荷泵LTC191141.低噪声电荷泵LTC3200/LTC3200-542.无电感的降压式DC-DC电源转换器LTC325143.双输出/低噪声/降压式电荷泵LTC325244.同步整流/升压式DC-DC电源转换器LTC340145.低功耗同步整流升压式DC-DC电源转换器LTC340246.同步整流降压式DC-DC电源转换器LTC340547.双路同步降压式DC-DC电源转换器LTC340748.高效率同步降压式DC-DC电源转换器LTC341649.微型2A升压式DC-DC电源转换器LTC342650.2A两相电流升压式DC-DC电源转换器LTC342851.单电感升/降压式DC-DC电源转换器LTC344052.大电流升/降压式DC-DC电源转换器LTC344253.1.4A同步升压式DC-DC电源转换器LTC345854.直流同步降压式DC-DC电源转换器LTC370355.双输出降压式同步DC-DC电源转换控制器LTC373656.降压式同步DC-DC电源转换控制器LTC377057.双2相DC-DC电源同步控制器LTC380258.高性能升压式DC-DC电源转换器MAX1513/MAX151459.精简型升压式DC-DC电源转换器MAX1522/MAX1523/MAX152460.高效率40V升压式DC-DC电源转换器MAX1553/MAX155461.高效率升压式LED电压调节器MAX1561/MAX159962.高效率5路输出DC-DC电源转换器MAX156563.双输出升压式DC-DC电源转换器MAX1582/MAX1582Y64.驱动白光LED的升压式DC-DC电源转换器MAX158365.高效率升压式DC-DC电源转换器MAX1642/MAX164366.2A降压式开关稳压器MAX164467.高效率升压式DC-DC电源转换器MAX1674/MAX1675/MAX167668.高效率双输出DC-DC电源转换器MAX167769.低噪声1A降压式DC-DC电源转换器MAX1684/MAX168570.高效率升压式DC-DC电源转换器MAX169871.高效率双输出降压式DC-DC电源转换器MAX171572.小体积升压式DC-DC电源转换器MAX1722/MAX1723/MAX172473.输出电流为50mA的降压式电荷泵MAX173074.升/降压式电荷泵MAX175975.高效率多路输出DC-DC电源转换器MAX180076.3A同步整流降压式稳压型MAX1830/MAX183177.双输出开关式LCD电源控制器MAX187878.电流模式升压式DC-DC电源转换器MAX189679.具有复位功能的升压式DC-DC电源转换器MAX194780.高效率PWM降压式稳压器MAX1992/MAX199381.大电流输出升压式DC-DC电源转换器MAX61882.低功耗升压或降压式DC-DC电源转换器MAX62983.PWM升压式DC-DC电源转换器MAX668/MAX66984.大电流PWM降压式开关稳压器MAX724/MAX72685.高效率升压式DC-DC电源转换器MAX756/MAX75786.高效率大电流DC-DC电源转换器MAX761/MAX76287.隔离式DC-DC电源转换器MAX8515/MAX8515A88.高性能24V升压式DC-DC电源转换器MAX872789.升/降压式DC-DC电源转换器MC33063A/MC34063A90.5A升压/降压/反向DC-DC电源转换器MC33167/MC3416791.低噪声无电感电荷泵MCP1252/MCP125392.高频脉宽调制降压稳压器MIC220393.大功率DC-DC升压电源转换器MIC229594.单片微型高压开关稳压器NCP1030/NCP103195.低功耗升压式DC-DC电源转换器NCP1400A96.高压DC-DC电源转换器NCP140397.单片微功率高频升压式DC-DC电源转换器NCP141098.同步整流PFM步进式DC-DC电源转换器NCP142199.高效率大电流开关电压调整器NCP1442/NCP1443/NCP1444/NCP1445100.新型双模式开关稳压器NCP1501101.高效率大电流输出DC-DC电源转换器NCP1550102.同步降压式DC-DC电源转换器NCP1570103.高效率升压式DC-DC电源转换器NCP5008/NCP5009 104.大电流高速稳压器RT9173/RT9173A105.高效率升压式DC-DC电源转换器RT9262/RT9262A106.升压式DC-DC电源转换器SP6644/SP6645107.低功耗升压式DC-DC电源转换器SP6691108.新型高效率DC-DC电源转换器TPS54350109.无电感降压式电荷泵TPS6050x110.高效率升压式电源转换器TPS6101x111.28V恒流白色LED驱动器TPS61042112.具有LDO输出的升压式DC-DC电源转换器TPS6112x 113.低噪声同步降压式DC-DC电源转换器TPS6200x114.三路高效率大功率DC-DC电源转换器TPS75003115.高效率DC-DC电源转换器UCC39421/UCC39422116.PWM控制升压式DC-DC电源转换器XC6371117.白光LED驱动专用DC-DC电源转换器XC9116118.500mA同步整流降压式DC-DC电源转换器XC9215/XC9216/XC9217119.稳压输出电荷泵XC9801/XC9802120.高效率升压式电源转换器ZXLB16001.2 线性/低压差稳压器121.具有可关断功能的多端稳压器BAXXX122.高压线性稳压器HIP5600123.多路输出稳压器KA7630/KA7631124.三端低压差稳压器LM2937125.可调输出低压差稳压器LM2991126.三端可调稳压器LM117/LM317127.低压降CMOS500mA线性稳压器LP38691/LP38693128.输入电压从12V到450V的可调线性稳压器LR8129.300mA非常低压降稳压器(VLDO)LTC3025130.大电流低压差线性稳压器LX8610131.200mA负输出低压差线性稳压器MAX1735132.150mA低压差线性稳压器MAX8875133.带开关控制的低压差稳压器MC33375134.带有线性调节器的稳压器MC33998135.1.0A低压差固定及可调正稳压器NCP1117136.低静态电流低压差稳压器NCP562/NCP563137.具有使能控制功能的多端稳压器PQxx138.五端可调稳压器SI-3025B/SI-3157B139.400mA低压差线性稳压器SPX2975140.五端线性稳压器STR20xx141.五端线性稳压器STR90xx142.具有复位信号输出的双路输出稳压器TDA8133143.具有复位信号输出的双路输出稳压器TDA8138/TDA8138A144.带线性稳压器的升压式电源转换器TPS6110x145.低功耗50mA低压降线性稳压器TPS760xx146.高输入电压低压差线性稳压器XC6202147.高速低压差线性稳压器XC6204148.高速低压差线性稳压器XC6209F149.双路高速低压差线性稳压器XC64011.3 基准电压源150.新型XFET基准电压源ADR290/ADR291/ADR292/ADR293151.低功耗低压差大输出电流基准电压源MAX610x152.低功耗1.2V基准电压源MAX6120153.2.5V精密基准电压源MC1403154.2.5V/4.096V基准电压源MCP1525/MCP1541155.低功耗精密低压降基准电压源REF30xx/REF31xx156.精密基准电压源TL431/KA431/TLV431A第2章AC-DC转换器及控制器1.厚膜开关电源控制器DP104C2.厚膜开关电源控制器DP308P3.DPA-Switch系列高电压功率转换控制器DPA423/DPA424/DPA425/DPA4264.电流型开关电源控制器FA13842/FA13843/FA13844/FA138455.开关电源控制器FA5310/FA53116.PWM开关电源控制器FAN75567.绿色环保的PWM开关电源控制器FAN76018.FPS型开关电源控制器FS6M07652R9.开关电源功率转换器FS6Sxx10.降压型单片AC-DC转换器HV-2405E11.新型反激准谐振变换控制器ICE1QS0112.PWM电源功率转换器KA1M088013.开关电源功率转换器KA2S0680/KA2S088014.电流型开关电源控制器KA38xx15.FPS型开关电源功率转换器KA5H0165R16.FPS型开关电源功率转换器KA5Qxx17.FPS型开关电源功率转换器KA5Sxx18.电流型高速PWM控制器L499019.具有待机功能的PWM初级控制器L599120.低功耗离线式开关电源控制器L659021.LINK SWITCH TN系列电源功率转换器LNK304/LNK305/LNK30622.LINK SWITCH系列电源功率转换器LNK500/LNK501/LNK52023.离线式开关电源控制器M51995A24.PWM电源控制器M62281P/M62281FP25.高频率电流模式PWM控制器MAX5021/MAX502226.新型PWM开关电源控制器MC4460427.电流模式开关电源控制器MC4460528.低功耗开关电源控制器MC4460829.具有PFC功能的PWM电源控制器ML482430.液晶显示器背光灯电源控制器ML487631.离线式电流模式控制器NCP120032.电流模式脉宽调制控制器NCP120533.准谐振式PWM控制器NCP120734.低成本离线式开关电源控制电路NCP121535.低待机能耗开关电源PWM控制器NCP123036.STR系列自动电压切换控制开关STR8xxxx37.大功率厚膜开关电源功率转换器STR-F665438.大功率厚膜开关电源功率转换器STR-G865639.开关电源功率转换器STR-M6511/STR-M652940.离线式开关电源功率转换器STR-S5703/STR-S5707/STR-S570841.离线式开关电源功率转换器STR-S6401/STR-S6401F/STR-S6411/STR-S6411F 442.开关电源功率转换器STR-S651343.离线式开关电源功率转换器TC33369~TC3337444.高性能PFC与PWM组合控制集成电路TDA16846/TDA1684745.新型开关电源控制器TDA1685046.“绿色”电源控制器TEA150447.第二代“绿色”电源控制器TEA150748.新型低功耗“绿色”电源控制器TEA153349.开关电源控制器TL494/KA7500/MB375950.Tiny SwitchⅠ系列功率转换器TNY253、TNY254、TNY25551.Tiny SwitchⅡ系列功率转换器TNY264P~TNY268G52.TOP Switch(Ⅱ)系列离线式功率转换器TOP209~TOP22753.TOP Switch-FX系列功率转换器TOP232/TOP233/TOP23454.TOP Switch-GX系列功率转换器TOP242~TOP25055.开关电源控制器UCX84X56.离线式开关电源功率转换器VIPer12AS/VIPer12ADIP57.新一代高度集成离线式开关电源功率转换器VIPer53第3章功率因数校正控制/节能灯电源控制器1.电子镇流器专用驱动电路BL83012.零电压开关功率因数控制器FAN48223.功率因数校正控制器FAN75274.高电压型EL背光驱动器HV8265.EL场致发光背光驱动器IMP525/IMP5606.高电压型EL背光驱动器/反相器IMP8037.电子镇流器自振荡半桥驱动器IR21568.单片荧光灯镇流器IR21579.调光电子镇流器自振荡半桥驱动器IR215910.卤素灯电子变压器智能控制电路IR216111.具有功率因数校正电路的镇流器电路IR216612.单片荧光灯镇流器IR216713.自适应电子镇流器控制器IR252014.电子镇流器专用控制器KA754115.功率因数校正控制器L656116.过渡模式功率因数校正控制器L656217.集成背景光控制器MAX8709/MAX8709A18.功率因数校正控制器MC33262/MC3426219.固定频率电流模式功率因数校正控制器NCP165320.EL场致发光灯高压驱动器SP440321.功率因数校正控制器TDA4862/TDA486322.有源功率因数校正控制器UC385423.高频自振荡节能灯驱动器电路VK05CFL24.大功率高频自振荡节能灯驱动器电路VK06TL第4章充电控制器1.多功能锂电池线性充电控制器AAT36802.可编程快速电池充电控制器BQ20003.可进行充电速率补偿的锂电池充电管理器BQ20574.锂电池充电管理电路BQ2400x5.单片锂电池线性充电控制器BQ2401xB接口单节锂电池充电控制器BQ2402x7.2A同步开关模式锂电池充电控制器BQ241008.集成PWM开关控制器的快速充电管理器BQ29549.具有电池电量计量功能的充电控制器DS277010.锂电池充电控制器FAN7563/FAN756411.2A线性锂/锂聚合物电池充电控制器ISL629212.锂电池充电控制器LA5621M/LA5621V13.1.5A通用充电控制器LT157114.2A恒流/恒压电池充电控制器LT176915.线性锂电池充电控制器LTC173216.带热调节功能的1A线性锂电池充电控制器LTC173317.线性锂电池充电控制器LTC173418.新型开关电源充电控制器LTC198019.开关模式锂电池充电控制器LTC400220.4A锂电池充电器LTC400621.多用途恒压/恒流充电控制器LTC400822.4.2V锂离子/锂聚合物电池充电控制器LTC405223.可由USB端口供电的锂电池充电控制器LTC405324.小型150mA锂电池充电控制器LTC405425.线性锂电池充电控制器LTC405826.单节锂电池线性充电控制器LTC405927.独立线性锂电池充电控制器LTC406128.镍镉/镍氢电池充电控制器M62256FP29.大电流锂/镍镉/镍氢电池充电控制器MAX150130.锂电池线性充电控制器MAX150731.双输入单节锂电池充电控制器MAX1551/MAX155532.单节锂电池充电控制器MAX167933.小体积锂电池充电控制器MAX1736B接口单节锂电池充电控制器MAX181135.多节锂电池充电控制器MAX187336.双路输入锂电池充电控制器MAX187437.单节锂电池线性充电控制器MAX189838.低成本/多种电池充电控制器MAX190839.开关模式单节锂电池充电控制器MAX1925/MAX192640.快速镍镉/镍氢充电控制器MAX2003A/MAX200341.可编程快速充电控制器MAX712/MAX71342.开关式锂电池充电控制器MAX74543.多功能低成本充电控制器MAX846A44.具有温度调节功能的单节锂电池充电控制器MAX8600/MAX860145.锂电池充电控制器MCP73826/MCP73827/MCP7382846.高精度恒压/恒流充电器控制器MCP73841/MCP73842/MCP73843/MCP73844 647.锂电池充电控制器MCP73861/MCP7386248.单节锂电池充电控制器MIC7905049.单节锂电池充电控制器NCP180050.高精度线性锂电池充电控制器VM7205。

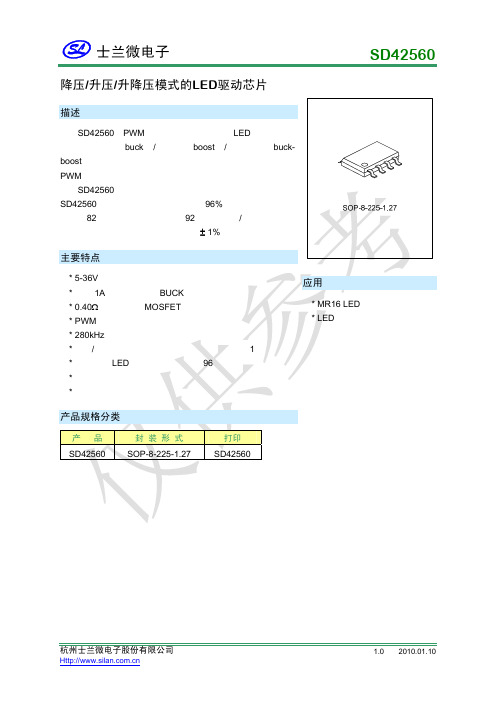

SD42560 LED驱动芯片说明书

1. PWM 调光功能 SD42560 内部设定 PWM 调光功能。当 PWM 电压悬空或者接高电平时,芯片正常工作,当

PWM 电压接低电平时,COMP 脚与芯片断开,电容上的电荷处于保持状态,电平保持,电流比较

杭州士兰微电子股份有限公司

版本号:1.0 2010.01.10 共8页 第4页

功率管漏电流 电流限制 最大占空比 振荡频率

PWM 调光脚开启电压

PWM 调光脚关断电压

PWM 脚下拉电流 PWM 脚上拉电流 COMP 端箝位电压 开关管导通电阻 VDD 电压 采样电压阈值

符号

测试条件

最小值 典型值 最大值

VIN VCC=5/36V,

IIN VPWM=5V

IL

VSW=36V

5

36

I/O 补偿端,外接补偿元件。

6

PWM

I PWM 调光端,外接 PWM 信号改变输出电流的大小。

7

VDD

I 5V 基准输出端。

8

VIN

I 输入电压。

功能描述

SD42560 是电流模式的 LED 驱动电路,可以应用与降压模式(Buck),升压模式(Boost),升 降压模式(Buck-Boost)三种模式。用于满足不同的 LED 应用。

升压/降压模式的工作原理为:在一个工作周期的开始时,内部振荡器输出触发信号,将芯片 内部功率管导通,SW 输出低电平,VIN,电感和内部开关管,GND 组成通路,给电感储能,电感 上的电流增加。LED 上的电流通过 SENSE-和 SENSE+进行采样,将采样值与阈值进行误差放 大,输出信号再与功率管的峰值电流进行比较,当功率管的峰值电流值达到误差放大输出值时, 功率管截止。电感,肖特基,Rs,LED 组成的回路给 LED 供电,电感电流降低。在下一个时钟到 来时,开关管开通,进入下一个开关周期。

锐尔威视A63-Core产品硬件手册说明书

A63-Core 产品硬件手册2020-5-28 Ver.C锐尔威视版本更新说明1. 产品概述1.1 产品简介锐尔威视的A63-Core模块是基于全志A63平台设计的高性价比嵌入式核心模块板。

A63-Core采用130pin邮票孔封装形式,六层高速PCB设计,体积非常小,适合做手持便携类产品。

A63-Core模块集成2GB LPDDR3内存和16GB EMMC存储器,集成PMU芯片,带电池充放电管理。

集成音频Codec功能,GPU为Mali-T760,可满足人脸识别及AI算法的需求,支持硬解H.265/H.264 4K@30fps,提供丰富的外设资源:USB、UART、SDIO、SPI、IIC、GPIO。

支持驱动2个4-lane MIPI 或1个8-lane MIPI接口的显示屏,最大分辨率2560x1600,支持驱动2-lane EDP屏,分辨率1920x1080。

搭载Android7.1操作系统,经过深度优化定制,运行流畅,用户可由PC端的固件修改工具定制个性化固件,如修改开机图片动画声音、设置开机自启动应用、更改LCD屏配置、设置屏幕旋转方向、修改机器信息等1.2 产品规格2. 应用接口2.1 邮票孔接口A63-Core采用邮票孔封装,间距1.2mm,共130个引脚2.1.1 管脚分布2.1.2 管脚定义2.2 电源2.2.1 DC供电A63-Core模块用直流5V电源供电,上电即可开机,电压范围4.8~6V。

用户根据应用场合,选择使用12V或24V降压DC/DC设计电源为保证系统的稳定运行,电源输入处的滤波电容建议不小于100uF。

具体要根据产品应用场合和经验选择合适的电容值2.2.2 电池充电和电池管理使用3.7V锂电池供电A63-Core内置线性充电管理电路,支持对3.7V锂电池进行充电。

支持DC和USB接口充电,当两种充电口同时接通时,优先选择DC充电如需要使用电池给外设(屏,USB)供电,建议用PS接升压IC,升压到5V2.2.3 RTC电源内部VRTC耗电较大,不建议使用,需要使用外挂RTC芯片(PCF8563),软件默认支持外挂RTC。

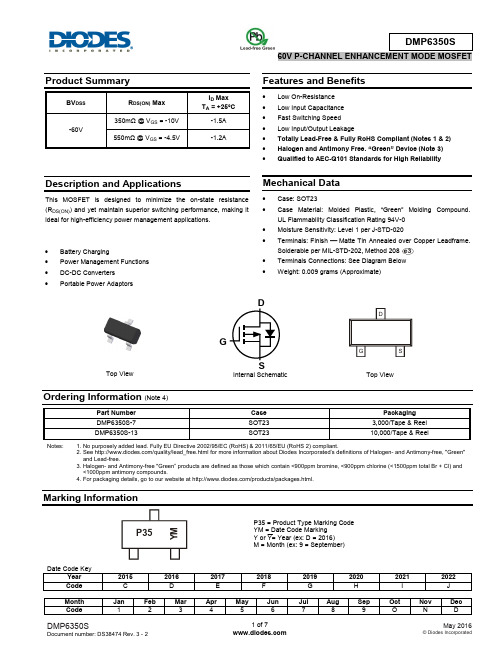

晶体管说明书:Diodes Incorporated DMP6350S 60V P-CHANNEL

Description and ApplicationsThis MOSFET is designed to minimize the on-state resistance (R DS(ON)) and yet maintain superior switching performance, making it ideal for high-efficiency power management applications. ∙ Battery Charging∙ Power Management Functions ∙ DC-DC Converters ∙ Portable Power AdaptorsFeatures and Benefits∙ Low On-Resistance ∙ Low Input Capacitance ∙ Fast Switching Speed ∙ Low Input/Output Leakage∙ Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2) ∙ Halogen and Antimony Free. “Green” Device (Note 3) ∙Qualified to AEC-Q101 Standards for High ReliabilityMechanical Data∙ Case: SOT23∙ Case Material: Molded Plastic, “Green” Molding Compound. UL Flammability Classification Rating 94V-0 ∙ Moisture Sensitivity: Level 1 per J-STD-020∙ Terminals: Finish − Matte Tin Annealed over Copper Leadframe. Solderable per MIL-STD-202, Method 208 ∙ Terminals Connections: See Diagram Below ∙Weight: 0.009 grams (Approximate)Ordering Information (Note 4)Notes: 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS) & 2011/65/EU (RoHS 2) compliant.2. See /quality/lead_free.html for more information about Diodes Incorporated’s definitions of Halogen - and Antimony-free, "Green" and Lead-free.3. Halogen- and Antimony-free "Green” products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and<1000ppm antimony compounds.4. For packaging details, go to our website at /products/packages.html.Marking InformationTop View Internal SchematicTop ViewP35 = Product Type Marking Code YM = Date Code Marking Y or Y= Year (ex: D = 2016) M = Month (ex: 9 = September)DSGP35Y MMaximum Ratings(@T A = +25°C unless otherwise specified.)Thermal CharacteristicsElectrical Characteristics(@T A = +25°C unless otherwise specified.)Notes: 5. Device mounted on FR-4 substrate PC board, 2oz copper, with minimum recommended pad layout.6. Device mounted on FR-4 substrate PC board, 2oz copper, with 1inch square copper plate.7. Short duration pulse test used to minimize self-heating effect.8. Guaranteed by design. Not subject to product testing.4.0-50-25 0 25 50 75 100 125 150R D S (O N ), D R A I N -S O U R C E O N -R E S I S T A N C E (Ω)T J , JUNCTION TEMPERATURE (℃)Figure 7. On-Resistance Variation with JunctionTemperaturePackage Outline DimensionsPlease see /package-outlines.html for the latest version.SOT23Suggested Pad LayoutPlease see /package-outlines.html for the latest version.SOT23All 7°。

E6Y2 E6Y5 E6Y6 32-bit ARM M0-based MCU 技术手册说明书

版本历史版本号说明日期1.0 初版2019-6-171.1 1. 增加型号E6Y6,更新WLCSP25封装引脚图和封装框图2. LRC频率:min(30->27),max(50->62)3. ADC特性更新: fADC-40℃≤ Trange ≤ 85℃,fADC≤14MHz,支持电压范围2.65≤ VDDA ≤5.5V;-40℃≤ Trange ≤ 105℃,fADC≤14MHz,支持电压范围2.7≤ VDDA ≤5.5V;-40℃≤ Trange ≤ 105℃,fADC≤12MHz,支持电压范围2.4≤ VDDA ≤5.5V;进入校准模式,fADC≤12MHz。

进入正常转换模式,fADC≤14MHz。

支持:-40℃≤ Trange ≤ 105℃和电压范围2.4≤ VDDA ≤5.5V;4. ADC特性更新:VDDA=2.4V时,Offset和ERR Gain更新5. 增加QFN28封装热特性2020-7-161.2 1.更新温度传感器线性度参数,区分不同温度范围2020-8-261.3 1.更新QFN32封装信息2.更新订货信息2021-2-31.4 1. 更新QFN32封装公差信息2021-4-141.5 1.修正部分数据单位2021-10-272/57文件编号:CS-QR-YF-054A02目录版本历史 (2)目录 (3)1 介绍 (5)2 功能 (6)3 器件一览 (9)4 引脚描述 (11)4.1LQFP48 (11)4.2QFN32 (11)4.3QFN28 (12)4.4WLCSP25 (12)4.5引脚描述 (13)5 I/O 复用 (17)5.1PA口复用功能 (17)5.2PB口复用功能 (18)6 存储器 (19)7 功能描述 (22)7.1ARM®C ORTEX®-M0内核 (22)7.2存储器 (22)7.3时钟 (22)7.4工作环境 (24)7.4.1 工作电压 (24)7.5启动模式 (24)7.6电源管理 (24)7.6.1 低功耗模式 (24)7.6.2 RTC和不掉电寄存器 (24)7.6.3 上电复位/掉电复位(POR/PDR) (24)7.6.4 低电压复位模块(LVD) (25)7.7通用输入输出端口(GPIO) (25)7.8模数转换器(ADC) (25)7.8.1 温度传感器(TS) (25)7.8.2 内部参考电压 (25)7.8.3 VBAT监测 (26)7.9定时器 (26)7.9.1 高级定时器 (TIM1) (26)7.9.2 通用定时器 (TIM2, 3, 14, 15,16, 17) (26)7.9.3 基本定时器(TIM6) (27)7.9.4 独立看门狗定时器(FWDT) (27)7.9.5 窗看门狗定时器(WWDT) (27)7.9.6 滴答定时器(SysTick) (27)7.10直接内存存取(DMA) (27)3/57文件编号:CS-QR-YF-054A027.11中断和事件 (27)7.12实时时钟(RTC)和不掉电寄存器 (27)7.13串行外设总线(SPI)/集成电路内置音频总线(I2S) (28)7.14通用同步异步收发器(USART) (28)7.15I2C接口 (29)7.16循环冗余校验 (29)7.17串行调试端口(SWD-DP) (29)8 电气特性 (30)8.1说明 (30)8.2绝对最大额定值 (31)8.3工作条件 (31)8.4I/O端口特性 (32)8.5低功耗模式唤醒时间 (33)8.6RC振荡器特性 (33)8.7晶振特性 (34)8.8外部时钟特性 (36)8.9PLL特性 (36)8.10功耗 (36)8.11内部参考电压特性 (38)8.12ADC特性 (38)8.13温度传感器特性 (39)8.14VBAT监测器特性 (39)8.15F LASH特性 (39)8.16定时器特性 (39)8.17SPI/I2S特性 (40)8.18I2C特性 (43)8.19ESD特性 (44)9 封装信息 (45)9.1LQFP48 (45)9.2QFN32(0505×0.55-E=0.50) (46)9.3QFN32(0505×0.75-E=0.50) (47)9.4QFN28 (49)9.5WLCSP25 (50)10 产品命名规则 (52)10.1产品丝印说明 (52)11 订货信息 (53)12 勘误表 (54)13 缩略语 (55)14 销售和服务 (57)4/57文件编号:CS-QR-YF-054A021介绍CS32F031系列微控制器采用高性能的32位ARM® Cortex®-M0 内核,嵌入高达64K Bytes flash和8K Bytes SRAM,最高工作频率48MHz。

EMD56324P-60资料